**Titre:** Traçage et profilage d'applications d'apprentissage automatique de type flot de données utilisant un processeur graphique

**Title:** Traçage et profilage d'applications d'apprentissage automatique de type flot de données utilisant un processeur graphique

**Auteur:** Pierre Zins

Author:

**Date:** 2018

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Zins, P. (2018). Traçage et profilage d'applications d'apprentissage automatique de type flot de données utilisant un processeur graphique [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

**Citation:** <https://publications.polymtl.ca/3242/>

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/3242/>

PolyPublie URL:

**Directeurs de recherche:** Michel Dagenais

Advisors:

**Programme:** Génie informatique

Program:

UNIVERSITÉ DE MONTRÉAL

TRAÇAGE ET PROFILAGE D'APPLICATIONS D'APPRENTISSAGE

AUTOMATIQUE DE TYPE FLOT DE DONNÉES UTILISANT UN PROCESSEUR

GRAPHIQUE

PIERRE ZINS

DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

AOÛT 2018

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

TRAÇAGE ET PROFILAGE D'APPLICATIONS D'APPRENTISSAGE

AUTOMATIQUE DE TYPE FLOT DE DONNÉES UTILISANT UN PROCESSEUR

GRAPHIQUE

présenté par : ZINS Pierre

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. ANTONIOL Giuliano, Ph. D., président

M. DAGENAIS Michel, Ph. D., membre et directeur de recherche

M. ALOISE Daniel, Ph. D., membre

**DÉDICACE**

*À mes parents, mon frère et ma famille pour leur grande confiance

et leur soutien sans faille tout au long de mes études,

malgré la distance.*

## REMERCIEMENTS

Je tiens tout d'abord à remercier mon directeur de recherche Michel Dagenais qui m'a accompagné tout au long de ce projet. Son suivi constant, sa disponibilité, ses connaissances techniques ainsi que ses nombreux conseils ont été très précieux pour l'avancement du projet.

Je souhaite également remercier les deux associés de recherche, Geneviève et Naser, pour leurs conseils et les nombreuses aides qu'ils ont pu apporter. Leurs très bonnes connaissances et leur expérience dans le domaine ont constitué une aide significative pour mon travail.

Merci ensuite à tous mes collègues et amis du laboratoire DORSAL pour leur bonne humeur et les agréables moments partagés. Cela a représenté un élément clé pour l'avancement de mon travail. De même, je remercie toutes les personnes avec qui j'ai pu discuter à propos de mon projet de recherche et qui m'ont permis d'avoir des conseils et commentaires quant à mon travail.

Enfin, je souhaite également souligner le support financier de la part des partenaires industriels : Ericsson, EfficiOS, Ciena, Google, Prompt et le Conseil de Recherches en Sciences Naturelles et en génie du Canada (CRSNG). Merci également à AMD pour leur don de matériel ainsi que leur disponibilité qui ont rendu possible ce projet de recherche.

## RÉSUMÉ

Actuellement, les besoins en puissance de calcul sont de plus en plus importants, alors que les améliorations au niveau du matériel commencent à ralentir. La puissance des processeurs et notamment leur fréquence de fonctionnement stagnent pour des raisons physiques comme la finesse de gravure ou la dissipation de chaleur.

Afin de surpasser ces limites, le calcul en parallèle semble être une solution prometteuse avec l'utilisation d'architectures hétérogènes. Ces dernières mettent en œuvre une combinaison de plusieurs unités de calculs de types possiblement différents, ce qui leur permet d'offrir un fonctionnement hautement parallèle. Malgré tout, utiliser l'ensemble du matériel efficacement reste difficile, et la programmation au niveau logiciel de ces architectures pose problème. Par conséquent, différents modèles ont émergé avec notamment les approches flot de données. Ces dernières proposent des caractéristiques très adaptées pour ce genre de contexte parallèle. Elles permettent de programmer plus facilement les différentes unités de calcul afin de bénéficier au maximum du matériel disponible.

Dans un contexte de recherche de performance optimale, il est essentiel d'avoir des outils permettant de diagnostiquer d'éventuels problèmes. Quelques solutions ont déjà pu démontrer leur efficacité dans le cas d'un modèle de programmation plus traditionnel et séquentiel, utilisant ou non un processeur graphique. On retrouve par exemple des outils comme *LTtng* ou *Ftrace* destinés à l'analyse du processeur central. Concernant les processeurs graphiques, les outils propriétaires et à sources fermées, proposés par les constructeurs sont en général les plus complets et privilégiés par les programmeurs. Cela présente toutefois une limite, puisque les solutions ne sont pas générales et restent dépendantes du matériel proposé par un constructeur. Par ailleurs, elles offrent une flexibilité limitée avec des visualisations et analyses définies et fixes qui ne peuvent ni être modifiées ni améliorées en fonction des besoins d'un utilisateur. Finalement, aucun outil existant ne s'intéresse spécifiquement aux modèles flot de données.

Dans le cadre de ce projet de recherche, nous essayons donc de répondre à ces manques. Nous cherchons à proposer un outil ou une technique pour le diagnostic et l'analyse de performance destiné aux applications basées sur des approches flot de données et s'exécutant sur une architecture hétérogène. Nous nous concentrerons sur le cas où le processeur traditionnel est accompagné par un processeur graphique afin d'accélérer certaines tâches impliquant beaucoup de calculs sur un grand ensemble de données. Notre travail est basé sur des techniques de traçage et de profilage et a pour objectif de rester relativement général. Ainsi,

même si l'implémentation proposée est destinée à la bibliothèque logicielle TensorFlow, il serait envisageable de l'appliquer à d'autres cas. TensorFlow est l'un des outils phare pour l'apprentissage automatique et propose un fonctionnement basé sur un modèle flot de données avec un graphe de calcul. Cette bibliothèque est évidemment destinée à une utilisation sur une architecture hétérogène avec notamment un ou plusieurs processeurs graphiques. Par ailleurs, un mode de fonctionnement distribué est aussi proposé et sera étudié. TensorFlow supporte de manière officielle les processeurs graphiques Nvidia mais plusieurs travaux visent à étendre cela à d'autres constructeurs. On note une première solution basée sur la plateforme ROCm de AMD. La seconde option concerne la spécification SYCL qui propose une couche d'abstraction haut niveau au-dessus d'OpenCL afin de programmer un processeur graphique. La technique proposée est générale et fonctionne avec les trois possibilités offertes par TensorFlow pour utiliser un processeur graphique. Elle permet de collecter un grand nombre de données à propos de divers éléments et de les combiner dans une trace. Par la suite, un traitement de cette dernière ainsi que plusieurs méthodes de visualisations permettent de dégager des informations intéressantes à propos de l'exécution d'une application. À partir de ces résultats, une analyse de la performance est possible pour détecter une utilisation inefficace du matériel disponible, des éléments limitants ou des parties propices à des optimisations. Dans ce mémoire, nous présentons différents cas pour lesquels les résultats fournis à l'utilisateur ont permis d'optimiser une application et de réduire le temps d'exécution. Finalement, nous nous assurons que le surcoût introduit par notre technique reste raisonnable et ne compromet pas son utilisation.

## ABSTRACT

Recently, increasing computing capabilities have been required in various areas like scientific computing, video games and graphical rendering or artificial intelligence. These domains usually involve the processing of a large amount of data, intended to be performed as fast as possible. Unfortunately, hardware improvements have recently slowed down. The CPU clock speed, for example, is not increasing much any more, possibly nearing technological limits. Physical constraints like the heat dissipation or fine etching are the main reasons for that.

Consequently, new opportunities like parallel processing using heterogeneous architectures became popular. In this context, the traditional processors get support from other computing units like graphical processors. In order to program these, the dataflow model offers several advantages. It is inherently parallel and thus well adapted.

In this context, guaranteeing optimal performances is another main concern. For that, tracing and profiling central processing and graphical processing units are two useful techniques that can be considered. Several tools exist, like *LTTng* and *FTrace* that can trace the operating system and focus on the central processor. In addition, proprietary tools offered by hardware vendors can help to analyze and monitor the graphical processor. However, these tools are specific to one type of hardware and lack flexibility. Moreover, none of them target in particular dataflow applications executed on a heterogeneous platform.

Through this research project, our objective is to provide a very flexible and complete performance analysis environment with information related to the traditional processor, the graphical processor, the operating system and also the dataflow model. We evaluate our solution with TensorFlow, a popular machine learning and deep learning library that uses a dataflow model for the execution. In our project, we focused on this library but our work remains generally applicable, and the implementation for another library is possible.

The proposed method is based on collecting information during the execution of an application by using tracing and profiling. After this step, we obtain a trace that contains numerous events. Then, the trace is post-processed and analyzed. Graphical visualizations are offered to the user and help to understand the execution of an application as well as its performance.

To demonstrate the efficiency of our proposed technique, we present several examples in which the information collected, the analyses and the visualizations offered are helpful for the user. We show that we are able to optimize a TensorFlow application by using the results of our tracing and profiling method. Most of the time, it consists in an execution time or

memory usage reduction. Finally, we also measure the introduced overhead to demonstrate that it stays reasonable and does not represent a serious drawback for our work.

## TABLE DES MATIÈRES

|                                                                               |      |

|-------------------------------------------------------------------------------|------|

| DÉDICACE . . . . .                                                            | iii  |

| REMERCIEMENTS . . . . .                                                       | iv   |

| RÉSUMÉ . . . . .                                                              | v    |

| ABSTRACT . . . . .                                                            | vii  |

| TABLE DES MATIÈRES . . . . .                                                  | ix   |

| LISTE DES TABLEAUX . . . . .                                                  | xii  |

| LISTE DES FIGURES . . . . .                                                   | xiii |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                                    | xvii |

| <br>CHAPITRE 1 INTRODUCTION . . . . .                                         | 1    |

| 1.1 Définitions et concepts de base . . . . .                                 | 1    |

| 1.1.1 Processeur graphique et processeur central . . . . .                    | 1    |

| 1.1.2 Traçage, instrumentation et profilage . . . . .                         | 2    |

| 1.1.3 Visualisation des résultats . . . . .                                   | 2    |

| 1.2 Éléments de la problématique . . . . .                                    | 3    |

| 1.3 Objectifs de recherche . . . . .                                          | 5    |

| 1.3.1 Questions de recherche . . . . .                                        | 5    |

| 1.3.2 Objectifs spécifiques . . . . .                                         | 5    |

| 1.3.3 Hypothèse de recherche . . . . .                                        | 5    |

| 1.4 Plan du mémoire . . . . .                                                 | 6    |

| <br>CHAPITRE 2 REVUE DE LITTÉRATURE . . . . .                                 | 7    |

| 2.1 Modèle flot de données . . . . .                                          | 7    |

| 2.1.1 Principes théoriques . . . . .                                          | 7    |

| 2.1.2 Langages de type flot de données . . . . .                              | 8    |

| 2.1.3 Méthodes et techniques flot de données . . . . .                        | 9    |

| 2.1.4 Modèle flot de données appliqué à l'apprentissage automatique . . . . . | 10   |

| 2.2 Architectures hétérogènes et processeurs graphiques . . . . .             | 14   |

| 2.2.1 Architectures hétérogènes . . . . .                                     | 14   |

|       |                                                                                                         |    |

|-------|---------------------------------------------------------------------------------------------------------|----|

| 2.2.2 | Historique . . . . .                                                                                    | 15 |

| 2.2.3 | Architectures . . . . .                                                                                 | 16 |

| 2.2.4 | Librairies pour le calcul parallèle sur GPU . . . . .                                                   | 18 |

| 2.2.5 | OpenCL . . . . .                                                                                        | 21 |

| 2.2.6 | HSA . . . . .                                                                                           | 22 |

| 2.2.7 | HIP . . . . .                                                                                           | 22 |

| 2.3   | Traçage et profilage . . . . .                                                                          | 23 |

| 2.3.1 | Traçage et profilage du processeur traditionnel . . . . .                                               | 23 |

| 2.3.2 | Traçage et profilage du processeur graphique . . . . .                                                  | 27 |

| 2.4   | Analyse et visualisation des résultats . . . . .                                                        | 37 |

| 2.4.1 | Babeltrace . . . . .                                                                                    | 37 |

| 2.4.2 | Trace Compass . . . . .                                                                                 | 38 |

| 2.5   | Profilage d'applications flot de données . . . . .                                                      | 39 |

| 2.6   | Conclusion de la revue de littérature . . . . .                                                         | 41 |

|       | CHAPITRE 3 MÉTHODOLOGIE . . . . .                                                                       | 43 |

| 3.1   | Utilisation de TensorFlow avec un processeur graphique . . . . .                                        | 43 |

| 3.2   | Environnement de travail . . . . .                                                                      | 45 |

| 3.3   | Traçage et profilage avec la technique proposée . . . . .                                               | 46 |

| 3.4   | Code source du travail . . . . .                                                                        | 48 |

|       | CHAPITRE 4 ARTICLE 1 : TRACING AND PROFILING MACHINE LEARNING<br>DATAFLOW APPLICATIONS ON GPU . . . . . | 49 |

| 4.1   | Introduction . . . . .                                                                                  | 49 |

| 4.2   | Related work . . . . .                                                                                  | 52 |

| 4.2.1 | CPU tracing and profiling . . . . .                                                                     | 52 |

| 4.2.2 | GPU tracing and profiling . . . . .                                                                     | 53 |

| 4.2.3 | Dataflow profiling . . . . .                                                                            | 54 |

| 4.3   | Background . . . . .                                                                                    | 55 |

| 4.3.1 | TensorFlow concepts . . . . .                                                                           | 55 |

| 4.3.2 | TensorFlow with a GPU . . . . .                                                                         | 56 |

| 4.4   | Proposed method . . . . .                                                                               | 56 |

| 4.4.1 | Architecture . . . . .                                                                                  | 57 |

| 4.4.2 | Multilevel Data Collection . . . . .                                                                    | 57 |

| 4.4.3 | Trace Correlation and Analysis . . . . .                                                                | 66 |

| 4.4.4 | Visualization . . . . .                                                                                 | 68 |

| 4.5   | Use cases . . . . .                                                                                     | 72 |

|                                              |                                               |     |

|----------------------------------------------|-----------------------------------------------|-----|

| 4.5.1                                        | Triplet loss example . . . . .                | 72  |

| 4.5.2                                        | Compute-bound example . . . . .               | 76  |

| 4.5.3                                        | Distributed Dataflow graph . . . . .          | 79  |

| 4.5.4                                        | Inference example . . . . .                   | 83  |

| 4.5.5                                        | Memory management example . . . . .           | 85  |

| 4.6                                          | Evaluation . . . . .                          | 87  |

| 4.6.1                                        | Setup . . . . .                               | 89  |

| 4.6.2                                        | Overhead analysis and discussion . . . . .    | 89  |

| 4.7                                          | Conclusion and future work . . . . .          | 94  |

| <br>CHAPITRE 5 DISCUSSION GÉNÉRALE . . . . . |                                               | 95  |

| 5.1                                          | Cas d'utilisation . . . . .                   | 95  |

| 5.2                                          | Utilisation . . . . .                         | 95  |

| 5.3                                          | Performance . . . . .                         | 96  |

| 5.4                                          | Contributions additionnelles . . . . .        | 96  |

| <br>CHAPITRE 6 CONCLUSION . . . . .          |                                               | 98  |

| 6.1                                          | Synthèse des travaux . . . . .                | 98  |

| 6.2                                          | Limitations de la solution proposée . . . . . | 99  |

| 6.3                                          | Améliorations futures . . . . .               | 100 |

| <br>RÉFÉRENCES . . . . .                     |                                               | 102 |

**LISTE DES TABLEAUX**

|             |                                                                                                   |    |

|-------------|---------------------------------------------------------------------------------------------------|----|

| Tableau 3.1 | Configuration matérielle . . . . .                                                                | 45 |

| Tableau 3.2 | Configuration logicielle . . . . .                                                                | 46 |

| Table 4.1   | Most demanding nodes of the graph. Several of them are related to the MaxPool operations. . . . . | 77 |

| Table 4.2   | Hardware and software configuration . . . . .                                                     | 89 |

| Table 4.3   | Benchmark : Autoencoder - ROCm platform . . . . .                                                 | 90 |

| Table 4.4   | Benchmark : Autoencoder - CUDA . . . . .                                                          | 91 |

| Table 4.5   | Benchmark : Autoencoder - SYCL . . . . .                                                          | 92 |

| Table 4.6   | Benchmark : Convolutional Neural Network - ROCm platform . . . . .                                | 92 |

| Table 4.7   | Benchmark : Convolutional Neural Network - CUDA . . . . .                                         | 93 |

| Table 4.8   | Benchmark : Convolutional Neural Network - SYCL . . . . .                                         | 93 |

## LISTE DES FIGURES

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

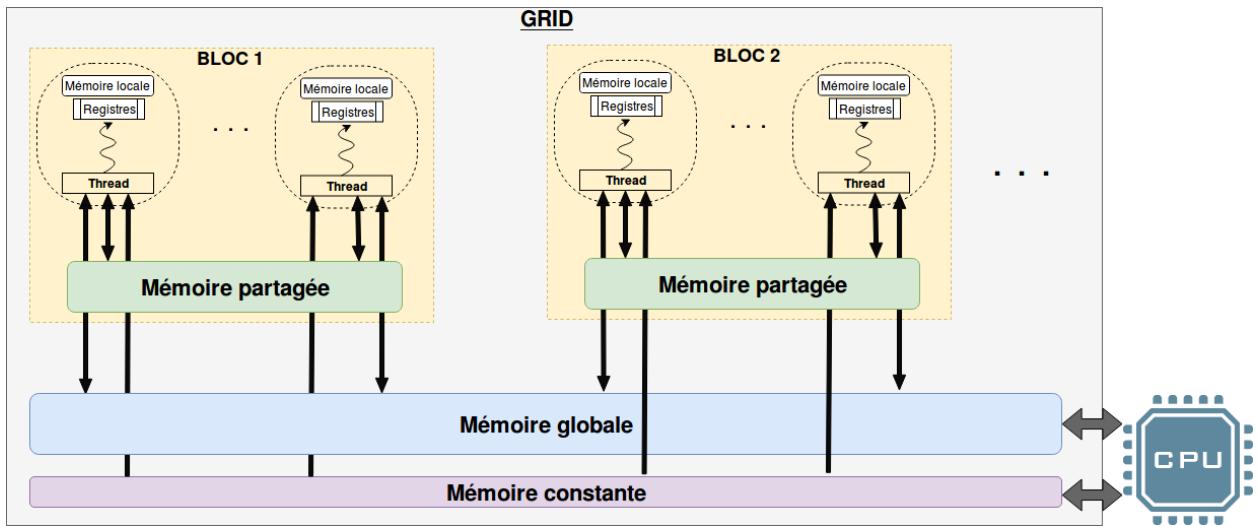

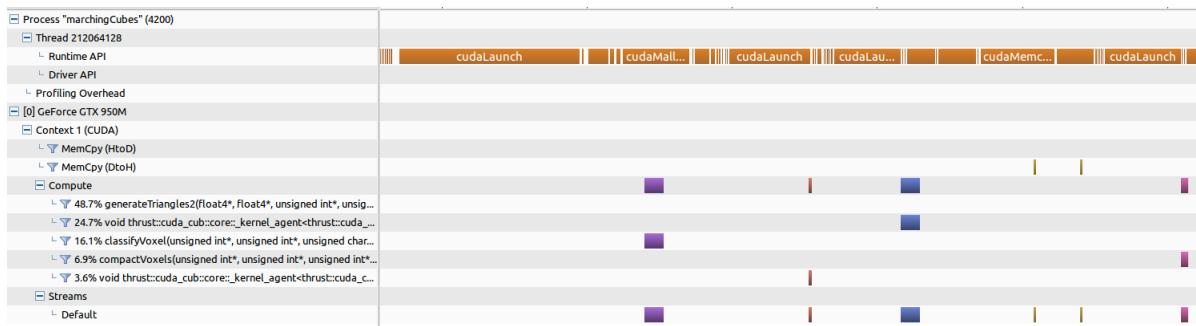

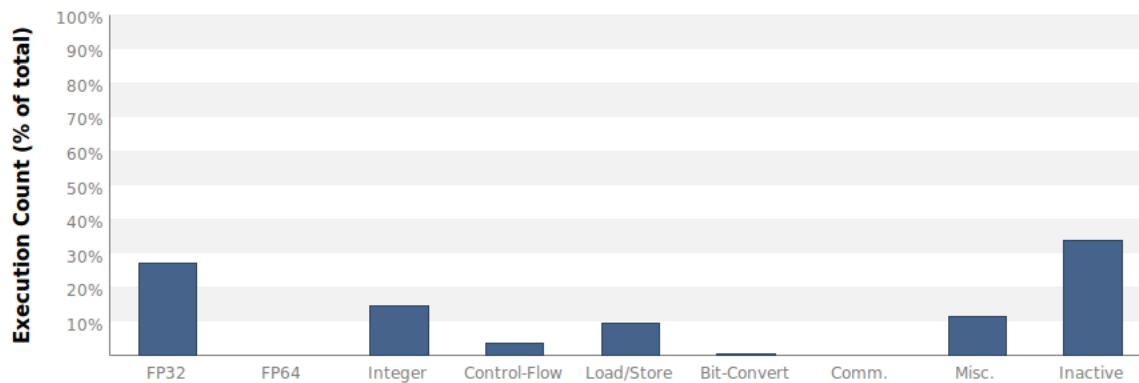

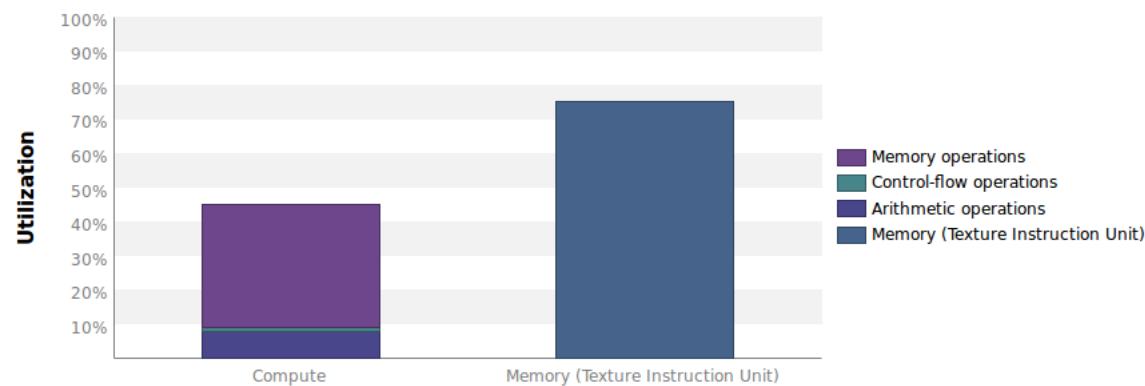

| <p>Figure 2.1 Exemple de modèle flot de données. Les données de départ sont fournies en entrée aux noeuds 1 et 3. Elles circulent ensuite le long des arcs et sont traitées par chaque noeud. Le résultat final correspond à la sortie du noeud 8. . . . .</p> <p>Figure 2.2 Tensorboard : visualisation du graphe d'un réseau de neurones ayant deux couches cachées et une couche de sortie. Une partie annexe du graphe va gérer la propagation arrière et le calcul des gradients mais n'est pas représentée ici. . . . .</p> <p>Figure 2.3 Exemple de programme TensorFlow . . . . .</p> <p>Figure 2.4 Graphe de calcul correspondant au code précédent . . . . .</p> <p>Figure 2.5 Modèle d'exécution de CUDA. La grille et les différents blocs peuvent avoir 1, 2 ou 3 dimensions. . . . .</p> <p>Figure 2.6 Modèle de mémoire utilisé par CUDA . . . . .</p> <p>Figure 2.7 Exemple de résultat de profilage avec <code>nvprof</code>. On retrouve une ligne pour chaque opération effectuée sur le processeur graphique (noyau de calcul, copie de données). Plusieurs statistiques sont disponibles : le nombre total d'appels, la durée totale, la durée moyenne, les durées maximale et minimale. . . . .</p> <p>Figure 2.8 Graphique temporel de l'exécution d'une application. Cette visualisation est disponible avec <b>Nvidia Visual Profiler</b>. On retrouve plusieurs lignes représentant les appels de fonction à l'API CUDA, les transferts de mémoire, les noyaux de calculs exécutés par le GPU ainsi que les streams (ou files) dans lesquelles les opérations destinées au processeur graphique ont été soumises. . . . .</p> <p>Figure 2.9 L'analyse automatique de <b>Nvidia Visual Profiler</b> propose un classement des noyaux de calcul en fonction de l'importance de leur optimisation. Les critères utilisés sont la durée d'exécution ainsi que le taux d'occupation atteint par chaque noyau. Ainsi, les noyaux les mieux classés sont les plus intéressants à optimiser afin de gagner en performance. . . . .</p> <p>Figure 2.10 Graphique présentant le nombre d'exécution de chaque type d'instruction sous la forme de pourcentage. Cela concerne l'exécution d'un unique noyau de calcul. . . . .</p> | <p style="text-align: right;">8</p> <p style="text-align: right;">11</p> <p style="text-align: right;">13</p> <p style="text-align: right;">13</p> <p style="text-align: right;">19</p> <p style="text-align: right;">20</p> <p style="text-align: right;">28</p> <p style="text-align: right;">29</p> <p style="text-align: right;">29</p> <p style="text-align: right;">30</p> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                                                                                                                                                                                                                                                                                                  |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.11 | Graphique proposé par <b>Nvidia Visual Profiler</b> montrant l'utilisation de l'unité de calcul et de mémoire. Il permet d'expliquer à l'utilisateur si l'exécution d'un noyau de calcul est limitée par les calculs ou par la mémoire. . . . .                                                  | 30 |

| Figure 2.12 | Information détaillée à propos de l'utilisation des différents composants de mémoire (mémoire partagée, cache L2, cache unifié, mémoire globale). . . . .                                                                                                                                        | 31 |

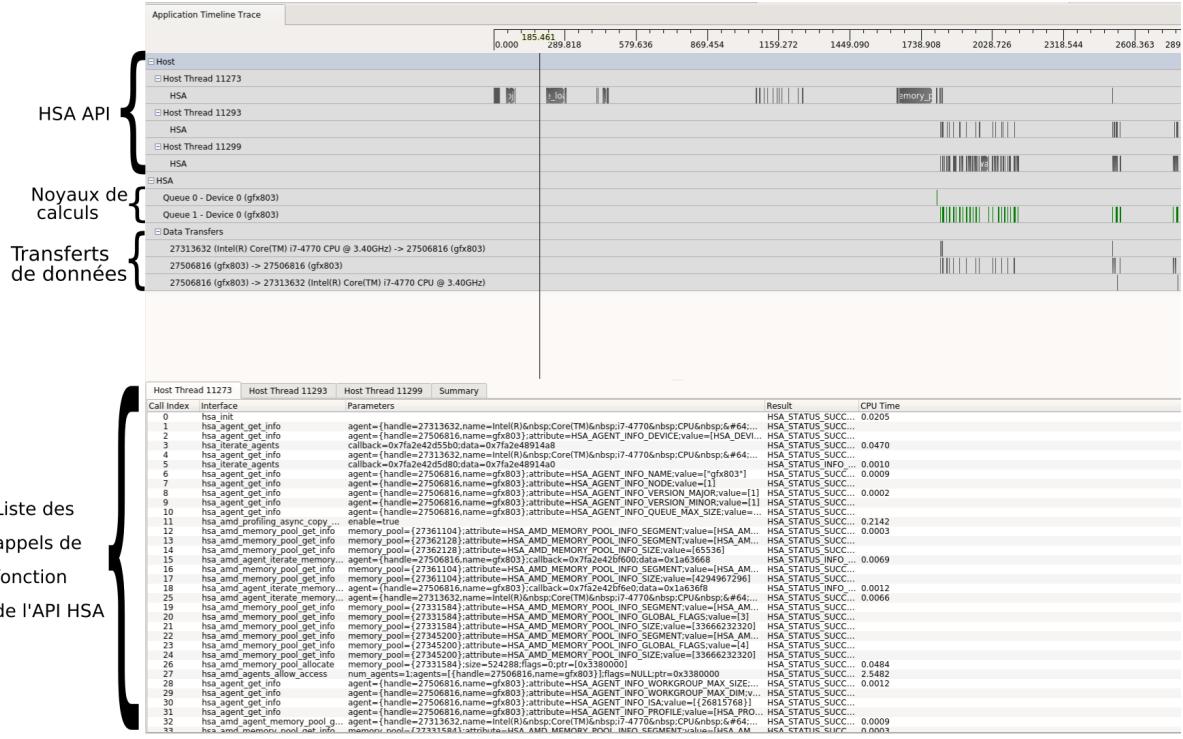

| Figure 2.13 | Vue temporelle CodeXL. On peut suivre l'ensemble des appels de fonction de l'API HSA, les noyaux de calculs exécutés ainsi que les transferts de données entre la mémoire centrale et celle de la carte graphique. . . . .                                                                       | 33 |

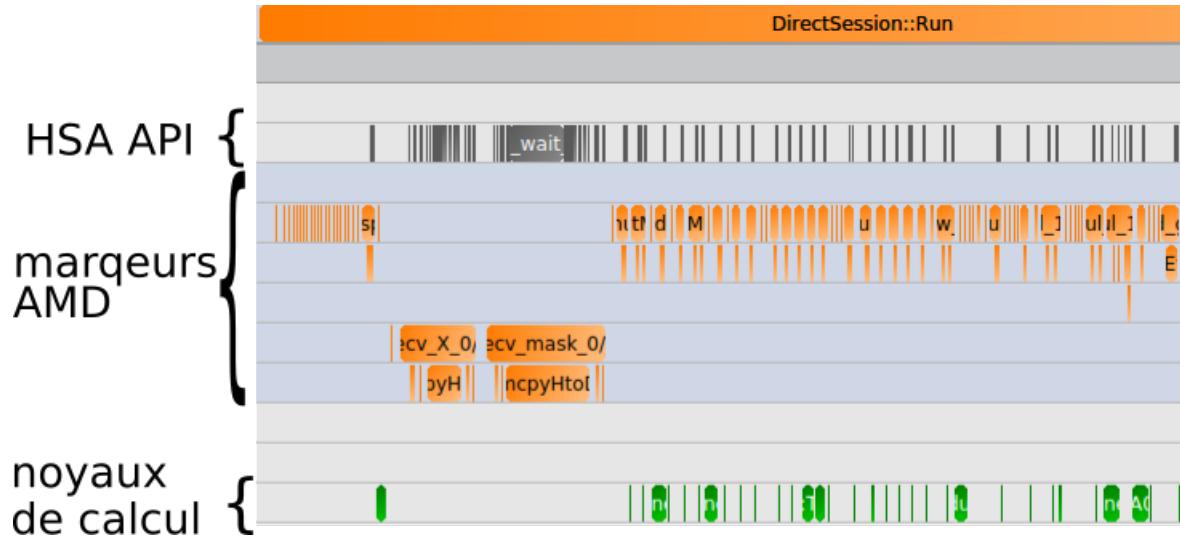

| Figure 2.14 | Vue temporelle du profilage d'une application ayant été instrumentée avec les marqueurs AMD. L'ensemble des événements liés à l'instrumentation statique sont présentés en orange. . . . .                                                                                                       | 34 |

| Figure 2.15 | Vue présentant les compteurs de performance sous la forme d'un tableau. Chaque ligne montre différentes métriques à propos de l'exécution d'un noyau de calcul. . . . .                                                                                                                          | 35 |

| Figure 2.16 | Exemple de trace du noyau Linux générée avec LTTng et visualisée avec Babeltrace. . . . .                                                                                                                                                                                                        | 38 |

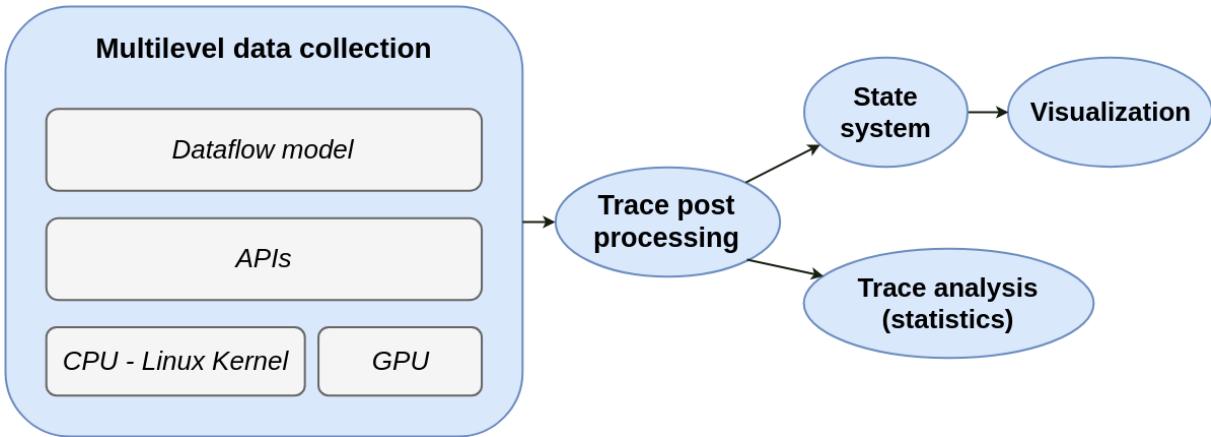

| Figure 4.1  | Performance analysis architecture. Information about different components is collected at several levels. The resulting trace is post-processed and then the results can be statistically analyzed or graphically visualized. . . . .                                                            | 57 |

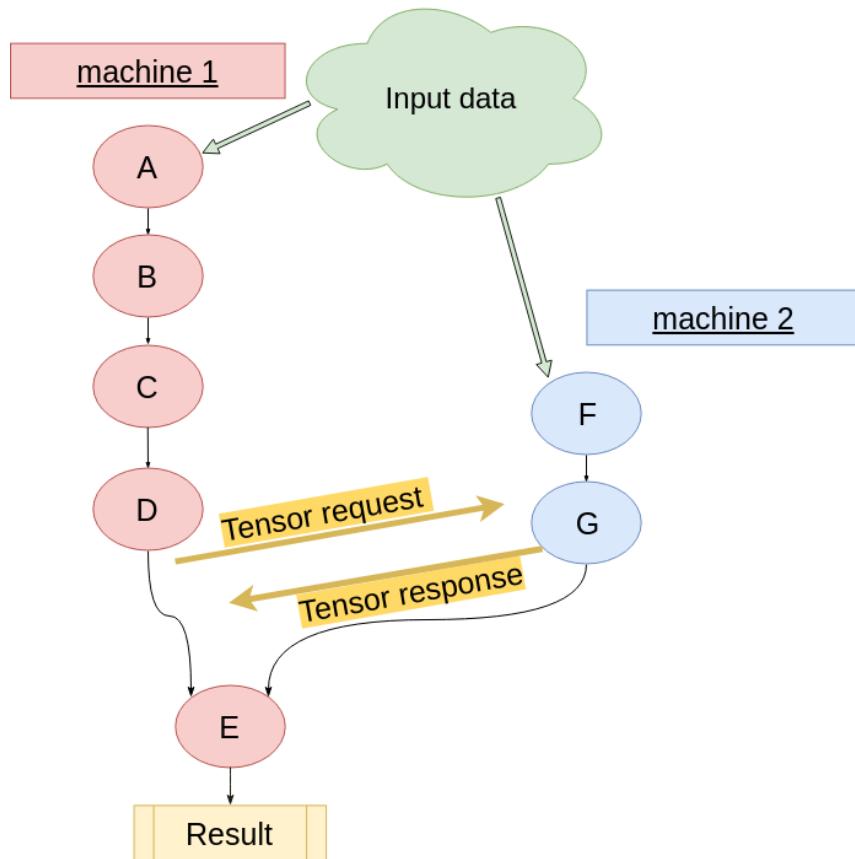

| Figure 4.2  | Distributed dataflow example : the graph is shared among two machines and data is fed to two input nodes (A and F). The computation of node E (assigned to machine 1) needs the result of node G (assigned to machine 2). Therefore, a tensor exchange between the machines is required. . . . . | 62 |

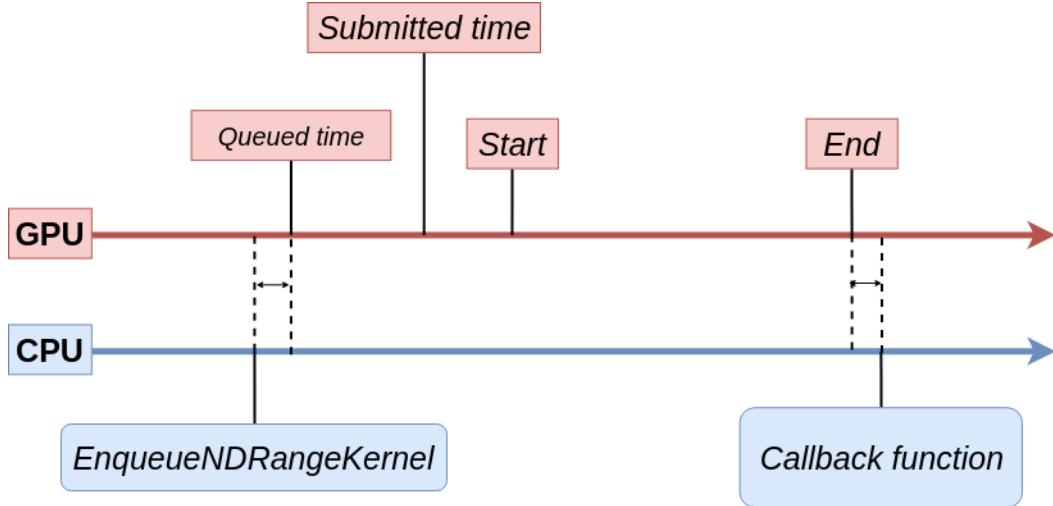

| Figure 4.3  | OpenCL profiling : Several events happen on both devices and the corresponding timestamps can be collected and used for synchronization . . . . .                                                                                                                                                | 68 |

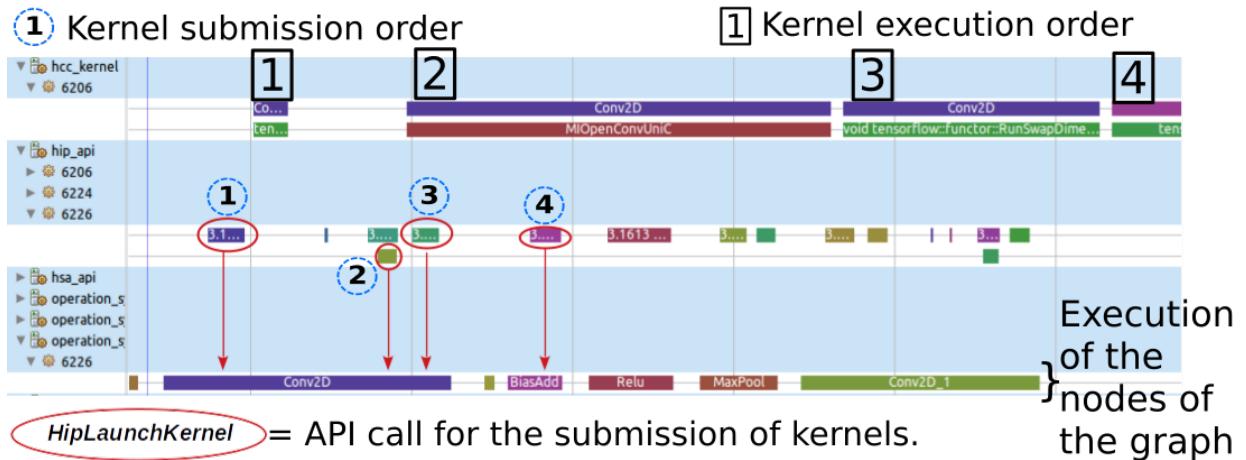

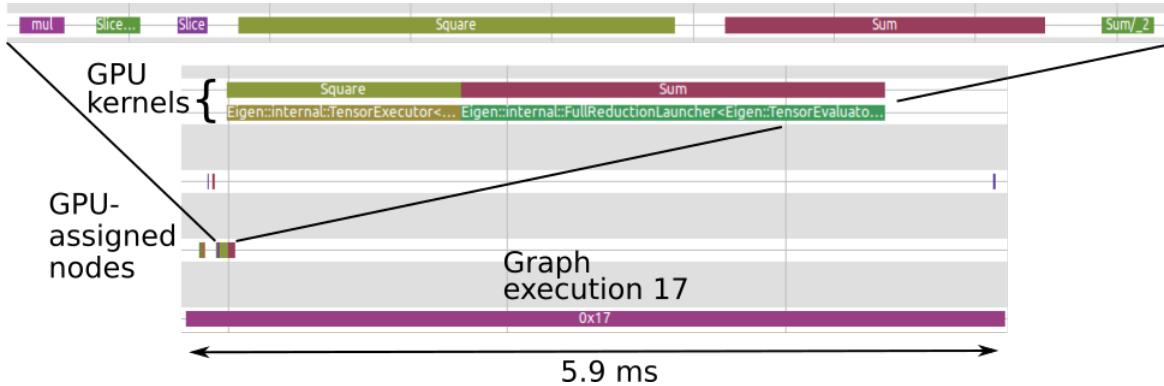

| Figure 4.4  | Example of matching of the GPU kernels with the nodes from the computation graph . . . . .                                                                                                                                                                                                       | 68 |

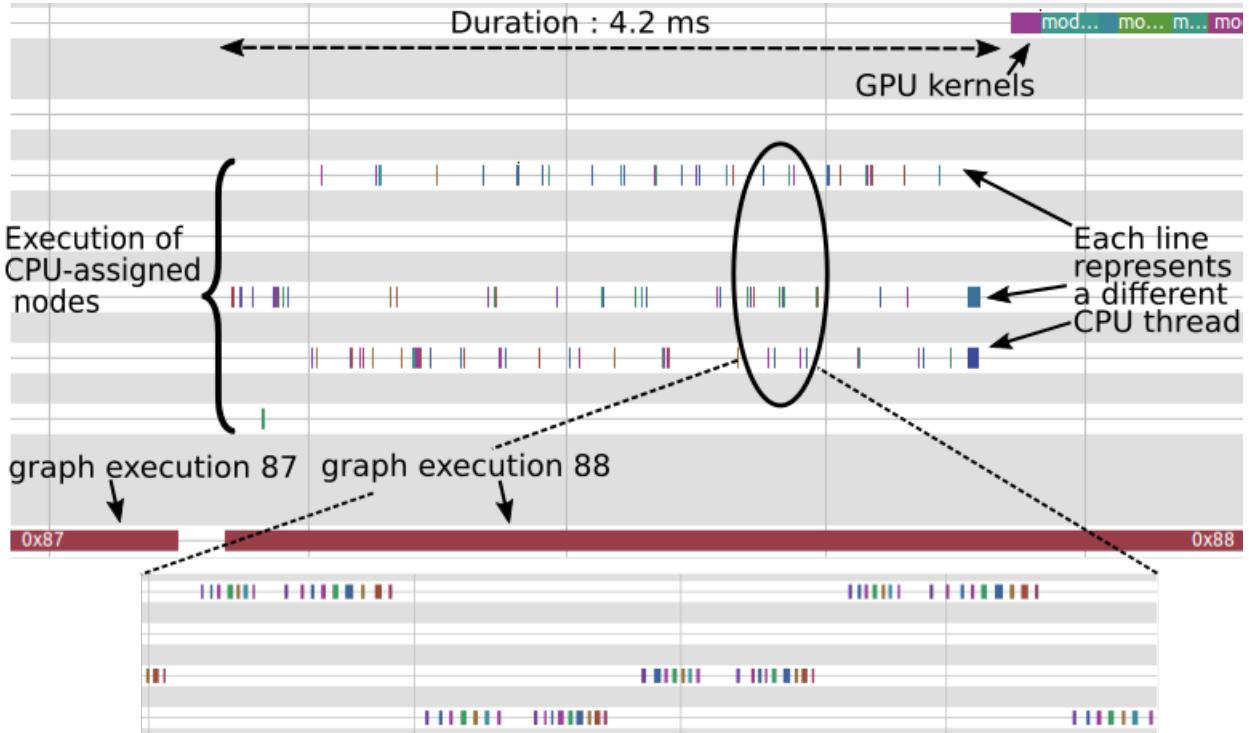

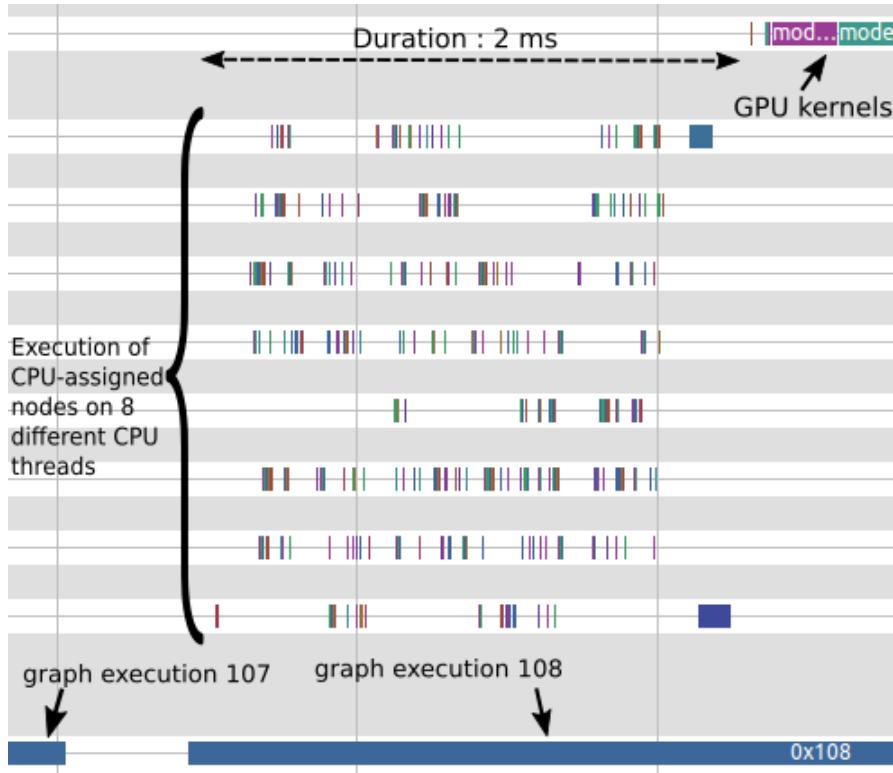

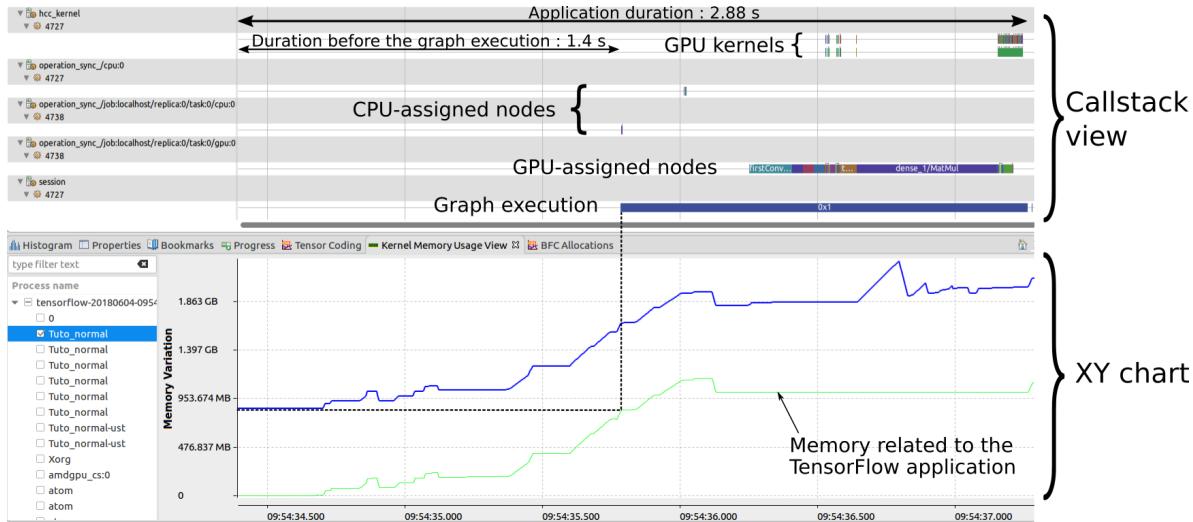

| Figure 4.5  | Initial application : the beginning of the 88 <sup>th</sup> execution of the graph is shown. The GPU waits for a significant time before starting its job, and the CPU seems to inefficiently process some nodes during this time. . . . .                                                       | 73 |

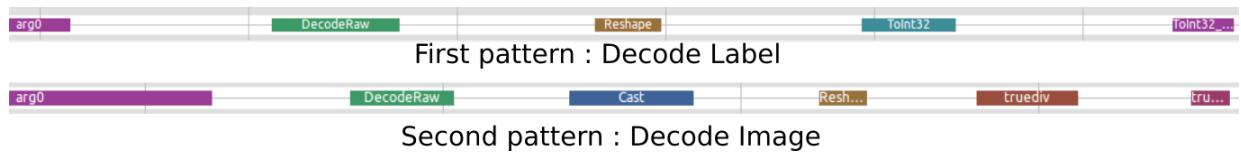

| Figure 4.6  | CPU-assigned pre-processing operations : The CPU processes many times these two sequences of nodes before the GPU starts. . . . .                                                                                                                                                                | 73 |

|             |                                                                                                                                                                                                                                                                                                                                                                         |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.7  | Execution with the first optimization : setting <i>num_parallel_calls</i> to 8. The processing done on the CPU has been parallelized and is more efficient now. Significant time was saved. . . . .                                                                                                                                                                     | 74 |

| Figure 4.8  | Execution with the two optimizations : setting <i>num_parallel_calls</i> to 8 and <i>prefetch</i> to 1. In addition to the parallelization of CPU work, pipelining has been added and increases again the performance. . . . .                                                                                                                                          | 75 |

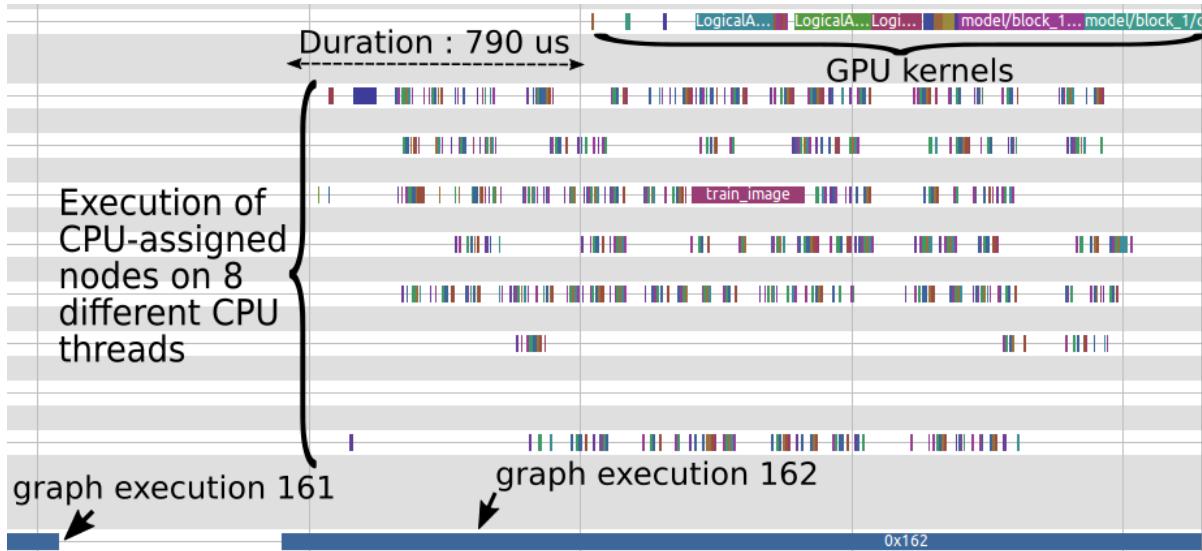

| Figure 4.9  | Initial execution with the convolution and maxpool operations. The GPU seems to be in use all the time. . . . .                                                                                                                                                                                                                                                         | 76 |

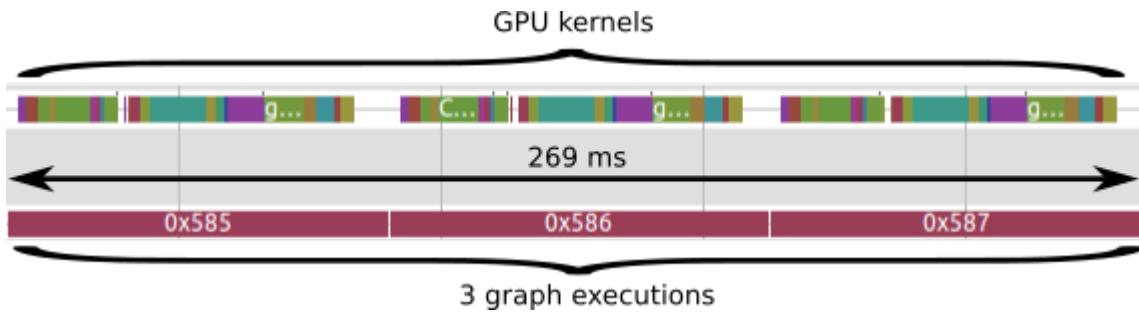

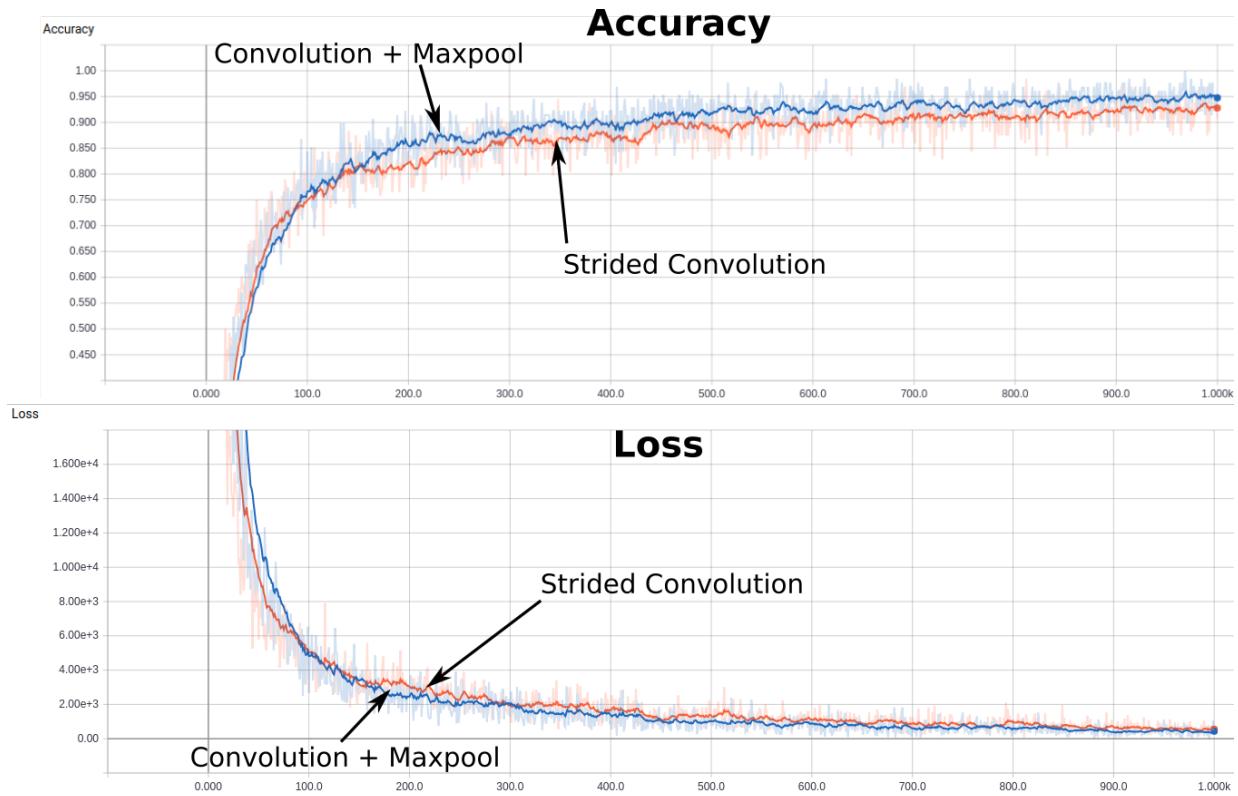

| Figure 4.10 | Evolution of the accuracy and the loss after 1000 iterations. The accuracy loss caused by the use of strided convolutions with no maxpool layer is subtle. . . . .                                                                                                                                                                                                      | 78 |

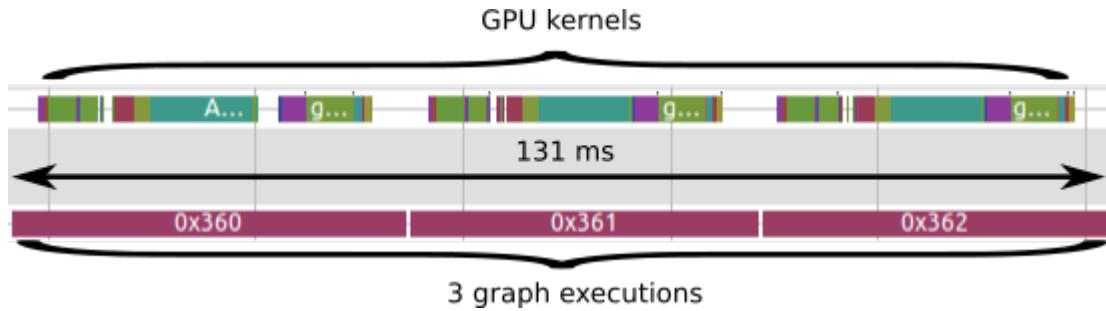

| Figure 4.11 | Execution with the strided convolution. The GPU is still used all the time, but the duration of 3 executions of the graph has been reduced.                                                                                                                                                                                                                             | 79 |

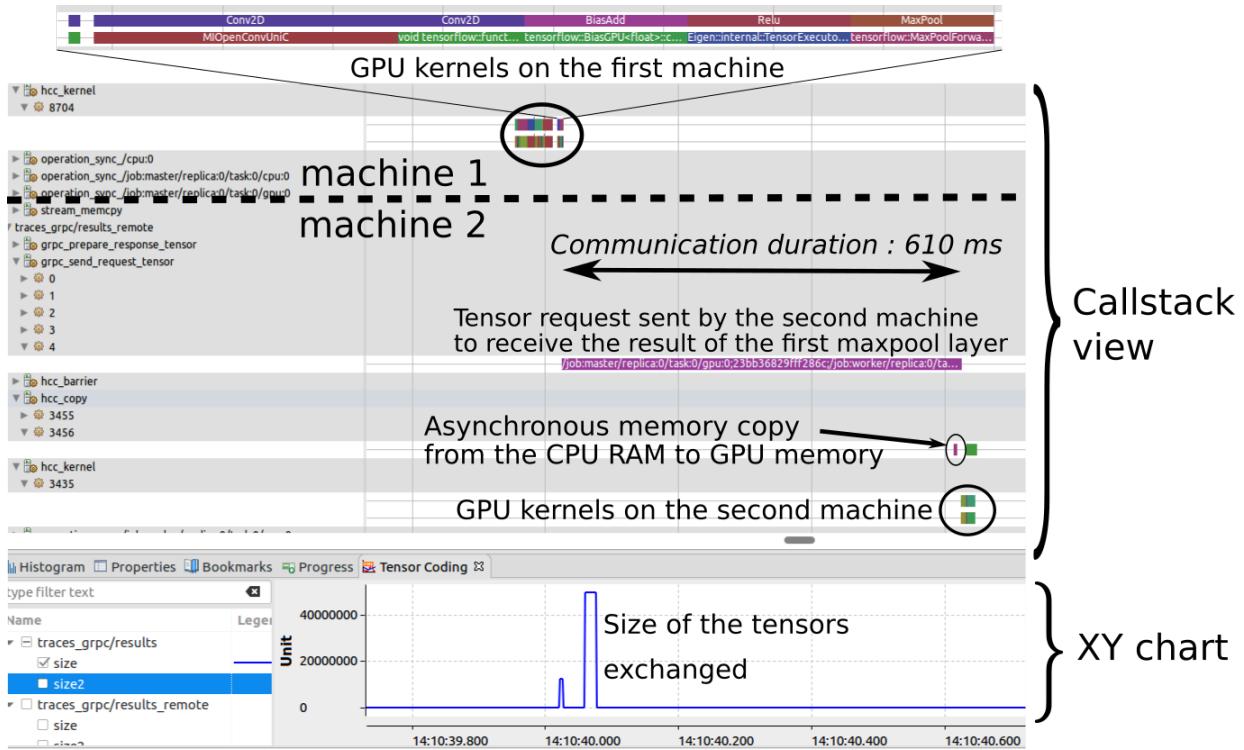

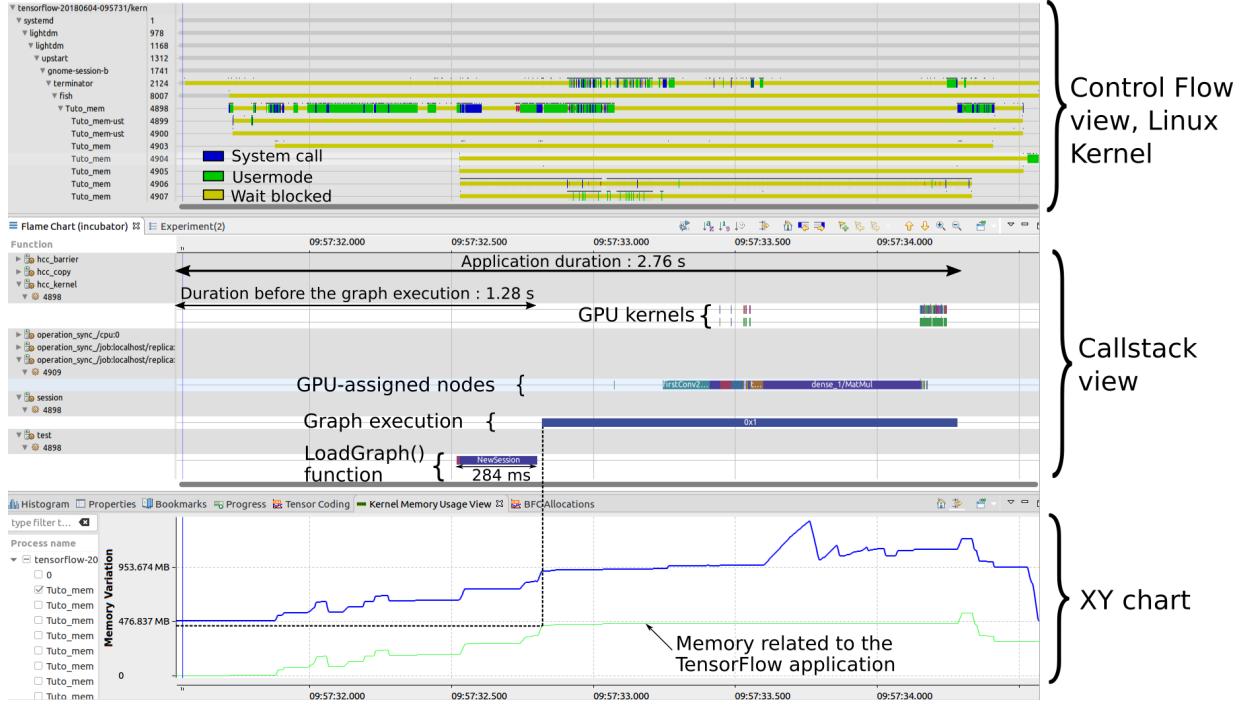

| Figure 4.12 | Distributed execution of a CNN on 2 machines - first experiment. Machine 1 executes the first convolutional layer and the machine 2 asks for the result. Once received, machine 2 can compute the second convolutional layer and the dense layer. The XY chart at the bottom shows the size of the tensors exchanged between the machines. . . . .                      | 80 |

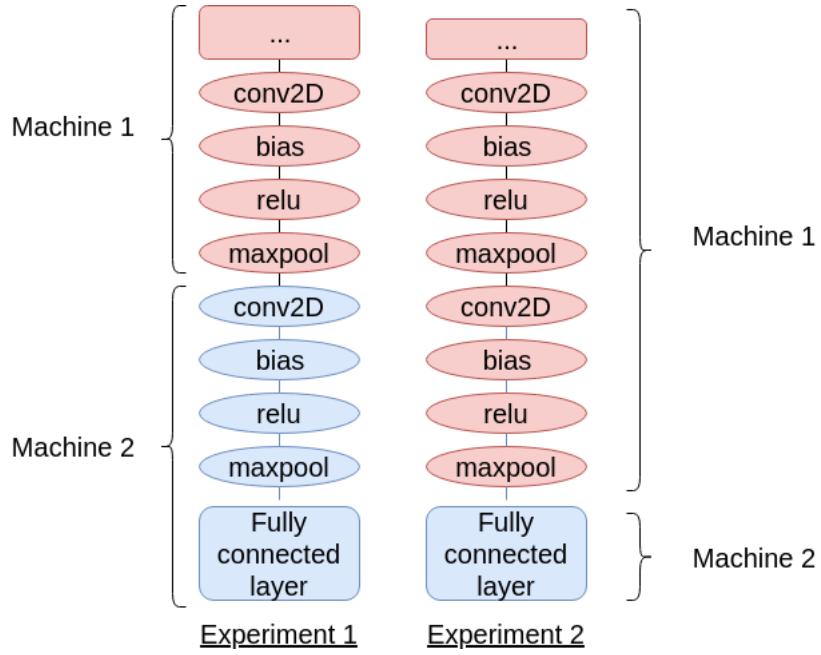

| Figure 4.13 | Division of the graph for both experiments. . . . .                                                                                                                                                                                                                                                                                                                     | 81 |

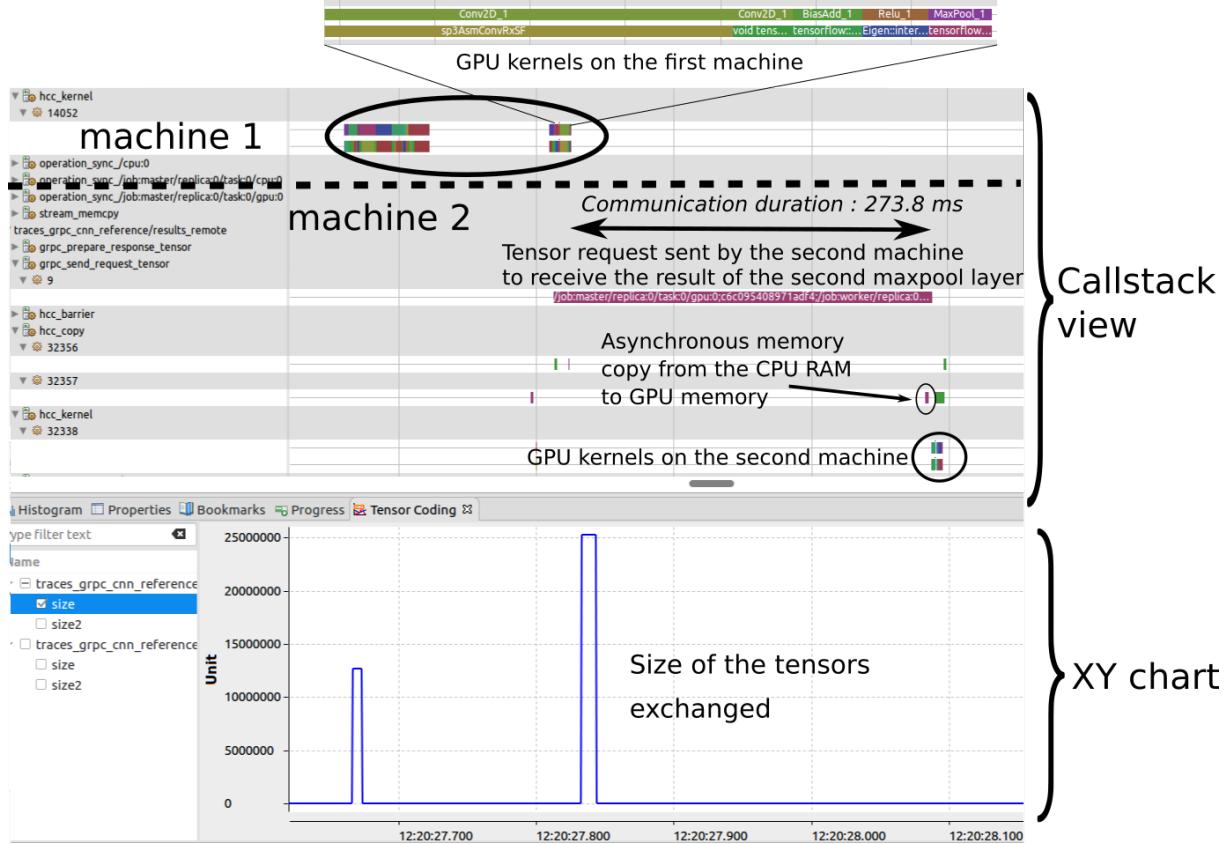

| Figure 4.14 | Distributed execution of a CNN on 2 machines - second experiment. This time, machine 1 executes the two convolutional layers and machine 2 asks for the result. Once received, machine 2 can compute the dense layer. The XY chart at the bottom shows that the size of the tensors exchanged between the machines is reduced compared to the first experiment. . . . . | 82 |

| Figure 4.15 | Initial Callstack and Linux Kernel memory usage views for an inference step. A long time is spent before the beginning of the graph execution and around 800 MB of RAM memory is used by the TensorFlow application. . . . .                                                                                                                                            | 83 |

| Figure 4.16 | Kernel traces of the inference step. We can detect a lot of <i>pread</i> system calls. They correspond to the loading of the model file. . . . .                                                                                                                                                                                                                        | 84 |

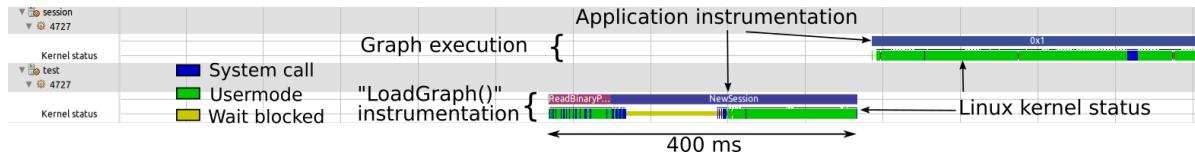

| Figure 4.17 | Callstack and kernel status, with the static instrumentation of the <i>LoadGraph</i> function. We can verify that this function is indeed time consuming. . . . .                                                                                                                                                                                                       | 84 |

|             |                                                                                                                                                                                                                                                                                                                                                        |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.18 | Kernel traces, Callstack and Linux Kernel memory usage view of the optimized application. Using the memory mapping technique to load the model file decreases the duration of the <i>LoadGraph</i> function. The RAM memory usage is also decreased at the beginning of the graph execution, compared to the first version of the application. . . . . | 85 |

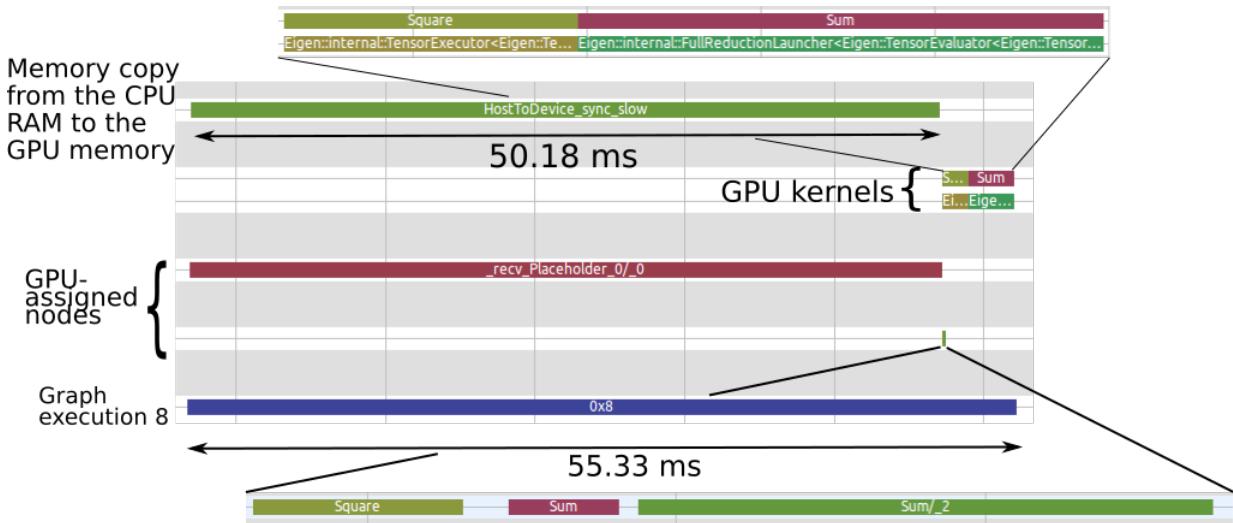

| Figure 4.19 | Normal execution using <code>feed_dict</code> argument. An important percentage of the execution is dedicated to a large memory transfer from the RAM memory to the GPU memory. . . . .                                                                                                                                                                | 86 |

| Figure 4.20 | After the optimization with a slice operation and a unique large memory copy. Now, the whole dataset is copied to the GPU memory at the application initialization. Consequently, the data batches are already in the GPU memory for all the graph executions. Therefore, each execution is much faster and consists mostly in GPU kernels processing. | 87 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|                  |                                                 |

|------------------|-------------------------------------------------|

| ADN              | DNA - Deoxyribonucleic acid                     |

| AMD              | Advanced Micro Devices                          |

| API              | Application Programming Interface               |

| APU              | Accelerated Processing Unit                     |

| ARM              | Advanced RISC Machine                           |

| AVC              | Advanced Video Coding                           |

| BLAS             | Basic Linear Algebra Subprograms                |

| CAL              | Cal Actor Language                              |

| clBLAS           | OpenCL Basic Linear Algebra Subprograms         |

| CLUST            | OpenCL User Space Tracepoint                    |

| CPU              | Central Processing Unit                         |

| CTF              | Common Trace Format                             |

| CUDA             | Compute Unified Device Architecture             |

| CUPTI            | CUDA Profiling Tools Interface                  |

| DMA              | Direct Memory Access                            |

| DSP              | Digital Signal Processor                        |

| Factorisation LU | Factorisation Lower Upper                       |

| FPGA             | Field Programmable Gate Array                   |

| GCN              | Graphical Cores Next                            |

| GPA              | GPU Performance API                             |

| GNU              | GNU's Not Linux                                 |

| GPU              | Graphical Processing Unit                       |

| HC               | Heterogeneous Compute                           |

| HCC              | Heterogeneous Compute Compiler                  |

| HDL              | Hardware Description Language                   |

| HEVC             | High Efficiency Video Coding                    |

| HIP              | Heterogeneous-Compute Interface for Portability |

| HSA              | Heterogeneous System Architecture               |

| IGP              | Integrated Graphic Processor                    |

| ISA              | Instruction Set Architecture                    |

| JPEG             | Joint Photographic Experts Group                |

| kprobe           | Kernel probe                                    |

| GPGPU            | General Purpose Graphical Processing Unit       |

|         |                                                     |

|---------|-----------------------------------------------------|

| LTTng   | Linux Tracing Toolkit next generation               |

| MATLAB  | Matrix Laboratory                                   |

| MPEG    | Moving Picture Experts Group                        |

| MPI     | Message Passing Interface                           |

| NVPROF  | Nvidia Visual Profiler                              |

| OpenCL  | Open Computing Language                             |

| OpenGL  | Open Graphics Library                               |

| OpenMP  | Open Multi-Processing                               |

| OS      | Operating System                                    |

| OTF     | Open Trace Format                                   |

| RAM     | Random-Access Memory                                |

| RCP     | Radeon Compute Profiler                             |

| RCV     | Reconfigurable Video Coding                         |

| RCV-CAL | Reconfigurable Video Coding - Cal Actor Language    |

| RDF     | Resource Description Framework                      |

| ROCm    | Radeon Open Compute platform                        |

| SCADE   | Safety-Critical Application Development Environment |

| SIMD    | Single Instruction Multiple Data                    |

| TAU     | Tuning and Analysis Utilities                       |

| TPU     | Tensor Processing Unit                              |

| TraceFS | Trace File System                                   |

| uprobe  | user probe                                          |

| USDT    | User Statically Defined Tracing                     |

| UST     | User-Space Tracing                                  |

| VHDL    | VHSIC Hardware Description Language                 |

| XML     | Extensible Markup Language                          |

## CHAPITRE 1 INTRODUCTION

Au cours des dernières années, les besoins en termes de puissance de calcul n'ont cessé d'augmenter. De nombreux domaines comme le calcul scientifique, le rendu graphique en plusieurs dimensions ou encore l'apprentissage automatique requièrent des performances toujours plus grandes afin de traiter un maximum de données en un minimum de temps. Par ailleurs, les améliorations matérielles ont peu à peu stagné. Il n'est plus possible, par exemple, de continuellement augmenter le nombre de transistors sur un microprocesseur afin d'accroître sa fréquence, ou encore d'améliorer indéfiniment la finesse de gravure.

Pour remédier à cela, le calcul en parallèle a été considéré et permet d'augmenter les performances. Par conséquent, le principe d'architectures hétérogènes a émergé et combine plusieurs unités de calcul afin de mettre en place ce parallélisme. Un cas très fréquent concerne l'utilisation d'un processeur graphique permettant d'assister le processeur traditionnel pour les tâches très exigeantes en termes de calcul. La programmation de ce genre d'architecture est souvent complexe et difficile à mettre en place avec une approche traditionnelle et séquentielle. Par conséquent, d'autres possibilités ont été envisagées comme le modèle flot de données qui offre des caractéristiques avantageuses.

Par ailleurs, assurer une performance optimale est un point essentiel lors du développement d'une application. Pour cela, on retrouve notamment des techniques de traçage et de profilage. Ces dernières consistent à collecter de nombreux événements durant l'exécution d'une application afin de former une trace. Le traitement, l'analyse ainsi que la visualisation de cette dernière permettent à l'utilisateur de comprendre la performance d'une application et d'identifier d'éventuels problèmes ou limitations. Des outils permettant cela existent et ont déjà prouvé leur efficacité dans un cadre d'exécution plus traditionnel. Cependant, dans ce mémoire, nous nous intéressons aux architectures hétérogènes utilisant une approche de calcul par flot de données. Nous verrons dans les sous-sections 2.3 et 2.5 que les outils existants montrent des limites dans ce genre de contexte et nous chercherons à les combler au cours du projet de recherche.

### 1.1 Définitions et concepts de base

#### 1.1.1 Processeur graphique et processeur central

Le processeur central correspond au composant traditionnel utilisé dans un ordinateur pour le calcul. Dans ce mémoire, différents termes seront utilisés pour le désigner : **processeur**

**central, processeur traditionnel** ou encore l'acronyme **CPU** correspondant au terme anglophone **Central Processing Unit**.

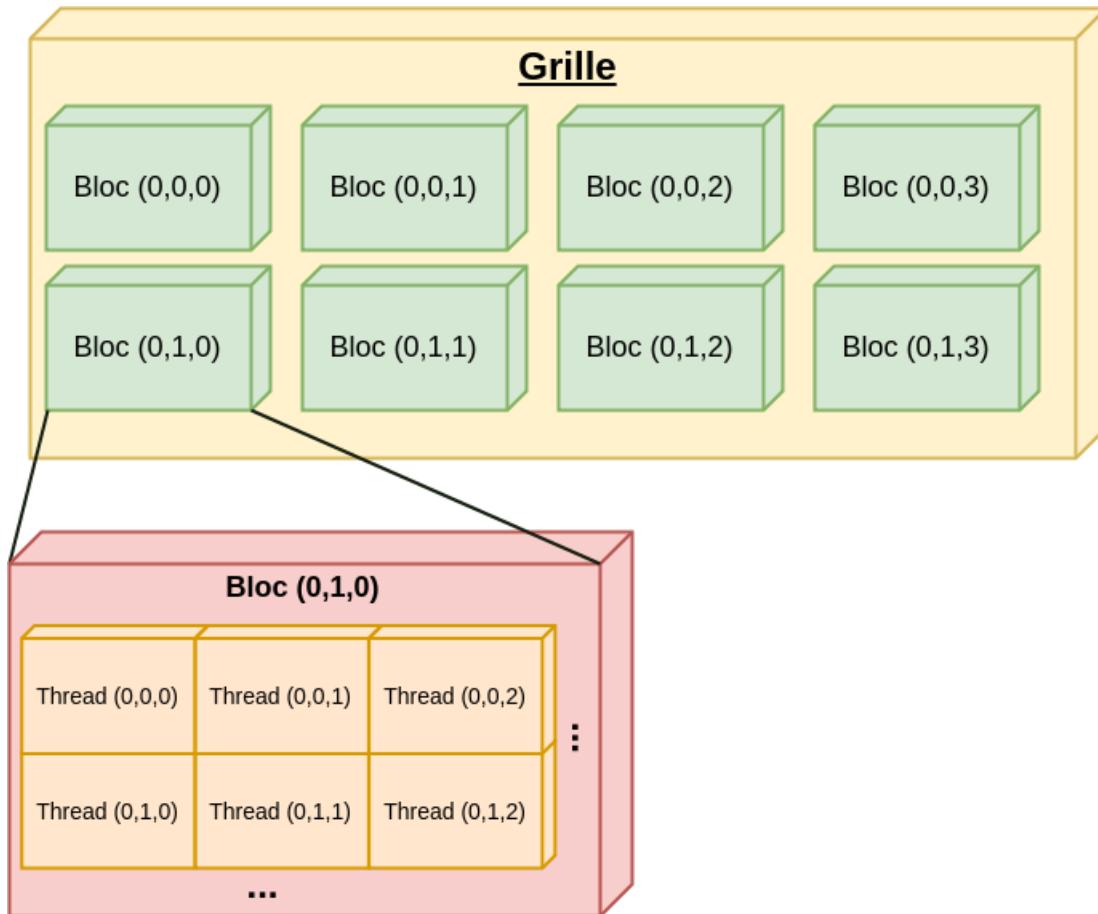

Le processeur graphique quant à lui correspond à une autre unité de calcul, destinée à l'origine aux parties graphiques des applications et à l'affichage sur l'écran. Récemment, le concept de **GPGPU (General Purpose GPU)** a émergé et consiste à utiliser ce composant pour toute tâche impliquant beaucoup de calcul sur un grand nombre de données. En effet, un processeur graphique est basé sur le concept de **SIMD (Single instruction, multiple data)** de la taxonomie de Flynn et consiste à appliquer une même instruction à plusieurs données simultanément. Cela est rendu possible par son architecture composée d'un très grand nombre de cœurs de calcul en comparaison d'un processeur traditionnel. Dans la suite du mémoire, on retrouve ce composant sous les termes suivants : **processeur graphique, carte graphique** ou encore **GPU (Graphical Processing Unit)**.

### 1.1.2 Traçage, instrumentation et profilage

Le traçage est une technique très utilisée dans le cadre de l'analyse de performance. Elle désigne le fait de collecter un grand nombre d'événements durant l'exécution d'une application sans dégrader de manière significative sa performance. Ces événements formeront une trace qui pourra être analysée et visualisée afin d'en faire ressortir des informations bénéfiques. Le traçage fonctionne souvent de pair avec une instrumentation qui consiste à insérer des points de trace à des endroits spécifiques dans le code source d'une application. Chaque point de trace atteint lors de l'exécution générera un événement en sortie. Une instrumentation demande généralement l'accès au code source de l'application, ou de la bibliothèque logicielle, et nécessite la recompilation de cette dernière. Ainsi, il sera possible de tracer au niveau utilisateur. Le traçage du noyau du système d'exploitation est également disponible et se base sur une instrumentation existante dans le noyau Linux.

Le profilage quant à lui correspond davantage à la collecte de mesures et métriques à propos de l'exécution d'une application. On peut notamment évoquer la récupération de compteurs de performance à propos du matériel ou encore le suivi de la consommation mémoire d'une application.

### 1.1.3 Visualisation des résultats

Le résultat d'une opération de traçage ou de profilage consiste généralement en une trace contenant des événements. En raison de leur très grand nombre, il n'est pas envisageable d'analyser simplement une liste d'événements présentée sous un format texte. Il est donc

essentiel de proposer des méthodes de visualisation graphiques. Trace Compass est une des solutions privilégiées pour cela et fonctionne avec des vues qui vont présenter de manière graphique les résultats à l'utilisateur. Chacune d'entre elles se concentrera sur des aspects précis et permettra de faire ressortir des informations utiles pour l'utilisateur. Dans ce mémoire, quatre types de vues sont abordés.

- La vue **Callstack** permet notamment de représenter l'imbrication des différents appels de fonctions réalisés par chaque fil d'exécution.

- La vue **Contrôle de flux** ou **Control Flow View** représente l'ensemble des fils d'exécution au niveau du noyau du système d'exploitation. Elle permet de suivre leur activité avec notamment les appels système, les blocages, les interruptions, le temps passé en mode utilisateur, les temps d'attentes, ...

- La vue des **Ressources** ou **Resources View** représente quant à elle l'état des différents cœurs du processeur central au cours de la session de traçage.

- Les **graphiques XY** ou **XY charts** sont plus adaptés à d'autres cas qui consistent à suivre l'évolution d'une certaine métrique au cours de l'exécution d'une application. Il peut par exemple s'agir de la consommation mémoire de l'application.

## 1.2 Éléments de la problématique

Actuellement, des outils permettant l'analyse de performance existent pour les processeurs centraux et graphiques. Cependant, de nombreux problèmes persistent dans le cas d'analyses réalisées pour des applications s'exécutant sur des plateformes hétérogènes.

Tout d'abord, les outils de traçage et de profilage existants se concentrent généralement sur un type de processeur. On peut penser à **Ftrace**, **Perf** ou **LTTng** qui sont à l'origine destinés au processeur central. En ce qui concerne les processeurs graphiques, les outils les plus utilisés restent ceux proposés par les constructeurs comme **Nsight** pour Nvidia ou **CodeXL** pour AMD. Ces derniers proposent des éléments très intéressants pour l'analyse de performance, mais uniquement du point de vue du processeur graphique. Ainsi, les outils existants peinent à faire le lien entre l'activité de ce dernier et celle du processeur traditionnel. Or, dans le cadre d'architectures hétérogènes, il est justement essentiel d'analyser l'ensemble des unités de calcul disponibles ainsi que leur coopération. Les transferts de mémoire entre les processeurs peuvent notamment affecter grandement la performance. Par ailleurs, ces outils de profilage pour les cartes graphiques manquent généralement de flexibilité, ne supportent pas du matériel de différents constructeurs et ne s'intègrent pas bien dans un environnement d'analyse de performance complet.

Au travers de ce projet de recherche, nous viserons donc à solutionner ces problèmes en proposant des outils ou méthodes mieux adaptés. De nombreux problèmes concernant l'utilisation d'un processeur graphique ont été rencontrés, comme la gestion des opérations effectuées de manière asynchrone par celui-ci et la différence d'horloges entre les unités de calcul. En effet, le principe de fonctionnement d'un processeur graphique s'articule autour d'une ou plusieurs queues dans lesquelles les tâches lui sont soumises. Ces dernières sont ordonnancées par la carte graphique elle-même et généralement exécutées de manière asynchrone. Par conséquent, les événements correspondants sont collectés *a posteriori* et il faut veiller à les réordonner au sein de la trace finale. Par ailleurs, les temps récupérés pour le processeur graphique n'ont généralement aucun sens du point de vue du processeur central, puisque les horloges utilisées par les deux composants sont différentes.

Par ailleurs, il sera aussi nécessaire de relier les informations de bas niveau à propos de l'exécution avec d'autres à un niveau d'abstraction plus élevé, concernant le modèle flot de données lui-même. Actuellement, aucun outil pour l'analyse de performance ne permet cela. D'autres défis sont inhérents à l'approche flot de données. Il faudra s'assurer de pouvoir combiner ensemble toutes les informations collectées afin d'analyser la totalité du matériel utilisé. De plus, le travail effectué par le processeur graphique dans ce contexte est souvent important, de nombreux noyaux de calculs sont exécutés et parfois un grand nombre de fois. Il sera par conséquent essentiel de gérer toutes ces données de manière adéquate.

Un dernier défi provenait de notre volonté d'implémenter notre solution pour chacune des versions de TensorFlow qui permettait d'utiliser un processeur graphique. Nous avons donc considéré les trois solutions principales pour l'utilisation d'une carte graphique avec TensorFlow (CUDA, ROCm et SYCL). Chacune d'entre elles comprenait certains éléments spécifiques, ce qui a complexifié le développement de notre implémentation.

Au cours du projet de recherche, nous avons eu besoin d'un outil pour le traçage et l'instrumentation de code source. Le choix de LTTng s'est fait naturellement pour différentes raisons. En premier lieu, sa performance était très attrayante. De plus, cet outil est relativement simple à utiliser et propose un résultat sous la forme d'une trace au format CTF. Ce format offre un avantage du point de vue de la performance, par un stockage compact de données, et bénéficie d'un environnement complet et flexible pour l'analyse et la visualisation de trace. Un autre avantage est la possibilité de collecter des traces concernant le noyau Linux.

### 1.3 Objectifs de recherche

Il existe déjà des outils permettant le traçage et profilage de processeurs traditionnels et graphiques. Cependant, ces derniers permettent rarement de considérer de manière conjointe les deux unités de calculs. Par ailleurs, les analyses de systèmes ou d'applications flot de données se limitent généralement à une analyse d'assez haut niveau, sans fournir d'information précise à propos du matériel, du système d'exploitation ou des bibliothèques logicielles intermédiaires. L'objectif principal de ce projet de recherche est donc de proposer une méthode de traçage et de profilage complète, à différents niveaux, et visant les applications flot de données qui s'exécutent sur des architectures hétérogènes.

#### 1.3.1 Questions de recherche

Afin de remplir, l'objectif principal nous répondons à trois questions de recherche :

1. Quelles informations permettraient de comprendre la performance d'une application flot de données s'exécutant sur une architecture hétérogène ?

2. Quels méthodes et outils pourraient être utilisés conjointement afin de collecter ces informations ?

3. Quels types de visualisation et analyses permettraient de présenter les résultats de manière adéquate à l'utilisateur dans un objectif final d'optimisation de la performance ?

#### 1.3.2 Objectifs spécifiques

Afin de répondre à l'objectif principal de ce projet de recherche, des objectifs spécifiques ont été énoncés.

1. Démontrer l'efficacité des méthodes de traçage et profilage pour la détection de problèmes de performance ou la suggestion d'optimisations dans le cadre d'applications de type flot de données bénéficiant de l'accélération des processeurs graphiques.

2. Développer des outils ou méthodes de traçage adaptés à la bibliothèque logicielle TensorFlow.

3. Développer des vues adéquates, présentant de manière efficace, détaillée et claire l'exécution d'une application flot de données sur l'ensemble du matériel disponible.

#### 1.3.3 Hypothèse de recherche

Notre projet de recherche repose sur l'hypothèse suivante : Les méthodes de traçage et profilage permettent de détecter des problèmes de performance ainsi que d'identifier les éléments

les plus propices à des optimisations pour des applications flot de données s'exécutant sur des systèmes hétérogènes. L'originalité réside dans le fait qu'il n'existe pas d'outil permettant d'avoir une vue claire, complète et détaillée de l'exécution du programme flot de données sur un système hétérogène combinant CPU et GPU. L'hypothèse sera réfutée si les méthodes de traçage et profilage ne permettent pas d'identifier des problèmes de performance ou de suggérer des éléments à optimiser pour l'exécution d'un programme flot de données sur un système hétérogène. Le surcoût introduit par notre travail devra également rester raisonnable, sans quoi l'hypothèse sera également réfutée.

#### 1.4 Plan du mémoire

Ce mémoire suit le plan suivant. Après cette introduction, le chapitre 2 présente une revue critique de la littérature. Elle permet d'informer le lecteur à propos des principaux outils et des technologies abordées dans le mémoire. Le lecteur sera ainsi plus familier avec les différents concepts et thèmes du mémoire et la lecture sera facilitée.

Par la suite, le chapitre 3 décrit la méthodologie utilisée dans le cadre du projet de recherche. Des éléments techniques ainsi que certains points clés de l'implémentation sont présentés. Les configurations matérielle et logicielle sont également décrites, ce qui est bénéfique à la compréhension et pour la reproduction des résultats.

Puis, le chapitre 4 représente la partie principale de ce mémoire. Il prend la forme d'un article de recherche décrivant la méthode développée. Nous y présentons également plusieurs cas d'utilisations afin de démontrer l'efficacité de la solution proposée. Une analyse et une discussion à propos de la performance de notre méthode sont également menées.

Dans le chapitre 5, nous procédons à une analyse critique des résultats du chapitre 4. Nous revenons sur les points clés, notamment le surcoût introduit par notre solution dans différents cas.

Enfin, ce mémoire se termine par une conclusion dans laquelle nous commençons par résumer les travaux de recherche. Nous discutons ensuite des limites de notre solution et évoquons des possibilités de travaux futurs.

## CHAPITRE 2 REVUE DE LITTÉRATURE

Ce chapitre constitue un état de l'art des différents domaines en lien avec le travail présenté et pourra faciliter la compréhension du lecteur dans la suite du mémoire. Nous abordons dans un premier temps le modèle flot de données, en présentant notamment des langages et applications utilisant ce genre d'approche. Nous nous intéressons par la suite à TensorFlow (Abadi et al., 2016a,b), une librairie pour l'apprentissage automatique et profond utilisant un graphe de calcul pour représenter les algorithmes et qui constitue la base pour l'implémentation de notre travail. Après cela, nous évoquons les techniques ainsi que les outils existants pour le traçage et le profilage d'applications. Nous visons les processeurs traditionnels dans un premier temps et les processeurs graphiques ensuite. Nous présentons également certains outils permettant la visualisation et l'analyse des traces. Enfin, nous terminons par détailler les travaux existants à propos du profilage et de l'analyse d'applications flots de données.

### 2.1 Modèle flot de données

Dans cette section, nous rappellerons tout d'abord les principes théoriques des modèles flot de données. Nous présenterons ensuite des langages développés, ainsi que plusieurs méthodes et techniques dans différents domaines qui sont basés sur ce genre d'approches. Enfin, nous aborderons plusieurs bibliothèques logicielles pour l'apprentissage automatique et profond qui utilisent un modèle de calcul flot de données. Nous détaillerons en particulier TensorFlow, pour laquelle l'ensemble du travail présenté dans ce mémoire a été développé.

#### 2.1.1 Principes théoriques

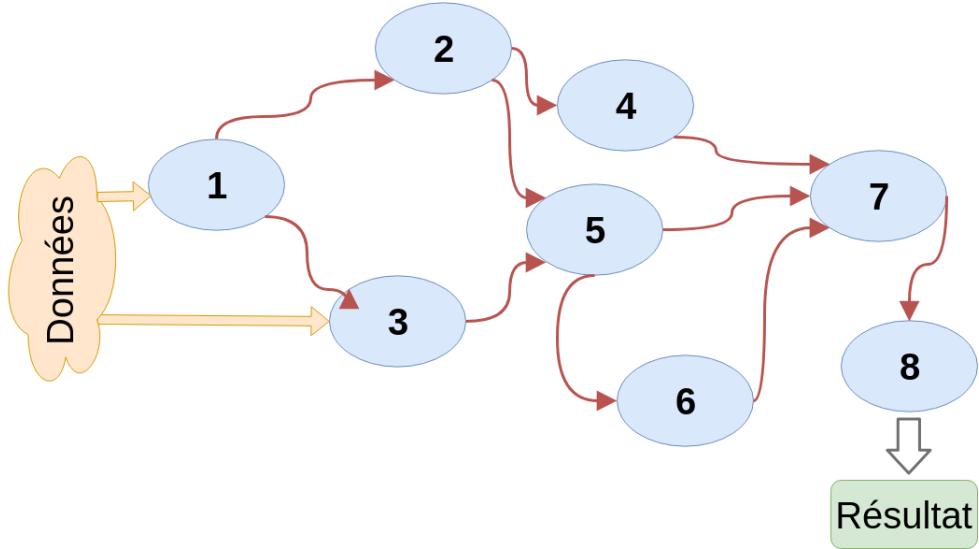

Le modèle flot de données est un paradigme de programmation apparu à la fin des années 1960 qui consiste en un graphe acyclique contenant des noeuds reliés entre eux par des arcs. Chaque noeud représente une unité de calcul ayant une ou plusieurs entrées et sorties. Les arcs correspondent à des liens, le long desquels les données fournies au graphe vont pouvoir circuler. Chaque noeud appliquera une opération spécifique aux données reçues en entrée puis fournira le résultat en sortie. Il est donc possible de définir ce modèle de programmation comme une approche centrée sur les données et leur mouvement, et qui permet de modeler un programme en un groupement de connexions entre des unités de calcul. La figure 2.1 représente un modèle flot de données sous la forme d'un graphe. On peut identifier facilement les 8 noeuds de calcul qui vont opérer sur les données. Ces dernières seront

Figure 2.1 Exemple de modèle flot de données. Les données de départ sont fournies en entrée aux noeuds 1 et 3. Elles circulent ensuite le long des arcs et sont traitées par chaque noeud. Le résultat final correspond à la sortie du noeud 8.

fournies au graphe au travers d'un ou de plusieurs noeuds, les numéros 1 et 3 dans cet exemple. Puis, elles circuleront le long des axes jusqu'à atteindre le dernier noeud du graphe, le numéro 8 ici.

Ce modèle de programmation partage des principes similaires avec l'architecture matérielle flot de données. Cette dernière, également connue sous le nom *d'ordinateur cadencé par les données* propose une alternative à l'architecture traditionnelle de von Neumann et sa vision de programmation séquentielle. Dans ce cas, aucun compteur de programme n'est utilisé, mais toute l'exécution repose sur la disponibilité des données en entrée qui déclenchera l'exécution d'une opération. Le fait de séparer le traitement en unité de calcul individuelle, rend ce modèle très bien adapté à la programmation parallèle ou distribuée. Cela constitue une des principales motivations pour son développement et contraste avec l'architecture classique de von Neumann, par essence mal adaptée au principe de parallélisme. Comme de nos jours les traitements en parallèle sont essentiels pour atteindre des performances toujours plus importantes, les approches flots de données sont devenues très populaires.

### 2.1.2 Langages de type flot de données

Ce modèle étant très répandu, il a inspiré de nombreux langages de programmation et travaux de recherche. Lee (1991) a étudié les propriétés analytiques de ces langages et notamment la cohérence de leur graphe flot de données. Lustre (Caspi et al., 1987; Halbwachs et al., 1991),

par exemple, est un langage déclaratif, synchrone et adoptant le modèle flot de données qui est utilisé pour programmer des systèmes réactifs. Aujourd’hui intégré à l’environnement commercial SCADE, il sert principalement à la conception logicielle de systèmes critiques dans l’aéronautique, le ferroviaire ou encore les centrales nucléaires. Lucid (Wadge and Ashcroft, 1985) est un second exemple de langage de programmation suivant ce genre d’approche. CAL (CAL Actor langage) (Eker and Janneck, 2003) est un autre exemple de langage haut niveau, compilé et destiné à différents types d’architectures hétérogènes (Boutellier and Nylanden, 2017) et (Lin et al., 2016). Il a été développé au sein du projet Ptolemy (Eker et al., 2003), un environnement de développement Java pour la conception, modélisation et simulation hétérogène de systèmes flot de données concurrents. Bhattacharyya et al. (2008) proposent un environnement de compilation et simulation pour CAL, contenant un support pour la génération de code HDL (Verilog ou VHDL) (Janneck et al., 2008) et de code C en vue d’une intégration avec SystemC (Roquier et al., 2008). Par ailleurs, ce langage a été ajouté au nouveau standard MPEG "Reconfigurable Video Coding (RCV)" (ISO/IEC 23001-4 et 23002-4) pour former RVC-CAL. Ce dernier est notamment utilisé pour le traitement de signal (Hentati et al., 2012), la compression (Bezati et al., 2010), la programmation haute performance de GPU (Boutellier and Nylanden, 2015) ainsi qu’en cryptographie. Dans le domaine de la conception matérielle, de nouveaux langages de description ont été développés (Port and Etsion, 2017), tout comme dans celui du Big Data où des approches flot de données innovantes ont vu le jour comme SYRql (Maali et al., 2014) qui vise à traiter des données RDF à très grande échelle.

### **2.1.3 Méthodes et techniques flot de données**

Étant très bien adapté au principe de parallélisme, ce modèle de programmation constitue un sujet de recherche important et très étudié. Le domaine du traitement de signal, d’image et de vidéos l’utilise par exemple régulièrement. Boutellier et al. (2018) proposent un modèle de calcul dynamique basé sur une approche flot de données pour le déploiement d’applications de traitement du signal dans des environnements matériels hétérogènes. Bourrasset et al. (2016a) décrivent une implémentation flot de données d’un détecteur d’objets configurables sur une plateforme constituée de FPGAs. Enfin, Blattner et al. (2017) proposent un ordonnanceur de tâches hybrides dans un graphe en se basant également sur une approche flot de données. D’autres domaines comme les réseaux (Kohler et al., 2000) ou la conception matérielle (Li et al., 2016) bénéficient également des avancés de ces modèles. Plusieurs méthodes et techniques de conception utilisent un modèle unique flot de données afin de synthétiser conjointement les composants matériels et logiciels ainsi que leurs interfaces (Roquier et al., 2011) et (Carlsson et al., 2010). Le niveau d’abstraction élevé apporté par ces approches

est tout particulièrement apprécié dans le cadre d'architectures hétérogènes. Enfin, des techniques inspirées des approches flot de données sont également apparues comme TiDeFlow (Orozco et al., 2016) qui propose l'utilisation d'un graphe orienté pour représenter un programme. Ce dernier offre différents avantages, comme la possibilité d'exprimer nativement des boucles parallèles afin de modéliser un programme avec un meilleur niveau d'abstraction, et l'introduction du pipeline de tâches permettant un gain de performance.

#### **2.1.4 Modèle flot de données appliqué à l'apprentissage automatique**

Dans le domaine de l'apprentissage automatique et de la fouille de données, ce type de modèle est également apprécié. En effet, les applications pour l'apprentissage sont en général très exigeantes en termes de calcul et de quantité de données à traiter. Pour cela, de nouvelles architectures matérielles hétérogènes et parallèles ont été mises en place, où les processeurs traditionnels sont supportés par d'autres composants matériels comme les processeurs graphiques ou encore les "processeurs de tenseurs" *Tensor Processing Unit (TPU)* en anglais (Jouppi et al., 2017). Comme expliqué précédemment, les modèles flots de données sont particulièrement adaptés pour obtenir une performance maximale avec ce genre d'architecture hautement parallèle. Orange (Demšar et al., 2013) est un outil libre de sources pour l'apprentissage automatique, la fouille de données ainsi que la visualisation et propose un fonctionnement basé sur des unités de calcul connectées entre elles qui vont traiter continuellement de nouvelles données. Theano (Bergstra et al., 2010; Al-Rfou et al., 2016) est une librairie pour l'apprentissage automatique et profond qui utilise un modèle de calcul flot de données.

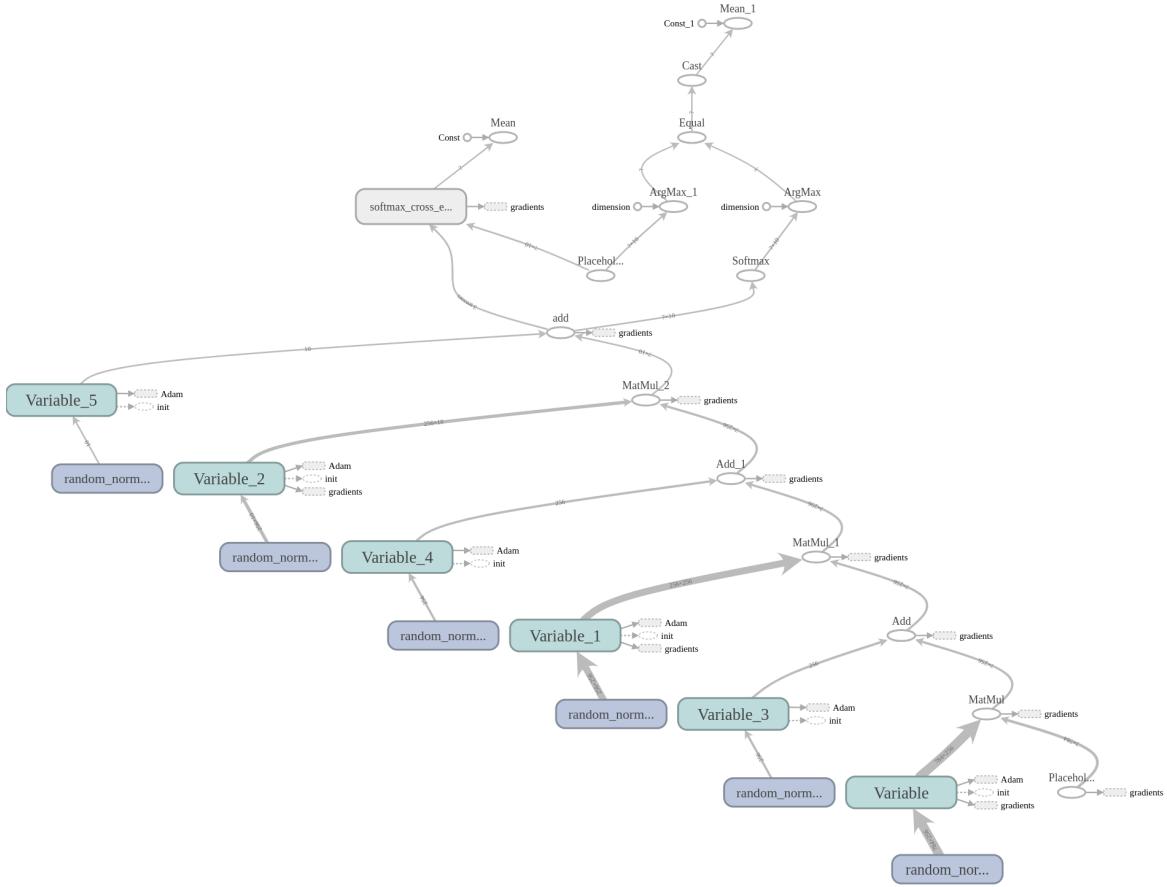

TensorFlow (Abadi et al., 2016a,b, 2017) est un autre exemple de bibliothèque logicielle libre de sources pour l'apprentissage machine et profond qui présente les calculs sous la forme d'un graphe direct et acyclique. Tensorboard (Wongsuphasawat et al., 2018), un outil de visualisation, intégré à TensorFlow permet notamment de visualiser le graphe de calcul d'une application. La figure 2.2 présente un exemple de graphe pour un réseau de neurones basique contenant deux couches cachées et une couche de sortie. Cette librairie, développée majoritairement par Google, est extrêmement populaire dans le domaine de l'intelligence artificielle. Elle propose une implémentation complète et très performante du modèle flot de données. De plus, elle est utilisée par un très grand nombre de personnes et reste activement développée. Pour toutes ces raisons, TensorFlow constitue une excellente base pour l'implémentation de nos travaux.

Les nœuds du graphe correspondent à des opérations qui vont traiter les données circulant le long des axes. Dans un contexte d'apprentissage automatique, ces données sont habituel-

Figure 2.2 Tensorboard : visualisation du graphe d'un réseau de neurones ayant deux couches cachées et une couche de sortie. Une partie annexe du graphe va gérer la propagation arrière et le calcul des gradients mais n'est pas représentée ici.

lement des tableaux multi-dimensionnels appelés *tenseurs* ou *tensors* en anglais. Chaque opération sera associée à une entité matérielle de calcul : processeur central, processeur graphique ou encore processeur de tenseurs. TensorFlow ajoute automatiquement des noeuds au graphe de calcul afin de gérer les transferts de mémoire nécessaires lorsque des noeuds liés ensemble sont associés à différentes entités physiques. Par ailleurs, TensorFlow propose également de réaliser de l'apprentissage de manière distribuée sur plusieurs machines. Dans ce cas, le graphe de calcul peut être partagé sur plusieurs ordinateurs et chaque noeud sera associé à une entité de calcul sur une des machines utilisées. À nouveau, la librairie ajoutera automatiquement des noeuds nécessaires pour gérer les transferts de mémoire.

Dans le cas de TensorFlow, l'approche flot de données facilite l'exécution sur des plateformes hétérogènes. En effet, il est facile d'envisager une exécution sur plusieurs entités physiques du

fait de la décomposition du programme en plusieurs opérations individuelles. Chaque nœud pourra donc être associé à un composant de calcul physique sous la seule condition que ce dernier soit capable d'effectuer l'opération correspondante. Pour un processeur graphique, un noyau de calcul doit par exemple avoir été implémenté. En général, on cherchera à utiliser le processeur graphique pour la plupart des nœuds exigeants en termes de calcul et effectuant un traitement sur un grand nombre de données. On retrouve notamment la majorité des opérations mathématiques comme les fonctions d'activation (*Softmax*, *Relu*, *Sigmoid*) et celles impliquant des additions ou des multiplications de matrices comme les convolutions 2D.

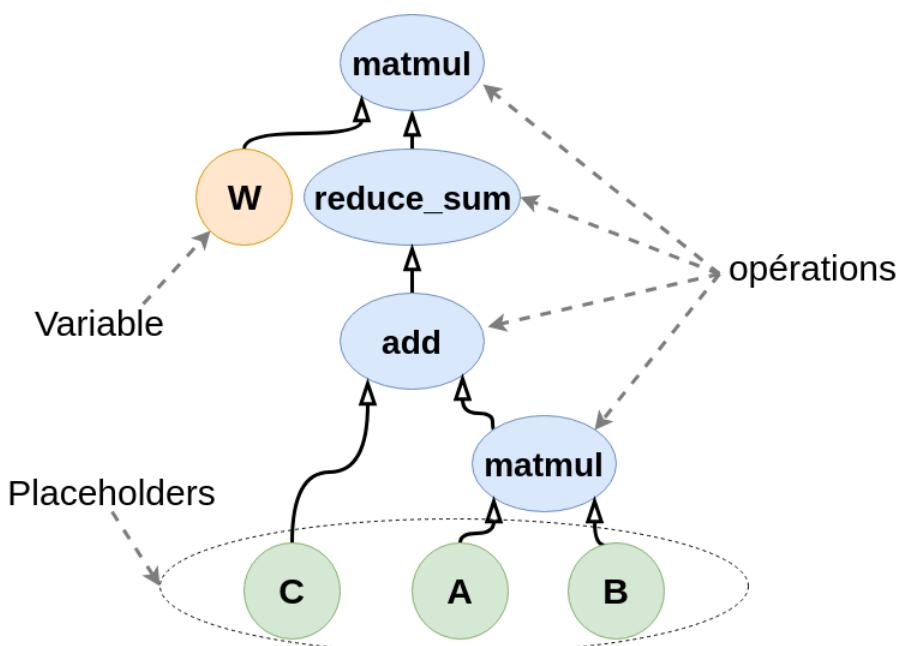

D'un point de vue du code, une application utilisant TensorFlow contient toujours deux étapes distinctes. Dans un premier temps, l'utilisateur doit définir l'algorithme en combinant différentes opérations disponibles, à partir desquelles le graphe de calcul sera créé. C'est ce dernier qui va permettre l'approche flot de donnée. Dans un second temps, un objet *Session* sera créé et on pourra l'utiliser afin de fournir des données en entrée du graphe, démarrer l'exécution et récupérer un ou plusieurs résultats en sortie. Le graphe défini dans la première étape sera lié à la *Session* et c'est elle qui va gérer l'ensemble de l'exécution. Habituellement, les algorithmes d'apprentissage automatique ou profond, comme les réseaux de neurones ou réseaux de neurones convolutifs, impliqueront un très grand nombre d'exécutions du graphe de calcul, avec à chaque fois de nouvelles données en entrée. L'exécution sera déclenchée par un appel à la méthode *Run* de l'objet *Session*. On fournira à cet appel un ou plusieurs nœuds du graphe, dont on souhaite récupérer les résultats en sortie ainsi que les données d'entrées, généralement sous forme de lots. Les figures 2.3 et 2.4 présentent respectivement un exemple de code effectuant plusieurs opérations sur des matrices ainsi que le graphe correspondant.

Comme on l'a vu, TensorFlow se base sur une approche flot de données contenant de nombreux nœuds qui vont appliquer des opérations sur des données. Par ailleurs, cette bibliothèque vise à être utilisée dans un contexte d'architectures hétérogènes avec différents coprocesseurs pour assister le processeur traditionnel. Pour l'instant, seules les cartes graphiques et les processeurs de tenseur sont supportés mais d'autre unités physique comme les DSPs ou les FPGAs pourraient l'être prochainement. Ainsi, l'association entre les nœuds logiques du graphe et les unités physiques de calcul est importante. Par défaut, TensorFlow effectue ce placement de manière automatique. Toutefois, un utilisateur peut aussi placer manuellement certains nœuds sur des entités physiques. Il sera alors essentiel de s'assurer que la performance de l'exécution soit très bonne, voire optimale. De très nombreux éléments devront être considérés comme les transferts de mémoire, le parallélisme ou encore l'utilisation adéquate des différentes unités de calcul. Aucun outil ne le permet actuellement et c'est un des manques que nous chercherons à combler dans ce projet de recherche.

```

# ...

# Génération de données aléatoire pour fournir au graphe

A_values = np.random.randint(10, size=(10,10))

B_values = np.random.randint(10, size=(10,10))

C_values = np.random.randint(10, size=(10,10))

# déclaration des placeholders, qui vont accueillir les données d'entrées

A = tf.placeholder(shape=(10,10), dtype=tf.float32)

B = tf.placeholder(shape=(10,10), dtype=tf.float32)

C = tf.placeholder(shape=(10,10), dtype=tf.float32)

# déclaration d'une variable

W = tf.Variable(tf.random_uniform([10,1], -1, 1))

# construction du programme sous forme d'un graphe de calcul

tmp = tf.add(tf.matmul(A, B), C)

result = tf.matmul(tf.reduce_sum(tmp, 0, keepdims=True), W)

# Création d'une session et lancement de l'exécution

with tf.Session() as sess:

sess.run(tf.initialize_all_variables())

res = sess.run(result, feed_dict={A: A_values, B: B_values, C: C_values})

print("result:", res)

```

Figure 2.3 Exemple de programme TensorFlow

Figure 2.4 Graphe de calcul correspondant au code précédent

## 2.2 Architectures hétérogènes et processeurs graphiques