|                         | Implementation of New Multiple Access Technique Encoder for 5G Wireless Telecommunication Networks                                                                                                                                                                                   |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Zahra Rahmani                                                                                                                                                                                                                                                                        |

| Date:                   | 2017                                                                                                                                                                                                                                                                                 |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                            |

| Référence:<br>Citation: | Rahmani, Z. (2017). Implementation of New Multiple Access Technique Encoder for 5G Wireless Telecommunication Networks [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/2761/">https://publications.polymtl.ca/2761/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/2761/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Yvon Savaria                          |

| Programme:                               | génie électrique                      |

#### UNIVERSITÉ DE MONTRÉAL

# IMPLEMENTATION OF NEW MULTIPLE ACCESS TECHNIQUE ENCODER FOR 5G WIRELESS TELECOMMUNICATION NETWORKS

# ZAHRA RAHMANI DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAITRISE ÈS SCIENCES APPLIQUÉE

(GÉNIE ÉLECTRIQUE)

AOÛT 2017

© Zahra Rahmani, 2017.

## UNIVERSITÉ DE MONTRÉAL

### ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

# IMPLEMENTATION OF NEW MULTIPLE ACCESS TECHNIQUES ENCODER FOR 5G WIRELESS TELECOMMUNICATION NETWORKS

présenté par : RAHMANI Zahra

en vue de l'obtention du diplôme de : Maitrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

- M. DAVID Jean-Pierre, Ph. D, président

- M. SAVARIA Yvon, Ph. D, membre et directeur de recherche

- M. BOYER François-Raymond, Ph. D, membre

# **DEDICATION**

To my family and beloved ones...

For making my earlier heaven more wonderful each day by being who they are

For their endless love, support and encouragement

#### **ACKNOWLEDGEMENTS**

One of the joys of completion is to look over the journey past and remember all the people who have helped and supported me along this long but fulfilling road. The present work would not have been possible without the valuable help of my academic advisor.

I would like to express my sincere gratitude to my supervisor, Prof. Yvon Savaria, for his support and valuable comments during my studies at Polytechnique Montréal. His guidance and patience smoothed the path and made it possible for me to develop this thesis. It was both an honor and a privilege to work with him. His feedback on this work brought new and interesting perspectives to the problem.

I must thank Dr. Normand Belanger for his professional advice and feedback during my research work. Our productive discussions helped me to elevate the quality of my research work. His passion for research, his patience, and his innovative ideas have impressed me and driven me to explore new space in our field and accomplish this thesis.

I am also grateful of the jury members for generously accepting to evaluate my thesis.

But most of all, I would like to thank and express my deepest gratitude to my family and friends for their continuous support and love especially my dearest Alireza who kept his amiable company with me in the ups and downs during my studies, the most wonderful parents whom I am eternally grateful and my beloved ones.

#### RÉSUMÉ

Les exigences de la connectivité mobile massive de différents appareils et de diverses applications déterminent les besoins des prochaines générations de technologies mobiles (5G) afin de surmonter les demandes futures. L'expansion significative de la connectivité et de la densité du trafic caractérisent les besoins de la cinquième génération de réseaux mobiles. Par conséquent, pour la 5G, il est nécessaire d'avoir une densité de connectivité beaucoup plus élevée et une plus grande portée de mobilité, un débit beaucoup plus élevé et une latence beaucoup plus faible.

En raison de l'exigence d'une connectivité massive, de nombreuses nouvelles technologies doivent être améliorées: le codage des canaux, la technique d'accès multiple, la modulation et la diversité, etc. Par conséquent, compte tenu de l'environnement 5G, surcoût de signalisation et de la latence devrait être pris en compte [1]. En outre, l'application de la virtualisation des accès sans fil (WAV) devrait également être considérée et, par conséquent, il est également nécessaire de concevoir la plate-forme matérielle prenant en charge les nouvelles normes pour la mise en œuvre des émetteurs-récepteurs virtuels.

L'une des nouvelles technologies possibles pour la 5G est l'accès multiple pour améliorer le débit. Par conséquent, au lieu d'OFDMA utilisé dans la norme LTE (4G), l'application d'une nouvelle technique d'accès multiple appelée Sparse Code Multiple Access (SCMA) est investiguée dans cette dissertation. SCMA est une nouvelle technique d'accès multiple non orthogonale du domaine fréquentiel proposée pour améliorer l'efficacité spectrale de l'accès radio sans fil [2]. L'encodage SCMA est l'un des algorithmes les plus simples dans les techniques d'accès multiple qui offre l'opportunité d'expérimenter des méthodes génériques de mise en œuvre. En outre, la nouvelle méthode d'accès multiple est supposée fournir un débit plus élevé. Le choix du codage SCMA avec moins de complexité pourrait être une approche appropriée. La cible fixée pour cette recherche était d'atteindre un débit d'encodage de plus de 1 Gbps pour le codeur SCMA.

Les implémentations de codage SCMA ont été effectuées à la fois en logiciel et en matériel pour permettre de les comparer. Les implémentations logicielles ont été développées avec le langage de programmation C. Parmi plusieurs conceptions, la performance a été améliorée en utilisant différentes méthodes pour augmenter le parallélisme, diminuer la complexité de calcul et par conséquent le temps de traitement. Les résultats de la mise en œuvre logicielle ont permis d'atteindre un débit de 3,59 Gbps, soit 3,5 fois plus que le débit cible.

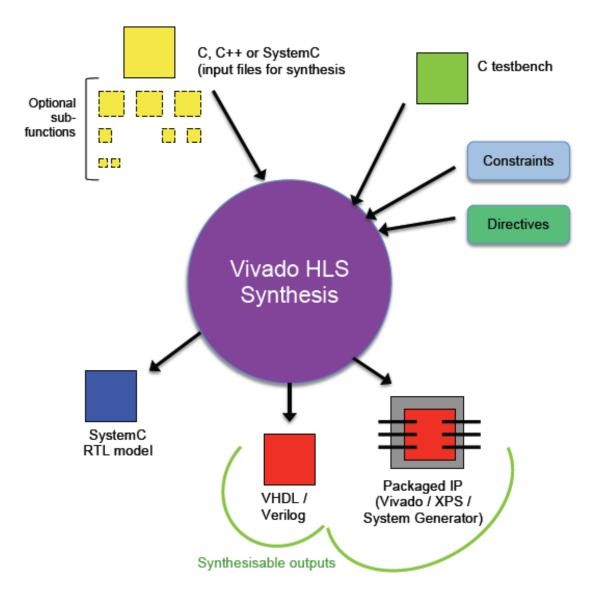

Pour la mise en œuvre matérielle, une synthèse de haut niveau a été expérimentée. Pour ce faire, les fonctions et les bancs de test exprimés en langage C et développés pour les implémentations logicielles ont été utilisées comme entrées pour Vivado HLS. En ce qui concerne les caractéristiques de la conception réalisée avec Vivado HLS, cet outil est guidé par un ensemble de contraintes et directives appliquées aux modèles pour obtenir les meilleurs résultats. L'exploitation des contraintes et directives a permis d'obtenir des mises en œuvre performantes. Les meilleurs résultats de synthèse obtenus ont produit un encodage à 8 Gbps, soit 8 fois plus que le débit cible. En dépit du fait que la principale préoccupation de la mise en œuvre du codage SCMA est d'avoir un débit plus élevé, afin de déterminer les meilleurs résultats d'implémentations matérielles, La complexité de la zone a également été considérée. Par conséquent, la meilleure conception a été choisie en fonction de l'analyse de type Aire×Temps.

#### **ABSTRACT**

The demands of massive mobile connectivity of different devices and diverse applications at the same time set requirements for next generations of mobile technology (5G). The significant expansion of connectivity and traffic density characterize the requirements of fifth generation mobile. Therefore, in 5G, there is a need to have much higher connectivity density, higher mobility ranges, much higher throughput, and much lower latency.

In pursuance of the requirement of massive connectivity, numerous technologies must be improved: channel coding, multiple access technique, modulation and diversity, etc. For instance, with 5G, the cost of signaling overhead and latency should be taken into account [1]. Besides, applying wireless access virtualization (WAV) should be considered and there is also a need to have effective implementations supporting novel virtual transceiver.

One of the possible new technologies for 5G is exploiting multiple access techniques to improve throughput. Therefore, instead of OFDMA in LTE (4G), applying a new multiple access technique called Sparse Code Multiple Access (SCMA) is an approach considered in this dissertation. SCMA is a new frequency domain non-orthogonal multiple access technique proposed to improve spectral efficiency of wireless radio access [2]. SCMA encoding is one of the simplest multiple access technique that offers an opportunity to experiment generic implementation methods. In addition, the new multiple access method is supposed to provide higher throughput, thus choosing SCMA encoding with less complexity could be an appropriate approach. The target with SCMA was to achieve an encoding throughput of more that 1Gbps.

SCMA encoding implementations were done both in software and hardware to allow comparing them. The software implementations were developed with the C programing language. Among several designs, the performance was improved by using different methods to increase parallelism, decrease the computational complexity and consequently the processing time. The best achieved results with software implementations offer a 3.59 Gbps throughput, which is 3.5 times more that the target.

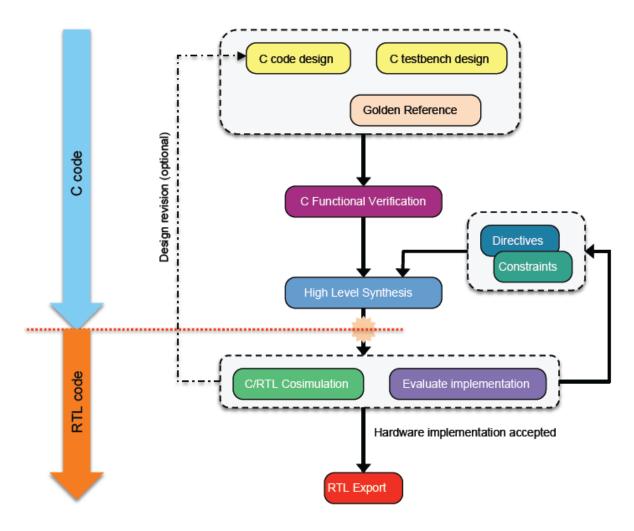

For hardware implementation, high level synthesis was experimented. In order to do that, the C based functions and testbenches which were developed for software implementations, were used as inputs to Vivado HLS. Regarding the characteristics of the design and Vivado HLS features, different sets of constraints and directives were applied to the designs to achieve the best

results. Finding the proper set of constraints and directives is quite challenging. The best achieved results with high level synthesis achieved an 8 Gbps throughput, which is 8 times more that the target. In spite of the fact that the main concern in SCMA encoding implementations is to have high throughput, to find the best design, the area complexity was also considered. Therefore, the best design was chosen based on an Area×Time analysis.

# TABLE OF CONTENTS

| DEDICATION                                       | III                          |

|--------------------------------------------------|------------------------------|

| ACKNOWLEDGEMENTS                                 | IV                           |

| RÉSUMÉ                                           | V                            |

| ABSTRACT                                         | VII                          |

| LIST OF TABLES                                   | XI                           |

| LIST OF FIGURES                                  | XII                          |

| LIST OF SYMBOLS AND ABBREVIATIONS                | XIII                         |

| CHAPTER 1 INTRODUCTION                           | 1                            |

| 1.1 CONCEPT OVERVIEW                             | 1                            |

| 1.2 RESEARCH OBJECTIVES                          | 5                            |

| 1.3 Contribution                                 | 8                            |

| 1.4 DISSERTATION PLAN                            | 9                            |

| CHAPTER 2 EFFICIENT HARDWARE ARCHITECHTU         | JRE FOR NEXT GENERATION OF   |

| MOBILE NETWORKS                                  | 11                           |

| 2.1 Wireless Network Virtualization Literatur    | Е12                          |

| 2.2 Next Generation Wireless Networks (5G) Lit   | TERATURE17                   |

| 2.3 Promising Research Ideas                     | 20                           |

| 2.3.1 Technologies for small packet transmission | 21                           |

| 2.3.2 Software-Defined-Networking                | 23                           |

| 2.3.3 Virtualized mobile core network            | 24                           |

| 2.3.4 Virtualized C-RAN                          |                              |

| 2.3.5 New waveforms                              | 25                           |

| 2.4 SCMA IMPLEMENTATION                          |                              |

| 2.4.1 SCMA a Solution Proposed for Improved 5G T |                              |

| 2.5 GENERIC TOOLS AND METHODOLOGY FOR HARDW.     | ARE ACCELERATORS DEVELOPMENT |

|                                                  | 33                           |

| 2.5.1 Programming tool                           | 33                           |

| 2.5.2 High Level Synthesis                       | 34                           |

| 2.6 Summary of Literature Review                                | 38 |

|-----------------------------------------------------------------|----|

| CHAPTER 3 SCMA ENCODING IMPLEMENTATION EXPERIMENTS              | 40 |

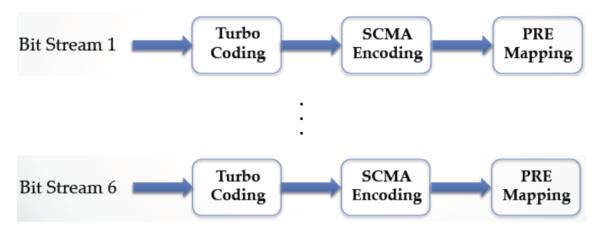

| 3.1 SCMA Transmitter Chain                                      | 42 |

| 3.1.1 SCMA Encoder                                              | 43 |

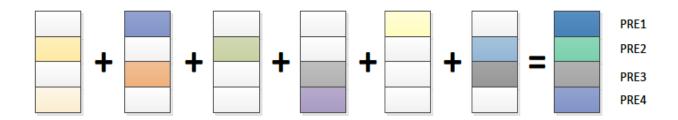

| 3.1.2 PRE (Physical Resource) Mapping                           | 44 |

| 3.2 MATLAB IMPLEMENTATION                                       | 45 |

| 3.3 SCMA Encoder Software Implementation and Results            | 46 |

| 3.3.1 Improved SCMA Encoder Software Implementation and Results | 49 |

| 3.4 VIVADO HLS IMPLEMENTATION EXPERIMENTS                       | 52 |

| 3.4.1 Improved Vivado HLS Implementation                        | 54 |

| 3.5 SUMMARY ON EFFORTS TO IMPLEMENT THE SCMA ENCODER            | 56 |

| CHAPTER 4 IMPLEMENTATION RESULTS                                | 59 |

| 4.1 SCMA TRANSMITTER CHAIN MATLAB IMPLEMENTATION RESULTS        | 59 |

| 4.2 SCMA Encoder Software Implementation Results                | 64 |

| 4.2.1 Improved SCMA Encoder Software Implementation Results     | 65 |

| 4.3 VIVADO HLS IMPLEMENTATIONS RESULTS                          | 66 |

| 4.3.1 Improved Vivado HLS Implementation Results                | 69 |

| 4.4 SUMMARY ON THE SCMA ENCODER IMPLEMENTATIONS RESULTS         | 73 |

| CHAPTER 5 CONCLUSION                                            | 74 |

| 5.1 SUMMARY OF THE WORK AND CONTRIBUTION                        | 74 |

| 5.2 Future work Objectives                                      | 77 |

| BIBLIOGRAPHY                                                    | 79 |

## LIST OF TABLES

| Table 3.1: Turbo Encoding using MATLAB Communication Toolbox                                                  | 45     |

|---------------------------------------------------------------------------------------------------------------|--------|

| Table 3.2: Codeword Mapping for one user                                                                      | 45     |

| Table 3.3: PRE (Physical Resource) Mapping                                                                    | 46     |

| Table 3.4: SCMA Encoding pseudo code for the first implementation                                             | 47     |

| Table 3.5: SCMA Encoding pseudo code for the second implementation                                            | 48     |

| Table 3.6: Configurable SCMA Encoding pseudo code                                                             | 49     |

| Table 3.7: Configurable SCMA Encoding with No Adder (Multiple Table) pseudo code                              | 51     |

| Table 4.1: The three preliminary software implementation results summary                                      | 64     |

| Table 4.2: SCMA Encoder Software Implementation with No Adder and Multiple Table Re                           | esults |

|                                                                                                               | 65     |

| Table 4.3: Running time profiling comparison among two versions of SCMA encoder                               | 65     |

| Table 4.4: First HLS implementation synthesis results                                                         | 66     |

| Table 4.5: Second HLS Implementation synthesis results                                                        | 67     |

| Table 4.6: Solution D HLS implementation synthesis results                                                    | 67     |

| Table 4.7: Solution E HLS implementation synthesis results                                                    | 68     |

| Table 4.8: Solution F HLS implementation synthesis results                                                    | 68     |

| Table 4.9: Summary of HLS implementation synthesis results for different implementations                      | 69     |

| Table 4.10: High Synthesis Results - SCMA Encoder with No Adder and Multiple Tables                           | 70     |

| Table 4.11: High Level Synthesis Results - Configurable SCMA Encoder with Parallelism Short Integer data type |        |

| Table 4.12: High Level Synthesis Results - Configurable SCMA Encoder with No Adder and S                      | Short  |

| Integer data type                                                                                             | 71     |

| Table 4.13: Summary of memory usage                                                                           | 72     |

| Table 4.14: Area×Time analysis results                                                                        | 72     |

# LIST OF FIGURES

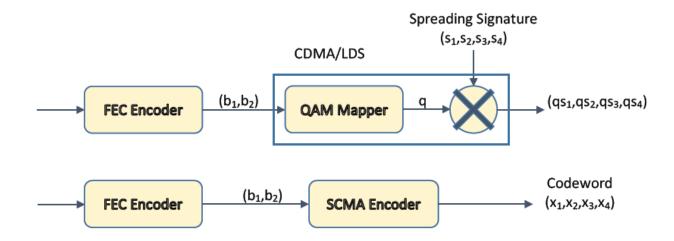

| Figure 2.1: Merged QAM mapper and Spreading in SCMA waveform                        | 28 |

|-------------------------------------------------------------------------------------|----|

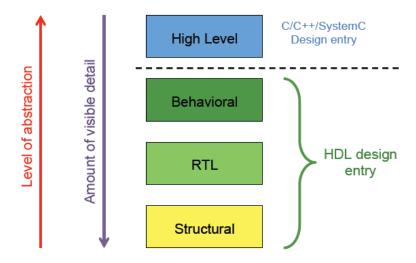

| Figure 2.2: Levels of abstraction for current FPGA design [55]                      | 35 |

| Figure 2.3: An overview of the Vivado HLS design method [55]                        | 35 |

| Figure 2.4: An overview of the Vivado HLS synthesis process [55]                    | 37 |

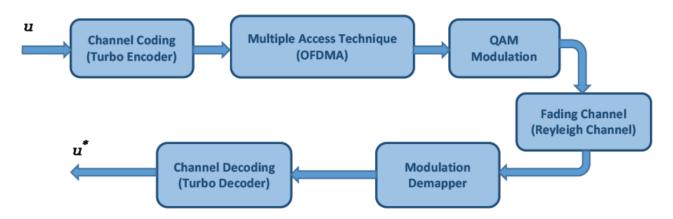

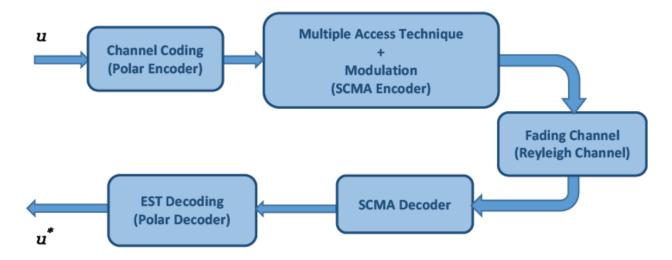

| Figure 3.1: An overview of 4G system technology                                     | 40 |

| Figure 3.2: Possible technologies for 5G system                                     | 41 |

| Figure 3.3: A Simple SCMA Transmitter Chain                                         | 44 |

| Figure 3.4: PRE mapping                                                             | 44 |

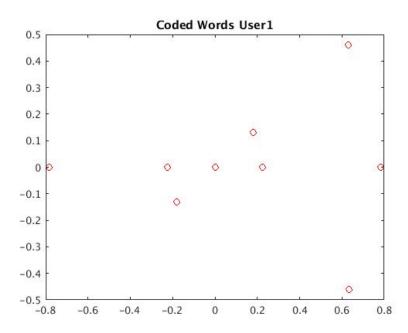

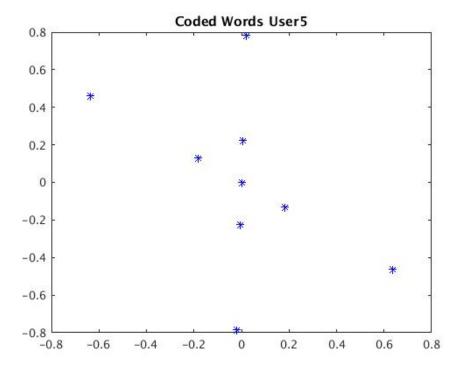

| Figure 4.1: SCMA Codewords presented by Constellation points – User1                | 59 |

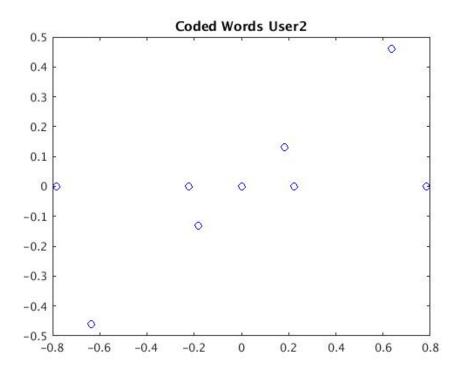

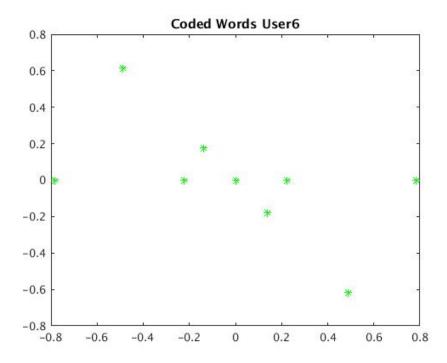

| Figure 4.2: SCMA Codewords presented by Constellation points – User2                | 60 |

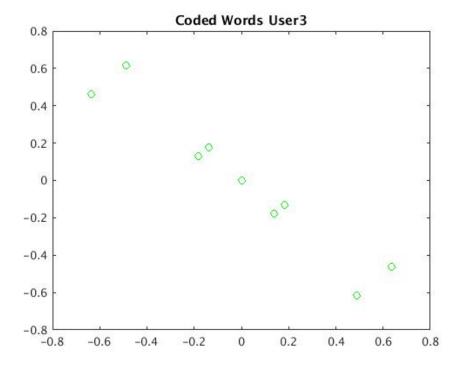

| Figure 4.3: SCMA Codewords presented by Constellation points – User3                | 60 |

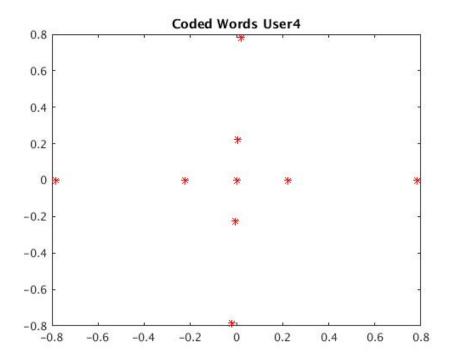

| Figure 4.4: SCMA Codewords presented by Constellation points – User4                | 61 |

| Figure 4.5: SCMA Codewords presented by Constellation points – User5                | 61 |

| Figure 4.6: SCMA Codewords presented by Constellation points – User6                | 62 |

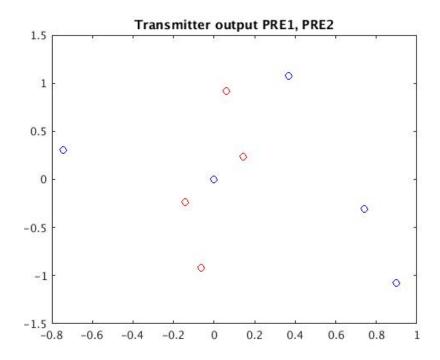

| Figure 4.7: SCMA Transmitter outputs presented by Constellation points – PRE1, PRE2 | 63 |

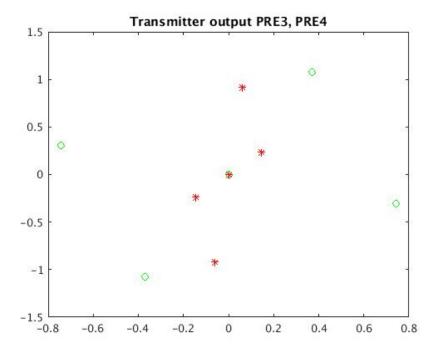

| Figure 4.8: SCMA Transmitter outputs presented by Constellation points – PRE3, PRE4 | 63 |

#### LIST OF SYMBOLS AND ABBREVIATIONS

3GPP 3<sup>rd</sup> Generation Partnership Project

BDMA Beam Division Multiple Access

CDMA Code Division Multiple Access

CQI Channel Quality Indication

CSM Code-Space-Multiplexing

DVS Distributed Virtual Switch

E2E End to End

FBMC Filter-Bank Multi-Carrier

FDMA Frequency Division Multiple Access

FEC Forward Error Correction

FTN Faster Than Nyquist

GbE Gigabit Ethernet

GFDM Generalized Frequency Division Multiplexing

GPRS General Packet Radio Services

IDMA Interleave Division Multiple Access

IoT Internet of Things

IPTV Internet Protocol Television

LDS Low Density Spreading

LTE Long Term Evolution

M2M Machine to Machine

MAC Media Access Control

MIMO Multiple-Input Multiple-Output

MPA Message Passing Algorithm

MUD Multi-User Detection

MVNO Mobile Virtual Network Operator

NGMN Next Generation Mobile Networks

NIC (Network Interface Controller)

NOMA Non-orthogonal Multiple Access

OFDMA Orthogonal Frequency Division Multiple Access

OMA Orthogonal Multiple Access

PHY Physical

PIP Physical Infrastructure Provider

PRE Physical Resource

PTP Precision Timing Protocol

RAT Radio Access Technology

RDMA Remote Direct Memory Access

RRC Radio Resource Control

RTL Register Transfer Level

SCMA Sparse Code Multiple Access

SDN Software Defined Networking

SIMD Single Instruction Multiple Data

SMS Short Message Service

SoC Systems on Chip

SON Self Organizing Networks

SP Service Providers

TDMA Time Division Multiple Access

UFMC Universal Filter Multi-Carrier

VN Virtual Network

VNO Virtual Network Operators

VNP Virtual Network Provider

VO Virtual Operator

WAM Wave Amplitude Modulation

WAV Wireless Access Virtualization

WNC Wireless Network Cloud

#### CHAPTER 1 INTRODUCTION

# 1.1 Concept Overview

Nowadays, the influence of information and communication technologies on the world economy cannot be denied and every innovation in this field is able to improve it. In the past, mobile communication was an expensive and luxury technology that just few people could afford, but today, it has become an accessible technology that is available almost everywhere and used by almost everyone. The most critical part in communication technologies is wireless communication networks that play an undeniable role in affordable broadband connectivity in the information society we have today. Also, it is growing extremely fast. For instance, mobile phone has changed from very simple devices with a simple screen and little processing capability to multitask devices with a large screen and a powerful processor. Besides this transformation in mobile phones, new wireless services such as social networking, web browsing and multimedia streaming are used more and more. In addition, users of other mobile devices like tablets have been added to mobile phone devices and constitute a large number of additional users of mobile devices. Furthermore, the mobile data traffic has been growing especially between 2010 and 2015 and it is expected to grow more in coming years, thus the current networks needs to be redesigned to increase coverage, data rate and capacity [1].

Obviously people can communicate more effectively in social or business manners when wireless networks develop more. Wireless networks have changed profoundly since the beginning of mobile communication systems. The network evolved from a simple telephone network which supports analog voice to a complex multitask network that supports hundreds of thousands of diverse applications and multimedia for billion users.

The first generation of mobile communication network was an analog radio system in 1980s but the first digital radio system that was called 2G introduced text messaging as Short Message Service (SMS) and circuit-switched data service with a maximum data rate of 9.6kbps. Later on, the General Packet Radio Services (GPRS) was offered in 2.5G, which introduced packet data in cellular networks. Then the first mobile network that was able to deliver data with higher bandwidth radio interface was unrolled as 3G that today is known as 3GPP (3<sup>rd</sup> Generation Partnership Project) and that is now used globally. The fourth generation of mobile network (4G) is LTE (Long Term

Evolution) or LTE-Advanced that is a more advanced release of more or less the same technology. The deployment of 4G happened in coincidence with a significant evolution of telecommunications systems supporting networks and mobile devices. [2] [3]

Although packet-switched service was introduced in 3G, it became a very important design goal for 4G as well as IP services. This service could provide a wide range of different services along with different requirements. The requirements include high data rate, high capacity and low latency targets. The maximum data rate in 2G was on the order of kbps, in 3G it was on the order of Mbps but for 4G it should have been close to Gbps. Capacity to provide data rate for lots of users was another challenge in 4G, because the shortage in capacity influences the quality of service. Capacity has been measured as spectral efficiency. In 4G, latency plays a critical role in real time applications, and it was measured as a delay experience by a packet from a server to its reception by a user. [3]

3G and 4G networks were mainly designed to provide a consistent coverage, but that coverage was specifically intended for outdoor services, particularly when it is delivered with macro-cells. By contrast, the upcoming fifth generation mobile technology (called 5G) is a heterogonous frameworks. High data rate services are offered by leveraging indoor hotspots, and voice services as well as other data rate services are always consistent in the whole system. These kinds of services make differentiate 5G. Also, in 5G users should be able to have both indoor and outdoor connectivity simultaneously. Therefore, one of the main changes in 5G should be a design combining macro based telecommunication paths and local telecommunication paths [4].

Form another point of view, Internet of Things (IoT) is becoming more and more popular, and it can be highly beneficial if it is utilized for industrial purposes or in health related applications. This should increase in amount of data that the network must handle, setting a requirement for extra capacity that requires both additional spectrum as well as higher spectral efficiency.

In order to provid service to many users, bandwidth must be expanded. Although 4G supports high downlink data rates of up to 1 Gbps, 5G networks need to provide much higher data rate and extended coverage. Therefore, lots of interests go to beyond 4G technologies. The most important and the first thing that should be reconsidered for next generation of wireless networks is wireless standards, specially data rates and spectral efficiency.

The prediction says that fifth generation wireless networks will be deployed around 2020. There are clear requirements for low latency and more than one Gbps data rates [5]. In order to improve spectral efficiency, a main challenge is to have smaller cells for network nodes, better interference mitigation and using massive MIMO (multiple-input multiple-output) techniques.

Furthermore, different wireless devices have different variety of features and characteristics such as cost, hardware platform and processing power. Accordingly, different applications need different and diverse data rate and latency. Therefore, diversity in devices as well as in the applications should be taken into account as another technical challenge.

As a brief, some of the main 5G requirements in comparison with 4G discussed in the NGMN (Next Generation Mobile Networks) white paper [6] are:

- Higher capacity, 100 to 1000 times more

- Providing Gbps data rate everywhere

- Less that 1ms latency for E2E use case

- Higher connectivity rate, 10 to 100 times more

By providing these main requirements for 5G networks, users will experience better quality of services in terms of connectivity and data rate. To deliver higher data rate and capacity, some technologies should be considered such as massive MIMO, millimeter wave spectrum usage, D2D (device to device) connectivity and using more small base station in order to support multi-RAT (Radio Access Technology). Using small base stations can leverage small cell networking to enhance inter-cell interference but it needs to be improved in terms of its performance in the peak traffic. [7]

The predictions express that in the next decade the data rate will be doubled each year and to prevent increasing in the users' costs, some new, innovative and cost effective wireless access should be provided by the wireless communication industries. In this way, to achieve new applications like machine to machine (M2M) communication and cloud computing require diverse features. Also, advanced signal processing, heterogeneous base stations and finding new way to use spectrum much more efficient can be some of potential technologies for 5G.

Furthermore, being continuesly connected has more benefits for people that just being able to connect in the future and even now that new generation of wireless networks are trying to provide. These benefits include diverse applications to control the traffic, monitor different systems for safety, having remote access to the household appliances, medical purposes and much more. As a consequence, for making next generation of mobile networks commercialized and available for users the preliminary step is to figure out the requires characteristics and features. The second step is to reconsider the existing standards for wireless networks and prepare new standard package for components of 5G system.

However, data traffic demand from mobile board band will increase more in the future. With this assumption that the wireless networks deliver the service to the users with the same energy consumption like existing networks, the cost of delivering a bit to the end user will significantly increase in the massive traffic. Therefore, 5G networks have to offer lower energy consumption components to keep the cost of traffic as low as possible. In addition, for 5G networks there is a need to provide data rate about 10Gbps for specific purpose but the data rate that should generally be accessible for the users must be more that 100Mbps. Finally at least a few Mbps must be available everywhere and all the time. In addition to high demand for traffic and data rate, machine type communication like M2M needs some other requirements to be used in 5G [7].

The applications related to machine type communication needs very low access latency to perform their tasks perfectly, specially in critical mission such as traffic safety or some emerging industrial Internet applications that need less that 1ms as latency. LTE provides acceptable latency for lots of applications but for latency-critical applications this amount of latency is not acceptable to be sure that the application works well in order to perform its task in a timely manner. Also, this kind of applications requires a reliable connectivity that the network is able to guarantee its availability. And this reliability for the service should be higher than what exist in LTE as well which has already had a high reliability.

On the other hand, as it is mentioned, 5G needs to deliver very low cost connectivity and traffic. Therefore, for massive machine type connectivity 5G can use very large number of connected devices and sensors with low cost connections that consume a small amount of energy. Thus they can operate continuously for several years without need to recharge. Consequently, some features, performances and capabilities of next generation of wireless access needs to be improved. These improvements should be done in dimensions such as traffic capacity, higher data rate, access latencies and massive diverse connectivity that are figured out from the user experience of LTE

wireless networks.

In brief, beyond 2020 5G technology will provide a telecommunication service to deliver information and data to anyone and anything, anytime and anywhere in land.

## 1.2 Research Objectives

In comparison with what today wireless networks deliver, next generation must provide a much wider range of access requirements. In order to do that, 5G needs to consider a novel multiple access technique which has a high spectral efficiency. Besides, the performance of wireless communication networks depends on multiple access techniques. Thus, multiple access techniques always are the key technology in wireless network from the first generation till today. In general, there are two classes of multiple access techniques that are orthogonal and non-orthogonal. This classification is done based on how the resources are dedicated to the users. Since in the orthogonal multiple access techniques (OMA), no inter-user interference exists, the receiver can utilize a low complexity detection method to receive the signals form users. However, in the non-orthogonal multiple access techniques (NOMA), there is interference among users because all users can use all resources simultaneously. Thus, there is a need to use more complex techniques in the receiver that are called as multi-user detection techniques (MUD) [8]. In the OMA techniques, signals from users are placed orthogonally to each other and therefore the cross correlation between them are zero. While in NOMA techniques, inter-cell interference become important and they have non-zero cross correlation.

Both OMA and NOMA techniques have their own advantages and disadvantages. OMA cannot provide a high spectral efficiency in uplink and system upper bound, while NOMA techniques deliver high spectral efficiency. On the other hand, OMA techniques have a proper performance but NOMA techniques needs complex MUD techniques that must be implemented at user devices and because of limited processing capability in users' equipment, that is not easy. Since the spectral efficiency plays an important role in delivering service to users in a fair manner in the system and considering a high demand for it in the future, NOMA technique can be a better option than OMA techniques. In an optimal NOMA techniques, users share the resources in time or frequency domain but the number of users of each subcarrier are not controllable that causes MUD technique implementation too difficult. However, some techniques such as CDMA (Code

Division Multiple Access), IDMA (Interleave Division Multiple Access) and LDS (Low Density Spreading) by using some coding and spreading methods can help NOMA to separate users at receiver [8].

In the first and second generations, FDMA (Frequency Division Multiple Access) and TDMA (Time Division Multiple Access) were used respectively. In 3G and 4G, CDMA and OFDMA (Orthogonal Frequency Division Multiple Access) have been used. The previous orthogonal techniques users are allocated orthogonally to the resources and the resources could be in time, frequency or code domain, while NOMA techniques are usually based on power domain instead of time, frequency or code domains and make all subcarriers available for each user. Although these orthogonal multiple access techniques have provided acceptable gains, for 5G considering spectral efficiency and Internet of Things (IoT) requirements, NOMA techniques are better choice. In addition, NOMA can provide the timely manner service to users with different channel conditions that eventuates very low latency and very high connectivity [3].

The first generation of mobile networks delivered a data rate up to 2.4kbps while the second generation provide the data rate of 64kbps to 144kbps. The 3G networks in the beginning has data rate of 2Mbps but after some improvement in this generation the delivered data rate was increased about 5Mbps to 30Mbps. Although in 4G, data rate has been improved up to 1Gpbs that is very significant in comparison with previous generations, regarding the high demand for connectivity in 5G this amount is not enough [4].

In 4G system, an orthogonal frequency division multiplexing (OFDM) used with an advanced radio interface. This system provide up to 1Gbps. OFDM can be used as multiple access technique that provide separated transmission in frequency domain to or from different terminals. In uplink, for data transmission from different terminals a set of subcarriers are used and also in downlink for data transmission to terminal a set of available subcarrier are used. This process is called OFDMA (Orthogonal Frequency Division Multiple Access). Since in OFDMA transmission is done from different terminals, time alignment in the base station is very important. Therefore, there is a need to use some timing and synchronising control techniques. Even with a perfect transmission time control scheme, interference between some subcarriers is inevitable because of some frequency errors. While in a NOMA scheme there is no need to have such synchronization [3].

CDMA is an orthogonal approach which is used in 3G networks has a proper performance in terms of inter-cell interference cancelling and robustness against fading but it is not suitable for high data rate especially for asynchronous transmission environment. Consequently, this technique is not a good choice for 5G and it is needed to utilize other approaches [9].

Another approach for 5G multiple access is combining two techniques, one orthogonal and one non-orthogonal. The idea is to consider two regions for the cellular network and use one technique for inner region and the other technique for outer region. OFDMA can be used for inner region and a specific case of CDMA (CP-CS-CDMA) for outer region. The reason of using OFDMA for inner region is the interference and the reason of using CDMA for outer region is higher system capacity. It seems that to choose between a NOMA scheme and a combination scheme for 5G networks, it is required to determine the radio technology aspect for 5G in order to adapt an appropriate multiple access technique to that [9].

In almost all the present multiple access techniques, the resources such as time and frequency are divided between the users, therefore each user has a portion of resources and the system capacity depends on time and frequency that make some limitation for the system capacity. Another proposed multiple access technique for 5G is BDMA (Beam Division Multiple Access) that is independent on time or frequency. In BDMA, the antenna beam is divided by the base station and dedicated to mobile station according to mobile station location. This scheme helps to increase the system capacity. Since, the angle of mobile stations to base station can be different, base station can transfer data to different mobile stations simultaneously. BDMA is expected to provide more than 1Gbps that make it a very interesting option for 5G but its performance can be challenged when some mobile stations locations are in the same angle with base station. In the case the mobile stations are in this situation, they need to share the same beam thus the data rate they receive is less than the case the mobile stations are in different angle with base station. Also the beam these mobile stations share should have lower peak to decrease power ratio problem [10].

The 5G mobile technology is characterized by a tremendous growth in connectivity and density of traffic. In comparison with 4G-LTE (Long Term Evolution), fifth generation wireless technology aims to support massive connectivity of different devices and diverse applications at the same time, with levels of performance beyond what is offered by LTE. In pursuance of the requirement of massive connectivity, numerous new technologies are to be improved: channel

coding, multiple access, modulation and diversity etc. Therefore, the cost of signaling overhead and latency should be taken into account while considering the 5G environment [11].

CDMA technique works like a coding procedure that encode the binary data to a multidimensional complex data. LDS is a specific scheme of CDMA that use a few nonzero elements in coding sequence. SCMA (Sparse Code Multiple Access) have some similarity with CDMA and specially LDS but it is a non-orthogonal multiple access. SCMA uses coding process form binary domain to multidimensional complex domain. This encoding process can be done differently for different users and in the receiver users' data can be detected using MPA (Message Passing Algorithm) because of sparse feature of coding process. By using SCMA, system can be overloaded like LDS when the number of users are higher than spreading factor which is the codeword length in SCMA [11] [12].

As LTE networks do not support massive connectivity in the uplink, SCMA as a new multiple access scheme with the characteristics of providing massive connectivity can be a proper substitute for OFDMA. SCMA with a large number of layers allows system to be overloaded that enables massive connectivity. Each layer in SCMA represent a user and has a specific coding process as a codebook.

The research objective in this project is to implement SCMA main uplink algorithm, as a new multiple access technique, SCMA encoder to propose a new encoding system for next generation of mobile networks.

#### 1.3 Contribution

As it was explained in previous section, one the basic requirements for 5G is new multiple access and a NOMA technique is much more suitable for this purpose. SCMA is one of the most novel multiple access techniques that is proposed for 5G. It is expected to provide more than 1Gbps data rate and because of sparsity it is also expected that the implementation complexity of SCMA algorithms are in the acceptable levels. Therefore, in this thesis, the efforts are focused on implementing one of this algorithms that is fundamental for uplink SCMA system. This algorithm includes SCMA encoding part and multiplexing part that have the responsibility of encoding binary data of SCMA layers to multidimensional complex codes and provide multiplexing for physical resources.

My main contribution in this project is to implement a SCMA encoding system both in software and in hardware in order to have more than 1 Gbps throughput. Another contribution is to experiment high level synthesis as a proper substitude for low level synthesis and HDL codes. The results of this experiment are useful not only in implementing SCMA encoding but also in implementing other algorithms needed for 5G wireless communication.

In the process of SCMA encoding implementation, since the main application for uplink SCMA system is for base stations, two types of implementation are considered with a goal of delivering a data rate more than 1Gbps. In order to do that the processing time for each bit of each data layer must be less than 1ns. Therefore, encoding algorithm should be deeply reviewed in terms of computational complexity to figure out the obstacles in minimizing processing time for a bit. The implementations both in software and hardware are done and have being improved regarding algorithm complexity assessment. Sometimes, to reduce computational complexity the algorithm and consequently the implementation code needs to be re-arranged but these re-arrangements and other complexity reduction techniques almost never reduced the accuracy of encoding.

Although the most popular way to implement a hardware on FPGA is using HDL codes, in this thesis another way has been experimented that is High Level Synthesis (HLS). For HLS instead of a low level programming language like HDL, a high level language like C, C++ or SystemC is used that helps to improve time and cost efficiency of hardware implementation. The chosen language for software implementation in this thesis is C that make a proper opportunity to re-use the codes for HLS implementation as well.

The achieved results were benchmarked using 4G data rate range and the turbo encoder implemented by Xilinx. These results illustrated that the processing time for each bit in the implemented SCMA encoding is much less that 1ns both in software and hardware. Therefore, the achieved data rate is much more than 1Gbps that 4G delivers in uplink. Consequently, the target dedicated to this project was obtained.

#### 1.4 Dissertation Plan

This dissertation choses SCMA encoding technique to experiment implementations for a possible uplink system in 5G networks and proposes two types of SCMA encoding implementations, software and HLS. The organization of this document is as follow. Chapter 2

reviews the literatures considering Virtualization in wireless networks, 5G networks, SCMA technique and implementation methodology in 4 sections. Chapter 3 explains the SCMA encoding algorithm and implementations experiments. In this chapter, the improvement process and experiments performed to achieve the target in terms of high data rate is discussed. In addition, it includes explanation about how to use different options of hardware synthesis. This describes all experiments done in Xilinx Vivado HLS. The results of all different implementations both in software and hardware are listed in Chapter 4. This chapter provides an opportunity of making comparisons among software and hardware implementations regardless of type of implementation and also between different versions of software implementations and hardware implementations themselves. The achieved results are calculated for SCMA encoding system contain SCMA encoder and physical resource multiplexing. All these results are studied and benchmarked in order to validate them and represent the high performance SCMA encoding system.

# CHAPTER 2 EFFICIENT HARDWARE ARCHITECHTURE FOR NEXT GENERATION OF MOBILE NETWORKS

In homogeneous or heterogeneous wireless virtual networks (VNs), hardware platform architectures need to assign resources to perform different functionalities in order to support Wireless Access Virtualization (WAV), which is a major challenge. Therefore, new accelerator architectures are required to enable WAV at both PHY (Physical) and MAC (Media Access Control) layers. New architectures should consider deterministic low latency means for computation that could have energy efficiency management scheme as well. Co-operation between multi-tier Heterogenous Networks (HetNets) with different parameter settings and timing synchronization schemes is another challenge of future 5G systems. In addition, some issues that should be considered in the design of baseband accelerators are listed as follows:

- Defining efficient hardware platform architectures to enable WAV using CPU cores, DSP cores and baseband accelerators;

- Forward error correction (FEC) encoding and decoding;

- MIMO signal processing;

- Developing virtual cores to support new features such as channel aggregation and distributed signal processing across distributed platforms;

- Designing baseband accelerators with the least-overhead that offer distributed signal combining and interference suppression techniques;

- Considering various constraints related to synchronization complexity, throughput and latency in baseband accelerators design;

- Implementing synchronization mechanisms in the HetNet WAV.

Considering that one of the main challenges in this thesis is reducing computation time in the proposed architecture in next generation of wireless networks (5G), several previous contributions were reviewed to leverage methods and protocols for 5G that can lead the project to define a high performance hardware architecture. Some results of this literature review are summarized in this chapter that is divided into six sections. In Sections 2.1, 2.2 and 2.3, the literature concerning wireless network virtualization, 5G networks and research ideas about 5G are reviewed respectively. In Section 2.4, SCMA algorithms are reviewed. Section 2.5 describes generic tools and methodology for hardware implementation. Finally, Section 6 summarizes the key points

reviewed in this chapter.

#### 2.1 Wireless Network Virtualization Literature

Virtualization in wireless networks allows a node to split physical resources between different system users [13]. Although many technical issues must be addressed for successful realization of virtualization, flexibility, security, diversity and manageability are provided for multiple heterogeneous network architectures sharing a substrate of network virtualization [14], [15]. Extra functionality at no extra cost and better resource control are the most important potential benefits of virtualization [13]. The first definition of network virtualization categorizes the roles of the traditional Internet service providers into two independent entities. These two entities are infrastructure providers and service providers, which manage physical infrastructure and create virtual networks respectively [16], [17].

The first step toward virtualization is providing isolation between multiple virtual entities but, in the wireless context, isolation is not guaranteed by over provisioning [13]. Also, as wireless spectrum does not increase, advanced resource isolation models are needed. The second step involves resource partitioning, which may depend on the hardware capabilities. Thirdly, wireless technologies enable a different level of flexibility in the medium access operations, which does not generally allow full control of the medium and differentiation of virtual entity behavior [13].

There are different levels of virtualization of wireless networks resources based on levels of isolation, flexibility and partitioning. A temporal partitioning of the hardware in terms of channel switching and power saving, and a MAC scheme for virtual interfaces are the most common solution for virtualization. In addition, solutions for virtualization can be a simple scheduling virtualization framework or a complex low level differentiated MAC functionality management [13].

The idea proposed in [13] is performing virtualization functions utilizing a hardware platform in terms of a MAC engine, which is abstracting the device resources and capabilities, and a virtual MAC monitor, which is solving the hardware conflicts. The MAC machine, which is proposed in [6], is a MAC program executer. It is a high-level state machine that can be implemented on different system cards as follows [13]:

• A source state, which is the starting state of state machine operations;

- A trigger event, like a signal generated by the hardware platform;

- An action, representing an atomic program code, which can also work on the hardware configuration registers;

- An optional guard condition, to be evaluated after the trigger event.

The responsibility of the virtual MAC monitor, which is proposed in [13], is controlling and managing access to the hardware. To implement a virtual MAC monitor, there are two approaches. The first approach is a classical time-based mechanism. This mechanism assigns the hardware to a single virtual entity in a given time interval. The second approach is a virtual collision management mechanism. This mechanism uses time slicing and virtual slicing to perform multiple accesses to the hardware. In the time slicing approach, the virtual MAC monitor enables the MAC engine to do thread switching and in case of virtual collision, the virtual MAC monitor enables parallel MAC machine execution.

Also in [13], a MAC virtualization architecture is proposed, whose main components are the MAC Engine and the Virtual MAC Monitor, where the MAC Engine acts as a host. It is an abstraction of the hardware in terms of actions, event signals and configuration. The Virtual MAC Monitor allows exposing multiple virtual engines, which can independently run their guest MAC machines and corresponding upper network applications.

In [15], an architecture for network virtualization is proposed. It is composed of four main parts: Physical Infrastructure Providers (PIPs), Virtual Network Providers (VNPs), Virtual Network Operators (VNOs) and Service Providers (SPs). In this architecture, the SP gives his requirements to the VNO. This VNO encloses its needs on the VNet, and then on a chosen VNP, which is responsible for assembling the VNet, is provided with this description. Each VNet has a data plane, which refers to a virtual network context, and a control plane, which is necessary for specific VNet management tasks during VNet operation. This architecture defines the interaction between the roles of this architecture without prescribing their internal organization, structure and policies.

Generally, virtualization of the wireless medium is performed based on a Time Division Multiple Access (TDMA) virtualization technique [19]. The main purposes of wireless medium virtualization are sharing the network infrastructure and sharing an over-provisioned wireless infrastructure with lower usage of resources [20], [21]. Although sharing the use of wireless

medium bandwidth is a form of wireless medium virtualization, the main goal of this sharing is maximizing the use of the wireless medium while preserving the quality of service.

In [19], a wireless network virtualization method is proposed. That method considers network usage and quality of service. The method introduces a scheduler to organize wireless medium access from a node. Inside the node, there is a simple traffic management aspect. It stores the arriving packets in a virtual operator (VO) queue and then the TMDA scheduler sends the corresponding packets to the wireless interface based on the type of traffic and scheduling techniques.

A packet that enters the VO queues suffers from a delay until it is transferred to the wireless interface; that is called packet delay. The duration of this delay depends on the number of packets waiting in the VO queue, the time slot duration, the number of VOs and the available bandwidth. The variation in delay, especially in services like voice application, is called jitter [22]. If the VOs have only one traffic, the delay is very low, but if they have two traffics the delay stays very similar to their peers in the symmetric scenarios.

In [23], the authors propose Cabernet (Connectivity Architecture for Better Network Services), a three-layer network architecture that lowers the barrier for deploying wide-area services. They introduce many challenges: how do the connectivity providers build virtual networks, and what do they need from the infrastructure providers? What is the functionality required at the infrastructure routers or servers to realize Cabernet while achieving high performance? How can the network services run on this layered architecture? The paper discusses how these challenges are addressed in the Cabernet design. Although IPTV (Internet Protocol Television) delivery is the case study used to develop and explain this design, there is no experimental result in this paper.

In [24], the authors propose a wireless network cloud (WNC) for a wireless access network. It provides all the necessary transmission and processing resources in a cloud. They analyze several important system challenges involving computational requirements of virtual base stations, I/O throughput, and timing networks for synchronization.

They consider six scenarios to implement WNC (just description, no details or results):

1) considering WNC as a resource pool to support various kinds of wireless access networks,

- 2) considering a Mobile Virtual Network Operator (MVNO),

- 3) considering different wireless traffic in the daytime and nighttime,

- 4) involving the rural area,

- 5) collaborating of multiple BSs (Base Station) in the PHY layer signal processing such as in cooperative MIMO, and

- 6) using open IT platforms in the WNC.

They mention that precise synchronization and timing is required to avoid interference. The IEEE 1588 Precision Timing Protocol (PTP) is used in this platform. Three kinds of structure are considered to construct the virtual BS pool. In the first structure, the software packages of virtual BS-PHY and virtual BS-MAC are combined into one virtual BS. In the second one, virtual BS-PHY and virtual BS-MAC are separated. Furthermore, one virtual BS-MAC can serve multiple virtual BS- PHY components. The third structure supports the cooperative radio processing which implies splitting the workload between base stations for most efficiency.

Reference [24] explains that multithreaded processors such as IBM wire-speed processor (with 16 cores and 64 hardware threads) and the Raza XLR processor (with 8 cores and 32 hardware threads) could match the multithreaded program model in the MAC layer. Also, the authors propose network accelerators and cryptographic coprocessors to accelerate MAC-layer processing. Furthermore, they state that the MAC-layer requires 10% of the computation resources of the whole BS, while the PHY layer uses 90% of the resources. It is stated in this paper that only 29.6% of the instructions in the PHY layer are SIMD instructions.

In [24], system throughput of the WiMAX BS-PHY stack using a Cell/B.E. Blade is demonstrated for three scenarios. The first scenario is related to computation only. In this case, all the R-B link data are stored in memory rather than in the Ethernet interface. The R-B link refers to the link between the radio front end and the virtual BS pool. This link is able to support the topology of multiple-point to multiple-point models. The second result is for the scenario with computation and data transfer over a 10GbE (Gigabit Ethernet) interface without RDMA (remote direct memory access). Compared to the case of computation-only, it has a 68% performance loss. The third result is for the scenario with computation and data transfer over a 10GbE interface with remote direct memory access (RDMA). It only has a 4.5% performance loss when compared with the one for computation-only. With RDMA, data can directly be moved between the memory of the RRH and

the virtual BS, or between two virtual BSs, without involving the operating system of either one. Only a small overhead is required for a zero-copy protocol used in RDMA.

The IEEE 1588 PTP provides a means by which networked computer systems can agree on a master clock reference time, as well as a means by which slave clocks can estimate their offset from a master clock time. The closer the time stamp is taken from the hardware transmission or receipt of the messages, the smaller the latency, and consequently, the accuracy is also better (of the order of  $10\mu s$ ).

As a conclusion, the WNC proposes two important ideas that can be useful for new wireless architectures. First, it adopts an open IT architecture that could replace today's proprietary hardware design in a BS system. Second, cloud-computing concepts are used in building the wireless access network. To meet the computational requirements, SIMD techniques or reconfigurable hardware accelerators (e.g., FPGAs) of channel decoders can be considered in future multicore and SMT-based system designs. To relieve the CPU overhead for the high I/O throughput on an R-B link, different methods should be considered for the virtual BS platform, such as RDMA over the R-B link, processors with network accelerators, or the advanced Ethernet NIC (Network Interface Controller) with an OS-bypass functionality. To construct an accurate timing network with the IEEE 1588 PTP, the authors in [24] propose a software implementation using multicore processors with a network accelerator.

The challenge in [25] is to allow multiple OS images to transparently share the same physical server and I/O devices. It requires supporting local switching between different virtual machines within the same server. In [25], Cisco and VMware have collaborated to define a set of APIs that enable transparent integration of third-party networking capabilities within the VMware Virtual Infrastructure. VN-Link (Virtual Network-Link) provides another solution as a Cisco Distributed Virtual Switch (DVS) running entirely in software within the hypervisor layer (Cisco Nexus 1000V Series).

In [26], the challenge is to analyze the feedback mechanisms for CoMP transmission modes. The aim is reducing the overhead of signaling in CoMP. Authors in this paper mention implicit feedback methods for different CoMP modes. They have two proposals. Firstly, they recommend per cell reporting of the feedback regardless if an implicit or explicit one is used. Secondly, they recommend if implicit feedback is agreed upon mechanism, a single additional joint

Channel Quality Indication (CQI) is included along with the per cell feedback.

In [27], the idea is to deploy and evaluate researchers' ideas with real routing software, traffic loads, and network events. The challenge is to explore a set of concepts and techniques, which facilitate flexible, realistic, and controlled experimentation (e.g., multiple topologies and the ability to tweak routing algorithms) on a fixed physical infrastructure. Virtual network infrastructure's (VINI's) high level design and the challenges of virtualizing a single network are presented. Further, PL-VINI, an implementation of VINI on PlanetLab, running the "Internet In a Slice" is proposed. The evaluation of PL-VINI shows that it provides a realistic and controlled environment for evaluating new protocols and services.

Based on this paper, constructing a virtual network involves solving four main problems. First, the infrastructure must provide support for virtualizing network devices and attachment points because a network researcher may wish to use the physical infrastructure to build an arbitrary topology. Second, once the basic topology is established, the infrastructure must facilitate running routing protocols over this virtual topology. Third, once the virtual network can establish its own routing and forwarding tables, it must be able to transport traffic to and from real networks. Finally, the virtual network infrastructure should allow multiple network researchers to perform the above three steps using the same physical infrastructure. Experimental results show that running Internet In a Slice (IIAS) architecture on PL-VINI provides a 4 times increase in throughput and reduces variability by over 80%.

Authors in [28] provide some qualitative analyses on the principle of CoMP, and point out some issues within the scope of the CoMP technology. For intra-eNodeB co-operation, it is necessary to further investigate coordinated scheduling, channel measurement and estimation, interference management, and overhead. For inter-eNodeB cooperation, it is important to consider the balance between the flexibility of cooperation and the modification of X2 interface. Additionally, a virtual BS pool will require real-time support from the OS, hypervisor, and scheduler.

## 2.2 Next Generation Wireless Networks (5G) Literature

The fifth generation of mobile technology (5G), which is positioned to address the demands and business contexts of 2020 and beyond, is a main concern of our research. For the first step,

recognizing the status of 5G seems essential to figure out the up-link/down-link processing chains and suitable algorithms for each step. Thus, we performed a literature review that led us to believe that the 5G definition is in a very preliminary stage. In order to confirm this, we looked at the recently published NGMN (Next Generation Mobile Networks) White Paper that gives critical information that reviews features of 5G that are defined together with other aspects that are hard requirements or nice to have features. This is partly defined in comparison with 4G [6].

For future mobile communication networks, some technologies need innovation such as signal processing techniques, spectrum usage concepts, air interface numerology and usage of more heterogeneous base stations. Some key challenges for this purpose, which are inherent in designing and systems operation are interference, mobility and session management, and network infrastructure [18]. Regarding those key challenges, Cellular M2M (Machine-to-Machine) connections, Cloud computing and Three-dimensional (3-D) video are required for future mobile communication networks. Also, future systems will require more flexibility and especially for M2M connections, systems need to be more robust in time and frequency, while enabling low-power and low-cost operation in sensor nodes.

As interference scenarios are frequently changing, more complex, out of operators control and less structured, interference management is a key concern. Various solutions should be analyzed in consideration of required resources and various modulation schemes exploited for different services. Additionally, a fundamental question regarding interference management is where knowledge about interference is available and where decisions on its management are performed.

To answer this question two solutions are proposed: single-cell solutions and multi-cell solutions (decentralized solutions, centralized solutions). Compared to 4G, various use cases for 5G are associated with more handover between base stations. Thus, mobility and session management has to be performed more often based on radio condition, service availability for certain types of traffic and QoS level [18]. Some networks have features to enhance mobility, such as the ability to obtain and distribute information on the access point topography and traffic flow statistics, and ability to decide which cell should give service to a particular device and trigger handover. In future mobile communication networks, in order to simplify device architecture and reduce power consumption, device related overhead has to be minimized.

Another important challenge in future mobile communication networks is the way data is transmitted or information is exchanged between access points [18]. Considering required research, there is a need to investigate where devices have links to different cells in uplink and downlink connections or through data and control channels, in order to provide alternative connectivity and signaling concepts, respectively. Also, research should be performed on virtual cell concepts, alternative session management methods, and protocol stack modifications allowing reduced signaling overhead in low payload M2M connections.

Requirements for 5G can be defined relative to the level of performance in 4G. Thus, it is expected that 5G will provide: 100-1000 times higher system capacity, user data rates in the order of Gbps everywhere, latency in the order of 1 millisecond for E2E (End to End) use case, while supporting 10-100 times more connected devices per area, and offering 10 times longer battery life for portable devices [6], [7]. Whether all these characteristics will be met simultaneously remains to be seen.

To enable technologies and architectures for 5G wireless communication networks, there are some candidate solutions including: utilizing more compressive heterogeneous networks with large number of small base stations supporting various Radio Access Technologies (RATs), using very large Multiple Input Multiple Output (MIMO) arrays, utilizing millimeter wave spectrum where larger wider frequency bands are available, direct device to device (D2D) communication, and simultaneous transmission and reception, between others [7]. Hence, densification using multi-RAT HetNet can provide significant gains in average cell and celle-dge throughput possible in comparison with LTE-only small cells in a typical deployment with 4 outdoor small cells (pico cells) per macro cell [29]. Also, to achieve higher spectral efficiency for cellular systems, advanced MIMO techniques and specially MultiUser MIMO offers higher multiplexing gain. Direct device to device (D2D) communication are considered to support data exchange between user devices without using base stations or the core network. D2D could increase network capacity by reusing the spectrum, which is an effect similar to that obtained with macro cells. That could also be done by using otherwise unused unlicensed spectrum. In addition, full duplex would allow a wireless device to transmit and receive data in the same frequency band simultaneously. That would increase the physical layer capacity, which could be a good technology for 5G wireless networks [7].

In [30], a proposed cellular architecture would separate indoor and outdoor scenarios. In this architecture, a distributed antenna system and massive MIMO technology are required [31]. According to that proposal, a large number of antenna arrays are distributed geographically. Although this architecture would likely increase the cost of the infrastructure, it is expected that it would improve cell average throughput, spectral efficiency, energy efficiency and data rate in the long term. A massive MIMO system, which consists of multiple antennas at the transmitter and receiver, can enhance both spectral and energy efficiency [32]. As a novel MIMO technique, spatial modulation (SM) is proposed. In SM, some part of the data encodes information to be transmitted onto the spatial position of each transmit antenna in the array. SM can alleviate three important problems in MIMO systems: inter-channel interference, inter-antenna synchronization and multiple RF chains.

Cognitive Radio (CR) is another part of the architecture proposed in [30]. It is a software defined radio technique proposed to improve the utilization of the congested RF spectrum. Generally, a CR network needs to be aware of the surrounding radio environment and manage its transmission accordingly. As a result, the proposed techniques provide high quality and high data rate services to indoor users and reduce the pressure on outdoor base stations at the same time [33].

# 2.3 Promising Research Ideas

In order to propose enhancements contributing to the deployment of fifth generation mobile technology (5G), one of first steps is to understand the status of 5G. It seems essential to define some up-link/down-link processing chain, including algorithms suitable for each step. In order to confirm this observation, the NGMN White Paper [6] provides very useful information.

NGMN (Next Generation Mobile Networks) is an industrial cooperative initiative that has a core mandate of defining operator requirements for 5G. The NGMN White Paper was published in February 2015 as a guideline to facilitate 5G definition and design. The NGMN requirements discussed in the White paper cover a number of areas to leverage the overall success of LTE and the structural separation of hardware and software based on design principles and proposed architecture. This White Paper has been endorsed by the following NGMN Board Members: AT&T, Bell, BT (British multinational Telecommunications services Company), T (Deutsche Telekom), Kpn (Netherland Mobile Telecommunication Company), Kt (Korea Telecom

Company), NTT Docomo (Japan Mobile phone Operator Company), Orange, Singtel, Sk Telecom, TELE2, TELECOM Italia, Telefunica, TELEKOM Austria Group, Teliasorena, Telstar, TELUS, TURKCELL, VimpleCom and Vodafone [6].

According to the NGMN White paper, in its Appendix C, useful guidance regarding target applications is found. Various suggestions relate to energy consumption and power efficiency, and the following subjects could be related to our research [6]:

- 1) New waveforms;

- 2) Advanced multiple access technologies

- 3) Massive MIMO and enhanced multi-antenna schemes;

- 4) Interference coordination;

- 5) Technologies for small packet transmission;

- 6) Densification: Small cells/Ultra-dense networks;

- 7) Dual connectivity-capacity/coverage split system design;

- 8) Device-to-device communication:

- 9) Software-Define-Networking;

- 10) Virtualized mobile core network;

- 11) Virtualized C-RAN;

- 12) Micro-servers;

- 13) Intelligent heterogeneous management;

- 14) Embedded measurement of network performance;

- 15) All optical transport networks with optical router/switch.

From the 15 listed challenges, five topics will be described in more detail in the following paragraphs in order to provide a short explanation and review some possible solutions.

# 2.3.1 Technologies for small packet transmission

There are different schemes for small packet transmission with different Quality of Experience, but the three most important ones are:

1) Periodical keep-alive packets, which are transmitted with minimal non-intrusive content

One of the most important roles of keep-alive packets is verifying the status of the computer

at the remote end of a connection and determine whether it is still alive. Each keep-alive packet can be sent over a connection at every specific time slot called the KeepAliveTime, if there is not another data or higher-level keep-alive packet carried by the connection. When a keep-alive packet is not responded in another specific time slot, the KeepAliveInterval, it will be repeated. For instance, in TCP, an ACK message with sequence number for the connection, which should set to one less than the current sequence number, is a keep-alive packet. When a host receives an ACK, it will respond with another ACK with the current sequence number [34].

#### 2) Bursty Instant Messages

As a comparison between voice and instant messaging, voice is a continuous stream of packets that can tolerate bit errors while instant messaging is bursty and does not tolerate errors, so instant messaging typically causes cycles of abstruseness and repair. Also, since it is asynchronous, short messages are sent in bursty fragments by the sources. For mastering issues that situation needs immediate action, and sources may send requests in parallel in the medium. Increased clarity is a result of using bursty instant messages [35].

#### 3) Real-time critical message delivery

When a failure happens in distributed real-time systems, it is essential to maintain reliable and timely message delivery between nodes. It is needed that the system has the ability to deliver a message within its deadline, so the system has to perform a recovery action. Usually this recovery action implies additional costs to the system, which can be very high. These costs can be very high if the recovery action fails because of lack of time or resources [36].

Because of the features of the above small packet transmission, they can cause network signaling congestion due to frequent RRC (Radio Resource Control) transmission. In addition, the RRC transmission can cause extra delay and consequently can influence the achievable real-time performance of some small packets transmission. Therefore, 5G needs a proper mechanism to support transmitting this kind of packets [6].

Scheduling according to packet type (using, e.g., their priority, time-tag or collision probability) can be one of the proposed solutions. Managing and sharing processing resources between different queues in such a way that each queue behaves as if it has its own resources should be part of this solution (virtualization). It could reduce congestion probability and delay if

scheduling does not cause extra overhead to packets. So, some new scheduling without too much signaling overhead should also be studied, like Periodic scheduling of Keep-Alive packets [6].

The proposed solution can be related to the project due to its ability to reduce power consumption: using proper scheduling can accelerate packet transmission, prevent congestion and retransmission, because in the proposed solution, each kind of small packet requires specific resources, therefore this solution causes significant reduction in the amount of signaling and leads to faster message delivery.

### 2.3.2 Software-Defined-Networking

Software Defined Networking (SDN) is synonymous of a programmable network that has a separate centralized logically abstracted control plane and a flow-based data/forwarding plane. This simplifies the network and makes it more flexible and efficient. Besides, SDN provides Open APIs between the applications and the control plane, and between the control and data planes. Open APIs define functions to support, for example, mobility management of core networks [6].

In addition to separate radio access and radio core networks, SDN utilizes flexible combination and reload of functional building blocks. It means that software-defined content delivery supports distributing those functional building blocks across the network nodes based on needs [37].

Currently, the data/forwarding plane and control planes are mixed together, which increases processing requirements and provide less control, and consequently affects the error correction and re-transmission process, also regarding what is mentioned above and regarding increasing heterogeneous access demands to network, the 5G core network should leverage SDN to increase flexibility and scalability [33].

As OpenFlow-based SDN is the first standard for the SDN body and Wireless and the mobile working group of the Open Networking Foundation is currently working on SDN-based mobile packet core network, utilizing OpenFlow concept and standards in the wireless context could be a solution for this purpose. SDN and control/data plane separation are two of the most important concepts in the virtualization context. At first sight, it may seem that this subject is only weakly related to the project but, in order to leverage WAV, SDN could be a good solution because of its inherent features in terms of virtualization.

#### 2.3.3 Virtualized mobile core network