**Titre:** Exploration d'une méthodologie de développement matériel et logiciel au niveau système appliquée à un système d'encodage de flux vidéo évolutif

Title: Exploration d'une méthodologie de développement matériel et logiciel au niveau système appliquée à un système d'encodage de flux vidéo évolutif

**Auteur:** Etienne Gauthier

Author: Etienne Gauthier

**Date:** 2017

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Gauthier, E. (2017). Exploration d'une méthodologie de développement matériel et logiciel au niveau système appliquée à un système d'encodage de flux vidéo évolutif [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: Gauthier, E. (2017). Exploration d'une méthodologie de développement matériel et logiciel au niveau système appliquée à un système d'encodage de flux vidéo évolutif [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

<https://publications.polymtl.ca/2747/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/2747/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois

Advisors:

**Programme:** Génie informatique

Program:

UNIVERSITÉ DE MONTRÉAL

EXPLORATION D'UNE MÉTHODOLOGIE DE DÉVELOPPEMENT MATÉRIEL ET

LOGICIEL AU NIVEAU SYSTÈME APPLIQUÉ À UN SYSTÈME D'ENCODAGE DE

FLUX VIDÉO ÉVOLUTIF

ETIENNE GAUTHIER

DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

AOÛT 2017

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

EXPLORATION D'UNE MÉTHODOLOGIE DE DÉVELOPPEMENT MATÉRIEL ET

LOGICIEL AU NIVEAU SYSTÈME APPLIQUÉ À UN SYSTÈME D'ENCODAGE DE

FLUX VIDÉO ÉVOLUTIF

présenté par : GAUTHIER Etienne

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

Mme NICOLESCU Gabriela, Doctorat, présidente

M. BOIS Guy, Ph. D., membre et directeur de recherche

M. DAVID Jean Pierre, Ph. D., membre

## DÉDICACE

*À mon père qui est pour moi l'exemple de la persévérance, de la détermination et de

l'intégrité.*

*Tu m'as prouvé qu'on pouvait accomplir de grandes choses lorsqu'on se donnait à fond.

Merci de m'avoir encouragé toutes ces années... .*

## REMERCIEMENTS

J'aimerais tout d'abord remercier mon directeur de recherche, le professeur Guy Bois, qui m'a guidé durant ce projet. Votre support et vos conseils m'ont été d'une grande aide pour bien orienter ma recherche.

J'aimerais aussi remercier mes collègues de laboratoire Mathieu Goudron et Arnaud Desaulty d'avoir rendu chaque journée plus intéressante et enrichissante au laboratoire.

Finalement, je tiens à remercier l'équipe de SpaceCodesign plus particulièrement Hubert Guérard et Fellipe Monteiro qui m'ont offert un excellent support pour l'application SpaceStudio.

## RÉSUMÉ

La compagnie Grass Valley, fabricant de cartes de traitement vidéo, désire mettre à jour leur sous-système « thumbnail » qui produit des vidéos à échelle réduite à des fins de diagnostic. Afin de le moderniser, ils ont arrêté leur choix sur une implémentation d'un « proxy » vidéo produisant un flux vidéo compressé avec la norme H.264. Afin d'épargner en coût de développement et assurer son indépendance au cycle de vie des composantes tierces, Grass Valley est à la recherche d'une implémentation évolutive et indépendante d'une plateforme. Afin de résoudre ce problème, Grass Valley a fait appel à Polytechnique.

Le développement d'un encodeur H.264 pour système sur puce personnalisé peut nécessiter plusieurs mois à plusieurs années de développement pour une équipe d'ingénierie. Il existe actuellement peu de solutions possibles pour concevoir un tel sous-système rapidement. Afin de développer le sous-système d'encodage H.264 rapidement, nous avons opté pour une méthodologie de développement à l'aide de l'approche du point de vue du système basée sur une spécification exécutable d'un encodeur H.264 en utilisant l'outil SpaceStudio.

SpaceStudio est un logiciel permettant l'exploration architecturale à l'aide de plateforme virtuelle configurable. La conception de système à l'aide de cet outil se fait par une approche modulaire sous SystemC. Le système est séparé en module logiciel et matériel fonctionnel et ceux-ci sont développés itérativement. L'utilisation d'un code applicatif comme base afin d'en produire un système embarqué sous SpaceStudio n'a pas été expérimentée. Dans cette optique, ce travail à deux objectifs : 1) développer un système pouvant encoder un flux vidéo et 2) expérimenter avec une approche de développement du point de vue du système à l'aide d'une spécification exécutable sous SpaceStudio. Il est donc question de développer la méthodologie et le projet en parallèle.

Au terme de ce projet, nous aurons implanté un système d'encodage H.264 sur une plateforme virtuel et défini la méthodologie nécessaire afin de produire un système sur puce à l'aide d'une référence logicielle. Cette recherche nous a permis de découvrir les obstacles à la conception de système complexe à l'aide de code C/C++ existant sous SpaceStudio et de développer les bases nécessaires pour rendre la totalité de la méthodologie réalisable dans le futur.

## ABSTRACT

GrassValley, a manufacturer of video processing cards, wants to upgrade their thumbnail subsystem which produces scaled-down videos for diagnostic purposes. In order to modernize this subsystem, they have decided to go with a video proxy producing a video stream compressed with the H.264 standard. In order to save development costs and ensure its independence of third-party components, Grass Valley is looking for a scalable platform-independent implementation. To solve this problem, they called upon Polytechnique.

The development of an H.264 encoder for custom system-on-a-chip may take several months to several years of development for an engineering team. There are currently very few possible solutions to design such a subsystem quickly. In order to do so, we opted for a development methodology using the system-level approach based on an executable specification of an H.264 encoder using SpaceStudio.

SpaceStudio is a computer aided design software for architectural exploration using a configurable virtual platform. Designing a system with this tool is done through a modular approach using the SystemC library. The designed system is separated into functional software / hardware modules developed iteratively. The use of a software application as a basis to produce a system under SpaceStudio has not been yet tested. This work has two objectives: 1) to develop a system capable of encoding a video stream and 2) to experiment with a system level development approach using a executable specification under SpaceStudio. It is therefore a question of developing the methodology and the encoder in parallel.

At the end of this project, we will have implemented a H.264 encoding system on a virtual platform and defined the methodology needed to produce a full system on chip using a software reference as a basis for development. This research allowed us to discover the obstacles associated to the design of a complex systems using C "legacy" code under SpaceStudio and to develop the necessary tools to make the whole methodology achievable in the future.

## TABLE DES MATIÈRES

|                                                            |      |

|------------------------------------------------------------|------|

| DÉDICACE . . . . .                                         | iii  |

| REMERCIEMENTS . . . . .                                    | iv   |

| RÉSUMÉ . . . . .                                           | v    |

| ABSTRACT . . . . .                                         | vi   |

| TABLE DES MATIÈRES . . . . .                               | vii  |

| LISTE DES TABLEAUX . . . . .                               | x    |

| LISTE DES FIGURES . . . . .                                | xi   |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                 | xiii |

| LISTE DES ANNEXES . . . . .                                | xiv  |

| <br>CHAPITRE 1 INTRODUCTION . . . . .                      | 1    |

| 1.1 Éléments de la problématique . . . . .                 | 2    |

| 1.1.1 Problématique principale . . . . .                   | 2    |

| 1.1.2 Problématique explorée dans ce mémoire . . . . .     | 4    |

| 1.2 Objectifs de recherche . . . . .                       | 4    |

| 1.3 Résumé des contributions . . . . .                     | 5    |

| 1.4 Plan du mémoire . . . . .                              | 5    |

| <br>CHAPITRE 2 REVUE DE LITTÉRATURE . . . . .              | 6    |

| 2.1 Le codesign . . . . .                                  | 6    |

| 2.2 Méthodologie ESL . . . . .                             | 8    |

| 2.2.1 Modélisation . . . . .                               | 8    |

| 2.2.2 Plateforme Virtuelle . . . . .                       | 12   |

| 2.2.3 HLS . . . . .                                        | 13   |

| 2.3 Logiciels de développement au niveau système . . . . . | 14   |

| 2.3.1 SpaceStudio . . . . .                                | 16   |

| 2.4 Standard H.264 . . . . .                               | 19   |

| 2.4.1 Division de l'image . . . . .                        | 20   |

|                                                                     |                                                                                |    |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------|----|

| 2.4.2                                                               | Prédiction . . . . .                                                           | 21 |

| 2.4.3                                                               | Transformée . . . . .                                                          | 25 |

| 2.4.4                                                               | Quantification . . . . .                                                       | 25 |

| 2.4.5                                                               | Codage entropique . . . . .                                                    | 26 |

| 2.4.6                                                               | Network Abstraction Layer (NAL) . . . . .                                      | 26 |

| 2.4.7                                                               | Profils . . . . .                                                              | 27 |

| 2.5                                                                 | Implémentations matérielles de la norme H.264 . . . . .                        | 28 |

| <b>CHAPITRE 3 MÉTHODOLOGIE DE DÉVELOPPEMENT À L'AIDE D'UN MODEL</b> |                                                                                |    |

| <b>SYSTÈME EXÉCUTABLE . . . . .</b>                                 |                                                                                | 29 |

| 3.1                                                                 | Besoin de Grass Valley . . . . .                                               | 29 |

| 3.2                                                                 | Approche initiale . . . . .                                                    | 31 |

| 3.3                                                                 | Développement niveau système à partir d'une spécification exécutable . . . . . | 32 |

| 3.4                                                                 | Méthodologie de développement expérimentale à l'aide de SpaceStudio . . . . .  | 32 |

| 3.4.1                                                               | Création du modèle fonctionnel . . . . .                                       | 34 |

| 3.4.2                                                               | Migration de l'application vers SpaceStudio : Modèle fonctionnel . . . . .     | 39 |

| 3.4.3                                                               | Migration de l'application vers SpaceStudio : Modèle de simulation . . . . .   | 39 |

| 3.4.4                                                               | Implémentation du processus de validation . . . . .                            | 41 |

| 3.4.5                                                               | Profilage . . . . .                                                            | 43 |

| 3.4.6                                                               | Déterminer les sections pertinentes . . . . .                                  | 46 |

| 3.4.7                                                               | Modularisation des zones chaudes du code . . . . .                             | 54 |

| 3.4.8                                                               | Suppression des pointeurs de fonctions . . . . .                               | 56 |

| 3.4.9                                                               | Abstraction mémoire . . . . .                                                  | 59 |

| 3.4.10                                                              | Migration des modules d'estimation du mouvement . . . . .                      | 64 |

| 3.4.11                                                              | Insertion des modules au flot de traitement . . . . .                          | 73 |

| 3.5                                                                 | Architecture finales du système . . . . .                                      | 75 |

| <b>CHAPITRE 4 RÉSULTATS THÉORIQUES ET EXPÉRIMENTAUX . . . . .</b>   |                                                                                | 77 |

| 4.1                                                                 | Plateformes . . . . .                                                          | 77 |

| 4.2                                                                 | Résultats . . . . .                                                            | 77 |

| 4.3                                                                 | Discussion . . . . .                                                           | 79 |

| 4.4                                                                 | Limitations de la solution proposée . . . . .                                  | 81 |

| 4.4.1                                                               | Système H.264 . . . . .                                                        | 81 |

| 4.4.2                                                               | Méthodologie . . . . .                                                         | 83 |

| 4.5                                                                 | Réflexion sur l'automatisation du processus . . . . .                          | 86 |

| <b>CHAPITRE 5 AMÉLIORATION DU PROCESSUS . . . . .</b>               |                                                                                | 88 |

|                                 |                                   |     |

|---------------------------------|-----------------------------------|-----|

| 5.1                             | Profilage . . . . .               | 88  |

| 5.2                             | Flot de données . . . . .         | 89  |

| 5.2.1                           | Adressage mémoire . . . . .       | 90  |

| 5.2.2                           | Analyse statique . . . . .        | 91  |

| 5.2.3                           | Analyse dynamique (PIN) . . . . . | 93  |

| 5.2.4                           | Transformation . . . . .          | 99  |

| CHAPITRE 6 CONCLUSION . . . . . |                                   | 101 |

| 6.1                             | Synthèse des travaux . . . . .    | 101 |

| 6.2                             | Améliorations futures . . . . .   | 102 |

| 6.2.1                           | Système H.264 . . . . .           | 102 |

| 6.3                             | Méthodologie projeté . . . . .    | 105 |

| RÉFÉRENCES . . . . .            |                                   | 107 |

| ANNEXES . . . . .               |                                   | 111 |

**LISTE DES TABLEAUX**

|             |                                                                         |    |

|-------------|-------------------------------------------------------------------------|----|

| Tableau 3.1 | Paramètre d'encodage du «proxy» . . . . .                               | 36 |

| Tableau 3.2 | Pourcentage d'utilisation du temps processeur selon Pareon . . . . .    | 45 |

| Tableau 3.3 | Analyse des temps de communication pour une trame . . . . .             | 52 |

| Tableau 3.4 | Analyse des temps de communication pour un macrobloc . . . . .          | 53 |

| Tableau 3.5 | Flot de haut niveau du traitement d'un macrobloc . . . . .              | 56 |

| Tableau 4.1 | Encodage d'une vidéo ayant des scènes statique et de couleur uniforme   | 78 |

| Tableau 4.2 | Encodage d'une vidéo ayant des scènes dynamiques et de couleur uniforme | 78 |

| Tableau 4.3 | Encodage d'une vidéo ayant des scènes dynamiques et de couleur variées  | 79 |

## LISTE DES FIGURES

|             |                                                                                                                                        |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1  | Espace de solution matériel/logiciel . . . . .                                                                                         | 7  |

| Figure 2.2  | Architecture de la librairie SystemC . . . . .                                                                                         | 9  |

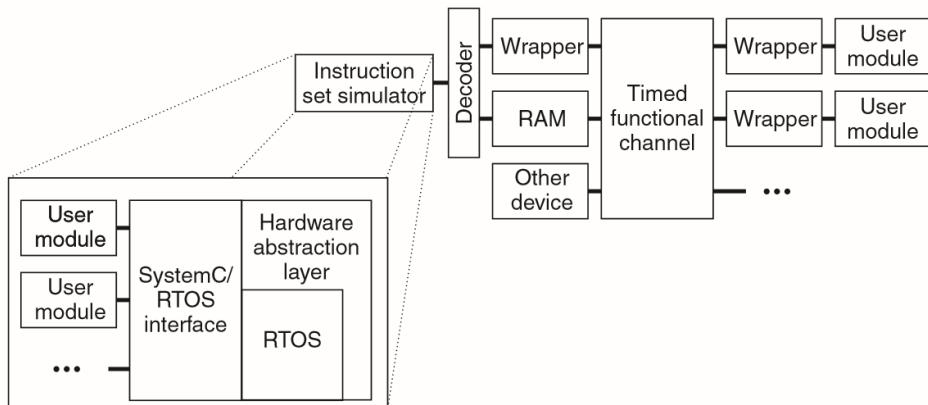

| Figure 2.3  | Modèle TLM [13] . . . . .                                                                                                              | 11 |

| Figure 2.4  | Vitesse de simulation en fonction de l'abstraction [41] . . . . .                                                                      | 12 |

| Figure 2.5  | SpaceStudio RTOS sur ISS SystemC [15] . . . . .                                                                                        | 17 |

| Figure 2.6  | Flot de la plateforme SpaceStudio . . . . .                                                                                            | 18 |

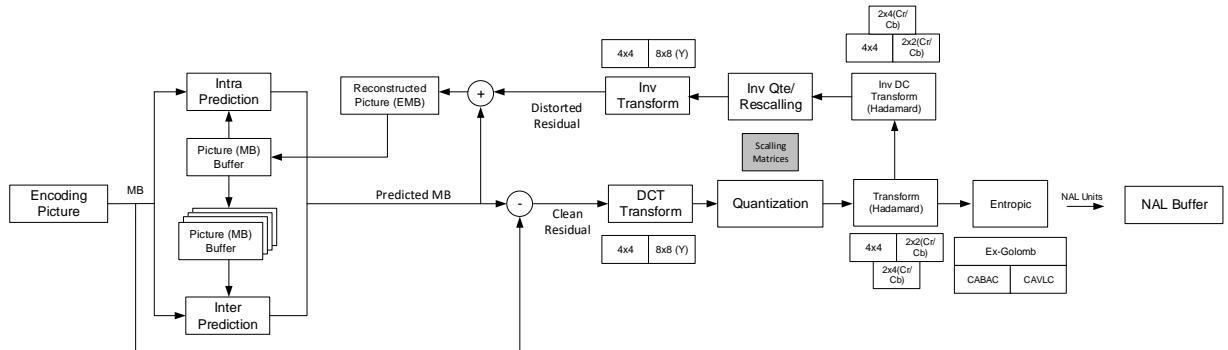

| Figure 2.7  | Schéma fonctionnel des étapes d'encodage et de décodage afin de traiter une trame . . . . .                                            | 19 |

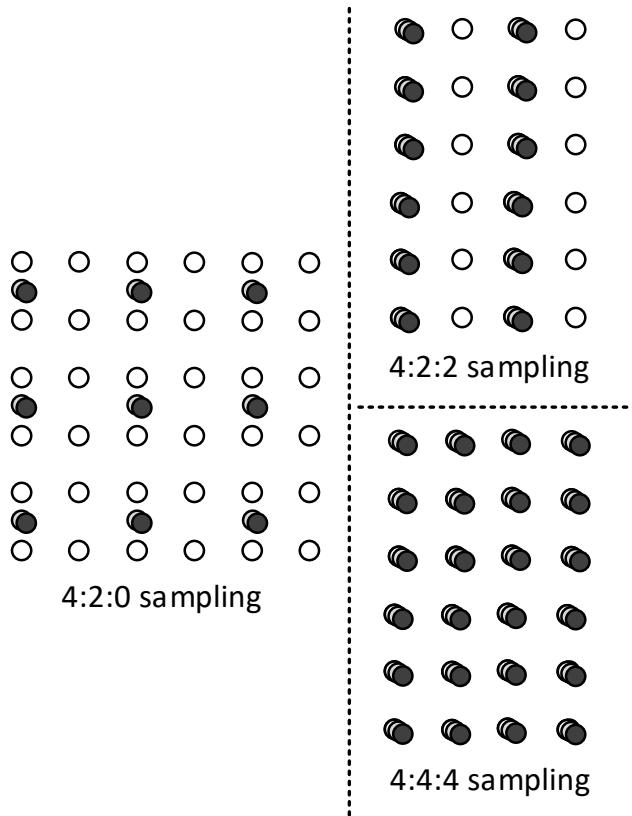

| Figure 2.8  | Échantillonnage supporté par la norme H.264 [39] . . . . .                                                                             | 20 |

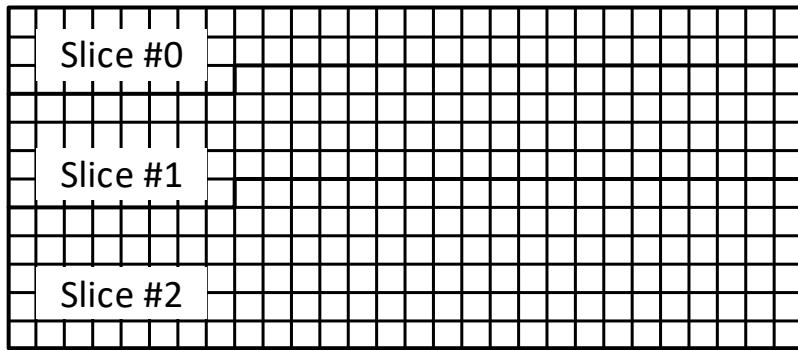

| Figure 2.9  | Séparation de l'image en slices et macroblocs [50] . . . . .                                                                           | 21 |

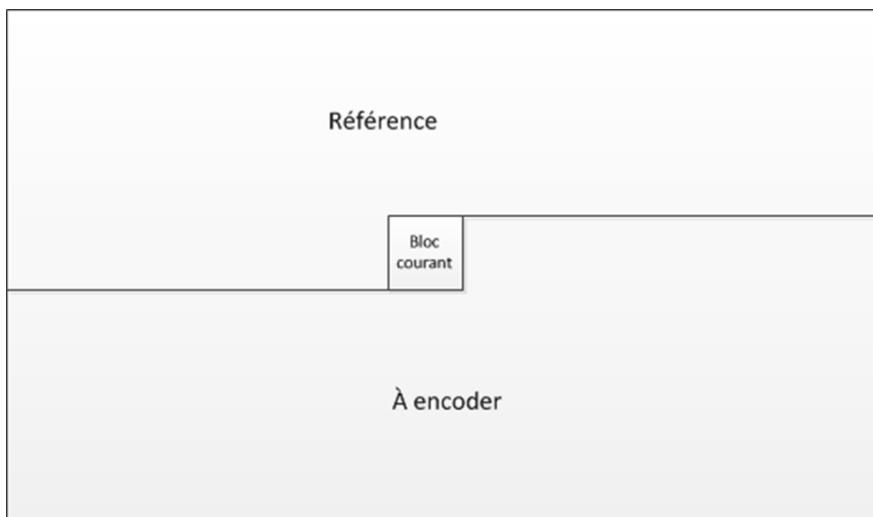

| Figure 2.10 | Partage des macroblocs de référence lors du processus de prédition spatial . . . . .                                                   | 22 |

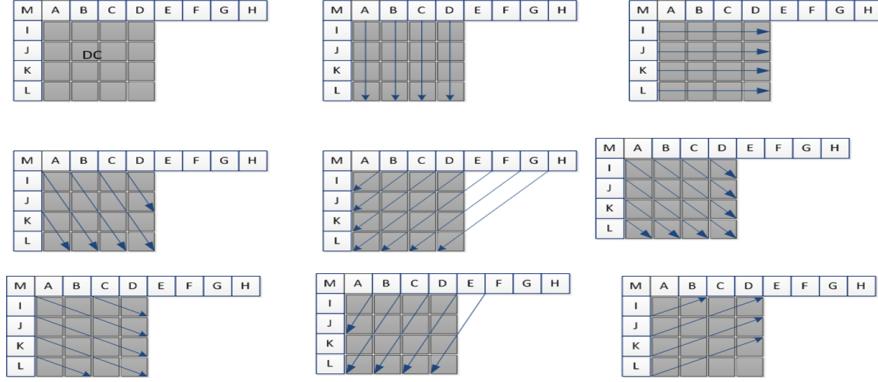

| Figure 2.11 | Méthodes d'interpolation spatiale possible sous la norme H.264 . . . . .                                                               | 23 |

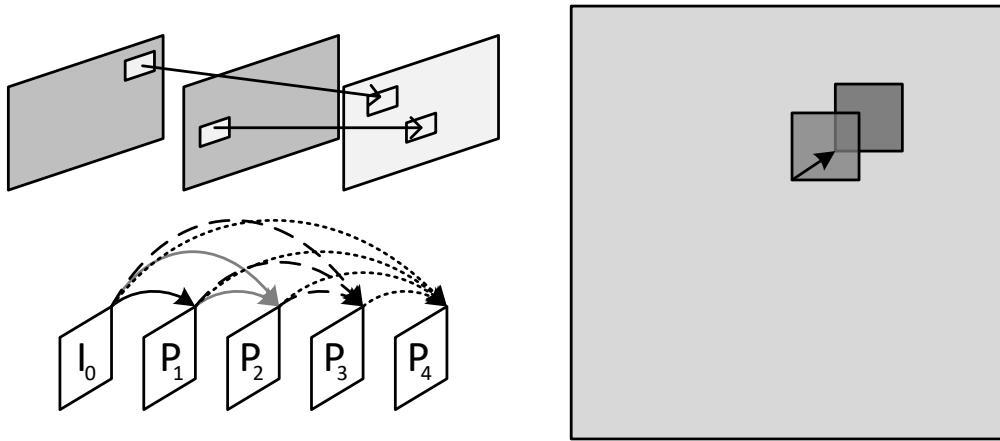

| Figure 2.12 | Prédiction temporelle et vecteur de déplacement [39] . . . . .                                                                         | 24 |

| Figure 2.13 | Prédiction au sous pixel [39] . . . . .                                                                                                | 24 |

| Figure 2.14 | Encapsulation des données produite par un encodeur . . . . .                                                                           | 27 |

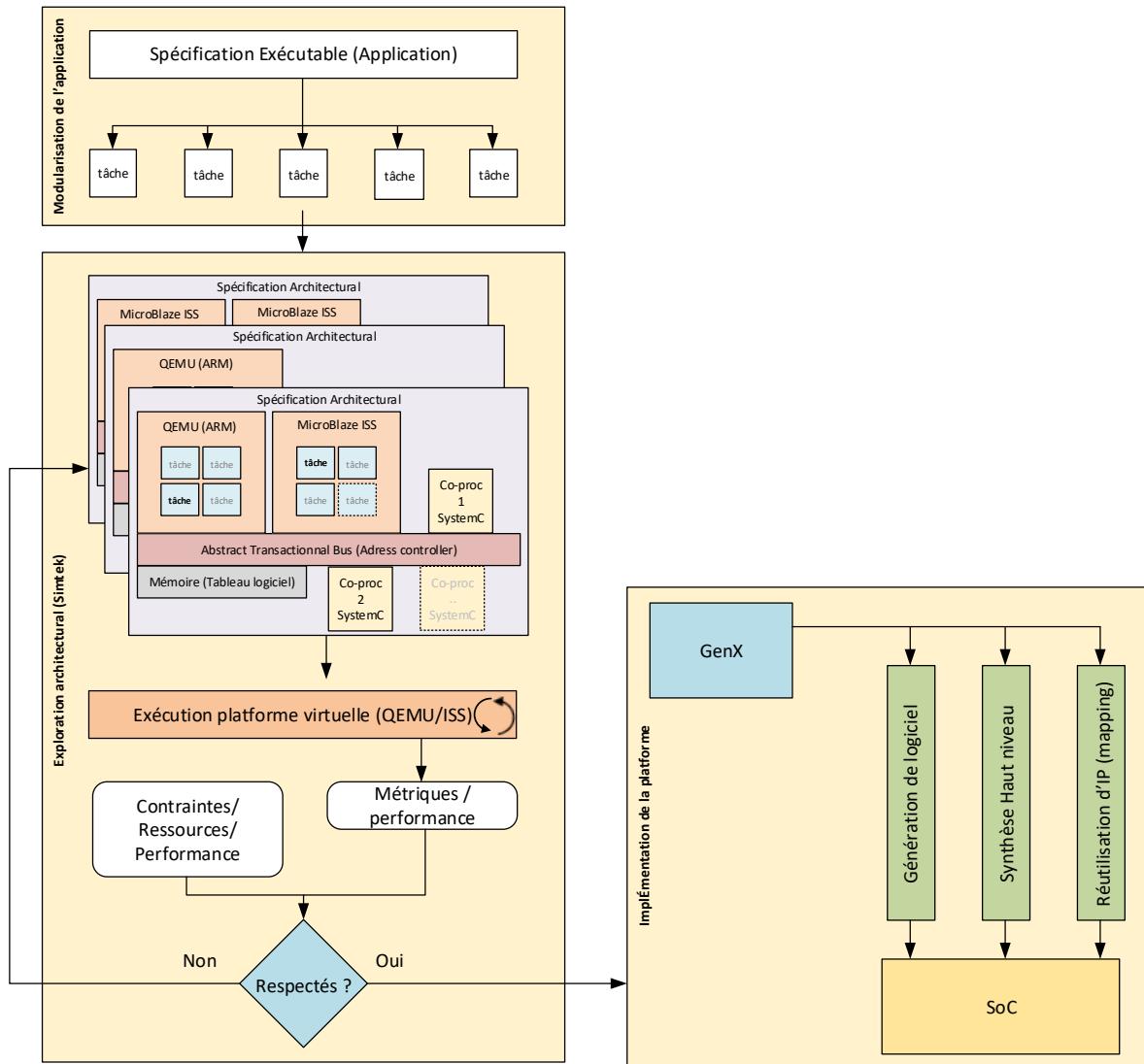

| Figure 3.1  | Graphique (a) représente le flot standard, Graphique (b) représente le flot ESL à l'aide d'une spécification exécutable [43] . . . . . | 33 |

| Figure 3.2  | Flot de modularisation expérimental . . . . .                                                                                          | 34 |

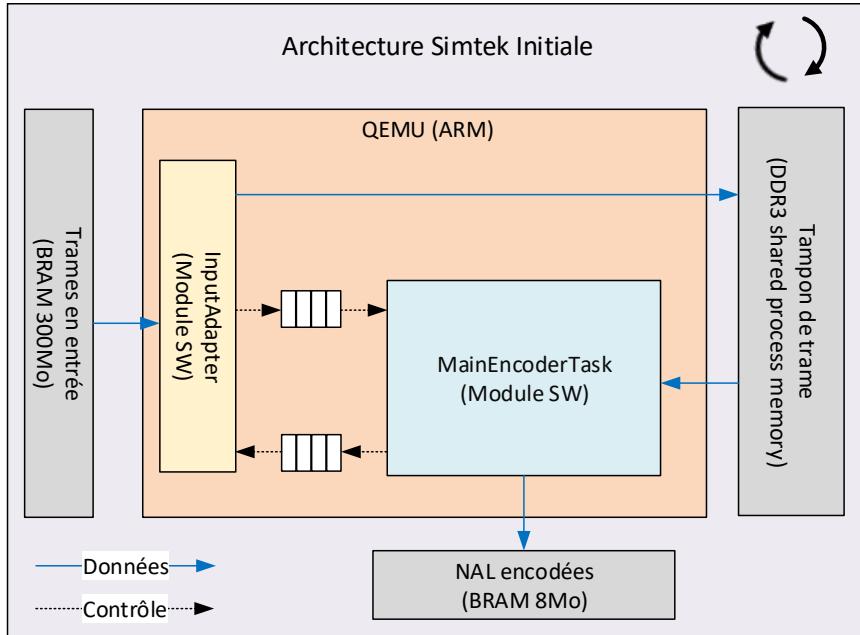

| Figure 3.3  | Architecture Simtek initiale . . . . .                                                                                                 | 41 |

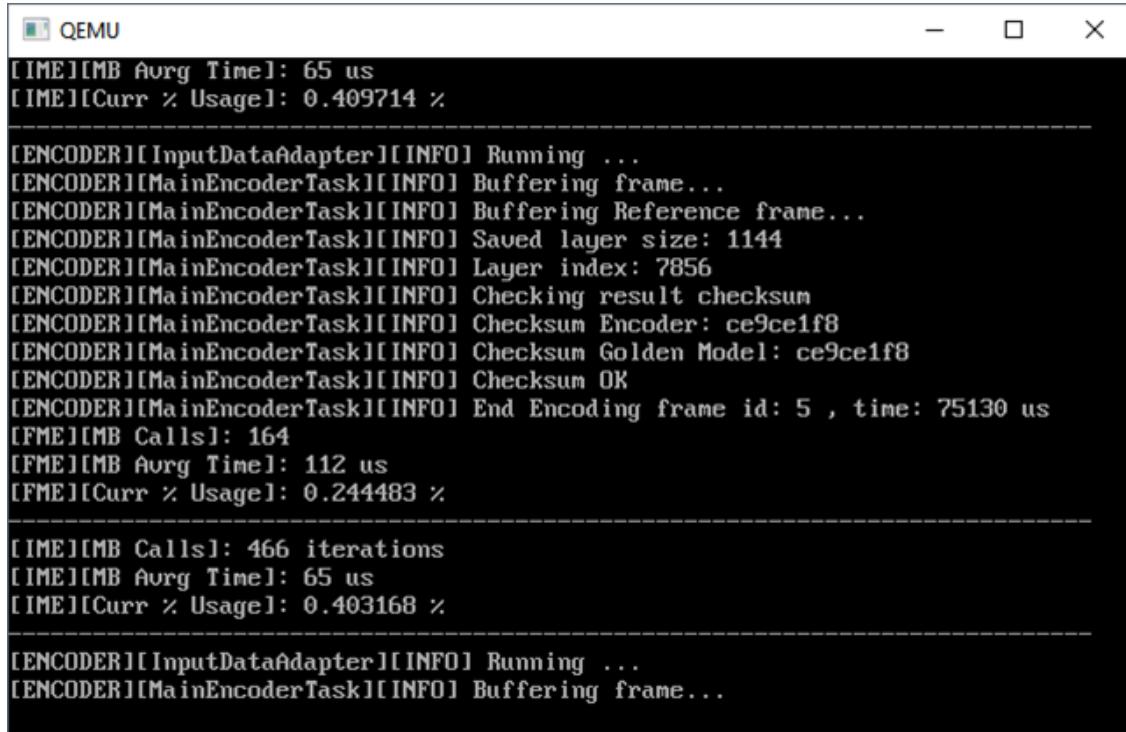

| Figure 3.4  | Exécution de l'encodeur et de la suite de tests sur la plateforme virtuelle de SpaceStudio . . . . .                                   | 43 |

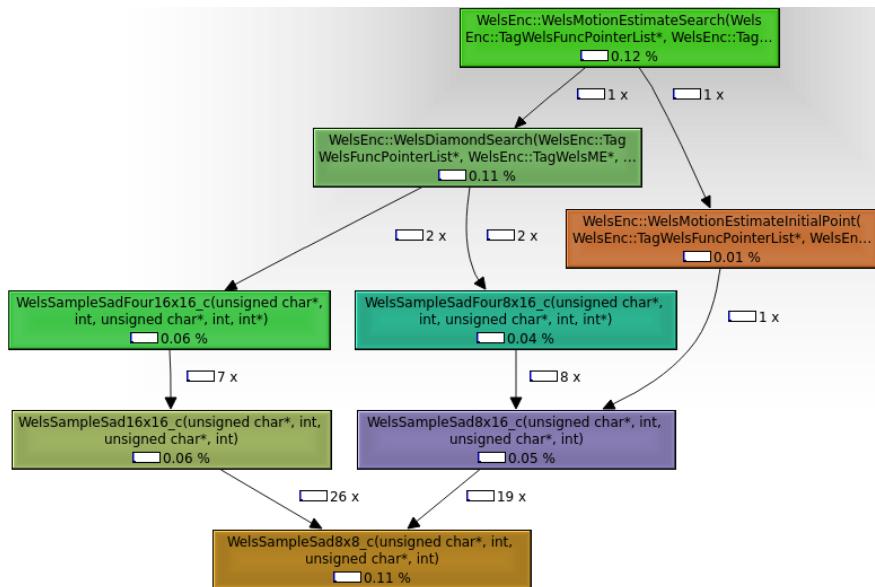

| Figure 3.5  | Pourcentage d'utilisation du temps processeur des fonctions principales selon Valgrind . . . . .                                       | 46 |

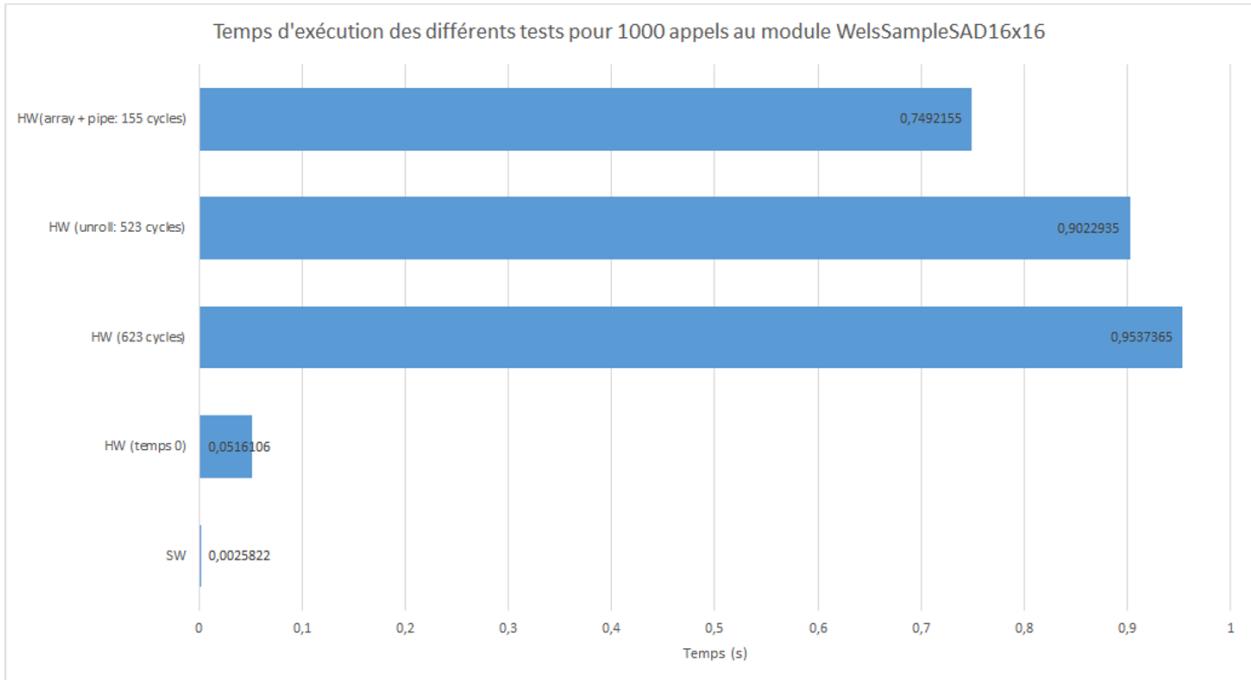

| Figure 3.6  | Temps d'exécution des différents tests en fonction des optimisations pour 1000 appels au module WelsSampleSad16x16 . . . . .           | 47 |

| Figure 3.7  | Graphe d'appels de la fonction welsMotionEstimateSearch() pour le traitement d'un macrobloc . . . . .                                  | 48 |

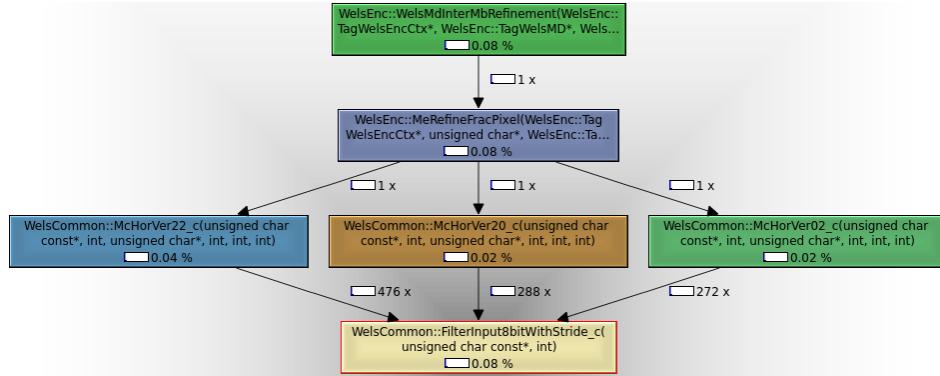

| Figure 3.8  | Graphe d'appel de la fonction welsMdInterMbRefinement() centré sur les filtres pour le traitement d'un macrobloc . . . . .             | 49 |

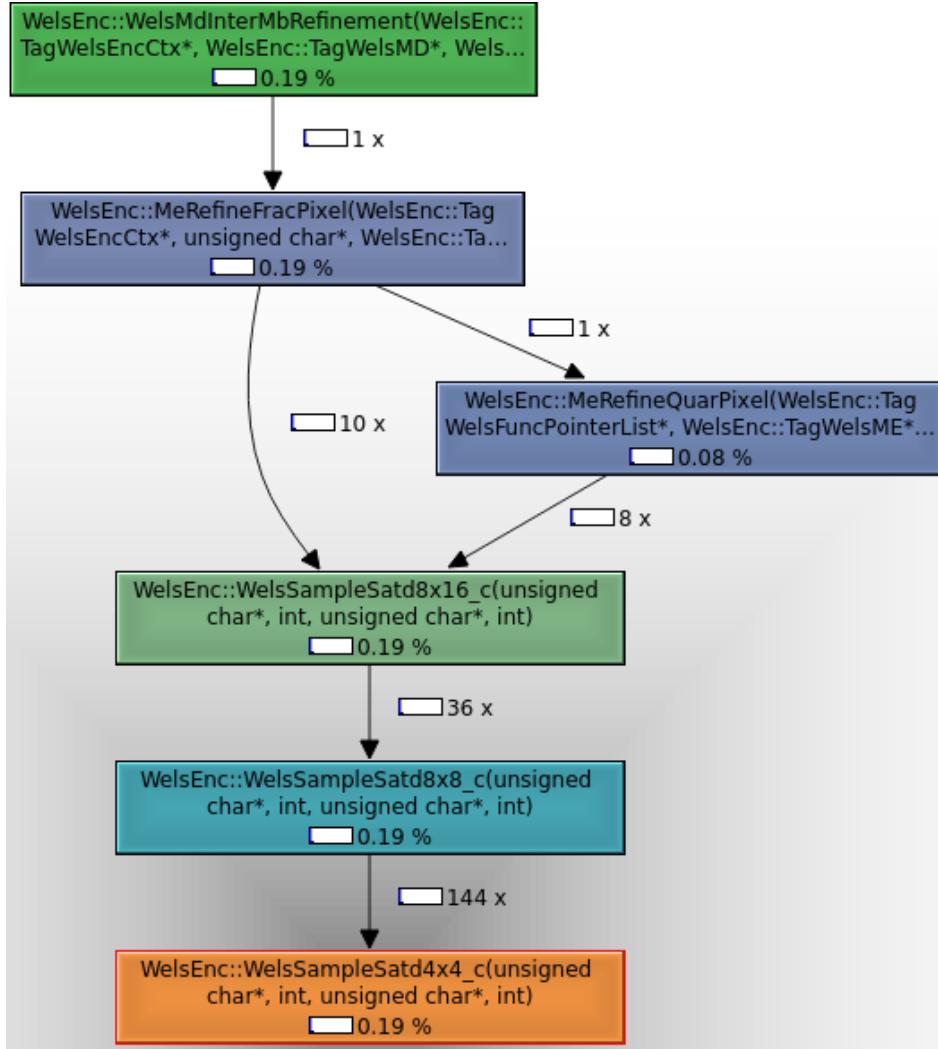

| Figure 3.9  | Graphe d'appel de la fonction welsMdInterMbRefinement() centré sur les SAD pour le traitement d'un macrobloc . . . . .                 | 50 |

|             |                                                                                                                                                                                             |     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.10 | Liste des fonctions appelées à travers le pointeur pSad de la fonction WelsDiamondSearch()                                                                                                  | 57  |

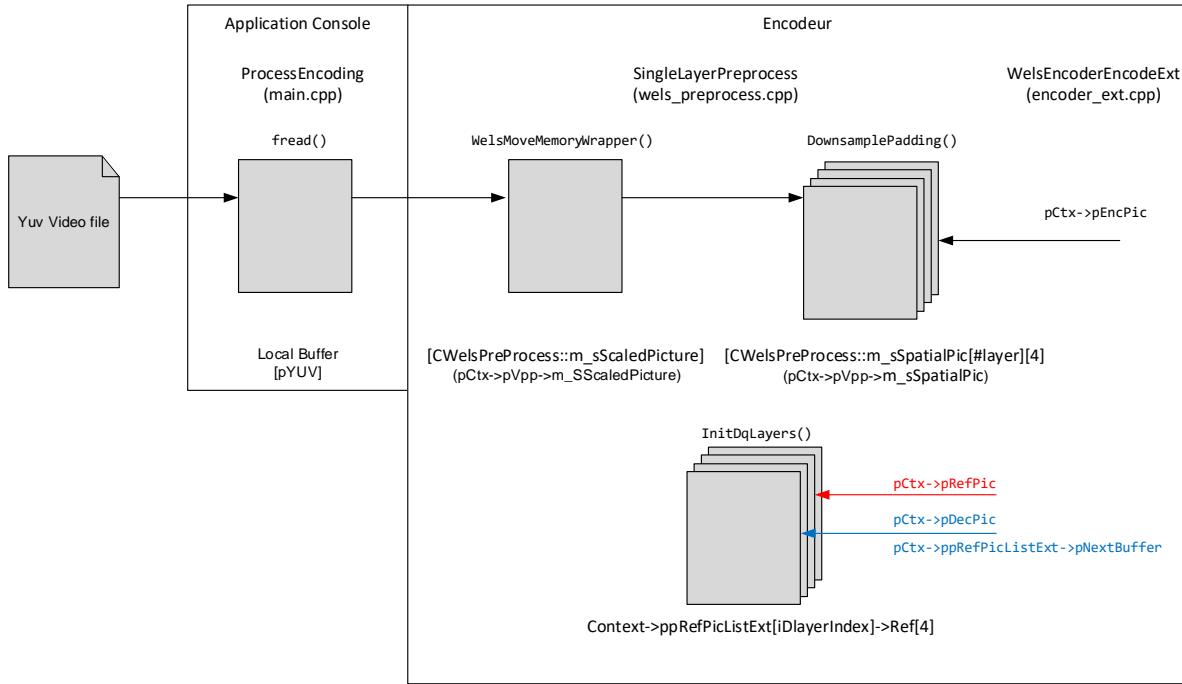

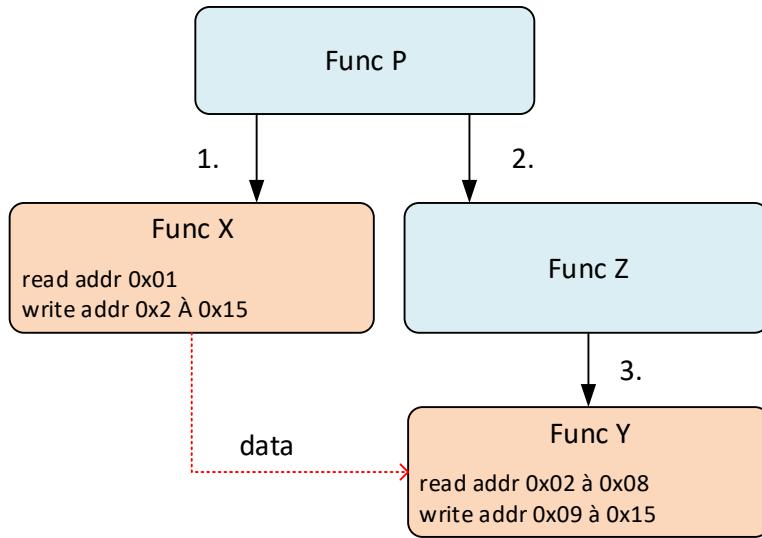

| Figure 3.11 | Flot d'entrée des images et pointeurs vers les tampons de l'encodeur .                                                                                                                      | 60  |

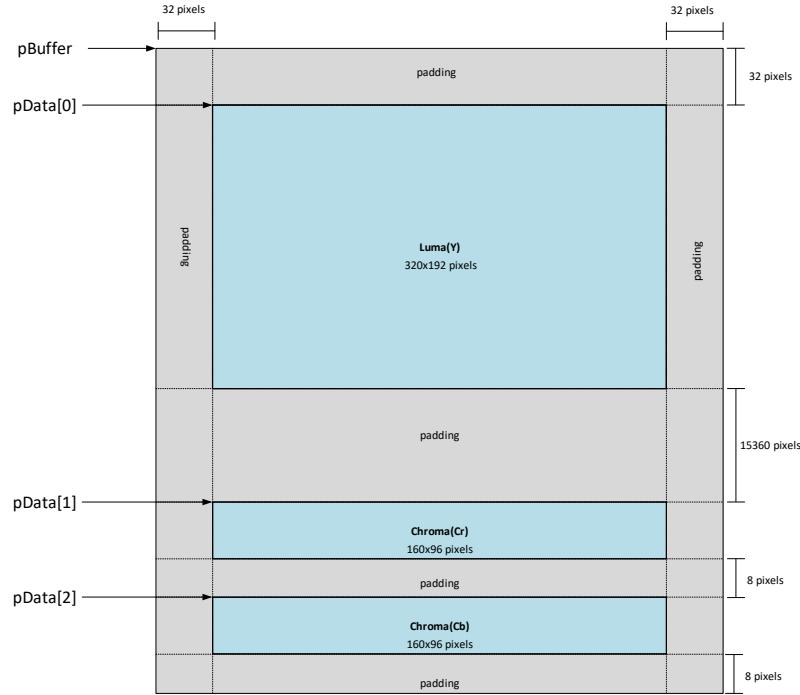

| Figure 3.12 | Disposition d'une trame YUV en mémoire par la structure <i>SPicture</i> d'OpenH264 . . . . .                                                                                                | 62  |

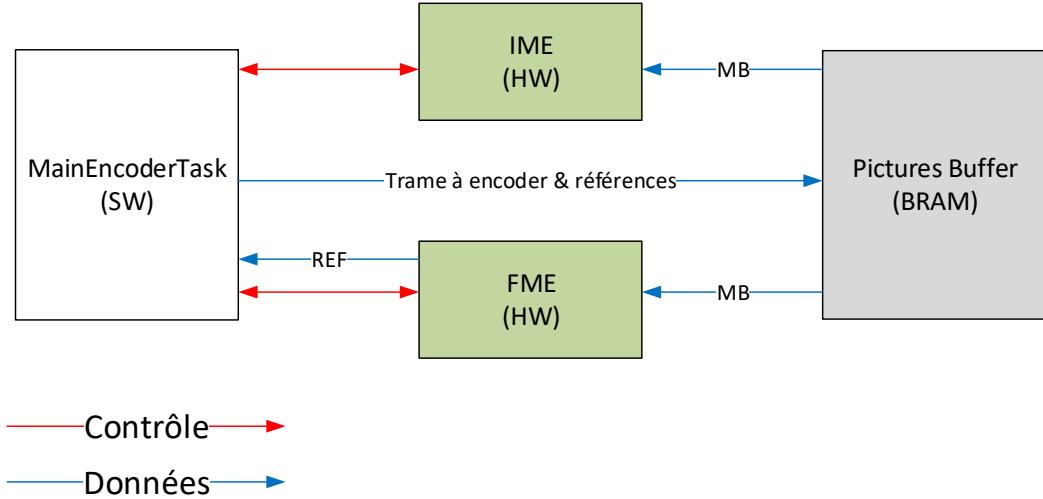

| Figure 3.13 | Schéma bloc de l'architecture mémoire . . . . .                                                                                                                                             | 64  |

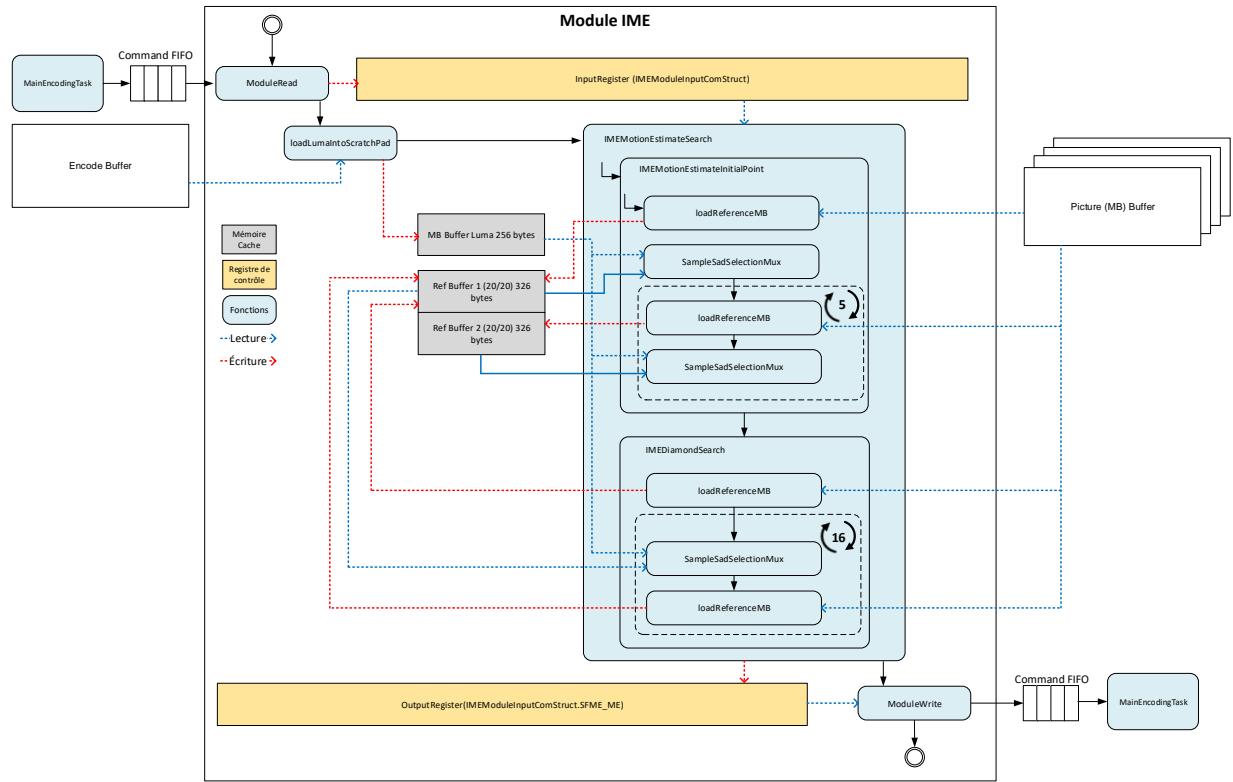

| Figure 3.14 | Schéma des opérations mémoire du module IME . . . . .                                                                                                                                       | 66  |

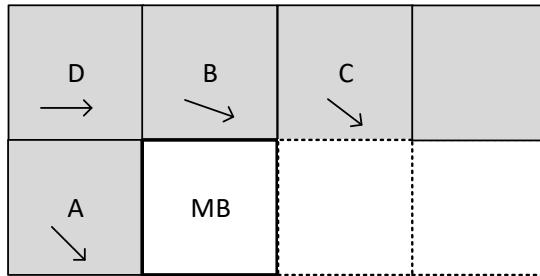

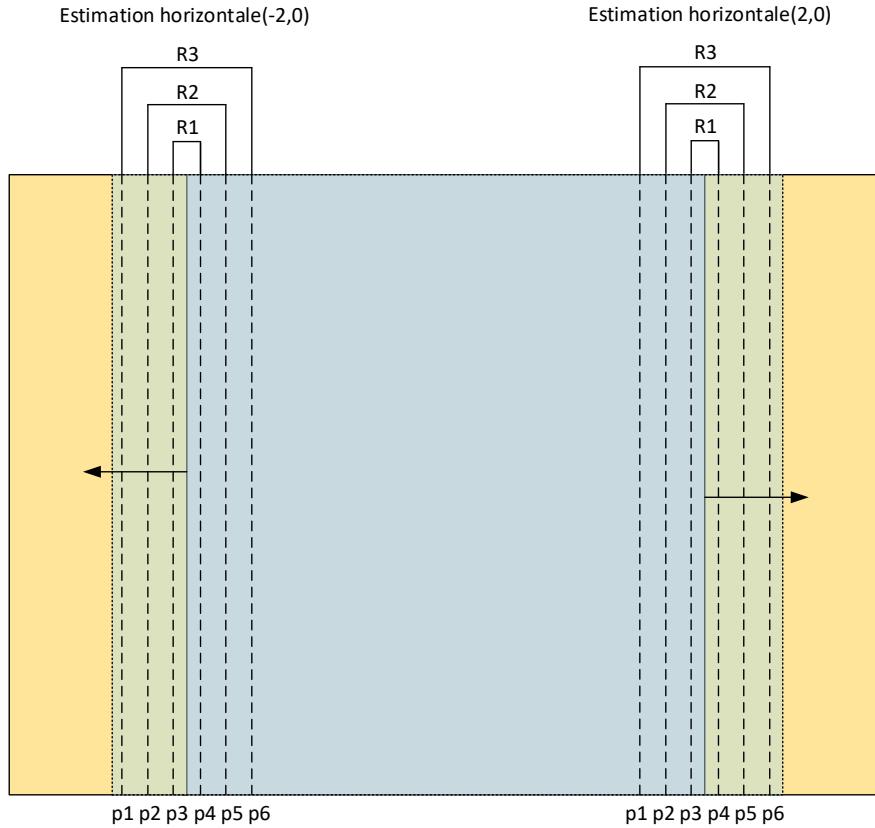

| Figure 3.15 | Vecteurs de mouvements dans le voisinage du macrobloc à encoder .                                                                                                                           | 67  |

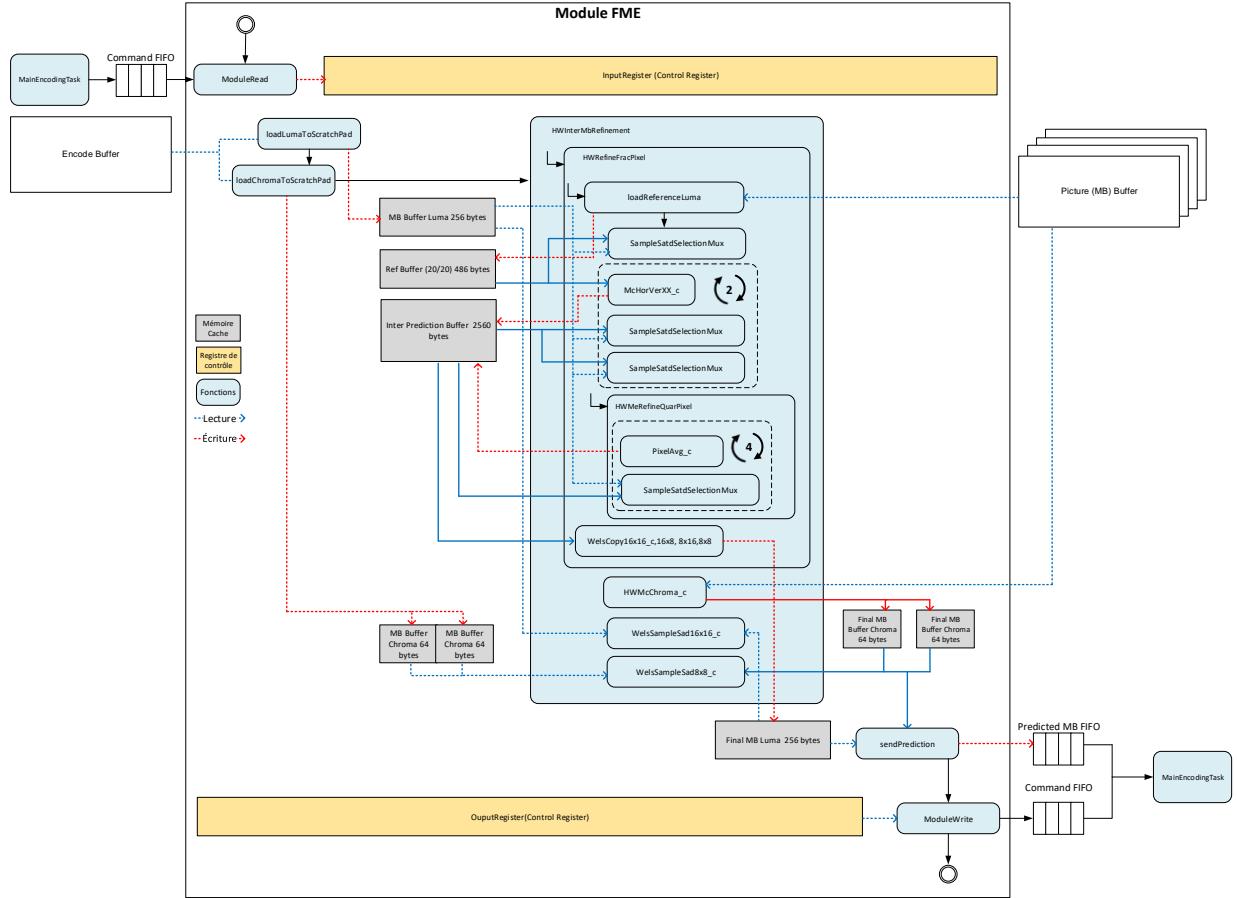

| Figure 3.16 | Schéma des opérations mémoires du module FME . . . . .                                                                                                                                      | 70  |

| Figure 3.17 | Exemple d'interpolation au demi-pixel pour les déplacements gauche et droite en bordure du macrobloc. Le même algorithme est utilisé pour les déplacements vers le haut et le bas . . . . . | 72  |

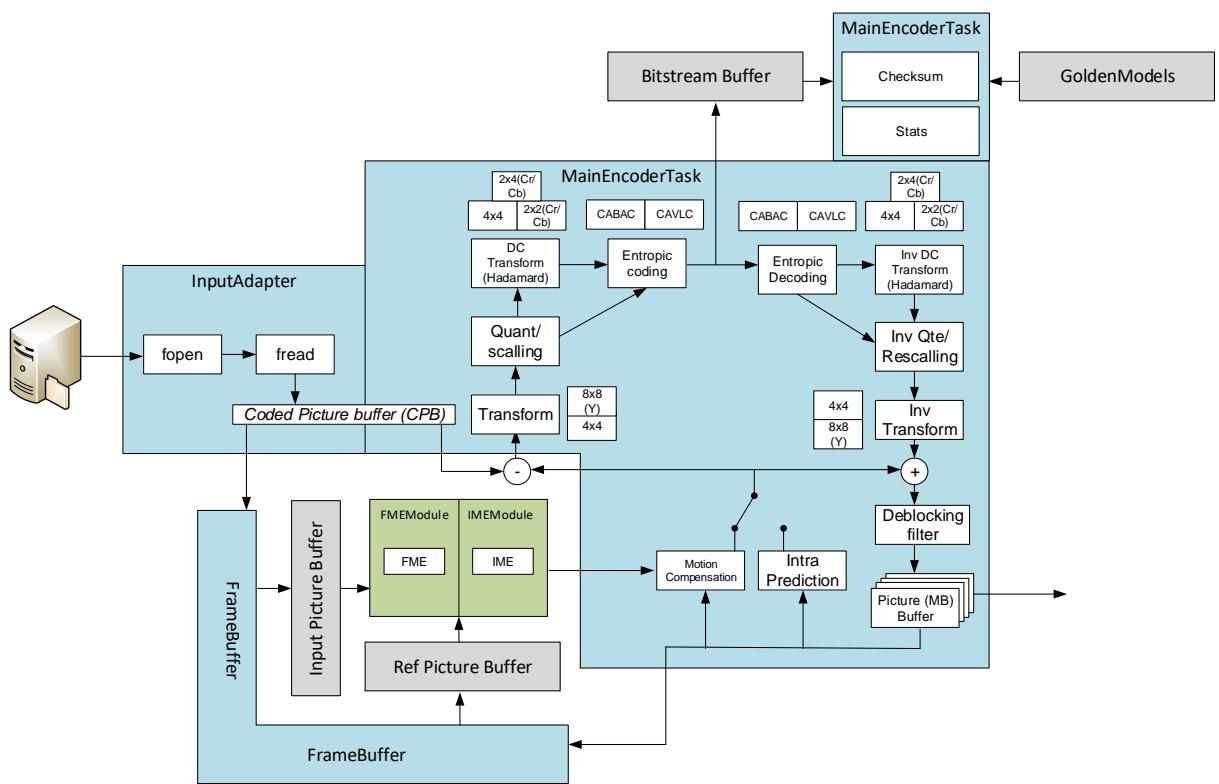

| Figure 3.18 | Architecture finale du système . . . . .                                                                                                                                                    | 76  |

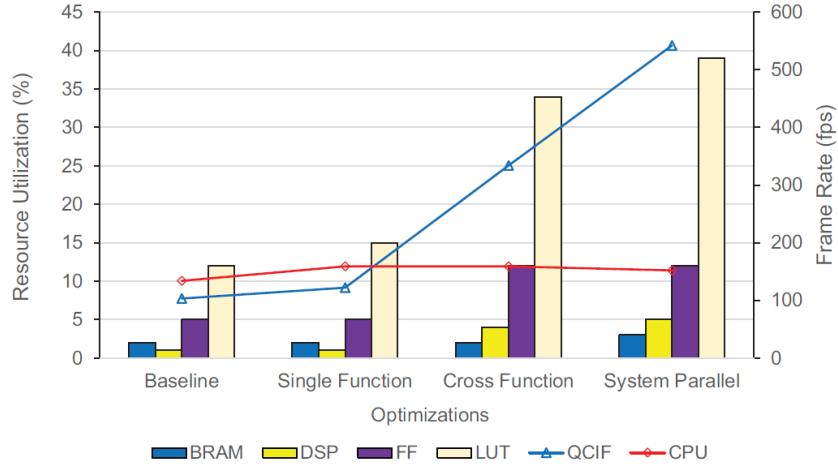

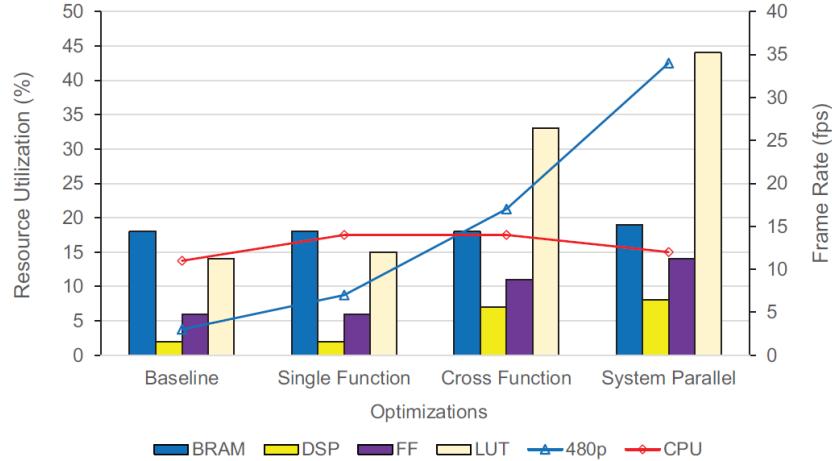

| Figure 4.1  | Article[26], décodage des trames de résolution QCIF (176x144) . . . .                                                                                                                       | 81  |

| Figure 4.2  | Article[26], décodage des trames de résolution 640x480 . . . . .                                                                                                                            | 82  |

| Figure 5.1  | Liens mémoires rendus explicites par l'analyse dynamique . . . . .                                                                                                                          | 99  |

| Figure 6.1  | Architecture incorporant le nouveau flot de données . . . . .                                                                                                                               | 104 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|       |                                              |

|-------|----------------------------------------------|

| ACP   | Accelerator Coherency Port                   |

| AVC   | Advanced Video Coding                        |

| CABAC | Context Adaptive Binary Arithmetic Coding    |

| CAPI  | Coherent Accelerator Processor Interface     |

| CAVLC | Context Adaptive Variable Length Coding      |

| EDA   | Electronic Design Automation                 |

| ESL   | Electronic System-level                      |

| FME   | Fractionnal motion estimation                |

| FPGA  | Field-Programmable Gate Array                |

| HLS   | High level synthesis                         |

| IDR   | instantaneous decoding refresh               |

| IME   | Integral motion estimation                   |

| ISS   | Instruction Set Simulator                    |

| ITU   | International Telegraph Union                |

| ITU-T | ITU Telecommunication Standardization Sector |

| JVT   | Joint Video Team                             |

| MPEG  | Moving Picture Experts Group                 |

| PPS   | picture parameter sets                       |

| RBSP  | Raw byte sequence payload                    |

| RTL   | Register transfert level                     |

| SoC   | System on Chip                               |

| SPS   | sequence parameter sets                      |

| TLM   | Transaction level modeling                   |

| UMA   | Unified Memory Architecture                  |

**LISTE DES ANNEXES**

|          |                                                                                  |     |

|----------|----------------------------------------------------------------------------------|-----|

| Annexe A | PARAMÈTRES DE L'ENCODEUR . . . . .                                               | 111 |

| Annexe B | PROTOTYPE DÉVELOPPÉ DE L'OUTIL PIN . . . . .                                     | 115 |

| Annexe C | PROBLÈMES RENCONTRÉS LORS DE LA MIGRATION INITIALE<br>VERS SPACESTUDIO . . . . . | 121 |

## CHAPITRE 1 INTRODUCTION

La compagnie Grass Valley conçoit un grand nombre de systèmes de traitement vidéo. Inclus avec ces systèmes de traitement vidéo se trouve un sous-système qui produit des vidéos de type « thumbnail ». Ceux-ci consistent en l'acquisition de petites images instantanées prises dans le traitement principal d'un flot vidéo. Ces images sont donc des versions à échelle réduite des images originales et sont utilisés pour surveiller, assurer la qualité ainsi que le bon fonctionnement d'une production télévisuelle. La compagnie Grass Valley est en processus de modernisation de sa gamme de produits et aimerait améliorer les fonctionnalités de ce sous-système tout en respectant diverses contraintes associées à la consommation de puissance et au coût de production. De plus, elle aimerait migrer vers un système offrant des images suivant un standard plus moderne, laissant de côté l'approche basse qualité actuellement offerte.

Il existe actuellement deux solutions possibles pour concevoir un sous-système pour la création de séquence vidéo dit « thumbnail ». La première consiste en l'utilisation seulement d'un processeur bas de gamme, par exemple ARM. Cette option est la moins chère, mais offre de moins bonnes performances comparativement à la seconde qui consiste en l'utilisation d'un processeur commercial spécialisé jumelé à une logique dédiée pour l'accélération d'encodage/-décodage. Celle-ci offre de meilleures performances comparativement à la première solution, mais l'évolutivité n'est pas garantie en plus de devoir faire face à un potentiel problème d'obsolescence lorsque le processeur spécialisé arrive en fin de vie. Dénormes coûts peuvent ainsi être engendrés afin de recibler l'architecture initiale vers une nouvelle plateforme.

Afin de pallier en coût de développement et assurer son indépendance au cycle de vie des composants tierce, la compagnie Grass Valley est à la recherche d'un système indépendant et évolutif pour leur prochaine version de leur sous-système « thumbnail ». Celui-ci doit être réalisé à l'aide de composantes pouvant être implémentées sur FPGA facilitant ainsi ces deux points. De plus, l'utilisation de la spécification H.264 pour l'encodage des images a été choisie. Ce point est particulièrement important, car non seulement une telle spécification est très complexe, mais cela demande aussi une profonde exploration architecturale afin de bien évaluer et répartir la charge des algorithmes vers une implémentation logicielle ou matérielle. Il est donc nécessaire de développer un nouveau flot de conception afin de livrer un prototype rapidement malgré la complexité tout en tenant compte des restrictions imposées par le client.

## 1.1 Éléments de la problématique

La création de circuits numériques est un processus dont la complexité ne cesse de grandir depuis l'arrivée des circuits intégrés. Chaque nouvelle génération du processus permet d'intégrer plus de transistors sur une même puce suivant la loi de Moore [31]. Or, afin d'utiliser ces nouvelles ressources, les concepteurs doivent produire des modules permettant l'utilisation de logique plus complexe.

Pour augmenter la productivité des ingénieurs, un flot de conception s'est tranquillement développé. On cherchait à normaliser la description de système et trouver un langage commun désignant les procédés numériques. De cela sont nés plusieurs langages de description matérielle tels que ABEL, AHPL , ELLA , VHDL et Verilog. Par la suite, ont été développés des logiciels pouvant simuler ces descriptions, ainsi que des synthétiseurs logiques traduisant ces modèles en porte élémentaire et pouvant être éventuellement intégré sur un support physique (silicium).

Bien que cette approche apporte plus de flexibilité, elle n'est plus à elle seule suffisante afin de réduire le manque de productivité apporté par le développement des systèmes modernes. Ces derniers se sont complexifiés rapidement. Il suffit de regarder les téléphones portables modernes : unité graphique (GPU), décodeur, encodeur, processeur haute performance, processeur applicatif, etc. Il ne s'agit plus seulement de produire un seul module, mais des systèmes hétérogènes complexes sur puce tout comme l'encodeur/décodeur H.264 à développer pour la compagnie Grass Valley [44, 38, 42] . Un module matériel peut être créé et ajouté au système afin d'augmenter la performance de celui-ci et réduire la consommation. Un tel module nommé logique dédiée est toujours plus performant. Afin de pallier l'augmentation des besoins d'accélération, les logiciels de synthèse algorithmique ont fait leur apparition. Ceux-ci sont en mesure de prendre un code logiciel et de créer un modèle RTL synthétisable. À l'aide de ces outils, nous avons maintenant une approche plus automatisée pour passer du modèle logiciel au modèle matériel.

### 1.1.1 Problématique principale

Bien qu'ils facilitent la tâche des ingénieurs, les logiciels de synthèse algorithmique ne répondent pas à toutes ces nouvelles questions qui font surface lors de la création de systèmes hétérogènes. Par exemple, quelle partie du système doit être accélérée à l'aide de logique

dédiée et de quelles façons ? Est-ce que telle portion en matériel me permet une meilleure performance plutôt que tel autre ? Quels modèles de communication utiliser ? Ces questions sont encore plus difficiles lorsqu'on doit aussi respecter les objectifs de consommation (thermique), de surface (coût) et de performance. Dans cette optique, il ne s'agit plus d'utiliser une grande quantité de transistors, mais aussi de les utiliser le plus efficacement possible. Comment faisons-nous pour trouver la meilleure configuration pour le système, afin de respecter tous ces requis surtout lorsque ceux-ci peuvent être orthogonaux ? Comment pouvons-nous connaître les compromis le plus tôt possible lors de la conception pour réduire le risque d'erreur ? Une approche de bas vers le haut « bottom up » traditionnelle utilisant seulement les langages de description matérielle ou la synthèse algorithmique ne peut certifier que le produit final saura répondre à ces exigences. Cette méthodologie considère que ces décisions ont déjà été prises préalablement. Si une erreur s'est glissée lors des spécifications, qu'une mauvaise élaboration a été choisie ou si nous voulons tester d'autres architectures, le temps de conception sera grandement prolongé si celui-ci nécessite beaucoup d'itération afin d'atteindre ces différents objectifs. Même chose si la plateforme cible change (différents processeurs, mémoires, etc.). L'itération de logique est toujours plus ardue lorsqu'on travaille à plus bas niveau (RTL).

Il est alors nécessaire de développer une méthodologie permettant de travailler à l'aide d'une plus grande abstraction et d'être en mesure de faire la recherche de solutions et de modéliser les communications le plus rapidement possible dans la conception d'un système. Afin d'être en mesure d'effectuer une exploration architecturale tôt dans le développement on se doit de réduire le couplage des communications et les détails d'implémentation matérielle ou du moins en cacher l'implémentation. On doit travailler sur une vue système en terme de tâches que celui-ci doit accomplir et leurs interactions plutôt que de penser en terme de composantes (Processeurs, coprocesseurs, logiques dédiées, etc.). On doit donc travailler à très haut niveau comparativement aux méthodes de développement actuelles. Plusieurs articles sont disponibles sur l'implémentation matérielle en format RTL (circuit numérique) de diverse partie de l'algorithme d'encodage H.264. Or, ces implémentations RTL sont, par définition, liées à une architecture et peuvent être difficilement portées vers d'autres (changement de processeur ou fabrique). De plus, les optimisations appliquées en RTL ne peuvent directement s'appliquer lors de la conception d'un modèle plus abstrait du système. Jusqu'à maintenant, les méthodologies de développement du point de vue du système sont très peu couvertes et nécessitent encore une grande portion de développement manuel.

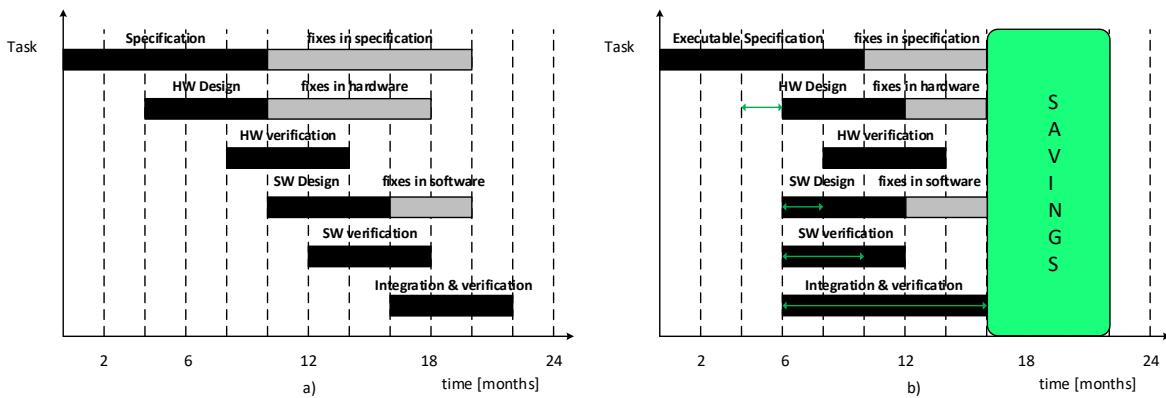

### 1.1.2 Problématique explorée dans ce mémoire

Les méthodologies de conception actuelles prévoient un modèle système à des fins d'évaluation fonctionnelle et de référence aussi appelé « golden model ». Cette référence exécutable n'est pas elle-même utilisée pour le produit final, c'est-à-dire que le code fonctionnel du modèle, préalablement validé, peut ne pas être réutilisé pour l'élaboration même du système sur puce. Cette référence qui est alors du jetable pourrait servir comme base afin de réduire le temps entre la conception et la création du système. Ce format exécutable devient la référence du projet et c'est celle-ci qui sera transformée en système sur puce. De cette façon, le temps de développement fait sur la spécification est alors sauvé par sa réutilisation et permet une mise en marché plus rapide. Il s'agit donc d'augmenter l'intégration et l'utilisation du modèle exécutable dans le flot de conception.

Un système tel que demandé par Grass Valley est un bon exemple de cette problématique. Nous disposons d'un grand nombre d'implémentations logicielles d'encodeur/décodeur H.264 et il serait intéressant de les réutiliser afin d'accélérer la production de l'encodeur sur puce. L'implémentation complète de la norme à partir de ces spécifications nécessite une très grande charge de travail qui dépasse le cadre de cette maîtrise.

## 1.2 Objectifs de recherche

Ce projet comporte deux principaux volets. Le premier volet consiste à explorer la possibilité de développer un système sur puce (SoC) à l'aide d'un modèle système, examiner la possibilité d'intégrer les techniques de codesign matériel/logiciel ainsi qu'ESL (Electronic System Level) et définir la méthodologie requise pour mettre à terme ce type de projet. Ce que nous proposons est le développement et la modélisation du système en entier à l'aide d'un langage haut niveau sans déterminer les particularités logicielles et matérielles préalablement, mais que ce choix soit fait lors de l'exploration architecturale. Le modèle devra être découpé de son architecture pouvant alors être modifiée et reciblée rapidement. Ce sont ces choix architecturaux qui deviendront l'implémentation concrète du système qui sera ensuite synthétisé vers une puce FPGA.

Le second volet porte sur le développement d'un module « proxy » qui agira comme encodeur H.264 afin de remplacer le module « Thumbnail » de Grass Valley et de leur fournir une plateforme évolutive leur permettant la mise à jour de celui-ci à un faible coût tout en

éitant le problème de dépendance à une tierce partie. Ce module servira donc de cas de figure pour la recherche d'une méthodologie de développement au point de vue du système mentionné au premier volet.

### 1.3 Résumé des contributions

Ce projet de maîtrise a conduit aux contributions suivantes :

1. Démonstration de la faisabilité de développer un encodeur H.264 à partir d'une référence logicielle utilisée en entrée d'un processus de codesign logiciel/matériel. (Autant que nous sachions, il s'agit là d'une première.)

2. À partir des résultats du point 1), proposition d'étapes d'une exploration architecturale afin de déplacer un code applicatif vers une implémentation matérielle.

3. Expérimentation du développement d'un SoC encodeur H.264 logiciel/matériel s'exécutant sur une plateforme virtuelle du FPGA Zynq de Xilinx. Cette même plate-forme virtuelle servant à faire la validation de l'exploration architecturale.

4. L'identification d'obstacles qui rend complexe la migration d'algorithmes logiciels vers un modèle matériel durant l'exploration architecturale.

5. Réalisation d'une preuve de concept visant à éliminer certains obstacles qui n'ont pu être traités dans le cadre de ce projet et qui serviront aux travaux futurs.

### 1.4 Plan du mémoire

Ce mémoire est organisé comme suit. Le second chapitre sera dédié à la revue de littérature traitant du codesign, de la méthodologie ESL, du développement système et de la norme H.264. Le troisième chapitre sera dédié à l'expérimentation de la méthodologie et le développement de l'encodeur alors que le quatrième chapitre présentera les résultats. Le chapitre 5 fera suite au résultat avec une exploration afin d'améliorer le processus de développement. Finalement le chapitre 6 présente la conclusion et les travaux futurs.

## CHAPITRE 2 REVUE DE LITTÉRATURE

Ce chapitre se veut un survol des domaines pertinents pour la compréhension de ce mémoire. Nous allons d'abord définir les concepts de codesign, de la méthodologie ESL et de divers outils nécessaires à l'application de celle-ci. Nous présenterons par la suite l'approche du développement système et les divers travaux effectués dans ce domaine, pour ensuite poursuivre sur une introduction de la norme H.264. Finalement, quelques implémentations d'encodeur H.264 seront présentées.

### 2.1 Le codesign

La méthodologie codesign [20, 23, 44, 51] dans le domaine des circuits numériques apporte une solution afin d'accélérer l'exploration architecturale d'un système logiciel et matériel. Il s'agit donc de concevoir à l'aide d'une vue système plutôt qu'une vue par module. De haut vers le bas « Top down » plutôt que de bas vers le haut « Bottom up ». Le but est d'atteindre plus facilement les contraintes telles que le coût, la performance et la puissance tout en réduisant le temps de développement nécessaire pour la mise en marché d'un produit.

Cette méthodologie invite les membres des équipes logicielles (OS, firmware, et application) à travailler de pair avec l'équipe de développeurs matériels sur tous les modules du système. On veut réduire le temps de mise en marché, alors le développement logiciel et matériel doit se faire en parallèle afin d'augmenter la productivité comparativement à l'approche séquentielle traditionnelle. Tout comme la validation du produit qui doit aussi se faire sur la totalité du système [44].

La première ébauche du codesign tentait de formuler une approche aux problèmes de partitionnement des tâches et leur ordonnancement sur une plateforme multiprocesseur [44]. Elle consistait à des plateformes fixes comportant un processeur et un groupe de coprocesseur de type ASIC communiquant sur un bus et utilisant de la mémoire partagée. Les développeurs analysaient la complexité algorithmique et déterminaient quelles tâches étaient candidates à la conception de modules matériels et la plateforme était fixe tout le long du développement. Aussi, ce modèle n'avait aucune notion de concurrence. Une tâche s'exécute sur le processeur et celui-ci attend après ses coprocesseurs.

La seconde approche ajouta l'inclusion de plusieurs processeurs, le support d'exécution de plusieurs tâches en parallèle et apporta un des éléments clés du codesign, la cosimulation [44]. La cosimulation consiste en la simulation de l'environnement logiciel et matériel sous le même système [40, 47]. À ce moment, on utilisait un modèle virtuel des processeurs sur lequel on exécutait le code logiciel ou sous une version synthétisé des modules matériels. Le modèle virtuel est l'approche la plus souvent utilisée, car la simulation par RTL est typiquement trop lente. Une chose était claire, on se devait d'aller plus haut en abstraction afin de gagner en temps d'exécution. Il s'agit de gérer correctement l'abstraction en fonction de la précision voulue [20].

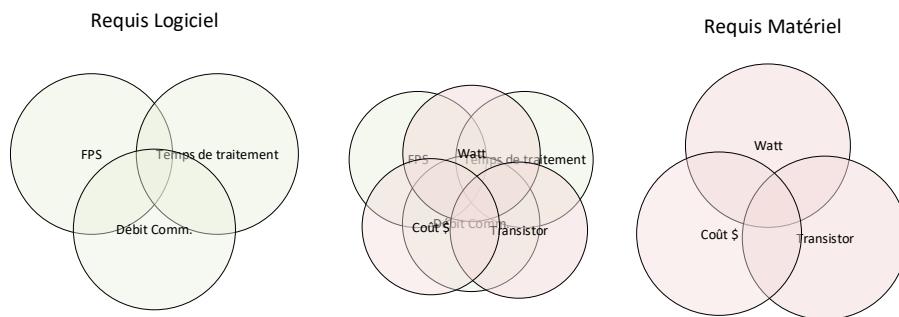

De nos jours, les systèmes modernes sont beaucoup plus complexes et remettent en question deux hypothèses à la base des premières générations de codesign. La première hypothèse stipulant que la plateforme donnée est fixe. Ceci n'est plus toujours le cas. En effet, les systèmes sont maintenant hétérogènes [49, 38] et souvent taillés sur mesure selon leurs fonctions [46, 25, 52, 38]. La seconde hypothèse dit qu'il est possible de minimiser ou maximiser le coût et la performance par l'approche de techniques d'optimisation. Étant donné que chaque produit nécessite alors une approche particulière, ceci devient grandement complexe étant donné le nombre de paramètres à optimiser. Afin de répondre adéquatement au besoin des utilisateurs, une application suit habituellement un groupe de requis. Par exemple, une acquisition de 30 images seconde, un débit de communication, etc. Or, un système embarqué possède lui aussi des requis qui sont de différentes natures telles que la performance (la rapidité de traitement), les ressources disponibles (espace, transistors, etc.), la consommation (watt), la fiabilité, le coût, etc. Tel qu'illustré à la figure 2.1, les fonctions d'optimisation pilotant le partitionnement doivent donc être flexibles et à multiples objectifs. Ceci est considéré comme un problème NP complet [45].

Figure 2.1 Espace de solution matériel/logiciel

## 2.2 Méthodologie ESL

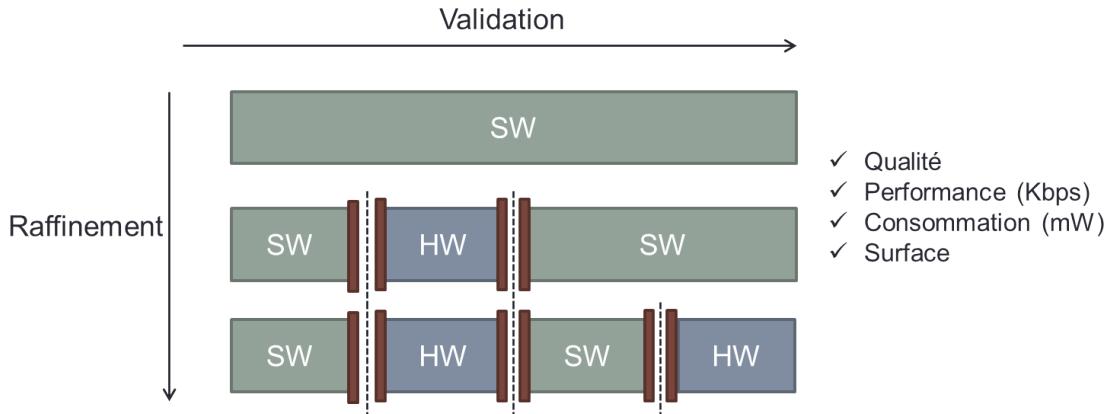

Afin de faire face à la croissance en complexité des systèmes sur puce, le codesign s'est modernisé avec l'arrivée de la méthodologie « Electronic System Level » (ESL). L'approche ESL a pour but de simplifier le développement de système électronique/informatique en proposant d'augmenter le niveau d'abstraction des spécifications, de l'analyse, de la conception et de la vérification afin que cela soit fait sur l'entièreté du système. L'approche vise à développer le système comme un tout plutôt que d'opérer module par module. L'objectif de la méthodologie est d'implémenter les fonctionnalités du système sans égard à ce qu'elle doit se faire en matériel et logiciel ou une combinaison des deux. On parle alors de conception du point de vue du système [29].

La méthodologie ESL définit seulement un flux de conception qui décrit les étapes nécessaires afin de pouvoir produire un système à divers niveaux d'abstraction. Tel que décrit dans [29], il n'y a pas une seule bonne méthodologie pour tous les types de système. On parle alors de méthodologies ESL. Pour cette recherche, nous nous concentrerons sur ESL appliqué au système sur puce avec une approche du haut vers le bas.

### 2.2.1 Modélisation

La première étape de la méthodologie ESL est celle de la modélisation du système. Le modèle d'un système est la description (ou l'analogie) utilisée pour aider la compréhension de quelque chose qui ne peut être observé directement. Par exemple, une liste de spécifications ou de requis. La plupart du temps, un modèle utilise l'abstraction qui peut camoufler les détails d'implémentation et ainsi mettre en avant-plan les aspects importants du modèle en les rendant plus simples à comprendre [29].

Pour se faire, la méthodologie ESL nécessite un langage permettant de spécifier le système à différents niveaux d'abstraction. Il existe plusieurs langages de modélisation tels que MATLAB M-Code, SystemC, SystemVerilog, Specification and Description Language (SDL), UML, eXtensible Markup Language (XML), BlueSpec, etc [29]. Dans le cadre de cette recherche, l'utilisation d'outils comme SystemC d'Accelera et de librairie d'abstraction telle que « Transaction Layer Model » (TLM) [13] nous a permis de décrire un système sur puce à très haut niveau de façon simple.

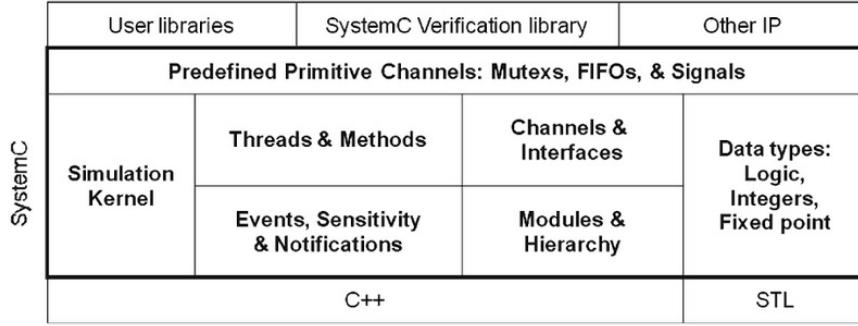

## SystemC

SystemC est une librairie de conception système pour le langage C++. Elle permet, entre autres, la définition de module similaire à ceux pouvant être créés à l'aide de langage HDL tel que Verilog et VHDL.

Figure 2.2 Architecture de la librairie SystemC

La figure 2.2 tirée de [11] décrit ce que la librairie apporte au concepteur système. Elle ajoute les types, interfaces, canaux, primitive de temps et autres objets nécessaires pour la description de module matériel, leur interaction et la concurrence. De plus, elle inclut un noyau permettant la simulation de ces modules.

Cette librairie permet à l'aide d'un seul langage de spécifier les modules matériels et logiciels. Elle permet l'utilisation de C++ comme langage de base faisant ainsi levier sur l'utilisation d'un grand nombre de logiciel et de librairie déjà existante. Cela apporte une meilleure réutilisation et un gain de productivité. La librairie possède aussi un sous-ensemble permettant la synthèse algorithmique. Les modules conçus strictement à l'aide de ce sous-ensemble peuvent être transformés par un outil en module RTL.

L'utilisation de SystemC, comparativement au langage HDL traditionnel, apporte aussi une meilleure abstraction et permet de définir un module à plusieurs niveaux de précision tel que le demande la méthodologie ESL. Il est possible de cette façon de définir des algorithmes et des canaux de communications de haut niveau en utilisant les types entiers de C++ ou en concevant des objets spécifiques à l'aide de classe.

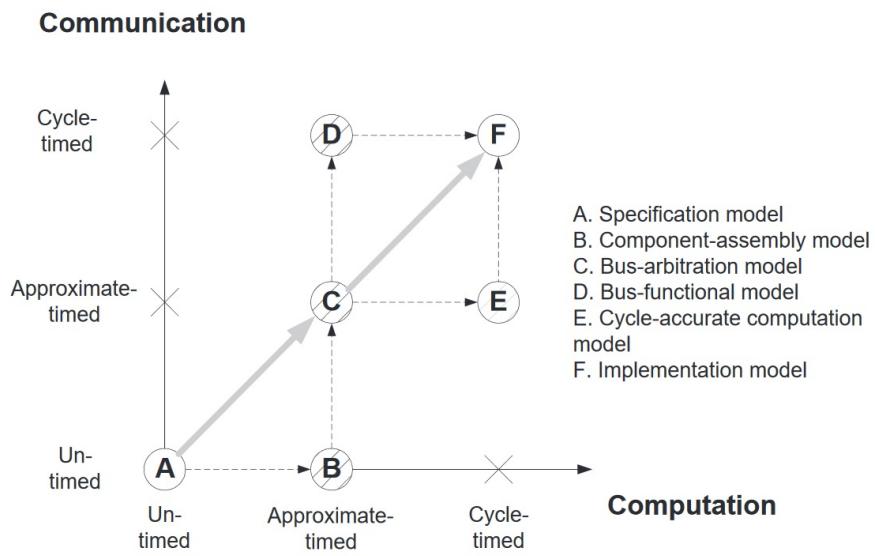

## TLM

Afin de modéliser ces abstractions, SystemC est utilisé de pair avec la méthodologie de modèles de niveau transactionnel « transaction-level model » (TLM). La méthodologie TLM consiste à séparer la représentation de l'algorithme ou le fonctionnement d'un module de ses communications. Les communications sont définies par des canaux alors que la demande de transactions est effectuée par l'appel de fonctions sur les interfaces représentant ces canaux. De cette façon le détail des communications (signaux, synchronisme, etc.) est caché par cette abstraction. Les détails des communications peuvent ainsi être définis plus tard dans la conception du système [13]. Cela permet donc l'implémentation des niveaux d'abstraction mentionnés par la méthodologie ESL. En effet, la représentation de chaque partie du système peut évoluer indépendamment, c'est-à-dire que le module peut être du niveau RTL alors que les communications peuvent être du niveau transactionnel. Cette approche permet aussi d'accélérer la simulation du système. Afin d'implémenter ces niveaux d'abstractions, la méthodologie TLM définit quatre modèles de programmation [37].

- **Untimed** : La conception d'un modèle « untime », aussi appelé « untimed fonctionnel » (UTF), inclut peu ou pas de notion de temps. La synchronisation se fait de façon explicite à l'aide du mécanisme d'évènements « event » et des fonctions « wait » et « notify ». Ce modèle est utile pour l'approche fonctionnelle où l'on conçoit le système sans se préoccuper des contraintes de temps. Cela permet de valider que le système respecte les spécifications fonctionnelles. Ce modèle n'offre aucune distinction entre matériels et logiciel. L'architecture n'est pas considérée dans ce modèle.

- **Loosly timed** : Ce modèle ajoute deux points de chronométrage/synchronisation au modèle de simulation. Un à l'envoi d'une transaction et l'autre à la réponse à celle-ci. De plus, la simulation utilise un logiciel d'ordonnancement permettant la synchronisation à un delta de temps paramétrable (1 ns, ms, s, etc.). Avec l'ajout de ces fonctionnalités, cette approche permet de modéliser des horloges et interruptions. Ceci est suffisant pour exécuter un système d'exploitation et exécuter des tâches sur celui-ci. Cela permet donc une première ébauche d'une plateforme virtuelle pour concevoir et exécuter le logiciel. Ce modèle permet aussi aux tâches SystemC, tout en respectant les détails de temps, de s'exécuter plus rapidement que la simulation en effectuant le traitement jusqu'à la rencontre d'un point de synchronisation de la simulation (quanta).

- **Approximated timed** : Le modèle « Approximated timed » aussi appelé « Timed

fonctionnel » apporte une plus grande granularité de temps que le modèle « loosely timed ». Les communications ont quatre points de chronométrage. Il s'agit d'un modèle comportemental avec concept de temps. Les modules et communications sont raffinés par l'ajout de latence à leur implémentation à l'aide de la commande SystemC « wait ». Par exemple, l'ajout d'annotations temporelles pour modéliser le temps d'exécution d'un corps de boucle « while » ou encore pour modéliser le temps de communication vers un autre module, etc. Tout comme le modèle précédent, une simulation de ce modèle opère avec des quantas de temps paramétrable (1ns, ms, s, etc.).

- **Cycle-timed** : Le modèle au précis au cycle « cycle-timed » ou « cycle accurate » correspond au RTL équivalent d'une implémentation à l'aide d'un langage HDL. Les modules sont définis à l'aide de chemin de données et de contrôle à l'aide de machine à états et les communications sont implémentées par des signaux élémentaires.

Figure 2.3 Modèle TLM [13]

Grâce au découplage des communications et des modules, chacun peut être raffiné indépendamment tel qu'illustré à la figure 2.3. Le modèle « loosely timed » a été ajouté pour la version 2 de TLM et n'est pas affiché sur cette figure. On peut voir que l'axe des communications peut évoluer indépendamment de l'axe de calcul et le concepteur est libre de choisir la direction pour le raffinement de ses modules.

À l'aide de la librairie SystemC et de la méthodologie TLM, nous sommes en mesure de développer un système avec plusieurs niveaux d'abstraction. Ce modèle doit être exécuté afin

d'avoir une idée des performances de celui-ci selon ces divers modèles d'abstraction et des choix architecturaux. Pour se faire, la méthodologie ESL préconise une approche à l'aide de plateforme virtuelle.

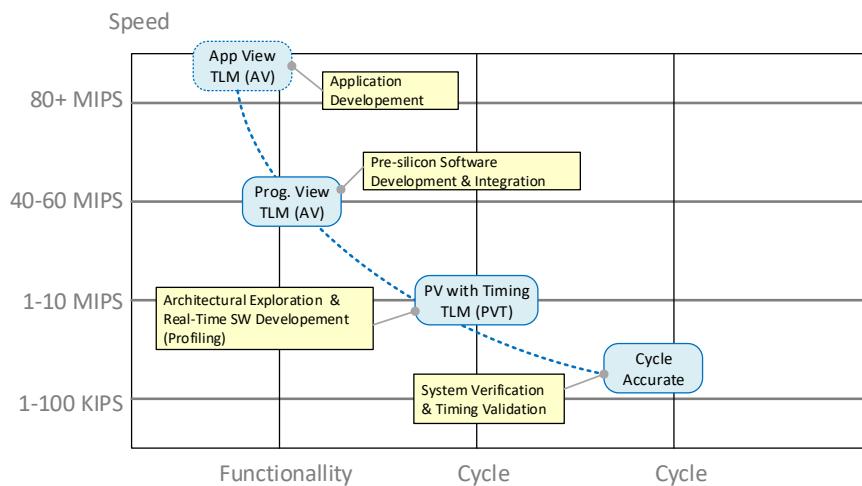

### 2.2.2 Plateforme Virtuelle

Les plateformes virtuelles sont une représentation logicielle fonctionnelle d'un système matériel sous forme logicielle qui peut être basée sur une suite de processeurs (ARM, x86, PowerPC, etc.), de périphériques, de mémoires et d'autre module plus spécifique au domaine dans lequel le système opérera. Sur une plateforme virtuelle, ces éléments sont modélisés à haut niveau par des simulateurs de jeu d'instruction « Instruction Set Simulator » (ISS), des appels de fonction, des accès mémoire et des transactions de communication. Ces modèles matériels peuvent exécuter un système d'exploitation (Linux RT, uC-II, QNX, etc.) et des logiciels tout comme si cela était exécuté sur un système physique [5].

Comme discuté dans la sous-section précédente, une plateforme virtuelle peut implémenter plusieurs modèles de communication et d'architecture avec des contraintes de temps plus ou moins précises. Ceci est grandement plus rapide comparativement à l'approche de type précis au cycle et au bit près « cycle/bit accurate » associée à la simulation RTL traditionnel. La précision de ces modèles peut alors être augmentée en fonction de l'avancement du développement pour obtenir des métriques plus précises toujours en étant plus rapide [5].

Figure 2.4 Vitesse de simulation en fonction de l'abstraction [41]

L'idée principale derrière l'utilisation de plateforme virtuelle pour le domaine des systèmes embarqués sur puce c'est d'accélérer le développement en permettant l'accès à un modèle fonctionnel du matériel afin d'entreprendre le développement des logiciels plus rapidement [5]. Cette approche offre aussi plusieurs autres possibilités. Une possibilité importante parmi ces dernières est la possibilité de tester en continu le développement du système. La plateforme virtuelle permet d'intégrer rapidement au niveau fonctionnel le matériel et le logiciel en simultané. Les changements incrémentaux peuvent alors être testés sur l'entièreté du système de façon continué plutôt qu'à la fin d'un cycle de développement. [19]. Une autre fonctionnalité importante pour ce projet est l'extensibilité de la plateforme. Afin d'inclure le développement matériel, certaines plateformes possèdent une possibilité d'extension pour « cosimuler » avec les blocs matériels spécialement développés pour ce système. Il existe plusieurs plateformes virtuelles développées capables d'offrir cette fonctionnalité, dont SIMICS de Wind River et OVPSim de Imperas. Ces plateformes offrent une suite d'outils commerciaux permettant l'extension et la configuration d'ISS et des différents périphériques modélisés [28, 4]. Il existe aussi des plateformes de virtualisation à source ouvert comme QEMU[9] et GEM5[10]. Ces logiciels ont l'avantage d'être gratuits et peuvent aussi être étendus afin de répondre aux besoins des architectes système.

Dans le cas de ce mémoire, nous utilisons le logiciel SpaceStudio qui inclue la plateforme QEMU avec l'extension TLMu [18]. Cette extension permet la communication par protocole TLM avec QEMU. Cette approche permet d'utiliser QEMU afin de fournir un ISS pour le cœur ARM. Plus précisément le Cortex-A9 à coeurs double dans notre cas. Afin de définir des modules matériels spécialisés préalablement développés ou en développement pour ce système, on peut utiliser la modélisation SystemC ainsi que le noyau de simulation de celui-ci pour effectuer une cosimulation.

Suite au partitionnement, le code source C/C++ et SystemC peut être transformé en modèle RTL à l'aide d'une plateforme EDA permettant la synthèse haut niveau (HLS).

### 2.2.3 HLS

La synthèse comportementale (High Level Synthesis) aussi appelée « ESL synthesis » permet de créer un système à haut niveau à l'aide de code C/C++/SystemC et produire la logique numérique en format RTL (Verilog/VHDL). De ces sources RTL il est possible de créer une implémentation « gate-level » (porte logique de base) à l'aide de la synthèse logique.

La synthèse à haut niveau est un domaine de recherche très actif et est issue du besoin de palier à l'augmentation de la complexité des systèmes numériques. En permettant de définir un système à un plus haut niveau d'abstraction à l'aide d'un langage comme SystemC, la synthèse permet une plus grande productivité, mais aussi une meilleure optimisation des ressources et des performances de la microarchitecture du module synthétisé. Il existe plusieurs outils HLS notamment des outils commerciaux tels que Vivado HLS de Xilinx [21], CatapultC de Calypto Design Systems [12], Cynthesizer de Forte [30], A++ d'Altera [3] et des outils de recherche tels que DWARV de l'université de Technologie de Delft [35].

Il est aussi connu que les outils HLS d'aujourd'hui procurent de la contrôlabilité (à travers les pragma). Plus l'ingénieur sait comment contrôler, plus optimal est le résultat. Selon les algorithmes analysés et des synthétiseurs utilisés [36], l'approche HLS peut présentement offrir des performances comparables ou moins bonnes que la conception manuelle. En effet, l'article [17] démontre que le module créer à l'aide d'un outil HLS est 3.4 fois plus lent comparativement à une conception manuelle. Par contre, d'autre article comme [6] apporte une nuance en démontrant des performances comparables à un RTL manuel dépendamment de l'approche utilisée par les développeurs. Ceci dit, le bénéfice de la synthèse à haut niveau, pour l'approche ESL, est le gain en temps de productivité étant donné qu'un logiciel HLS peut donner un module RTL en quelques minutes, voir heures, plutôt qu'en semaines, voir mois, si le module doit être fait manuellement.

La synthèse comportementale ne comble que la partie calcul d'un bloc. En ce qui concerne les communications avec celui-ci, elles doivent être établies avant la synthèse en format « pin accurate ». Il y a donc une nécessité de travaillée à un plus haut niveau afin d'abstraire ces communications et permettre une définition d'interface automatiquement [32].

### **2.3 Logiciels de développement au niveau système**

La méthodologie ESL tente d'introduire le développement en maintenant une vue globale du système. Comme discuté dans les sections précédentes, il existe différents outils permettant de développer les diverses étapes de la méthodologie ESL, mais qu'advent-il des environnements de développement les mettant en communs dans un même flot de conception ? Les environnements de développement intégré tel que Vivado de Xilinx [21] et Quartus d'Altera [2] ne représentent eux aussi qu'une partie de la méthodologie. Ils aident à l'implémentation finale du système sur FPGA en prenant en entrée les partitionnements préétablis lors de la conception de l'architecture.

Il existe pour le moment quelques logiciels permettant le design d'un système complet à l'aide de la méthodologie ESL au niveau système. Un de ceux-ci est le logiciel « CoFluent Studio » d'Intel, initialement développé par l'École polytechnique de l'Université de Nantes. Cet outil s'occupe de la modélisation du système à l'aide d'une approche d'ingénierie dirigée par les modèles. Une approche similaire au UML du côté logiciel. Les modèles développés par CoFluent peuvent être transformés automatiquement en module SystemC pouvant ensuite être simulé et testé. Pour valider plus en profondeur l'architecture, l'application est compatible avec les plateformes Virtuel SIMICS de Wind River [16]. Par contre, ce logiciel ne permet pas de continuer dans le flot de conception et produire une implémentation du système. Nous avons une modélisation système qui doit être par la suite répliquée manuellement en logiciel et RTL afin d'en produire une implémentation. Cette traduction a pour désavantage de possiblement introduire des défauts ou des modifications à la spécification initiale. De plus, l'environnement de test devra être reproduit partiellement ou en totalité.

Il existe un projet plus intégré à la méthodologie nommé SystemCoDesigner [24]. Ce logiciel prend en entrée une modélisation du système sous la forme « actor-oriented model » développée en SystemMOC. SystemMOC est une extension de SystemC pour y appliquer la modélisation du comportement des communications. Chaque acteur du système défini en SysteMoC est par la suite transformé en logiciel ou matériel à l'aide d'un outil HLS. La particularité de ce logiciel est l'exploration architecturale automatique. Afin de l'utiliser, l'information de la synthèse est réintroduite dans le logiciel. L'utilisateur élabore les choix architecturaux appelés « architecture template » et les relie au système à l'aide d'une représentation formelle de ces liens avec les requis logiciels et les communications. L'application fournit une suite d'outils afin de développer ces modèles formels. L'algorithme tente par la suite de trouver les meilleures solutions en suivant les compromis décrits dans le modèle formel [24]. Une des principales difficultés de cette application est la définition de ses modèles formels des communications et ressources. Les règles à appliquer nécessitent beaucoup de temps et sont loin d'être intuitif, et ce même si SystemCoDesigner fournit un éditeur pour créer ces modèles plus facilement.

Il y a donc pour le moment un nombre restreint de logiciels qui permet de produire la grande vision de la conception au niveau système et implémenter la fonctionnalité sans égard si cela doit se faire en matériel et logiciel ou une combinaison des deux. Le logiciel SpaceStudio, tout comme SystemCoDesigner tente de remplir ce vide, en apportant un environnement intégré

de développement logiciel/matériel en utilisant des modèles intuitifs incluant une plateforme virtuelle, divers niveaux d'abstraction et la possibilité de l'implémentation du système à l'aide d'outil EDA tierce.

### 2.3.1 SpaceStudio

L'application SpaceStudio comble ce vide à l'aide d'une vue à haut niveau sur le développement de système embarqué sur puce [34, 33, 32, 8]. L'application permet de manipuler à haut niveau les diverses applications et algorithmes du système afin d'explorer leur implémentation à l'aide de différentes ressources (processeur général, coprocesseur, protocole, etc.). Ceci de façon rapide à l'aide de sa plateforme virtuelle et d'une représentation par module des diverses tâches du système. Il utilise une approche similaire aux processus de khan [32, 8] et chaque module communique par lien bien défini modélisé par des fifo, bus, DMA, mémoire partagée et registre. SpaceStudio offre des facilités afin que chaque module puisse être exécuté comme logiciel ou coprocesseur matériel facilement. Ainsi le concepteur est capable d'obtenir une estimation des performances du système [8]. Ceci permet d'expérimenter plusieurs solutions en fonctions des requis pour réduire rapidement l'espace de recherche d'un système logiciel/matériel.

Afin de modéliser un système sous SpaceStudio, on doit implémenter les blocs fonctionnels de celui-ci sous forme de modules. L'application contient la librairie SpaceLib qui abstrait tous les interconnexions et périphériques de la plateforme. Elle implémente un premier niveau d'abstraction qui permet la simulation et vérification au niveau fonctionnel du système. La caractéristique principale de cette configuration est l'utilisation de modèle abstrait pour les communications. Celles-ci se font à l'aide soit d'un modèle de bus de type UTF (untimed functional) ou TF (timed functional). À ce niveau, les simulations sont rapides et peu précises. Elles ne donneront pas nécessairement un bon estimé des performances, mais elle permet rapidement de vérifier que notre implémentation est fonctionnelle. Suite à cela, le logiciel implémente une seconde phase d'où il est possible de raffiner en passant à une plateforme virtuelle plus précise (modélisation des délais, ISS plus précise, etc.) et effectuer une recherche en profondeur. C'est lors de cette configuration que l'on spécifie une plateforme matérielle du système (CPU, DSP, Bus, mémoire, DMA, etc.) et les protocoles de communication de type AT (Approximately Timed). À cette étape, il est possible de faire l'exploration architecturale et produire plusieurs configurations différentes afin de réduire l'espace de solution.

Les modules matériels sont exécutés à l'aide du simulateur de SystemC alors que le logiciel est exécuté par un ISS. Dans le cas d'un ISS pour Microblaze, son implémentation est faite en SystemC [8]. Cet ISS offre aussi la possibilité d'exécuter un RTOS grâce à une translation des appels système [15]. D'autre part, l'ISS du processeur ARM a pour noyau l'émulateur de QEMU qui communique par lien TLM au simulateur SystemC à l'aide de TLMu préalablement présenté. Cette approche permet d'exécuter différentes partitions logiciels/matérielles composées de tâches SystemC, soit sous format logiciel ou matériel, reliées entre eux par des interconnexions TLMu.

Figure 2.5 SpaceStudio RTOS sur ISS SystemC [15]

Finalement, les solutions élaborées à l'aide de la plateforme peuvent être implémentées et validées sur FPGA à l'aide de la Synthèse algorithmique (HLS) d'un CAD ou EDA tierce. Lors de l'utilisation des outils de Xilinx, il est aussi possible de spécifier une liste de « pragma » ou spécification pour optimisation. SpaceStudio vérifie le design du système selon les contraintes physiques du FPGA ciblé, traduit toutes les composantes du système vers des IP de la librairie utilisée (Xilinx ISE, Xilinx EDA), fait les interconnexions, instancie toute autre composante nécessaire, génère les déclarations d'entités pour chaque module utilisateur, associe les fichiers logiciels au processeur approprié, ajuste les options de compilation et joint les librairies nécessaires et ajoute un OS au besoin.

Figure 2.6 Flot de la plateforme SpaceStudio

L'approche de haut niveau de SpaceStudio force par contre la séparation d'un système en modules fonctionnels. Cela a pour effet d'influencer la solution finale avant même de connaître le profil de performance de celle-ci. En effet, l'ajout de communication entre deux modules logiciel ou matériel augmente les délais comparativement à un seul module fonctionnel. Le système évalué n'est alors par le même que celui du début, car nous y avons ajouté de nouveaux délais. En pratique, la séparation doit se faire seulement aux endroits jugés propices à l'exploration matérielle suite à un profilage du modèle fonctionnel. Pour ce faire, nous

regardons la possibilité de développer itérativement les modules sous SpaceStudio à l'aide d'une spécification exécutable sous forme d'un système logiciel déjà existant.

## 2.4 Standard H.264

La norme H.264 a été définie par l'« International Telecommunications Union » (ITU), l'« International Standards Organisation » (ISO) et MPEG (Moving Picture Experts Group) comme successeur à la norme MPEG4. La norme conçue en 2003 a pour but d'offrir une efficacité de codage accrue et une robustesse aux environnements réseau. La norme riche de plus de 700 pages définit les différents algorithmes nécessaires afin de produire un décodeur. L'augmentation de la compression et de la qualité vient avec un coût en temps de calcul.

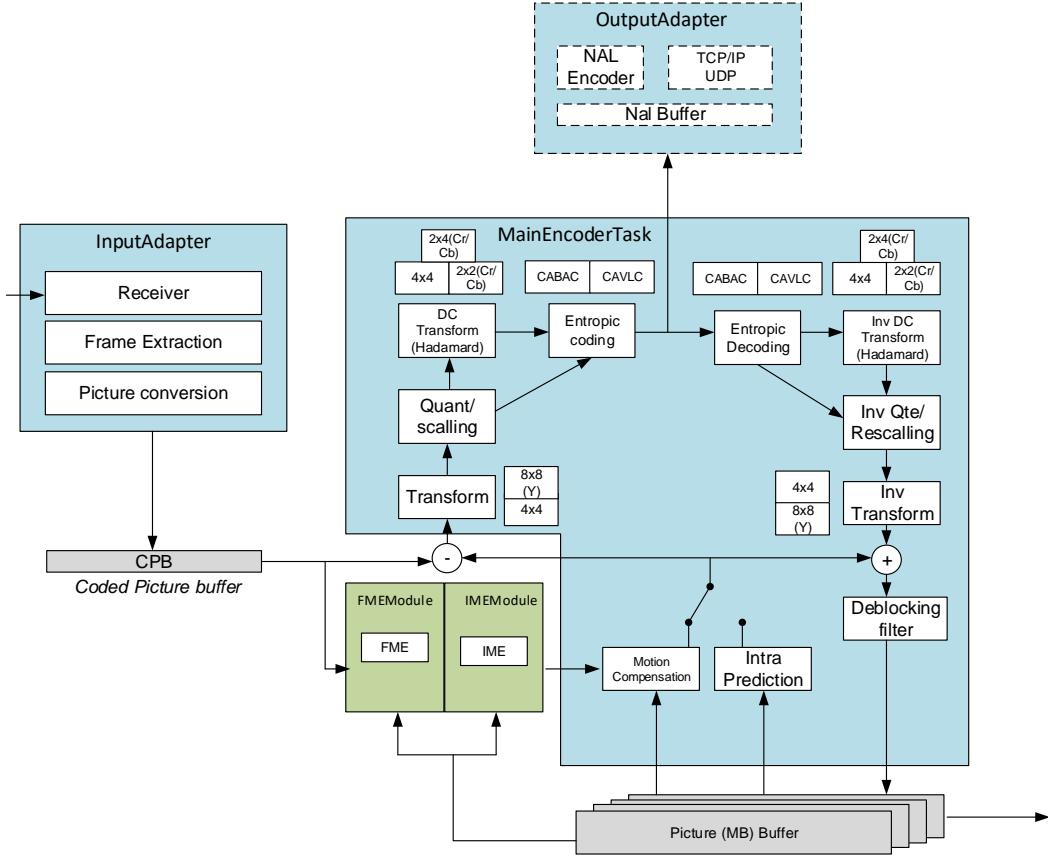

La figure 2.7 démontre sous forme de schéma bloc le flot traditionnel d'un encodeur sous la norme H.264. La section inférieure du schéma illustre le processus d'encodage alors que la section supérieure illustre la boucle de décodage et de reconstruction de l'image de référence pour l'encodage. L'encodeur utilise toujours en référence les images encodées/décodées afin de reproduire le processus d'un décodeur. L'utilisation des images décodées ayant subi une distorsion comme référence assure que l'erreur des prédictions à l'encodage ne divergera pas comparativement à un décodeur n'ayant pas l'image originale.

Figure 2.7 Schéma fonctionnel des étapes d'encodage et de décodage afin de traiter une trame

Dans cette section il sera question de survoler les diverses étapes encadrées par la norme et de détailler au besoin les algorithmes pertinents à notre recherche.

#### 2.4.1 Division de l'image

On doit tout d'abord détailler le format des données en entrée. L'image à encoder doit être dans le format YCbCr. C'est-à-dire un canal de luminance Y (intensité lumineuse) et deux canaux de couleur Cb ( Chrominance bleue) et Cr (Chrominance rouge). L'isolation de la luminance dans un seul canal permet d'effectuer des changements sur l'image sans affecter significativement les variations d'intensité auxquelles l'œil humain est plus sensible. Ces trois canaux sont par la suite échantillonnés indépendamment.

Figure 2.8 Échantillonnage supporté par la norme H.264 [39]

Le but est de réduire l'information en entrée afin de traiter moins de données. Comme mentionné, l'être humain est plus sensible aux intensités lumineuses qu'aux couleurs, il est donc

possible de réduire l'espace utilisé par celles-ci à l'aide d'un sous échantillonnage qui réduit la résolution des chrominances. La norme supporte les échantillonnages suivants :

- **4 :2 :0** : Pour quatre pixels de luminance (Y), la résolution horizontale est alors réduite de moitié.

- **4 :2 :2** : Pour quatre pixels de luminance (Y), la résolution verticale est alors réduite de moitié.

- **4 :4 :4** : Toutes les composantes de l'image sont conservées. Il s'agit d'un échantillonnage sans perte.

Une fois échantillonnée, l'image à traiter est séparée en « slice » et macrobloc (MB). Une « slice » est une portion de l'image pouvant être décodée indépendamment des autres. Une image peut avoir une ou plusieurs « slice » ayant chacune des options d'encodage différentes. À l'intérieur de celle-ci, l'image est séparée à nouveau en blocs de 16 par 16 pixels nommés macrobloc. Le macrobloc est la plus petite division de l'image. Il représente l'entrée attendue pour la plupart des algorithmes qui compose le standard H.264. La figure 2.9 illustre une configuration possible des « slice » composées de macroblocs.

Figure 2.9 Séparation de l'image en slices et macroblocs [50]

#### 2.4.2 Prédiction

Les gains offerts par la norme H.264 proviennent principalement de la performance de ses méthodes de prédictions. La prédition sous H.264 fonctionne comme suit. Pour chaque macrobloc l'encodeur créer une prédition de ce macrobloc en utilisant les données précédemment encodées. Cette prédition est ensuite soustraite au macrobloc pour obtenir le résiduel.

L'efficacité et la précision du processus de prédiction ont un impact significatif sur l'efficacité de la compression. Plus la prédiction est précise, moins le résiduel contiendra de données et cela augmente l'efficacité de l'encodeur. C'est sans surprise qu'il s'agit de la zone la plus lourde d'un encodeur, car augmenter la précision de la prédiction demande une plus grande recherche et une augmentation de la complexité des algorithmes.

Donc afin d'avoir le plus petit résiduel on se doit de trouver la meilleure prédiction. Par contre, les délais engendrés par la recherche de celle-ci doivent être raisonnables en fonction des besoins de l'application de l'encodeur. Par exemple, pour produire un flot encodé en temps réel, chaque image doit être traitée rapidement pour produire le nombre d'images par seconde requis pour conserver une fluidité. Par contre, pour l'utilisation hors ligne comme les films Blu-Ray, l'encodeur peut prendre plus de temps pour trouver la meilleure prédiction.

Les algorithmes de prédiction de la norme H.264 peuvent être séparés en deux types. Prédiction spatiale (intra image) et prédiction temporelle (inter image).

### Prédiction spatiale

La prédiction spatiale tente d'exploiter la redondance d'information dans une image. L'idée est de produire à l'aide des macroblocs déjà encodés de l'image une interpolation produisant un macrobloc similaire à celui qui doit être encodé. La figure 2.10 illustre quelle partie de l'image peut agir à titre de référence.

Figure 2.10 Partage des macroblocs de référence lors du processus de prédiction spatial

Afin de produire ce macrobloc à partir de ceux déjà encoder, la norme décrit neuf interpolations possibles. Celles-ci sont illustrées par la figure 2.11. Le produit de chaque interpolation est alors comparé au macrobloc à encoder à l'aide d'une somme de différences (Sum of Absolute Differences SAD). Plus la somme est grande, plus les données diffèrent. La plus petite somme est alors équivalente à la meilleure prédition spatiale.

Figure 2.11 Méthodes d'interpolation spatiale possible sous la norme H.264

## Prédiction temporelle

La prédiction temporelle tente d'exploiter la redondance d'information dans le temps. C'est-à-dire que l'algorithme utilise les images passées et futures afin de trouver une référence qui minimise le résiduel. L'algorithme nomme ces images encodées de type P (passé) et de type B (bidirectionnel, passé et futur) illustré par la figure 2.12.

L'algorithme recherche dans une fenêtre parmi une suite d'images un macrobloc qui serait proche du macrobloc à encoder. Les références potentielles sont par la suite analysées au macrobloc à encoder toujours à l'aide de somme des différences. La plus petite somme est équivalente à la meilleure prédition spatiale. Comme la recherche se fait sur une fenêtre plus grande que le macrobloc, la référence peut avoir une position différente dans l'image. Simplement penser à une suite d'image d'une personne qui se déplace. Ce déplacement est alors encodé sous forme de vecteur de mouvement. Ce déplacement est aussi illustré par la figure 2.12.

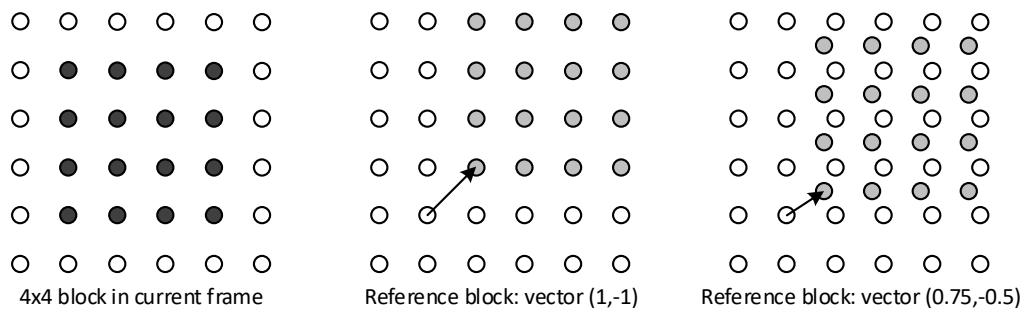

Figure 2.12 Prédiction temporelle et vecteur de déplacement [39]

L'algorithme de recherche supporte aussi le déplacement d'un demi et quart de pixel illustré par la figure 2.13. Ceci peut permettre un meilleur agencement afin de réduire le résiduel au prix d'un temps de calcul plus long. La prédiction aux sous pixel produit une nouvelle référence à l'aide de l'interpolation.

Figure 2.13 Prédiction au sous pixel [39]

Il est aussi possible d'utiliser la prédiction pondérée avec la prédiction temporelle. La pondération permet de mieux prédire un bloc lorsqu'il y a un effet de transition dans la suite d'images. Si les deux blocs sont très semblables et que seulement la luminosité est différente,

il est possible d'encoder un facteur qui pondère le bloc de référence pour le rendre similaire à celui que l'on tente d'estimer.

La prédiction temporelle nécessite une prédiction spatiale (image type I) comme trame initiale. Il peut y avoir plusieurs images de type P et B entre les images de type I. Le nombre de prédictions temporel entre les images de type I est configurable par l'algorithme.

### 2.4.3 Transformée

La transformée est un processus mathématique qui permet, entre autres, de traduire l'image dans le domaine fréquentiel. La transformée est détaillée par l'équation 2.1. Dans le domaine fréquentiel, les basses fréquences représentent l'uniformité alors que les hautes fréquences représentent les changements, discontinuité et détails de l'image. Il est alors possible d'opérer sur ces fréquences et, par exemple, d'éliminer les hautes fréquences qui représentent de l'information moins sensible à l'œil humain (filtre passe-bas). La transformer en elle-même est une opération complètement réversible et n'entraîne aucune perte sur les données. La norme définit une approximation entière de la transformée cosinus discret inverse de laquelle on peut déduire la transformée direct.

$$X_{ij} = \sum_{x=0}^{N-1} \sum_{y=0}^{N-1} C_x C_y Y_{xy} \cos \frac{(2j+1)y\pi}{2N} \cos \frac{(2i+1)x\pi}{2N} \quad (2.1)$$

La transformée utilisée est similaire à celle utilisée dans les normes précédentes (JPEG, MPEG2, MPEG4) à la seule différence que celle utilisée sous H.264/AVC est entière. Une transformée entière permet d'éviter que l'incertitude apportée par les calculs à virgule flottante introduise une erreur dans le décodage d'une image. Étant donné que la spécification utilise les images décodées pour reconstruire les autres (images de type P et B), l'erreur pourrait alors s'additionner et produire des artefacts à l'image. De plus, cette estimation permet aussi d'accélérer les calculs.

### 2.4.4 Quantification

Comme discuté la transformée permet de départager l'information de l'image en hautes et basses fréquences. La quantification est l'opération qui introduit une perte d'information au détriment de la qualité d'image pour réduire l'entropie. La quantification est effectuée sur les résultats de la transformée. Sous H.264 elle permet l'élimination des petits détails (haute

fréquence) dont l'oeil humain est moins sensible. La norme fournit plusieurs matrices de quantification dépendant de la qualité recherchée. Plus la quantification est forte, plus les détails de l'image seront perdus et plus le résultat sera petit.

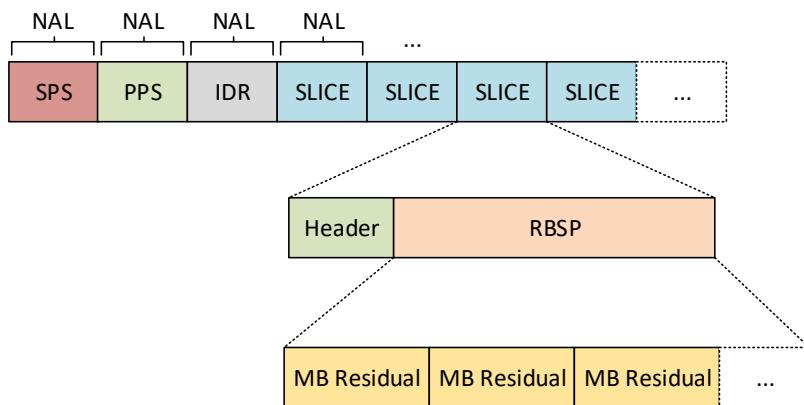

#### **2.4.5 Codage entropique**

Après avoir retiré les détails considérer superflus au résiduel, celui-ci passe dans un algorithme de codage entropique. Le codage entropique est une de compression sans perte. La norme H.264 utilise deux types d'encodage entropique. Soit la «Context Adaptive Variable Length Coding» (CAVLC) et «Context Adaptive Binary Arithmetic Coding» (CABAC).

L'encodage entropique est basé sur la fréquence des données (réduite par la quantification).

##### **Context Adaptive Variable Length Coding (CAVLC)**

Le CAVLC est basé sur le codage de Huffman utilisant les probabilités d'apparition des symboles. L'idée est d'associer aux symboles les plus fréquents le plus petit nombre de bit et vice versa. Les symboles constituant le résiduel sont encodés selon une table de références « look-up table ». Ces tables ne sont pas transmises et font partie du standard et chaque décodeur qui supporte le décodage de trame H.264 se doit d'avoir en mémoire ces tables. À l'aide de ce traitement, l'encodage final comporte moins de bits que les symboles originaux.

##### **Context Adaptive Binary Arithmetic Coding (CABAC)**