|                         | Stateful Data Plane Abstractions for Software-Defined Networks and Their Applications                                                                                                                                                                            |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Carmelo Cascone                                                                                                                                                                                                                                                  |

| Date:                   | 2017                                                                                                                                                                                                                                                             |

| Туре:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                        |

| Référence:<br>Citation: | Cascone, C. (2017). Stateful Data Plane Abstractions for Software-Defined Networks and Their Applications [Ph.D. thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/2741/">https://publications.polymtl.ca/2741/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/2741/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Brunilde Sanso, & Antonio Capone      |

| <b>Programme:</b><br>Program:            | génie électrique                      |

## UNIVERSITÉ DE MONTRÉAL

# STATEFUL DATA PLANE ABSTRACTIONS FOR SOFTWARE-DEFINED NETWORKS AND THEIR APPLICATIONS

CARMELO CASCONE DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE PHILOSOPHIÆ DOCTOR (GÉNIE ÉLECTRIQUE) JUILLET 2017

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée :

# STATEFUL DATA PLANE ABSTRACTIONS FOR SOFTWARE-DEFINED NETWORKS AND THEIR APPLICATIONS

présentée par: <u>CASCONE Carmelo</u> en vue de l'obtention du diplôme de: <u>Philosophiæ Doctor</u> a été dûment acceptée par le jury d'examen constitué de:

M. CARDINAL Christian, Ph. D., président

Mme SANSÒ Brunilde, Ph. D., membre et directrice de recherche

M. CAPONE Antonio, Ph. D., membre et codirecteur de recherche

M. SCHNEIDER Fabian, Ph. D., membre

${\rm M.}\ \underline{\rm GIACCONE\ Paolo},\ {\rm Ph.}\ {\rm D.},$  membre externe

## **DEDICATION**

To my family.

#### **ACKNOWLEDGEMENTS**

This work would not have been possible without the support and help of many talented and generous people.

First and foremost, I wish to thank my two advisors Antonio Capone and Brunilde Sansò, without them, the journey to the point where I am writing this would not have been nearly possible. Apart from sharing their deep technical expertise, I thank them for seeing something in me and convincing me to start this Ph.D. adventure four years ago. They have been a role model, providing invaluable support and advice on shaping my research, presenting my work to the scientific community, advising students, finding jobs, and on life in general. Thank you!

I would also like to thank my thesis committee members, Paolo Giaccone and Fabian Schneider, who dedicated part of their precious time to read this work. Their comments on draft versions were helpful and improved the document considerably.

Since the very beginning of my Ph.D., I was fortunate to have many collaborators with whom I worked on projects which led to this dissertation. I would like to thank Giuseppe Bianchi and Marco Bonola for having me involved in this great idea of making OpenFlow stateful. Without them, the topic of this thesis would have been different. Thank you for sharing with me your ideas and enthusiasm for research. I am also grateful to Roberto Bifulco, Salvatore Pontarelli, and Nicola Bonelli. Roberto's help was fundamental in shaping my research style, he taught me the importance of being honest when writing papers, and that of always keeping an eye on the "broad picture"; Salvatore taught me everything I know about hardware, and Nicola everything I know about high-performance packet processing in software. Along with them, I would like to thank all the people involved in the BEBA EU project, for sharing their expertise and for the fun moments. It has been great working with all of you!

This work would not have been possible without the generous help of Davide Sanvito, Luca Pollini, Alessandro Q.T. Nguyen, and Luca Bianchi, whom I had the pleasure of tutoring while working on their master thesis, and which help significantly contributed to this thesis.

I would like to thank also my lab mates Davide Sanvito (again!), Luca Gianoli, Filippo Malandra, Silvia Boiardi, and all the people of the AntLab and the ISGP group at Politecnico di Milano. Thank you for sharing your knowledge with me and for all the lunches and coffee breaks. Special mention goes to Luca Gianoli: I received my first taste of research while working under his supervision for my master thesis. He helped me write my very first paper,

an experience that motivated me to apply for the Ph.D.

A big thank goes to the administrative personnel that kept these four years running smoothly. Thanks to Francesca Clemenza, Marie Perreault, and Nathalie Levesque for helping me with all the bureaucratic requirements. Thanks to Roberto Resmini, Edoh Logo, and Pierre Girard for providing the necessary technical support and for allowing me to perform crazy experiments on the campus network.

Many friends outside school provided the necessary encouragement and distraction that made this ride more enjoyable and most importantly kept me up in tough moments. Special mention goes to Gianmaria, for the culinary experiences and for making my time in Milan more pleasant; to Fabrizio, for allowing me to cultivate my other big passion for music; to Gabriel, Hugo, Lorenzo, Oren, Paul, Sarah, and Sophy for making me feel so welcome during my time in Montreal.

I am grateful to my family, particularly to my parents, for their continued support of my plans, and their encouragement both before and during my studies. Without them, I probably would not have moved to Milan to study telecommunications engineering, and I would not have written this.

Finally, thank you is not enough to express how grateful I am to my partner Viviana. It's only with her endless love and support that this dissertation was possible. She was always there during tougher times. How many times did I tell you that I wanted to drop out? She made sure that I did not, and that I did not forget the lighter side of things.

## RESUMÉ

Le Software-Defined Networking (SDN) permet la programmation du réseau. Malheureusement, la technologie SDN actuelle limite la programmabilité uniquement au plan de contrôle. Les opérateurs ne peuvent pas programmer des algorithmes du plan de données tels que l'équilibrage de charge, le contrôle de congestion, la détection de pannes, etc. Ces fonctions sont implémentées à l'aide d'hardware dédié, car elles doivent fonctionner au taux de ligne, c'est-à-dire 10-100 Gbit/s sur 10-100 ports.

Dans ce travail, nous présentons deux abstractions de plan de données pour le traitement de paquets à états (stateful), OpenState et OPP. OpenState est une extension d'OpenFlow qui permet la définition des règles de flux en tant que machines à états finis. OPP est une abstraction plus flexible qui généralise OpenState en ajoutant des capacités de calcul, permettant la programmation d'algorithmes de plan de données plus avancés. OpenState et OPP sont à la fois disponibles pour les implémentations d'haute performance en utilisant des composants de commutateurs hardware courants. Cependant, les deux abstractions sont basées sur un choix de design problématique : l'utilisation d'une boucle de rétroaction dans le pipeline de traitement des paquets. Cette boucle, si elle n'est pas correctement contrôlée, peut nuire à la cohérence des opérations d'état. Les approches de verrouillage de la mémoire peuvent être utilisées pour éviter les incohérences, au détriment du débit. Nous présentons des résultats de simulations sur des traces de trafic réelles, montrant que les boucles de rétroaction de plusieurs cycles d'horloge peuvent être supportées avec peu ou pas de dégradation des performances, même avec les charges de travail des plus défavorables.

Pour mieux prouver les avantages d'un plan de données programmables, nous présentons deux nouvelles applications : Spider et FDPA. Spider permet de détecter et de réagir aux pannes de réseau aux échelles temporelles du plan de données (i.e., micro/nanosecondes), également dans le cas de pannes à distance. En utilisant OpenState, Spider fournit des fonctionnalités équivalentes aux protocoles de plans de contrôle anciens tels que BFD et MPLS Fast Reroute, mais sans nécessiter un plan de contrôle. Autrement dit, la détection et le ré-acheminement se produisent entièrement dans le plan de données.

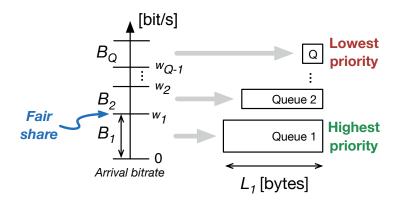

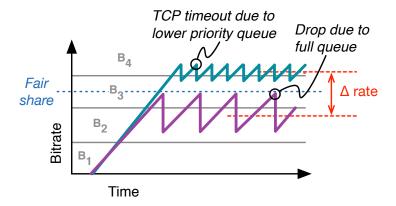

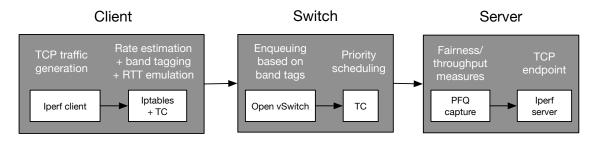

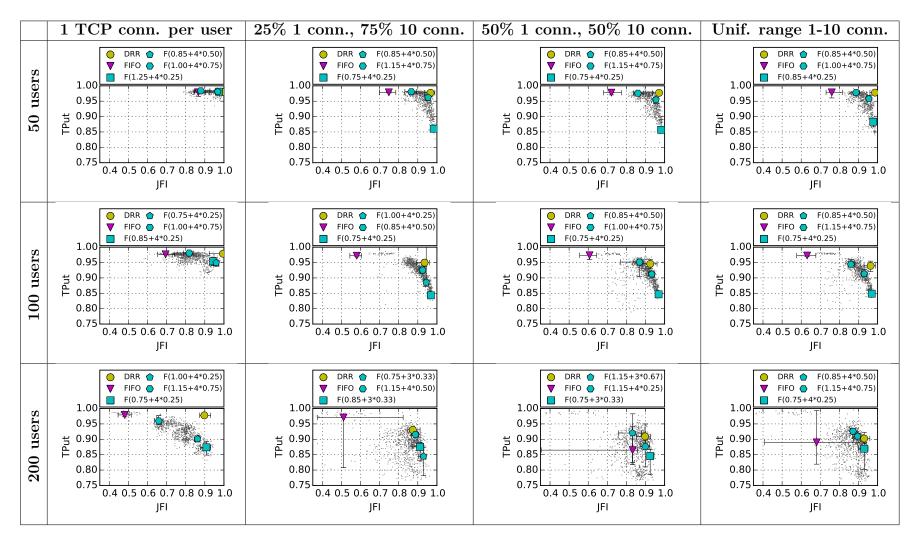

FDPA permet à un commutateur d'imposer de façon approximative une juste répartition de la bande passante entre plusieurs sources de trafic TCP. La plupart des mécanismes pour résoudre ce problème sont basés sur des algorithmes d'ordonnancement de paquets (scheduling) complexes, dont la faisabilité devient très coûteuse avec les exigences actuelles de taux de ligne. FDPA, qui est basé sur OPP, traduit la complexité de l'ordonnancement

avec l'état par utilisateur. FDPA fonctionne en assignant dynamiquement les utilisateurs à des files d'attente prioritaires, où la priorité est choisie en fonction de l'historique des taux d'émission d'un utilisateur. Les résultats expérimentaux sur un banc d'essai de 10 Gbit/s montrent que FDPA est capable de fournir une répartition juste de la bande et un débit comparable aux approches basées sur les algorithmes d'ordonnancement.

#### **ABSTRACT**

Software-Defined Networking (SDN) enables programmability in the network. Unfortunately, current SDN limits programmability only to the control plane. Operators cannot program data plane algorithms such as load balancing, congestion control, failure detection, etc. These capabilities are usually baked in the switch via dedicated hardware, as they need to run at line rate, i.e. 10-100 Gbit/s on 10-100 ports.

In this work, we present two data plane abstractions for stateful packet processing, namely OpenState and OPP. These abstractions allow operators to program data plane tasks that involve stateful processing. OpenState is an extension to OpenFlow that permits the definition of forwarding rules as finite state machines. OPP is a more flexible abstraction that generalizes OpenState by adding computational capabilities, opening for the programming of more advanced data plane algorithms. Both OpenState and OPP are amenable for high-performance hardware implementations by using commodity hardware switch components. However, both abstractions are based on a problematic design choice: to use a feedback-loop in the processing pipeline. This loop, if not adequately controlled, can represent a harm for the consistency of the state operations. Memory locking approaches can be used to prevent inconsistencies, at the expense of throughput. We present simulation results on real traffic traces showing that feedback-loops of several clock cycles can be supported with little or no performance degradation, even with near-worst case traffic workloads.

To further prove the benefits of a stateful programmable data plane, we present two *novel* applications: Spider and FDPA. Spider permits to detect and react to network failures at data plane timescales, i.e. micro/nanoseconds, also in the case of distant failures. By using OpenState, Spider provides functionalities equivalent to legacy control plane protocols such as BFD and MPLS Fast Reroute, but without the need of a control plane. That is, both detection and rerouting happen entirely in the data plane.

FDPA allows a switch to enforce approximate fair bandwidth sharing among many TCP-like senders. Most of the mechanisms to solve this problem are based on complex scheduling algorithms, whose feasibility becomes very expensive with today's line rate requirements. FDPA, which is based on OPP, trades scheduling complexity with per-user state. FDPA works by dynamically assigning users to few (3-4) priority queues, where the priority is chosen based on the sending rate history of a user. Experimental results on a 10 Gbit/s testbed show that FDPA is able to provide fairness and throughput comparable to scheduling-based approaches.

## TABLE OF CONTENTS

| DEDICA | ATION  |                                                 | iii |

|--------|--------|-------------------------------------------------|-----|

| ACKNO  | WLED   | GEMENTS                                         | iv  |

| RESUM  | ιÉ     |                                                 | vi  |

| ABSTR  | ACT .  |                                                 | iii |

| TABLE  | OF CC  | ONTENTS                                         | ix  |

| LIST O | F TABI | LES                                             | xi  |

| LIST O | F FIGU | TRES                                            | xii |

| LIST O | F ACR  | ONYMS x                                         | iv  |

| СНАРТ  | ER 1   | INTRODUCTION                                    | 1   |

| 1.1    | Contro | l plane programmability                         | 2   |

| 1.2    |        | lane programmability                            | 3   |

| 1.3    |        | ch questions                                    | 6   |

| 1.4    |        | ary of contributions and organization of thesis | 6   |

| СНАРТ  | ER 2   | ABSTRACTIONS FOR STATEFUL DATA PLANES           | 8   |

| 2.1    | OpenS  | tate                                            | 8   |

|        | 2.1.1  | Abstraction                                     | 9   |

|        | 2.1.2  | From state machines to pipelines                | 11  |

|        | 2.1.3  |                                                 | 21  |

|        | 2.1.4  |                                                 | 24  |

| 2.2    | Open 1 |                                                 | 25  |

|        | 2.2.1  |                                                 | 26  |

|        | 2.2.2  |                                                 | 27  |

|        | 2.2.3  | •                                               | 29  |

|        | 2.2.4  |                                                 | 32  |

|        | 2.2.5  | ·                                               | 36  |

| 2.3    |        |                                                 | 37  |

|        | 2.3.1  | · · ·                                           | 38  |

|        | 2.3.2  | Measuring the risk of data hazards           | 41  |

|--------|--------|----------------------------------------------|-----|

|        | 2.3.3  | Preventing data hazards via memory locking   | 44  |

|        | 2.3.4  | Discussion                                   | 48  |

|        | 2.3.5  | Remarks                                      | 55  |

| 2.4    | Relate | ed work                                      | 55  |

| 2.5    | Conclu | usions                                       | 61  |

|        | 2.5.1  | Future work                                  | 63  |

| СНАРТ  | ΓER 3  | APPLICATION: FAULT RESILIENCE                | 65  |

| 3.1    | Introd | uction                                       | 65  |

| 3.2    | Relate | ed work on fault resilience in SDN           | 66  |

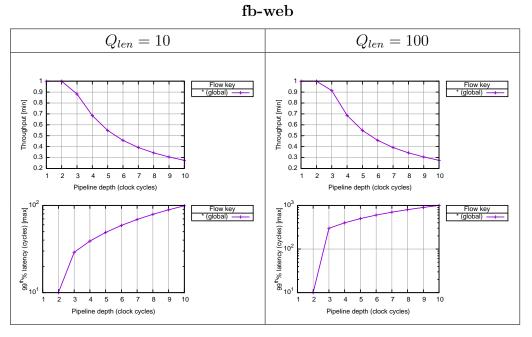

| 3.3    | Spider | approach sketch                              | 68  |

| 3.4    |        | ${ m mentation}$                             | 70  |

| 3.5    | Perfor | mance evaluation                             | 75  |

| 3.6    | Discus | ssion                                        | 81  |

|        | 3.6.1  | Comparison with BFD                          | 81  |

|        | 3.6.2  | Comparison with MPLS Fast Reroute            | 83  |

|        | 3.6.3  | Data plane reconciliation                    | 84  |

|        | 3.6.4  | P4-based implementation                      | 86  |

| 3.7    | Conclu | usions                                       | 87  |

| СНАРТ  | ΓER 4  | APPLICATION: FAIR BANDWIDTH SHARING          | 88  |

| 4.1    | Introd | uction                                       | 88  |

| 4.2    | Relate | ed work on enforcing fair bandwidth sharing  | 90  |

| 4.3    | FDPA   | design                                       | 91  |

|        | 4.3.1  | Rationale                                    | 91  |

|        | 4.3.2  | Implementation with programmable data planes | 93  |

| 4.4    | Exper  | imental results                              | 94  |

| 4.5    | Discus | ssion                                        | 98  |

| 4.6    | Conclu | usions                                       | 99  |

| СНАРТ  | ΓER 5  | CONCLUSION                                   | 100 |

| PREVI  | OUSLY  | PUBLISHED MATERIAL                           | 103 |

| BIBLIC | GRAP   | HY                                           | 104 |

# LIST OF TABLES

| Table 2.1 | Parameters of the OPP hardware prototype                          | 33 |

|-----------|-------------------------------------------------------------------|----|

| Table 2.2 | Hardware cost comparison of OPP, NetFPGA SUME ref. switch and     |    |

|           | OpenState                                                         | 33 |

| Table 2.3 | ALU basic instruction set                                         | 35 |

| Table 2.4 | ALU advanced instruction set                                      | 35 |

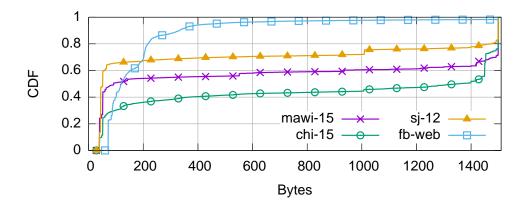

| Table 2.5 | Packet traces used in simulations                                 | 41 |

| Table 2.6 | Area and minimum critical-path delay of one comparator            | 47 |

| Table 2.7 | Clock cycle budget (and latency) when using memory locking        | 49 |

| Table 3.1 | Summary of the configurable state timeouts of the Spider pipeline | 76 |

| Table 3.2 | Number of flow entries per node                                   | 76 |

## LIST OF FIGURES

| Figure 2.1            | FSM of the port knocking example                                          | 10       |  |  |

|-----------------------|---------------------------------------------------------------------------|----------|--|--|

| Figure 2.2            | State Table, FSM table, and packet handling for the port knocking example |          |  |  |

| Figure 2.3            | Abstract pipeline model of a stateful processing block in OpenState.      | 12<br>14 |  |  |

| Figure 2.4            | OpenState configuration of the port-knocking example                      | 16       |  |  |

| Figure 2.4 Figure 2.5 |                                                                           | 17       |  |  |

| 0                     | OpenState configuration to implement a L2 learning switch                 | 18       |  |  |

| Figure 2.6            | Simplified configuration of a L2 learning switch                          |          |  |  |

| Figure 2.7            | OpenState configuration to implement a flowlet-based load balancer.       | 20       |  |  |

| Figure 2.8            | Logical pipeline of a stateful block in OpenState                         | 23       |  |  |

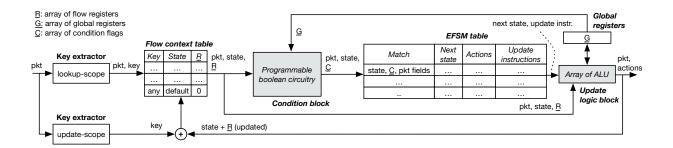

| Figure 2.9            | Abstract pipeline model of an OPP processing block                        | 28       |  |  |

| Figure 2.10           | OPP configuration to implement detection of long-lived flows              | 30       |  |  |

| Figure 2.11           | OPP configuration to implement a flowlet-based load balancer              | 30       |  |  |

| Figure 2.12           | OPP configuration to implement priority queuing based on rate esti-       |          |  |  |

|                       | mation                                                                    | 31       |  |  |

| Figure 2.13           | Programmable data plane architecture                                      | 39       |  |  |

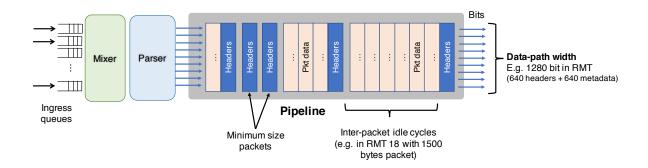

| Figure 2.14           | Processing of a RMT-like pipeline. Packets are read from input ports      |          |  |  |

|                       | in chunk of 80 bytes. Longer packets cause idle cycles in the pipeline.   | 41       |  |  |

| Figure 2.15           | Packet size cumulative distribution                                       | 42       |  |  |

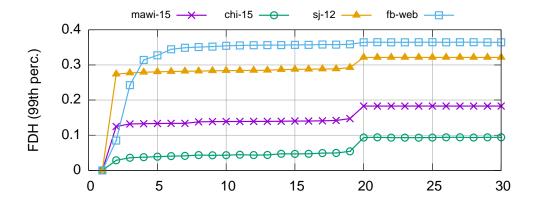

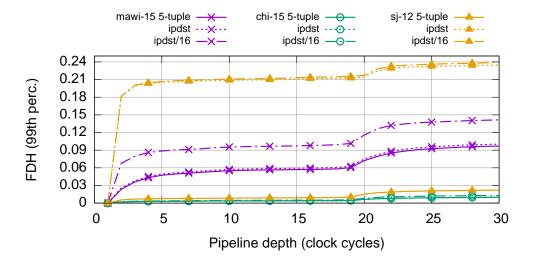

| Figure 2.16           | Fraction of data hazards (FDH) w.r.t. increasing pipeline depth when      |          |  |  |

|                       | all packets are considered belonging to the same flow                     | 45       |  |  |

| Figure 2.17           | Fraction of data hazards (FDH) w.r.t. increasing pipeline depth when      |          |  |  |

|                       | aggregating packets per different flow keys                               | 45       |  |  |

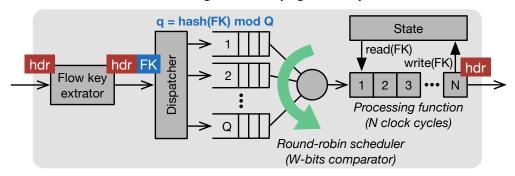

| Figure 2.18           | Architecture of a stateful processing block with memory locking           | 46       |  |  |

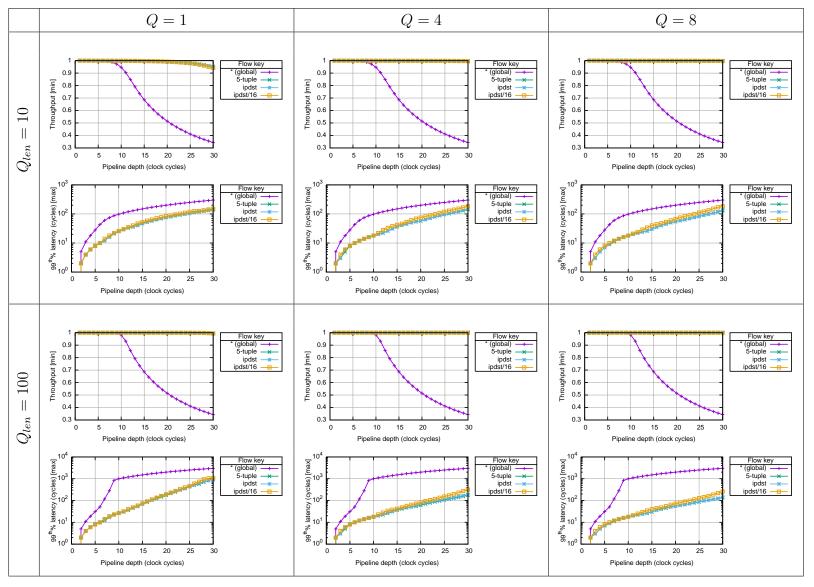

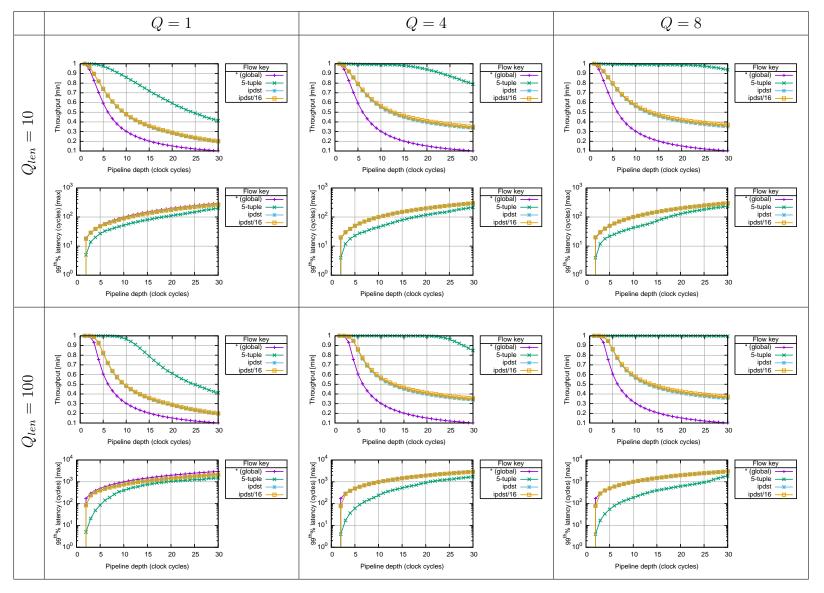

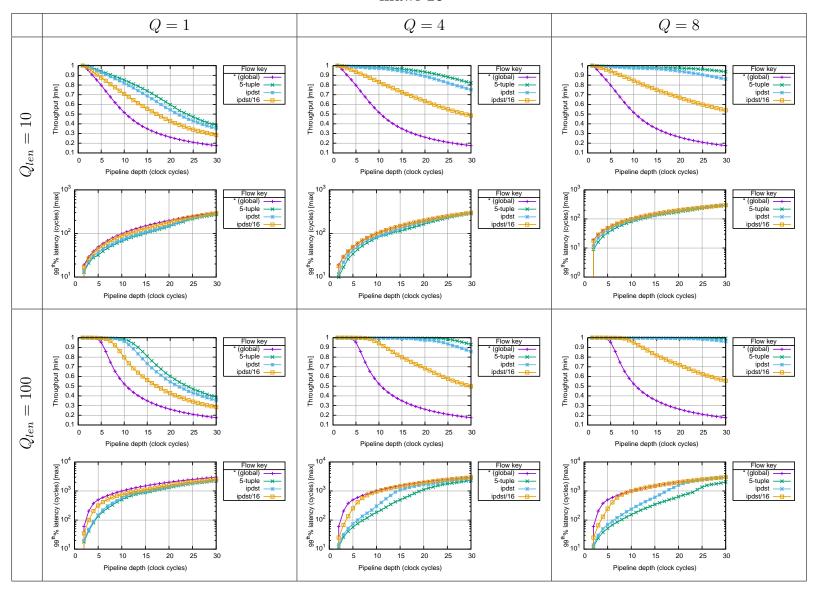

| Figure 2.19           | Throughput and latency for the $chi$ -15 traffic trace                    | 50       |  |  |

| Figure 2.20           | Throughput and latency for the $sj-12$ traffic trace                      | 51       |  |  |

| Figure 2.21           | Throughput and latency for the $mawi-15$ traffic trace                    | 52       |  |  |

| Figure 2.22           | Throughput and latency for the $fb$ -web traffic trace                    | 53       |  |  |

| Figure 3.1            | Example of the different forwarding behaviors implemented by Spider.      | 67       |  |  |

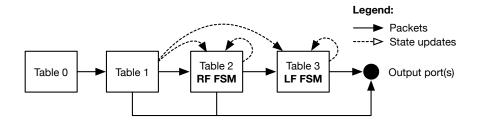

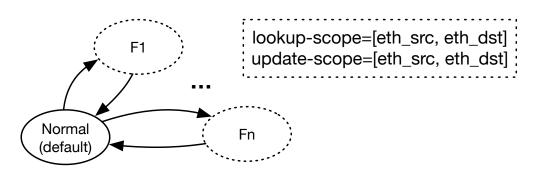

| Figure 3.2            | Spider pipeline architecture                                              | 71       |  |  |

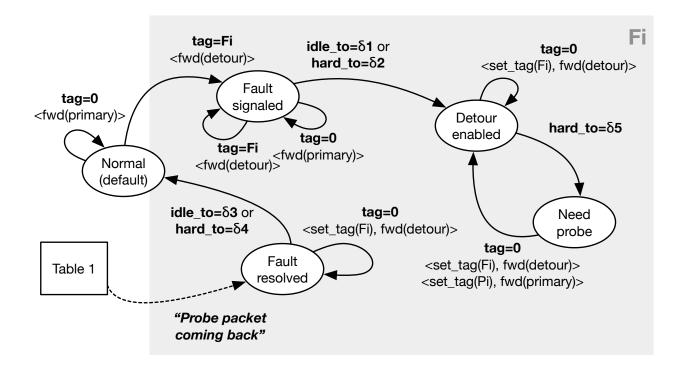

| Figure 3.3            | Macro states of the Remote Failover process                               | 72       |  |  |

| Figure 3.4            | Detail of the macro state Fi for the Mealy Machine of the Remote          |          |  |  |

|                       | Failover process                                                          | 73       |  |  |

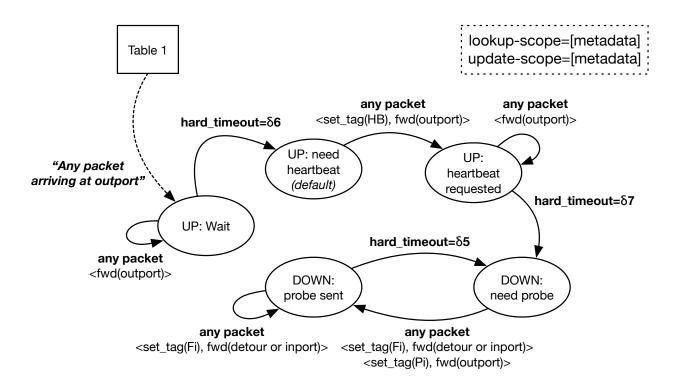

| Figure 3.5            | Mealy machine of the Local Failover process                               | 74       |  |  |

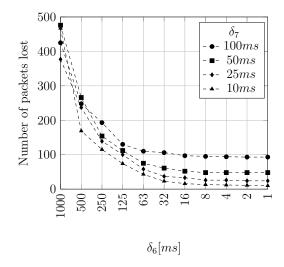

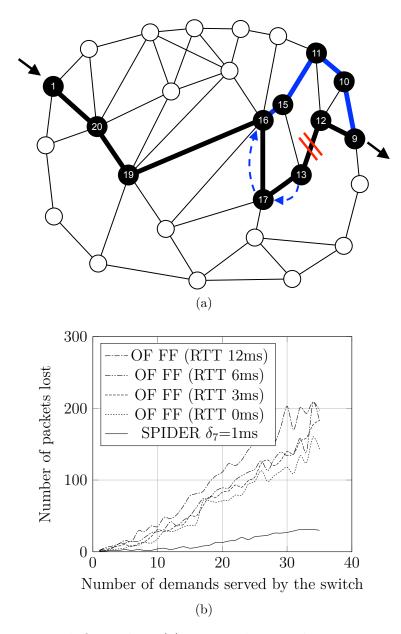

| Figure 3.6 | Packet loss (data rate $1000 \ pkt/sec$ )                                          | 78 |

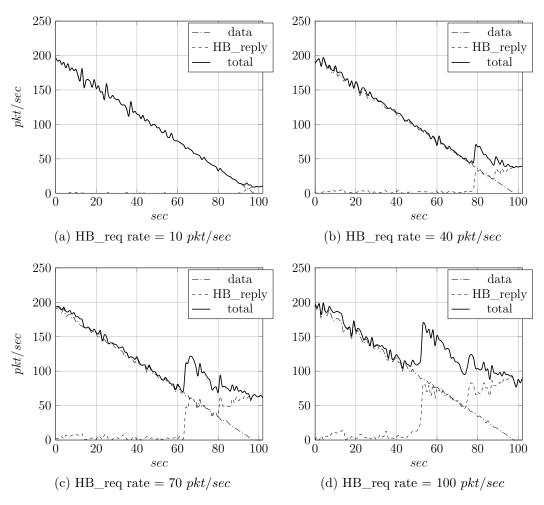

|------------|------------------------------------------------------------------------------------|----|

| Figure 3.7 | Heartbeat overhead with decreasing data traffic                                    | 79 |

| Figure 3.8 | ${\bf Comparison\ of\ Spider\ with\ an\ OpenFlow-based\ reactive\ implementation}$ | 80 |

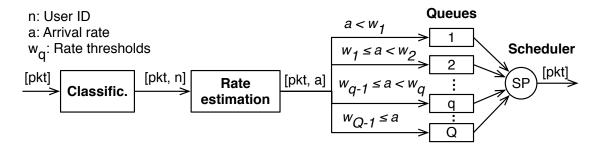

| Figure 4.1 | FDPA forwarding pipeline                                                           | 92 |

| Figure 4.2 | Rate bands and queue size in FDPA                                                  | 92 |

| Figure 4.3 | Example of 2 TCP sources competing for the excess bandwidth when                   |    |

|            | using more than 2 priorities                                                       | 94 |

| Figure 4.4 | Software-based processing pipeline used in experiments                             | 94 |

| Figure 4.5 | FDPA experimental results                                                          | 97 |

# LIST OF ACRONYMS

| ACL  | Access Control List                          |  |  |  |

|------|----------------------------------------------|--|--|--|

| ALU  | Arithmetic Logic Unit                        |  |  |  |

| API  | Application Programming Interface            |  |  |  |

| AQM  | Active Queue Management                      |  |  |  |

| ASIC | Application-Specific Integrated Circuit      |  |  |  |

| BDP  | Bandwidth-Delay Product                      |  |  |  |

| BFD  | Bidirectional Forwarding Detection (protocol |  |  |  |

| BGP  | Border Gateway Protocol                      |  |  |  |

| CAM  | Content-Addressable Memory                   |  |  |  |

| CPU  | Central Processing Unit                      |  |  |  |

| DPI  | Deep Packet Inspection                       |  |  |  |

| DRAM | Dynamic Random-Access Memory                 |  |  |  |

| DRR  | Deficit Round Robin                          |  |  |  |

| DSCP | Differentiated Services Code Point           |  |  |  |

| DSP  | Digital Signal Processor                     |  |  |  |

| ECMP | Equal-Cost Multi Path                        |  |  |  |

| EFSM | Extended Finite-State Machine                |  |  |  |

| FDPA | Fair Dynamic Priority Assignment             |  |  |  |

| FF   | Fast-Failover (OpenFlow)                     |  |  |  |

| FIFO | First In First Out                           |  |  |  |

| FPGA | Field-Programmable Gate Array                |  |  |  |

| FQ   | Fair Queuing                                 |  |  |  |

| FRR  | Fast-Reroute (MPLS)                          |  |  |  |

| FSM  | Finite-State Machine                         |  |  |  |

| GPU  | Graphic Processing Unit                      |  |  |  |

| IETF | Internet Engineering Task Force              |  |  |  |

| IP   | Internet Protocol                            |  |  |  |

| IR   | Intermediate Representation                  |  |  |  |

| ISP  | Internet Service Provider                    |  |  |  |

| LPM  | Longest-Prefix Match                         |  |  |  |

| LSP  | Label-Switched Path (MPLS)                   |  |  |  |

| LSR  | Label Switch Router (MPLS)                   |  |  |  |

| LUT  | LookUp Table (FPGA)                          |  |  |  |

MAT Match+Action Table

MPLS MultiProtocol Label Switching

MTU Maximum Transmission Unit

NAT Network Address Translation

NFV network Function Virtualization

NIC Network Interface Card

NPU Network Processing Unit

OPP Open Packet Processor

OSPF Open Shortest Path First

RAM Random-Access Memory

RFC Request For Comment (IETF)

RISC Reduced Instruction Set Computer

RMT Reconfigurable Match Table

RSVP Resource Reservation Protocol

RTT Round Trip Time

SDN Software-Defined Networking

SFQ Stochastic Fair Queuing

SRAM Static Random-Access Memory

SSH Secure Shell

TCAM Ternary Content-Addressable Memory

TCP Transmission Control Protocol

TPU Tensor Processing Unit

UDP User Datagram Protocol

VNF Virtual Network Function

## CHAPTER 1 INTRODUCTION

Networking technologies have undergone a major revolution in recent years. Both academia and industry have worked to make networks more open and programmable. Open, as opposed to the traditional closed paradigm, where network equipment vendors develop both proprietary hardware and software, bundled together in the same black box, hard to change once deployed. Programmable, to give system owners the possibility to code their needs, instead of relying on the slow development cycles adopted by vendors to add support for new protocols and services.

Software-Defined Networking (SDN) has been the epicenter of this revolution. SDN is based on the simple idea of decoupling the control plane from the forwarding devices' data plane. Abstracting networks into separate planes is a convenient way of reasoning about network programmability. The data plane is the one responsible for the forwarding of packets, i.e. the circuitry necessary to move (or drop) packets between ports of the same device. The control plane is where the network-level intelligence is implemented, i.e. decide which devices and ports a packet should be sent through to implement a given network policy, such as routing or security.

The two planes have different operative requirements that significantly affect how programmability is enabled. The data plane needs to process packets as fast as possible. Today's line rate requirements are 10–100 Gbit/s on 10–100 ports. For this reason, the data plane is also called the fast-path. Such high-performance requirements call for implementations based on dedicated hardware, such as ASIC, network processors (NPU), or FPGAs. In contrast, the control plane can operate at lower speeds, but it needs to perform relatively complex computations, e.g. find the best path in BGP. As a consequence, implementations favor general purpose CPUs and high-level languages such as C, Java or Python.

SDN was first introduced to enable programmability of the control plane. Indeed, SDN abstracts the data plane by means of an Application Programming Interface (API). Software running on the control plane can use such API to instruct the devices on how to forward packets. SDN's primary challenge was that of convincing network equipment vendors to open their boxes and provide such APIs to operators, to let them implement their own control software, i.e. convince vendors to abandon a generous stream of revenues. Clearly, a daunting task. However, challenges in the data plane are of a different nature, as they relate to the inherent technical complexity of making high-performance architectures programmable. This thesis is about mechanisms to enable programmability in the data plane. However,

before deepening into this topic, it is useful to discuss how control planes have been made programmable.

## 1.1 Control plane programmability

SDN builds upon the observation that most protocols, e.g. OSPF, BGP, etc. all define similar mechanisms to distribute state such as the network topology and other metadata (e.g. link utilization). Decisions on where to forward packets are then taken independently from each device, according to a given routing logic that looks at the distributed network state. The result is a plethora of standard protocols, such as IETF's RFCs (more than 8000 at the time of writing). RFCs, apart from describing ideas on how to improve networks, specify in plain English language (sometimes ambiguously) the expected behavior that the control plane of a device should implement to support a given protocol. It comes that most protocol designers had to repeat the same effort over and over to develop and debug complex state distribution mechanism for each protocol. Similarly, software engineers from different vendors had to produce many similar implementations of these specifications for the control plane of many different network devices.

In SDN, the control plane resides in a logically centralized software external to the switches, usually running on commodity servers called "controllers". A controller communicates with many devices' data plane using a forwarding API. OpenFlow [5] is a prominent instance of such an API. It is a standardized open protocol that abstracts the data plane as match+action tables (MAT). Controllers can instruct devices on where to forward packets by installing entries in the devices' MAT. Each MAT entry specifies a match, used to identify a slice of traffic, and an action that specifies processing to apply to matching packets, such dropping or forwarding to one or more ports, placing packets in output queues, and modifications to header fields.

The motivation of creating OpenFlow as an open protocol is that switches can be developed to be vendor-agnostic, greatly simplifying the work of control plane writers who can now reuse principles common in software engineering. Indeed, given the initial SDN observation and the assumption of a data plane API common to all vendors, most software engineers would end up with the same conclusion: (i) write a distributed data store to maintain an updated view of the network topology and other metadata; (ii) make it fault tolerant and scalable by replicating the data onto multiple machines; (iii) write it once and reuse it over and over for many protocols. Now, protocol developers do not have to worry about writing each time a new state distribution mechanism or a standard binary protocol. This is the purpose of today's network operating systems (OS) such as ONOS [6], OpenDaylight [7], RYU [8], and

many others. They provide high-level APIs to application developers, such as an updated topology view, monitoring primitives, hooks for link/node failure events, and other services that make far easier the implementation of networking applications, such as routing, security or virtualization. That is, operators of an SDN network can incrementally add support for new services or optimize existing ones by writing high-level software operating on a data structure, running on top of a network OS, instead of designing and standardizing a complex distributed protocol, finally waiting for equipment vendors to adopt it.

The aftermath of SDN and OpenFlow is a vendor-agnostic architecture that has profoundly changed the market. On one side, switching silicon suppliers are let free to focus on improving performance and resources of their chips, i.e. more throughput and memory. On the other end, third-party companies, or even network owner themselves, who develop the software needed to control these chips. Today one can buy so called "white-box" off-the-shelf switches at a cheaper price compared to that of traditional vendors. These switches are equipped with generic hardware and are shipped without any protocol implementation, one can then decide to run it using a free open source network OS.

### 1.2 Data plane programmability

Even if some ideas on programmable networking have been researched for nearly two decades [9], it is fair to say that OpenFlow is the technology which brought SDN to the real world. Quoting [9], "Before OpenFlow, the ideas underlying SDN faced a tension between the vision of fully programmable networks and pragmatism that would enable real-world deployment. OpenFlow struck a balance between these two goals by enabling more functions than earlier route controllers and building on existing switch hardware, through the increasing use of merchant-silicon chipsets in commodity switches".

The OpenFlow's MAT abstraction proved to be valuable in describing *commonality* between many existing packet forwarding technologies. Switching chips were already designed using dedicated *tables* for tasks such as L2 learning, L3 longest-prefix match (LPM) routing, or access control lists (ACL). As a result, vendors were able to implement an OpenFlow interface on top of their existing switching chips, making their devices marketable for the new SDN market.

However, network switches perform many tasks in addition to standard packet forwarding, such as load balancing, to make a more efficient use of network paths; rate control and active queue management (AQM), to reduce network congestion; scheduling, to provide QoS and fairness; fine-grained measurements, to let network OSs take better decisions on where

to route packets; failure detection, to promptly reroute premium customers' traffic, etc. Differently from packet forwarding, these tasks read and write state maintained at the switch as part of the packet processing that happens in the fast-path. For this reason, we can refer to these tasks as *stateful data plane algorithms*. Today these algorithms are implemented in switching chips using dedicated hardware and cannot be changed by network operators.

Making stateful data plane algorithms programmable in switching chips would bring a number of benefits.

- 1. Optimize existing algorithms, research new ones. The lesson about SDN and OpenFlow teaches us that operators like to have finer control of their network, instead of relying on equipment vendors to listen to their requests to modify existing functions or implement new ones. Moreover, programmable switching chips would allow researchers to experiment new ideas on high-performance hardware, instead of relying on expensive ASIC design, time-consuming FPGA-based implementations, inaccurate and long simulations, or low-performance software-based emulation.

- 2. Lower the control burden on the SDN controller. OpenFlow forces a "twotiered" programming model: any stateful processing intelligence is delegated to the controller, whereas switches limit to install and enforce stateless packet forwarding rules delivered by the controller. Centralization of the network applications' intelligence turns out to be an advantage for all those applications where changes in the forwarding state do not have strict real time requirements, and depend upon global network state. But for applications which rely only on local flow or port states, the latency toll imposed by the reliance on an external controller cannot meet the requirements of high-performance networks [10]. Example of such applications are those that forward packets based on the status of a port, e.g. rerouting upon detection of a link that is down or congested, or applications that forward packets differently based on the state of a TCP connection, e.g. stateful ACLs that allow outbound connections, but not inbound. Adding support for programmable states in OpenFlow would allow for a more efficient implementation of these applications, without being affected by the latency and overhead imposed by the controller intervention. Interestingly, data center operators have already reported on the benefits of adopting a MAT-based programming model capable of using connection state as a base primitive, rather than just packets [11].

- 3. Offload of middlebox processing functions to the network. Following the programmability trend, stateful network functions commonly implemented using hardware middleboxes, are being transformed in virtualized software appliances that run on com-

modity servers [12]. Network operators are supporting this trend [13], usually called Network Function Virtualization (NFV) [14]. Virtual network functions (VNFs) have a number of advantages when compared to legacy hardware ones. They can be dynamically created, updated, migrated and run on commodity servers. However, developing VNFs on general purpose CPUs is a hard task [15]. Indeed, a commodity server is usually equipped with a couple of 10 Gbit/s network interfaces, and 40 Gbit/s interfaces are becoming common. Unfortunately, current general purpose CPUs speed is not growing as fast as the network interfaces speed [16]. Therefore, a switching chip with support for the programming of custom stateful processing tasks, would permit the offloading of some or all the processing to the server NICs [11] or to the network nodes, thus permitting VNFs to support larger traffic volumes, at a lower cost.

There is no reason why programmability should not be extended to the full spectrum of tasks performed by the data plane, even those requiring to access and modify state at each packet. A major concern is the feasibility of such a programmable *stateful* data plane. Indeed, state-of-the-art fixed-function switching chips are required to operate at line rate, i.e. 10–100 Gbit/s on 10–100 ports, likely more in the future. Programmability should not be introduced at the expenses of performance.

Luckily, silicon manufacturers are already producing programmable switching chips [17, 18, 19] competitive in performance with state-of-the-art fixed-function chips. These chips provide low-level primitives that can be configured with software to add support for arbitrary protocol headers and forwarding actions, i.e. a programmer is not restricted to a subset of L2-L4 headers as in OpenFlow, but she can program the switch to parse new, non-standard headers with arbitrary length and structure; he can also define custom actions to modify the parsed headers.

While these programmable chips greatly improve the flexibility of the forwarding tasks, they ignore or address only marginally the problem of programming stateful data plane algorithms. Some [20, 18] limits *statefulness* to dedicated, i.e. not programmable, functions, such as counters or metering. Others [17, 19], in order to guarantee the forwarding of packets at line rate, offer limited support [11]: have limited memory for state, support limited types of operations, and limit the type of per-packet computation.

The design of a switching chip is usually optimized to contain its area and power consumption. Seminal work on Reconfigurable Match Tables (RMT) [20], while addressing the case of a *stateless* programmable chip, proved an important result: the improved flexibility of the forwarding circuitry comes at an additional cost of less than 15% in chip area and power consumption when compared to a similar fixed-function chip. 80% of chip area is due to

memory (TCAMs and the IO/buffer/queue subsystem), and less than 20% area is due to logic. Hence, as a rule of thumb, if we would like to add more programmable processing logic to execute stateful tasks, that would be unlikely constrained by chip area or power consumption.

Despite the recent advances in programmable switching chips and the promising RMT result, the feasibility of a programmable data plane that is optimized for the programming of stateful data plane algorithms, is still an open question.

## 1.3 Research questions

In this thesis we address the following research questions:

- 1. Can we devise an abstraction for a programmable data plane that is specifically targeted for stateful packet processing?

- 2. Would this abstraction be feasible at line rate?

- 3. Is there a tradeoff between programmability and performance in packet processing? If yes, is there a sweet spot that maximizes both?

- 4. Which new applications would be enabled by such programmable data plane?

#### 1.4 Summary of contributions and organization of thesis

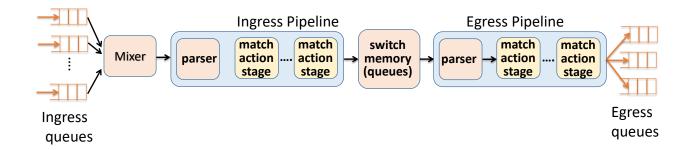

The remainder of this thesis is organized as follows. In Chapter 2, we present two abstractions to program stateful data plane algorithms: OpenState and Open Packet Processor (OPP). OpenState has been designed as an extension to OpenFlow and allows the description of forwarding rules as finite state machines (FSM) operating on per-flow state, maintained by the switch and updated as a consequence of packet-level and timeout events. We show how OpenState can be supported in hardware with minimal extension to an ordinary OpenFlow, TCAM-based, hardware pipeline. However, OpenState allows to describe a very limited set of applications. To solve this problem, we propose OPP. Building upon OpenState, OPP enables more programmability by permitting the description of packet processing tasks using Extended Finite State Machines (EFSM). Relative to OpenState, OPP adds support for the evaluation of conditions on state, arbitrary custom registers, and support for arithmetic and logic operations. We then discuss the hardware feasibility of OPP, which similarly to OpenState, can be realized with commodity switch hardware components.

The design of both OpenState and OPP is characterized by a feedback-loop architecture that might generate state inconsistencies when processing traffic at high-rates. Preventing such inconsistencies via memory locking introduces a tradeoff between programmability and performance. We analyze this tradeoff by running simulations on real traffic traces from both carrier and data center networks. We find that, in most of the cases, the risk of incurring in such inconsistencies is low. We design a scheme to perform memory locking in a packet forwarding pipeline. We show that even long complex operations (up to 30 clock cycles per packet) affect throughput only marginally, at the cost of extra processing latency in the order of hundreds of nanoseconds.

The rest of the thesis describes two *novel* applications of programmable stateful data planes.

In Chapter 3, we present Spider, a data plane scheme that provides (i) detection of failures based on switches' periodic link probing and (ii) fast reroute of traffic flows even in the case of distant failures. Spider is inspired by legacy control plane protocols such as Bidirectional Forwarding Detection (BFD) and MPLS Fast Reroute. Differently from these protocols, Spider performs detection and rerouting entirely in the fast-path. It offers guaranteed, short (few microseconds or less) failure detection and recovery delays, with a configurable tradeoff between probing overhead and failover responsiveness. We provide an analysis on flow tables' memory impact, and experimental results on its performance in terms of recovery latency and packet loss.

In Chapter 4, we present FDPA, a data plane scheme to enforce fair bandwidth sharing of the same link among many TCP-like senders. Most of the mechanisms to solve this problem are based on complex scheduling algorithms, whose feasibility becomes very expensive with today high-throughput requirements. We propose a scheme that does not modify the scheduler. FDPA enforce fairness by dynamically assigning traffic flows to an existing strict priority scheduler, based on the users' rate history, where rate estimation is performed using OPP capabilities. We conducted experiments on a physical 10 Gbit/s testbed with real TCP traffic. Results show that FDPA produces fairness comparable to approaches based on scheduling.

#### CHAPTER 2 ABSTRACTIONS FOR STATEFUL DATA PLANES

#### 2.1 OpenState

OpenFlow is a stateless data plane abstraction. Changes of the forwarding rules do not depend on the history of packets seen by the switch, rather, forwarding rules can be update only via the explicit involvement of an external controller. The latter implements stateful processing intelligence, i.e. decides how rules should evolve in time as a consequence of events, either generated at the data plane or external. The explicit involvement of the controller for any stateful task and for any update of the match+action rules, is problematic as it imposes excessive overheads [10]. Centralization of the stateful intelligence is an advantage for all those applications where changes do not have strict real time requirements, and depend upon global network states. But for applications relying only on local flow or port states, the reliance on an external controller for any update seems a very inefficient design choice. In the worst case, the slow control plane operations a priori prevents the support of network control algorithms which require prompt, real time reconfiguration of the data plane.

To solve this problem, we propose OpenState, an extension to OpenFlow that adds support for *stateful* forwarding behaviors. OpenState is based on the observation that many networking applications can be expressed as switch-local state machines operating on *flow-state*, i.e. state that is unique to each flow, where the definition of a flow is left to the programmer's choice, e.g. all packets belonging to the same IP source-destination address, or the same TCP/UDP 5-tuple. OpenState allows to program in the switch any networking tasks that can be modeled using a formal finite state machine abstraction called "Mealy Machine". While OpenState does not permit to describe *any* stateful data plane algorithm, it is important because it sets the basic requirements for a programmable packet processing architecture to support said stateful behaviors.

OpenState provides a new forwarding API for SDN. The design of such API builds upon the observation that the *very same* OpenFlow MAT primitives can be reused for a different goal and with a broadened semantic. In a nutshell, OpenState permits to i) perform matches on packet header fields plus a flow-state label maintained by the switch, and ii) associate to such match both a forwarding action (or set of actions) and a *state transition*, which determines the flow-state that will be visible to the next packet of the same flow. The immediate result is a forwarding behavior that depends on the history of packets seen by the switch.

The design of OpenState is based on two fundamental principles that follow the design of

#### OpenFlow itself:

- The abstraction must be amenable to high speed implementation, i.e. 10-100 Gbit/s on 10-100 ports.

- The abstraction must not violate the vendor-agnostic principle which has driven the OpenFlow invention, and that has fostered SDN, i.e. it must not emerge as a lowlevel technical approach, rather it should leave space to switch vendors to optimize and differentiate their implementations.

#### 2.1.1 Abstraction

#### An illustrative example: port knocking

A very descriptive example of an application that would benefit of a stateful data plane abstraction is that of a port knocking firewall, a well known method for opening a port on a server otherwise inaccessible. A host that wants to establish a connection (say an SSH session, i.e., port 22) delivers a sequence of packets addressed to an ordered list of pre-specified closed ports, say ports 5123, 6234, 7345 and 8456. Once the exact sequence of packets is received, the firewall opens port 22 for the considered host. Before this event, all packets including the knocking ones are dropped.

As any other stateful application, such an operation cannot be configured *inside* an OpenFlow switch, but must be implemented in an external controller. The price to pay is that a potentially large amount of signaling information (in principle up to all packets) must be conveyed to the controller. Moreover, a timely flow-mod command<sup>1</sup> from the controller is needed to open port 22 after a correct knocking sequence, to avoid that the first legitimate SSH packet finds port 22 still closed. Implementing this application in the logically centralized controller brings no gain: it does not benefit from network-wide knowledge or high level security policies, but uses just local states associated to specific flows on a single specific device. It is then reasonable to devise an abstraction to program the port knocking algorithm in the switch itself.

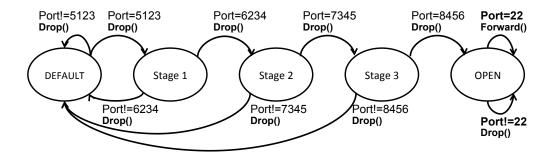

The port knocking behavior can be modeled as follows: each host is associated with the FSM illustrated in Figure 2.1. Starting from a DEFAULT state, each correctly knocked port will cause a transition to a series of three intermediate states, until a final OPEN state is reached. Any knock on a port different from the expected one will bring back to the DEFAULT state. When in the OPEN state, packets addressed to port 22 (and only to this port) will be

$<sup>^{1}\</sup>mathrm{A}$  flow-mod is message in the OpenFlow protocol to add, modify or remove MAT entries.

Figure 2.1 FSM of the port knocking example.

forwarded, whereas all remaining packets will be dropped, but without resetting the state to DEFAULT.

A closer look at Figure 2.1 reveals that each state transition is caused by an *event*, which specifically consists in a packet *matching* a given port number. Moreover, each state transition caused by a match event, is associated to a forwarding *action* (in the example, drop or forward). A state transition thus reminds very closely an OpenFlow match+action rule.

### **Mealy Machines**

The match which specifies an event not only depends on packet header information, but also depends on the state; using the above port knocking example, a packet with destination port 22 is associated to a forward action when in the OPEN state, but to a drop action when in any other state. Moreover, the event not only causes an action, but also a transition to a next state (including self-transitions from a state to itself).

All this can be modeled in an *abstract* form by means of Mealy finite-state Machine, or simply Mealy Machine<sup>2</sup> [21]. Formally, a Mealy Machine is an abstract model comprising a 4-tuple  $\langle S, I, O, T \rangle$  where:

- S is a finite set of states;

- I is a finite set of input symbols (events);

- O is a finite set of output symbols (actions); and

- $T: S \times I \to S \times O$  is a transition function which maps  $\langle \text{state}, \text{ event} \rangle$  pairs into  $\langle \text{next-state}, \text{ action} \rangle$  pairs.

<sup>&</sup>lt;sup>2</sup>Classical theory on state machines makes a distinction between a Mealy Machine and a Moore Machine. A Mealy Machine associates outputs with transitions, while a Moore Machine associates outputs with states.

Such an abstract model can be made concrete by restricting the set O of actions to those available in current OpenFlow devices, and by restricting the set I of events to OpenFlow matches on header fields and metadata easily implementable in hardware platforms. The finite set of states S (concretely, state labels, i.e., bit strings), and the relevant state transitions, in essence the "behavior" of a stateful function, are left to the programmer's choice.

In the following we will loosely refer to a Mealy Machine simply as a FSM.

#### 2.1.2 From state machines to pipelines

#### State management

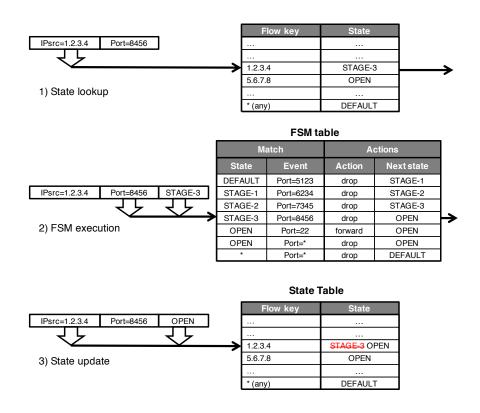

Matches in OpenFlow are generically collected in flow tables. The discussion carried out so far recommends to *clearly* separate the matches which define *events* (matching on the destination port in the port knocking example) from those which define *flows*, meant as entities which are attributed a state (each host IP address in the port knocking example). Two distinct tables, **State Table** and **FSM table**, and three logical steps thus naturally emerge for handling a packet (Figure 2.2):

- 1. **State lookup**: It consists in querying the state table using as key the packet header field(s) which identifies the flow, for instance the source IP address; if a state is not found for a queried flow, we can assume that a DEFAULT state is returned;

- 2. **FSM execution**: The retrieved state label, added as metadata to the packet, is used along with the header fields involved in the event matching (e.g., port number), to perform a match on the FSM table, which returns i) the associated actions, and ii) the label of the next state;

- 3. **State update**: It consists in rewriting or adding a new entry to the state table using the provided next state label.

The example in Figure 2.2 shows how the port knocking example is supported by the proposed approach. The 7 entries in the FSM table implement the port knocking state machine. Assuming the arrival of a packet from host 1.2.3.4; the state lookup (top figure) permits to retrieve the current state, STAGE-3. Via the FSM table (middle figure), we determine that this state, along with the knocked port 8456, triggers a drop action and a state transition to OPEN (middle figure). The new state is written (bottom figure) back in the state table for the host entry. In the FSM table, we assume an ordered matching priority, with the last row having the lowest priority. As a result, all the four transitions to the default state for

Figure 2.2 State Table, FSM table, and packet handling for the port knocking example.

packets not matching the expected knocked port are coalesced in the last entry. A notable characteristic of the proposed solution is that the length of the tables is proportional to the number of flows (state table) and number of states (FSM table), but *not* to their product.

The above described abstraction still misses a fundamental further step: how to extract the flow key from a packet? To this purpose, we have to conceptually separate the *identity* of the flow to which a state is associated, from the actual *position* in the header field from which such an identity is retrieved. Moreover, as further motivated in Section 2.1.2, we find useful to distinguish between two keys: lookup key, and update key, used respectively to read and write values in the state table. Thus, we need to provide the programmer with the ability to use eventually different header fields in these two accesses to the state table. We define as *lookup-scope* and *update-scope* the ordered sequence of header fields that shall be used to produce the key used to access the state table. In the port knocking example lookup\_scope = update scope = [ipsrc].

To summarize, the basic data plane abstraction introduced so far comprises the specification of:

1. an FSM table comprising four columns: i) a state, ii) an event expressed as an Open-

Flow ternary match on packet headers, iii) a list of OpenFlow actions to apply to the matching packet, and iv) a **next-state** label;

- 2. a state table comprising two columns: i) a flow key and the associated ii) state label.

- 3. the **lookup-scope** and **update-scope** used to extract the flow key to access the state table for, respectively, read and write operations. For simplicity we can refer to a *key scope* as any ordered sequence of pointers to header fields used to extract a key.

#### OpenState API

In this section we describe the API necessary to program an OpenState switch. We describe also two important additional capabilities that for simplicity we have not mentioned so far: cross-flow state handling, and time-based events.

The API is defined as an extension to OpenFlow, meaning that we can assume all primitives and capabilities assumed by OpenFlow plus the OpenState's primitives. The OpenFlow specification refers to a MAT simply as a flow table, and to MAT entries as flow entries. OpenFlow version 1.0 is based on a single flow table, while starting from version 1.1 the switch can support multiple flow tables pipelined. The protocol message used to add, modify and remove flow entries is the flow-mod message. Unless explicitly changed by the remote controller through flow-mod messages, flow tables are static, i.e., all packets matched by a given flow entry experience the same forwarding behavior, for this reason we can refer to an OpenFlow flow table as a stateless processing block. OpenState introduces the notion of a stateful block, as an extension of a single OpenFlow table. Stateful blocks can be pipelined with other stateful blocks as well as stateless blocks. In the following we describe the API necessary to program a single stateful block.

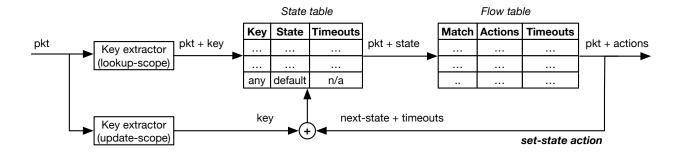

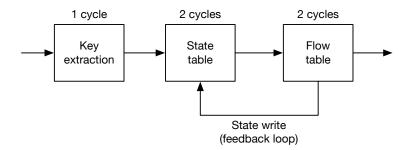

Figure 2.3 depicts the packet processing architecture of an OpenState's stateful block.

The FSM table introduced before is implemented using an ordinary OpenFlow flow table, preceded by a state table. Extraction of the key to access the state table is performed by two dedicated key extractors, configured respectively with the lookup-scope and update-scope. The key is extracted concatenating the header fields in the same order as specified in the key scopes. As further explained in Section 2.1.2, the order of the fields is important because it permits to handle the case of bidirectional flows, i.e. in a client/server paradigm, update the state of the flow carrying the reply as a consequence of the behavior of the flow carrying the request. The state table maps keys to state labels, an entry of such table is said state entry. When processing a packet, if a given key is not found in the state table a default state label, said also state 0, is returned. The state table has an additional column that

Figure 2.3 Abstract pipeline model of a stateful processing block in OpenState.

defines the timeouts associated with a given state entry. Similarly to flow entries timeout in OpenFlow, state timeouts allow a given state entry to expire after a certain amount of time, moreover they can be used in OpenState to define time-based events to force state transitions independently from packets received. Details of the state timeout mechanism are provided in Section 2.1.2.

After a state label is returned by the state table, the packet is processed by the flow table. Here flow entries can be defined to match both the packet headers (we assume the same headers as in OpenFlow) and on the state label, virtually added to the packet headers as a metadata. As in OpenFlow, the flow table returns the packet and a list of actions, to be applied either immediately or at the end of the pipeline.

The next-state column of the FSM table is embodied by a special action *set-state*. When adding an entry to the flow table, along with the ordinary OpenFlow actions, a programmer can add a set-state action to instruct the switch on how to update the state table when that entry is matched. The set-state action takes as parameters the new state label to write in the state table, and the timeouts associated with it. Differently from other OpenFlow actions, the set-state action is not appended to the action list, but instead it is executed immediately to update the state table, creating a *feedback-loop*.

When a packet triggers a set-state action, the state table is updated using the flow key returned by the key extractor configured with the update-scope, which can produce a key different from the one used in the lookup phase. If a given flow key already exists in the flow table, the state label is rewritten and the new timeouts are set, otherwise, if the flow key is not found, a new state entry is instantiated. It is important for the update key to be extracted *before* the packet is processed by the flow table, otherwise the evaluated key would depend on the result of any OpenFlow header rewrite action. As explained in Section 2.3, knowing beforehand which state entry could be potentially updated, allows us to lock access

to the state table when processing packets in parallel, so to prevent state inconsistencies.

To summarize, the necessary steps to configure a stateful block in OpenState are:

- 1. **Instantiate the state table**, via configuration of the lookup-scope and update-scope;

- 2. **Define state transitions**, by inserting flow entries that match the state label and use the set-state action.

After being provisioned, the state table is initially empty. It is then populated based on the set-state actions defined in the flow table.

Figure 2.4 show an example of OpenState configuration for the port knocking example.

#### Cross-flow state handling

There are a number of stateful processing functions where the history of packets of a given flow is used to determine the state of another flow, this situation can be defined as cross-flow state handling. We provide here an example and relative OpenState configuration of an application based on cross-flow state handling: a L2 learning switch.

**Example:** L2 learning switch L2 learning is the process implemented by a legacy L2 bridge. In such devices, each time a packet is received the following operations are performed:

- 1. a *learning table* is update mapping the Ethernet *source* address (for simplicity ethsrc) to the switch input port where the packet was received;

- 2. the learning table is queried using the Ethernet destination address (ethdst), if an entry is found, then the packet is forwarded to the corresponding port (learned before), otherwise the packet is flooded on all ports.

Without loss of generality, we assume the learning table is indexed using only the Ethernet address. In real bridge implementations, a combination of the Ethernet address, the VLAN ID and the switch input port is used to distinguish between VLANs and to avoid loops.

While there are many different OpenFlow-based implementations of a L2 learning switch, more or less optimized, given the stateless nature of the OpenFlow data plane, they are all based on the following reactive approach. The flow table of the OpenFlow switch is initially empty, apart for the *table-miss*<sup>3</sup> that generates a *packet-in*. The controller implements the

$<sup>^{3}</sup>$ Table-miss is the OpenFlow wording for the lowest priority rule that matches all packets otherwise not matched by any other rule.

### Port knocking

lookup\_scope = [ipsrc]

update\_scope = [ipsrc]

| Match                     | Actions                             |

|---------------------------|-------------------------------------|

| state=DEFAULT, dport=5123 | <pre>drop, set_state(STAGE-1)</pre> |

| state=STAGE-1, dport=6234 | <pre>drop, set_state(STAGE-2)</pre> |

| state=STAGE-2, dport=7345 | <pre>drop, set_state(STAGE-3)</pre> |

| state=STAGE-3, dport=8456 | <pre>drop, set_state(OPEN)</pre>    |

| state=OPEN, dport=22      | forward                             |

| state=OPEN                | drop                                |

| *                         | <pre>drop, set_state(DEFAULT)</pre> |

Figure 2.4 Example of flow table configuration and key scopes to implement the port knocking example. Flow entries are assumed to be in priority order, where the first entry has maximum priority. "dport" is the TCP/UDP destination port. The generic action "forward" indicates that the packet can be forwarded. In a real OpenFlow-like configuration, a programmer should include routing actions to output packets on specific ports.

learning table. Indeed, for each packet-in the controller updates and queries a local version of the learning table, if an entry is found for the packet-in's ethdst, then the controller installs a flow rule in the switch to forward this and subsequent packets of the same flow over the learned port, otherwise the controller generates a packet-out<sup>4</sup> to flood the packet on all switch ports. Using this approach, the number of flow rules depends on the number of hosts in the network, which can be problematic in some cases, e.g. in a data center with tens of thousands of virtual machines each one with a different Ethernet address.

A more efficient way of implementing a L2 learning switch based on OpenState, that does not involve interacting with the controller, is depicted in Figure 2.5. In this case, state labels are used to codify the location (port) of a given host. The state table is queried looking at the ethdst of the packet (lookup-scope), while it is updated using the ethsrc (update-scope). The entries in the table forward packets according to the state label (flood if default) and update the state based on the packet's input port. This example on purpose assumes compatibility with the current OpenFlow specification, and the  $N^2+N$  size of the table (being N the number of switch ports) thus depends on the OpenFlow limitations, and not on our abstraction. Indeed, assuming a platform compatible with RMT [20] where action parameters can be pointers to header fields, this assumption would yield a flow table comprising of only

<sup>&</sup>lt;sup>4</sup>Packet-out is the OpenFlow wording for the action of sending a data packet from the controller to a switch, encapsulated in an OpenFlow header that specifies the actions to be applied by the switch on the packet, e.g. output on a given port or flood.

### L2 learning switch

lookup\_scope = [ethdst]

update\_scope = [ethsrc]

| Match                         | Actions                                 |

|-------------------------------|-----------------------------------------|

| state=DEFAULT, inport=1       | flood, set_state(PORT-1)                |

| state=PORT-1, inport=1        | <pre>output(1), set_state(PORT-1)</pre> |

| state=PORT-2, inport=1        | output(2), set_state(PORT-1)            |

|                               |                                         |

| state=PORT- $N$ , inport=1    | $output(N)$ , $set\_state(PORT-1)$      |

|                               |                                         |

|                               |                                         |

| state=DEFAULT, inport=2       | flood, set_state(PORT-2)                |

| state=PORT-1, inport=2        | output(1), set_state(PORT-2)            |

|                               |                                         |

| state=PORT- $N$ , inport=2    | $output(N)$ , $set\_state(PORT-2)$      |

|                               | •••                                     |

|                               |                                         |

| state=DEFAULT, inport= $N$    | flood, set_state(PORT- $N$ )            |

| state=PORT-1, inport= $N$     | $output(1)$ , $set_state(PORT-N)$       |

| state=PORT-2, inport= $N$     | $output(2)$ , $set_state(PORT-N)$       |

|                               |                                         |

| state=PORT- $N$ , inport= $N$ | $output(N)$ , $set\_state(PORT-N)$      |

Figure 2.5 OpenState configuration to implement a L2 learning switch with N ports; inport indicates the switch input port of the packet, action flood replicates and forward a packet to all switch ports except inport; the state label represents the port number to which the packet shall be forwarded, i.e. the location of a given host.

two entries (Figure 2.6).

With OpenState, the size of the flow table does not depend on the number of host H but on the number of switch ports  $N \ll H$  (or just 2 if OpenFlow would support pointers to header fields as action parameters). Instead the size of the state table depends on H. As we will explain in Section 2.1.3, given the nature of the state table, i.e. exact match on the key, this can be implemented in a cheap RAM-based hash table, opposed to the expensive (in terms of chip area and power consumption) TCAM-based flow table, necessary to support OpenFlow ternary matches. Such consideration makes the OpenState-based L2 learning switch implementation scale easier than the OpenFlow one based on the reactive-approach.

Finally, to provide a further example of the generality of OpenState, if one would like to implement bridging based on VLANs, it would suffice to set the key scope as lookup\_scope

### Simplified L2 learning switch

lookup\_scope = [ethdst]

update\_scope = [ethsrc]

| Match         | Actions                                         |  |  |

|---------------|-------------------------------------------------|--|--|

| state=DEFAULT | <pre>flood, set_state(\$inport)</pre>           |  |  |

| state=*       | <pre>output(\$state), set_state(\$inport)</pre> |  |  |

Figure 2.6 Simplified configuration of the example in Figure 2.5. \$inport and \$state are used to point at the value contained in the packet header fields, respectively the switch input port and the state label.

= [vlanid, ethdst], and update scope = [vlanid, ethsrc].

#### Time-based events

OpenState defines timeouts for the entries of the state table, useful to specify time-based events and transitions in a FSM, e.g. "move to state B after X time in state A", or "set the state of the flow to IDLE if no packets are received for X time". So far, the only type of events that can trigger a state transition are packet-based events, i.e. match on an incoming packet. However, some applications would benefit from defining events based on time, regardless if a packet is received or not, i.e. in a stateful firewall, set the state of a TCP connection to CLOSED after no packets are received for a given amount of time. Similarly, timeouts could be used to flush unused state entries, to limit the size of the state table.

Analogue to OpenFlow's flow entries, the state table is designed such that each entry has an idle-timeout and a hard-timeout associated with it. Moreover, both timeouts are associated with an *expired state*, respectively idle-expired-state and hard-expired-state, to be applied when a state timeout expires. To summarize, a row of the state table would look like this:

| key | state | idle-timeout | hard-timeout | idle-expired-state | hard-expired-state |

|-----|-------|--------------|--------------|--------------------|--------------------|

|-----|-------|--------------|--------------|--------------------|--------------------|

Timeouts are set the same way state entries are added (updated) to the state table, by means of a set-state action. We can assume state timeouts are not set unless explicitly declared in the set-state action, i.e. the entry will never expire.

Hard-timeouts cause the state entry to be updated to the hard-expired-state after a given interval since the entry was last updated, regardless of how many packets it has matched. Idle-timeouts cause the state entry to be updated to the idle-expired-state when it has matched no packets in a given interval, i.e. the state entry was idle. When a state entry is expired because of a timeout, and its value updated with the expired state, it remains in that state

until a new set-state action is performed. If the expired state is the DEFAULT state, then the entry is removed from the state table. The reader should remember that all flows are virtually in state DEFAULT, even if a state entry is not present in the state table. Hence, removing an entry is equivalent to setting its state label to DEFAULT.

State timeouts are useful to define events at the granularity of packet time-scales, i.e. short time scales comparable to the interval between two packets of the same flow. Hence, a switch target implementing OpenState should provide a timeout granularity in the order of microseconds or less. This is easy, considering that current switch targets already expose a clock interface operating at finer frequencies, i.e. 0.1-1 GHz.

The application presented in Chapter 3 makes extensive use of state timeouts. However, it is useful to present another programming example of OpenState: flowlet-based path load balancing.

Example: flowlet-based path load balancing. Load balancing traffic over multiple paths (also known as load sharing) is an important feature that allows flexible and efficient allocation of network resources. Given multiple paths that a switch can use to forward a packet, legacy load balancing schemes such as ECMP selects an output port hashing the transport layer 5-tuple<sup>5</sup> modulo the number of paths, thus splitting load across multiple paths. Hashing is a convenient approach as it guarantees consistency of the forwarding decision, i.e. packets with the same 5-tuple will be forwarded to the same output port, and hashing is a stateless function that can be implemented very efficiently in hardware. Different hashing schemes exist, each one with its associated tradeoffs [22], however, a key limitation of hash-based schemes is that two or more large, long-lived flows (usually referred in the literature as "elephant" flows) can collide on their hash and end up on the same output port, creating a bottleneck.

The ideal solution would be to split traffic of the same flow at the packet level, instead of pinning the whole flow to a static path choice. However, sending two packets of the same flow over two different paths with different delays might generate packet reordering at the receiver, which can cause unnecessary throughput degradation when using TCP.

Flowlet-based switching is a technique first introduced in [23], that suggests splitting traffic at the level of bursts of packets, called flowlets. Switching bursts, instead of packets, minimizes the risk of packet reordering. The approach is based on the fact that, if the idle time between

<sup>&</sup>lt;sup>5</sup>A hash function is applied to the combination of 5 header fields: IP source address, IP destination address, IP protocol, source port, and destination port. Packets of the same transport layer flow will have the same hash value.

### Flowlet-based path load balancing

```

lookup_scope = [ipsrc,ipdst,ipproto,sport,dport]

update_scope = [ipsrc,ipdst,ipproto,sport,dport]

```

#### Flow table

| Match         | Actions   |  |

|---------------|-----------|--|

| state=DEFAULT | group(1)  |  |

| state=1       | output(1) |  |

| state=2       | output(2) |  |

| • • •         |           |  |

| state=N       | output(N) |  |

#### Group table

| Group ID | Туре   | Action buckets                                                                                                               |  |

|----------|--------|------------------------------------------------------------------------------------------------------------------------------|--|

| 1        | SELECT | <pre><set_state(1, idleto="D)," output(1)="">, <set_state(2, idleto="D)," output(2)="">,</set_state(2,></set_state(1,></pre> |  |

|          |        | <pre> <set_state(n, idleto="D)," output(n)="">,</set_state(n,></pre>                                                         |  |

Figure 2.7 OpenState configuration to implement a flowlet-based load balancer.

two successive packets is larger than the delay difference between two parallel paths, one can route the two packets on different paths without causing reordering at the receiver. The main origin of flowlets is the burstiness of TCP, where idle time at RTT and sub-RTT scales can be observed.

By using flow states and associated timeouts, OpenState allows a programmer to program a flowlet-based load balancer (Figure 2.7). Key scopes distinguish state between different TCP flows. For each incoming packet of a new TCP connection, a DEFAULT state is returned by the state table, causing a group table to be invoked. OpenFlow's group table are used to randomly choose (SELECT<sup>6</sup>) an output port among N available. Here the group table picks a random action bucket, forwarding the packet on one of the N available ports, and updating the state accordingly. Subsequent packets will be forwarded using the value returned from the state table, not anymore DEFAULT. By setting the state idle-timeout idleto = D we can define the lifetime of the forwarding decision. For example, with D = 10 seconds the flow-state will be maintained only if a packet from that flow is seen at least once every 10 seconds.