| <b>Titre:</b> Title:    | Electrolyte Gated Metal Oxide Transistors                                                                                                                                    |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Irina Valitova                                                                                                                                                               |

| Date:                   | 2017                                                                                                                                                                         |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                    |

| Référence:<br>Citation: | Valitova, I. (2017). Electrolyte Gated Metal Oxide Transistors [Thèse de doctorat,<br>École Polytechnique de Montréal]. PolyPublie.<br>https://publications.polymtl.ca/2552/ |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

URL de PolyPublie:

PolyPublie URL:

Directeurs de recherche:

Advisors:

Programme:

Program:

Génie métallurgique

# UNIVERSITÉ DE MONTRÉAL

# ELECTROLYTE GATED METAL OXIDE TRANSISTORS

# IRINA VALITOVA DÉPARTEMENT DE GÉNIE CHIMIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR

(GÉNIE MÉTALLURGIQUE)

AVRIL 2017

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

### Cette thèse intitulée:

# ELECTROLYTE GATED METAL OXIDE TRANSISTORS

présentée par : VALITOVA Irina

en vue de l'obtention du diplôme de : Philosophiae Doctor

a été dûment acceptée par le jury d'examen constitué de :

M. KÉNA-COHEN Stéphane, Ph. D., président

M. CICOIRA Fabio, Ph. D., membre et directeur de recherche

M. MOUTANABBIR Oussama, Ph. D., membre

M. HILKE Michael, Ph. D., membre externe

### **ACKNOWLEDGEMENTS**

I would like to express my deep gratitude to Professor Fabio Cicoira, my research supervisor, for his scientific guidance and the opportunity to get so vast experience; for his enthusiastic encouragement and useful critiques of this research work. My grateful thanks are also extended to Professor Clara Santato for her valuable advices and discussions, for the opportunity to work in her lab. I would like to thank our collaborator Professor Dr Francesca Soavi (Università di Bologna) for her advices in electrochemistry.

I am grateful for the funding provided by the Fonds de recherche du Québec - Nature et technologies (FRQNT) through a PhD scholarship and CMC Microsystems for microfabrication grants through programs MNT Financial Assistance and Solutions. My special gratitude goes to Christophe Clément, Yves Drolet, Alireza Mesgar, Josianne Lefebvre, Marie-Hélène Bernier, Francis Boutet, Daniel Pilon, Nicole MacDonald and Marta Maria Natile for their technical assistance during these years.

Also I would like to acknowledge the people I worked with, my colleagues and friends, Prajwal, Zhihui, Jonathan, Dilek, Olga, Fanny, Shiming, Xiang, Gaia, Guido, Tian, Eduardo, Xu, Elizabeth, Hao, Julia, Francis, Frédéric, Colleen, Tania, Dominic, Sampath, Gabriel, Mengjiao, Alex, Xinhe, Xiaojie, Shalin and Tom that were working along with me in labs and offices for all their help, support, guidance and just enjoyable quality of time during and in between my research. Thank you all very much. It was a great pleasure to work side-by-side with you!

I would like to thank my committee members, Profs. Stéphane Kena-Cohen, Oussama Moutanabbir, Michael Hilke, Antoniol Giuliano for volunteering their time to read this thesis and hear my defense and to make their valuable comments.

Finally, through all this I have had the unflagging support of my husband, who was "only" doing all housework and taking care of our kids all this time.

# **RÉSUMÉ**

L'invention du transistor a significativement affectée le progrès technique et scientifique de notre société. Depuis plus de 50 ans, les transistors sont utilisés comme composants actifs dans les circuits électroniques, pour réaliser des amplificateurs ou des interrupteurs par exemple. La plus fascinante des directions futures pour le développement des transistors consiste en leur utilisation dans des dispositifs électroniques flexibles, légers et biocompatibles.

Les oxydes métalliques semi-conducteurs ont été intensivement étudiés au cours des dernières décennies pour des applications dans les transistors, du fait de la grande mobilité de leurs porteurs de charges (~1– 100 cm²V¹s¹), de leur importante transparence optique, de leur stabilité chimique ainsi que de leur faible coût de fabrication. Les oxydes métalliques sont divisés entre les oxydes de transition et ceux post-transition, dépendamment des métaux, qui possèdent différentes configurations électroniques et donc différentes conductivités.

Dans cette thèse, nous allons nous concentrer sur les deux principaux représentants des oxydes métalliques de transition et post-transition, i.e., le TiO<sub>2</sub> et le SnO<sub>2</sub>, utilisés comme matériaux de canal dans des transistors utilisant un électrolyte comme diélectrique à la grille. Le TiO<sub>2</sub> et le SnO<sub>2</sub> sont abondants et biointégrables, possèdent une large bande interdite (3-4 eV), et peuvent être utilisés comme canal de transistor pour de nombreuses applications différentes.

Remplacer le diélectrique conventionnel dans les transistors à couche minces par un électrolyte donne l'opportunité de décroître le voltage auquel le transistor est opéré du fait de la haute capacitance de la double couche électrique (autour de  $10~\mu F/cm^2$ ) qui se forme à l'interface entre l'électrolyte et le semi-conducteur. Cette capacitance élevée permet l'accumulation d'une importante densité de porteurs de charges dans le canal et rend donc possible la transition entre un état isolant et un état semi-conducteur voire métallique. Les transistors utilisant un électrolyte comme diélectrique à la grille (EGTs) peuvent être employés comme éléments de matrice active pour les écrans à faible puissance ou encore intégrés dans des textiles ou d'autres matériaux flexibles. Les EGTs peuvent aussi être utilisés dans d'autres applications prometteuses que sont telles les capteurs chimiques ou biologiques, du fait de leur haute sensibilité aux ions et de leur compatibilité avec les électrolytes aqueux.

Le cœur de cette thèse est dévoué à une meilleure compréhension des mécanismes d'opération d'une importante classe de transistors à couche minces, i.e. les transistors à oxydes métalliques

utilisant un électrolyte comme diélectrique à la grille, afin d'optimiser leurs performances et de développer des agencements géométriques pour permettre d'obtenir des transistors à haute performance. Les EGTs consistent en un canal en oxyde métallique et en une électrode de grille en contact avec un électrolyte. L'application d'un voltage à la grille entraîne la formation d'une double couche électrique au niveau de l'interface entre le canal et l'électrolyte, qui permet de moduler la densité des porteurs de charges dans le canal. Les mécanismes de dopage et la modulation de la densité des porteurs de charges dans les EGTs ont été étudiés par caractérisation électrique des transistors, par voltammétrie cyclique (CV) ainsi que par spectroscopie d'impédance électrochimique.

Des transistors SnO<sub>2</sub> et TiO<sub>2</sub> utilisant des liquides ioniques à la grille ont été fabriqués sur des substrats en silicone. Une méthode de gravure non conventionnelle utilisant le parylène a été utilisée pour étudier le rôle joué par l'extension des interfaces électrolyte/semi-conducteur et électrode/semi-conducteur sur le dopage ainsi que sur les processus de transport des porteurs de charges. Le chevauchement entre les électrodes métalliques et le semi-conducteur, qui est en contact avec l'électrolyte, affecte le processus d'injection des charges. La gravure a entraîné l'augmentation de la densité des porteurs de charges d'un à deux ordres de magnitude dans les deux oxydes métalliques. De plus, les EGTs à SnO<sub>2</sub> ont été fabriqués sur des substrats flexibles en polyimide. Les transistors EGTs à SnO<sub>2</sub> flexibles possèdent de bonnes propriétés électriques lorsqu'ils sont pliés selon différents rayons de courbure et ils pourraient posséder un fort potentiel pour des applications dans le domaine de l'électronique flexible.

Les effets de la structure et de la morphologie des semi-conducteurs sur les performances des transistors ont été étudiés. Dans ce but, des films de TiO<sub>2</sub> poreux à très forte densité ont été fabriqués par traitement à partir d'une solution ainsi que par évaporation par faisceau d'électrons. Les EGTs à TiO<sub>2</sub> faits par évaporation possédaient un courant plus élevé ainsi qu'un ratio on/off plus haut du fait d'une meilleure qualité de la structure. Les effets des gros cations [EMIM] et des petits cations Li<sup>+</sup> sur les mécanismes de dopage ont été étudiés en utilisant deux électrolytes [EMIM][TFSI] et [EMIM][TFSI] mélangé avec un sel de lithium. Les relativement gros cations [EMIM] ne peuvent pas pénétrer à l'intérieur du maillage cristallin du TiO<sub>2</sub>. L'intercalation de petits cations comme le Li+ a été rendue possible à la fois dans les films denses et dans les films mésoporeux de TiO<sub>2</sub> par réduction de la vitesse de balayage dans les mesures courant/voltage.

Les mécanismes de transport des charges des transistors utilisant un électrolyte comme diélectrique à la grille ont été étudiés et une corrélation entre la capacitance de la double couche, la densité des porteurs de charges, la mobilité des électrons, la tension seuil et le ratio on/off a été démontrée. Nous pensons que nos transistors à oxydes métalliques utilisant un électrolyte comme diélectrique à la grille sont prometteurs pour de l'électronique flexible, produite sur de grandes surfaces et à faible coût.

### **ABSTRACT**

The invention of the transistor has significantly affected the technological and scientific progress of our society. For over 50 years, transistors have been used as the active components, such as amplifiers or switches, in electronic circuits. The most fascinating future direction for transistor development is towards flexible, lightweight and biocompatible electronics.

Metal oxide semiconductors have been intensively investigated over the past decades for transistor applications, due to their high charge carrier mobility (~1–100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>), high optical transparency, chemical stability and low-manufacturing cost. Metal oxides are divided into transition and post transition oxides, depending on the metals, which possess different electron configurations and, accordingly, different conductivity.

In this Thesis we focus on two main representatives of transition and post transition metal oxides, i.e., TiO<sub>2</sub> and SnO<sub>2</sub>, as the channel materials in electrolyte gated transistors. TiO<sub>2</sub> and SnO<sub>2</sub> are abundant and bio friendly, with high band gap (3-4 eV) and can be utilized as transistor channel for many different applications.

Replacing the conventional dielectric in thin film transistors with electrolyte gives the opportunity to decrease the transistor operating voltage due to the high capacitance of the electrical double layer (around  $10~\mu\text{F/cm}^2$ ) that form at the electrolyte/semiconductor interface. This high capacitance allows accumulation of high charge carrier density in the channel thus making possible a transition from an insulating state to semiconducting or metallic one. Electrolyte gated transistors (EGTs) can be utilized as backplanes for low powered displays and integrated into textiles or flexible materials. Other exciting applications of EGTs are chemical sensors or biosensors, due to the high sensitivity to ions and compatibility with aqueous electrolytes.

The core of this thesis is devoted to a better understanding of the operational mechanisms of an important class of thin film transistors, i.e. electrolyte gated metal oxide transistors, to optimize their performance and to develop the appropriate device geometry for high performance transistors. EGTs consist of metal oxide channel and a gate electrode in contact with an electrolyte. The application of a gate electrical bias leads to the formation of an electrical double layer at the channel/electrolyte interface, which permits to modulate the charge carrier density in

the channel. The doping mechanisms and the charge carrier density modulation in EGTs were investigated by transistor electrical characterization, cyclic voltammetry (CV) and electrochemical impedance spectroscopy.

Ionic liquid gated SnO<sub>2</sub> and TiO<sub>2</sub> transistors were fabricated on silicon substrates. Parylene patterning was utilized to investigate the role played by the extension of the electrolyte/semiconductor and electrode/semiconductor interfaces on the doping and charge carrier transport processes. The overlap between the metal electrodes and the semiconductor, which is in contact with the electrolyte, affects the charge injection process. By patterning the charge carrier density was increased on one or two order of magnitude in both metal oxide materials. Moreover, SnO<sub>2</sub> EGTs were fabricated on flexible polyimide substrate. EGT SnO<sub>2</sub> flexible transistors possessed good electrical properties under bending at different radius and could have high potential in flexible electronics.

The effect of structure and morphology of semiconductors on transistor performance was demonstrated. For this purpose, porous and highly dense films of TiO<sub>2</sub> were fabricated by solution processing and by electron beam evaporation. Evaporated TiO<sub>2</sub> EGT showed higher current and higher on/off ratio due to better structural quality. The effect of big [EMIM] and small Li<sup>+</sup> cation on doping mechanisms was investigated by using two electrolytes [EMIM][TFSI] and [EMIM][TFSI] mixed with a lithium salt. The relatively large [EMIM] cation cannot enter the crystal lattice of TiO<sub>2</sub>. The intercalation of small cation such as Li<sup>+</sup> was possible both in mesoporous and dense TiO<sub>2</sub> films by decreasing the sweeping rate in current / voltage measurements.

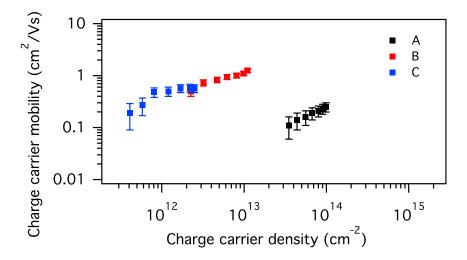

The charge transport mechanism of electrolyte gated transistors was investigated and a correlation between capacitance of the double layer, charge carrier density, electron mobility, threshold voltage and on/off ratio was demonstrated. We believe that our electrolyte gated metal oxide transistors are promising for low cost, flexible and large area electronics.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                            | III    |

|-----------------------------------------------------------------------------|--------|

| RÉSUMÉ                                                                      | IV     |

| ABSTRACT                                                                    | VII    |

| TABLE OF CONTENTS.                                                          | IX     |

| LIST OF TABLES                                                              | . XIII |

| LIST OF FIGURES.                                                            | .XIV   |

| LIST OF SYMBOLS AND ABBREVIATIONS                                           | .XIX   |

| LIST OF APPENDICES                                                          | XXIII  |

| CHAPTER 1 INTRODUCTION                                                      | 1      |

| 1.1 History of transistors                                                  | 1      |

| 1.2 Thin film transistors                                                   | 2      |

| 1.2.1 Working principle of thin film transistors                            | 3      |

| 1.2.2 Main characteristics of thin film transistors                         | 5      |

| 1.2.3 Thin film transistor configurations                                   | 7      |

| 1.2.4 The contact resistance and overlap capacitance                        | 8      |

| 1.3 Electrolyte gated thin film transistors                                 | 9      |

| 1.4 Metal oxides (TiO <sub>2</sub> and SnO <sub>2</sub> ) as semiconductors | 11     |

| 1.5 Problem identification                                                  | 14     |

| 1.6 General Objectives                                                      | 15     |

| 1.7 Motivation                                                              | 15     |

| 1.8 Specific objectives                                                     | 15     |

| 1.9 Organization of the work                                                | 16     |

| CHAPTER 2 LITERATURE REVIEW: METAL OXIDE THIN FILM TRANSISTORS              | 18     |

| 2.1 V  | apor processed thin film transistors                                              | 18 |

|--------|-----------------------------------------------------------------------------------|----|

| 2.2 S  | olution processed thin film transistors                                           | 21 |

| 2.2.1  | Reduction of the fabrication temperature                                          | 22 |

| 2.2.2  | Role of dopant                                                                    | 24 |

| 2.3 E  | lectrolyte gated thin film transistors                                            | 26 |

|        | R 3 ARTICLE 1: TIN DIOXIDE ELECTROLYTE-GATED IG IN DEPLETION AND ENHANCEMENT MODE |    |

| 3.1 A  | uthors                                                                            | 35 |

| 3.2 A  | bstract                                                                           | 35 |

| 3.3 Ir | itroduction                                                                       | 36 |

| 3.4 R  | esults and discussion.                                                            | 37 |

| 3.4.1  | Transistor fabrication and film characterization                                  | 37 |

| 3.4.2  | Electrical characterization of SnO <sub>2</sub> transistors                       | 39 |

| 3.4.3  | Electrochemical characterization of SnO <sub>2</sub> films                        | 43 |

| 3.4.4  | Electrical characteristics under mechanical deformations                          | 44 |

| 3.5 C  | onclusion                                                                         | 45 |

| 3.6 N  | laterials and methods                                                             | 46 |

| 3.6.1  | Processing of SnO <sub>2</sub>                                                    | 46 |

| 3.6.2  | Flexible transistor fabrication.                                                  | 46 |

| 3.6.3  | Purification of the ionic liquid.                                                 | 46 |

| 3.6.4  | Fabrication of the activated carbon (AC) electrodes                               | 46 |

| 3.6.5  | Morphology and structure of SnO <sub>2</sub> films.                               | 47 |

| 3.6.6  | Surface area measurements.                                                        | 47 |

| 3.6.7  | Transistor and electrochemical characterization.                                  | 47 |

| 37 A   | cknowledgments                                                                    | 47 |

| CHAP  | TER  | 4 ARTICLE 2: PHOTOLITHOGRAPHICALLY PATTERNED TIO <sub>2</sub> FI | LMS FOR |

|-------|------|------------------------------------------------------------------|---------|

| ELECT | ΓRΟΙ | LYTE-GATED TRANSISTORS                                           | 48      |

| 4.1   | Aut  | hors                                                             | 48      |

| 4.2   | Abs  | stract                                                           | 48      |

| 4.3   | Intr | oduction                                                         | 49      |

| 4.4   | Res  | ults and discussion                                              | 51      |

| 4.    | 4.1  | Patterning and Fabrication of the Devices                        | 51      |

| 4.    | 4.2  | Electrochemical characterization of TiO <sub>2</sub> films       | 54      |

| 4.    | 4.3  | TiO <sub>2</sub> transistors and role of patterning              | 56      |

| 4.5   | Cor  | nclusion                                                         | 59      |

| 4.6   | Exp  | perimental                                                       | 60      |

| 4.    | 6.1  | Processing of TiO <sub>2</sub>                                   | 60      |

| 4.    | 6.2  | Purification of the ionic liquid                                 | 60      |

| 4.    | 6.3  | Device Fabrication                                               | 60      |

| 4.    | 6.4  | Fabrication of the activated carbon (AC) electrodes.             | 61      |

| 4.    | 6.5  | Morphology and structure of TiO <sub>2</sub> films.              | 61      |

| 4.    | 6.6  | Surface area measurements.                                       | 61      |

| 4.    | 6.7  | Transistor and electrochemical characterization.                 | 62      |

| 4.7   | Ack  | xnowledgments                                                    | 62      |

| CHAP' | TER  | 5 CHARGE CARRIER DENSITY MODULATION IN DENSELY                   | PACKED  |

| AND F | PORC | DUS POLYCRYSTALLINE TIO2 FILMS BY ELECTROLYTE GATING             | 63      |

| 5.1   | Abs  | stract                                                           | 63      |

| 5.2   | Intr | oduction                                                         | 63      |

| 5.3   | Exp  | periments and methods                                            | 65      |

| 5     | 2 1  | Processing of TiO.                                               | 65      |

| 5.3.2     | Electrolyte preparation                             | 65 |

|-----------|-----------------------------------------------------|----|

| 5.3.3 I   | Fabrication of the activated carbon (AC) electrodes | 65 |

| 5.3.4 I   | Device Fabrication                                  | 66 |

| 5.3.5     | Morphology and structure of TiO <sub>2</sub> films  | 66 |

| 5.3.6     | Transistor and electrochemical characterization     | 66 |

| 5.4 Resu  | ılts and Discussion                                 | 66 |

| 5.5 Conc  | clusion                                             | 75 |

| CHAPTER 6 | GENERAL DISCUSSION                                  | 77 |

| CHAPTER 7 | CONCLUSION AND RECOMMENDATIONS                      | 79 |

| BIBLIOGRA | APHY                                                | 81 |

# LIST OF TABLES

| Table 2-1: Lewis acid strength of elements and their metal-oxide bonding strength. | Reprinted |

|------------------------------------------------------------------------------------|-----------|

| with permission from [91]. Copyright 2014 Cambridge University Press               | 25        |

| Table 2-2 The electrical characteristics of some main metal oxide transistors      | 33        |

# LIST OF FIGURES

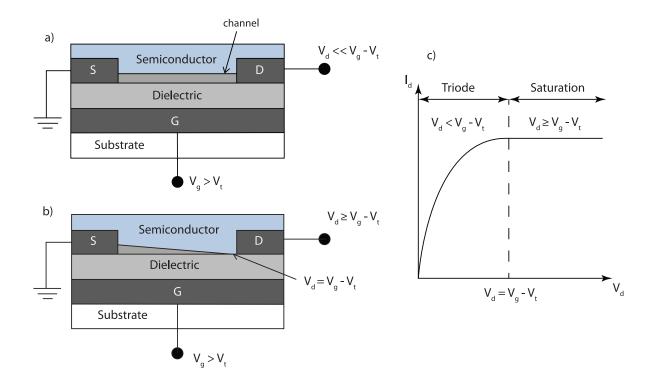

| Figure 1-1: Schematic illustration of operating regimes of field effect transistors: (a) linea regime; (b) saturation regime at pinch-off; (c) corresponding current voltage characteristics                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

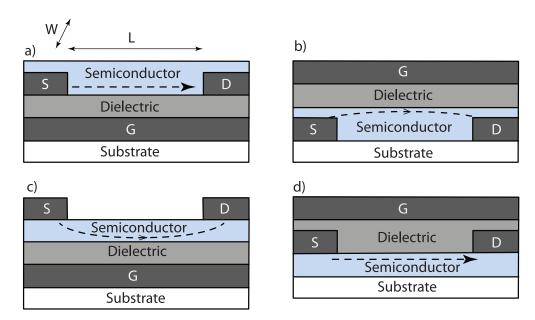

| Figure 1-2: Schematic illustration of thin film transistor configurations: bottom contacts - bottom gate (a, BC-BG), bottom contacts - top gate (b, BC-TG), top contacts - bottom gate (c, TC BG) and top contacts - top gate (d, TC-TG).                                                                                                                                                        |

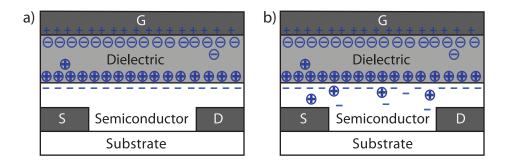

| Figure 1-3:Schematic illustration of an electrolyte gated thin film transistors operating in field effect (a) and electrochemical mode (b)                                                                                                                                                                                                                                                       |

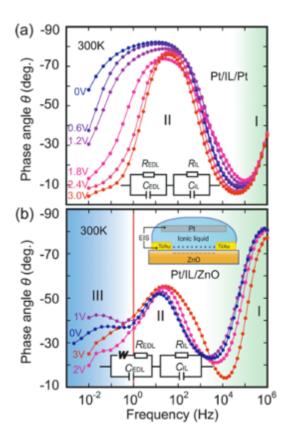

| Figure 1-4: Example of the Bode plot (θ-f) in Pt/IL/Pt structure. Inset: equivalent electric circuit two resistor-capacitor (RC) circuits in series. (b) The Bode plot of ZnO EDL transistor. I bulk IL capacitive region. II: electrostatic EDL capacitive region; III: electrochemical pseudocapacitive region. Reprinted with permission from [58]. Copyright 2010 American Chemical Society. |

| Figure 1-5: Schematic illustration for the carrier transport paths in crystalline and amorphous covalent semiconductors and post transition MeOs. Reprinted with permission from [60] Nature Publishing Group, 2004.                                                                                                                                                                             |

| Figure 1-6:The crystalline structures structures and Brillouin zones of rutile D4h14 and anatase D4h19. Reprinted with permission from [61]. © AIP Publishing LLC, 2013                                                                                                                                                                                                                          |

| Figure 1-7:Electronic structures structures of r- SnO <sub>2</sub> , r- TiO <sub>2</sub> , a- SnO <sub>2</sub> , and a- TiO <sub>2</sub> along two main symmetry directions (100) _ _ and (001)   . Reprinted with permission from [61]. © AIP Publishing LLC, 2013.                                                                                                                             |

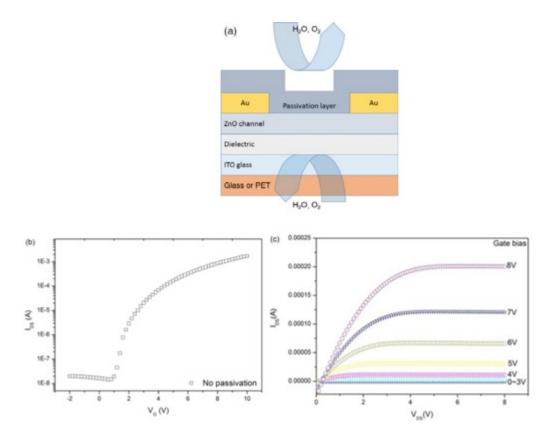

| Figure 2-1: (a) Schematic illustration of ZnO transistor; (b) transfer and (c) output characteristics of this transistor without passivation layer. Reprinted with permission from [72]. Copyrigh © 2015 American Chemical Society                                                                                                                                                               |

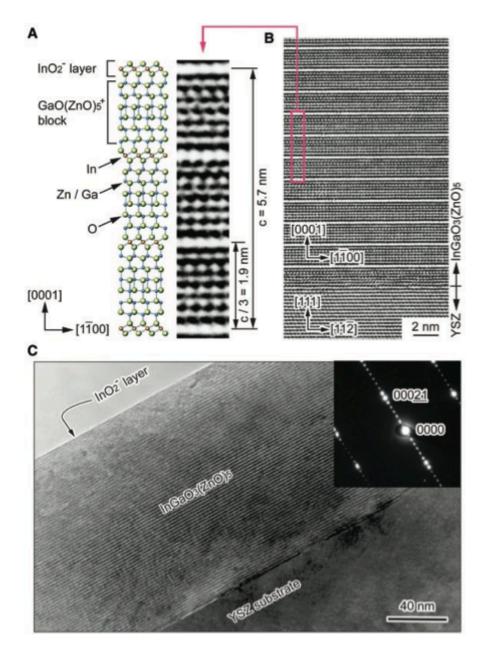

| Figure 2-2: Structure of InGaO <sub>3</sub> (ZnO) <sub>5</sub> . (A) Schematic illustration of the crystal structure. A HRTEM lattice image is shown for comparison. (B,C) Cross-sectional HRTEM images of a                                                                                                                                                                                     |

| InGaO <sub>3</sub> (ZnO) <sub>5</sub> thin film grown by reactive solid-phase epitaxy. Reprinted with permission                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| from [73]. Copyright 2003 The American Association for the Advancement of Science20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

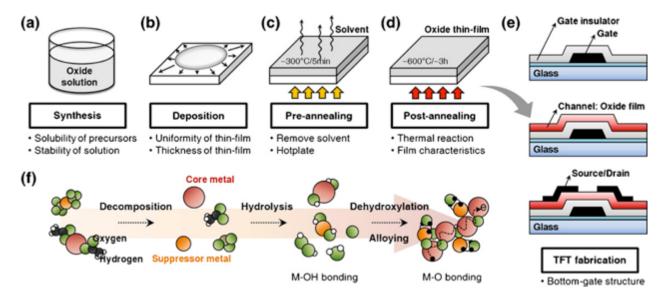

| Figure 2-3: Schematic illustration of the solution process for oxide TFTs: (a) Oxide solution was synthesized using metal precursors in solvent. (b) The synthesized oxide solution can be deposited on a substrate by various methods such as spin-coating, printing. (c) The oxide thin film was pre-annealed to remove the solvent and (d) post-annealed to develop an active layer. (e) The bottom-gate top-contact TFT structure was fabricated using solution process (f) The entire chemical reactions in the oxide solution. Reprinted with permission from [81]. Copyright 2014. |

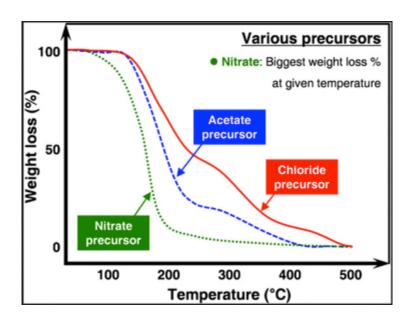

| Figure 2-4: Thermogravimetric analysis of different IZO precursors. Reprinted with permission from [81]. Copyright 2010 Creative Commons CC-BY license                                                                                                                                                                                                                                                                                                                                                                                                                                    |

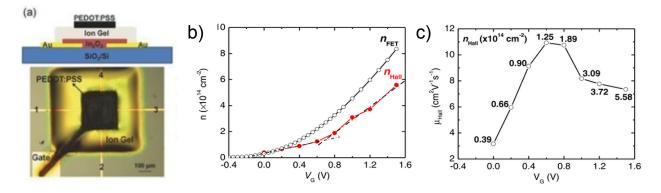

| Figure 2-5: a) Schematic illustration and optical image of a van der Pauw ion-gel-<br>([EMI][TFSI]+PS-PMMA-PS)-gated printed $In_2O_3$ TFT; b) Electron density from Hal<br>effect ( $n_{Hall}$ ), and from displacement current ( $n_{FET}$ ) versus $V_G$ . c) Hall mobility ( $\mu_{Hall}$ ) versus<br>$V_G$ ; $n_{Hall}$ is labeled for each point. Reprinted with permission from [92]. Copyright 2017<br>John Wiley and Sons.                                                                                                                                                       |

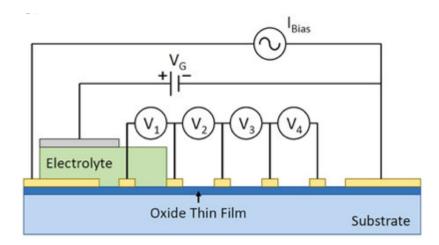

| Figure 2-6: Schematic of the device to test for long range effects in oxide thin films away from the area being charged. The gate was a platinum mesh connected to a DC power supply. The spacing of voltage contacts was 300 µm for all devices. Reprinted with permission from [96]. Copyright 2011 American Chemical Society                                                                                                                                                                                                                                                           |

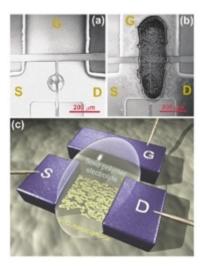

| Figure 2-7: Optical images of a typical in-plane In <sub>2</sub> O <sub>3</sub> transistor. (a) Patterned (with e-beam lithography) ITO electrodes and a printed drop of In <sub>2</sub> O <sub>3</sub> nanoink. (b) The optical image of the same device after printing the electrolyte. (c) A schematic illustration of the device Reprinted with permission from [96]. Copyright 2011 American Chemical Society28                                                                                                                                                                      |

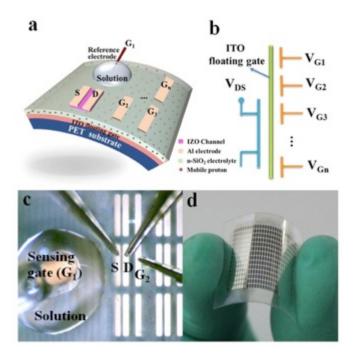

| Figure 2-8: Schematic diagram of a flexible IZO-based neuromorphic transistor with multiple in plane gate electrodes. Reprinted with permission from [75]. Copyright 2015 Creative Commons CC-BY license                                                                                                                                                                                                                                                                                                                                                                                  |

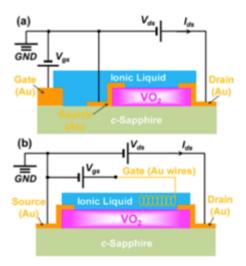

| Figure 2-9: Schematic illustration of VO <sub>2</sub> EGT devices with (a) planar gate geometry, and (b)                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vertical gate geometry. Reprinted with permission from [107]. Copyright 2012 AIF Publishing LLC.                                                                                                  |

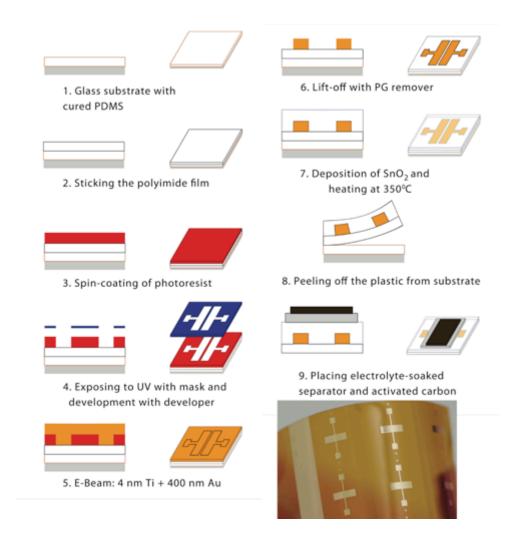

| Figure 3-1: Process flow for the fabrication of SnO <sub>2</sub> EG transistors on flexible polyimide                                                                                             |

| substrates and a photo of a final device (unpatterned flexible devices indicated as D). The                                                                                                       |

| geometric area of SnO <sub>2</sub> in contact with the electrolyte is 0.36 cm <sup>2</sup> , i.e. the area of the                                                                                 |

| Durapore® membrane filter soaked in the ionic liquid [EMIM][TFSI]. The therma treatment temperature of SnO <sub>2</sub> film was 350 °C                                                           |

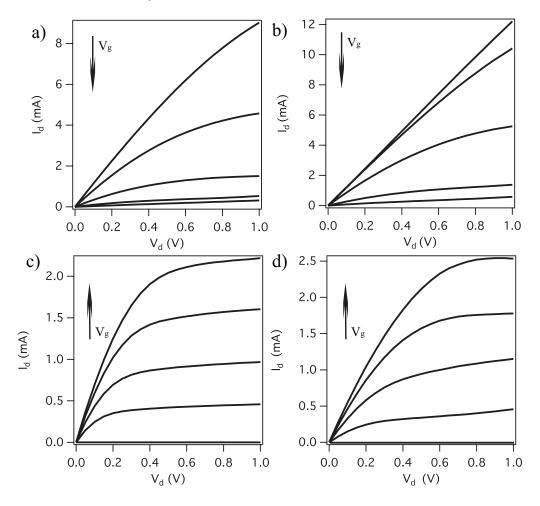

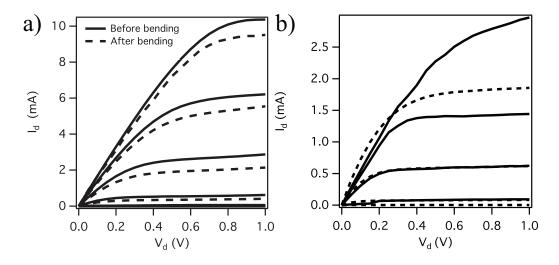

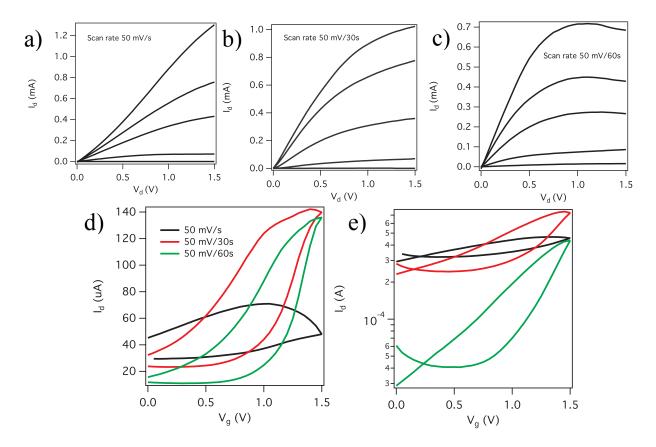

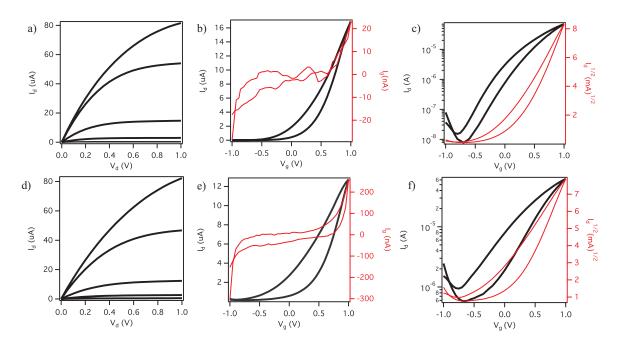

| Figure 3-2: Output characteristics of different types of [EMIM][TFSI]-gated SnO <sub>2</sub> transistors                                                                                          |

| (scan rate 50 mV/s). Patterned devices on $Si/SiO_2$ : a) type A and b) type B, with $V_g$ varying                                                                                                |

| from 1 V to -1 V with steps of 0.5V. Unpatterned SnO <sub>2</sub> transistors on Si/SiO <sub>2</sub> and flexible                                                                                 |

| substrates: c) type C and d) type D, at $V_g = 0V$ , 0.3V, 0.5V, 0.7V, 1V40                                                                                                                       |

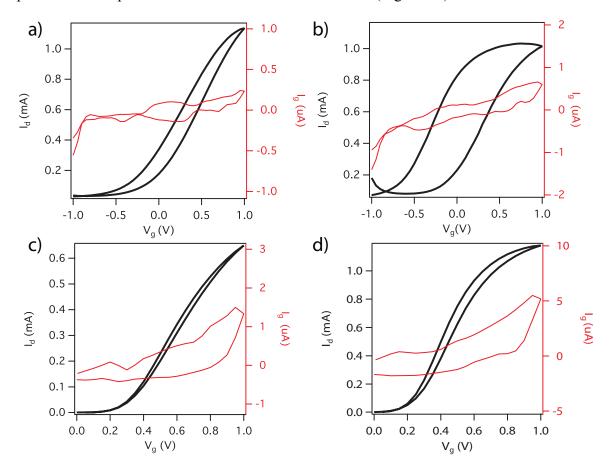

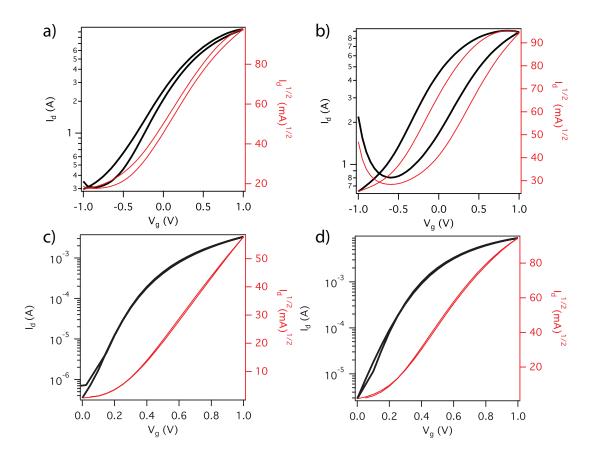

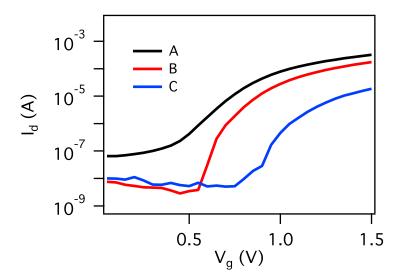

| Figure 3-3: Transfer characteristics in the linear regime of [EMIM][TFSI]-gated $SnO_2$ transistors at $V_d$ =0.2 V. Devices working in depletion mode: a) small pattern A and b) large pattern B |

| Devices working in enhancement mode: c) unpatterned transistors C and unpatterned                                                                                                                 |

| transistors D. Scan rate 50 mV/s                                                                                                                                                                  |

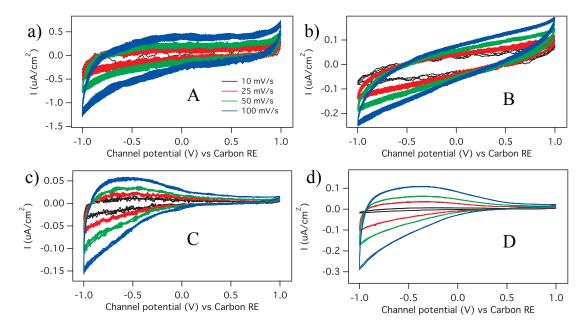

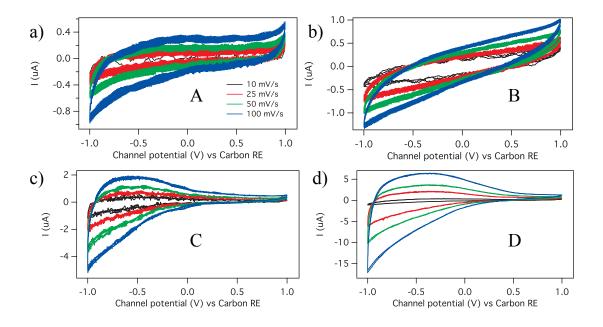

| Figure 3-4: Cyclic voltammetry of SnO <sub>2</sub> films in transistor configuration for the patterned and                                                                                        |

| unpatterned devices a) A, b) B, c) C, and d) D (see main text) in the electrolyte [EMIM][TFSI], at scan rates 10, 25, 50, 100 mV/s. The current is normalized to the surface                      |

| area of the SnO <sub>2</sub> films as deduced using the results of the BET measurements for the                                                                                                   |

| specific surface area                                                                                                                                                                             |

| Figure 3-5: Output characteristics of [EMIM][TFSI]-gated SnO <sub>2</sub> transistors on polyimide, under                                                                                         |

| bending at: a) R=30 mm and b) R=10 mm. $V_g = 0 \text{ V}$ , 0.3 V, 0.5 V, 0.7 V, 1 V. Scan rate 50                                                                                               |

| mV/s. The thermal treatment temperature of SnO <sub>2</sub> films is 350 °C45                                                                                                                     |

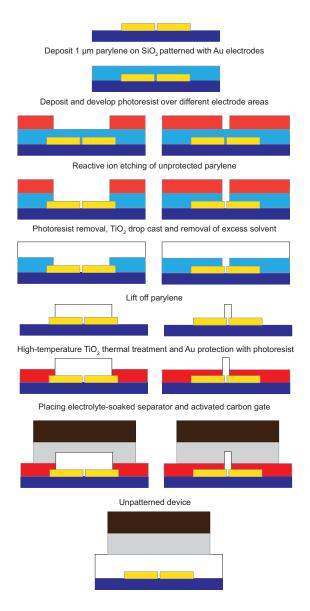

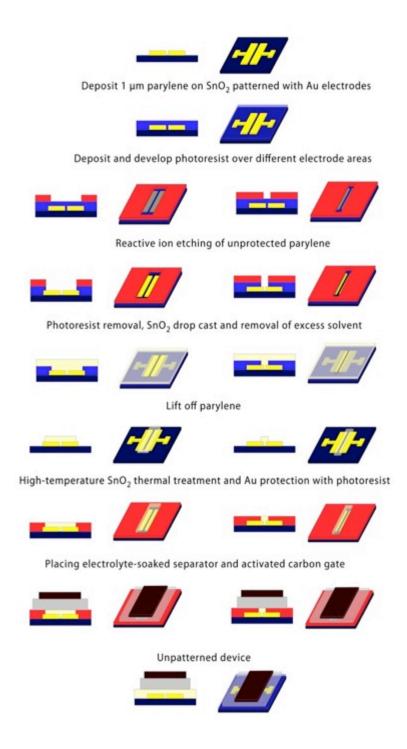

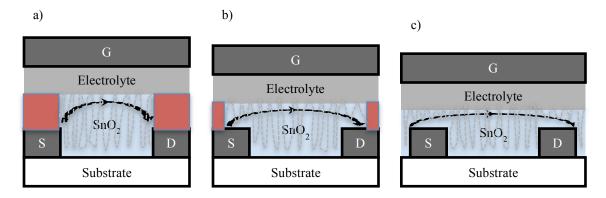

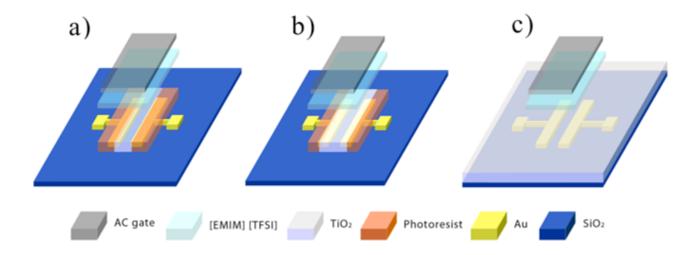

| Figure 4-1: Steps for device fabrication including patterning of TiO <sub>2</sub> films with ParyleneC. Two                                                                                       |

| types of patterns were used: covering the transistor channel and overlapping 20 µm over                                                                                                           |

| each Au electrode (pattern A, TiO <sub>2</sub> geometric area of 0.0025 cm <sup>2</sup> ); covering the transistor                                                                                |

| channel and overlapping about 500 mm over each Au electrode (pattern B, TiO2 geometric                                                                                                            |

| area of 0.0492 cm <sup>2</sup> ). Unpatterned devices were used for the sake of comparison (sample C                                                                                              |

| ٤            | geometric area of 0.36 cm <sup>2</sup> ). [EMIM][TFSI], soaked in a membrane filter (Durapore®, 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r            | mm×4 mm×125 μm), is used as the electrolyte. Activated carbon (6 mm×3 mm×170 μm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8            | acts as the gate53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

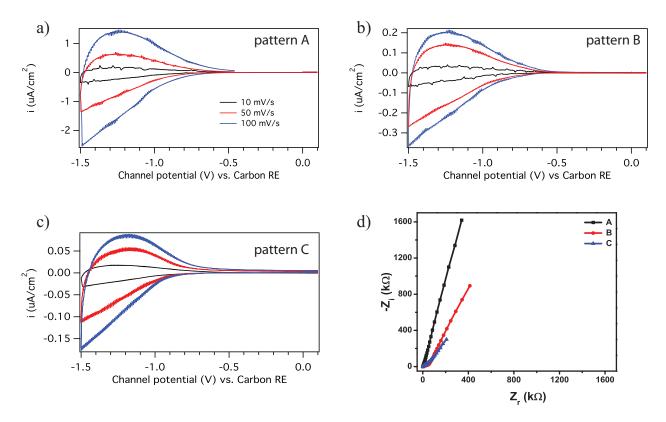

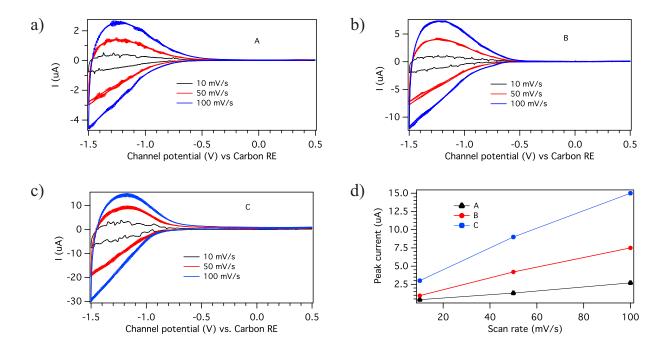

| 1            | e 4-2: Cyclic voltammetry of TiO <sub>2</sub> films of different geometric areas and surface areas (see main text): a) A; b) B c) C, in the electrolyte [EMIM][TFSI], at different sweeping rates (see egend). A TiO <sub>2</sub> film included between source and drain electrodes acts as the working electrode and the carbon gate acts as the counter and the quasi reference electrode. The current is normalized to the surface area of the TiO <sub>2</sub> films in contact with the electrolyte. d) Nyquist plots obtained in transistor configuration using TiO <sub>2</sub> films of different surface areas |

| i            | ncluded between source and drain as the working electrode and carbon as the counter and quasi reference electrode; the measurements were carried out at 1 V vs carbon quasi reference electrode, using [EMIM][TFSI] as the electrolyte                                                                                                                                                                                                                                                                                                                                                                                  |

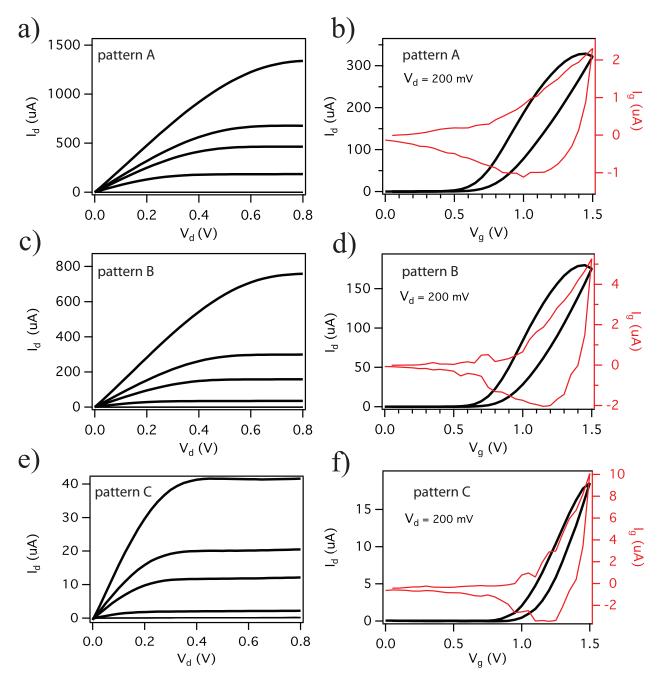

| í            | the 4-3: Output characteristics at $V_g = 0$ V, 1 V, 1.2 V, 1.3 V, 1.5 V and transfer characteristics at $V_d = 200$ mV of [EMIM][TFSI]-gated TiO <sub>2</sub> transistors: a) and b) are for films A; c) and d) for films B; e) and f) for unpatterned films C. The sweeping rate is 50 mV/s.                                                                                                                                                                                                                                                                                                                          |

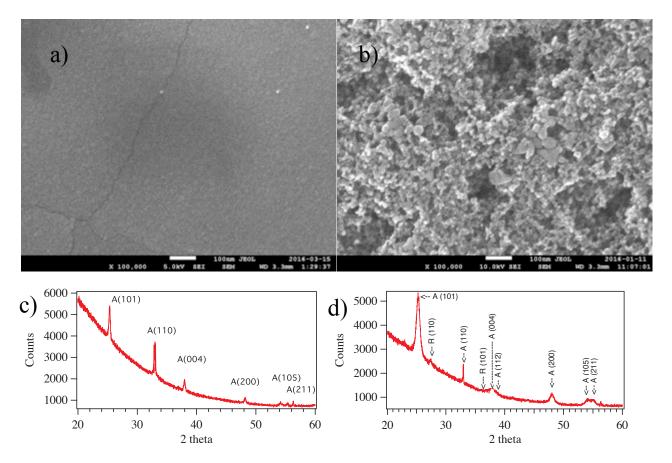

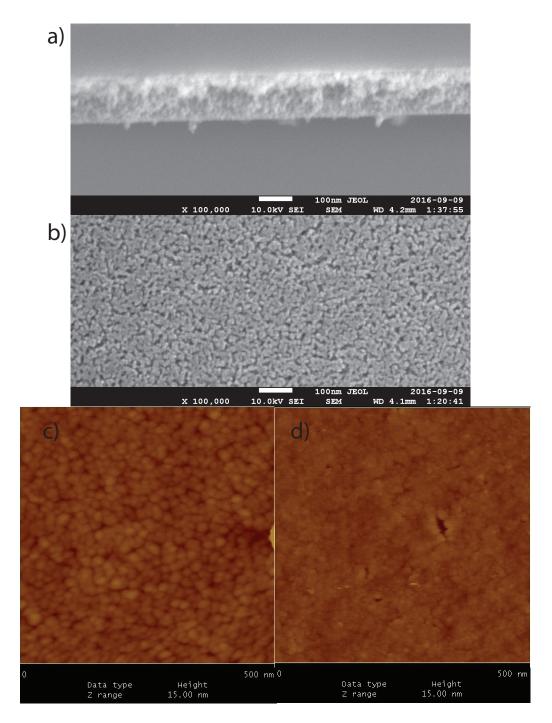

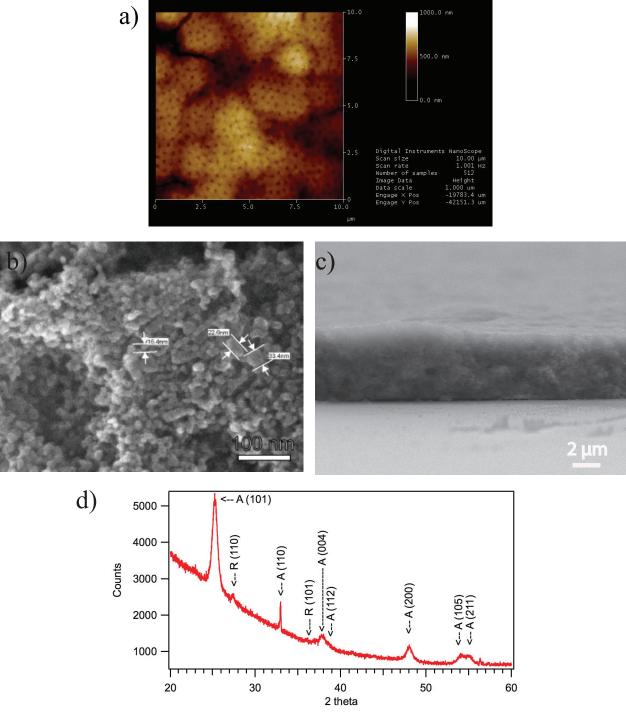

|              | e 5-1: Scanning electron microscopy and X ray diffraction images of (a,c) Ebeam evaporated and (b,c) solution processed TiO <sub>2</sub> films on Si/SiO <sub>2</sub> annealed at 450 C67                                                                                                                                                                                                                                                                                                                                                                                                                               |

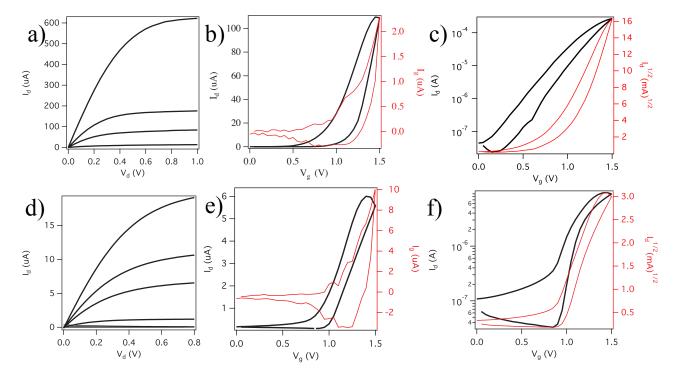

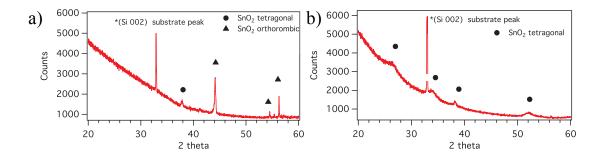

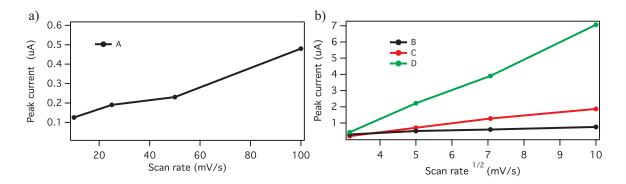

| (<br><u></u> | the 5-2: (a,d) Output characteristics at $V_g = 0$ V, 1 V, 1.2 V, 1.3 V, 1.5 V and (b,e) transfer characteristics at $V_d = 200$ mV; (c,f) transfer characteristics at $V_d = 1$ V of [EMIM][TFSI]-gated TiO <sub>2</sub> transistors: a), b), c) are for evaporated films A; d), f) and e) for solution processed films B. The scan rate is 50 mV/s                                                                                                                                                                                                                                                                    |

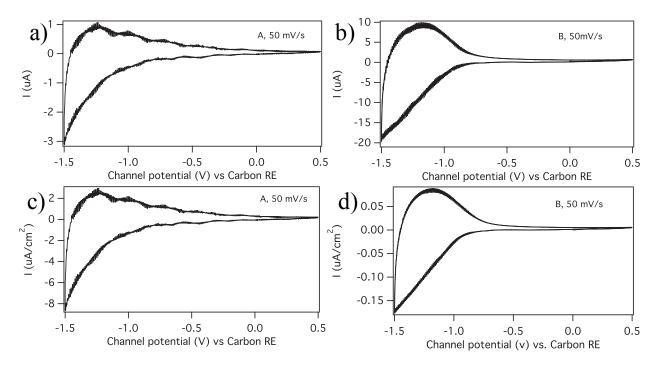

| I<br>t       | e 5-3: Cyclic voltammetry of TiO <sub>2</sub> films for evaporated devices type A (a,c) and solution processed type B (b,d). A TiO <sub>2</sub> film included between source and drain electrodes, acts as the working electrode and the carbon gate acts as the counter and the quasi reference electrode. For (c,d) the current is normalized to the surface area of the TiO <sub>2</sub> films in contact with the electrolyte. The measurements were carried out at scan rate 50 mV/s using [EMIM][TFSI] as the electrolyte.                                                                                        |

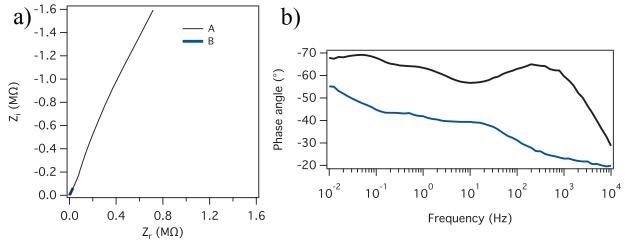

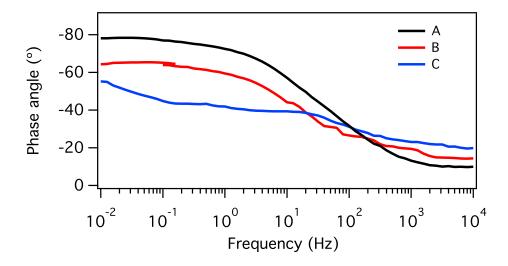

| Figure 5-4: Nyquist plots obtained in transistor configuration using dense (A) and porous (B)                          |

|------------------------------------------------------------------------------------------------------------------------|

| films of TiO2 included between source and drain as the working electrode and carbon as the                             |

| counter and quasi reference electrode. (b) Phase angle vs frequency of the same devices. In                            |

| samples A the film has a geometric surface area of 0.4 cm <sup>2</sup> , in samples B the BET surface                  |

| area is of 170 cm <sup>2</sup> . The measurements were carried out at 1 V vs carbon quasi reference                    |

| electrode, using [EMIM][TFSI] as the electrolyte                                                                       |

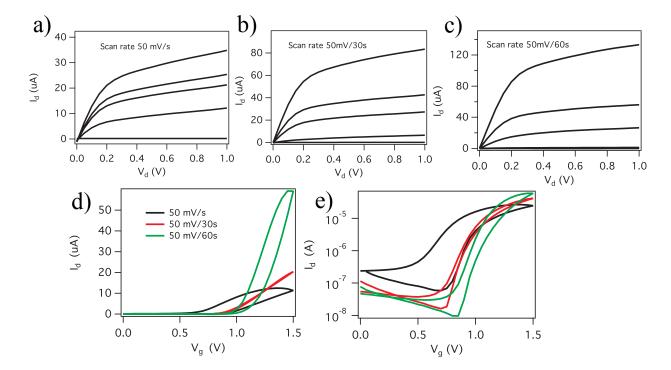

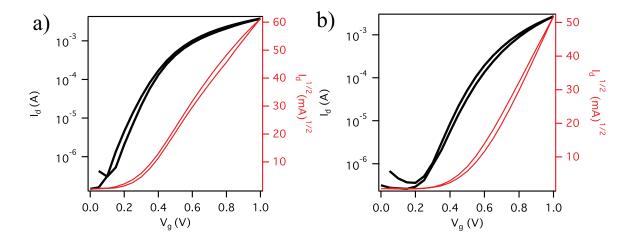

| Figure 5-5: Output characteristics at $V_g = 0$ V, 1 V, 1.2 V, 1.3 V, 1.5 V at sweeping rate (a) 50                    |

| mV/s; (b) 50 mV/30s and (c) 50 mV/60s. (d) Transfer characteristics at $V_d$ = 200 mV; (e)                             |

| transfer characteristics at $V_d$ = 1V of evaporated TiO <sub>2</sub> TFTs with [EMIM][TFSI] Lithium                   |

| perchlorate as gating medium (device C)                                                                                |

| Figure 5-6: Output characteristics at $V_g = 0$ V, 1 V, 1.2 V, 1.3 V, 1.5 V at sweeping rate (a) 50                    |

| mV/s; (b) 50 mV/30s and (c) 50 mV/60s. (d) Transfer characteristics at $V_d$ = 200 mV; (e)                             |

| transfer characteristics at $V_d = 1V$ of porous solution processed $TiO_2$ TFTs with                                  |

| [EMIM][TFSI] Lithium perchlorate as gating medium (device D)                                                           |

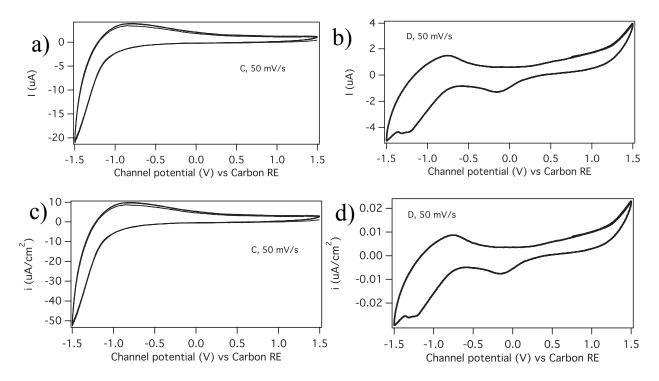

| Figure 5-7: Cyclic voltammetry of TiO <sub>2</sub> films for devices type C (a,c) and D (b,d). A TiO <sub>2</sub> film |

| included between source and drain electrodes acts as the working electrode and the carbon                              |

| gate acts as the counter and the quasi reference electrode. For (c,d) the current is normalized                        |

| to the surface area of the TiO2 films in contact with the electrolyte. The measurements were                           |

| carried out at scan rate 50 mV/s using [EMIM][TFSI]+Lithium perchlorate as the                                         |

| electrolyte                                                                                                            |

### LIST OF SYMBOLS AND ABBREVIATIONS

a-GSZO Amorphous gallium tin zinc oxide

a-HfO<sub>2</sub> Amorphous hafnium oxide

Ag Silver

AIZO Aluminum indium zinc oxide

Al<sub>2</sub>O<sub>3</sub> Aluminium oxide

ALD Atomic layer deposition

Au Gold

AZO Aluminum zinc oxide

BC-BG Bottom contacts - bottom gate

BC-TG Bottom contacts - top gate

BJT Bipolar junction transistor

C Capacitance

C gate medium Cpecific capacitance of dielectric

CB Conduction band

CdS Cadmium sulphide

C<sub>ov</sub> Overlap capacitance

CV Cyclic voltammetry

[DEME]-[TFSI] N,N-diethyl- N-(2-methoxyethyl)- N-methylammoniumbis-

(trifluoromethylsulfonyl)-imide

D Drain electrode

d Thickness of the insulator

[EMIM][TFSI] 1-ethyl-3-methylimidazolium

bis(trifluoromethylsulfonyl)imide

E<sub>g</sub> Band-gap energy

EGT Electrolyte gated transistors

$E_x(x)$  Electric field

FET Field effect transistor

f<sub>t</sub> Transit frequency

G Gate electrode

Ga Gallium

g<sub>m</sub> Transconductance

HRTEM high resolution transmission electron microscopy

I<sub>d</sub> Drain current

I<sub>dsat</sub> Saturation drain current

IGZO Gallium tin zinc oxide

I<sub>off</sub> Current in off state of transistor

I<sub>on</sub> Current in on state of transistor

ITO Indium tin oxide

IZO Indium zinc oxide

k Boltzmann constant

L Channel length

Li Lithium

$L_{overlap}$  Width of overlapping electrodes

MeO Metal oxide

MOCVD Metal oxide chemical vapor deposition

MOSFET Metal-oxide-semiconductor field-effect

MPa Mega pascal

NaOH Sodium hydroxide

N<sub>t</sub> Total trap density

PANI Polyaniline

PBS Phosphate-buffered saline

PEDOT:PSS Poly(3,4-ethylenedioxythiophene):polystyrenesulfonate

PEN Polyethylene naphthalate

PET Polyethylene terephthalate

PI Polyimide

Pt Platinum

PVA Poly(vinyl alcohol)

q Elementary charge

Q Mobile charges

R<sub>c</sub> Contact resistance

S Source electrode

S<sub>3</sub>N<sub>4</sub> Trisulfur tetranitride

Sb Antimony

$SnO_2$  Tin dioxide

Ta<sub>2</sub>O<sub>5</sub> Tantalum pentoxide

TC-BG Top contacts - bottom gate

TC-TG Top contacts - top gate

TFT Thin film transistor

Ti Titanium

TiO<sub>2</sub> Titanium dioxide

VB Valence band

V<sub>d</sub> Drain voltage

V<sub>eff</sub> Effective voltage

$V_{\rm g}$  Gate voltage

V<sub>th</sub> Threshold voltage

W Channel width

WO<sub>3</sub> Tungsten trioxide

WO<sub>4</sub> Orthotungstate

W<sub>overlap</sub> Length of overlapping electrodes

Y<sub>2</sub>O<sub>3</sub> Yttrium oxide

$Zn(OAc)_2$  Zinc acetate

Zn(OH)<sub>2</sub> Aqueous ammonia

$Zn_2^+$  Zinc ion

ZnO Zinc oxide

ZnO:Li Lithium - doped zinc oxide

ZnO•xH<sub>2</sub>O ZnO hydrate

ZrO<sub>2</sub> Zirconium dioxide

ZrO<sub>x</sub> Zirconium oxide

ZTO Zinc tin oxide

ε Vacuum permittivity

$\varepsilon_s$  Permittivity of semiconductor

μ Charge carrier mobility

# LIST OF APPENDICES

| APPENDIX A – SUPORTING INFORMATION FOR THE ARTICLE 1     | 95  |

|----------------------------------------------------------|-----|

| APPENDIX B – SUPPORTING INFORMATION FOR THE ARTICLE 2    | 109 |

| APPENDIX C – LIST OF PUBLICATIONS IN POLYTECHNIQUE MONTR | EAL |

| NOT INCLUDED IN THE THESIS                               | 117 |

| APPENDIX D – PARTICIPATION IN THE CONFERENCES            | 118 |

### **CHAPTER 1 INTRODUCTION**

The objectives of this chapter are to give a brief overview of transistor technology as well as the structure and the working principle of thin film transistors (TFT). In particular, I will discuss metal oxides used in this work as semiconductor materials and electrolyte gating principles.

# 1.1 History of transistors

The first reported transistors were based on field effect. In 1925, the Austro-Hungarian physicist Julius Edgar Lilienfeld patented the operating principles of field effect transistors (FET).[1] The first field effect transistor was patented in 1934 by the German Physicist Oscar Hale.[2] In 1959 scientists from Bell Labs manufactured a metal-oxide-semiconductor field-effect transistor (MOSFET). The first MOSFETs were commercialized in 1963.[3]

Meanwhile, in 1947, the Bell Labs scientists John Bardeen, William Shockley and Walter Brattain invented the point contact transistor, one of the type of bipolar junction transistor (BJT).[4, 5] By means of a simple device, consisting of a paper clip, a small amount of germanium and golden foil, they could amplify an input current by 100 times. In the point contact transistor the low current input terminal is emitter and amplified current output is between base and collector. In 1951 they invented bipolar junction transistor, which is used up till now. In this transistor, the input terminal is base and the amplified current is collected between emitter and collector. In 1956 they were awarded the Nobel Prize in Physics for their "researches on semiconductors and their discovery of the transistor effect".[6] In 1954, J. Bardeen and W. H. Brattain reported that gaseous ionic species adsorbed on germanium surface causes a change in the surface dipole and hence the conductivity of the germanium, leading to the development of gas sensors.[7] In 1955, their experiment was extended by to the surface of germanium electrodes in contact with aqueous electrolytes. This experiment is often considered as the first example of electrolyte gating.[8]

Early transistors were connected as individual components to other elements like resistors, diodes, capacitors and others on the board to make a circuit. In 1958, to make these circuits boards faster, Jack Kilby proposed the idea that all circuit components can be formed on one semiconductor crystal adding only the interconnections. Later, he fabricated two transistors on

the same silicon crystal leading to the first integrated circuit. Nowadays, it is possible to fit more than a billion transistors on a single crystal. Jack Kilby was awarded the Nobel Prize in Physics for the invention of the integrated circuit in 2000.[6]

The first thin film FET was developed in the RCA laboratory by Weimer in 1961. Polycrystalline cadmium sulphide (CdS) was the material used for the semiconducting thin-film and silicon monoxide, SiO, was the insulator.[9] In 1964, the first metal oxide (MeO) TFT, using evaporated SnO<sub>2</sub> as the semiconductor, was introduced by Klasens.[10] Later, TFTs with SnO<sub>2</sub> deposited by vapor phase reactions were introduced in 1970 by Aoki.[11] Single crystal lithium- doped zinc oxide (ZnO:Li) TFTs hydrothermally grown from solution had a very good electrical properties, such as hall mobility 220 cm<sup>2</sup>/Vs.[12]

With the invention of a transistor the techno-science progress was spinned with a new force. In the 1950s the first transistor radio was produced. In 1960, the first fully transistorized portable television appeared. In 1971, the first pocket calculator was fabricated. In 1983, after the invention of the mobile phone, the era of mobile communication began. Today, transistors are facing an explosive evolution towards the light weight, flexible, stretchable and biocompatible electronics for many applications, such as wearable and textile integrated systems [13-17], flexible and rollable displays [18, 19], medical implants [20] and artificial skin [21, 22] among others.

# 1.2 Thin film transistors

A thin film transistor (TFT) is a transistor where metal contacts and semiconductor material are deposited as thin films. The semiconductor film is separated from the gate electrode (G) by an electrically insulating dielectric. Source (S) and drain (D) electrodes, of given channel width (W) and length (L), inject charges into the semiconductor. TFTs can use several semiconductor materials, such as silicon, compound semiconductors, carbon nanotubes, metal oxides or organic semiconductors.[23-29]

The working principles of TFTs, their characteristics and components will be described below. All transistors components have an influence on the transistor characteristics and should be optimized for different applications.

# 1.2.1 Working principle of thin film transistors

Figure 1.1 represents the working mechanism of a thin film field effect transistor. A gate electrode, insulator and semiconductor form a capacitor. By applying, for example, a positive voltage,  $V_g$ , to the gate, while the source electrode is grounded, negative charge carriers start to accumulate in the channel. When the gate-source voltage exceeds the threshold voltage ( $V_g > V_{th}$ ) the channel becomes conductive.

If a voltage is applied between the drain and the source  $(V_d)$ , a current starts to flow between the two electrodes (drain-source current,  $I_d$ ). By gradually increasing  $V_d$ , the source-drain current increases till reaching a saturation point, this region is called a linear region due to linear increase of current. When  $V_d$  exceeds the effective gate voltage,  $V_{eff}$  ( $V_d > V_g - V_{th}$ ), the gate potential gets compensated by the drain potential and the channel is pinched off at the drain. This means that the transistor reaches the saturation regime, where further increase in  $V_d$  does not affect  $I_{dsat}$ .

Further increase of the  $V_d$  will only move the pinch off point closer to the source, thus shortening the channel length. The current will still be flowing from the drain to the source but will not increase, since the depletion region near the drain is lacking the majority charge carriers. The current will be sustained by the carriers injected directly from the electrode. The current flowing in the depletion region is called space-charge limited current and depends only on mobility and not on the charge carrier density. The gate voltage should regulate the distribution of charges within the channel. In the case of short channel devices, the drain field becomes stronger than the gate potential and the gate can not control the current in the transistor. Thus, the space-charge limited current will prevent saturation. So the channel length of transistor should be several times the thickness of dielectric.[30]

Figure 1-1: Schematic illustration of operating regimes of field effect transistors: (a) linear regime; (b) saturation regime at pinch-off; (c) corresponding current voltage characteristics.

The specific capacitance of the gate insulator is given by the formula:

$C = \frac{\varepsilon kA}{d}$ , where  $\varepsilon$  is the vacuum permittivity, k is the relative permittivity (dielectric constant), A is the area and d is the thickness of the insulator.

Therefore, the mobile charge density can be calculated from the following formula:

$$Q = C(V_g - V_t).$$

This charge density is given when  $V_d = 0$ . As soon as the drain voltage increases, the charge density will be a function of the distance from the source. The potential will gradually increase from the source to the drain and the charge density can be given as follows:

$$Q(x) = C \left( V_g - V_t - V(x) \right).$$

We can then derive the general formula for the drain current:

$I_d = W \mu Q(x) E_x(x)$ , where  $E_x(x)$  is an electric field in the direction of x.

Substituting  $E_x(x) = \frac{dV(x)}{dx}$  and Q(x) into this formula and integrating over x we get the following relationship:

$$I_d = \frac{W\mu C}{L} \left( \left( V_g - V_t \right) V_d - \frac{V_d^2}{2} \right).$$

Knowing that in the linear mode  $V_d \ll V_g$ - $V_t$  and in the saturation mode  $V_d = V_g$ - $V_t$  the above equation can be simplified to the following:

Linear:

$$I_d = \frac{W\mu C}{L} (V_g - V_t) V_d$$

,

Saturation:

$$I_d = \frac{W\mu C}{2L} (V_g - V_t)^2$$

.

# 1.2.2 Main characteristics of thin film transistors

The charge carrier mobility describes the efficiency of the charge carrier transport, i.e. how fast carriers can travel through the semiconductor. This parameter can be derived from  $I_d$  in the linear and saturation regimes. The charge carrier mobility values in saturation regime tell us about the efficiency of charge carrier transport when channel is formed, while in linear regime channel can be still in formation process. If contacts are ohmic the charge carrier mobility in linear and saturation regimes should be quite similar due to the same amount of charges in both regimes.

Linear :

$$\mu_{lin} = \frac{L}{WCV_d} \frac{dI_d}{dV_g}$$

.

Saturation :

$$\mu_{sat} = \frac{2L}{WC} \left( \frac{d\sqrt{I_{dsat}}}{dV_q} \right)^2$$

.

The charge carrier mobility in TFT configuration is usually different from intrinsic mobility, which is typically determined by the Hall effect in the bulk material. Charge transport in TFTs occurs in a narrow channel region close to the gate dielectric/semiconductor interface, where different sources of scattering are taking place, such as Coulomb scattering from dielectric charges, surface roughness scattering and others.[31]

The channel current on/off ratio ( $I_{on}/I_{off}$  ratio) is the ratio between the channel current in the on state and the current in the off state of the transistor, which is typically extracted from the transfer curves. The off current increases the static power consumption, so minimizing it is important.

Transistors can operate in enhancement (accumulation) or depletion mode. In absence of an applied  $V_g$ , enhancement mode transistors are in the off state ( $I_d \approx 0$ ), while depletion mode transistors are in the on state ( $I_d \neq 0$ ) and application of a  $V_g$  is needed to turn them off. Enhancement mode transistors decrease the free-running power consumption and are thus preferred for applications in circuits and display technology.

Another important parameter of TFTs is the threshold voltage ( $V_{th}$ ), i.e. the minimum gate voltage required for a drain source current to flow when the transistor channel is formed. The  $V_{th}$  depends on the semiconductor material as well as the type of dielectric, their interface, defect states, impurities and device geometry. [Veres, 2004] The most common methods to determine  $V_{th}$  is linear extrapolation from  $I_d$  versus  $V_g$  curves at low  $V_d$  (transfer curves in linear regime) or linear extrapolation from  $\sqrt{I_d}$  vs  $V_g$  curves at high  $V_d$  (transfer curves in saturation regime). When a n type transistor operates in the enhancement mode,  $V_{th}$  is positive, and negative in depletion mode of operation. Increasing the gate capacitance can reduce the threshold voltage. At higher capacitance more charges are induced in the channel making it conductive at lower voltages.

The transconductance,  $g_m$ , describes how the drain current is modulated by the gate voltage, and it is defined as:

$$\left[g_m = \frac{\partial I_d}{\partial V_g}\right]_{V_d}$$

The transconductance describes the behavior of the transistor at gate voltages above the threshold when the current originates from the drift of charges from source to drain. In the subthreshold regime ( $V_g < V_{th}$ ), the current is mostly originated by diffusion of charges. In this regime the important parameter is subthreshold swing.

The value of subthreshold swing is extracted from the plot of the logarithm of the drain current versus the gate voltage at a constant drain voltage (linear or subthreshold regime). It measures the amount of  $V_g$  change required to increase  $I_d$  by an order of magnitude in the subthreshold region. The subthreshold swing is represented by the following equation:

$$S = \frac{\partial V_g}{\partial log_{10}(I_d)}.$$

The knowledge of subthreshold swing can give information about the total defect density at the semiconductor dielectric interface.[32] The total trap density, N<sub>t</sub>, can be found from the equation:

$N_t = \left[ \left( \frac{S \log(e)}{kT/q} - 1 \right) C \right] \frac{1}{q^2 \varepsilon_s}$ , where, k is the Boltzmann constant, q is the elementary charge,  $\varepsilon_s$  is the permittivity of the semiconductor and C the dielectric capacitance.[33]

# 1.2.3 Thin film transistor configurations

Transistor performance significantly depends on the device configuration. The four main transistor configurations are presented in Figure 1.2.

Figure 1-2: Schematic illustration of thin film transistor configurations: bottom contacts - bottom gate (a, BC-BG), bottom contacts - top gate (b, BC-TG), top contacts - bottom gate (c, TC-BG) and top contacts - top gate (d, TC-TG).

In these device configurations, the injected charges travel different distances to reach the semiconductor/dielectric interface, i.e. the region where charge transport takes place. For instance, in the BC-BG and TC-TG configurations charges are injected directly close to the semiconductor/dielectric, whereas, in the BC-TG and TC-BG structures the injected charges must travel through the whole thickness of the semiconductor to reach the channel. Thus, the device configuration can affect the main figures of merit of the transistor, such as the threshold voltage and the charge carrier mobility. For instance, a large surface of the source and drain electrodes

overlapping the gate electrode can result in improved charge injection, leading to a small contact resistance.[34]

# 1.2.4 The contact resistance and overlap capacitance

Charge exchange (injection and extraction) depends on the workfunction of electrode and the bandgap of the semiconductor. When the workfunction of the electrode is close to the conduction or valence bands of the semiconductor the charges are easily injected and the contacts are called ohmic. A mismatch between the workfunction and the conduction band is called an injection barrier (Schottky barrier). This introduces a resistance to the transistor (contact resistance, Rc). The contact resistance can be significantly larger than the channel resistance depending on the channel length, applied voltage and mobility of the carriers. So, it is especially important to control Rc in short channel devices ( $L \le 5$ um) as it dominates over the total resistance and leads to degradation of electrical properties.[33]

The contacts materials in transistors are high work function metals such as Au, Ag, Pt. Conducting polymers, such as PEDOT:PSS, PANI [35-37], graphene and carbon nanotubes, can also be used.[38, 39] The high aspect ratio and 1D structure of carbon nanotubes facilitates charge carrier injection by tunneling and their low density of states provides a lever to further reduce the Schottky barrier height and width.

The overlap capacitance  $(C_{ov})$  is the capacitance between the overlapping parts of source-drain contacts with the gate and it doesn't depend on the applied potential. It can be found by the formula:

$C_{ov} = (L \cdot W)_{\text{overlap}} \cdot C_{\text{gate medium}}$ , where  $L, W_{\text{overlap}}$  is the length and width of overlapping electrodes and  $C_{\text{gate medium}}$  is the specific capacitance of dielectric.

The total capacitance of the transistor is:

$C_{total} = C_{channel} + C_{ov}$ , where  $C_{channel}$  is a capacitance between gate electrode and channel responsible for transistor operation.[40]

In the case of high-k dielectric materials or electrolytes as a gating media, the total capacitance is high enough that the overlap capacitance becomes negligible. The overlap capacitance directly influences the transit frequency of transistors, (f<sub>t</sub>), which quantifies the speed of the device.[41]

# 1.3 Electrolyte gated thin film transistors

A high operating voltage (tens of volts) is typically needed in conventional TFTs, due to the low capacitance. Typical dielectric materials, such as  $SiO_2$  (k~3.9) or  $S_3N_4$  (k~7) or others, possess capacitance density in the range of  $0.005\sim0.5~\mu F~cm^{-2}$ , depending on the thickness and dielectric constant.[42-44] Reducing the thickness of conventional dielectrics to achieve high capacitance can lead to high leakage current and reliability issues. The use of high-k dielectric materials such as  $ZrO_2$  (k~20),  $Ta_2O_5$  (~25), or  $TiO_2$  (~40) can increase the capacitance without significant gate current leakage.[45]

Another way to achieve a high capacitance and charge carrier density modulation is electrolytegating [46-49], where the gate dielectric is replaced by an electrolyte. By applying a gate voltage, the electrolyte ions redistribute at the electrolyte/semiconductor interface, forming a thin electrical double layer (EDL). The small thickness of the double layer ( $\sim$ 1nm) formed on the electrolyte semiconductor interface leads to high capacitance (typically 1-10  $\mu$ F/c²), which allows the transistor to operate at low voltages (less than 2 V).[50, 51]

The mode of operation of electrolyte-gated transistors is mainly governed by one or the two doping processes described below: electrostatic and/or electrochemical.[52, 53] For semiconductors, which are impermeable to ions, the double layer forming at interface with the electrolyte results in a gating mechanism similar to that taking place in field effect transistors (electrostatic, as shown on Figure 1.3a). For semiconductors which are permeable to ions, upon application of gate voltage, ions can have reversible redox reactions on the surface (electrosorption) or ions can enter the film leading to reversible redox reactions (intercalation), thus changing the charge carrier density and hence the conductivity of the film (as shown on Figure 1.3b).[54] It is worth noting that, in real devices, electrostatic and electrochemical doping may occur at the same time.[49, 55]. This faradaic charge transfer is called pseudocapacitance.

Figure 1-3:Schematic illustration of an electrolyte gated thin film transistors operating in field effect (a) and electrochemical mode (b).

The gate electrode, electrolyte and semiconductor as a second electrode form a capacitor. The electrolytic capacitance depends on the applied potential and frequency. It can be examined by impedance spectroscopy or cyclic voltammetry.[46, 56, 57] The equivalent circuit for such capacitor structure can be modeled as two resistor-capacitor (RC) circuits in series, see figure 1.4. One RC is related to the bulk of electrolyte and another one is related to the double layer.[58] [Yuan, 2010] Each RC circuit has a specific frequency domain and can be identified from the Bode plot (phase angle vs. frequency). At high frequencies (above 100 kHz) there is a bulk capacitive region (polarization of the bulk electrolyte); for the frequency range (10kHz to 1Hz) there is a EDL capacitive region, and below 1 Hz there is a EDL pseudocapasitive region (related to chemical processes on the electrolyte/semiconductor interfaces).

The total capacitor impedance (Z) is the sum of the real part (Z') and imaginary part (Z''):

Z = Z' + iZ'', where i is the imaginary unit.

When the electrolyte exhibits capacitive behavior at low frequency and resistive behavior at high frequency, the total impedance depends on the ohmic resistance R and on the electric double layer capacitance  $C_{EDL}$ :

$Z = R + i2\pi f C_{EDL}$ , where f is the frequency and  $C_{EDL}$  is the capacitance of the electric double layer.

The imaginary part of the impedance is inversely proportional to the capacitance, thus  $C = 1/(2\pi f Z'')$ .

The capacitance can also be calculated from cyclic voltammetry, where the integration of

voltametric current over time provides the amount of doping charges Q. And, capacitance can be deduced from the slope of the (linear) plot of the doping charge vs. potential: C = Q/V.

Figure 1-4: Example of the Bode plot (θ-*f*) in Pt/IL/Pt structure. Inset: equivalent electric circuit, two resistor-capacitor (RC) circuits in series. (b) The Bode plot of ZnO EDL transistor. I: bulk IL capacitive region. II: electrostatic EDL capacitive region; III: electrochemical pseudocapacitive region. Reprinted with permission from [58]. Copyright 2010 American Chemical Society.

# 1.4 Metal oxides (TiO<sub>2</sub> and SnO<sub>2</sub>) as semiconductors

Metal oxides (MeO) are among the most popular channel materials in transistors, especially in next generation flexible and transparent transistors, due to their superior electrical properties and high reliability.[46, 59] The more utilized metal oxides in optoelectronic applications are transition and post transition metal oxides. The transition metals exhibit multiple oxidation states. Their compounds in higher oxidation states are strong oxidizing agents, as they tend to accept electrons to reach a stable lower oxidation state.

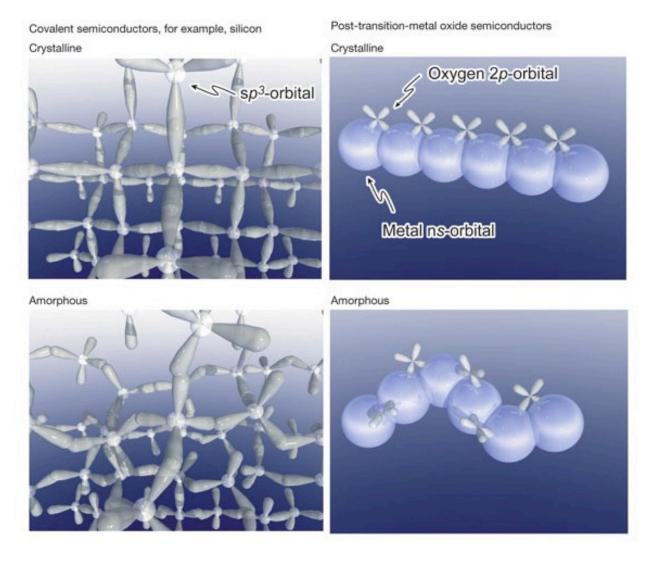

Electronic structures and charge transport mechanisms of metal oxides are quite different from conventional covalent semiconductors like silicon. CB of silicon formed by  $sp^3$   $\sigma$ -bonding and VB by  $sp^3$   $\sigma^*$ -antibonding, and the band gap is the energy difference between them. In this case, any structural change will influence the charge transport decreasing the charge mobility. For instance, at a carrier density of  $10^{19}$  cm<sup>3</sup> the electron mobility in a single crystalline and amorphous silicon is around 200 cm<sup>2</sup>/Vs and 1 cm<sup>2</sup>/Vs, respectively.[60] In metal oxides the band structure is different. The conduction path in crystalline and amorphous covalent semiconductors and post transition MeOs is shown in Figure 1.5.

Figure 1-5: Schematic illustration of orbitals for the carrier transport paths in crystalline and amorphous covalent semiconductors and post transition MeOs. a) the band structure in covalent semiconductors, like silicon, consists of overlapping sp<sup>3</sup> orbitals, so structural randomness greatly

degrades the magnitude of bond overlap. b) In post transition oxide semiconductors, spheres represent metal s orbitals (conduction band), the contribution of 2p orbitals (valence band) is small. The spread of metal s orbitals is high and their overlap doesn't significantly affected in amorphous state. Reprinted with permission from [60] © Nature Publishing Group, 2004.

In most metal oxide semiconductors, due to the high electronegativity of O, there are covalent bonds with a strong degree of ionicity. The ionicity creates an electronic structure where 2p orbitals of O form the valence band (VB) and the highest occupied metal orbitals form the conduction band (CB). In the case of transition metals, the conduction band consists of localized d orbitals. In the case of post transition metals, the conduction band consists of delocalized ns (n  $\geq$  4) orbitals.[60, 61] The overlap of big s orbitals is insensitive to distorted metal-oxygen-metal bonds in amorphous state.[62] Thus, the charge carrier mobilities of amorphous post transition MeOs can be similar to ones of crystalline.

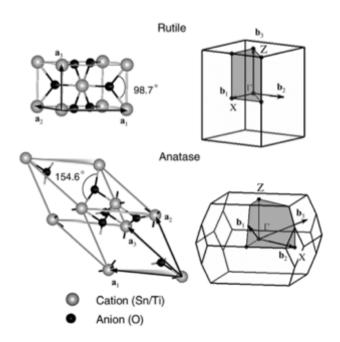

In this work, I studied the main representatives of binary transition and post transition metal oxides  $TiO_2$  and  $SnO_2$ , respectively. They possess similar crystal structures (Figure 1.6) and chemical bonds, and are comparable in electronic band-gap energies ( $E_g \approx 3-4$  eV). However, the electronic properties are quite different. The  $TiO_2$  has weak electron conductivity and optical absorption to UV light. While  $SnO_2$  combine electrical conductivity and optical transparency to visible light.[61, 63]

Figure 1-6:The crystalline structures and Brillouin zones of rutile  $D_{4h}^{14}$  and anatase  $D_{4h}^{19}$ . Reprinted with permission from [61]. © AIP Publishing LLC, 2013.

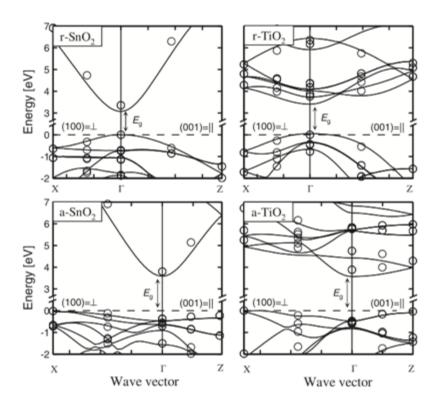

These differences can be described by their band structure. The VB formed by 2p orbitals of O are the same for all MeOs. The difference of CB, formed by Me cations, with electron configurations  $5s^25p^2$  for Sn and  $3d^24s^2$  for Ti gives rise to a single high dispersive CB for SnO<sub>2</sub> and to the several flat dispersed CBs for TiO<sub>2</sub>, see Figure 1.7. The overlap of high spread 5s orbitals is responsible for the delocalization of electrons in SnO<sub>2</sub> making the conduction band dispersive and responsible for higher conductivity. While in TiO<sub>2</sub>, the electrons are strongly localized in 3d orbitals making the CB flat dispersive. [60, 61]

Figure 1-7:Electronic structures of r-  $SnO_2$ , r-  $TiO_2$ , a-  $SnO_2$ , and a-  $TiO_2$  along two main symmetry directions (100) \_|\_ and (001) ||. Reprinted with permission from [61]. © AIP Publishing LLC, 2013.

### 1.5 Problem identification

The electrical characteristics of electrolyte-gated transistors depend on the device structure, the effective potential of gate electrode and the doping level of the semiconductor channel.

Understanding the electrical transport mechanisms in electrolyte-gated transistors is an ongoing challenge to design devices with better electronic performance. Moreover, the role played by the extension of the electrolyte/semiconductor and electrode/semiconductor interfaces on the doping and charge carrier transport processes requires deeper investigation. The overlap between the metal electrodes and the semiconductor, which is in contact with the electrolyte, might affect the charge injection process. Another challenge in the fabrication of high performance TFTs for flexible electronics, is the required low processing temperature (150 °C in the case of polyethylene naphthalate (PEN) substrates, maximum 350 °C for polyimide (PI) substrates).

# 1.6 General Objectives

The general objective of this Ph.D. thesis is the design, fabrication, and characterization of metal oxide electrolyte gated transistors based on TiO<sub>2</sub> and SnO<sub>2</sub>.

The objective was accomplished by tuning the structure and the morphology of semiconductor materials (SnO<sub>2</sub> and TiO<sub>2</sub>) as well as by selecting the appropriate gating media. To control the charge carrier density and understand the doping mechanism in the electrolyte gated TFT, patterning of the semiconductor material with different overlap of source-drain electrodes was implemented. SnO<sub>2</sub> TFTs were also fabricated on PI substrate and their electrical and mechanical properties were investigated to show high performance TFT for applications in flexible electronics.

#### 1.7 Motivation

Environmentally friendly and abundant metal oxides as SnO<sub>2</sub> and TiO<sub>2</sub> are promising transistors channels for flexible displays, medical implants and sensors, wearable electronics etc. Electrolyte gating allows TFTs to work at low voltages, which is critical for bio applications. Fabrication of high performance electrolyte gated TFTs and shedding light on their electrical, electrochemical and mechanical properties make an invaluable contribution to bio and flexible electronics.

# 1.8 Specific objectives

To achieve the main objective the following specific objectives need to be achieved:

1. Charge carrier density modulation of metal oxide thin films for electrolyte gated transistors and exploring the doping mechanisms