|                   |                                                                                                                                                                                                                                                                                                                        |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Titre:</b>     | Contributions à la modélisation et à la validation des modèles de liaisons HVDC de Type VSC-MMC dans les outils de simulation temps réel                                                                                                                                                                               |

| Author:           | Sébastien Dennetière                                                                                                                                                                                                                                                                                                   |

| <b>Date:</b>      | 2017                                                                                                                                                                                                                                                                                                                   |

| <b>Type:</b>      | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                                                              |

| <b>Référence:</b> | Dennetière, S. (2017). Contributions à la modélisation et à la validation des modèles de liaisons HVDC de Type VSC-MMC dans les outils de simulation temps réel [Ph.D. thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/2471/">https://publications.polymtl.ca/2471/</a> |

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/2471/>

PolyPublie URL:

**Directeurs de recherche:** Jean Mahseredjian

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

CONTRIBUTIONS A LA MODELISATION ET A LA VALIDATION DES

MODELES DE LIAISONS HVDC DE TYPE VSC-MMC DANS LES OUTILS

DE SIMULATION TEMPS REEL

SÉBASTIEN DENNETIÈRE

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR

(GÉNIE ÉLECTRIQUE)

FÉVRIER 2017

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée :

CONTRIBUTIONS A LA MODELISATION ET A LA VALIDATION

DES MODELES DE LIAISONS HVDC DE TYPE VSC-MMC

DANS LES OUTILS DE SIMULATION TEMPS REEL

présentée par : DENNETIÈRE, Sébastien

en vue de l'obtention du diplôme de : Philosophiae Doctor

a été dûment acceptée par le jury d'examen constitué de :

M. KOCAR Ilhan, Ph.D., président

M. MAHSEREDJIAN Jean, Ph.D., directeur de recherche

M. KARIMI Houshang, Ph.D., membre

M. FORTIN-BLANCHETTE Handy, Ph.D., membre externe

## REMERCIEMENTS

Cette thèse de doctorat a été un long processus de recherches, d'apprentissages, de remises en question et de découvertes avec de nombreuses personnes que je souhaite ici remercier.

Tout d'abord, Jean Mahseredjian a été le principal instigateur pour que je me lance dans cette aventure. Je tiens à lui exprimer ma gratitude d'avoir toujours cru dans ce projet et d'y avoir apporté un soutien indéfectible. Depuis maintenant plus de 15 ans, sa rigueur intellectuelle, sa passion pour la science et sa folie du travail guident ma démarche professionnelle. Mes remerciements vont également à Hani Saad pour son expertise sur les systèmes MMC et son aide à structurer cette thèse. Ses convictions dans ce domaine m'ont donné de beaux défis à relever. La contribution de Tarek Ould Bachir doit également être soulignée plus particulièrement pour sa patience à m'expliquer le domaine mystérieux de l'implémentation sur FPGA.

Cette thèse a été réalisée dans le cadre de mon activité professionnelle à RTE. Je tiens ainsi à souligner le soutien de Louis Sozzi, Patrick Auzary, David Landier, Bertrand Clerc et Samuel Nguefeu qui m'ont facilité la réalisation de ce travail malgré les contraintes d'organisation et de priorisation dans l'entreprise. J'ai bien conscience de la chance qui m'a été donnée de réaliser cette thèse dans le cadre de mon travail.

J'aimerais également remercier l'équipe de développement d'Hypersim chez OPAL-RT et à l'IREQ pour leur aide à rendre ce logiciel fonctionnel. Mes remerciements vont aussi à Wei Li, Xiao Xiao et Jean Bélanger pour leur support dans l'utilisation des plateformes FPGA.

Pour finir sur une note plus personnelle, je dois remercier mes parents de m'avoir donné la chance de croire que tout est possible dans la vie si nous en avons la volonté. Finalement, je n'aurais jamais pu réaliser cette thèse sans le soutien, l'amour et la patience de ma femme Mathilde qui a dû faire de nombreux renoncements durant cette période. Merci également à nos enfants Eloïse, Félix et Antoine d'avoir laissé votre Papa faire des activités bien mystérieuses avec ses ordinateurs au lieu de jouer avec vous. Votre futur petit frère ou petite sœur n'aura pas à subir cette contrainte !

## RÉSUMÉ

Le développement des réseaux de transport d'électricité est actuellement en pleine mutation. La transition énergétique en cours depuis plusieurs années, se concrétise par la fermeture de nombreuses centrales de production au charbon ou au fioul, l'installation massive de centres de production éolien et photovoltaïque et enfin une stagnation, voire une diminution de la consommation d'électricité. Cette transition impacte tous les pays d'Europe si bien que les interconnexions sont de plus en plus soumises aux variations des productions renouvelables.

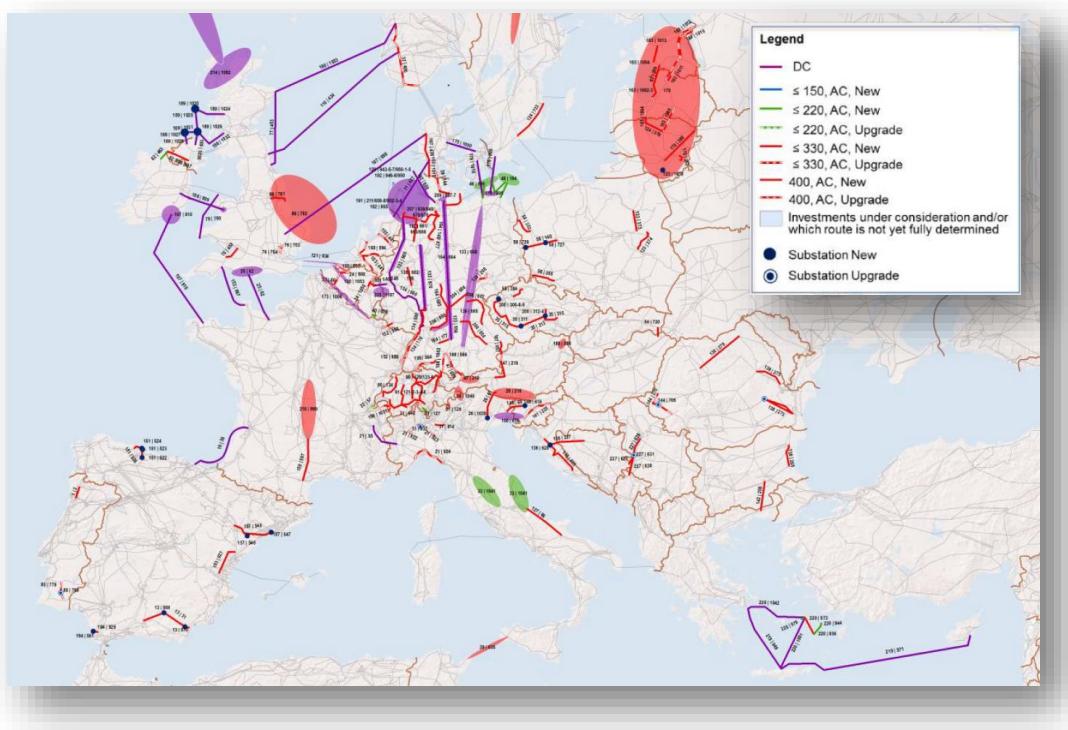

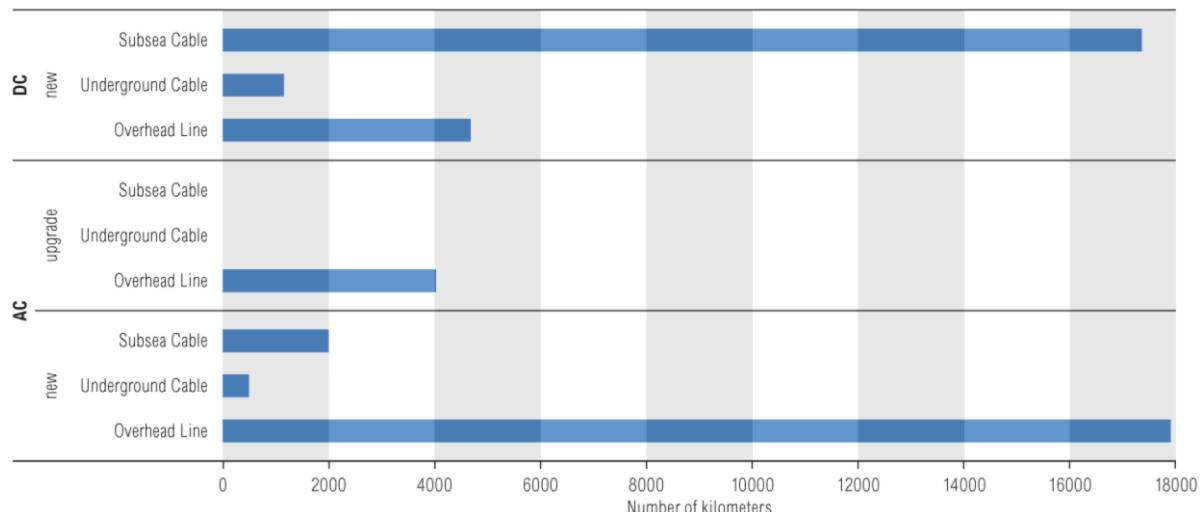

Cette évolution de la consommation et de la production impose l'installation de systèmes de contrôle des flux de puissance plus sophistiqués que ceux utilisés jusqu'à maintenant. On parle donc de plus en plus d'équipement à base d'électronique de puissance : liaisons à courant continu à haute tension (CCHT ou HVDC) et compensateur statique de puissance réactive. Les liaisons HVDC permettent en plus de répondre à la demande sociétale d'enfouir les ouvrages de transport d'électricité. Les réseaux de transport voient donc de plus en plus d'intégration de liaisons HVDC point à point. Le plan de développement du réseau européen ENTSO-E prévoit ainsi plus de 20 000 km de liaisons HVDC en 10 ans. Avec ce développement dans des zones relativement limitées (réseaux nationaux autour de la mer du Nord par exemple : Royaume Uni, France, Belgique, Pays-Bas, Danemark, Allemagne), la notion de réseaux à courant continu commence à se poser. Plusieurs projets de ce type de réseaux sont actuellement en cours d'étude de manière très avancée en Europe. En Chine deux réseaux HVDC sont désormais en exploitation.

Depuis maintenant plus de 20 ans, des liaisons VSC (Voltage Source Converter) à base de composants IGBT (Insulated Gate Bipolar Transistor) ou GTO (Gate Turn Off Thyristor) ont commencé à être installées. Elles étaient initialement synonymes d'onduleur autonome à modulation de largeurs d'impulsions et les commutations étaient réalisées à des fréquences de quelques centaines de Hz (voire quelques kHz pour les IGBT). La difficulté d'assembler des centaines de GTO/IGBT et de diodes en série pour former des valves à très haute tension (plus de 100 kV) et/ou le besoin de maîtriser les pertes par commutation dissipées dans ses convertisseurs ont conduit les constructeurs à privilégier des structures modulaires où de nombreux modules sont connectés en cascade. Les convertisseurs à multi-niveaux (MMC - Modular Multilevel Converter) vont de quelques dizaines de niveaux à plusieurs centaines en fonction de la technologie et du niveau de tension. Ce type de convertisseur est devenu en quelques années la solution quasi exclusive pour la conversion CA/CC à très haute tension en Europe. Des solutions à 400 kV voir 500 kV sont actuellement en cours de construction.

Afin de planifier l'installation de ces convertisseurs MMC et étudier leur fonctionnement dans des réseaux comportant une forte concentration d'électronique de puissance, il est nécessaire d'avoir des outils de simulation fiables. Les outils de simulation de transitoires électromagnétiques sont habituellement utilisés dans ce cadre car ce sont les outils les plus appropriés pour avoir une représentation détaillée des convertisseurs mais également de leur contrôle commande. En complément de ces outils, l'utilisation de la simulation temps réel associée à des répliques de contrôle commande s'impose de plus en plus comme un outil indispensable dans ce contexte.

C'est pour ces raisons que des laboratoires de simulation temps réel accueillant des répliques de contrôle commande ont été construits ou sont en cours de développement dans la plupart des zones intégrant des liaisons HVDC de manière massive. L'objectif est, pour certaines études spécifiques, de ne plus modéliser les systèmes de contrôle commande mais d'avoir les systèmes réels (avec les mêmes versions de logiciels que sur site) raccordés à des modèles de convertisseurs et de réseaux. Ces investissements conséquents seraient inutiles si les modèles temps réel étaient très approximatifs. La plus-value d'avoir les véritables systèmes de contrôle commande serait perdue. C'est pourquoi un soin particulier doit être apporté à la validation de ces modèles et à leur performance en temps réel.

Un des principaux objectifs de cette thèse est ainsi d'évaluer et si possible d'augmenter la précision des modèles MMC pour la simulation temps réel. Il est d'abord question de fournir des cas d'application dans un contexte industriel pour montrer les limites de certaines modélisations. Cette thèse permet également de mettre en lumière certaines limitations des modèles MMC détaillés. La validation des modèles MMC à l'aide de mesures réalisées sur des convertisseurs de forte puissance est aussi une contribution de cette thèse.

Des interfaçages entre simulateur temps réel et des systèmes de contrôle commande réels ont été développés dans cette thèse. Leurs performances temps réel et leur précision dans la plateforme de simulation complète ont été évaluées à l'aide de mesure sur site.

Afin de tester, valider et comparer des stratégies de contrôle commande et de protections adaptées aux réseaux à courant continu, il était nécessaire de développer des réseaux de test (ou benchmarks). Le deuxième volet de cette thèse a donc été de contribuer à la conception du réseau HVDC CIGRE qui est maintenant utilisé dans de nombreux groupes de travail et sert de base à des travaux de recherche dans ce domaine.

## ABSTRACT

Development of electrical transmission grids is presently undergoing radical changes. The energy transition towards renewable energy started a few years ago. It leads to closure of many coal-fired or oil-fired power plants, massive construction of photovoltaic plants and wind farms and a stagnation of electrical consumption. This transition has a huge impact in Europe on the electrical interconnections between countries. Sophisticated equipment to control power flow are now more and more required in this context. Power electronic based devices are often selected such as High-Voltage Direct Current transmission systems (HVDC) and Static Var Compensator (SVC). HVDC also offers a practical solution to the public demand to use underground cables instead of overhead lines. More and more HVDC point-to-point link are now integrated in transmission grids. More than 20,000 km of HVDC lines are expected in the 10-year ENTSO-E development plan. This development will occur in a limited area in Europe (national grid around the North Sea: United Kingdom, France, The Netherlands, Denmark, Germany) providing an opportunity to design HVDC grids. Several HVDC grids projects are now planned in Europe. In China, 2 HVDC grids are already in operation.

Voltage Source Converters (VSC) have been installed on transmission grids for more than 20 years. They have been limited until 2010 to the two-level and three level diode-clamped topology with switching frequencies around a few kHz. Several practical limitations as switching losses and difficulties in assembling very high voltage valves have been overcome by the modular technology called MMC (Modular Multilevel Converter). This topology consists of several sub-modules (SM) connected in series. Number of SMs per valve can go from a few tenth to several hundreds. MMC is now the quasi exclusive solution for AC/DCCC conversion on transmission grids in Europe. Technical solutions up to 400 kV and even 500kV DC are under construction.

In order to prepare the installation and analyze the behavior of MMC converters connected to grids with high penetration of power electronics based devices, reliable and accurate simulation tools are required. Electromagnetic Transient (EMT) tools are usually used in this context because they handle a detailed representation of converters and control systems. In addition to EMT offline simulation, real-time simulation with HVDC control systems replicas becomes more and more popular.

This is why, real-time simulation laboratories with replicas have been constructed or are planned in most of areas where HVDC is massively installed. The main objective of these tools,

is to avoid modeling of control systems and to use the physical hardware and same version of software than used on site. Real-time simulators and control systems replicas are quite expensive. These investments would be useless if converters modeled in real-time simulators were not accurate. The HVDC replicas added value would be quite limited in this case. This is why special care has to be taken to validate converter models and their performances in real-time simulation.

One of the main objective of this thesis is to evaluate and increase, when possible, precision of MMC models for real-time simulation. First, industrial test cases are provided to assess the limits of some modeling techniques. This thesis also highlights limitations of some detailed MMC models. Validation of MMC models with onsite measurements performed on an HVDC link in operation is also a contribution of this thesis.

Interfaces between real-time simulators and physical control systems have been developed in this thesis. Real-time performances and accuracy in a fully equipped platform have been compared against real measurements.

In order to test, validate and compare control and protection strategies adapted to DC grids, the development of a DC grid test system (or benchmark) was required. The second topic of this thesis was the design of the CIGRE DC grid which is now used by international working groups and serves as a basis for many research in this field.

## TABLE DES MATIERES

|                                                                                         |      |

|-----------------------------------------------------------------------------------------|------|

| REMERCIEMENTS .....                                                                     | III  |

| RÉSUMÉ.....                                                                             | IV   |

| ABSTRACT .....                                                                          | VI   |

| TABLE DES MATIERES .....                                                                | VIII |

| LISTE DES TABLEAUX.....                                                                 | XIII |

| LISTE DES FIGURES .....                                                                 | XIV  |

| LISTE DES SIGLES ET ABRÉVIATIONS .....                                                  | XX   |

| LISTE DES ANNEXES .....                                                                 | XXII |

| CHAPITRE 1 INTRODUCTION.....                                                            | 1    |

| 1.1 Motivation .....                                                                    | 1    |

| 1.2 Objectifs de la thèse .....                                                         | 5    |

| 1.3 Contributions de la thèse .....                                                     | 6    |

| 1.4 Liste des publications issues de ce travail .....                                   | 7    |

| 1.4.1 Chapitre de brochure .....                                                        | 7    |

| 1.4.2 Articles de journal .....                                                         | 7    |

| 1.4.3 Articles de conférence .....                                                      | 7    |

| CHAPITRE 2 TECHNOLOGIES HVDC ET SIMULATIONS DE TYPE EMT – REVUE DE LA LITTERATURE ..... | 9    |

| 2.1 L'essor des liaisons HVDC-VSC.....                                                  | 9    |

| 2.1.1 Les liaisons avec convertisseurs LCC et VSC .....                                 | 9    |

| 2.1.2 Avec des convertisseurs VSC à 2 ou 3 niveaux .....                                | 10   |

| 2.1.3 Avec des convertisseurs VSC de type MMC .....                                     | 11   |

| 2.2 Description de la topologie MMC.....                                                | 12   |

| 2.3 Les modèles EMT de convertisseurs MMC.....                                          | 15   |

| 2.3.1 Modèle 1 .....                                                                    | 15   |

|                                                                                                                       |           |

|-----------------------------------------------------------------------------------------------------------------------|-----------|

| 2.3.2 Modèle 2.....                                                                                                   | 15        |

| 2.3.3 Modèle 3.....                                                                                                   | 16        |

| 2.3.4 Modèle 4.....                                                                                                   | 18        |

| 2.4 Principes de résolution dans les outils de type EMT .....                                                         | 18        |

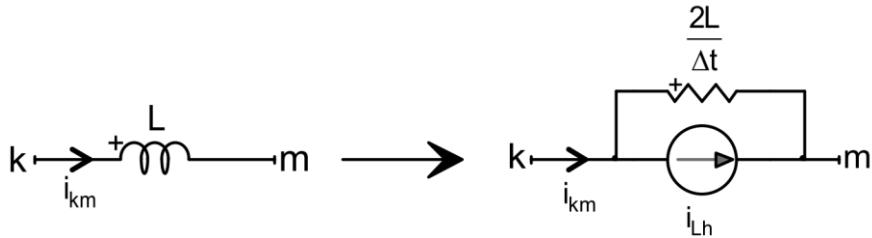

| 2.4.1 Modèles de composants - discrétisation des équations différentielles .....                                      | 19        |

| 2.4.2 Système de résolution.....                                                                                      | 20        |

| 2.4.3 Principes de la simulation temps réel .....                                                                     | 21        |

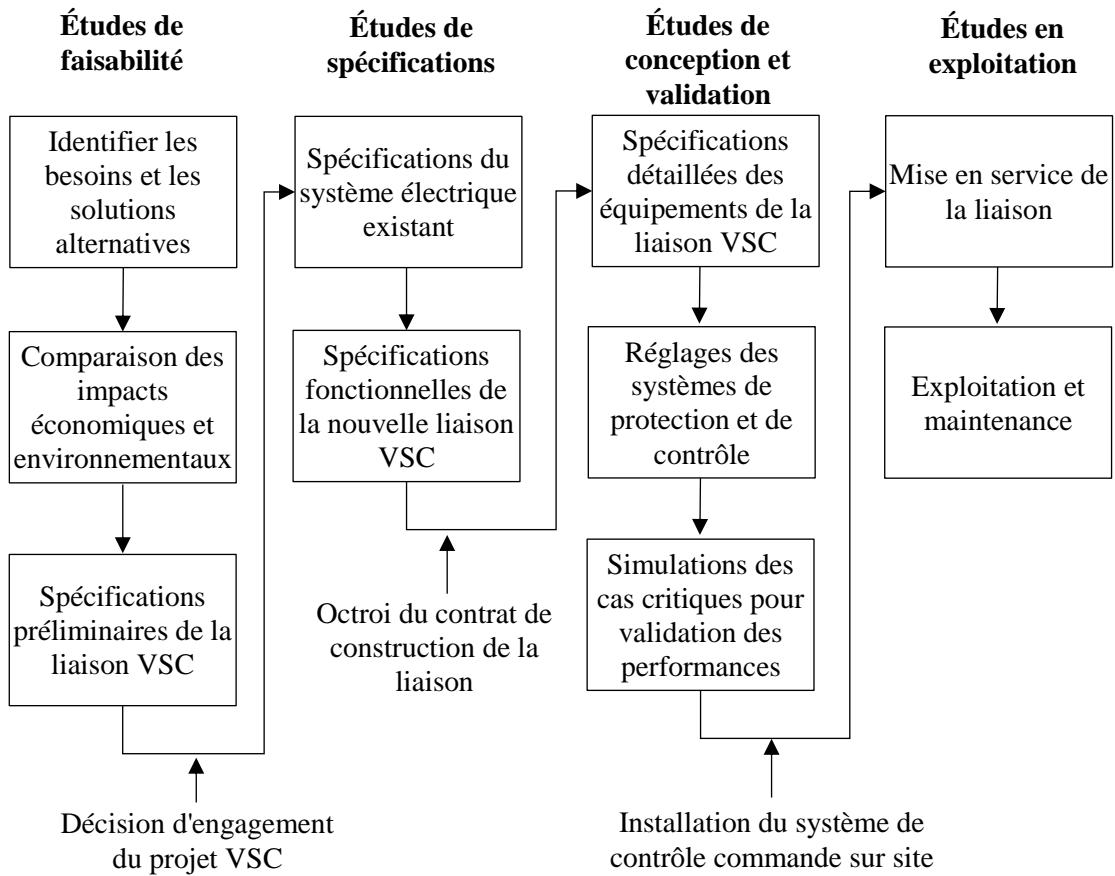

| 2.5 Les études EMT pour les projets de liaisons VSC-MMC .....                                                         | 22        |

| 2.5.1 Les études de faisabilité .....                                                                                 | 23        |

| 2.5.2 Les études de spécifications pour l'appel d'offre .....                                                         | 25        |

| 2.5.3 Les études de conception et de validation de performances .....                                                 | 26        |

| 2.5.4 Les études en exploitation .....                                                                                | 32        |

| 2.6 Les réseaux à courant continu .....                                                                               | 33        |

| 2.7 Conclusions .....                                                                                                 | 35        |

| <b>CHAPITRE 3 MODÉLISATION DES LIAISONS VSC DANS LES OUTILS DE TYPE EMT POUR DES APPLICATIONS INDUSTRIELLES .....</b> | <b>36</b> |

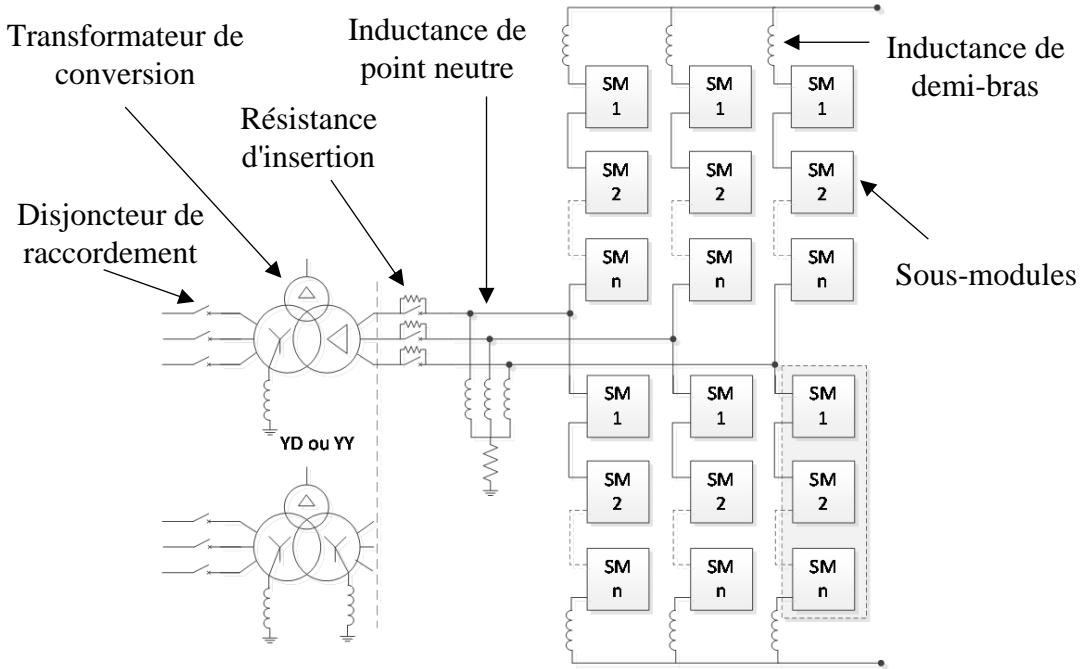

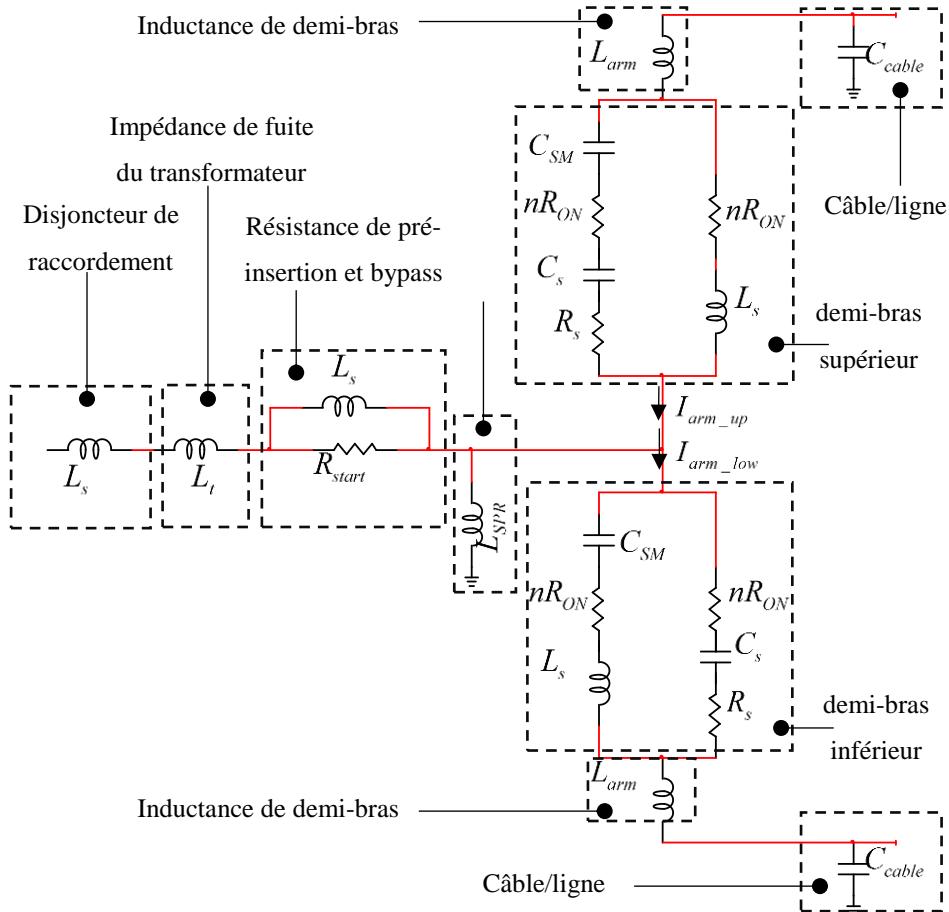

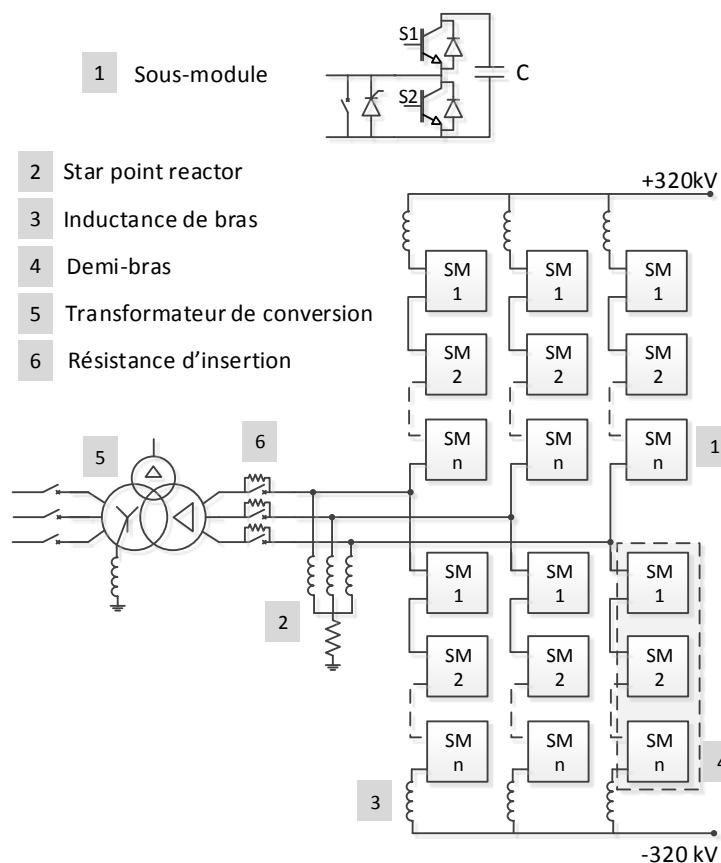

| 3.1 Description d'une liaison HVDC de type VSC MMC.....                                                               | 36        |

| 3.2 Les demi-bras des convertisseurs .....                                                                            | 37        |

| 3.2.1 Optimisations possibles du Modèle 1 .....                                                                       | 38        |

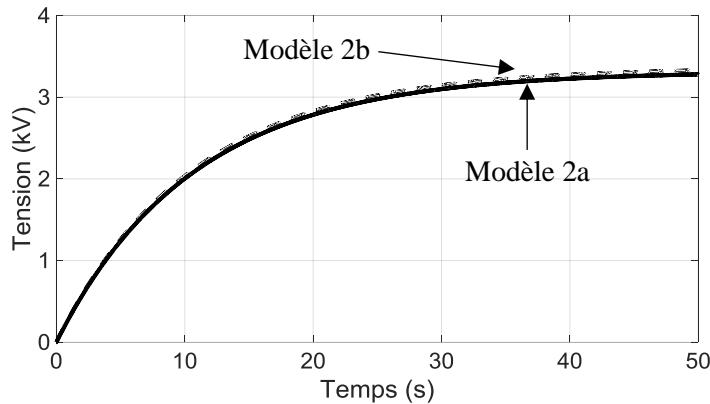

| 3.2.2 Le Modèle 2a.....                                                                                               | 43        |

| 3.2.3 Le Modèle 2b .....                                                                                              | 46        |

| 3.2.4 Le modèle 3 .....                                                                                               | 51        |

| 3.2.5 Comparaison Modèle 2a / Modèle 2b .....                                                                         | 52        |

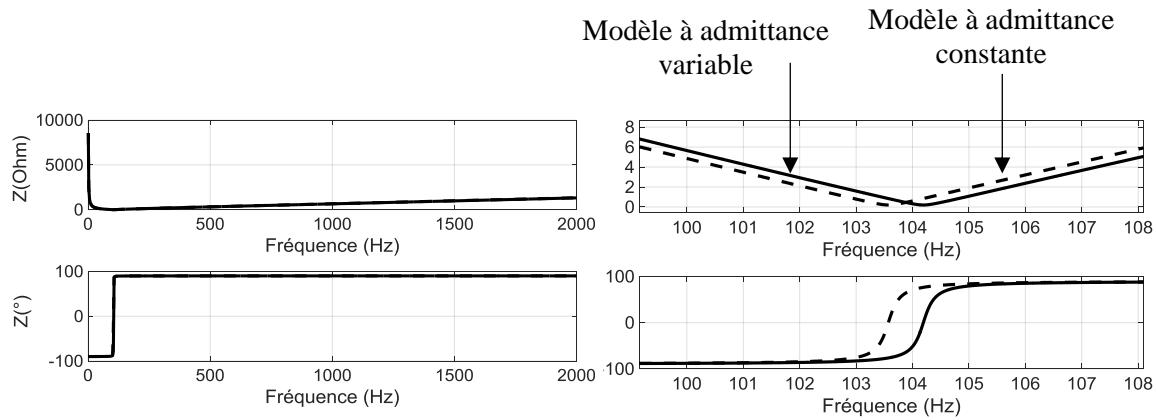

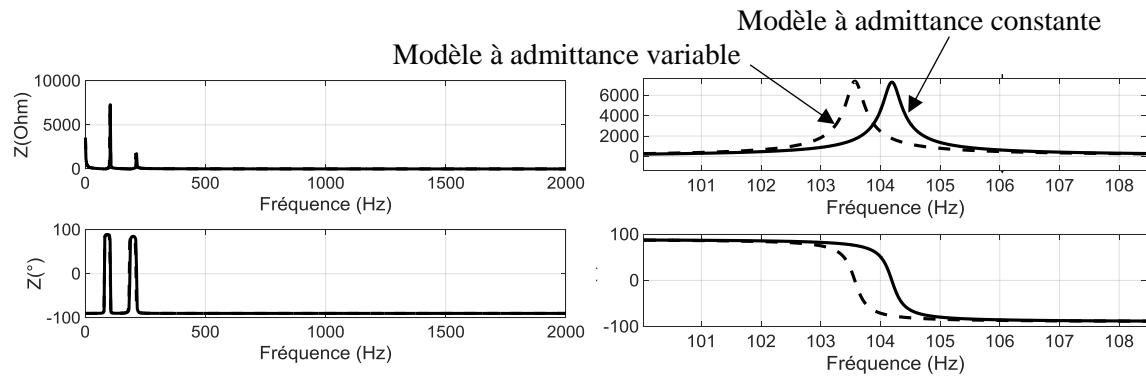

| 3.2.6 La modélisation à admittance constante.....                                                                     | 57        |

| 3.3 Les transformateurs de conversion.....                                                                            | 63        |

| 3.4 Les autres équipements .....                                                                                      | 64        |

|                                                                                                                            |                                                                                |           |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------|

| 3.4.1                                                                                                                      | Les inductances de point neutre .....                                          | 64        |

| 3.4.2                                                                                                                      | Les inductances de demi-bras .....                                             | 65        |

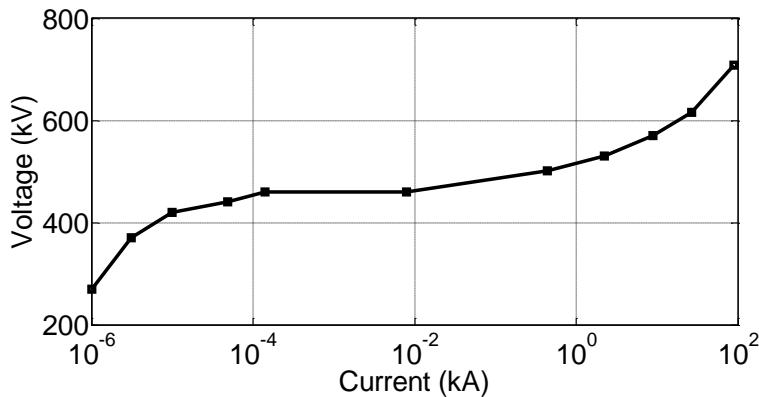

| 3.4.3                                                                                                                      | Les parafoudres .....                                                          | 65        |

| 3.4.4                                                                                                                      | Les disjoncteurs et équipements de sectionnement.....                          | 66        |

| 3.4.5                                                                                                                      | Les câbles souterrains et des lignes aériennes sur la partie continue. ....    | 67        |

| 3.5                                                                                                                        | Conclusions .....                                                              | 67        |

| <b>CHAPITRE 4    IMPLÉMENTATION DES MODÈLES DE LIAISONS VSC DANS DES SIMULATEURS TEMPS RÉELS.....</b>                      |                                                                                | <b>68</b> |

| 4.1                                                                                                                        | Exigences à respecter .....                                                    | 68        |

| 4.1.1                                                                                                                      | Pourquoi la simulation temps réel ? .....                                      | 68        |

| 4.1.2                                                                                                                      | Validation des modèles temps réel de liaisons HVDC .....                       | 68        |

| 4.1.3                                                                                                                      | Pourquoi l'utilisation de FPGA ?.....                                          | 71        |

| 4.2                                                                                                                        | Les modèles de convertisseurs adaptés à la simulation temps réel .....         | 74        |

| 4.2.1                                                                                                                      | Modèles basés l'utilisation de matrices d'admittance constantes .....          | 74        |

| 4.2.2                                                                                                                      | Modèle détaillé équivalent (Modèle 2a) adapté à la simulation temps réel ..... | 74        |

| 4.2.3                                                                                                                      | Modèle 3.....                                                                  | 88        |

| 4.2.4                                                                                                                      | Modèle 2b.....                                                                 | 88        |

| 4.3                                                                                                                        | Conclusions .....                                                              | 89        |

| <b>CHAPITRE 5    IMPLÉMENTATION ET VALIDATION DES MODÈLES DE LIAISONS VSC APPLIQUÉES À LA LIAISON FRANCE ESPAGNE .....</b> |                                                                                | <b>90</b> |

| 5.1                                                                                                                        | Description de la liaison France-Espagne .....                                 | 90        |

| 5.1.1                                                                                                                      | Contexte .....                                                                 | 90        |

| 5.1.2                                                                                                                      | Description de l'interconnexion.....                                           | 91        |

| 5.2                                                                                                                        | Principes de modélisation et de validation des stations de conversion .....    | 93        |

| 5.2.1                                                                                                                      | Modélisation sans FPGA – Modèle 3 .....                                        | 93        |

| 5.2.2                                                                                                                      | Description du modèle de station de conversion.....                            | 95        |

| 5.2.3                                                                                                                      | Validation du modèle de transformateur de conversion.....                      | 96        |

|                                                                                                    |                                                                                                    |            |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------|

| 5.2.4                                                                                              | Principes de validation du modèle de convertisseurs et des interfaces .....                        | 99         |

| 5.3                                                                                                | Validation du modèle temps réel.....                                                               | 100        |

| 5.3.1                                                                                              | Constitution des modèles temps réel/hors temps réel .....                                          | 100        |

| 5.3.2                                                                                              | Validation à l'aide de simulation en temps différé du modèle temps réel sans interface d'E/S ..... | 101        |

| 5.3.3                                                                                              | Validation à l'aide de mesures du modèle temps réel sans interface d'E/S .....                     | 105        |

| 5.4                                                                                                | Validation du modèle temps réel avec les interfaces d'E/S .....                                    | 109        |

| 5.5                                                                                                | Utilisation du modèle temps réel avec le contrôleur physique.....                                  | 111        |

| 5.5.1                                                                                              | Description du matériel .....                                                                      | 111        |

| 5.5.2                                                                                              | Validation de l'ensemble simulateur + réplique .....                                               | 113        |

| 5.6                                                                                                | Conclusions .....                                                                                  | 120        |

| <b>CHAPITRE 6 UTILISATION DE MODÈLES DÉTAILLÉS MMC DANS DES SIMULATIONS TEMPS RÉEL.....</b>        |                                                                                                    | <b>122</b> |

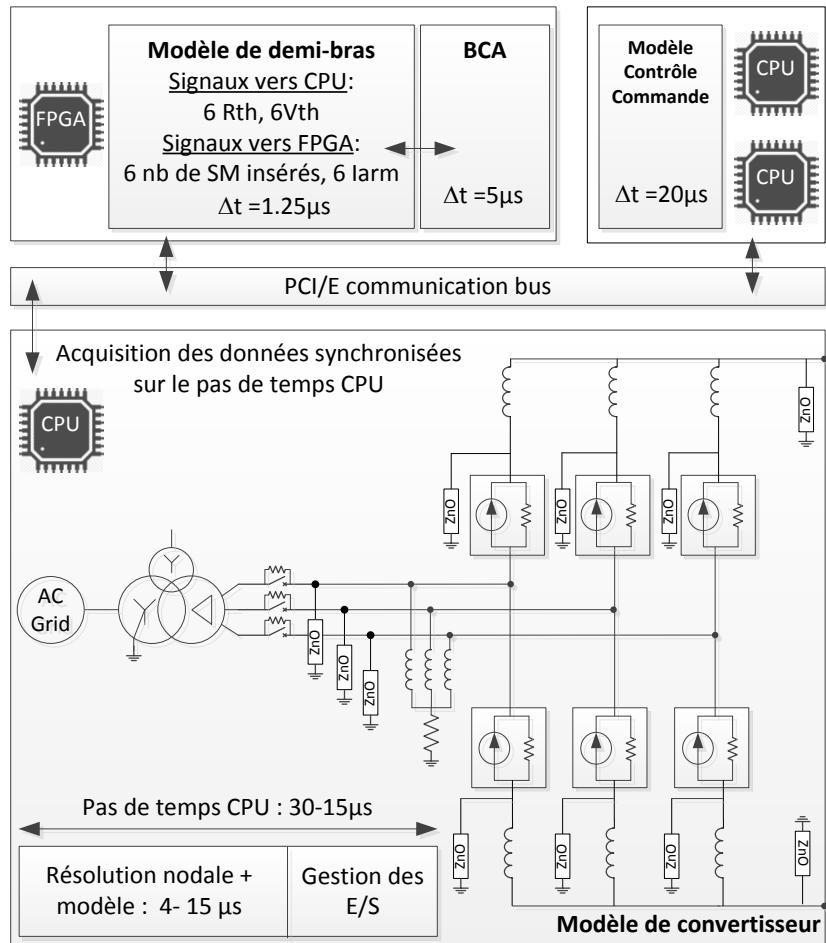

| 6.1                                                                                                | Modèle 2a implémenté sur FPGA .....                                                                | 122        |

| 6.1.1                                                                                              | Implémentation sur FPGA .....                                                                      | 122        |

| 6.1.2                                                                                              | Validation du modèle de convertisseur sur FPGA .....                                               | 125        |

| 6.1.3                                                                                              | Validation du modèle avec un grand nombre de niveaux .....                                         | 129        |

| 6.2                                                                                                | Modèle 2b implémenté sur FPGA.....                                                                 | 133        |

| 6.2.1                                                                                              | Implémentation sur FPGA .....                                                                      | 133        |

| 6.3                                                                                                | Validation du modèle de convertisseur sur FPGA .....                                               | 133        |

| 6.4                                                                                                | Conclusions .....                                                                                  | 137        |

| <b>CHAPITRE 7 RÉSEAUX HVDC - JUSTIFICATIONS DU BENCHMARK CIGRE ET RÉSULTATS DE CAS TESTS .....</b> |                                                                                                    | <b>138</b> |

| 7.1                                                                                                | Introduction .....                                                                                 | 138        |

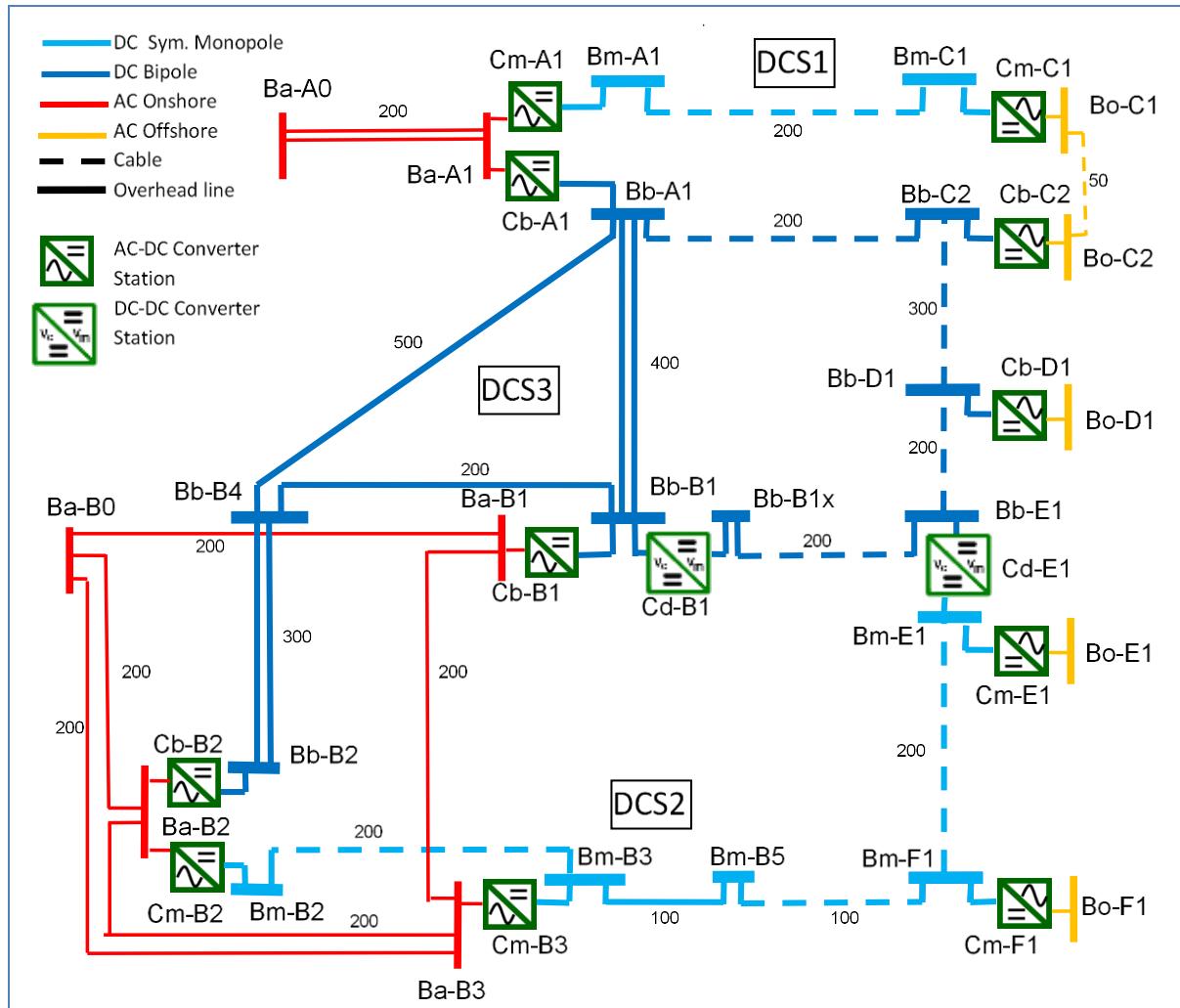

| 7.2                                                                                                | Description des réseaux CC et justifications.....                                                  | 138        |

| 7.2.1                                                                                              | Topologie du réseau .....                                                                          | 138        |

| 7.2.2                                                                                              | Description des principaux équipements.....                                                        | 140        |

|                             |                                  |     |

|-----------------------------|----------------------------------|-----|

| 7.3                         | Simulations du réseau test ..... | 149 |

| 7.4                         | Conclusions .....                | 154 |

| CHAPITRE 8 CONCLUSION ..... |                                  | 155 |

| BIBLIOGRAPHIE .....         |                                  | 157 |

| ANNEXES .....               |                                  | 161 |

## LISTE DES TABLEAUX

|                                                                                                            |     |

|------------------------------------------------------------------------------------------------------------|-----|

| Tableau 3-1: Temps d'exécution d'un modèle 1 de liaison HVDC .....                                         | 42  |

| Tableau 4-1: Étapes de validation d'un modèle temps réel de station de conversion VSC.....                 | 70  |

| Tableau 4-2: Modèle 2a - algorithme du demi-bras du MMC [9].....                                           | 80  |

| Tableau 4-3: Modèle 2a - algorithme du demi-bras du MMC adapté pour l'implémentation<br>FPGA.....          | 85  |

| Tableau 4-4: Nombre d'opérations nécessaires à la résolution du Modèle 2a – formulation<br>initiale.....   | 86  |

| Tableau 4-5: Nombre d'opérations nécessaires à la résolution du Modèle 2a – formulation<br>optimisée ..... | 87  |

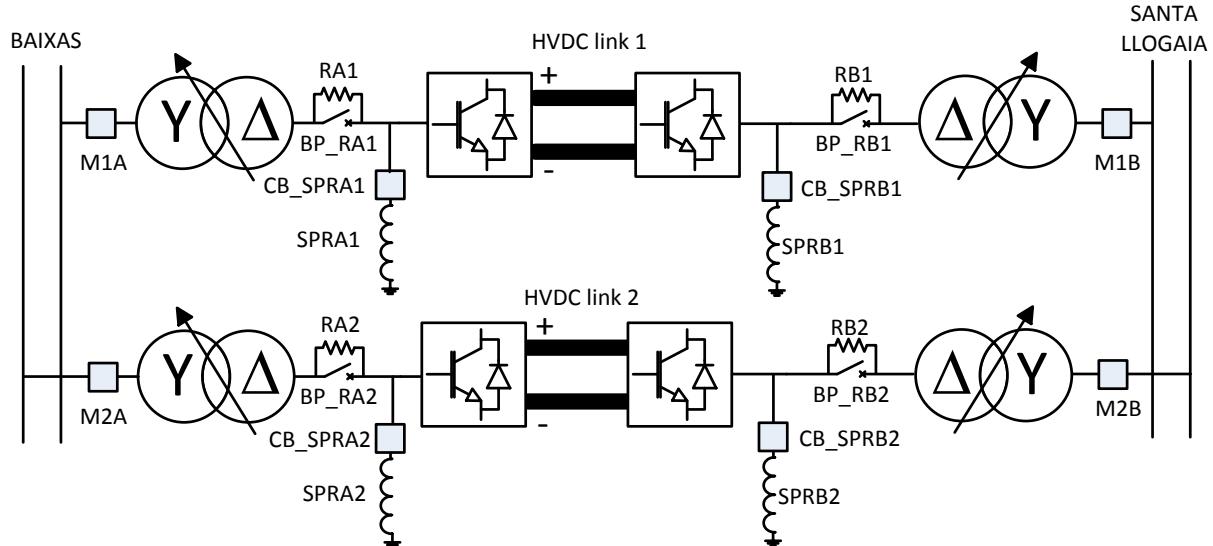

| Tableau 5-1: Paramètres des composants d'un convertisseur de la liaison France-Espagne ...                 | 93  |

| Tableau 6-1: Paramètres d'un sous-module.....                                                              | 123 |

| Tableau 6-2: Boucle temporelle de résolution CPU/FPGA du cas de la Figure 6-2.....                         | 124 |

| Tableau 7-1: Résultats des essais de transit de 1000MW au poste de BAIXAS .....                            | 143 |

| Tableau 7-2: Paramètres des convertisseurs du réseau test CIGRE .....                                      | 145 |

| Tableau 7-3: Consignes de contrôle des convertisseurs du réseau test .....                                 | 148 |

| Tableau 7-4: Caractéristiques des câbles CC du réseau test .....                                           | 149 |

| Tableau 7-5: Temps d'exécution du réseau test en simulation hors temps réel ( $\Delta t=20\mu s$ ) ....    | 150 |

| Tableau 7-6: Évènements suite à l'apparition du défaut CC .....                                            | 153 |

| Tableau A-1 : Paramètres du convertisseur MMC pour modèle à admittance fixe .....                          | 162 |

| Tableau A-2 : Paramètres du convertisseur MMC pour les modèles MMC à 21 niveaux ....                       | 164 |

| Tableau A-3 : Paramètres du convertisseur MMC pour les modèles MMC à 401 niveaux ..                        | 164 |

## LISTE DES FIGURES

|                                                                                                                              |    |

|------------------------------------------------------------------------------------------------------------------------------|----|

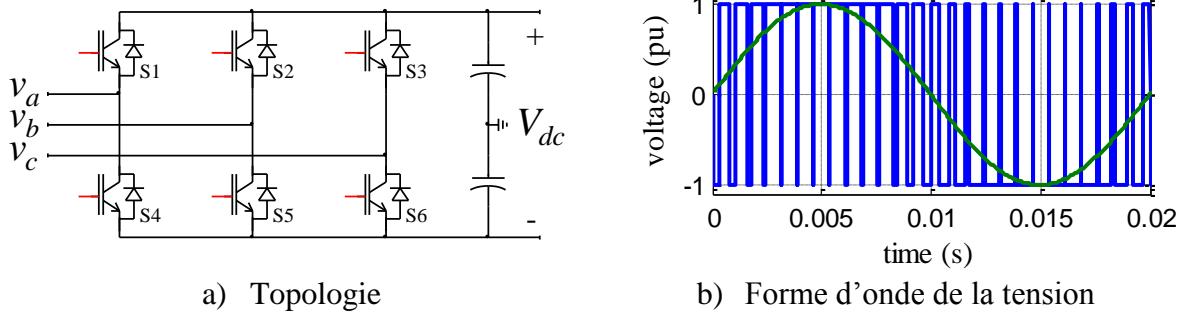

| Figure 2-1: VSC 2 niveaux.....                                                                                               | 11 |

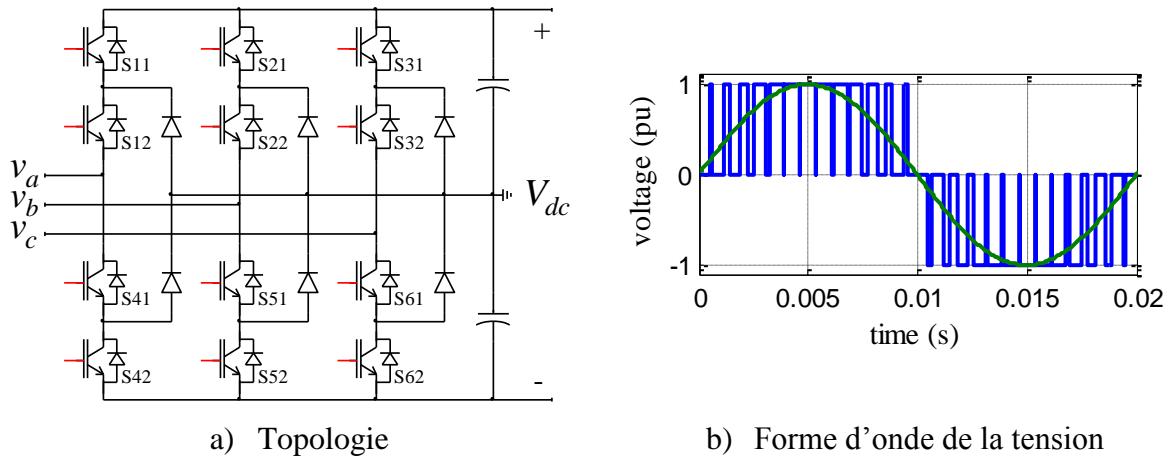

| Figure 2-2: VSC 3 niveaux.....                                                                                               | 11 |

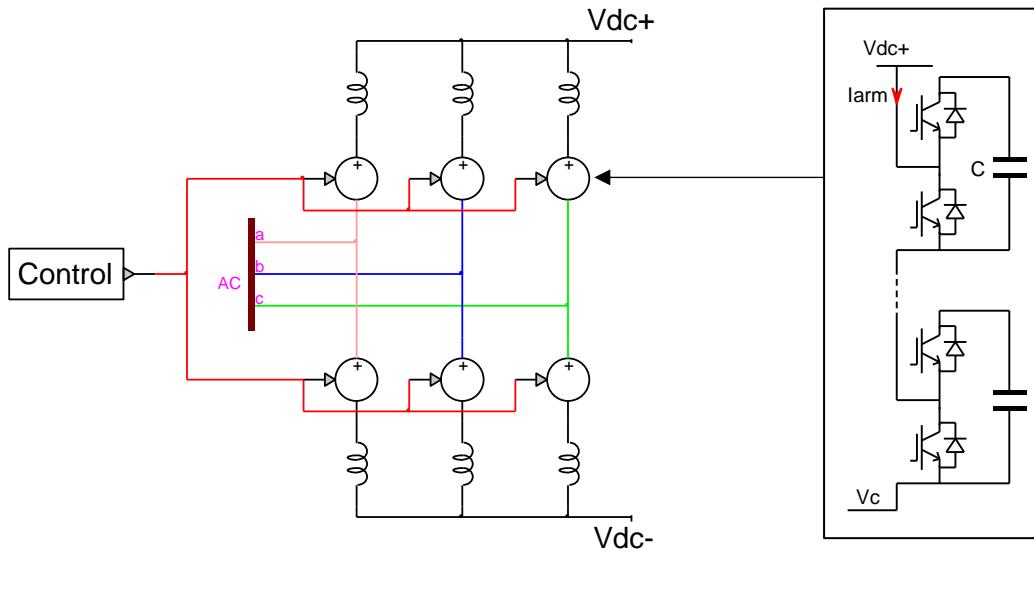

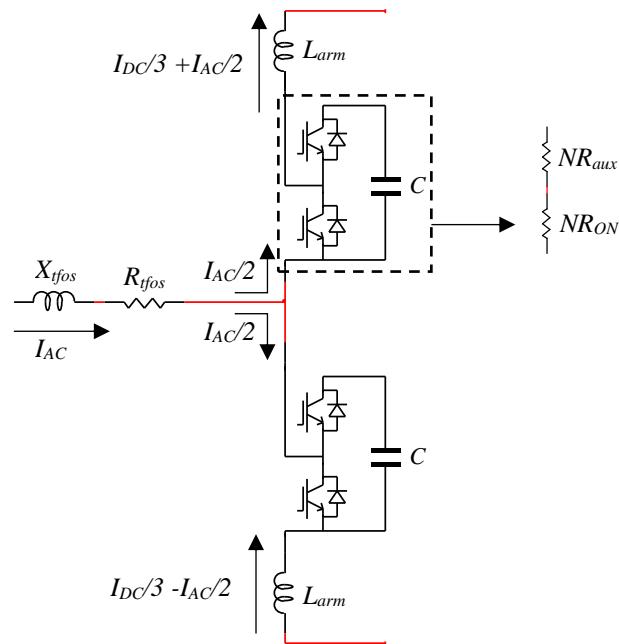

| Figure 2-3: Schéma simplifié d'un convertisseur MMC .....                                                                    | 13 |

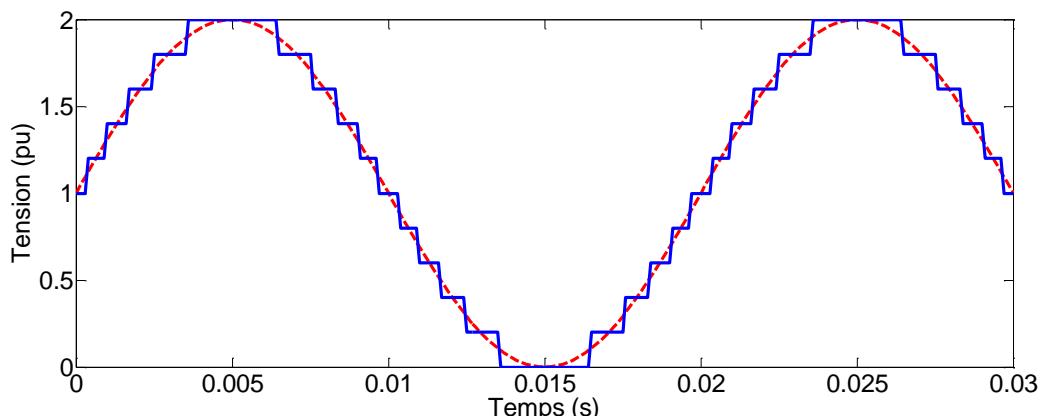

| Figure 2-4: Forme d'onde de la tension aux bornes d'un demi bras d'un MMC à 5 niveaux ...                                    | 14 |

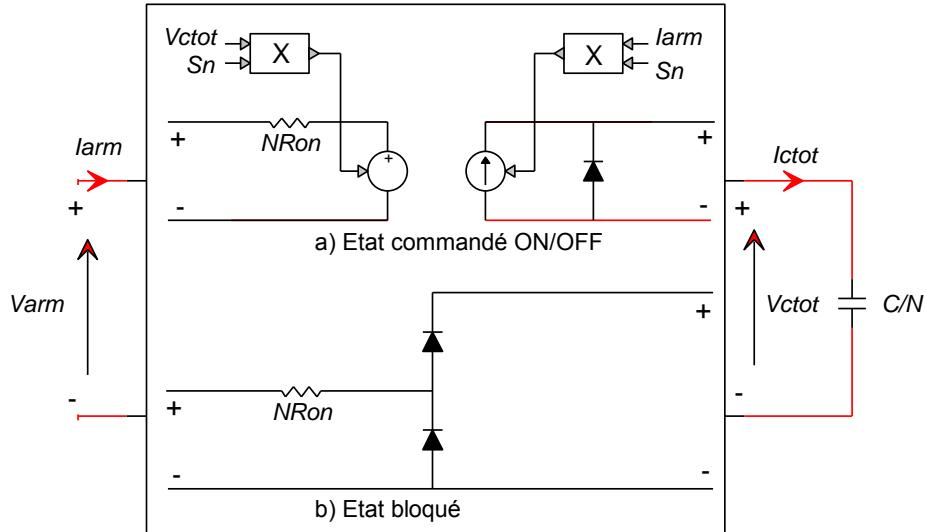

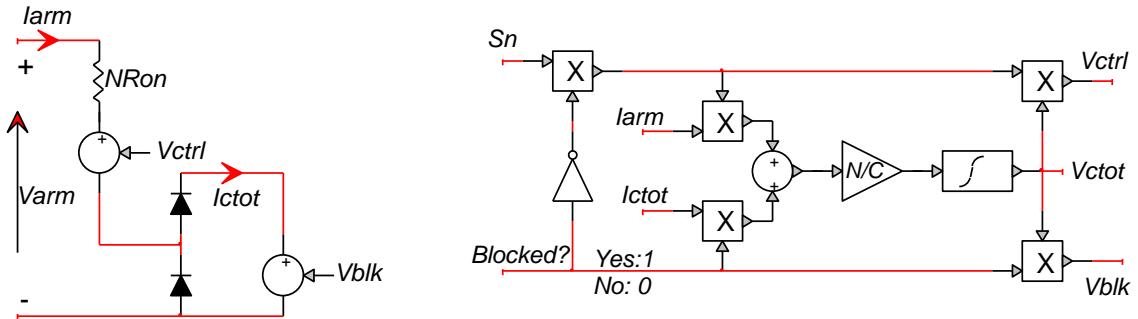

| Figure 2-5: Schéma équivalent d'un Modèle 3 pour l'état contrôlé et l'état bloqué .....                                      | 17 |

| Figure 2-6: Schéma équivalent unifié d'un Modèle 3 pour le mode contrôlé et le mode bloqué .....                             | 18 |

| Figure 2-7: Schéma équivalent unifié d'un modèle 3 pour le mode contrôlé et le mode bloqué .....                             | 20 |

| Figure 2-8: Vue d'ensemble des études pendant le cycle de vie d'un système VSC .....                                         | 23 |

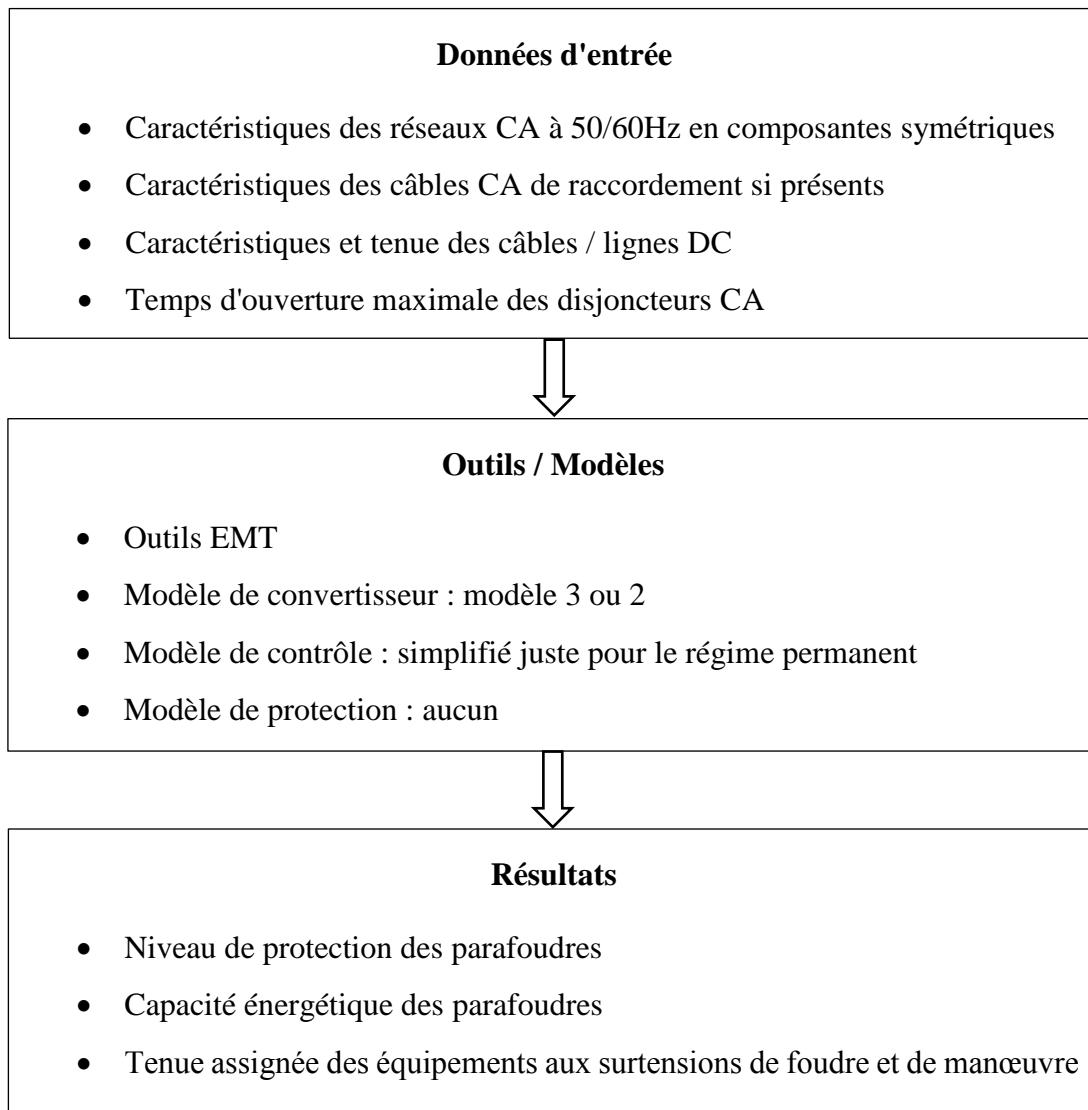

| Figure 2-9: Etudes des contraintes transitoires maximales pour les stations de conversion....                                | 28 |

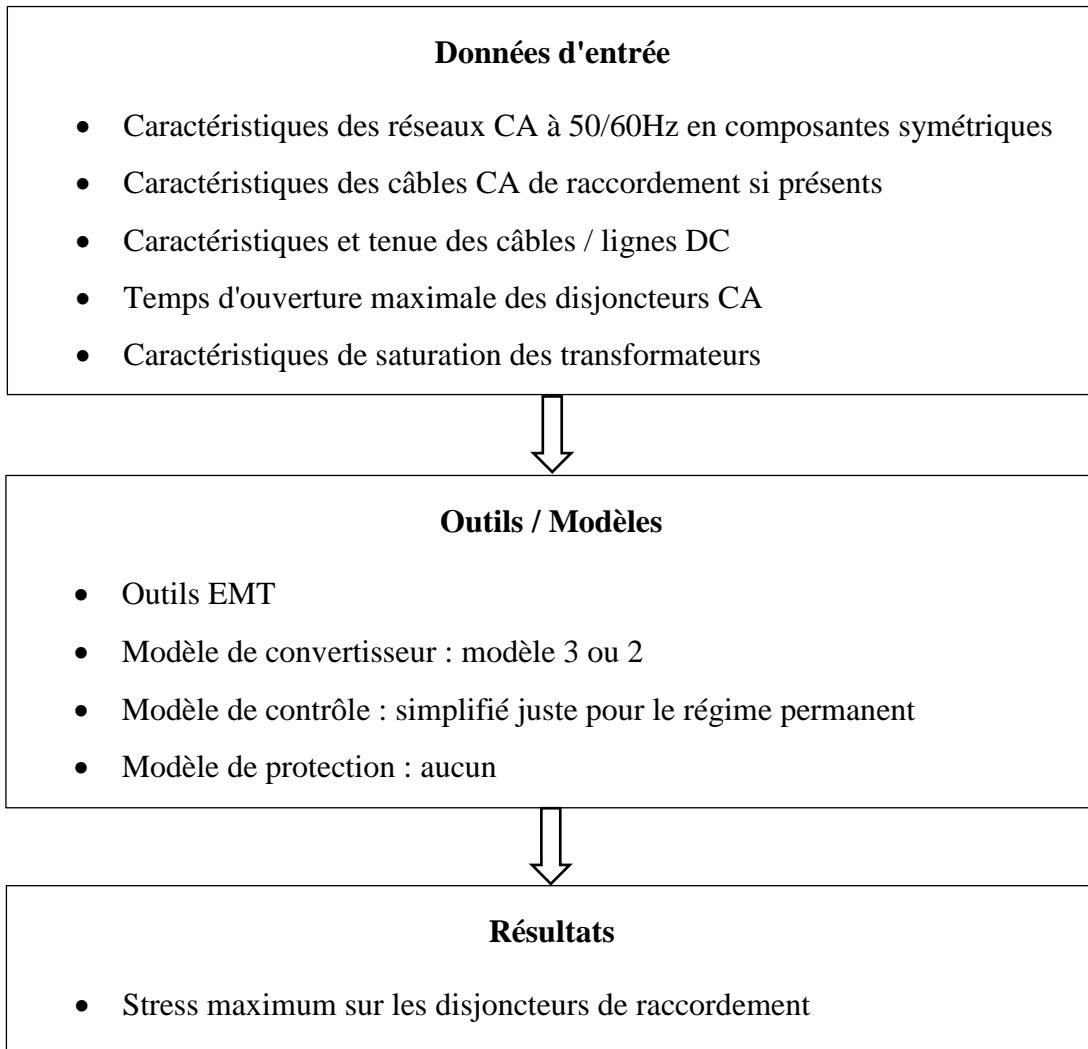

| Figure 2-10: Etudes des contraintes transitoires maximales pour les disjoncteurs de raccordement .....                       | 29 |

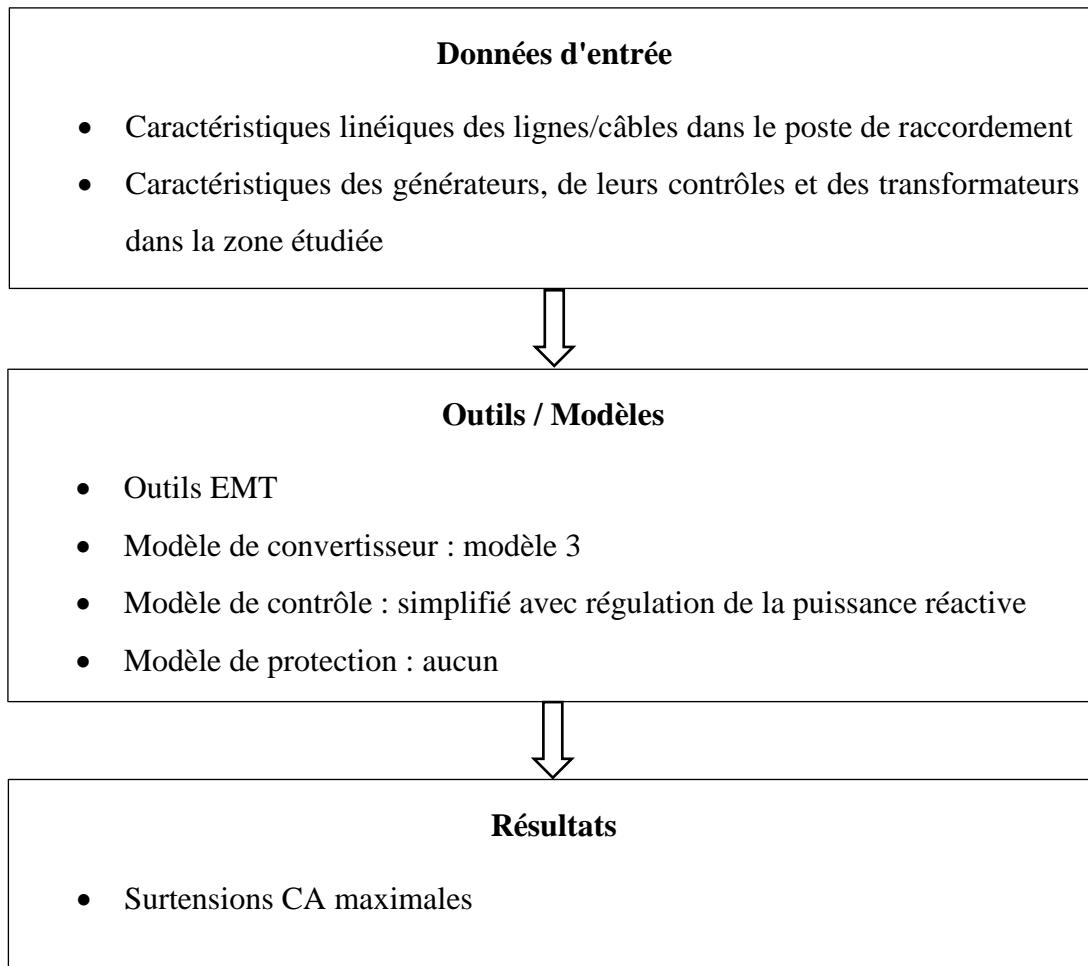

| Figure 2-11: Etudes pour l'évaluation des surtensions CA .....                                                               | 30 |

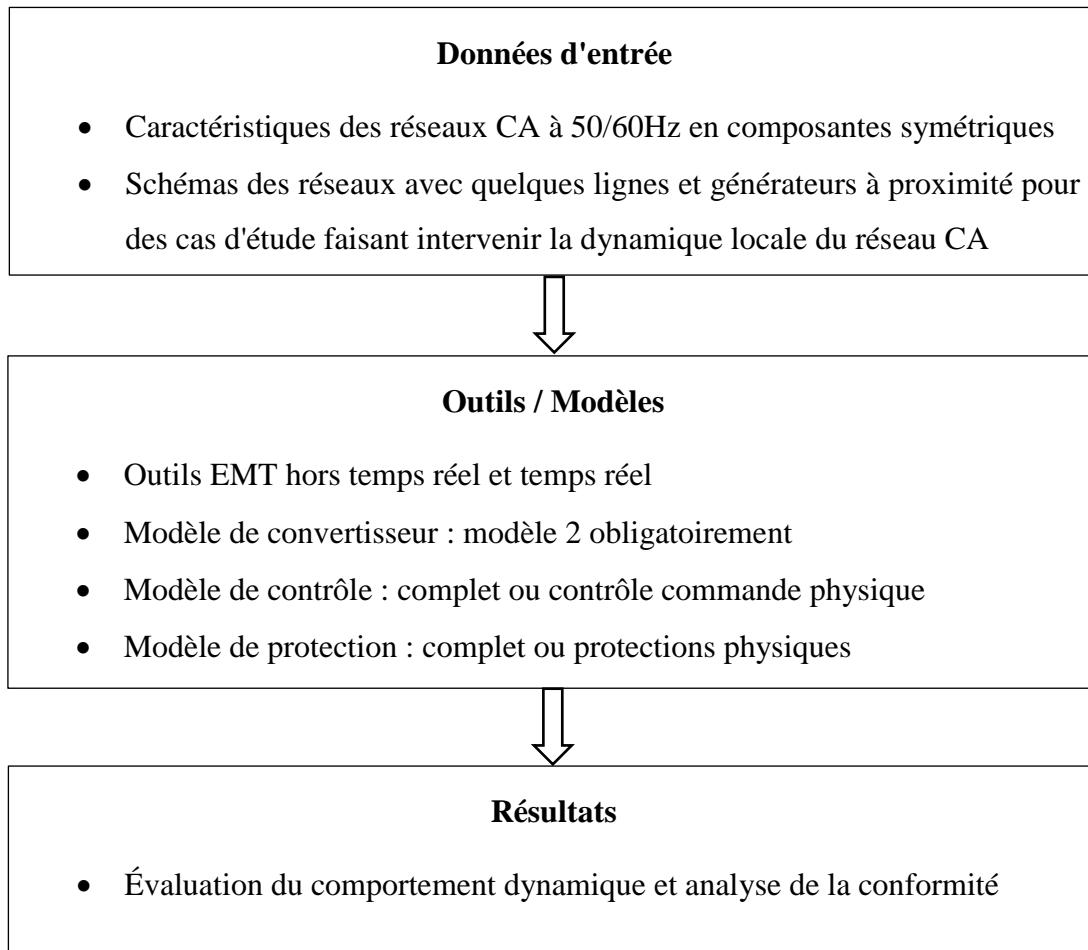

| Figure 2-12: Etudes pour la validation des performances.....                                                                 | 31 |

| Figure 2-13: Plan de développement 2014 du réseau ENTSO-E à 10 ans .....                                                     | 34 |

| Figure 2-14: Constructions ou réhabilitations prévisibles de liaisons CA et CC prévues à 10 ans sur le réseau européen ..... | 34 |

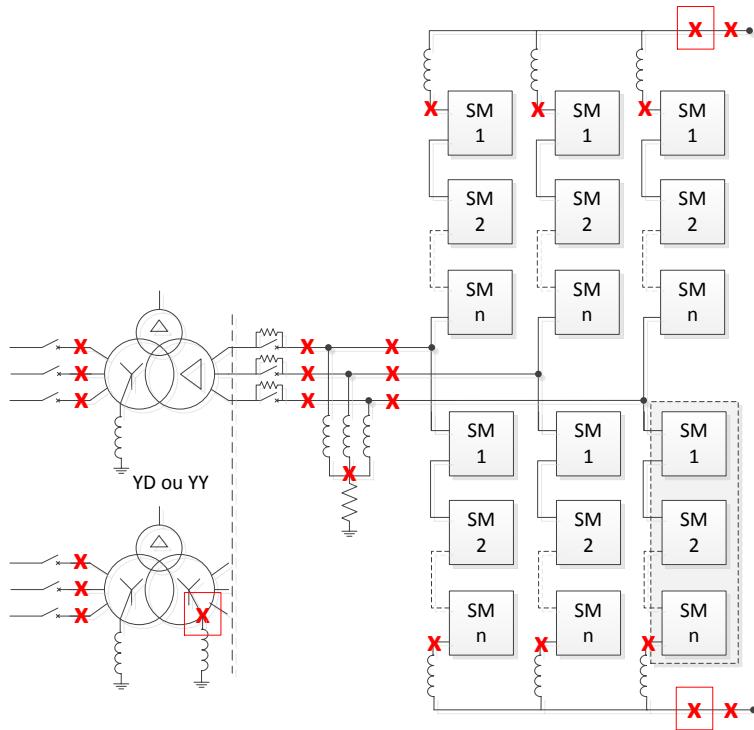

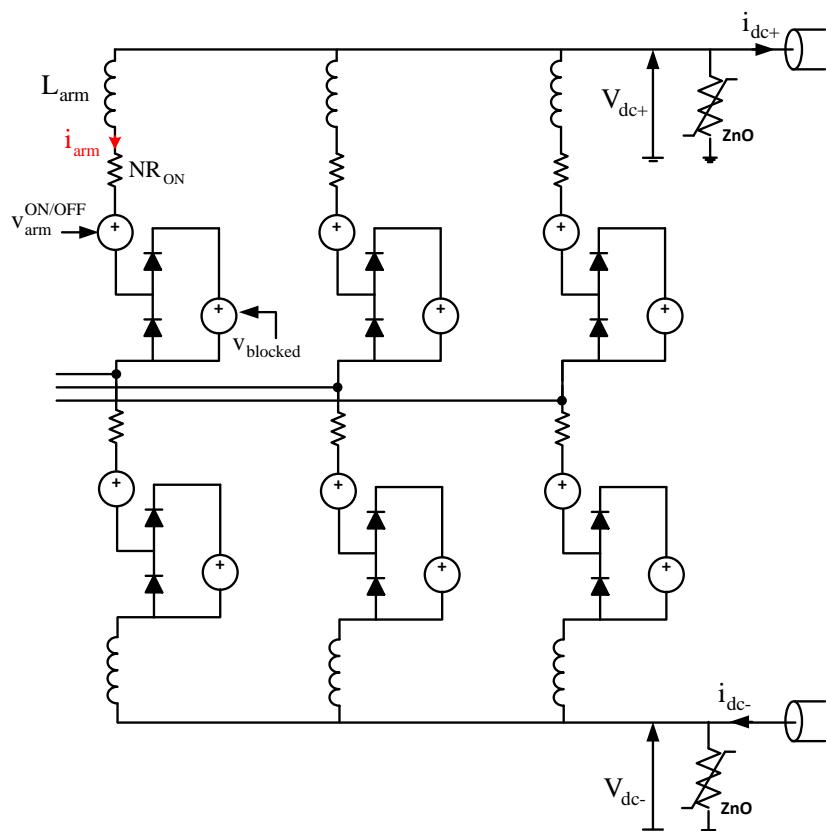

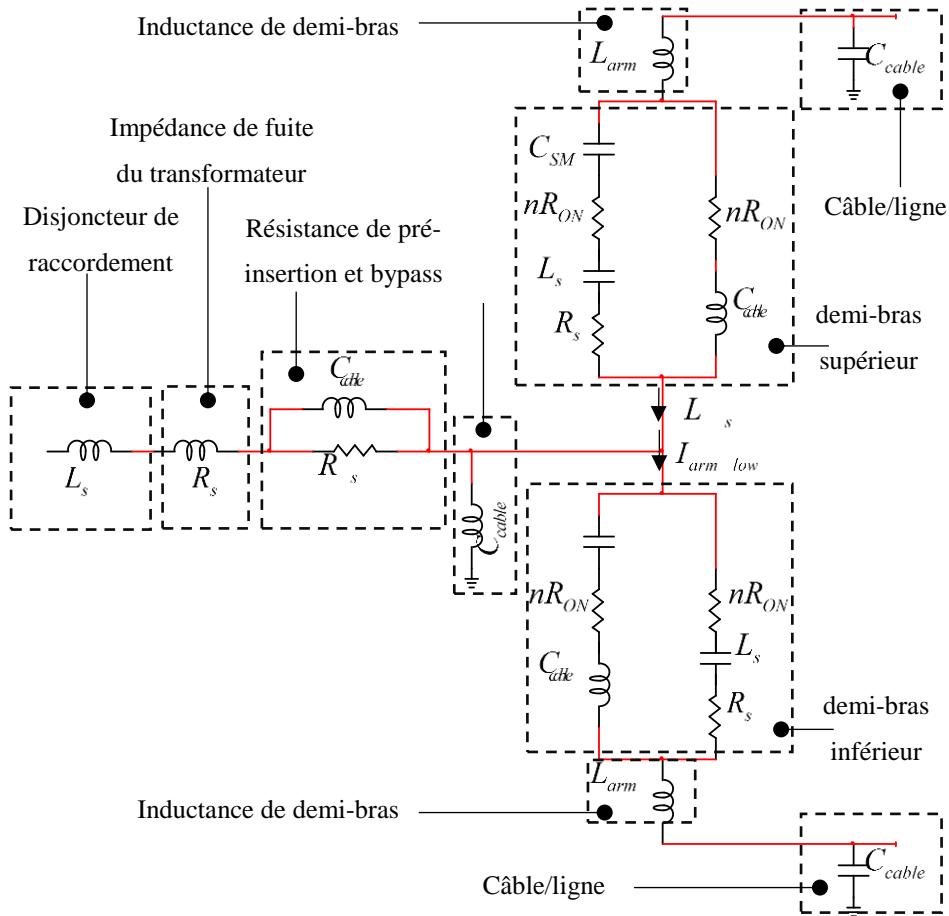

| Figure 3-1: Schéma unifilaire d'une station de conversion HVDC de type VSC MMC.....                                          | 37 |

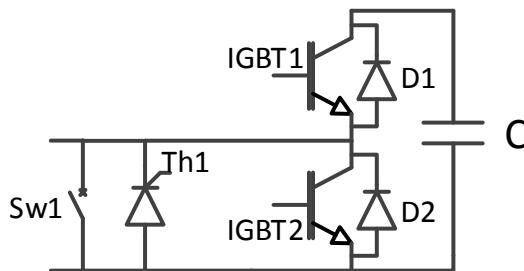

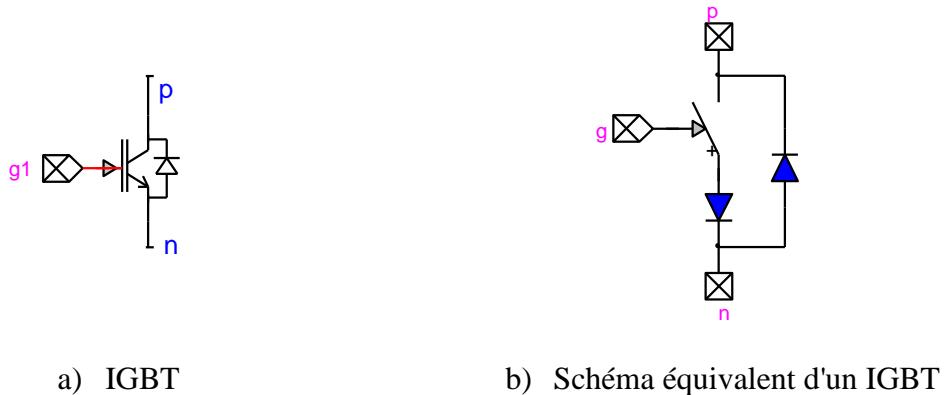

| Figure 3-2: Topologie des sous-modules utilisés dans les convertisseurs de la liaison France-Espagne .....                   | 37 |

| Figure 3-3: Schéma équivalent d'un IGBT intégré à un modèle 1 de convertisseur MMC ....                                      | 39 |

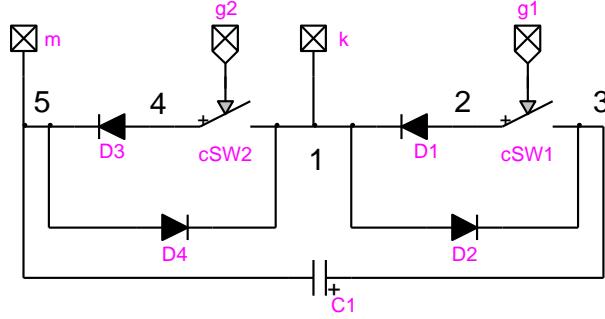

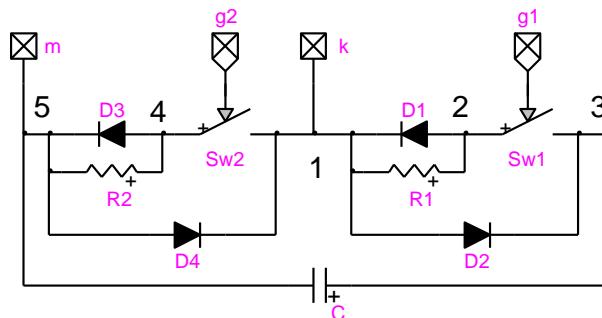

| Figure 3-4: Schéma équivalent d'un sous-module (avec diodes idéales).....                                                    | 40 |

| Figure 3-5: Schéma équivalent d'un sous-module (avec diodes idéales et résistances).....                                     | 40 |

| Figure 3-6: Matrices nodales pour la résolution temporelle d'une liaison HVDC .....                                          | 42 |

| Figure 3-7: Équivalent discréte du sous-module $i$ .....                                                                     | 44 |

|                                                                                                                              |    |

|------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3-8: Circuits pour valider le Modèle 2a amélioré .....                                                                | 45 |

| Figure 3-9: Comparaison des courants de demi-bras pour les 2 circuits (1 <sup>ère</sup> alternance et zoom) .....            | 46 |

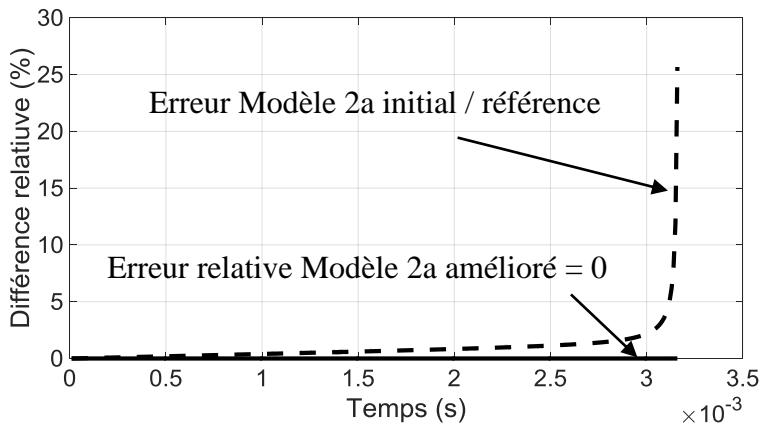

| Figure 3-10: Différences relatives entre le Modèle 2a initial et la référence et le Modèle 2a amélioré et la référence ..... | 46 |

| Figure 3-11: Modèle 3 présenté dans [9] .....                                                                                | 47 |

| Figure 3-12: État ON d'un sous-module et son schéma équivalent.....                                                          | 48 |

| Figure 3-13: État OFF d'un sous-module et son schéma équivalent .....                                                        | 48 |

| Figure 3-14: Schéma équivalent de l'état ON/OFF d'un sous-module .....                                                       | 49 |

| Figure 3-15: État bloqué d'un sous-module et son schéma équivalent .....                                                     | 50 |

| Figure 3-16: Schéma équivalent de l'état bloqué du sous-module <i>i</i> .....                                                | 50 |

| Figure 3-17: Schéma équivalent d'un demi-bras .....                                                                          | 51 |

| Figure 3-18: Schéma équivalent d'un demi-bras d'un modèle 3 moyen.....                                                       | 52 |

| Figure 3-19: Circuit test pour comparaison des Modèles 2 et 3 détaillés .....                                                | 53 |

| Figure 3-20: Tension aux bornes du premier sous module (aucune initialisation) .....                                         | 53 |

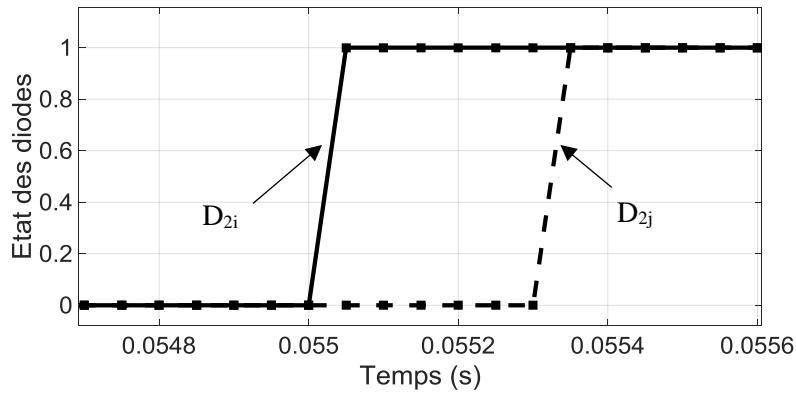

| Figure 3-21: Comportement des diodes dans le modèle 2 .....                                                                  | 54 |

| Figure 3-22: Changement d'état des diodes D <sub>2</sub> dans un Modèle 2a .....                                             | 55 |

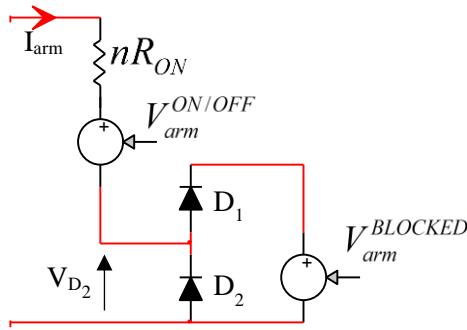

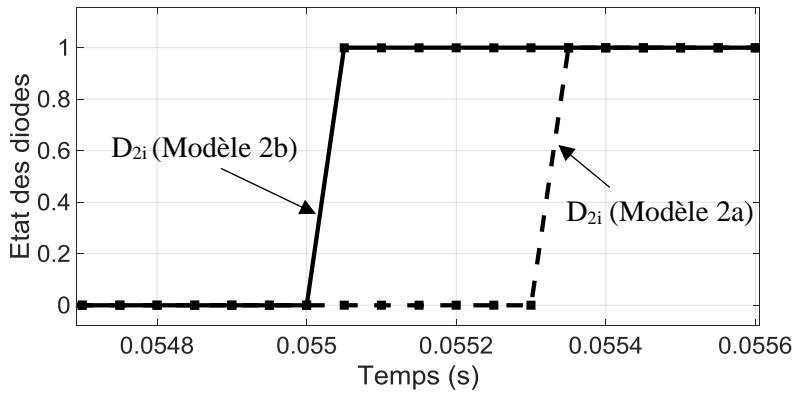

| Figure 3-23: Comportement des diodes dans le Modèle 2b .....                                                                 | 55 |

| Figure 3-24: Changement d'état de la diodes D <sub>2</sub> dans un Modèle 2b .....                                           | 56 |

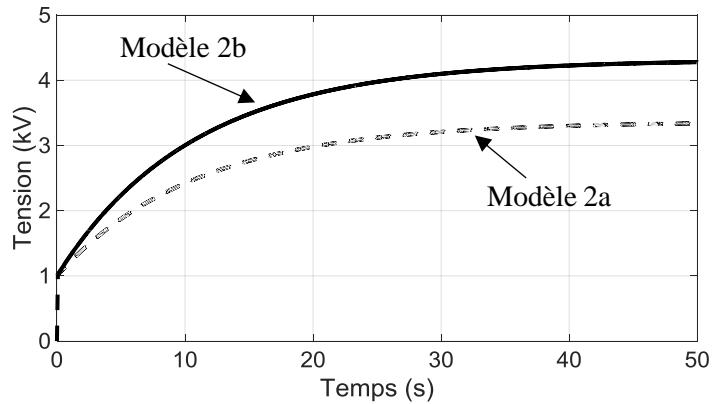

| Figure 3-25: Comparaison de la tension du sous-module avec une tension initiale non nulle                                    | 56 |

| Figure 3-26: Comparaison de la tension d'un sous-module sans tension initiale.....                                           | 57 |

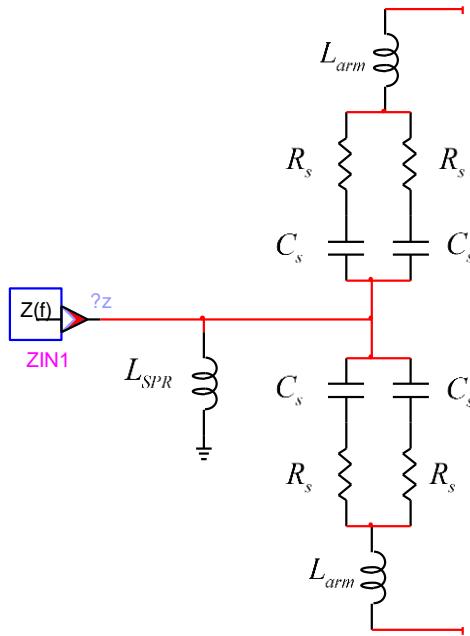

| Figure 3-27: Circuits équivalents d'un sous module avec la modélisation à admittance constante .....                         | 58 |

| Figure 3-28: Circuit équivalent d'une phase de convertisseur avec une modélisation à admittance constante .....              | 59 |

| Figure 3-29: Impédances dans le domaine fréquentiel vues du côté CA .....                                                    | 60 |

| Figure 3-30: Impédance dans le domaine fréquentiel vue du côté CC .....                                                      | 60 |

|                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------|----|

| Figure 3-31: Schéma équivalent simplifié d'une phase de convertisseur en mode haute impédance.....           | 61 |

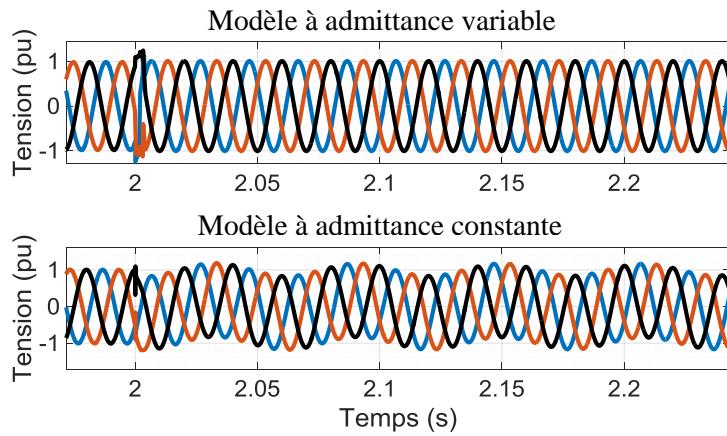

| Figure 3-32: Tension au secondaire du transformateur de conversion (côté convertisseur)....                  | 62 |

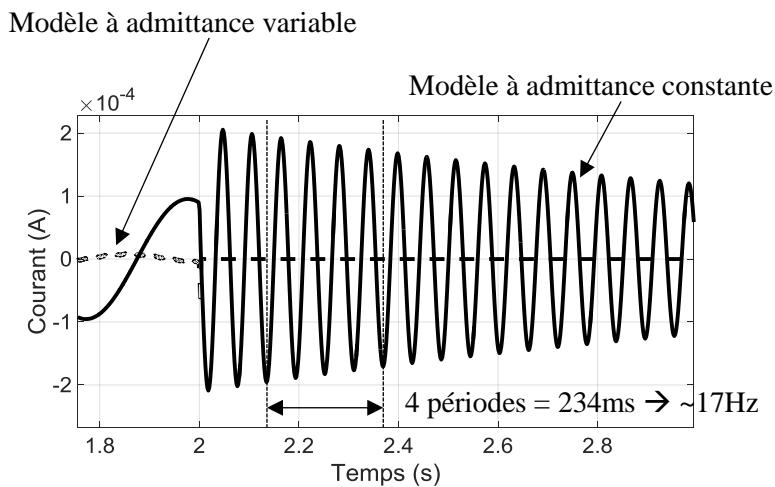

| Figure 3-33: Courant dans l'inductance de point neutre.....                                                  | 62 |

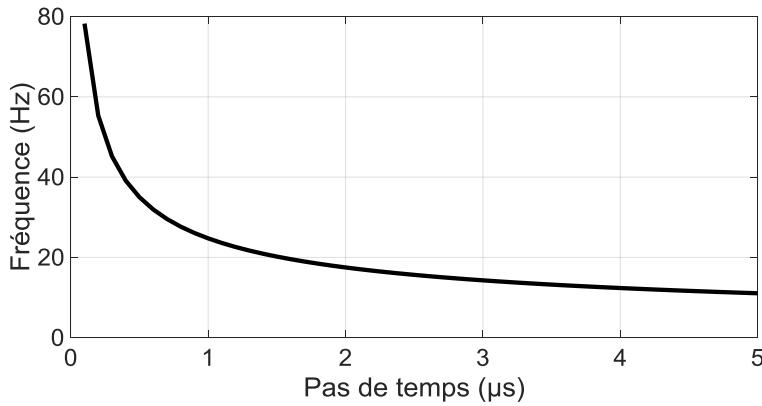

| Figure 3-34: Fréquence de la résonance avec l'inductance de point neutre .....                               | 63 |

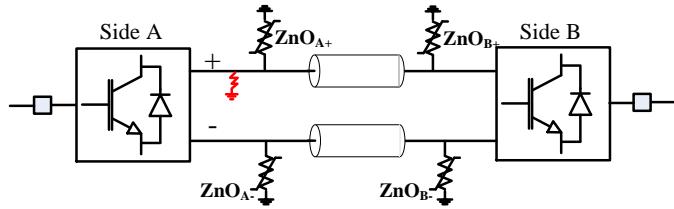

| Figure 3-35: Positionnement des parafoudres dans une station de conversion VSC-MMC ....                      | 66 |

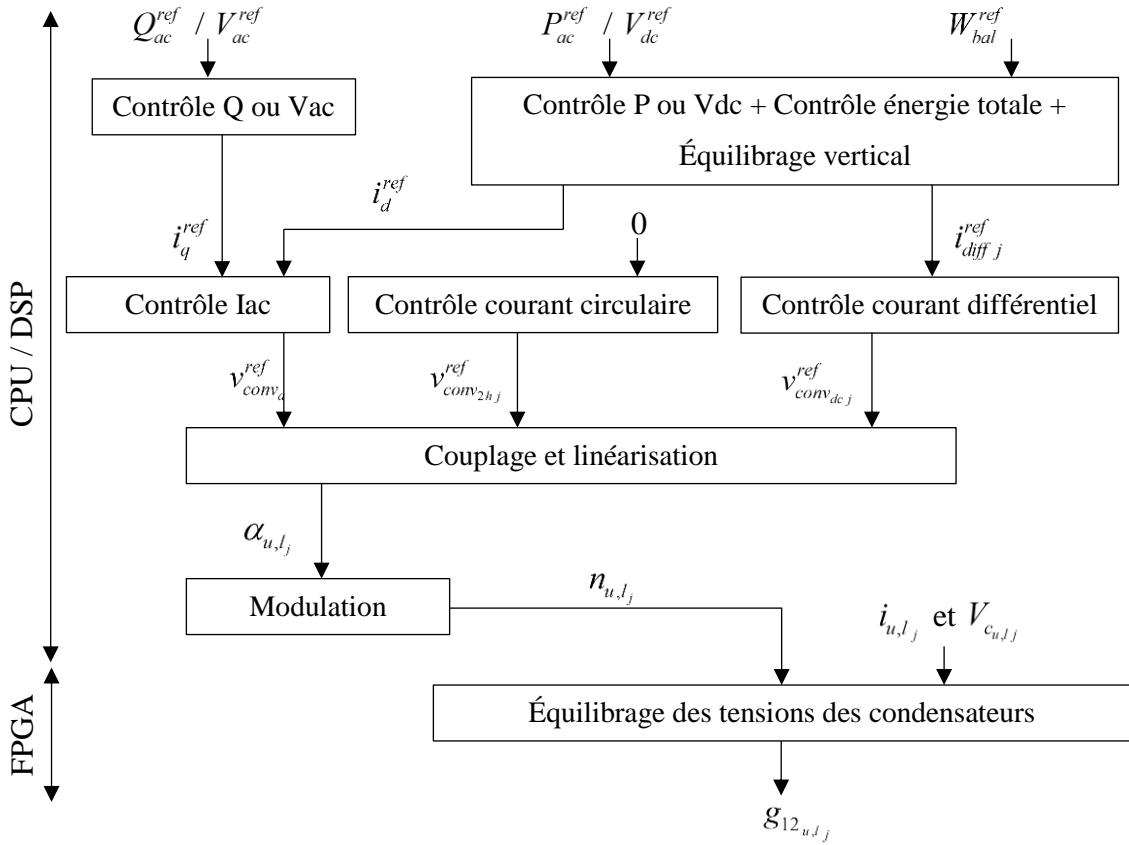

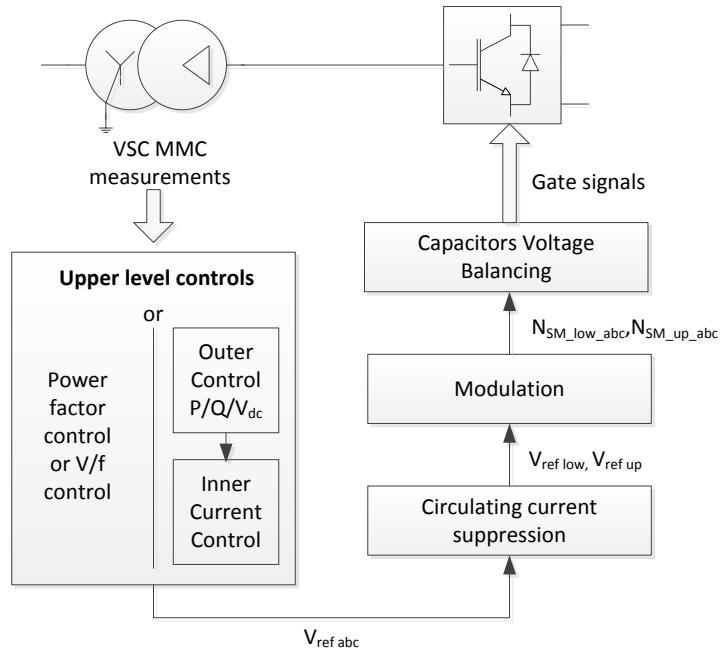

| Figure 4-1: Contrôle simplifié d'un convertisseur MMC [49] .....                                             | 72 |

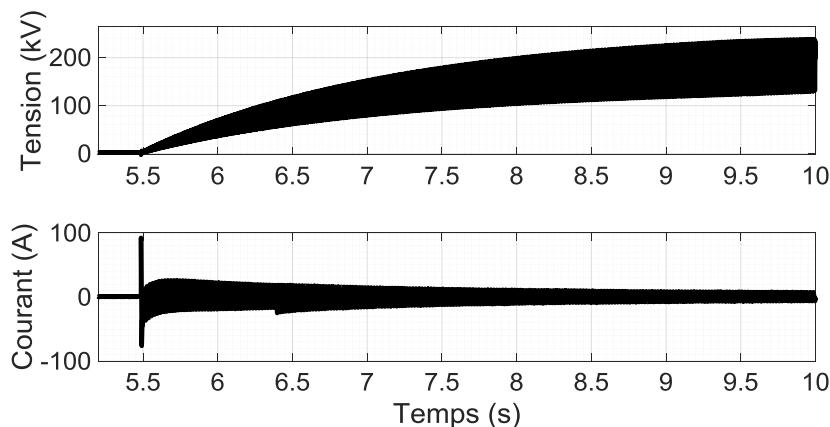

| Figure 4-2: Tension CC et courant CA mesurés lors de la mise sous tension de la liaison France Espagne ..... | 75 |

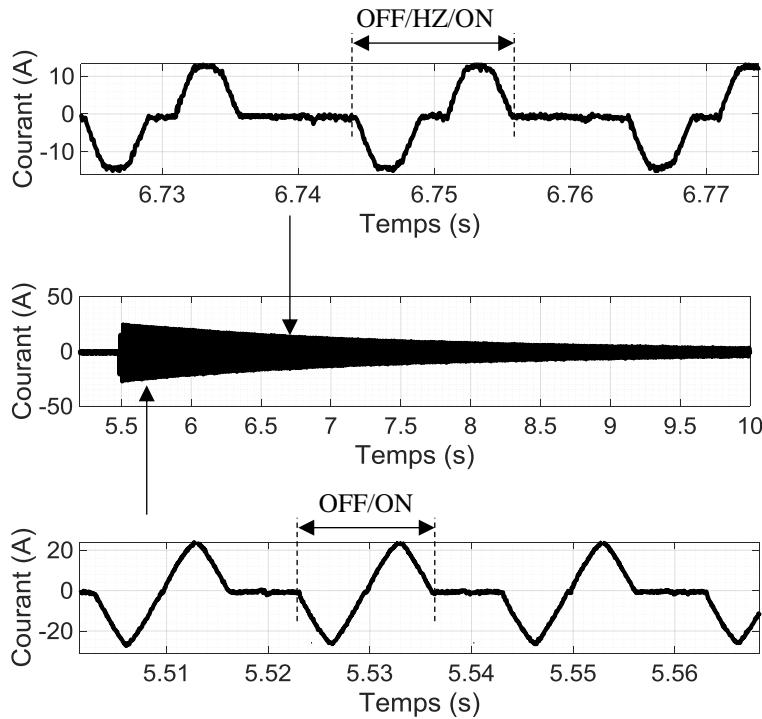

| Figure 4-3: Courants de demi-bras mesurés lors de la mise sous tension de la liaison France Espagne .....    | 76 |

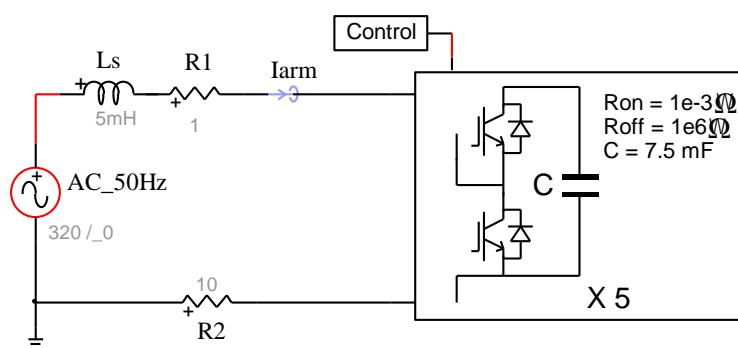

| Figure 4-4: Cas test pour comparaison des deux formulations du Modèle 2a .....                               | 77 |

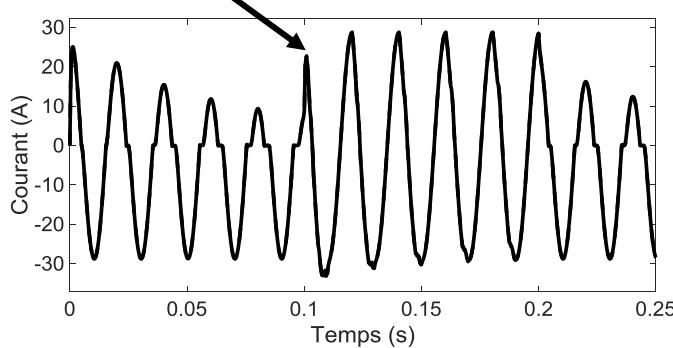

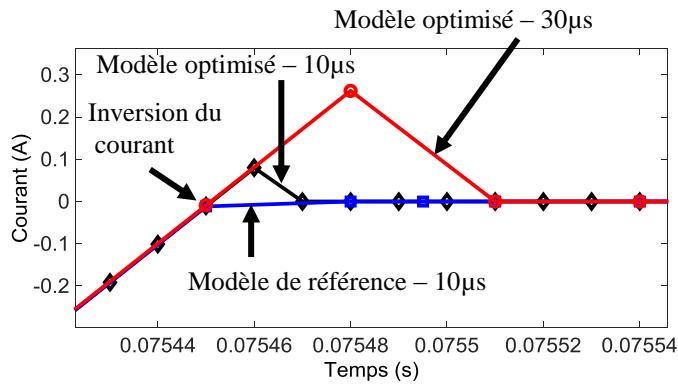

| Figure 4-5: Courant dans le demi-bras (modèles référence et optimisé superposés).....                        | 79 |

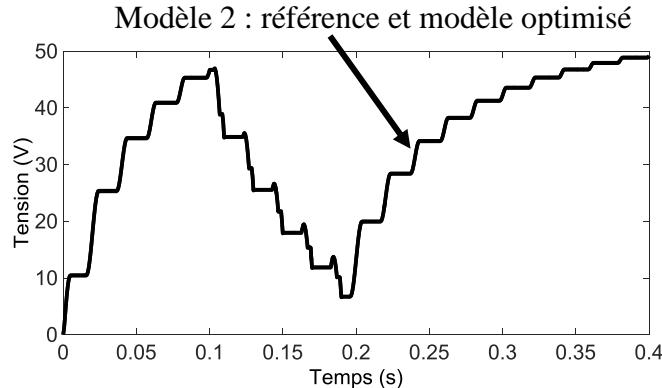

| Figure 4-6: Courant dans le demi-bras (zoom) .....                                                           | 79 |

| Figure 4-7: Tension du premier sous-module .....                                                             | 79 |

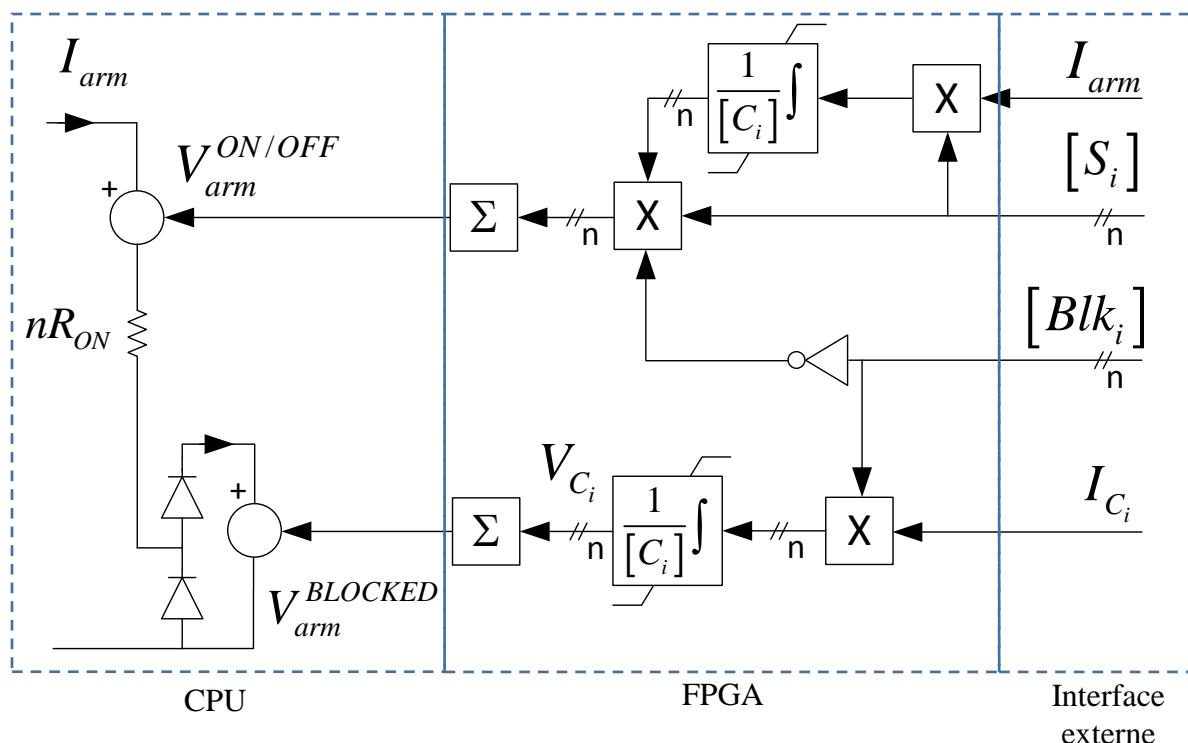

| Figure 4-8: Implémentation du Modèle 2b sur une plateforme CPU/FPGA .....                                    | 88 |

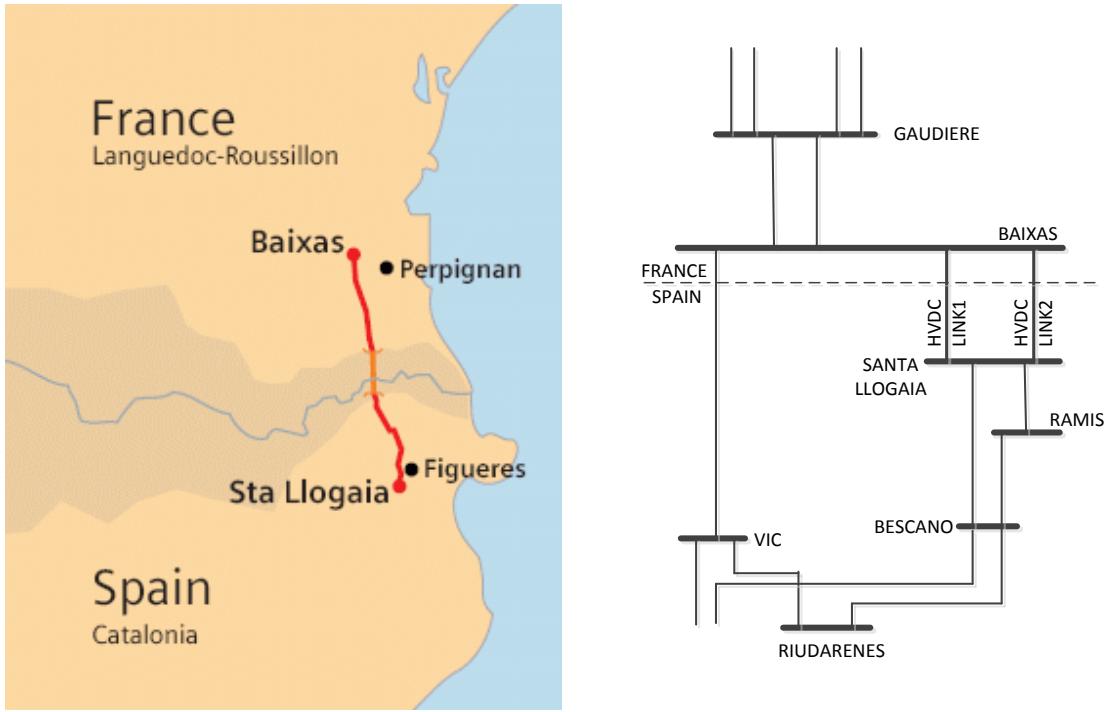

| Figure 5-1: Localisation de l'interconnexion HVDC France-Espagne.....                                        | 91 |

| Figure 5-2: Localisation de l'interconnexion HVDC France-Espagne.....                                        | 91 |

| Figure 5-3: Détails de la topologie des convertisseurs MMC de France-Espagne .....                           | 92 |

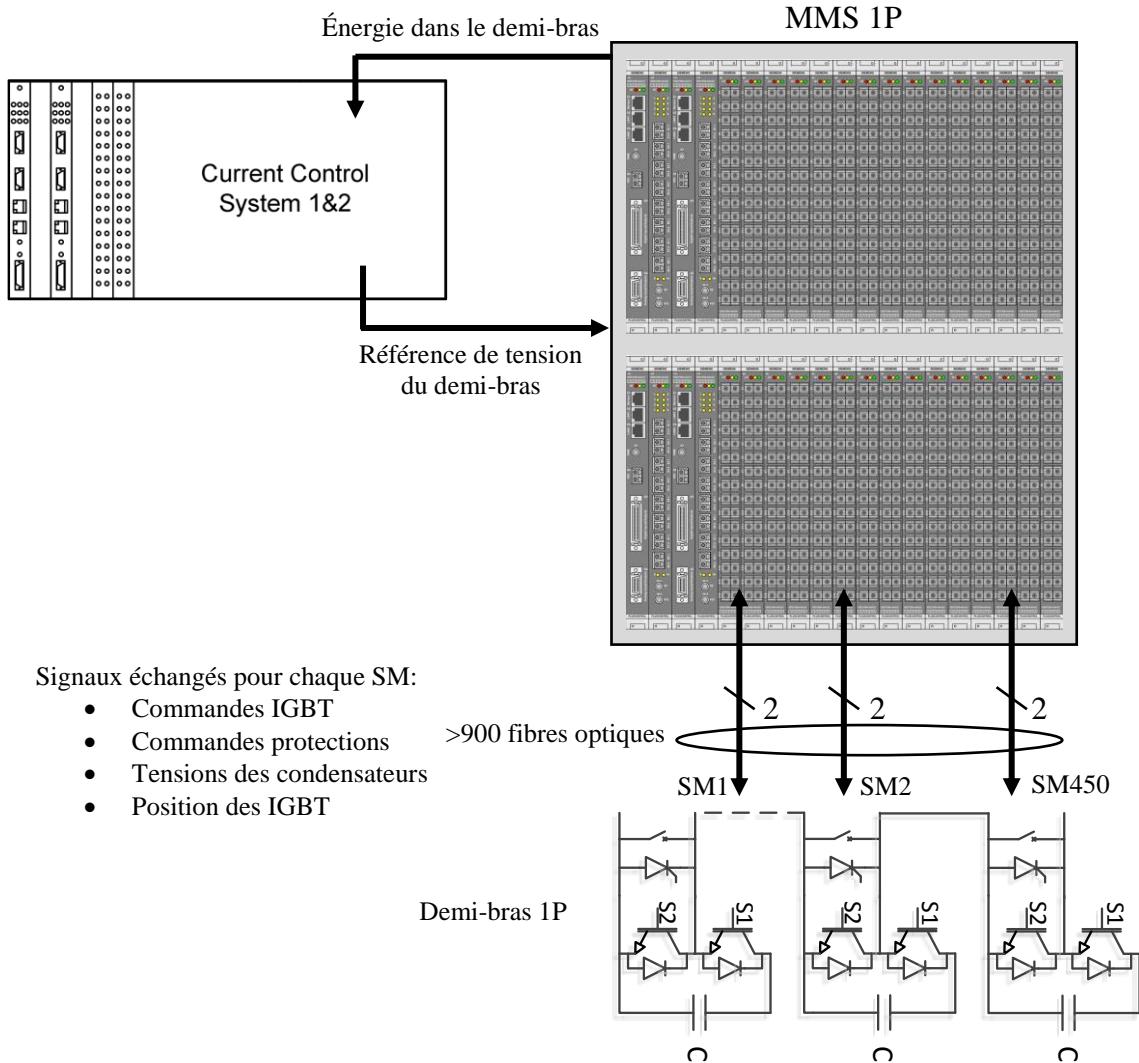

| Figure 5-4: Interface physique entre une armoire MMS et un demi-bras .....                                   | 94 |

| Figure 5-5: Circuit équivalent pour un convertisseur.....                                                    | 95 |

| Figure 5-6: Caractéristique tension/courant des parafoudres connectés en sortie de convertisseur .....       | 96 |

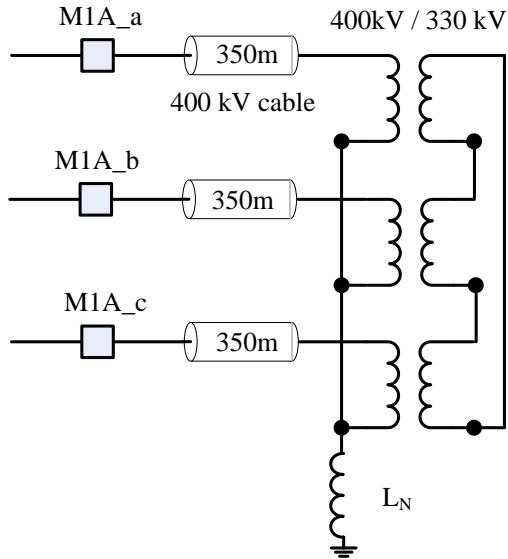

| Figure 5-7: Topologie de raccordement du transformateur de la liaison 2 INELFE .....                         | 97 |

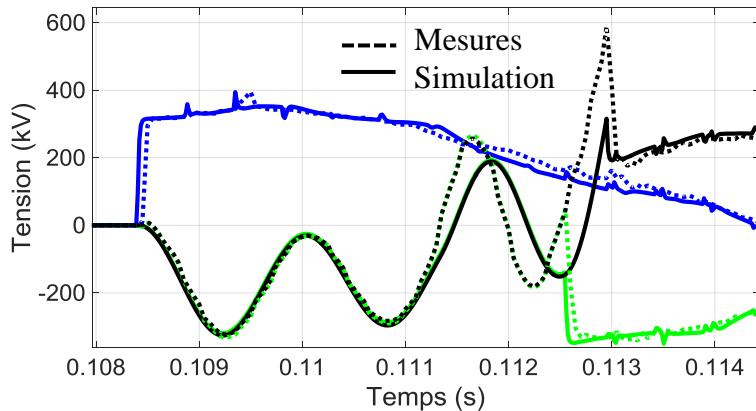

| Figure 5-8: Tensions au primaire du transformateur lors de sa mise sous tension .....                        | 98 |

| Figure 5-9: Tensions au primaire du transformateur lors de sa mise sous tension (Zoom) .....                 | 98 |

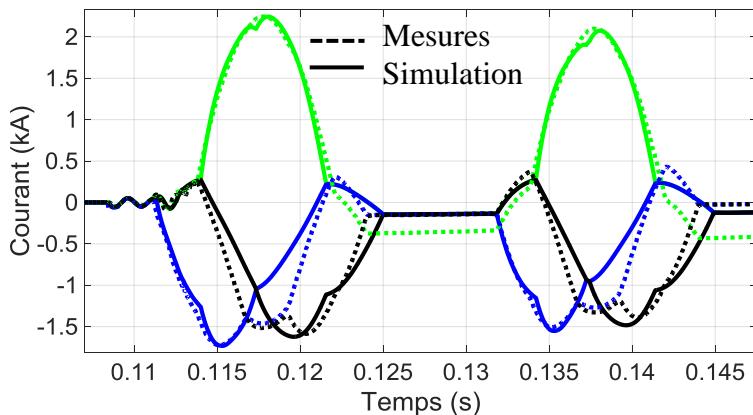

| Figure 5-10: Courant au primaire du transformateur lors de sa mise sous tension .....                        | 98 |

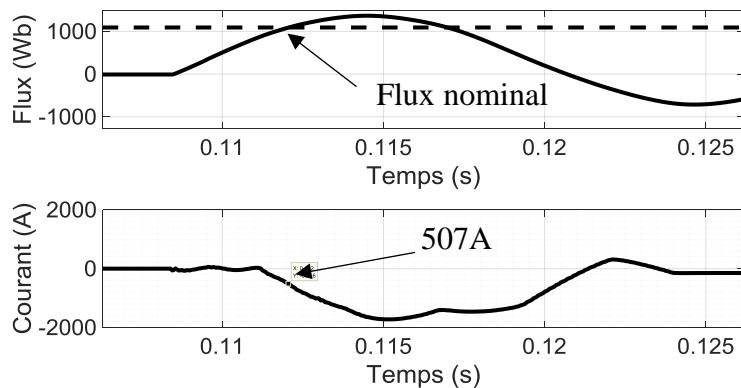

|                                                                                                              |     |

|--------------------------------------------------------------------------------------------------------------|-----|

| Figure 5-11: Flux et courant dans une unité du transformateur pendant la mise sous tension                   | 99  |

| Figure 5-12: Répartition des tâches de la simulation temps réel sans E/S .....                               | 101 |

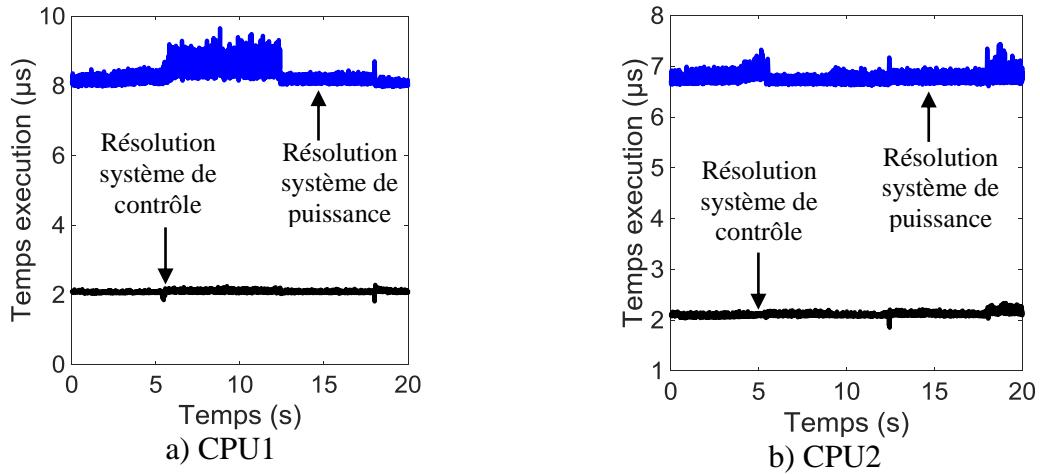

| Figure 5-13: Temps d'exécution des tâches dans Hypersim pour le circuit de la Figure 5-12 .....              | 102 |

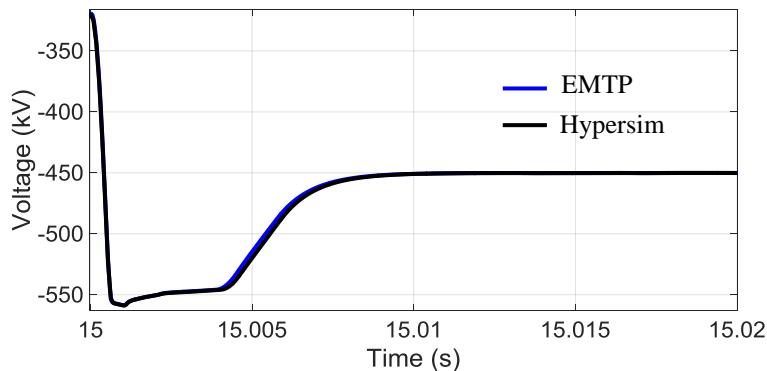

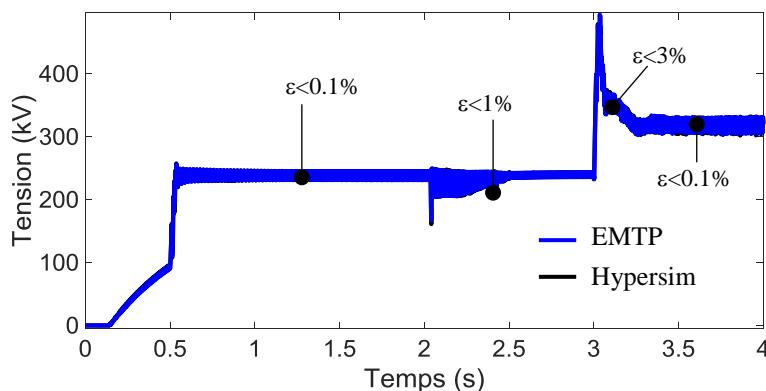

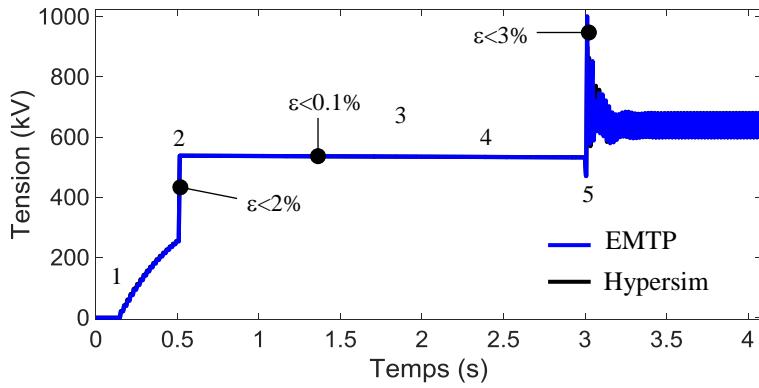

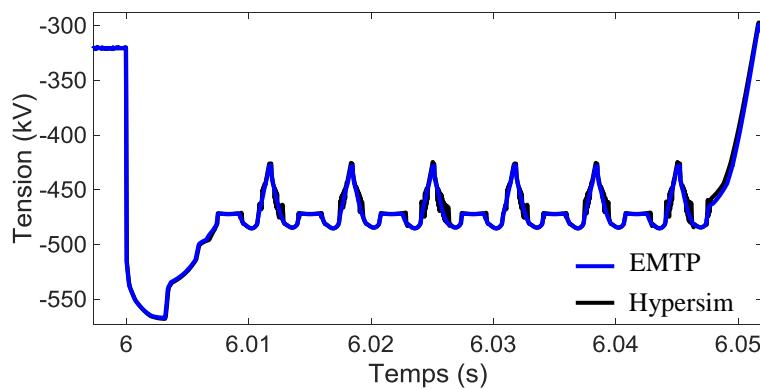

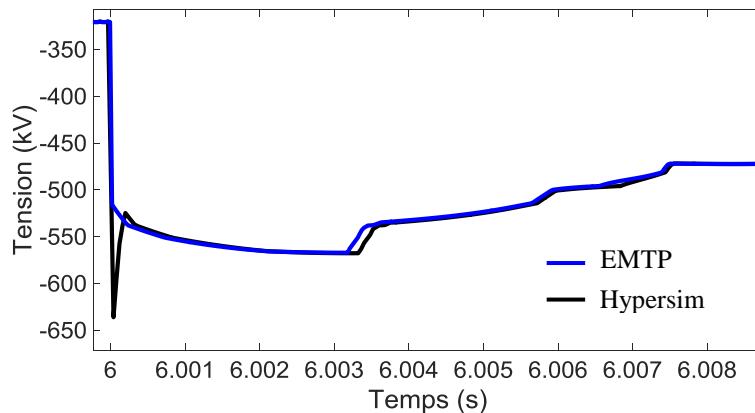

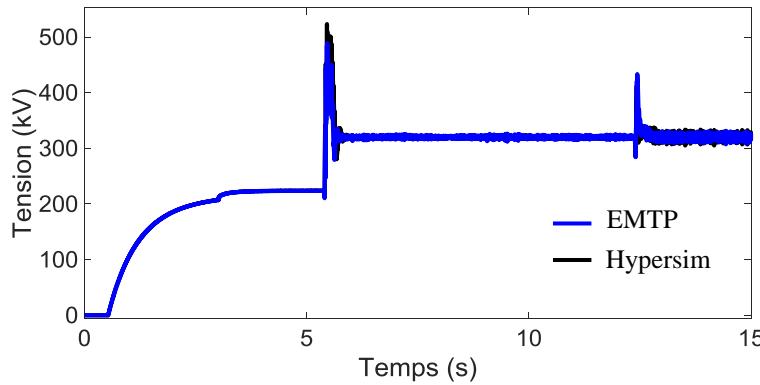

| Figure 5-14: Tension pôle-terre en sortie de convertisseur (pôle positif) .....                              | 103 |

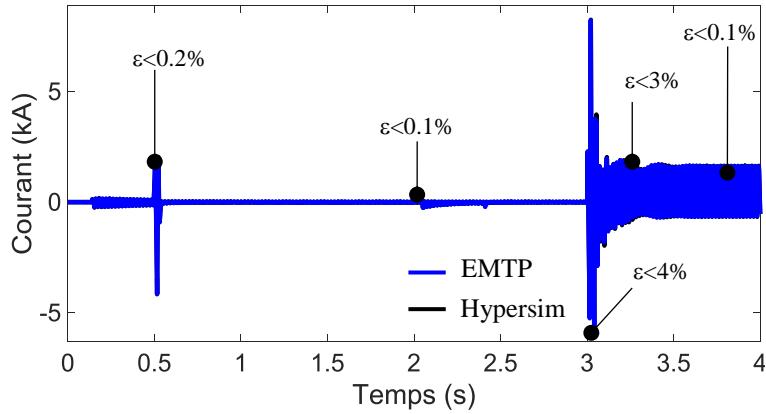

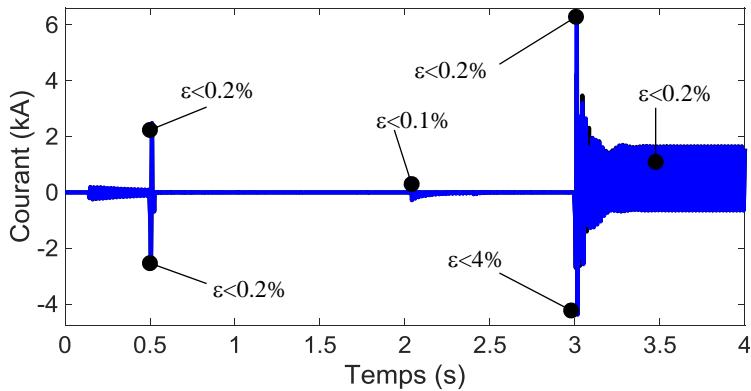

| Figure 5-15: Courant d'un demi-bras positif – phase a .....                                                  | 104 |

| Figure 5-16: Localisation du défaut pôle-terre et des parafoudres .....                                      | 105 |

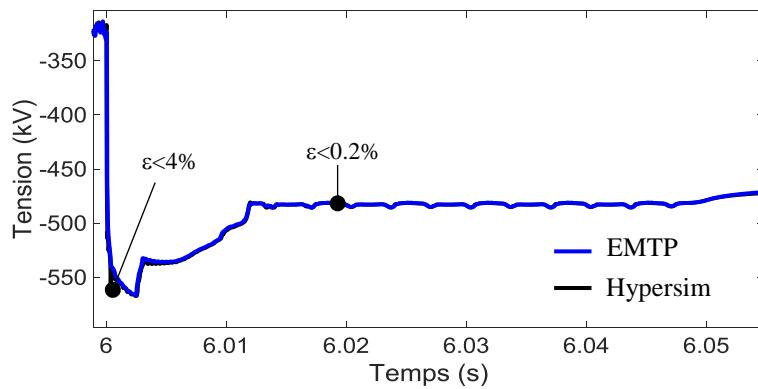

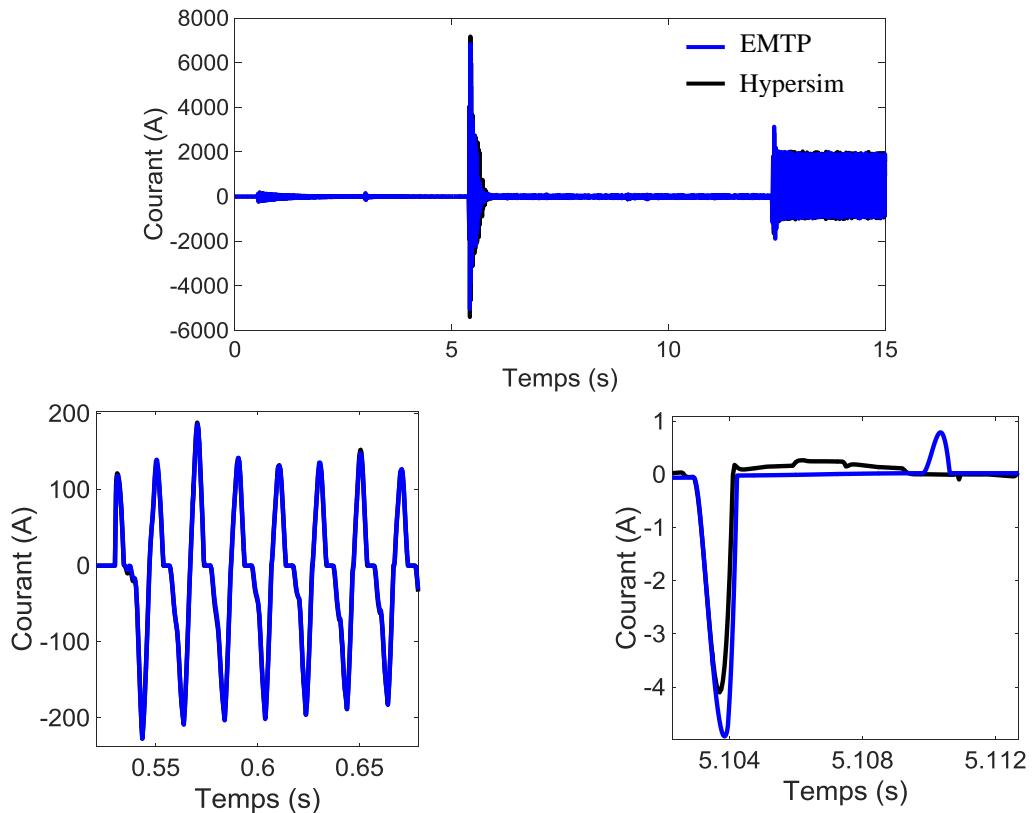

| Figure 5-17: Tension du pôle sain lors d'un défaut à la terre de l'autre pôle .....                          | 105 |

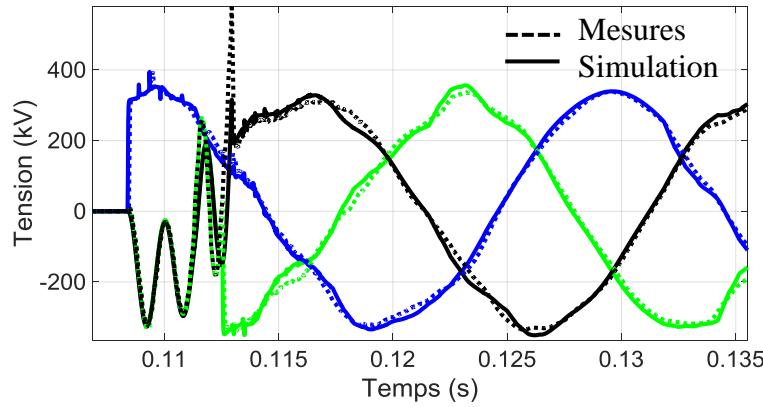

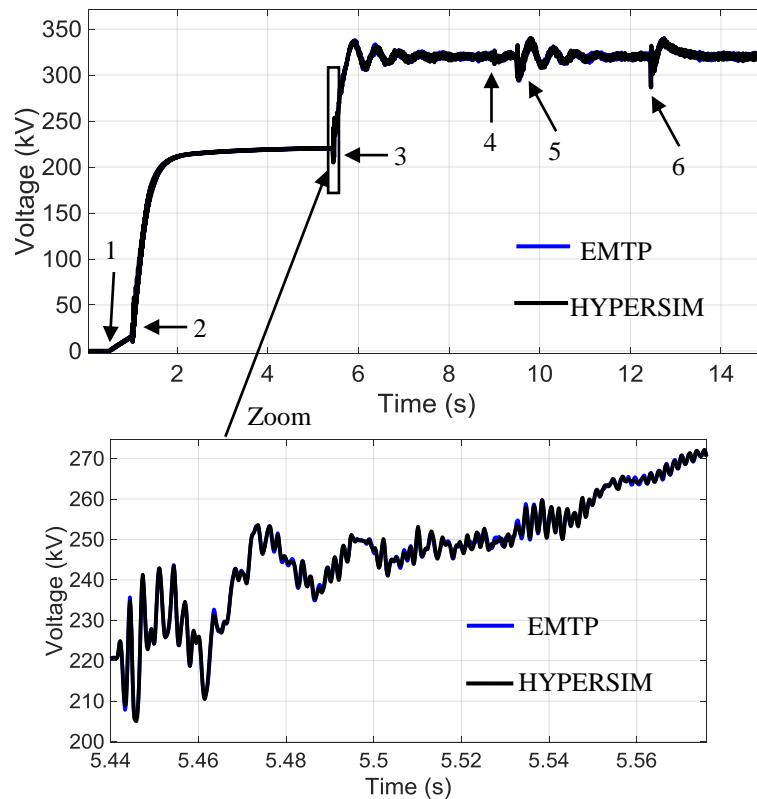

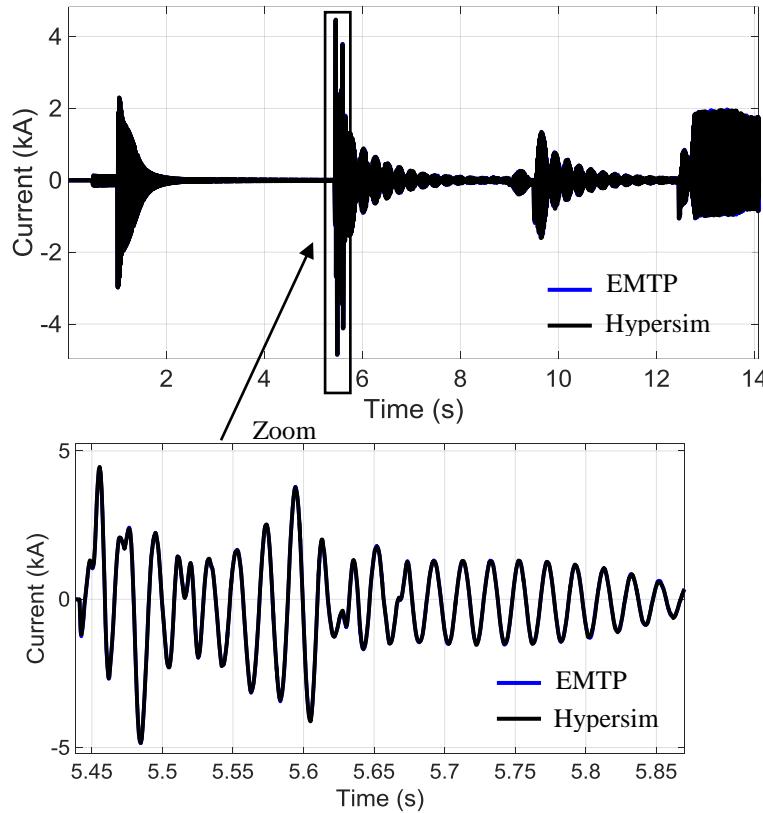

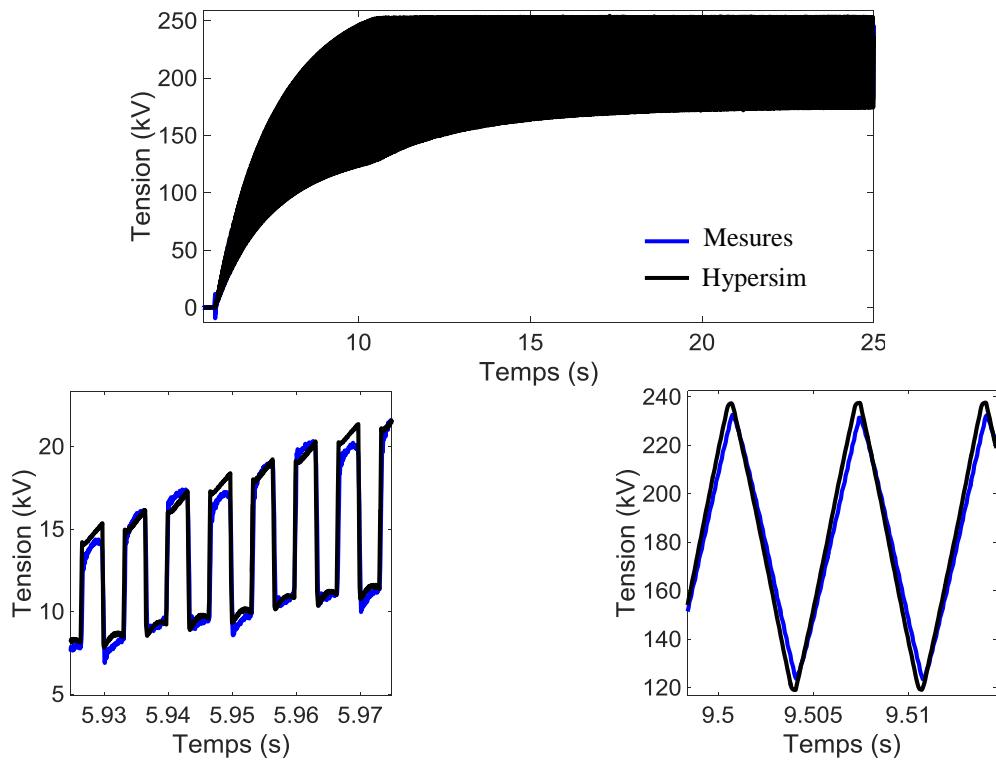

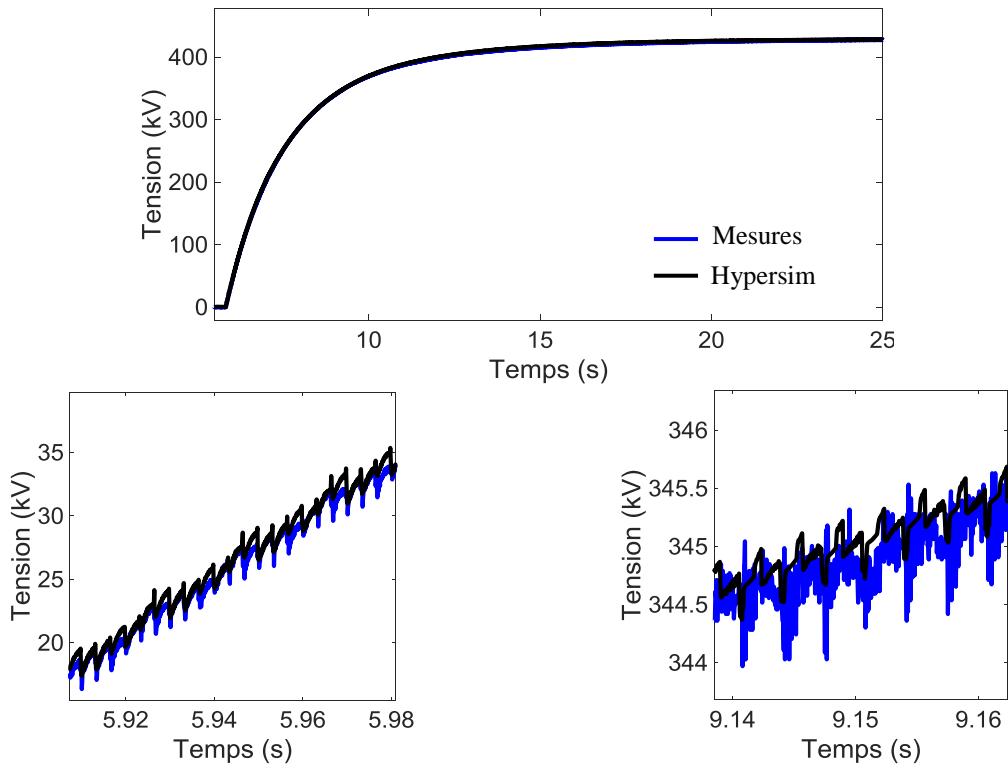

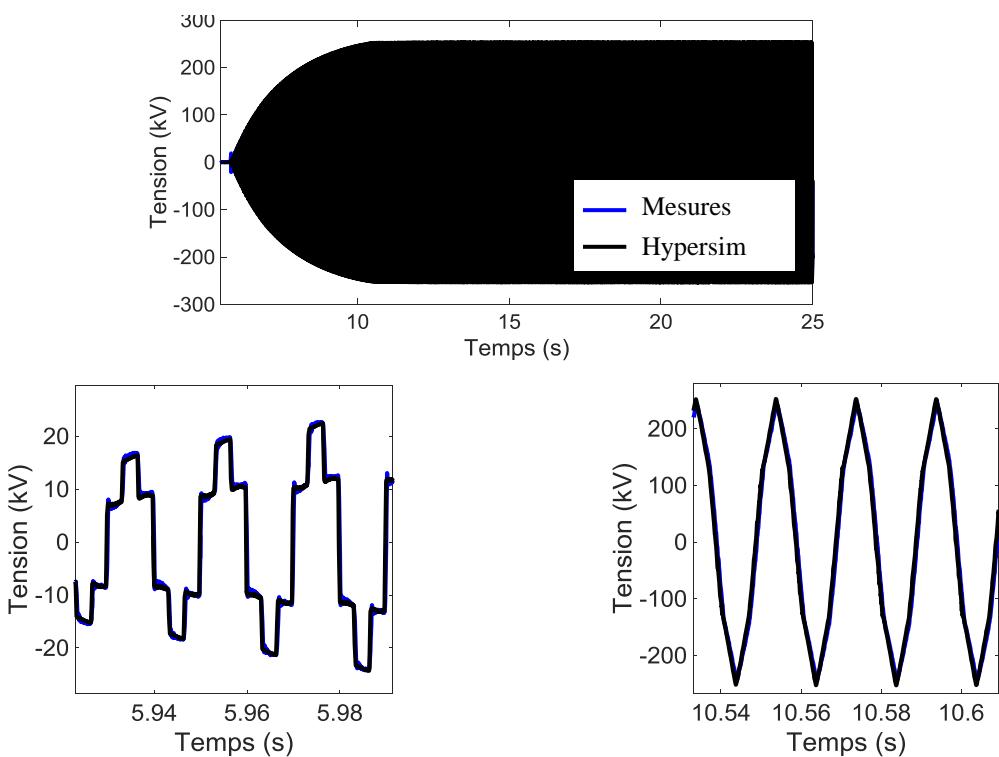

| Figure 5-18: Tension pôle-terre – séquence de démarrage STATCOM .....                                        | 107 |

| Figure 5-19: Tension pôle-pôle – séquence de démarrage STATCOM .....                                         | 107 |

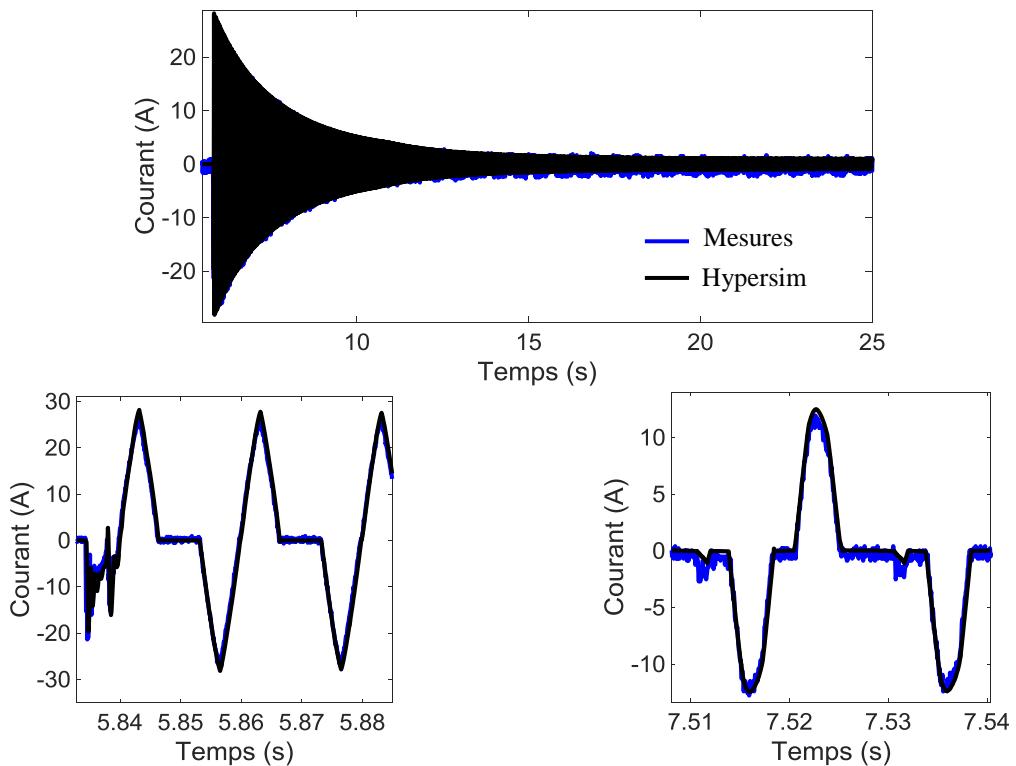

| Figure 5-20: Courant demi-bras positif phase-a – séquence de démarrage STATCOM .....                         | 108 |

| Figure 5-21: Tension transformateur côté convertisseur – séquence de démarrage STATCOM .....                 | 108 |

| Figure 5-22: Vue générale de la plateforme de test incluant les E/S .....                                    | 109 |

| Figure 5-23: Photo de la plateforme de test .....                                                            | 110 |

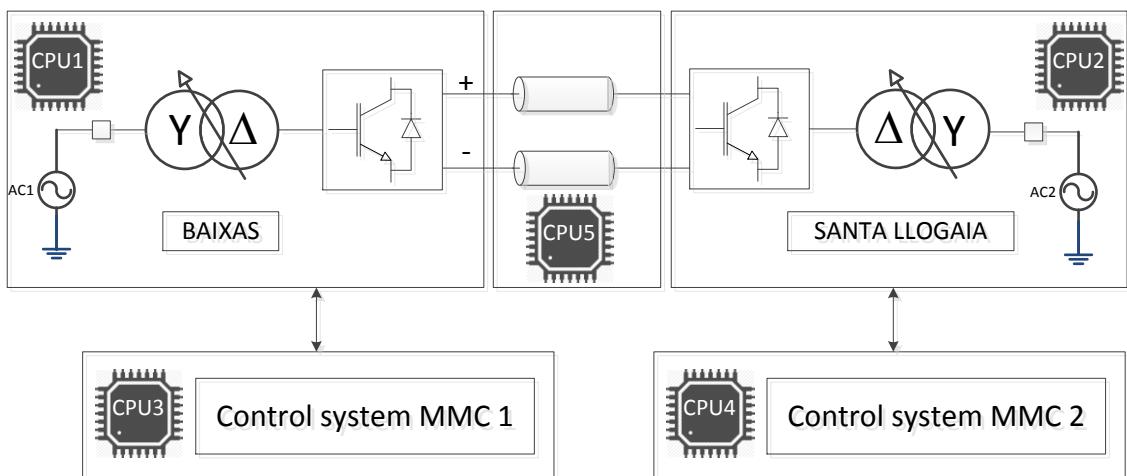

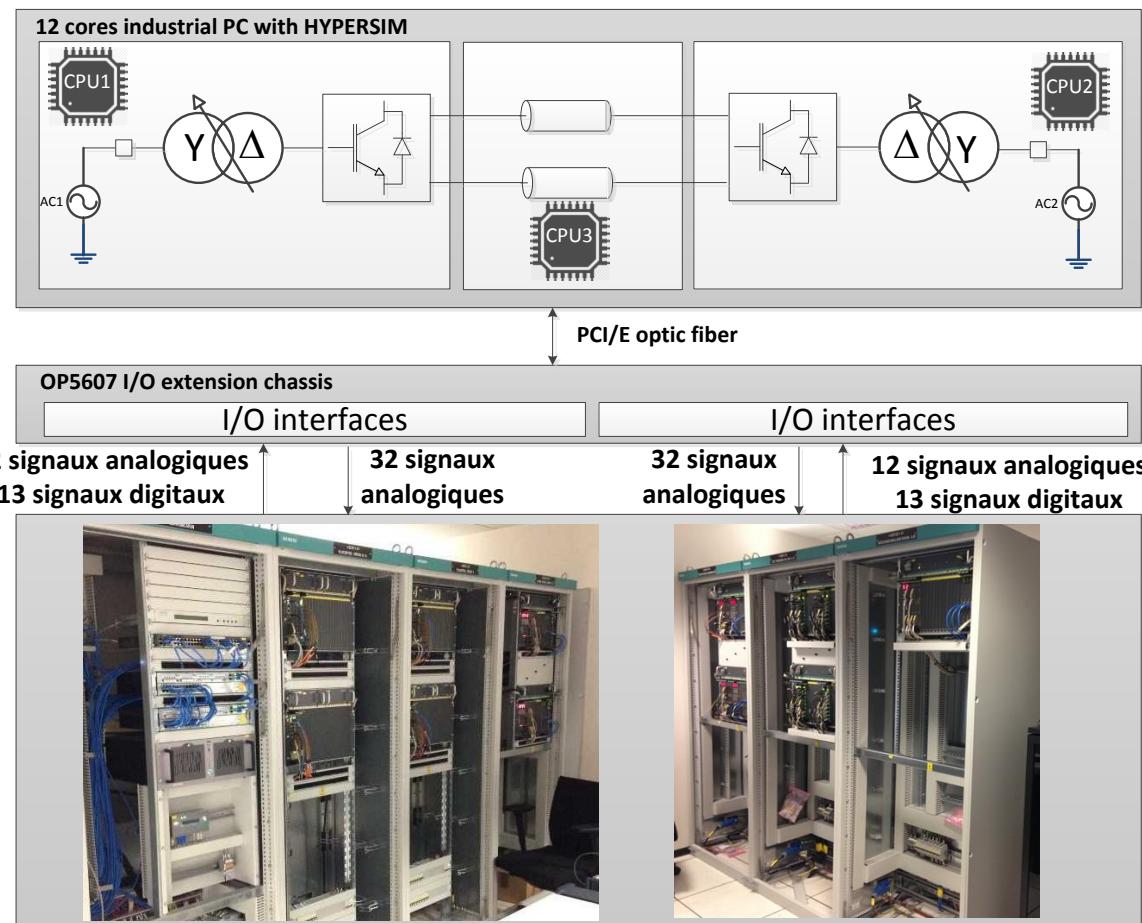

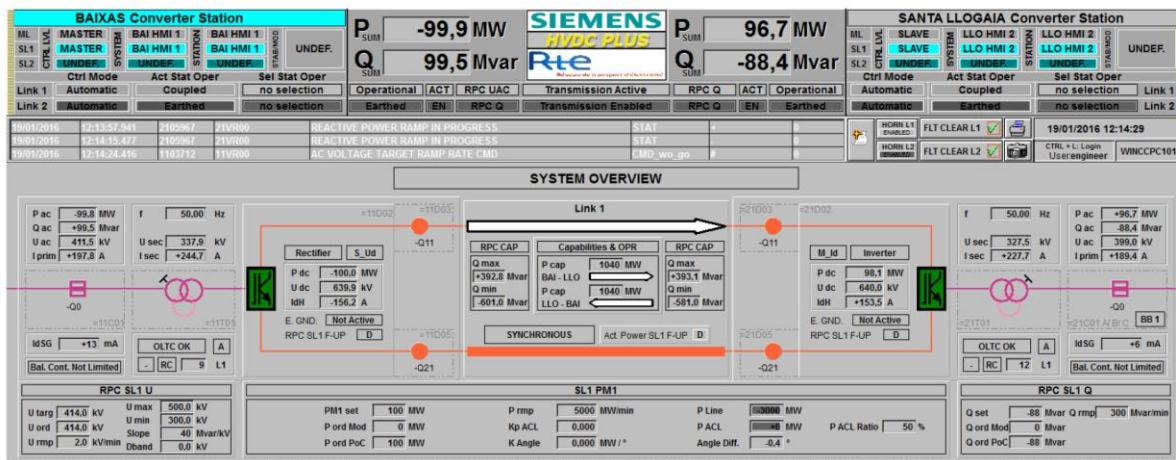

| Figure 5-24: Interfaçage des répliques de contrôle commande avec le modèle temps réel ..                     | 113 |

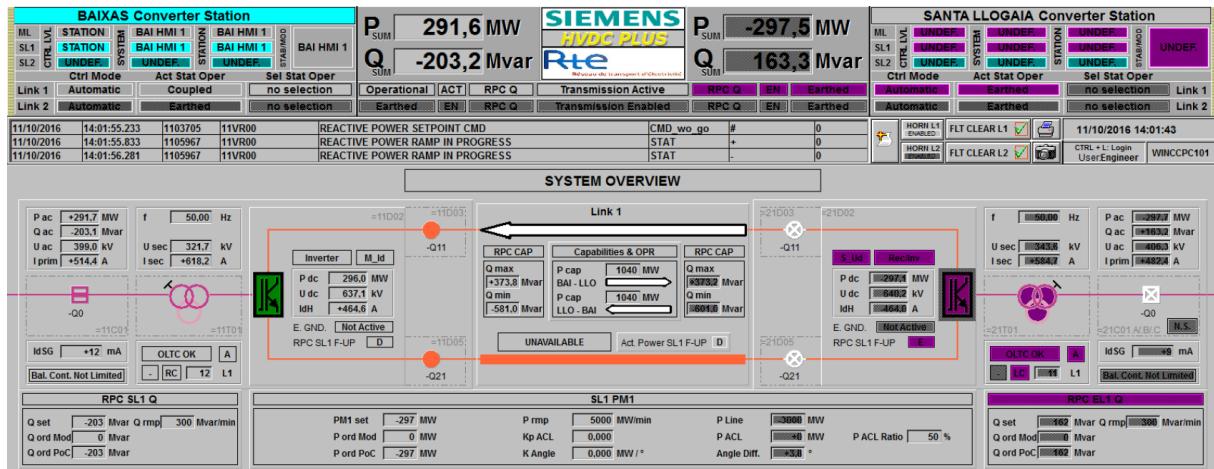

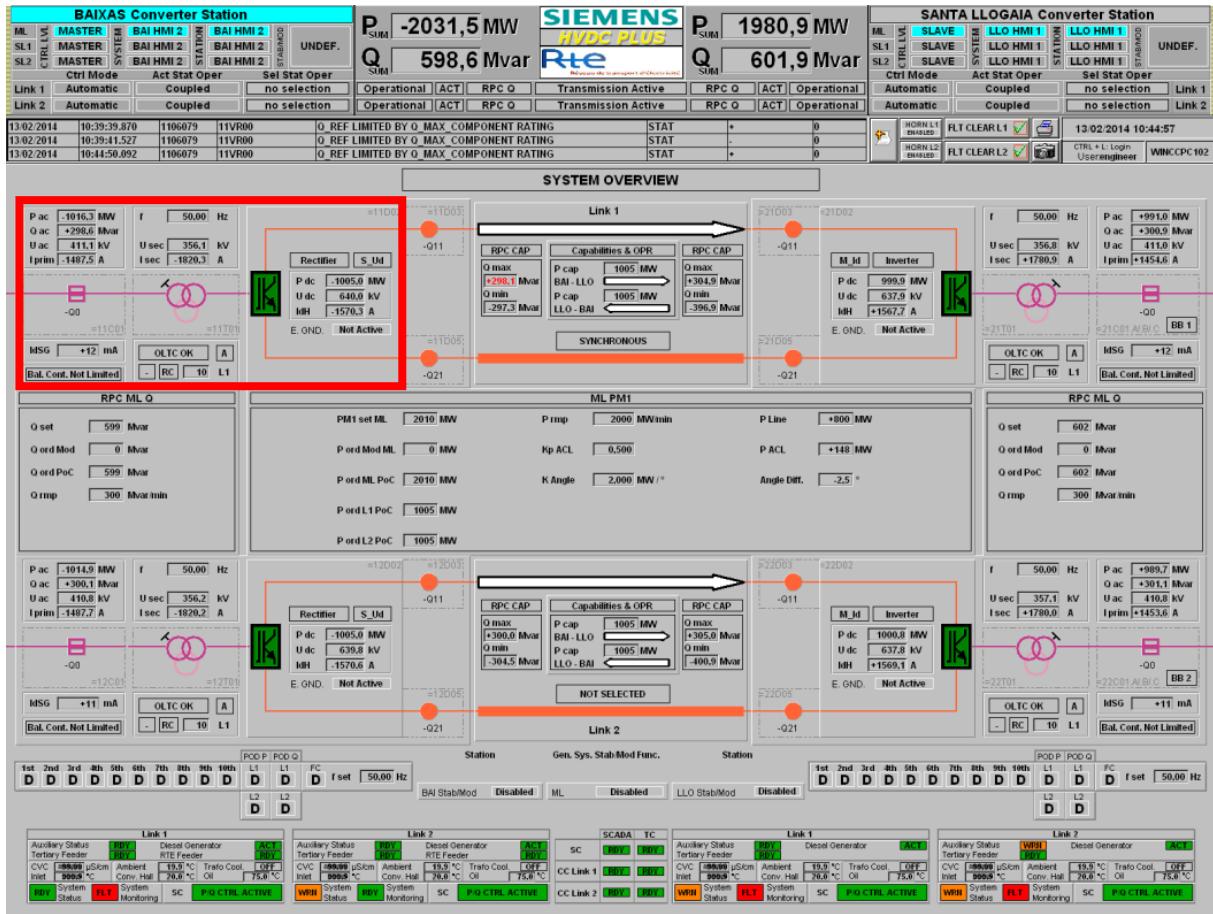

| Figure 5-25: IHM de la réplique du contrôle commande .....                                                   | 114 |

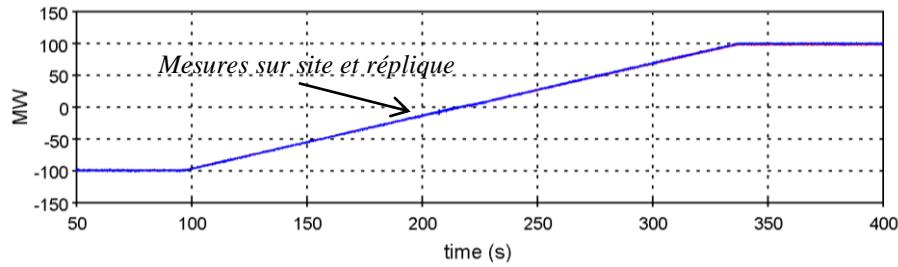

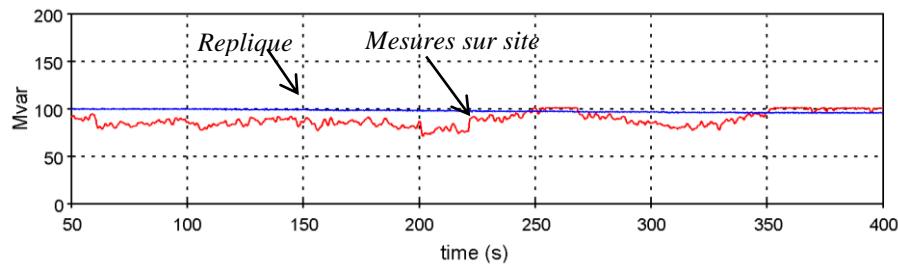

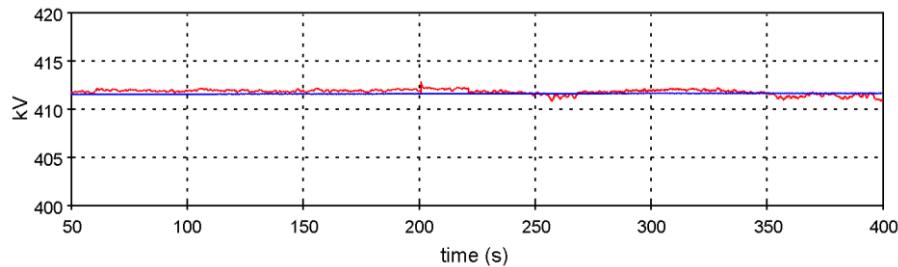

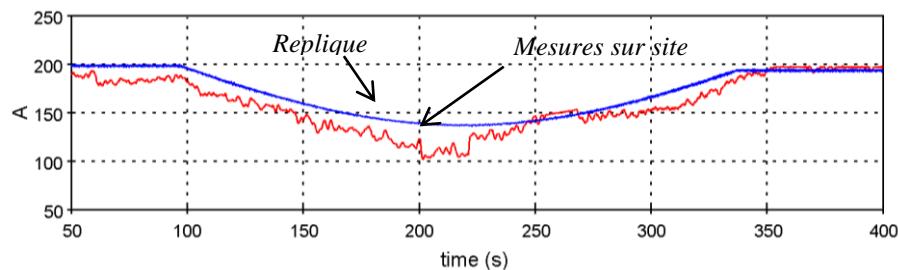

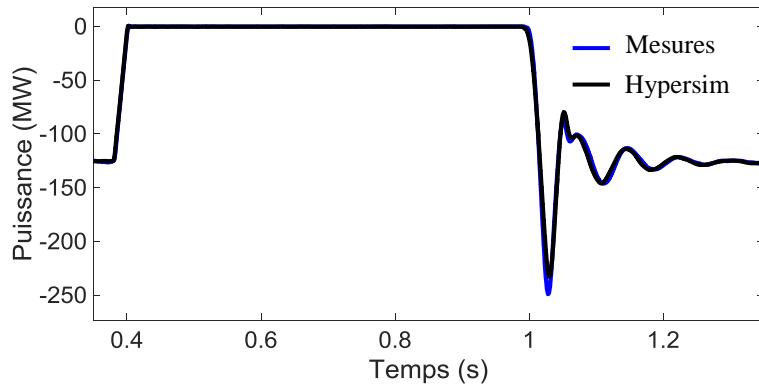

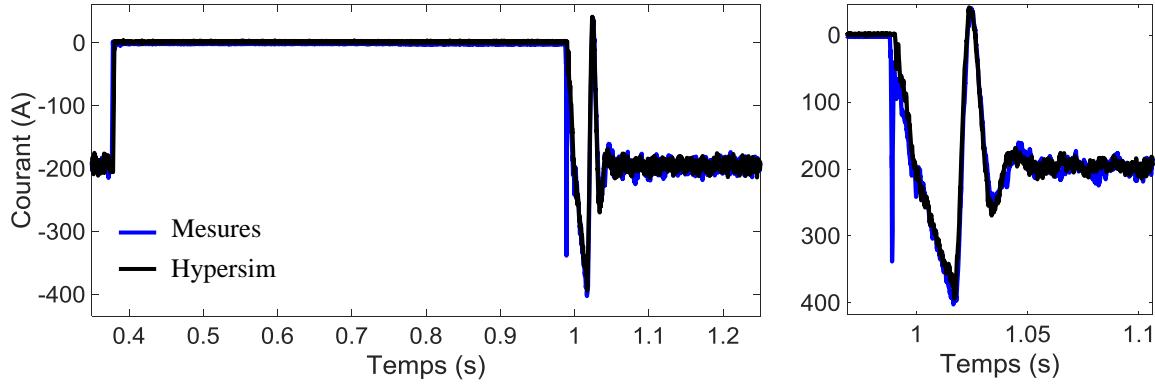

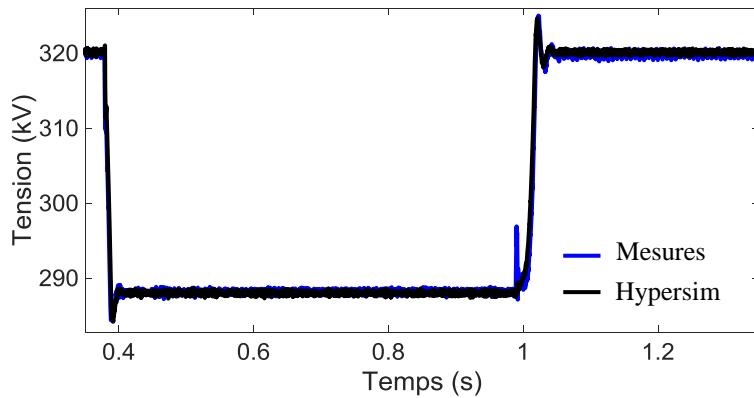

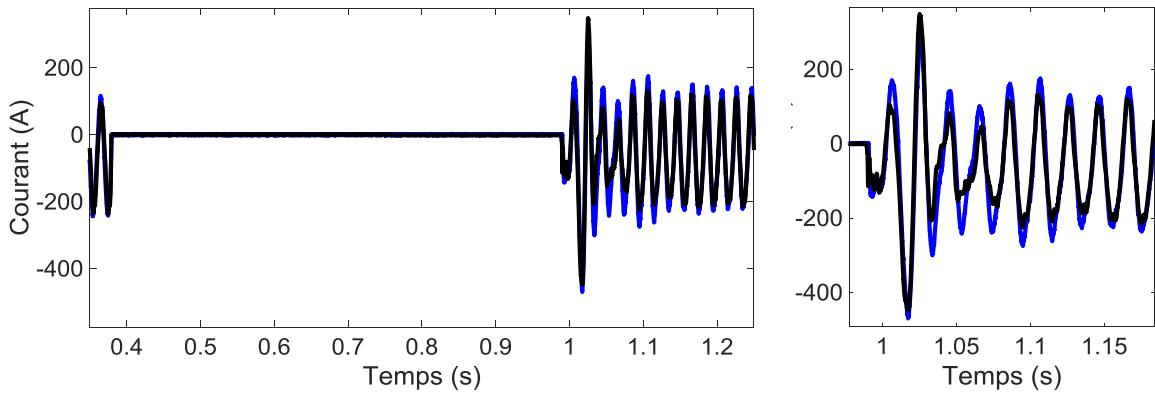

| Figure 5-26: Comparaisons entre mesures sur site et simulations temps réel avec les répliques à BAIXAS ..... | 116 |

| Figure 5-27: Etat de la liaison avant l'essai d'échelon de puissance .....                                   | 117 |

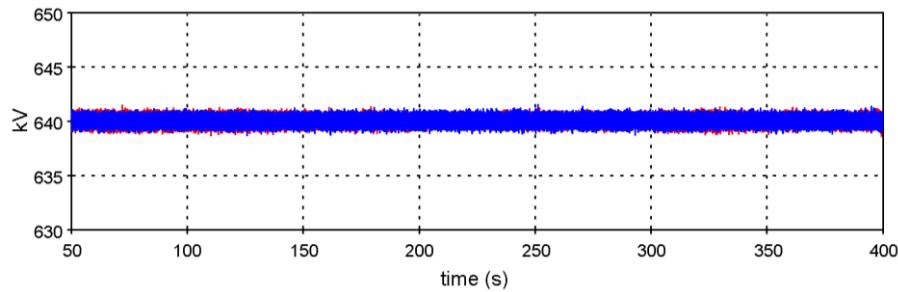

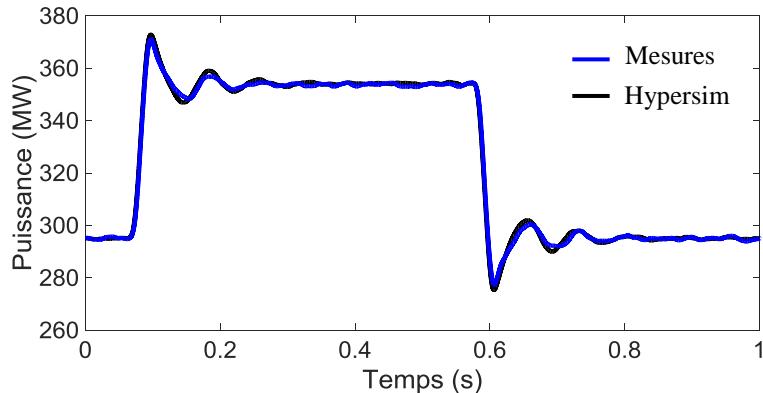

| Figure 5-28: Puissance active injectée sur le réseau français lors de l'essai d'échelon de puissance .....   | 117 |

| Figure 5-29: Courant CC lors de l'essai d'échelon de puissance .....                                         | 118 |

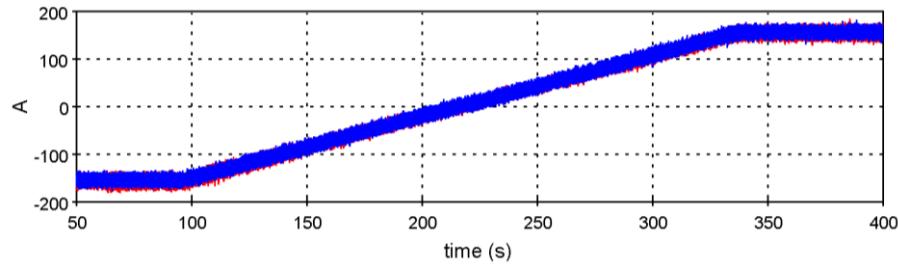

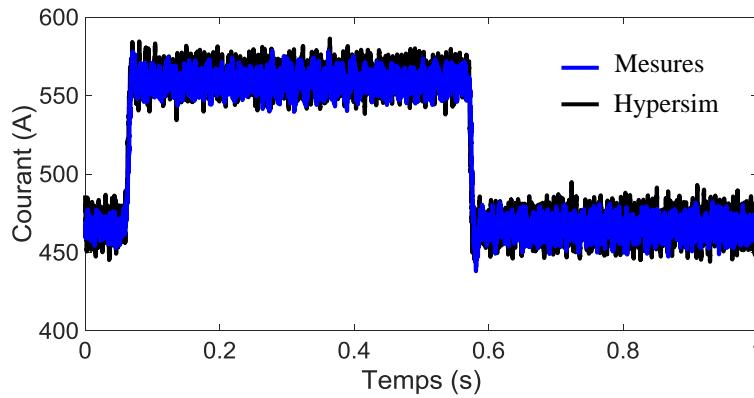

| Figure 5-30: Etat de la liaison avant l'essai de blocage .....                                               | 118 |

| Figure 5-31: Transit de puissance lors du blocage d'un convertisseur .....                                   | 119 |

| Figure 5-32: Courant CC lors du blocage d'un convertisseur .....                                             | 120 |

| Figure 5-33: Courant CC lors du blocage d'un convertisseur .....                                             | 120 |

|                                                                                                                             |     |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5-34: Courant dans le demi-bras supérieur phase-a lors du blocage d'un convertisseur .....                           | 120 |

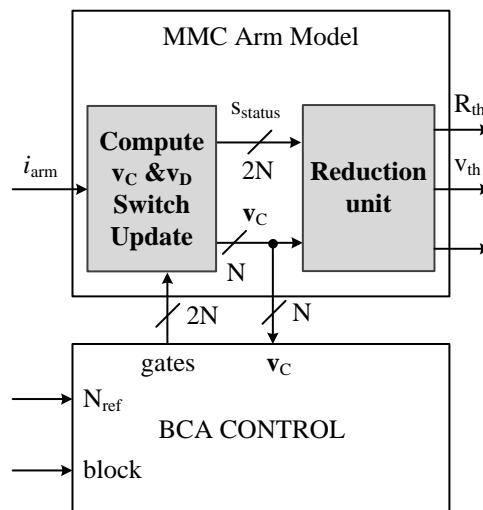

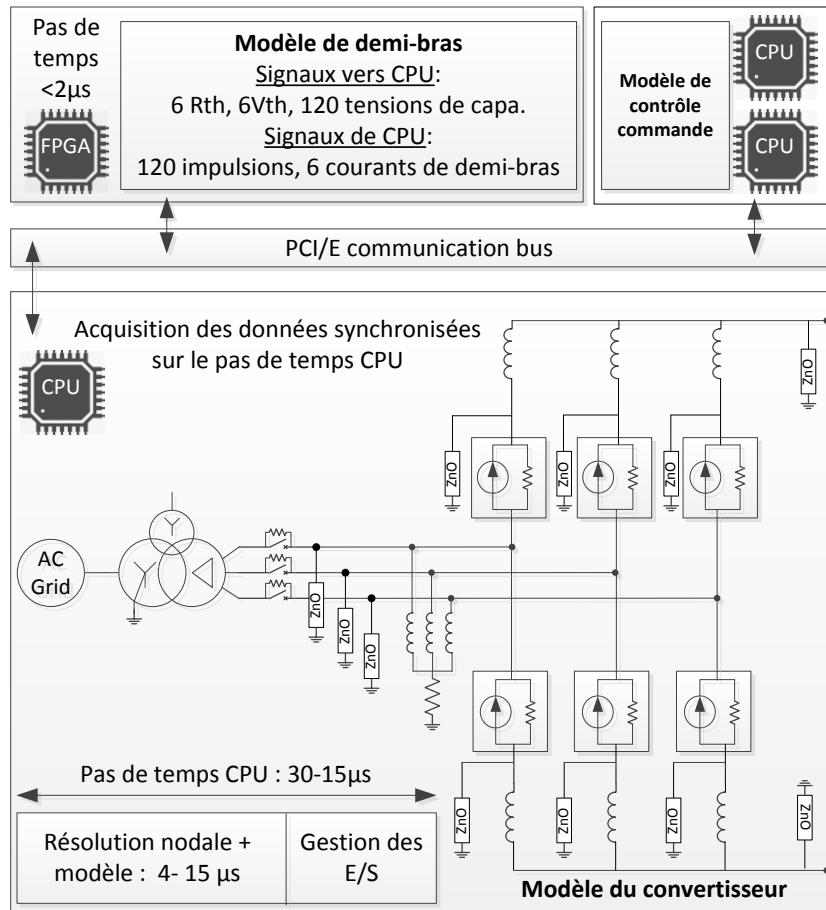

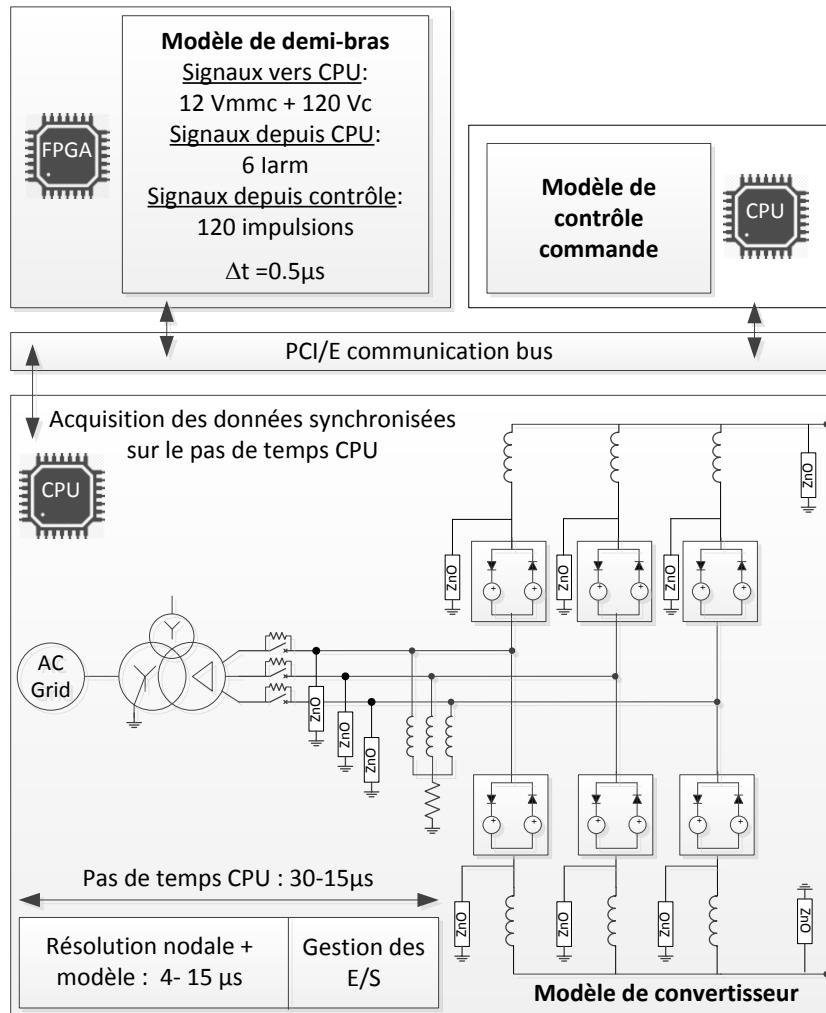

| Figure 6-1: Vue schématique du modèle 2 implémenté sur FPGA.....                                                            | 122 |

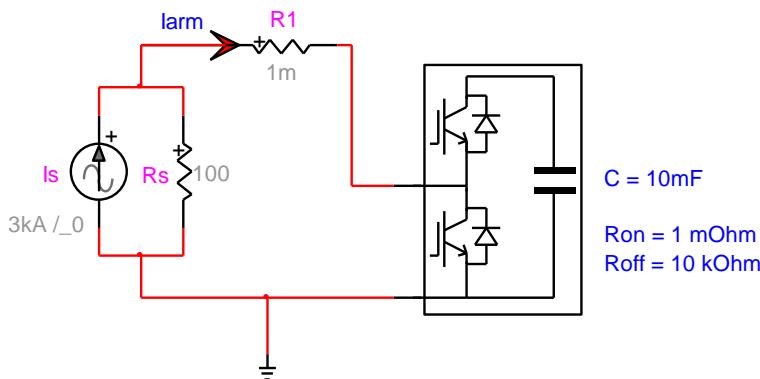

| Figure 6-2: Circuit de test pour comparaison des implémentations virgules flottantes/fixes                                  | 123 |

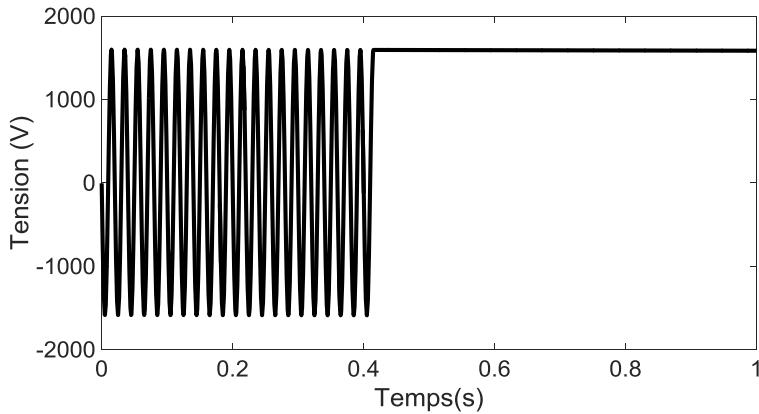

| Figure 6-3: Tension aux bornes du sous-module de la Figure 6-2 .....                                                        | 125 |

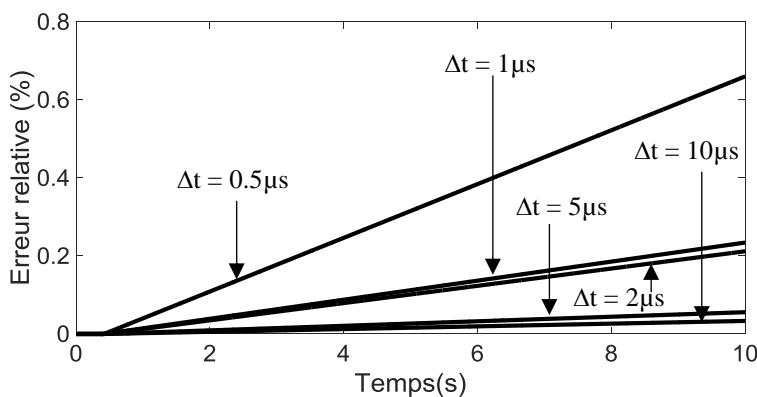

| Figure 6-4: Erreur relative en fonction du pas de temps de la simulation .....                                              | 125 |

| Figure 6-5: Etape 2c (voir section 4.1.2) de la validation du modèle 2 implémenté sur FPGA .....                            | 126 |

| Figure 6-6: Tension pôle-terre lors de la séquence de démarrage.....                                                        | 127 |

| Figure 6-7: Courant demi-bras positif – phase-a lors de la séquence de démarrage.....                                       | 128 |

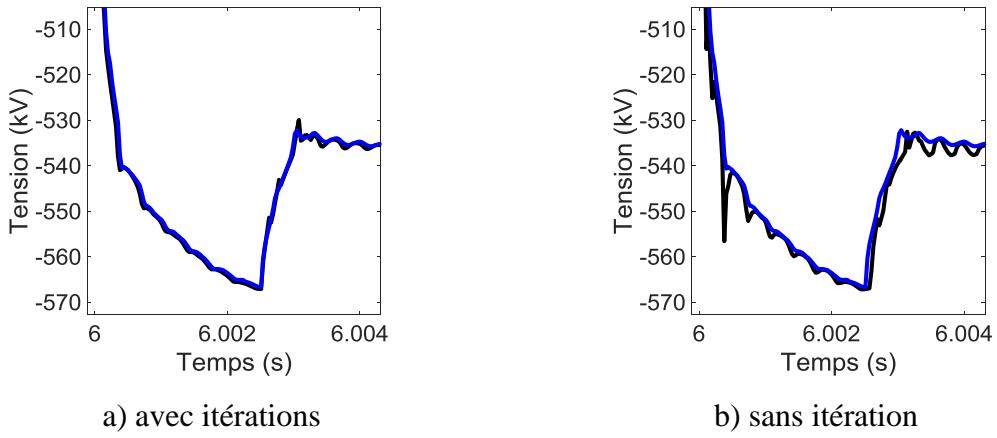

| Figure 6-8: Tension pôle-terre (pôle sain) lors d'un défaut pôle-terre (sans itération) .....                               | 128 |

| Figure 6-9: Tension pôle-terre (pôle sain) lors d'un défaut pôle-terre (Zoom) .....                                         | 129 |

| Figure 6-10: Etape 2c (voir section 4.1.2) de la validation du modèle 2 implémenté sur FPGA pour un grand nombre de SM..... | 130 |

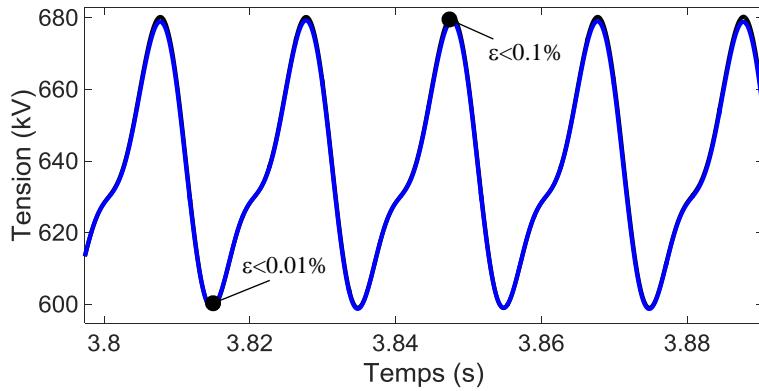

| Figure 6-11: Somme des tensions des condensateurs du demi-bras positif de la phase-a .....                                  | 131 |

| Figure 6-12: Somme des tensions des condensateurs du demi-bras positif de la phase-a (zoom) .....                           | 131 |

| Figure 6-13: Courant de demi-bras positif phase-a .....                                                                     | 131 |

| Figure 6-14: Tension pôle-terre (pôle sain) lors d'un défaut pôle-terre (avec itération) .....                              | 132 |

| Figure 6-15: Tension pôle-terre (pôle sain) lors d'un défaut pôle-terre (sans itération - Zoom) .....                       | 132 |

| Figure 6-16: Etape 2c (voir section 4.1.2) de la validation du Modèle 2b implémenté sur FPGA .....                          | 134 |

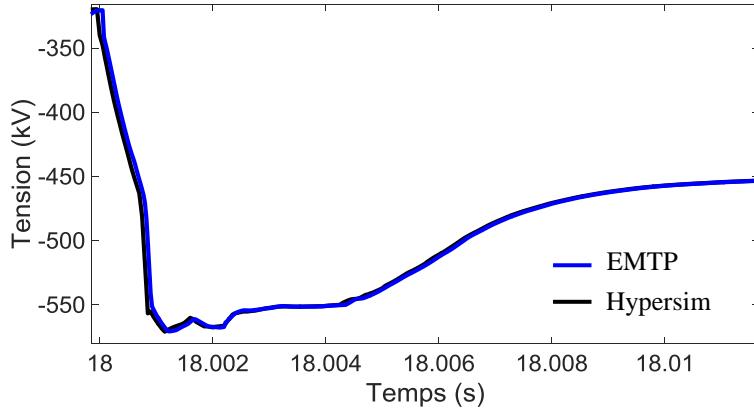

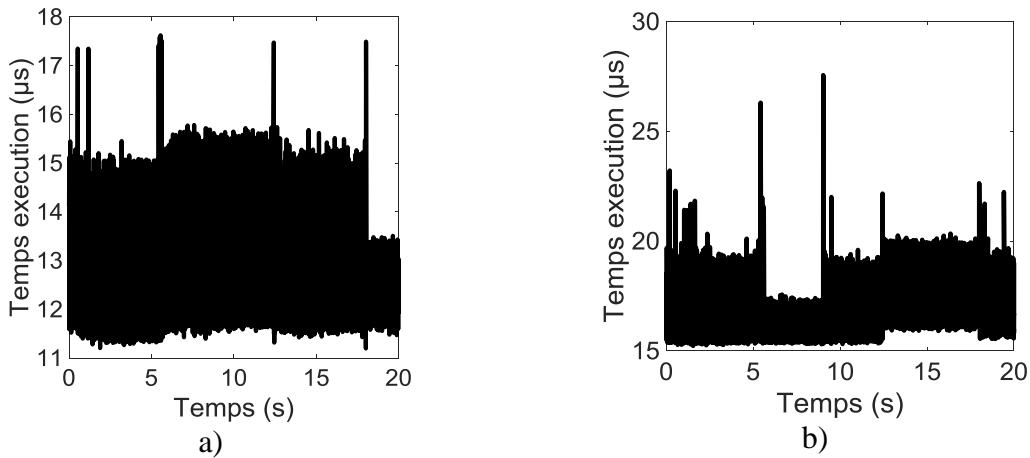

| Figure 6-17: Tension pôle-terre – Modèle 2b sur FPGA .....                                                                  | 135 |

| Figure 6-18: Courant du demi-bras supérieur phase a – Modèle 2b sur FPGA .....                                              | 135 |

| Figure 6-19: Tension pôle-terre du pôle sain – Modèle 2b sur FPGA .....                                                     | 136 |

| Figure 6-20: Temps d'exécution : Modèle 2b sur FPGA (a) ou sur CPU (b).....                                                 | 136 |

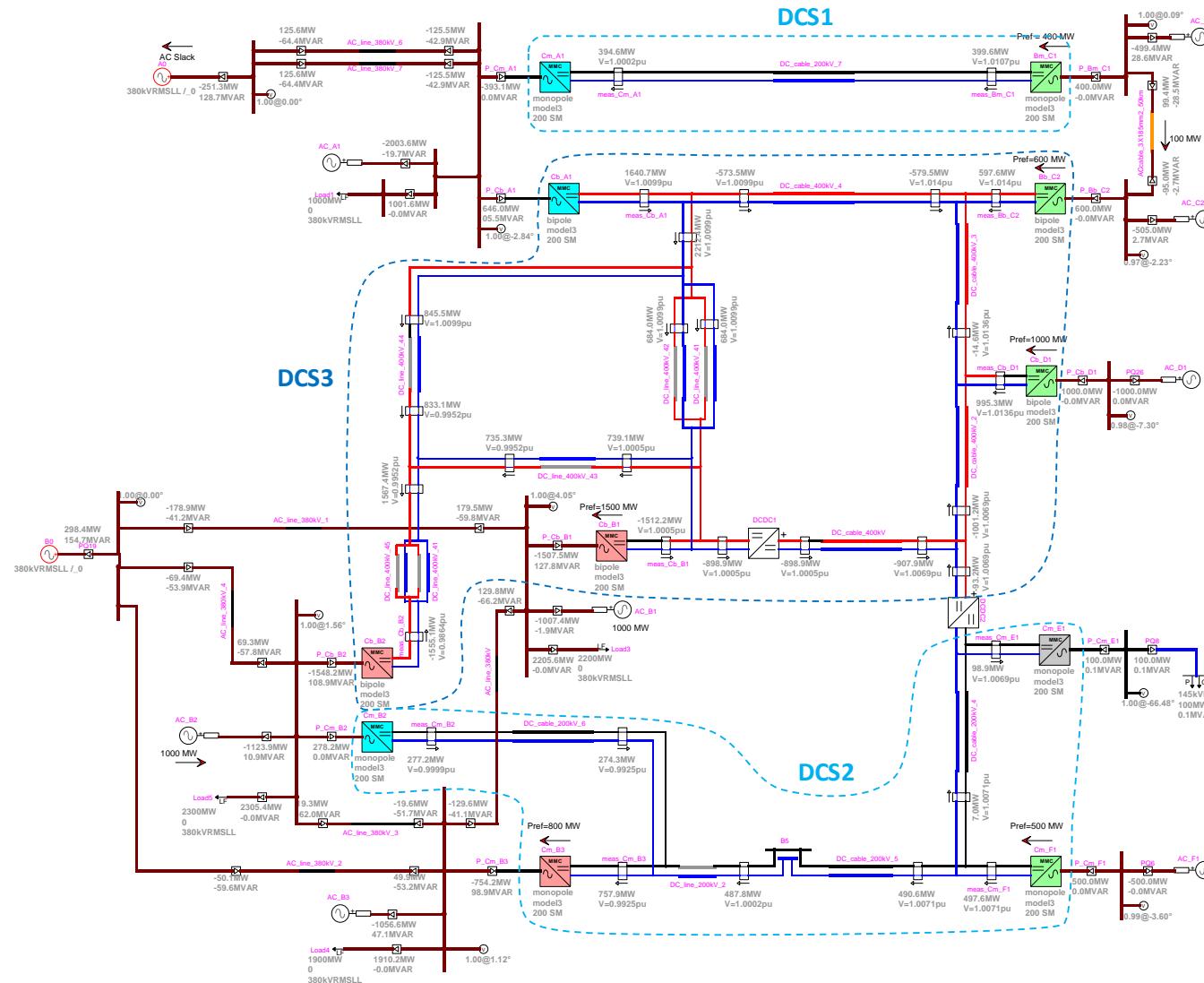

| Figure 7-1: Réseau test CIGRE.....                                                                                          | 139 |

|                                                                                               |     |

|-----------------------------------------------------------------------------------------------|-----|

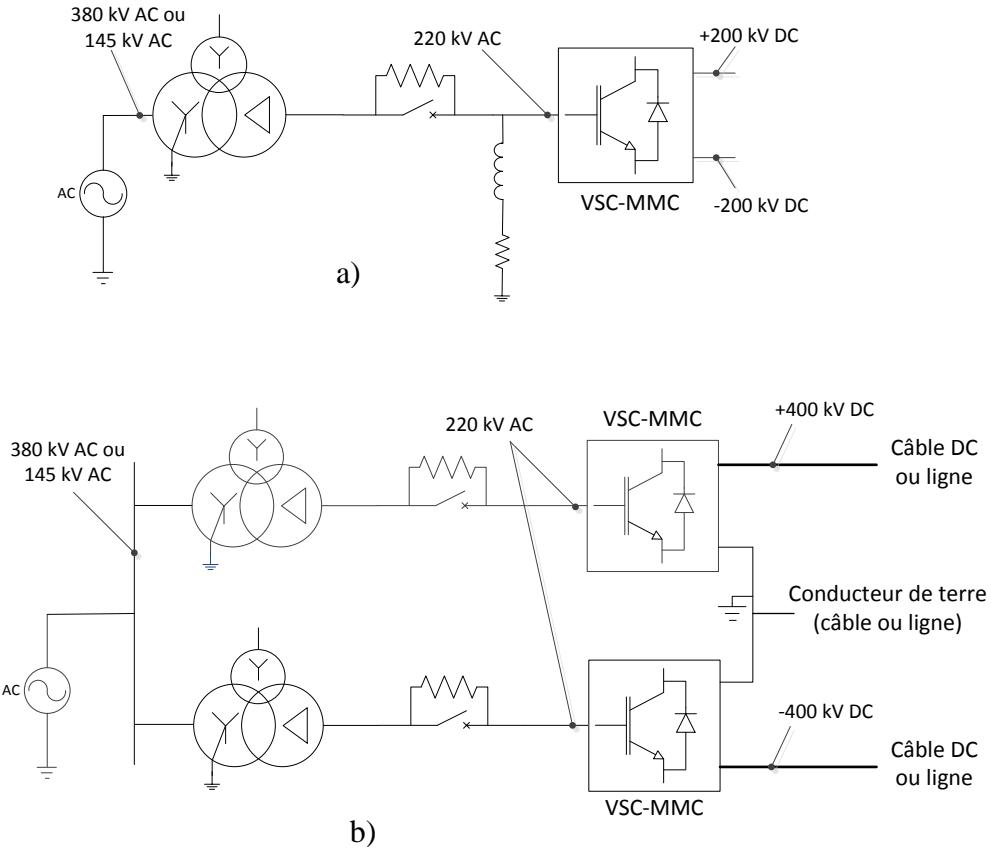

| Figure 7-2: Configuration des stations de conversion : monopolaire (a) et bipolaire (b) ..... | 141 |

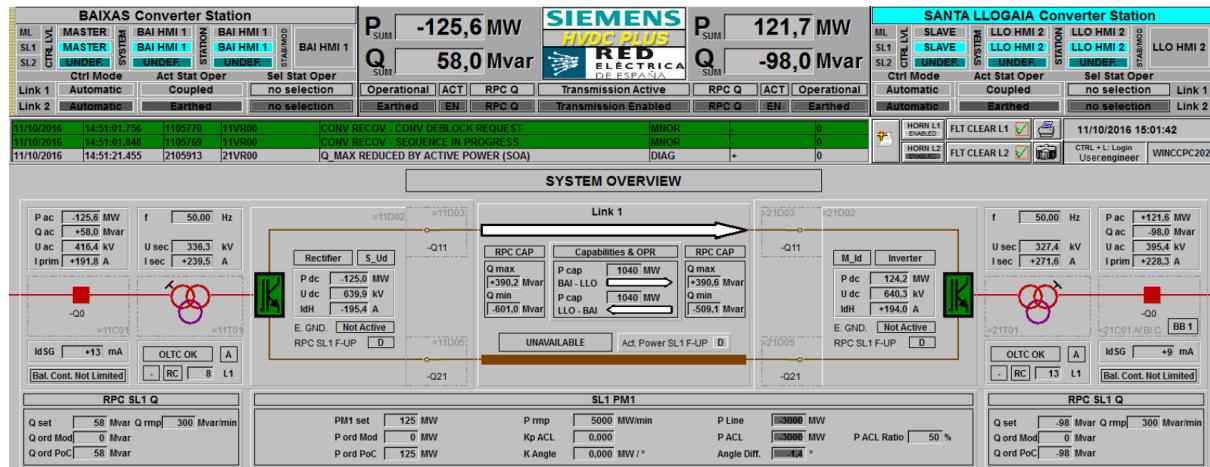

| Figure 7-3: IHM de la liaison France Espagne transitant 1000 MW (Essai réel) .....            | 143 |

| Figure 7-4: Circuit équivalent d'une phase de convertisseur pour la modélisation des pertes   | 144 |

| Figure 7-5: Vue schématique du système de contrôle commande des convertisseurs VSC ..         | 146 |

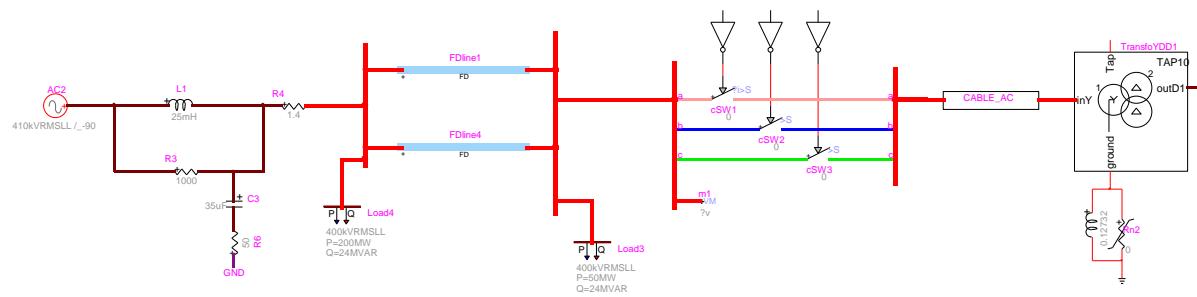

| Figure 7-6: Modélisation dans EMTP du réseau test CIGRE complet .....                         | 147 |

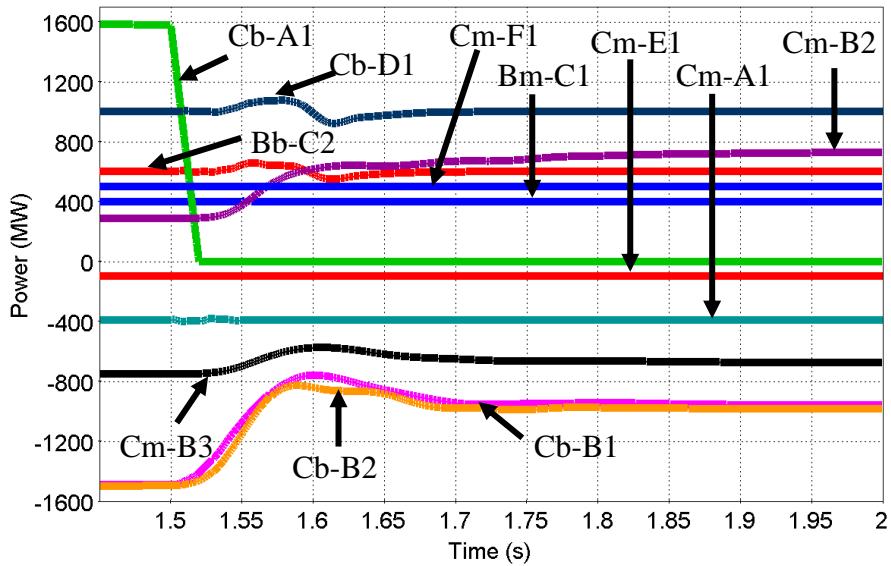

| Figure 7-7: Puissance active des stations de conversion suite au blocage de Cb-A1 .....       | 151 |

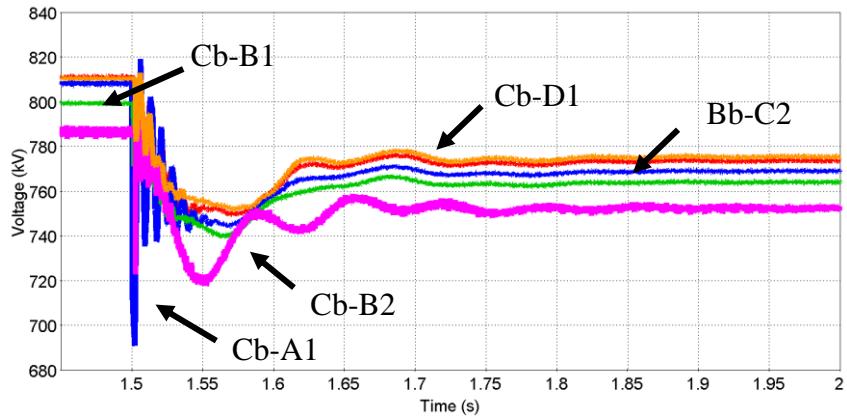

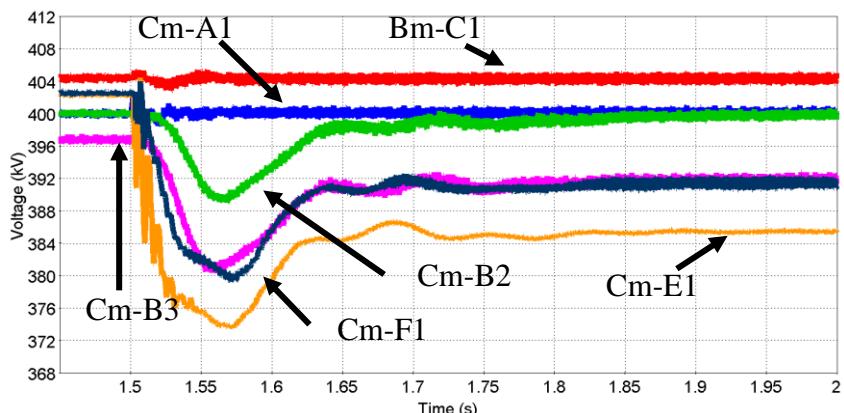

| Figure 7-8: Tension pôle-pôle dans le système DCS3 suite au blocage de Cb-A1.....             | 151 |

| Figure 7-9: Tension pôle-pôle dans les systèmes DCS1 &2 suite au blocage de Cb-A1 .....       | 151 |

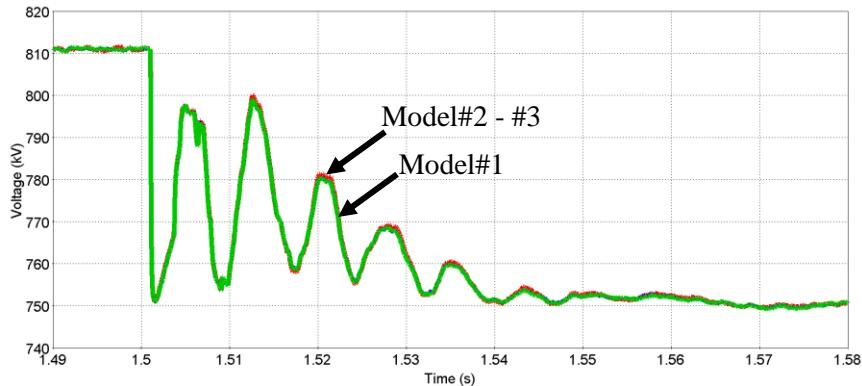

| Figure 7-10: Comparaison Modèles 1, 2 et 3 – tension au convertisseur Bb-C2.....              | 152 |

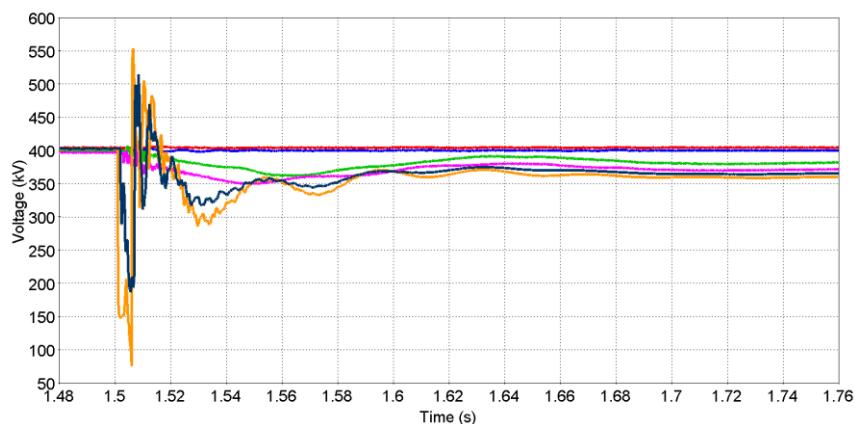

| Figure 7-11: Tensions dans les systèmes DCS1 et DCS2 suite au défaut CC .....                 | 153 |

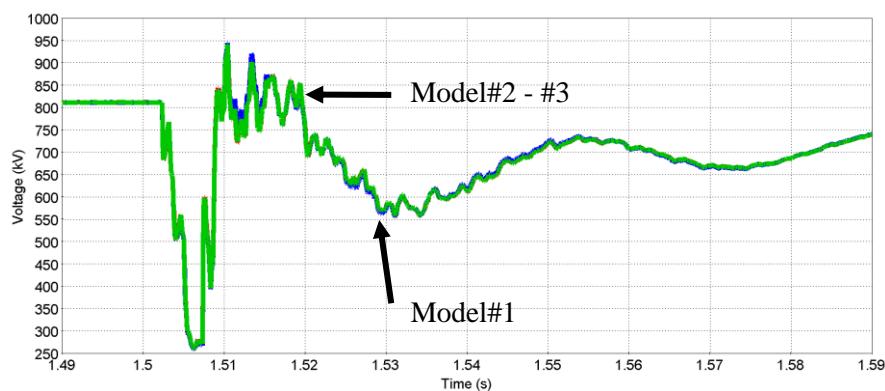

| Figure 7-12: Tension au convertisseur Bb-C2 avec les modèles 1, 2 et 3 suite au défaut CC     | 153 |

| Figure A-1: Schéma de l'étude de mise sous tension du transformateur.....                     | 163 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|                     |                                                                                         |

|---------------------|-----------------------------------------------------------------------------------------|

| BCA                 | Balancing Control Algorithm                                                             |

| $C$                 | Capacité d'un sous-module                                                               |

| $C_{arm}$           | Capacité équivalente d'un demi-bras $C/N$                                               |

| CPU                 | Central Processing Unit                                                                 |

| DSP                 | Digital Signal Processor                                                                |

| EMT                 | ElectroMagnetic Transient                                                               |

| FPGA                | Field-Programmable Gate Array                                                           |

| $g_{1i}$            | Commandes de la gâchette de l'IGBT supérieur du $i^{\text{ième}}$ sous-module           |

| $g_{2i}$            | Commandes de la gâchette de l'IGBT inférieur du $i^{\text{ième}}$ sous-module           |

| HIL                 | Hardware-In the Loop                                                                    |

| IHM                 | Interface Homme Machine                                                                 |

| LCC                 | Line-Commutated Converter                                                               |

| HVDC                | High Voltage Direct Current                                                             |

| $N$                 | Nombre de sous-module par demi-bras                                                     |

| $L_{arm}$           | Inductance d'un demi-bras                                                               |

| $i_{arm}$           | Courant d'un demi-bras                                                                  |

| $i_{arm}^h$         | Courant historique d'un demi-bras                                                       |

| $i_{C_i}$           | Courant du condensateur du $i^{\text{ième}}$ sous-module                                |

| $i_{C_i}^h$         | Courant historique du condensateur du $i^{\text{ième}}$ sous-module                     |

| $i_{C_{tot\ell_j}}$ | Courant du condensateur équivalent du demi-bras inférieur de la $j^{\text{ième}}$ phase |

| $i_{C_{totu_j}}$    | Courant du condensateur équivalent du demi-bras supérieur de la $j^{\text{ième}}$ phase |

| $I_{dc}$            | Courant continu                                                                         |

| $i_{diff_j}$        | Courant différentiel de la $j^{\text{ième}}$ phase                                      |

| IHM                 | Interface Homme Machine (HMI en anglais)                                                |

| $i_{\ell_j}$        | Courant du demi-bras inférieur de la $j^{\text{ième}}$ phase                            |

| $i_{u_j}$           | Courant du demi-bras supérieur de la $j^{\text{ième}}$ phase                            |

| MMC                 | Moduler Multilevel Converter                                                            |

| $n_{u,\ell_j}$      | Nombre de SM qui doit être inséré pour chaque demi-bras                                 |

| PCC                 | Point de raccordement ou « Point of Common Coupling »                                   |

|                      |                                                                                                              |

|----------------------|--------------------------------------------------------------------------------------------------------------|

| PLL                  | Phase-Locked Loop                                                                                            |

| $R_{l_i}$            | Résistance variable ( $R_{ON}$ ou $R_{OFF}$ ) représentant l'IGBT supérieur du $i^{\text{ième}}$ sous-module |

| $R_{2i}$             | Résistance variable ( $R_{ON}$ ou $R_{OFF}$ ) représentant l'IGBT inférieur du $i^{\text{ième}}$ sous-module |

| $R_C$                | Résistance de l'équivalent de Norton du condensateur discrétilisé                                            |

| $R_{OFF}$            | Résistance d'ouverture d'un IGBT/diode                                                                       |

| $R_{ON}$             | Résistance de fermeture d'un IGBT/diode                                                                      |

| $R_{SM_i}$           | Résistance de l'équivalent de Norton du $i^{\text{ième}}$ sous-module                                        |

| $S_i$                | Fonction de commutation du $i^{\text{ième}}$ sous-module (0 ou 1)                                            |

| $s_{\ell_j}$         | Fonction de commutation du demi-bras inférieur de la $j^{\text{ième}}$ phase [0;1]                           |

| $s_{u_j}$            | Fonction de commutation du demi-bras supérieur de la $j^{\text{ième}}$ phase [0;1]                           |

| SM                   | Sous-Module                                                                                                  |

| STATCOM              | STATic Synchronous COMpensator                                                                               |

| STR                  | Simulateur Temps Réel                                                                                        |

| $v_{arm}$            | Tension d'un demi-bras                                                                                       |

| $v_{arm}^h$          | Tension historique d'un demi-bras                                                                            |

| $v_{C_i}$            | Tension du condensateur du $i^{\text{ième}}$ sous-module                                                     |

| $v_{conv_{acj}}$     | Tension alternative de la $j^{\text{ième}}$ phase du convertisseur                                           |

| $\bar{v}_{C_{totj}}$ | Tension moyenne de la somme des condensateurs du demi-bras de la $j^{\text{ième}}$ phase                     |

| $v_{\ell_j}$         | Tension d'un demi-bras inférieur de la $j^{\text{ième}}$ phase                                               |

| $v_{u_j}$            | Tension d'un demi-bras supérieur de la $j^{\text{ième}}$ phase                                               |

| $v_{R_{l_i}}$        | Tension de la résistance représentant l'IGBT/diode supérieur du $i^{\text{ième}}$ sous-module                |

| $v_{R_{2i}}$         | Tension de la résistance représentant l'IGBT/diode inférieur du $i^{\text{ième}}$ sous-module                |

| VSC                  | Voltage Source Converter                                                                                     |

| $v_{SM_i}$           | Tension du $i^{\text{ième}}$ sous-module                                                                     |

| $v_{SM_i}^h$         | Tension historique du $i^{\text{ième}}$ sous-module                                                          |

| $Y_{arm}$            | Admittance d'un demi-bras                                                                                    |

## **LISTE DES ANNEXES**

|          |                                                                                          |     |

|----------|------------------------------------------------------------------------------------------|-----|

| ANNEXE A | - MODÉLISATION À BASE D'IMPÉDANCE FIXE .....                                             | 161 |

| ANNEXE B | - PARAMÈTRES DU CONVERTISSEUR MMC .....                                                  | 162 |

| ANNEXE C | - ÉTUDE DE MISE SOUS TENSION DU TRANSFORMATEUR DE CONVERSION DE LA LIAISON 2 INELFE..... | 163 |

| ANNEXE D | - PARAMÈTRES DES CONVERTISSEURS MMC.....                                                 | 164 |

## CHAPITRE 1 INTRODUCTION

### 1.1 Motivation

Le développement des réseaux de transport d'électricité est actuellement en pleine mutation. La transition énergétique en cours depuis plusieurs années, se concrétise par la fermeture de nombreuses centrales de production au charbon ou au fioul, l'installation massive de centres de production éolien et photovoltaïque et enfin une stagnation, voire une diminution de la consommation d'électricité. Cette tendance est particulièrement visible en Europe. Pour prendre l'exemple de la France, la consommation d'électricité s'établit autour de 475 TWh / an depuis 2011 et une diminution de cette consommation est prévue dans les années à venir. D'autre part la production à partir d'énergies renouvelables est en forte progression. Au 31 décembre 2015, la puissance installée totale d'énergie éolienne était de 10.3 GW, soit presque le double de la puissance installée début 2011. La puissance installée totale d'énergie photovoltaïque est passée de 2.5 GW fin 2011 à 6.2 GW au 31 décembre 2015. Cette transition impacte tous les pays d'Europe si bien que les interconnexions sont de plus en plus soumises aux variations des productions renouvelables.

Cette évolution de la consommation et de la production impose l'installation de systèmes de contrôle des flux de puissance plus sophistiqués que ceux utilisés jusqu'à maintenant. On parle donc de plus en plus d'équipement à base d'électronique de puissance : liaisons à courant continu et compensateur statique de puissance réactive. Les liaisons à courant continu permettent en plus de répondre à la demande sociétale d'enfouir les ouvrages de transport d'électricité. Les réseaux de transport voient donc de plus en plus d'intégration de liaisons HVDC point à point. Le plan de développement du réseau européen ENTSO-E prévoit ainsi plus de 20 000 km de liaisons HVDC en 10 ans [1]. Avec ce développement dans des zones relativement limitées (réseaux nationaux autour de la mer du Nord par exemple : Royaume Uni, France, Belgique, Pays-Bas, Danemark, Allemagne), la notion de réseaux à courant continu commence à se poser. Plusieurs projets de ce type de réseaux sont actuellement en cours d'étude de manière très avancée ou déjà en exploitation [1]-[5].

Depuis maintenant plus de 20 ans, des liaisons VSC (Voltage Source Converter) à base de composants IGBT (Insulated Gate Bipolar Transistor) ou GTO (Gate Turn Off Thyristor) ont commencé à être installées. Elles étaient initialement synonymes d'onduleur autonome à modulation de largeurs d'impulsions et les commutations étaient réalisées à des fréquences de

quelques centaines de Hz (voire quelques kHz pour les IGBT). La difficulté d'assembler des centaines de GTO/IGBT et de diodes en série pour former des valves à très haute tension (plus de 100 kV) et/ou le besoin de maîtriser les pertes par commutation dissipées dans ses convertisseurs ont conduit les constructeurs à privilégier des structures modulaires où de nombreux modules sont connectés en cascade. Les convertisseurs à multi-niveaux (MMC - Modular Multilevel Converter) ont de quelques dizaines de niveaux à plusieurs centaines en fonction de la technologie et du niveau de tension. Ce type de convertisseurs est généralement identifié dans les brochures CIGRE et les normes IEC comme étant à base de "valves de type source de tension contrôlable" ou en anglais "converter with valves acting as controllable voltage source". Il a été proposé pour la première fois dans [6] et dans [7]. Ce type de convertisseur est devenu en quelques années la solution quasi exclusive pour la conversion Courant Alternatif (CA)/ Courant Continu (CC) à très haute tension en Europe. Des solutions à 400 kV voir 500 kV sont en cours de construction comme dans [8].

Afin de planifier l'installation de ces convertisseurs MMC et étudier leur fonctionnement dans des réseaux comportant une forte concentration d'électronique de puissance, il est nécessaire d'avoir des outils de simulation fiables. Les outils de simulation de transitoires électromagnétiques sont habituellement utilisés dans ce cadre car ce sont les outils les plus appropriés pour avoir une représentation détaillée des convertisseurs mais également de leur contrôle commande. En complément de ces outils, l'utilisation de la simulation temps réel associée à des répliques de contrôle commande s'impose de plus en plus comme un outil indispensable dans ce contexte. En effet les modèles de liaisons HVDC dans des outils de simulation non temps réel présentent plusieurs limitations :

- Problèmes de validité dus à la complexité des vrais systèmes et des matériels hétérogènes utilisés (CPU, FPGA, DSP...),

- Quasi-impossibilité de maintenir sur plusieurs dizaines d'années ces modèles à cause des évolutions informatiques (systèmes d'exploitations, versions logiciels) et des évolutions du contrôle commande sur site.

C'est pour ces raisons que des laboratoires de simulation temps réel accueillant des répliques de contrôle commande existants ou en cours de développement dans la plupart des zones intégrant des liaisons HVDC de manière massive. L'objectif est, pour certaines études spécifiques, de ne plus modéliser les systèmes de contrôle commande mais d'avoir les systèmes réels (avec les mêmes versions de logiciels que sur site) raccordés à des modèles numériques de convertisseurs et de réseaux. Ces investissements conséquents seraient inutiles si les modèles

temps réel étaient très approximatifs. La plus-value d'avoir les véritables systèmes de contrôle commande serait perdue. C'est pourquoi un soin particulier doit être apporté à la validation de ces modèles et à leur performance en temps réel.

Une contribution majeure sur la modélisation des convertisseurs MMC dans les outils de type EMT a été réalisée dans [9]. Elle a permis de développer des modèles de convertisseurs et des contrôles commande génériques. Les modèles MMC développés dans ce travail ont été classés en 4 groupes :

- Modèle 1 : représentation de chaque sous-module avec une modélisation détaillée de chaque composant IGBT/diode de manière individuelle en allant jusqu'à la prise en compte de leur caractéristique non-linéaire. C'est le modèle le plus détaillé dans un outil de type EMT.

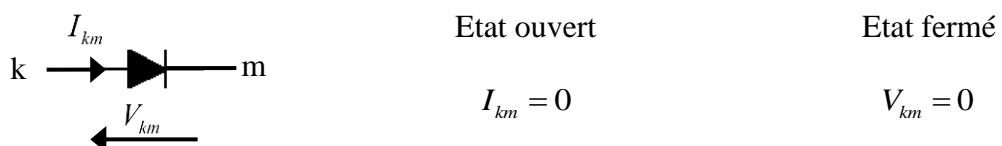

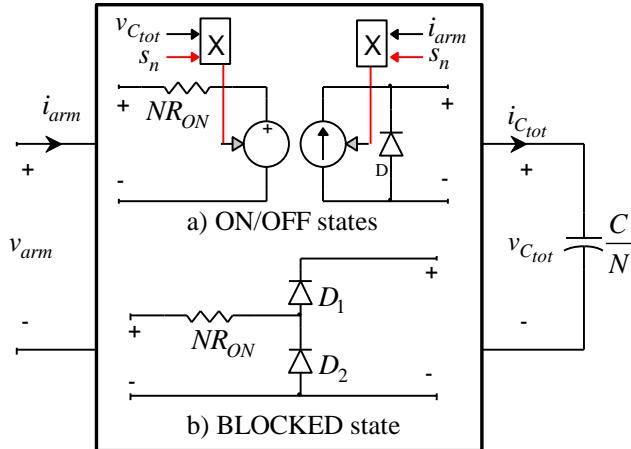

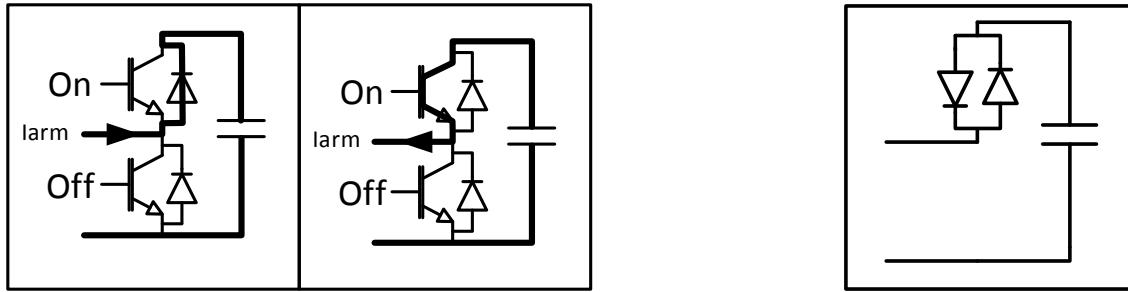

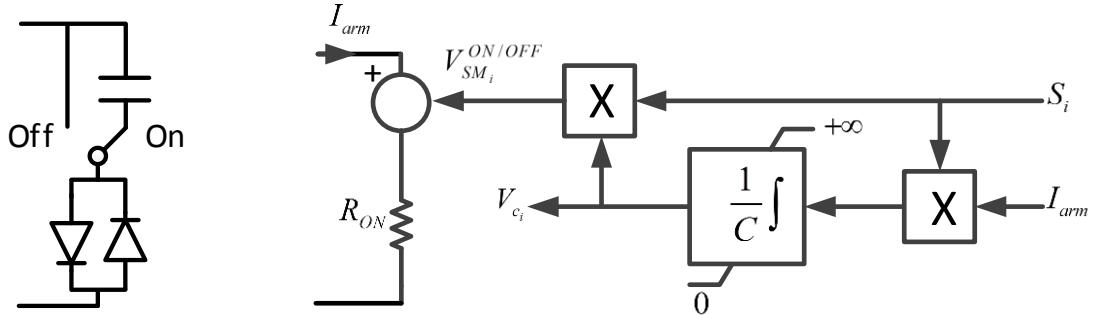

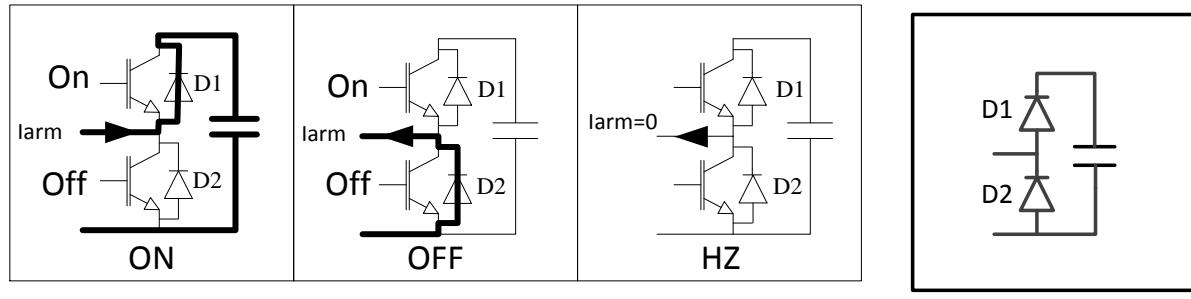

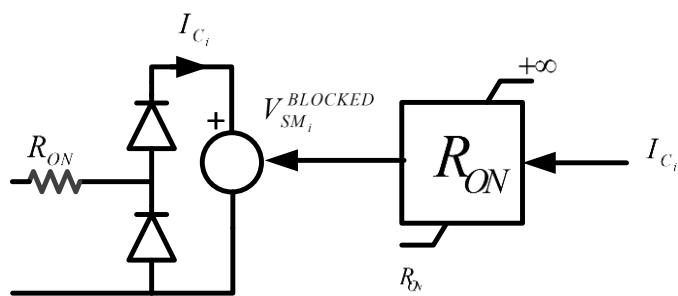

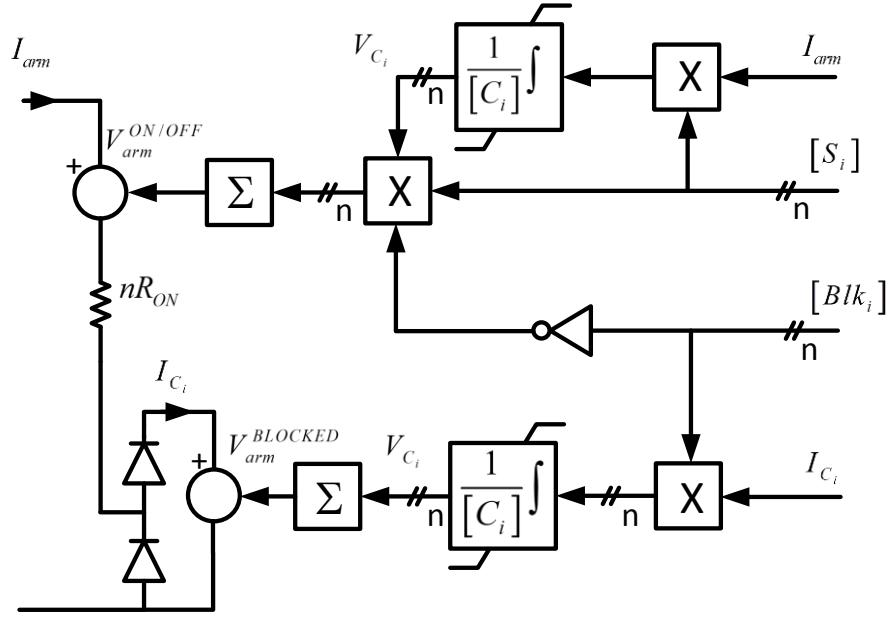

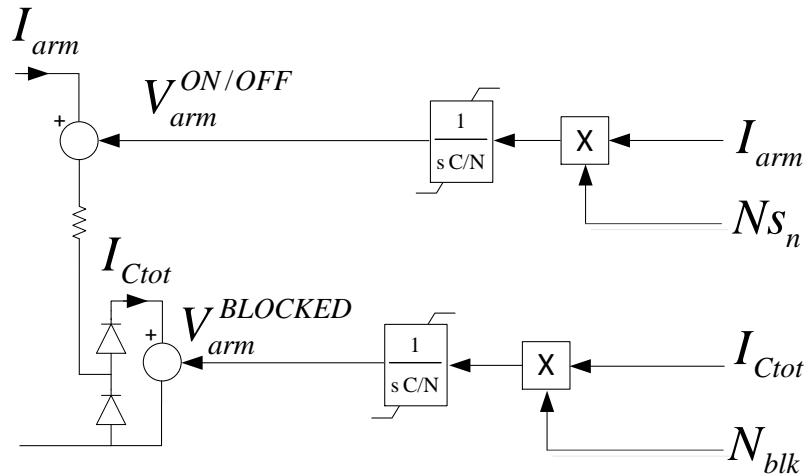

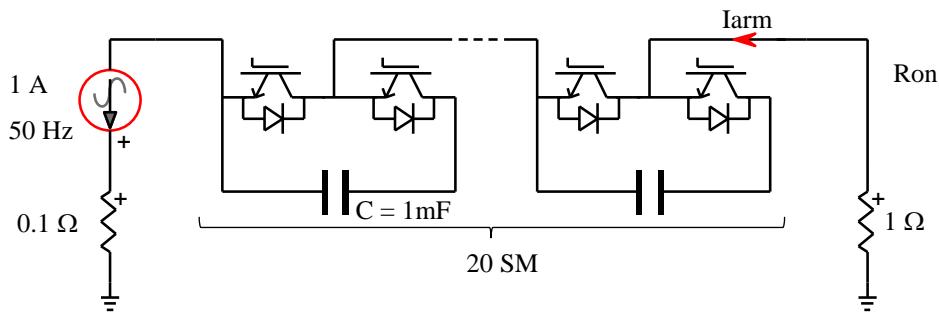

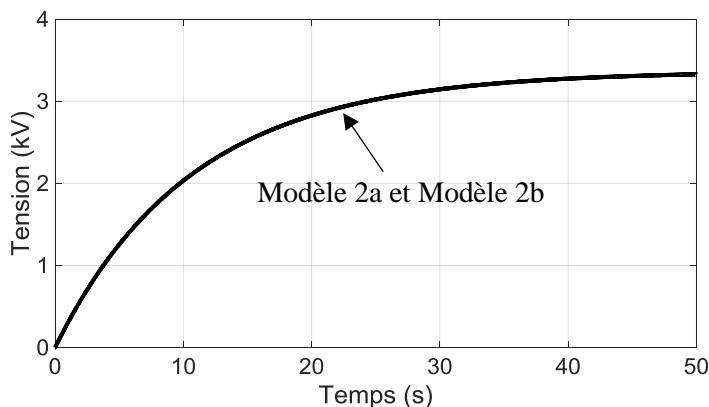

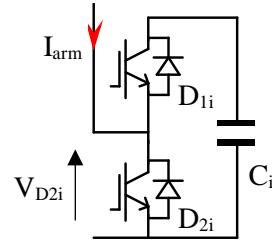

- Modèle 2 : représentation de chaque sous-module mais les IGBT/diode sont simplifiés sous la forme de résistances  $R_{ON}$  /  $R_{OFF}$ . Ce modèle permet de réduire fortement le nombre de nœuds électriques et donc le temps de calcul. Deux types de Modèle 2 existent : le Modèle 2a présente une interface avec le reste du convertisseur sous la forme d'équivalent de Norton alors que le Modèle 2b présente une interface sous la forme de deux sources de tension et des diodes.

- Modèle 3 : représentation "agrégée" de chaque demi-bras en prenant pour hypothèse que les tensions des sous-modules dans un demi-bras sont identiques. Ce modèle permet de représenter le mode bloqué et donne des résultats précis pour des convertisseurs de plusieurs centaines de niveaux. Ce modèle permet surtout d'améliorer les performances de calcul.

- Modèle 4 : Modèle moyen de convertisseur. C'est le modèle le moins précis mais le plus rapide. Il donne des résultats satisfaisants pour des perturbations de faible amplitude ou les études électromécaniques côté CA mais n'est pas adapté à l'étude des perturbations côté courant continu.

En plus de cette thèse, de nombreux travaux ont été réalisés sur la modélisation des MMC ces 5 dernières années [10]-[13], mais ces travaux restaient théoriques et n'ont pas été appliqués à des contextes industriels réels. Même les solutions de simulation temps réel utilisées par les constructeurs pour tester les systèmes de contrôle commande [14] sont généralement basées sur des approches de modélisation à admittance constante [15]-[17]. Cette approche conduit à des erreurs qui ne sont pas documentées dans la littérature car difficilement mises en lumière avec des cas simples.

Le travail réalisé dans cette thèse clarifie les types de modèles nécessaires à la réalisation des études VSC de la planification à la maintenance des installations sur site. Cette clarification manque encore aujourd'hui dans les documents normatifs ou prénormatifs (CIGRE, IEEE).

Cette thèse permet de fournir des cas d'application dans un contexte industriel pour montrer les limites de certaines modélisations. Elle permet également de mettre en lumière certaines limitations des modèles MMC détaillés et simplifiés.

De nombreux travaux ont été réalisés pour valider des approches de modélisation à l'aide de modèles détaillés comme dans [9]. La validation de ces modèles à l'aide de mesures réalisées sur des convertisseurs de forte puissance manquaient ainsi dans la littérature. Cette thèse apporte une contribution dans ce domaine en utilisant des mesures réalisées sur des convertisseurs de 1050 MVA.

Les solutions pour interfaçer des modèles MMC à des systèmes de contrôle commande réels sont très peu documentés dans la littérature car ce sont souvent des activités réservées aux constructeurs ou aux fabricants de simulateurs. Cette thèse contribue au développement des interfaçages entre simulateurs temps réel et systèmes de contrôle commande physiques. Elle contribue également à la validation de la performance et de la précision de la plateforme de simulation complète à l'aide de mesure sur site.

Le travail présenté en [9], avait identifié des sujets de recherche qui méritaient d'être approfondis :

- La réalisation d'un MMC sur FPGA incluant l'état bloqué.

- L'utilisation de MMC dans des réseaux CC multi-terminaux.

Le présent travail de thèse a répondu à la réalisation d'un modèle de MMC sur FPGA incluant l'état bloqué. Deux modèles ayant ces caractéristiques ont été intégrés à une plateforme de simulation temps réel et ont été validés.

Des travaux sur les réseaux à courant continu ont aussi été réalisés. Au-delà des projets de liaisons point-à-point, des projets de réseaux à courant continu voient maintenant le jour en Asie et en Europe [3]. Certains sont même déjà opérationnels [4]-[5]. Poussés par l'intégration d'énergies renouvelables (essentiellement les éoliennes offshore ou les hydroliennes) ces réseaux sont basés sur l'utilisation de convertisseurs MMC. Afin de tester, valider et comparer des stratégies de contrôle commande et de protections adaptées à ces nouveaux réseaux, il était nécessaire de développer des réseaux tests (ou benchmark). Cette thèse a contribué de manière

significative à la conception du réseau HVDC CIGRE qui est maintenant utilisé dans de nombreux groupes de travail et sert de base à des travaux de recherche dans ce domaine.

L'interconnexion HVDC France-Espagne a été mise en service en 2015 [18]. De nombreuses données de cette liaison étaient accessibles lors de la réalisation de cette thèse. Parmi celles-ci on peut citer : des mesures sur site, les caractéristiques des équipements, les stratégies de contrôle commande et de protections, l'analyse des problématiques d'essai des systèmes contrôle commande avec des simulateurs temps réel.

## 1.2 Objectifs de la thèse

L'objectif de cette thèse est de :

- Clarifier les modèles nécessaires aux différentes étapes d'un projet industriel de type VSC.

- Clarifier les erreurs induites par une modélisation des MMC à l'aide d'approche à admittance constante.

- Optimiser la précision et le temps de calcul des modèles MMC utilisés dans les outils de simulation de type EMT.

- Proposer et appliquer des solutions pour valider les modèles MMC dans des simulations temps réel.

- Implémenter des solutions techniques pour interfaçer des modèles MMC temps réel avec des systèmes de contrôle commande réels.

- Valider les modèles de MMC avec des mesures sur site.

- Intégrer à une plateforme de simulation temps réel des modèles MMC allant jusqu'à plusieurs centaines de niveaux sur FPGA incluant le mode bloqué

- Contribuer à la conception d'un réseau à courant continu test et analyser son comportement.

Le plan de la thèse se présente comme suit :

**CHAPITRE 2 :** Technologie HVDC et simulations de type EMT – revue de la littérature

**CHAPITRE 3 :** Modélisation des liaisons VSC dans les outils de type EMT pour des applications industrielles

**CHAPITRE 4 :** Implémentation des modèles de liaisons VSC dans des simulateurs temps réel

**CHAPITRE 5 :** Implémentation et validation des modèles de liaisons VSC appliquées à la liaison France Espagne

**CHAPITRE 6 :** Utilisation de modèles détaillés MMC dans des simulations temps réel

**CHAPITRE 7 :** Réseaux HVDC – justifications du benchmark CIGRE et résultats de cas tests

### 1.3 Contributions de la thèse

Les contributions principales de cette thèse sont :

- Description des modèles nécessaires aux différentes étapes d'un projet VSC.

- Mise en évidence des erreurs induites par une modélisation basée sur des approches à admittance constante.

- Optimisation de la précision du Modèle 2a.

- Optimisation des équations du Modèle 2a pour l'implémentation dans des outils de simulation temps réel en prenant en compte le mode bloqué.

- Proposition et développement d'un Modèle 2b détaillé pour la simulation temps réel.

- Clarifications sur le domaine de validité des Modèles 2 et 3.

- Méthodologie de validation des modèles MMC temps réel.

- Interfaçage d'un modèle MMC temps réel à un contrôle commande réel.

- Validation à l'aide de mesures sur site de modèles MMC temps réel pour différents modes de fonctionnement.

- Intégration et validation sur une plateforme temps réel d'un Modèle 2a et Modèle 2b détaillé de MMC incluant le mode bloqué et implanté sur FPGA.

- Contribution à la conception du réseau HVDC CIGRE : détermination des caractéristiques des équipements, modélisation et études dans des outils de type EMT.

## 1.4 Liste des publications issues de ce travail

### 1.4.1 Chapitre de brochure

- **S. Dennetière**, J. Jardini, J. C. G. Alonso, H. Saad, "Chapter 6 - DC Grid test systems description", in *CIGRE Technical Brochure 604*, December 2014.

### 1.4.2 Articles de journal

- **S. Dennetière**, H. Saad, B. Clerc, J. Mahseredjian, "Setup and performances of the real-time simulation platform connected to the INELFE control system", *Electric Power Systems Research*, Volume 138, September 2016, Pages 180-187, ISSN 0378-7796.

- T. K. Vrana, **S. Dennetière**, Y. Yang, J. Jardini, D. Jovcic, H. Saad, "The CIGRE DC Grid Test System", *ELECTRA brochure n°270*, October 2013.

### 1.4.3 Articles de conférence

- **S. Dennetière**, S. Nguefeu, H. Saad, J. Mahseredjian, "Modeling of Modular Multilevel Converters for the France-Spain link", *Proceedings of the International Conference on Power Systems Transients (IPST'13) in Vancouver*, Canada July 18-20, 2013

- **S. Dennetière**, H. Saad, A. Naud, P. Honda, "Transients on DC cables connected to VSC converters", *Proceedings of the Jicable'15 Conference in Versailles*, France June 21-25, 2015

- **S. Dennetière**, O. Saad, A. El. Akoum, J. Mahseredjian, H. Motoyama, "Involvement of electric utilities in the development of EMT simulation tools", *CIGRE Session 2014*, August 2014, Paris.

- **S. Dennetière**, H. Saad, B. Clerc, E. Ghahremani, W. Li and J. Bélanger, "Validation of a MMC model in a real-time simulation platform for industrial HIL tests," *2015 IEEE Power & Energy Society General Meeting*, Denver, CO, 2015, pp. 1-5.

- **S. Dennetière**, H. Saad, B. Clerc, "Setup and performances of the real-time simulation platform connected to the INELFE control system", *Proceedings of the International Conference on Power Systems Transients (IPST'15) in Cavtat, Croatia*, June 15-18, 2015.

- **S. Den netière**, H. Saad, "EMT simulation of the CIGRE B4 DC Grid test system", *Proceedings of the CIGRE Canada conference*, Toronto, Canada, 22-24 september, 2014.

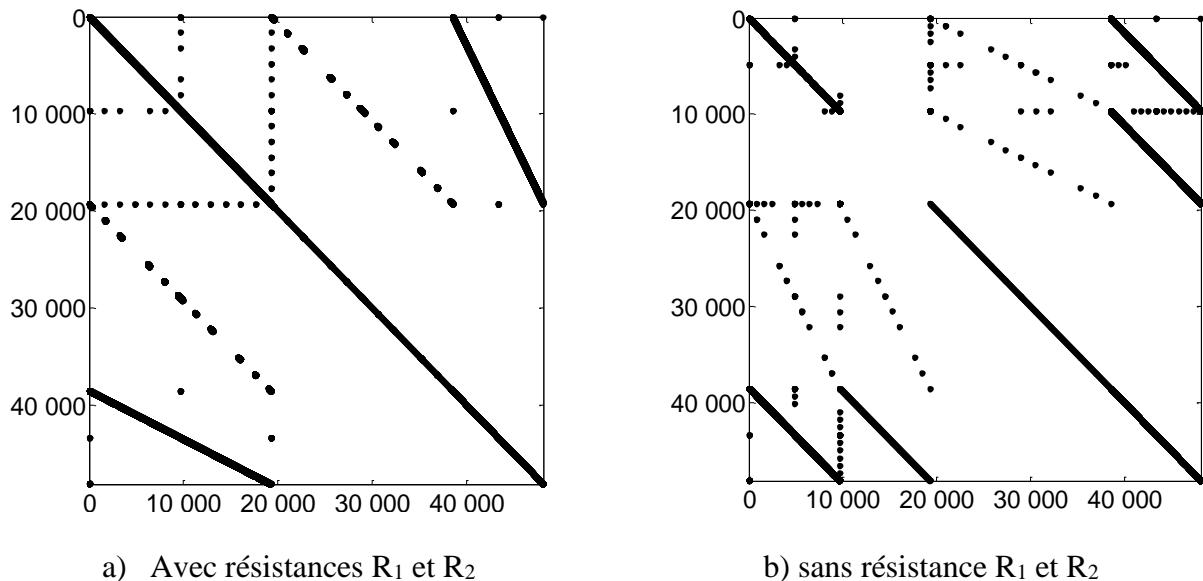

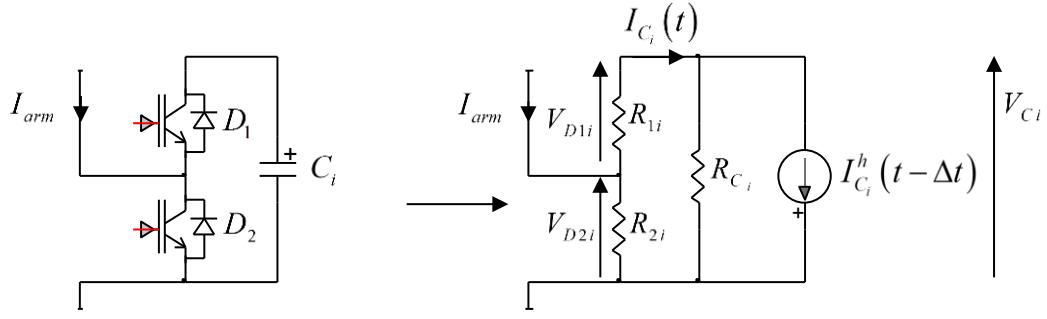

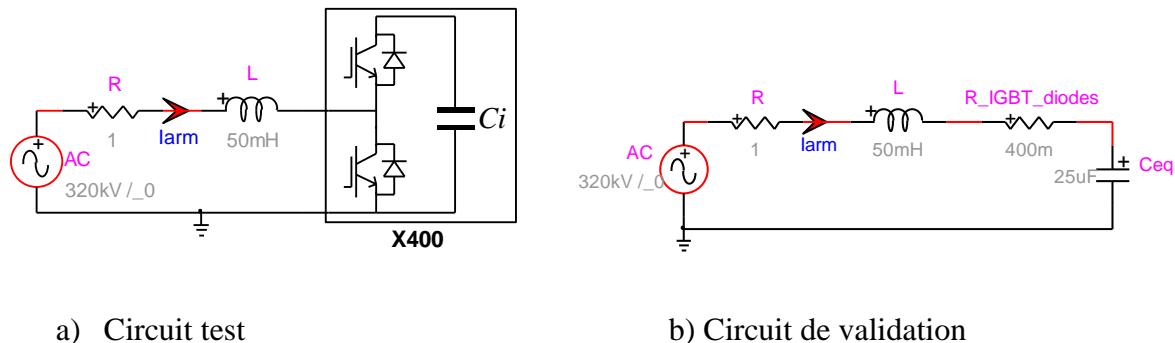

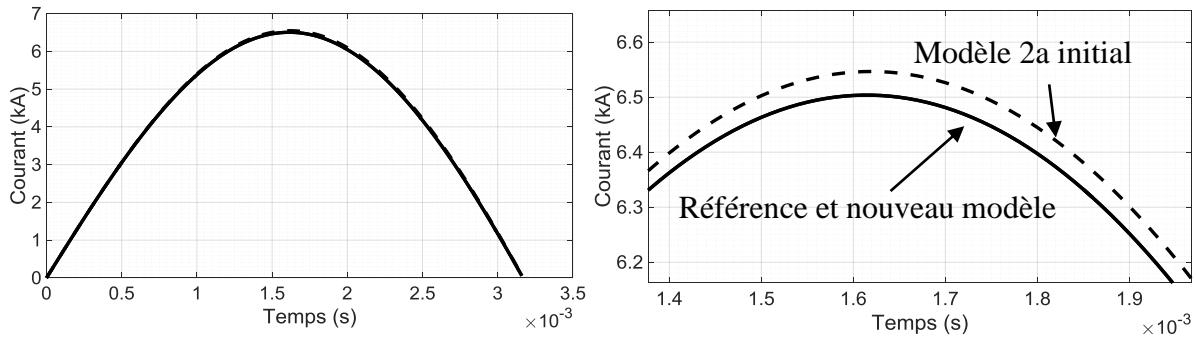

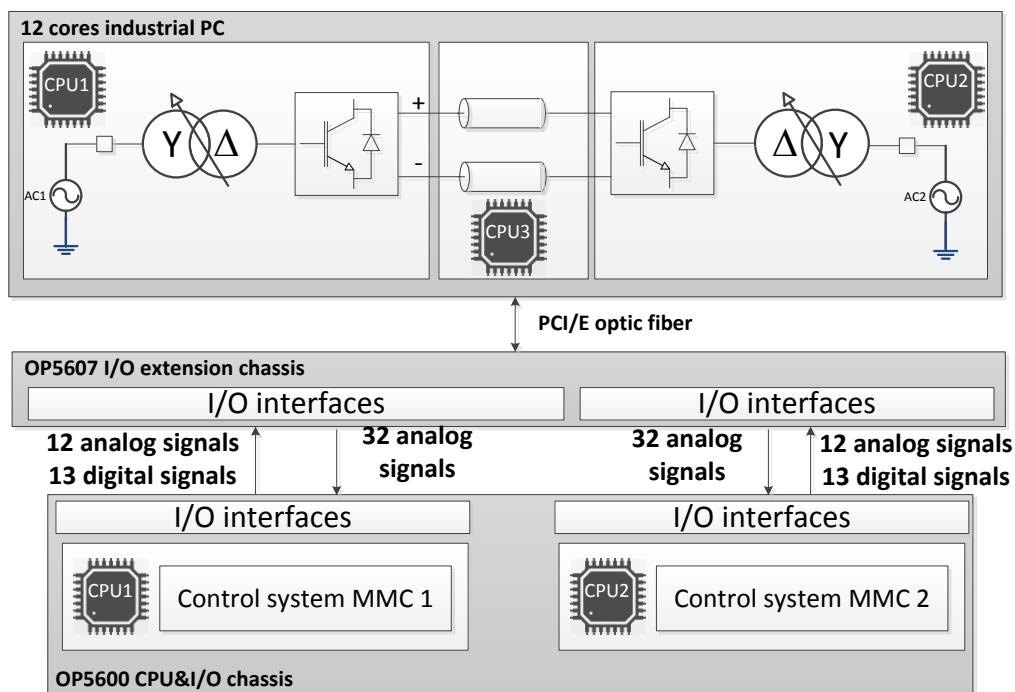

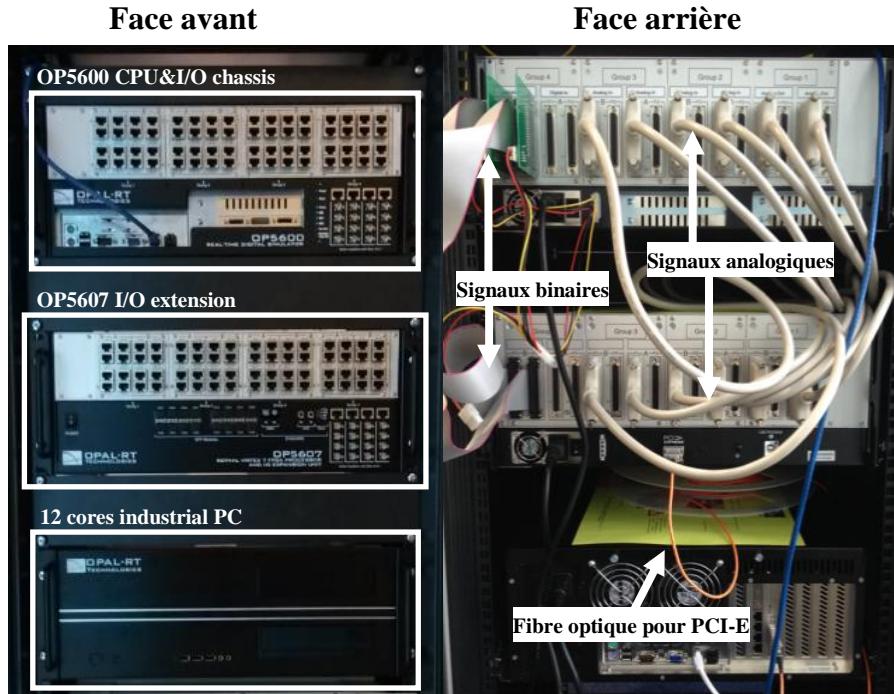

## CHAPITRE 2 TECHNOLOGIES HVDC ET SIMULATIONS DE TYPE EMT – REVUE DE LA LITTERATURE