|                   |                                                                                                                                                                                                                                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Titre:</b>     | Utilisation de la reconfiguration dynamique des FPGA pour le contrôle précis et exact des délais dans les convertisseurs temps à numérique                                                                                                                                                                                       |

| <b>Auteur:</b>    | Marc-André Daigneault                                                                                                                                                                                                                                                                                                            |

| <b>Date:</b>      | 2009                                                                                                                                                                                                                                                                                                                             |

| <b>Type:</b>      | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                                                                        |

| <b>Référence:</b> | Daigneault, M.-A. (2009). Utilisation de la reconfiguration dynamique des FPGA pour le contrôle précis et exact des délais dans les convertisseurs temps à numérique [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/239/">https://publications.polymtl.ca/239/</a> |

| Citation:         |                                                                                                                                                                                                                                                                                                                                  |

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/239/>

PolyPublie URL:

**Directeurs de recherche:** Jean Pierre David

Advisors:

**Programme:** Génie Électrique

Program:

UNIVERSITÉ DE MONTRÉAL

UTILISATION DE LA RECONFIGURATION DYNAMIQUE DES FPGA POUR

LE CONTRÔLE PRÉCIS ET EXACT DES DÉLAIS DANS LES

CONVERTISSEURS TEMPS À NUMÉRIQUE

MARC-ANDRÉ DAIGNEAULT

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE

MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2009

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

UTILISATION DE LA RECONFIGURATION DYNAMIQUE DES FPGA POUR

LE CONTRÔLE PRÉCIS ET EXACT DES DÉLAIS DANS LES

CONVERTISSEURS TEMPS À NUMÉRIQUE

présenté par : M. DAIGNEAULT Marc-André

en vue de l'obtention du diplôme de : Maîtrise ès Sciences Appliquées

a été dûment accepté par le jury constitué de :

M. SAVARIA Yvon, Ph.D., président.

M. DAVID Jean Pierre, Ph.D., membre et directeur de recherche.

M. BOIS Guy, Ph.D., membre.

*« Le temps nous égarre, le temps nous étirent,

le temps nous est gare, le temps nous est train. »,

Jacques Prévert.*

# Remerciements

J'aimerais profiter de cette occasion pour remercier mon directeur de recherche, le professeur Jean Pierre David, de m'avoir permis de réaliser mes travaux de recherches sous sa supervision. Bien plus qu'un directeur, de par sa rigueur, sa créativité, son ardeur au travail, et ses conseils, le professeur David à été pour moi une grande source d'inspiration. Au cours de cette grande aventure qu'a été la maîtrise en sciences appliquées où nous avons appris à nous connaître, j'ai eu la chance de découvrir qu'au delà du chercheur remarquable se trouve une personne d'une grande sagesse, bonté, et compréhensivité.

Je me souviendrai toujours à mes premiers pas dans son équipe, en marchant dans un couloir, lorsqu'un de ces anciens étudiants lui avait dit : « Ouin, il est pas pire ton nouvel étudiant ! », Jean Pierre avait répondu précipitamment, sur un ton d'humour qui me semblait mal cacher un léger embarras : « *Shhhhhh*, il ne faut pas lui dire ». Bien qu'anodin, ce geste témoignait sans équivoque de son désir d'obtenir le meilleur de chacun. Il n'y en aurait pas de faciles !

J'aimerais également profiter de l'occasion pour remercier les professeurs du Groupe de Recherche en Microélectronique et Microsystèmes (GR2M) Pierre Langlois, Guy Bois, et Yvon Savaria, pour la qualité et la pertinence de leurs enseignements au niveau des études supérieures en génie électrique et informatique. À ce titre, j'aimerais tout particulièrement souligner l'initiative du professeur Langlois d'initier les étudiants à l'analyse, la rédaction, et la présentation d'articles scientifiques dans le domaine des processeurs configurables.

# Résumé

La mesure d’intervalles de temps est importante dans différents domaines d’applications scientifiques. Un convertisseur numérique de temps (TDC) est un circuit électronique permettant de mesurer des intervalles de temps avec des résolutions de l’ordre de la picoseconde. Jusqu’à la dernière décennie, ces circuits étaient implémentés exclusivement sous forme de circuits dédiés (ASIC), mais depuis, plusieurs implantations sur circuits programmables (FPGA) ont été proposées. Bien qu’à ce jour de telles implantations accusent toujours des performances inférieures, il existe un intérêt réel pour réduire l’importance de cet écart. En effet, le progrès fulgurant de la technologie FPGA, en termes de densité logique et de fréquence d’opération, en fait aujourd’hui un candidat de choix pour l’implémentation de nombreux circuits et systèmes. Au delà du grand degré d’intégration qu’elle permet d’obtenir, ce type d’implémentation se démarque des circuits dédiés en ce qu’elle permet à la fois des temps de développement et des coûts non-récurrents nettement moins importants. C’est donc dans ce contexte que ce travail se penche sur l’implémentation FPGA d’un convertisseur numérique de temps.

Alors que les implantations de TDC sur circuits dédiés permettent d’obtenir des résolutions avoisinant la picoseconde, les implantations FPGA les plus récentes sont limitées à quelques dizaines de picoseconds. Puisque l’implémentation d’un TDC est intimement liée à la notion de délai, les FPGAs sont handicapés d’une part par l’irrégularité des délais d’interconnexions programmables générées par les outils de synthèse, et d’autre part par des délais d’interconnexions plus importants. C’est ainsi que les implantations FPGA offrant les meilleures performances dans la littérature reposent sur une architecture permettant d’exploiter la présence des structures d’interconnexions dédiés, telle la chaîne de retenue rapide. En effet, ces structures d’interconnexions dédiées offrent à la fois des délais réduits et une régularité accrue. Toutefois, la résolution atteignable avec cette architecture est limitée par les délais minimaux du circuit, et ces derniers sont sensiblement plus importants sur un FPGA que sur un circuit dédié. Néanmoins, cette architecture bénéficie directement des nouvelles générations de FPGA qui sont produites avec des procédés de fabrication permettant d’obtenir des délais minimaux réduits.

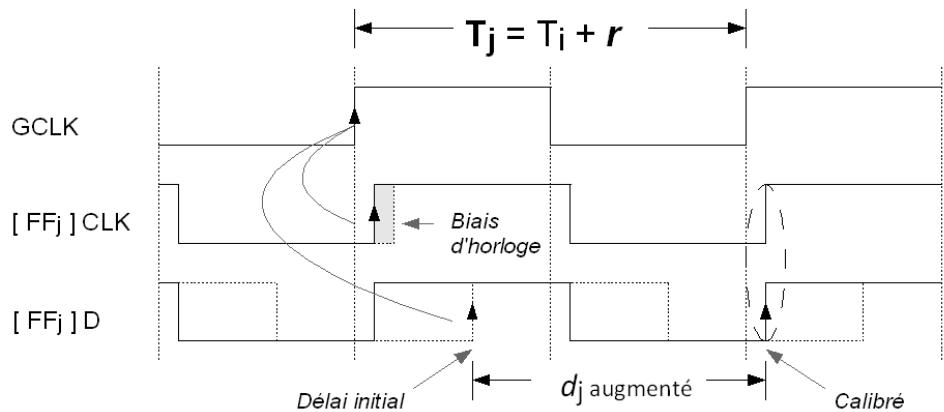

Afin de palier à cette limitation imposée par les délais minimaux disponibles, cet ouvrage propose une approche basée sur l'ajustement fin et précis des délais. L'originalité de l'approche proposée réside en ce qu'elle tire profit de deux caractéristiques propres aux FPGA : la richesse du système d'interconnexions programmables, conjointement avec la possibilité de reconfigurer dynamiquement le circuit. En effet la reconfiguration dynamique, supportée par certains FPGA, permet de reconfigurer partiellement le circuit lors de son opération. Ainsi, puisqu'il existe un nombre important de chemins possibles entre deux points du circuit, la reconfiguration dynamique du système d'interconnexions programmables permet potentiellement d'ajuster le délai entre ceux-ci avec une résolution autrement inaccessible. C'est ainsi que nos résultats font état d'une ligne à délai programmable ajustable avec une résolution de 1ps sur une plage de plus de 2,5ns.

Sur la base de ces lignes à délais programmables à fine résolution, une nouvelle architecture de TDC est proposée. Cette architecture se caractérise par l'utilisation de plusieurs lignes à délais en parallèles, et permet d'obtenir une résolution non pas limitée par les délais minimaux du circuit, mais plutôt par la différence minimale d'ajustement entre deux lignes à délais. Ainsi, au moyen d'une telle architecture, il devrait être possible de produire un TDC offrant des résolutions inférieures à celles obtenues à l'état de l'art. Néanmoins, l'ajustement fin des délais étant à lui seul insuffisant, une méthode de calibration permettant un ajustement précis de ces derniers est également proposée. Les délais d'un circuit sont affectés par les variations de températures, ainsi que les variations dues au procédé de fabrication de la puce. Afin de rendre possible un ajustement précis des délais, le processus de calibration proposé tient compte de ces deux facteurs, en plus de tenir compte du biais de l'horloge. En appliquant la méthodologie proposée, un TDC avec une résolution de 50ps et une précision de 48ps a été obtenue, et les résultats montrent que des résolutions aussi faibles que 10ps peuvent être atteintes. A notre connaissance, à ce jour cette résolution correspond à la plus fine valeur rapportée dans la littérature pour une implémentation sur FPGA.

L'approche basée sur l'ajustement fin et précis des délais est également appliquée à une architecture préexistante de TDC utilisant la méthode de Vernier avec deux oscillateurs. Avec cette architecture, la résolution atteignable correspond en fait à

la différence de périodes entre deux oscillateurs démarrables. Notre méthode permettant d'ajuster précisément la période d'un oscillateur en anneau, l'application de l'approche proposée à cette architecture devrait permettre d'atteindre des résolutions plus fines que celles rapportées dans la littérature. Effectivement, nos résultats font états de résolutions inférieures à 5ps. Toutefois, étant donnée l'instabilité des oscillateurs, on observe que la précision obtenue à de telles résolutions n'est pas meilleure que 100ps. Néanmoins, des résolutions de l'ordre de 25ps sont obtenues avec des précisions équivalentes avec cette implémentation. Comparativement aux implémentations statiques proposées dans la littérature, notre approche utilisant la reconfiguration dynamique apporte une contribution intéressante en permettant de tenir compte des variations de température, aussi bien que des variations dues au procédé de fabrication.

# Abstract

Time interval measurement is important in various scientific and engineering applications. A Time-to-Digital Converter (TDC) is an integrated circuit allowing measurement of time intervals with resolutions and precisions down to a picosecond. Until the last decade or so, these circuits were implemented exclusively as application specific integrated circuits (ASIC), but since then, various implementations targeting field-programmable gate arrays (FPGA) have been proposed. While these implementations still deliver reduced performances in terms of resolution and precision, there is a growing interest within the scientific community to reduce this gap. Indeed, with the dazzling progress of the FPGA technology over the past decade, both in terms of logic density and operation frequency, it is becoming a implementation target of choice for an ever growing range of circuit and systems. Two key benefits from such implementations are considerably reduced development times and non-recurring costs. It is therefore in this context that this work is focused on the FPGA implementation of time-to-digital converters.

While ASIC implementations of TDC can enable resolutions neighbouring a single picosecond, most recent FPGA implementations are still limited to a few tens of picoseconds. As the implementation of a TDC is closely related to the notion of delay, FPGAs are handicapped both by the irregularity of interconnection delays, and increased minimal delays. Therefore, to this day, the most successful FPGA implementations that have been proposed in the literature rely on architectures allowing to take advantage of dedicated interconnection structures, such as the carry-chain used in arithmetic circuits. Indeed, these dedicated interconnection structures provide both reduced delays and increased interconnection delay regularity. However, the resolution achievable with such architecture is limited by the minimal delays available on the circuit, which are substantially more important on an FPGA than on an ASIC. Nevertheless, this architecture directly benefits from newer generations of FPGAs, produced with fabrication processes that enable reduced minimal delay.

In order to address the limitation imposed by minimal delays, this work proposes an approach based on the fine and precise adjustment of delays. The novelty of this

approach resides in its ability to exploit two characteristics of FPGAs, namely the richness of the programmable interconnections fabric and the possibility to reconfigure the circuit dynamically. The latter, dynamic reconfiguration, is supported by some FPGAs and enables the user to reconfigure partially the circuit while in operation. As there exist a considerable amount of possible routes between two points of an FPGA, dynamic reconfiguration of the programmable interconnection fabric potentially enables delay adjustments with unprecedented resolutions. Indeed, our results show that the proposed delay line enables adjustments with a resolution of 1ps on a range that can span over 2,5ns.

On the basis of these fine resolution delay lines, a novel TDC architecture is proposed. Relying on the utilization of multiple parallel delay lines, the resolution achievable is now limited by the ability to adjust delay differences, instead of the previous limitation imposed by minimal delays. Therefore, such an architecture can potentially deliver resolutions lower than those found in state-of-the-art FPGA implementations. However, fine delay adjustment is itself insufficient to achieve the desired goal, and a calibration process enabling precise adjustment is also proposed. Delays are affected by both temperature and fabrication process variations of the chip. In order to enable precise delay adjustment, the proposed calibration take into account these variations, as well as clock skew. Using the proposed methodology, a TDC featuring 50ps resolution and 48ps precision was obtained. Moreover, results show that the methodology can be used to achieve resolutions as fine as 10ps. To our knowledge, to this day, such resolution is the lowest ever reported in the literature for an FPGA implementation.

Our approach based on fine and precise delay adjustment is also applied to a pre-existing TDC architecture based on the Vernier method with two oscillators. With this architecture, the achievable resolution corresponds to the period difference between the two oscillators. As our methodology enables precise period adjustment of a ring oscillator, the proposed implementation can deliver considerable resolution improvement when compared to those proposed in the literature. Indeed, our results show that resolutions below 5ps can be obtained. However, because of the instability of the oscillators, precision at such resolutions exceeds 100ps. Nevertheless, precisions of 25ps can be obtained at equivalent resolutions. Moreover, when compared

to static approaches proposed in the literature, our approach using dynamic reconfiguration is remarkable as it takes into account both temperature and fabrication process variations.

# Table des matières

|                                                                             |       |

|-----------------------------------------------------------------------------|-------|

| Dédicace . . . . .                                                          | iii   |

| Remerciements . . . . .                                                     | iv    |

| Résumé . . . . .                                                            | v     |

| Abstract . . . . .                                                          | viii  |

| Table des matières . . . . .                                                | xi    |

| Liste des tableaux . . . . .                                                | xiii  |

| Liste des figures . . . . .                                                 | xiv   |

| Liste des algorithmes . . . . .                                             | xvii  |

| Liste des annexes . . . . .                                                 | xviii |

| Liste des sigles et abréviations . . . . .                                  | xix   |

| Chapitre 1 INTRODUCTION . . . . .                                           | 1     |

| Chapitre 2 REVUE DE LITTÉRATURE . . . . .                                   | 8     |

| 2.1 Introduction . . . . .                                                  | 8     |

| 2.2 Résolution, Précision, et Exactitude . . . . .                          | 9     |

| 2.3 Critères de performance d'un TDC . . . . .                              | 13    |

| 2.4 Méthode d'interpolation . . . . .                                       | 15    |

| 2.5 Architecture basée sur la méthode du vernier avec deux oscillateurs . . | 16    |

| 2.6 Architecture basée sur la ligne à délais simple . . . . .               | 19    |

| 2.7 Architecture basée sur les lignes à délais de type vernier . . . . .    | 24    |

| 2.8 Conclusion . . . . .                                                    | 29    |

| Chapitre 3 APPROCHE PROPOSÉE . . . . .                                      | 31    |

| 3.1 Introduction . . . . .                                                  | 31    |

|                                              |                                                                                           |    |

|----------------------------------------------|-------------------------------------------------------------------------------------------|----|

| 3.2                                          | Une nouvelle architecture d'interpolateur basée sur l'ajustement fin des délais . . . . . | 32 |

| 3.2.1                                        | Calibration de l'interpolateur proposé . . . . .                                          | 33 |

| 3.2.2                                        | Une ligne à délai ajustable avec une résolution de l'ordre de la picoseconde . . . . .    | 36 |

| 3.2.3                                        | Un oscillateur à fréquence variable précis à l'ordre de la picoseconde . . . . .          | 41 |

| 3.2.4                                        | Avantages de la reconfiguration dynamique . . . . .                                       | 42 |

| 3.2.5                                        | Implémentation sur un FPGA Virtex-II Pro . . . . .                                        | 43 |

| 3.3                                          | Une nouvelle implémentation de la méthode du vernier avec deux oscillateurs . . . . .     | 49 |

| 3.3.1                                        | Conception de l'oscillateur démarrable . . . . .                                          | 49 |

| 3.3.2                                        | Calibration de l'interpolateur . . . . .                                                  | 49 |

| 3.3.3                                        | Implémentation sur un FPGA Virtex-II Pro . . . . .                                        | 50 |

| 3.4                                          | Conclusion . . . . .                                                                      | 51 |

| Chapitre 4 RÉSULTATS EXPÉRIMENTAUX . . . . . |                                                                                           | 53 |

| 4.1                                          | Introduction . . . . .                                                                    | 53 |

| 4.2                                          | Lignes à délais programmables . . . . .                                                   | 53 |

| 4.3                                          | Oscillateur à fréquence variable . . . . .                                                | 54 |

| 4.4                                          | Une nouvelle architecture de TDC basée sur l'ajustement fin des délais                    | 55 |

| 4.5                                          | Une nouvelle implémentation de la méthode du vernier avec deux oscillateurs . . . . .     | 59 |

| 4.6                                          | Conclusion . . . . .                                                                      | 64 |

| Chapitre 5 CONCLUSION . . . . .              |                                                                                           | 67 |

| 5.1                                          | Synthèse des travaux . . . . .                                                            | 67 |

| 5.2                                          | Limitations de la solution proposée . . . . .                                             | 68 |

| 5.3                                          | Améliorations futures . . . . .                                                           | 69 |

| Références . . . . .                         |                                                                                           | 71 |

| Publications de l'auteur . . . . .           |                                                                                           | 75 |

| Annexes . . . . .                            |                                                                                           | 76 |

# Liste des tableaux

|             |                                                                                                 |    |

|-------------|-------------------------------------------------------------------------------------------------|----|

| TABLEAU 2.1 | Performances des interpolateurs utilisant la méthode du vernier avec deux oscillateurs. . . . . | 30 |

| TABLEAU 2.2 | Performances des interpolateurs utilisant une ligne à délais simple. . . . .                    | 30 |

| TABLEAU 2.3 | Performances des interpolateurs utilisant des lignes à délais de type vernier. . . . .          | 30 |

| TABLEAU 4.1 | Comparaison des TDC dans la littérature offrant un temps mort d'un cycle ou moins. . . . .      | 66 |

| TABLEAU 4.2 | Comparaison des interpolateurs utilisant la méthode du vernier avec deux oscillateurs. . . . .  | 66 |

# Liste des figures

|             |                                                                                                                                                  |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

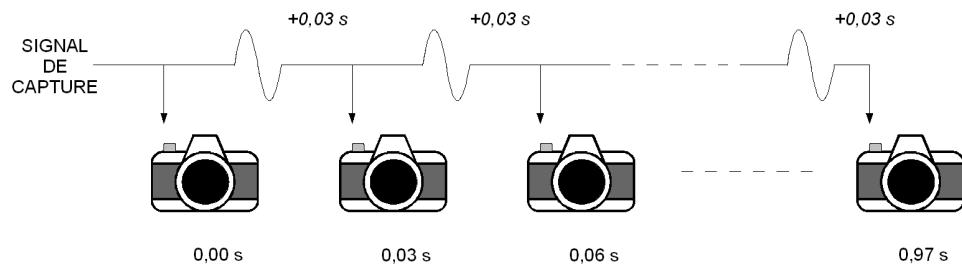

| FIGURE 1.1  | Capture d'une séquence vidéo à 30 images/seconde en utilisant des appareils photographiques, limités à 1 prise/seconde, reliés en série. . . . . | 3  |

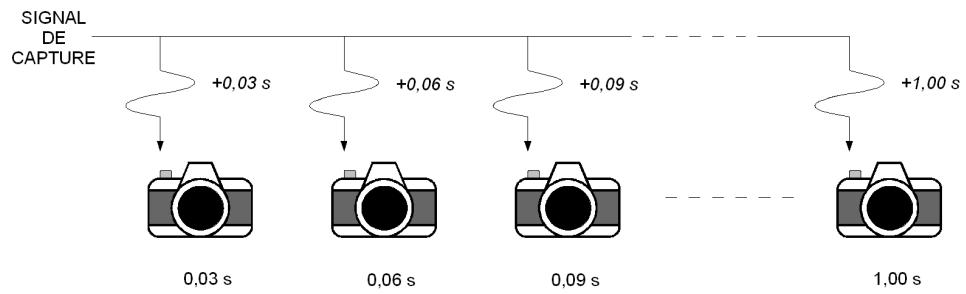

| FIGURE 1.2  | Illustration de l'approche proposée appliquée à l'exemple des appareils photographiques. . . . .                                                 | 6  |

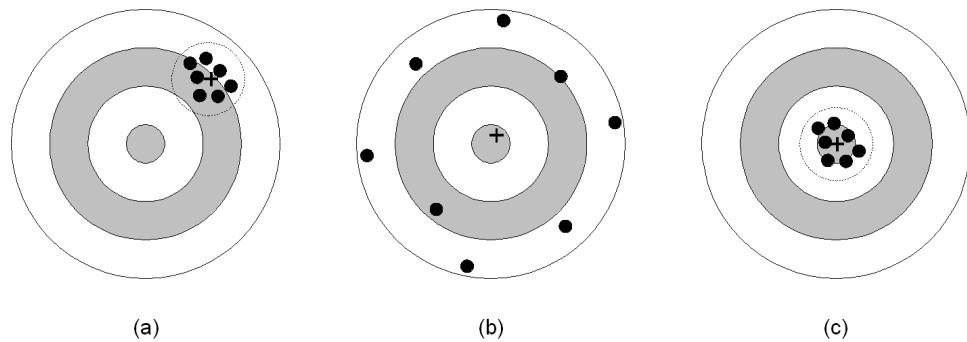

| FIGURE 2.1  | Analogie de la cible pour représenter la précision (a), la justesse (b) et l'exactitude (c) d'un instrument de mesure. . . . .                   | 12 |

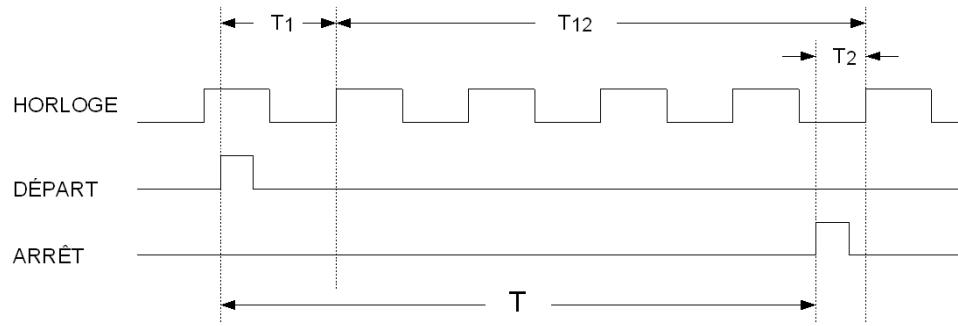

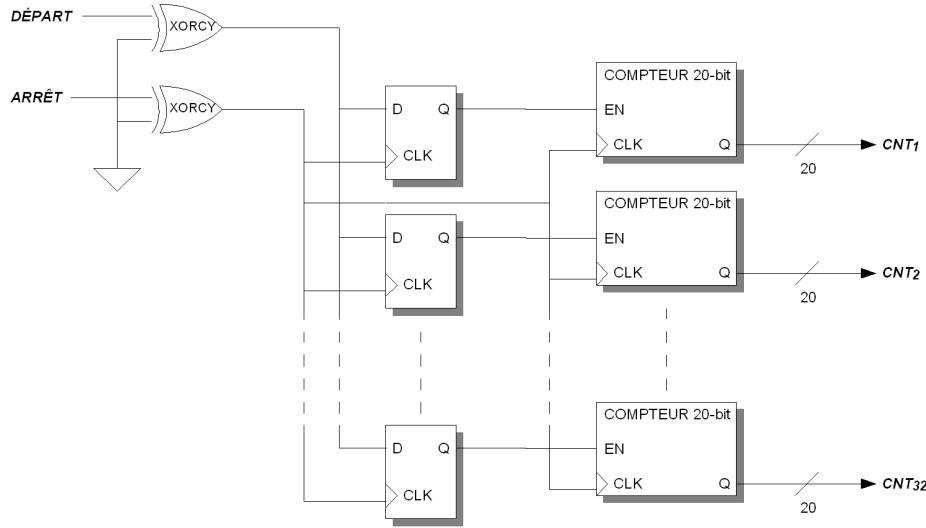

| FIGURE 2.2  | Méthode d'interpolation de Nutt, utilisant un compteur binaire et deux interpolateurs fins. . . . .                                              | 16 |

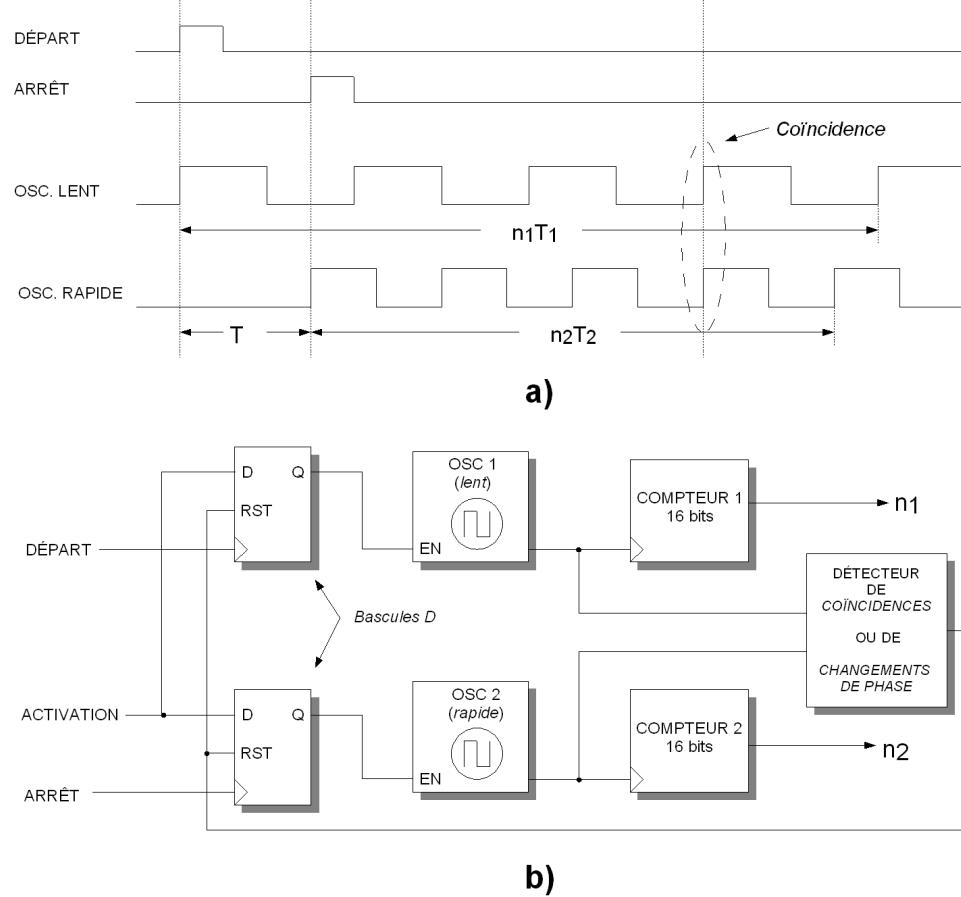

| FIGURE 2.3  | Diagrammes temporels (a), et architecture (b) de l'interpolator basé sur la méthode du vernier avec deux oscillateurs. . . .                     | 17 |

| FIGURE 2.4  | Oscillateur à anneau utilisant une porte XOR proposé par Lin <i>et al.</i> (2006). . . . .                                                       | 19 |

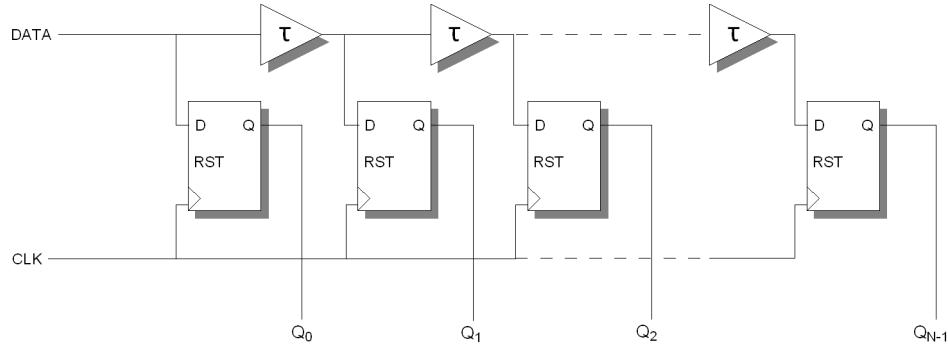

| FIGURE 2.5  | Échantillonnage de copies régulièrement retardées d'un même signal pour augmenter la fréquence d'échantillonnage efficace. . . . .               | 20 |

| FIGURE 2.6  | Architecture d'un interpolateur basé sur une ligne à délais sur écoute. . . . .                                                                  | 21 |

| FIGURE 2.7  | Implémentation d'une ligne à délais sur écoute avec la chaîne de retenue d'un additionneur proposée par Song <i>et al.</i> (2006). . . . .       | 22 |

| FIGURE 2.8  | Méthode d'union d'onde attaquant le problème des divisions larges. . . . .                                                                       | 23 |

| FIGURE 2.9  | Interpolator basé sur les lignes à délais de type vernier. . . . .                                                                               | 24 |

| FIGURE 2.10 | Implémentation d'un interpolateur basé sur les lignes à délais de type vernier proposée par (Kalisz <i>et al.</i> , 1997). . . . .               | 26 |

| FIGURE 2.11 | Implémentation d'un interpolateur basé sur les lignes à délais de type vernier proposée par Minas <i>et al.</i> (2007). . . . .                  | 27 |

| FIGURE 2.12 | Interpolator utilisant plusieurs lignes à délais de type vernier proposé par Amiri <i>et al.</i> (2009). . . . .                                 | 28 |

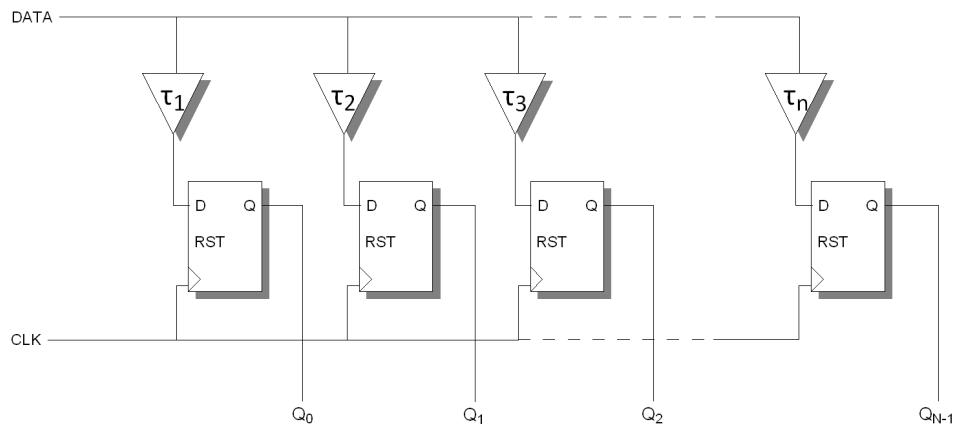

| FIGURE 3.1  | Architecture d'interpolator basé sur l'utilisation de lignes à délais programmables parallèles. . . . .                                          | 32 |

|            |                                                                                                                                                                                        |    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

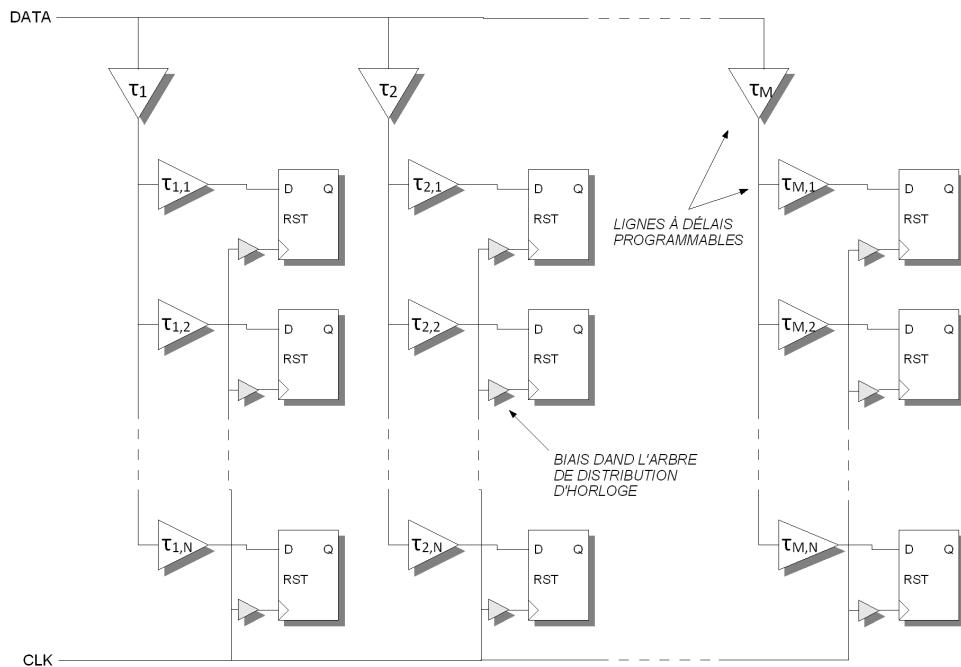

| FIGURE 3.2 | Architecture d'interpolator proposée utilisant plusieurs ensembles de lignes à délais programmables parallèles. . . . .                                                                | 33 |

| FIGURE 3.3 | Processus de calibration proposé pour ajuster les délais de l'interpolator en tenant compte des variations de procédés et de température, ainsi que du biais d'horloge. . . . .        | 35 |

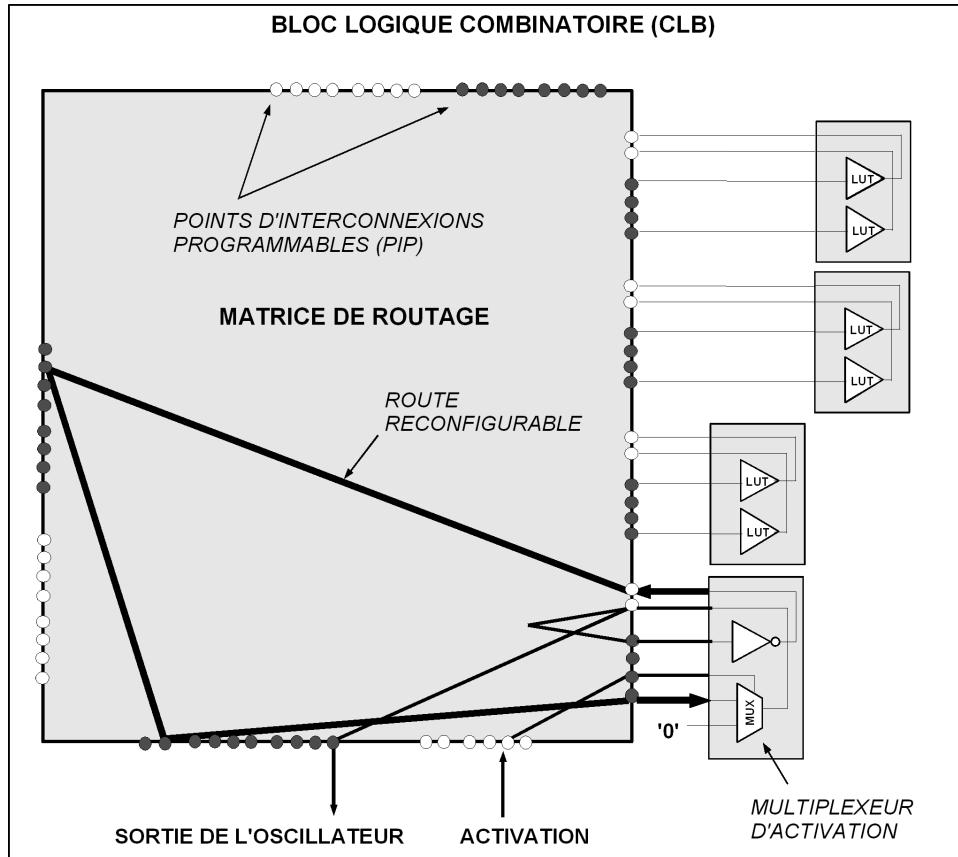

| FIGURE 3.4 | Reconfiguration dynamique de la ligne à délai en oscillateur en anneau, de manière à pouvoir mesurer les demi-périodes (proportionnelles aux délais) associées à chaque route. . . . . | 37 |

| FIGURE 3.5 | Implémentation proposée de la ligne à délai programmable. . .                                                                                                                          | 39 |

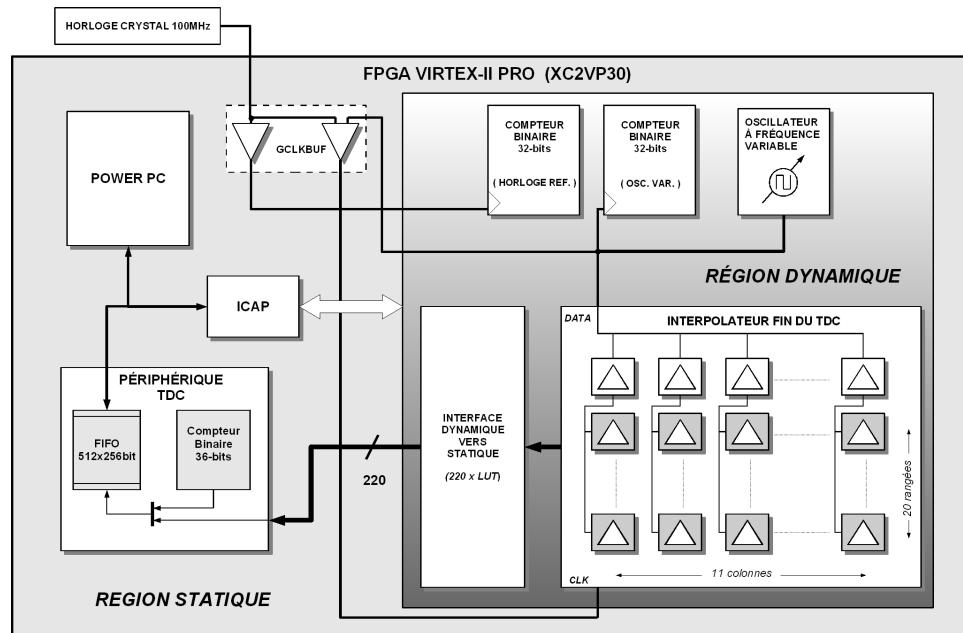

| FIGURE 3.6 | Implémentation du TDC proposé dans un Virtex-II Pro. Le design est partitionné en une région dynamique et une région statique. . . . .                                                 | 44 |

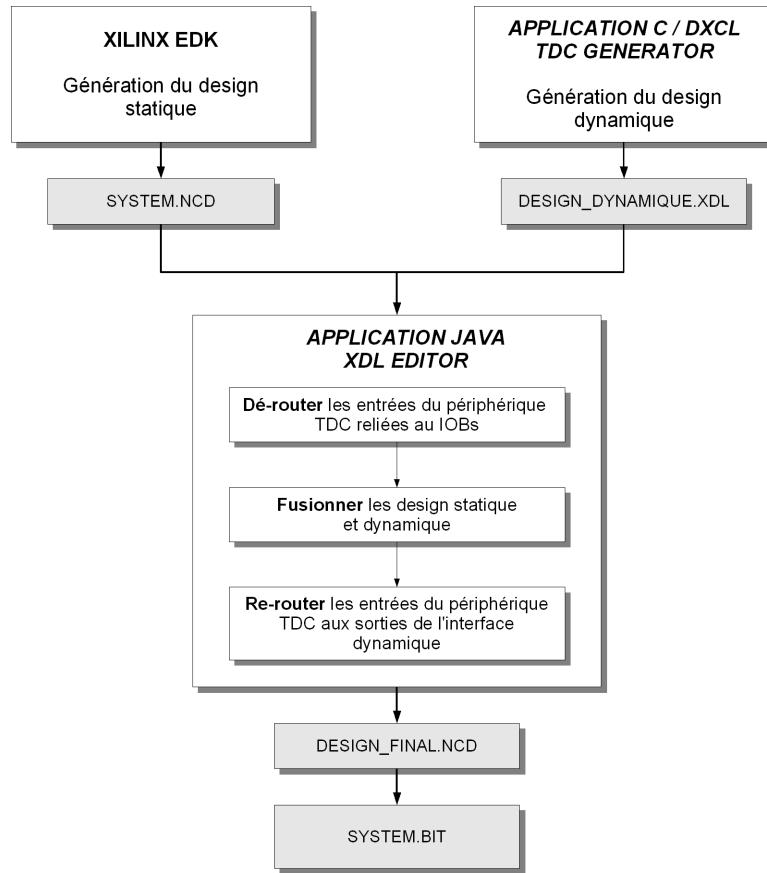

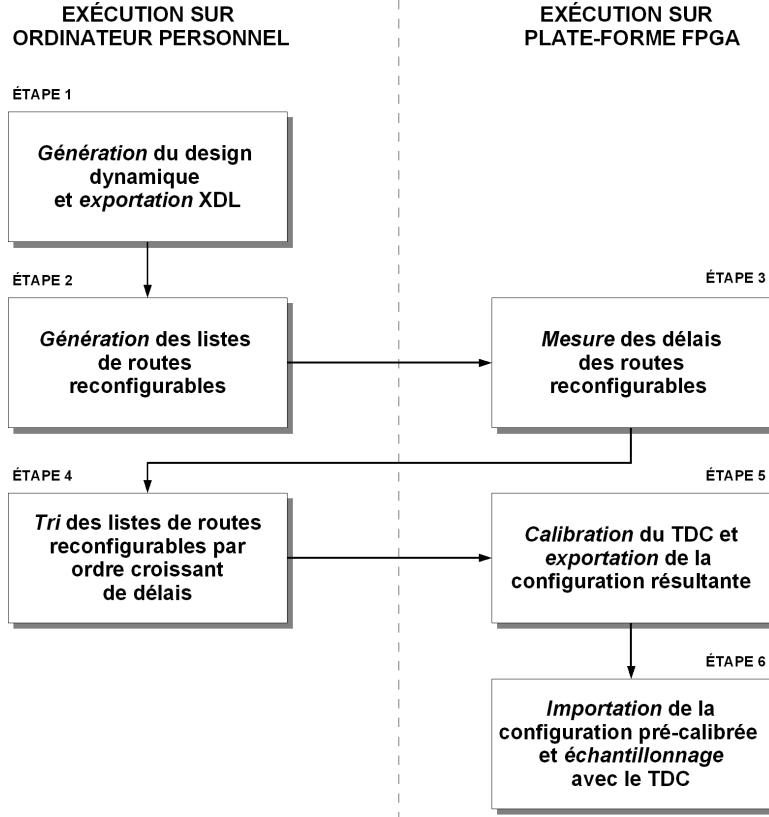

| FIGURE 3.7 | Processus de génération du design statique. . . . .                                                                                                                                    | 46 |

| FIGURE 3.8 | Processus de génération et calibration du design dynamique du TDC proposé. . . . .                                                                                                     | 48 |

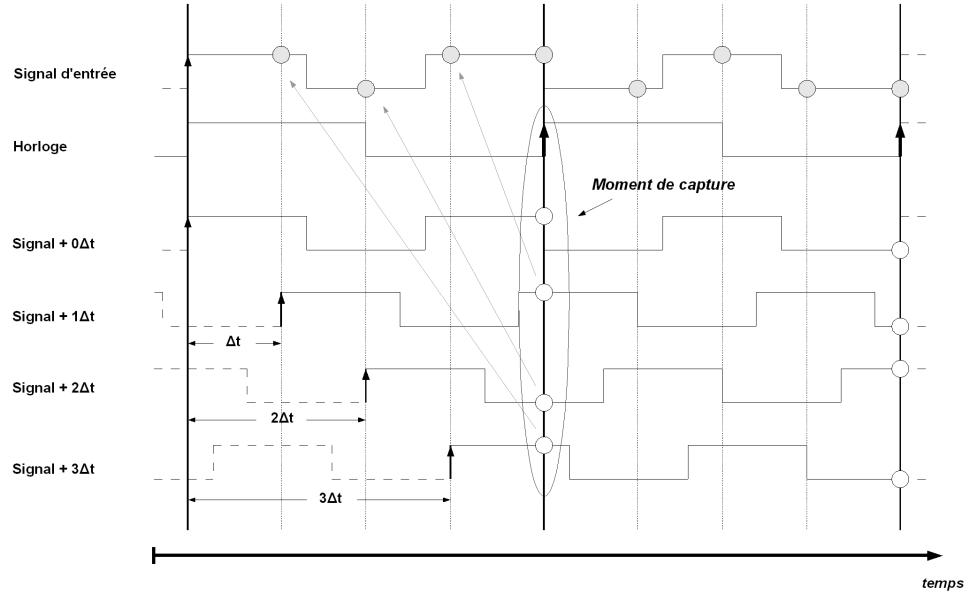

| FIGURE 3.9 | Implémentation proposée d'un oscillateur démarrable. . . . .                                                                                                                           | 50 |

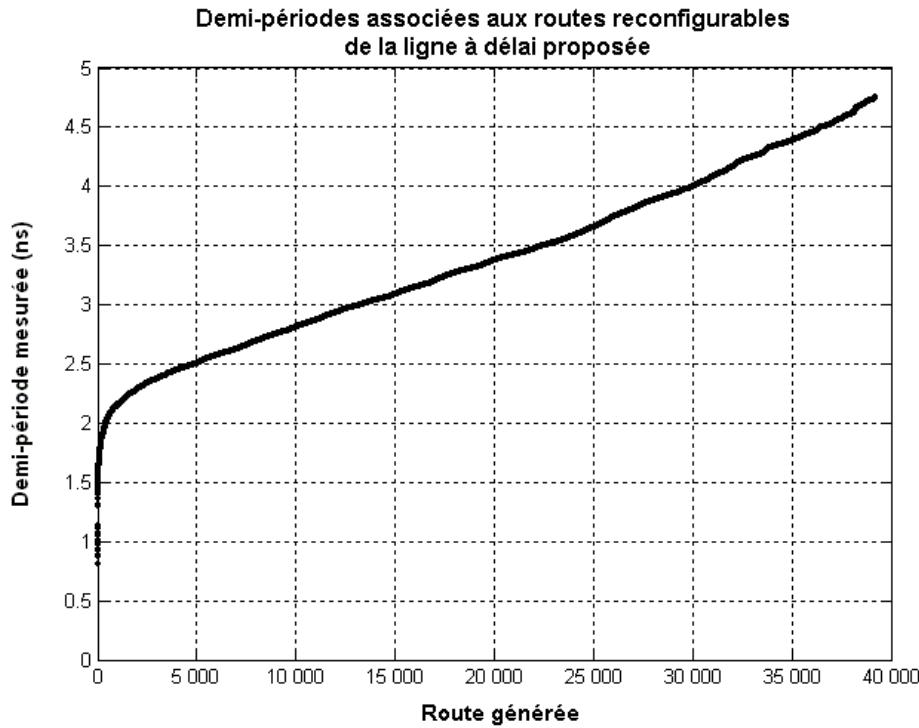

| FIGURE 4.1 | Demi-périodes associés à chaque route de la liste générée pour la ligne à délai programmable proposée. . . . .                                                                         | 54 |

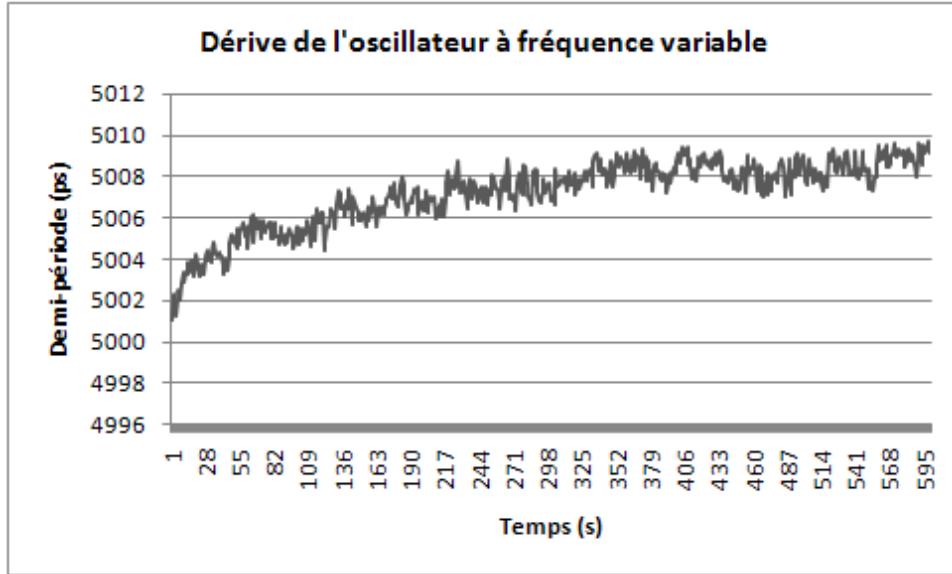

| FIGURE 4.2 | Dérive de la demi-période de l'oscillateur à fréquence variable sur une période de 10 minutes. . . . .                                                                                 | 55 |

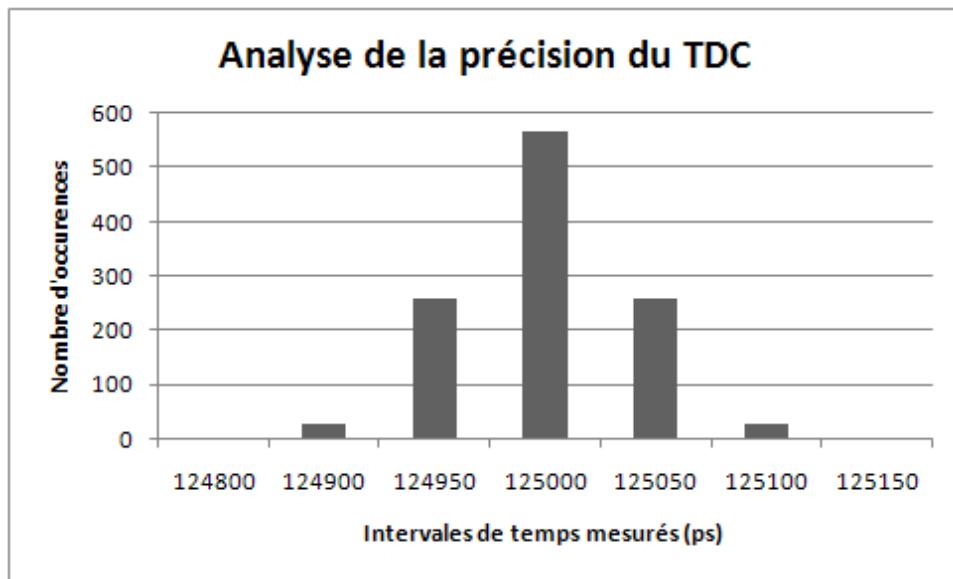

| FIGURE 4.3 | Distribution des mesures effectuées en injectant un signal d'horloge à période constante, avec une moyenne de 124,9997ns et un écart-type de 40,3ps. . . . .                           | 56 |

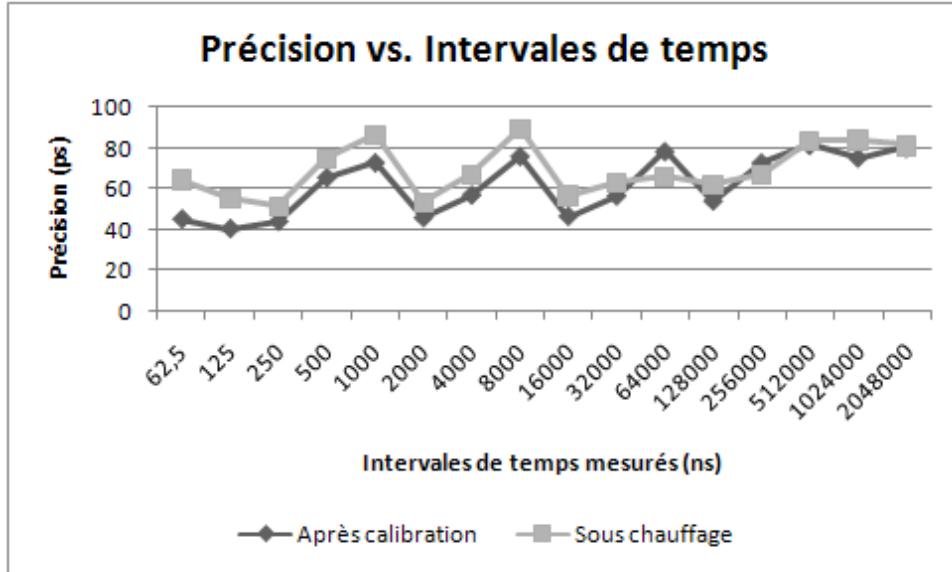

| FIGURE 4.4 | Influence d'un chauffage sur la précision pour différents intervalles de temps allant de 62,5ns à 2,048ms. . . . .                                                                     | 57 |

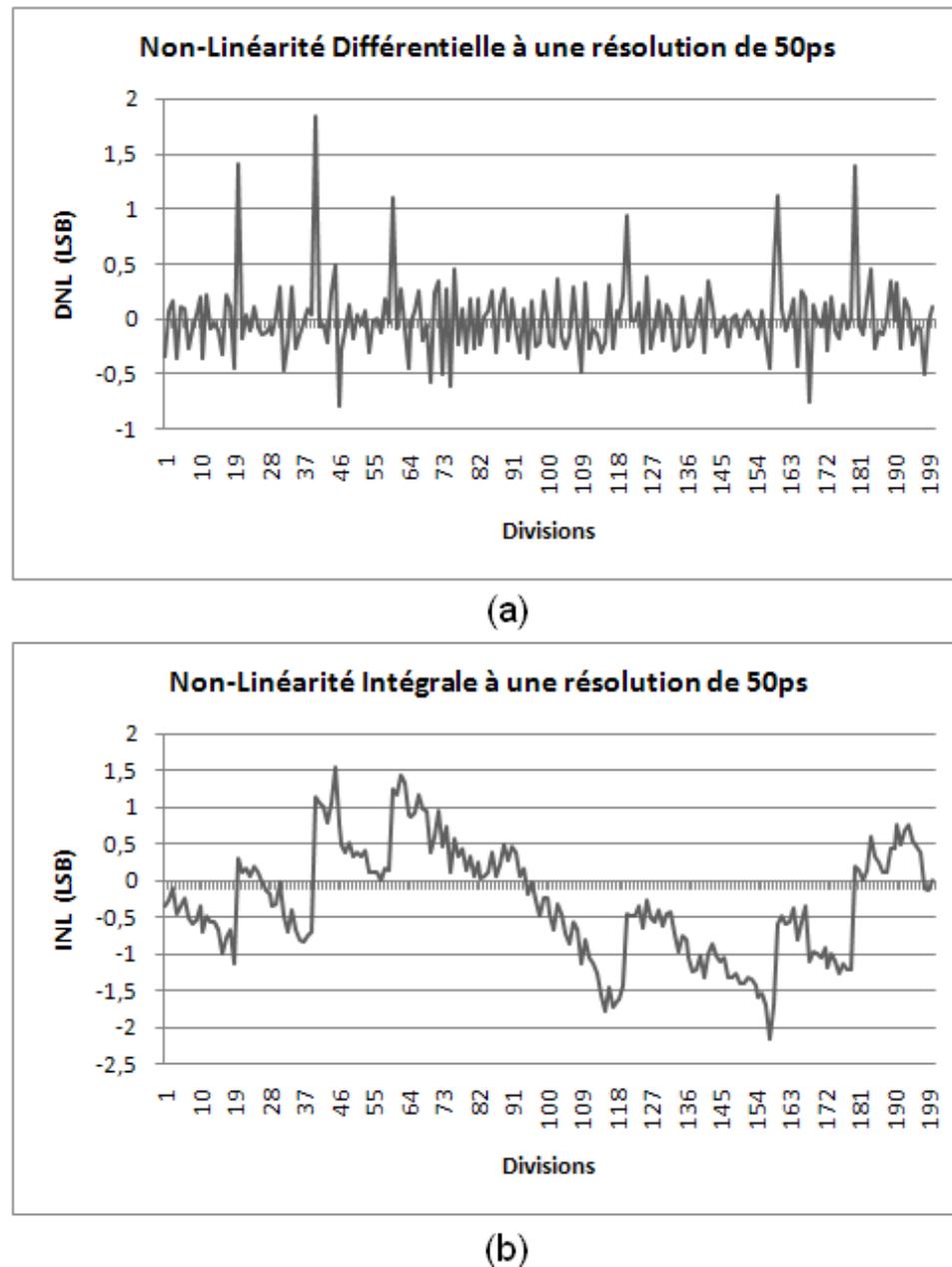

| FIGURE 4.5 | Non-linéarité différentielle (a) et intégrale (b), à une résolution de 50ps sur une portée dynamique de 10ns. . . . .                                                                  | 58 |

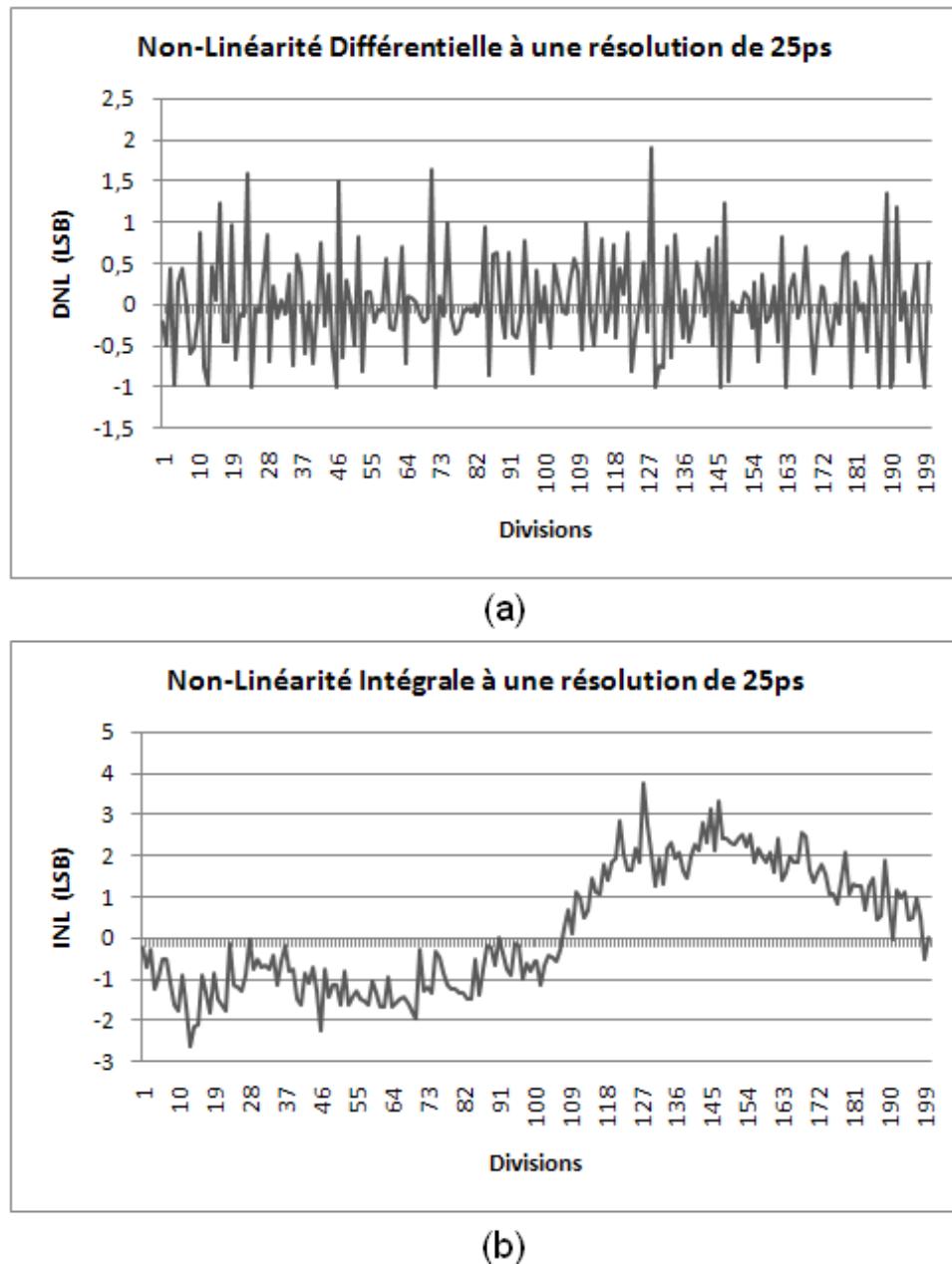

| FIGURE 4.6 | Non-linéarité différentielle (a) et intégrale (b), à une résolution de 25ps et sur une portée dynamique de 5ns. . . . .                                                                | 60 |

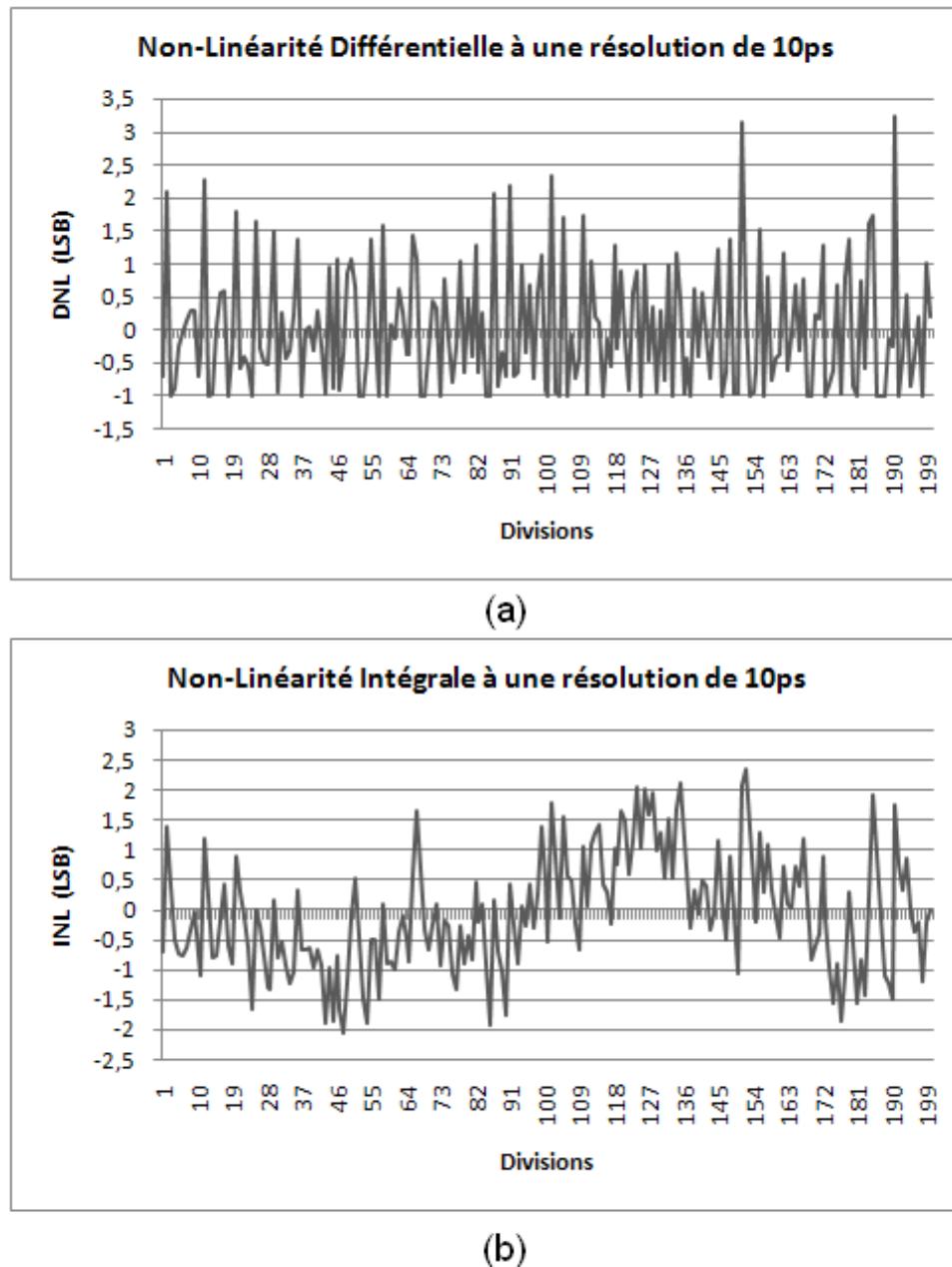

| FIGURE 4.7 | Non-linéarité différentielle (a) et intégrale (b), à une résolution de 10ps et sur une portée dynamique de 2ns. . . . .                                                                | 61 |

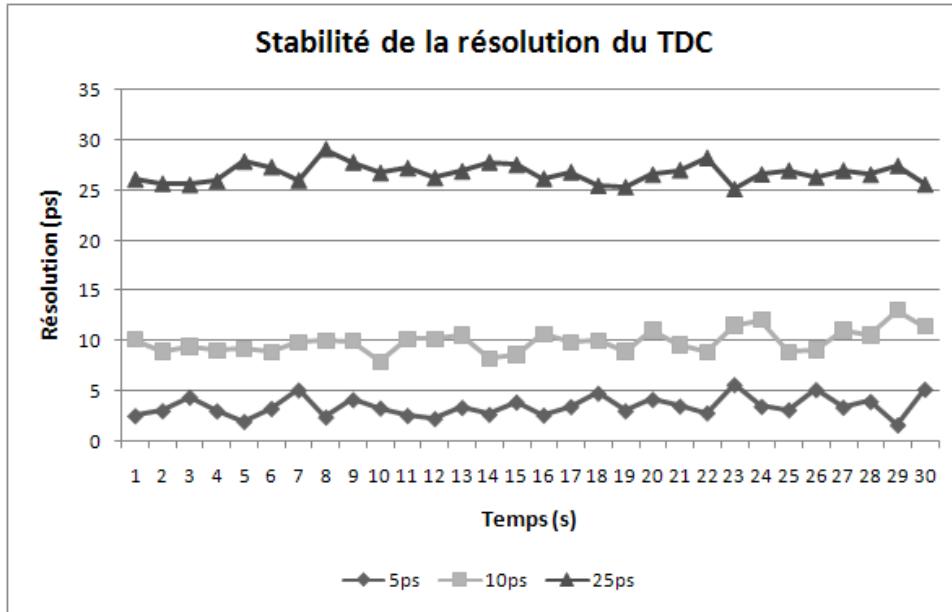

| FIGURE 4.8 | Stabilité sur 30 secondes des résolutions calibrées pour 25ps, 10ps, et 5ps. . . . .                                                                                                   | 62 |

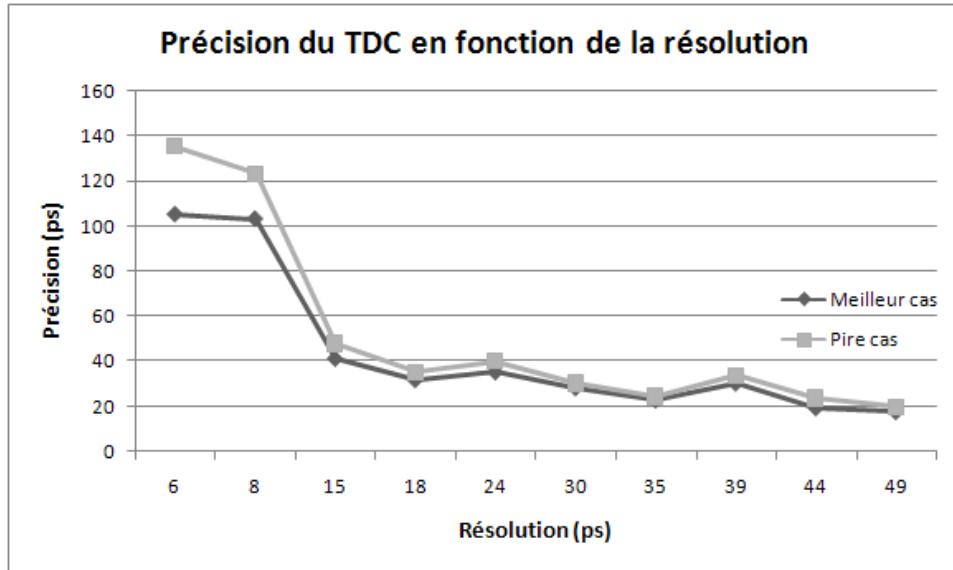

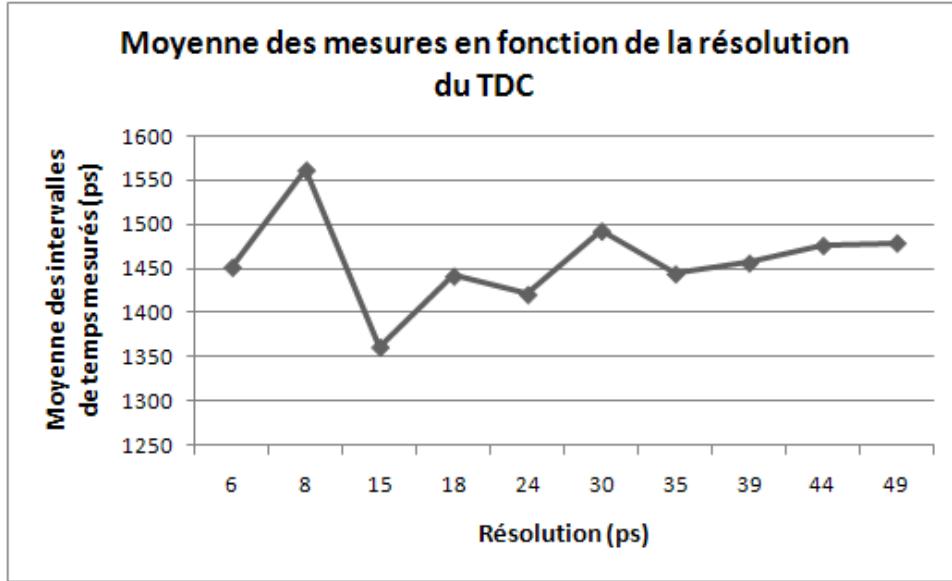

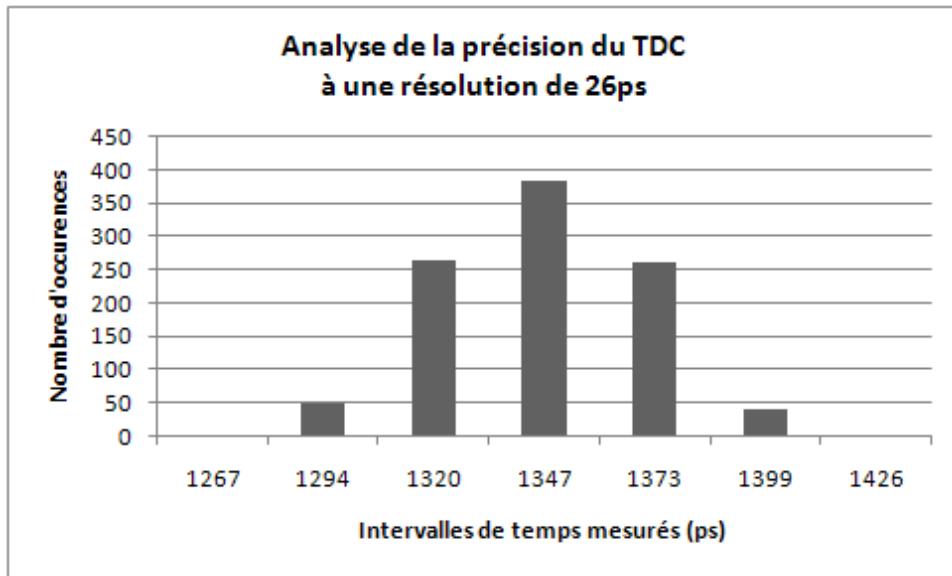

| FIGURE 4.9 | Précision du TDC en fonction de la résolution. . . . .                                                                                                                                 | 63 |

# Liste des algorithmes

|                |                                                          |    |

|----------------|----------------------------------------------------------|----|

| ALGORITHME 3.1 | Génération de routes reconfigurables . . . . .           | 41 |

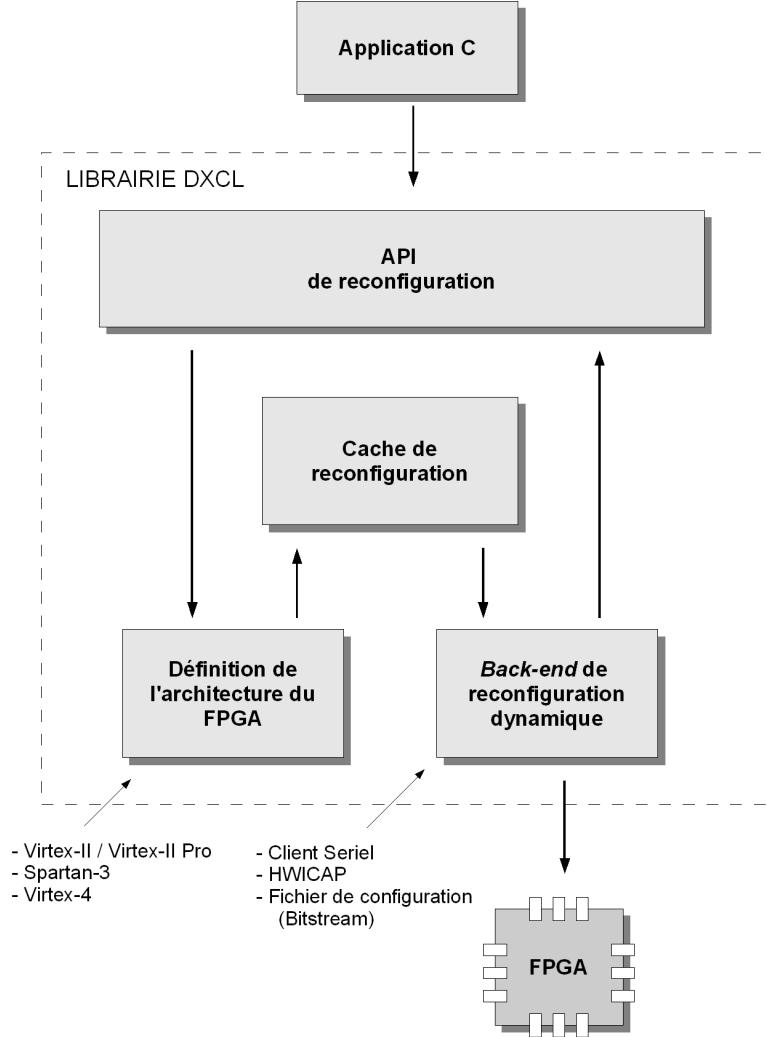

| ALGORITHME A.1 | Exemple simple d'application C avec la bibliothèque DXCL | 79 |

# Liste des annexes

|                                      |    |

|--------------------------------------|----|

| ANNEXE A Bibliothèque DXCL . . . . . | 76 |

|--------------------------------------|----|

# Liste des sigles et abréviations

|      |                                         |

|------|-----------------------------------------|

| ASIC | Application Specific Integrated Circuit |

| CLB  | Configurable Logic Block                |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| CPLD | Complex Programmable Logic Device       |

| DNL  | Differential Non-Linearity              |

| FPGA | Field Programmable Gate Array           |

| ICAP | Internal Configuration Access Port      |

| INL  | Integral Non-Linearity                  |

| IOB  | Input-Output Block                      |

| LSB  | Least Significant Bit                   |

| LUT  | Look-Up Table                           |

| OPB  | On-chip Peripheral Bus                  |

| PIP  | Programmable Interconnection Point      |

| PLB  | Processor Local Bus                     |

| TDC  | Time-to-Digital Converter               |

# Chapitre 1

## INTRODUCTION

Les instruments de mesure et la science expérimentale sont intimement liés. En effet, au cœur même de la méthode scientifique, l'observation et l'expérimentation reposent sur des moyens d'observer et de quantifier certaines propriétés physiques. D'autre part, les avancées scientifiques et technologiques rendent possible la création de nouveaux appareils de mesures et l'amélioration de la précision de ceux qui existent. Les instruments de mesure sont omniprésents dans nos vies, autant que dans les laboratoires scientifiques. Par exemple, une balance nous permet de mesurer notre masse, un thermomètre nous permet de connaître la température, une règle à mesurer de connaître notre taille, jusqu'à l'horloge qui nous indique le temps présent.

De toutes les mesures possibles, le temps a ceci de particulier qu'il ne peut être fixé, s'écoulant toujours dans la même direction, seconde par seconde. La mesure du temps par l'homme remonte à l'antiquité, le cadran solaire en étant souvent considéré le plus ancien instrument. Son principe était tout simple, basé sur le déplacement du soleil, la position de l'ombre projetée par un objet indiquait l'heure du jour. À la même époque existait également la clepsydre, que l'on peut décrire comme un sablier à base d'eau. Le problème de la clepsydre était malheureusement que le débit d'écoulement de l'eau n'était pas constant, la pression exercée par l'eau diminuant au fil du temps. Le sablier qui apparut plus tard n'avait pas ce problème, son principe reposant sur l'écoulement de sable au travers d'un orifice, et possédait également l'avantage d'être portable, en plus de ne pas geler au froid ! Bien qu'il soit aujourd'hui utilisé comme objet de décoration plutôt que pour le temps qu'il indique, le sablier demeure toujours un symbole largement répandu du temps. Il fallu attendre le 14<sup>e</sup> siècle pour voir l'apparition d'horloges mécaniques. Ces dernières utilisaient un mécanisme d'échappement afin de contrôler la rotation d'un engrenage souvent relié à un ressort où un poids suspendu. Le principe des montres de poche du 17<sup>e</sup> siècle n'était pas si différent, sinon que la période d'oscillation du mécanisme d'échappement était

contrôlée par un balancier plutôt qu'un pendule. Les montres Quartz tant répandues aujourd'hui ont vu le jour après l'avènement de l'électronique. Elles tiennent leur nom du fait qu'elles utilisent un oscillateur électronique réglé par un cristal quartz. L'avantage principal de l'oscillateur à quartz est que sa période est bien plus précise que celle de son prédecesseur. Plutôt que d'utiliser un train d'engrenage pour compter les oscillations et les transformer en heures, minutes et secondes, un circuit numérique simple (compteur binaire) prend généralement en charge cette responsabilité.

L'électronique est plus omniprésente que jamais dans nos vies, que ce soit dans notre montre quartz, notre cafetière, notre voiture, jusqu'à notre ordinateur personnel, il semble que rien ne puisse freiner la prolifération des transistors dans les objets que nous utilisons quotidiennement. Les instruments de mesure n'y échappent pas non plus, bien au contraire ! Dans un monde où les circuits intégrés se retrouvent presque partout, il n'est pas surprenant de s'intéresser à la mesure de signaux électriques. Dans le domaine de la microélectronique, un signal numérique peut prendre deux valeurs possibles, c'est ainsi que l'on s'intéresse tout particulièrement aux moments de transition de ceux-ci, de même qu'à leur synchronisation. Au-delà du domaine de la micro-électronique, la mesure d'intervalles de temps à de très fines résolutions est essentielle dans plusieurs domaines d'applications scientifiques. Dans le domaine de la physique des particules, le temps de vol d'une particule sur une distance connue permet d'en connaître la masse. Un radar laser requiert la mesure du temps de vol d'aller-retour d'une pulsation lumineuse vers un objet pour connaître la distance à laquelle il se trouve. En imagerie médicale, la tomographie par émission de positrons requiert la détection de coïncidences des temps d'émission de paires de photons. Or, bien que le temps de course d'un coureur de 100m soit mesuré au centième de seconde, des applications de pointes telles que celles mentionnées précédemment requièrent des résolutions inférieures au milliardième de seconde !

Un convertisseur numérique de temps (TDC) est un circuit intégré permettant de mesurer des intervalles de temps à de très fines résolutions avec une haute précision. À l'ère des circuits numériques cadencés par des horloges dont la fréquence se chiffre en gigahertz (un milliard d'oscillations par seconde et plus), en principe un convertisseur numérique de temps pourrait se contenter d'appliquer le principe de la montre Quartz, utilisant un oscillateur et un compteur d'oscillations très rapides. Ainsi, à

des fréquences d'oscillations allant de 1 à 10 GHz, il serait possible d'obtenir des résolutions temporelles se situant entre un milliardième et un dixième de milliardième de secondes. Néanmoins, en pratique, cette approche pose problème. D'une part, la conception et fabrication de circuits opérant à de telles fréquence comporte de nombreuses difficultés et exige des procédés de fabrication de pointe très onéreux. D'autre part, de manière plus fondamentale, afin de mesurer ou d'observer des signaux numériques dont les fréquences peuvent atteindre les gigahertz, il est impératif d'échantillonner ces signaux à des fréquences plus élevées encore. Le problème de conception d'un convertisseur numérique de temps est ainsi d'offrir une résolution de mesure d'un ordre au moins dix fois plus fine par rapport aux périodes d'oscillations atteignables avec les procédés les plus récents. C'est un peu comme si quelqu'un désirait utiliser des appareils photos limités à une prise de photo par seconde pour capter une séquence vidéo, à raison de 30 images par secondes. Après réflexion, une approche possible serait d'en utiliser 30 et de les déclencher les uns après les autres, à chaque 30ième de seconde. Malheureusement, aucun être humain n'est assez rapide pour suivre une telle cadence. Pour y parvenir, il pourrait être suffisant de propager un signal de capture à chaque appareil au travers d'un seul fil en série, de sorte à ce que le temps de propagation du signal entre chaque appareil soit de 1/30 de seconde (voir Figure 1.1). Il ne resterait qu'à déclencher le signal à chaque seconde. Effectivement, le principe d'opération d'un convertisseur numérique de temps s'apparente souvent à celui exposé dans cet exemple des appareils photos, de sorte à surmonter les limitations imposées en termes de fréquence d'opération.

FIGURE 1.1 Capture d'une séquence vidéo à 30 images/seconde en utilisant des appareils photographiques, limités à 1 prise/seconde, reliés en série.

En matière de circuits intégrés, on distingue deux grandes classes : les circuits dédiés (*ASIC*), et les circuits (re-) programmables (*FPGA*, *CPLD*, *PLA*). La dis-

tinction fondamentale entre ces deux classes est que les circuits (re-) programmables sont en fait des circuits dédiés à permettre, par programmation, l'implémentation de différents circuits. Cette capacité de programmer le circuit pour implémenter différents designs numériques a toutefois un prix. En effet, par rapport aux circuits dédiés, les circuits programmables offrent des performances nettement moindre, en termes de densité logique efficace, de fréquence d'opération maximale (délais d'interconnections plus grands), et de consommation de puissance. En contrepartie, les puces (re-) programmables requièrent un effort de conception nettement moindre, entraînant des temps de mise en marché réduits. De plus, en termes économiques, la fabrication d'un circuit dédié implique des coûts non-récurrents massifs, d'autant plus que le processus de fabrication ciblé est récent. Il en résulte que les procédés de fabrication de pointe sont essentiellement réservés aux compagnies concevant des circuits vendus en très grands volumes, et disposant de capitaux importants, tel qu'est le cas pour les fabricants de processeurs *Intel* et *AMD*, ainsi que les fabricants de FPGA *Xilinx* et *Altera*. Lorsque des plus petits volumes de production sont ciblés, il faut alors se tourner vers des procédés de fabrication plus anciens, offrant des performances réduites, ou bien vers des puces programmables. Puisque les FPGA permettent de bénéficier des procédés de fabrication les plus récents, la différence de performance est alors moindre que lorsqu'un FPGA et un circuit dédié de procédés de fabrication équivalents sont comparés l'un à l'autre.

Historiquement, les convertisseurs numériques de temps étaient exclusivement implémentés sous forme de circuits intégrés dédiés. À ce jour, les meilleurs convertisseurs numériques de temps sont encore des circuits dédiés, atteignant des résolutions avoisinant la picoseconde. Néanmoins, avec les progrès fulgurants de la technologie FPGA, plusieurs se sont intéressés au courant de la dernière décennie à l'implémentation de ces circuits avec cette technologie, si bien qu'à ce jour des résolutions inférieures à 100ps (0,1 milliardième de seconde) sont ainsi atteintes. Bien que l'implémentation de TDC sur puces programmables bénéficie des connaissances développées pour les circuits dédiés, cette dernière est également confrontée à de nouveaux problèmes. Essentiellement, la problématique est que contrairement au circuit dédié qui permet une grande flexibilité de conception, le concepteur pour FPGA doit composer avec ce que le circuit programmable met à sa disposition. Mais revenant aux avantages et inconvénients discutés, la difficulté additionnelle d'une telle implémentation pro-

vient principalement du fait que les délais d'interconnexions sont sensiblement plus élevés, avec pour corollaire que la fréquence d'opération maximale est moindre.

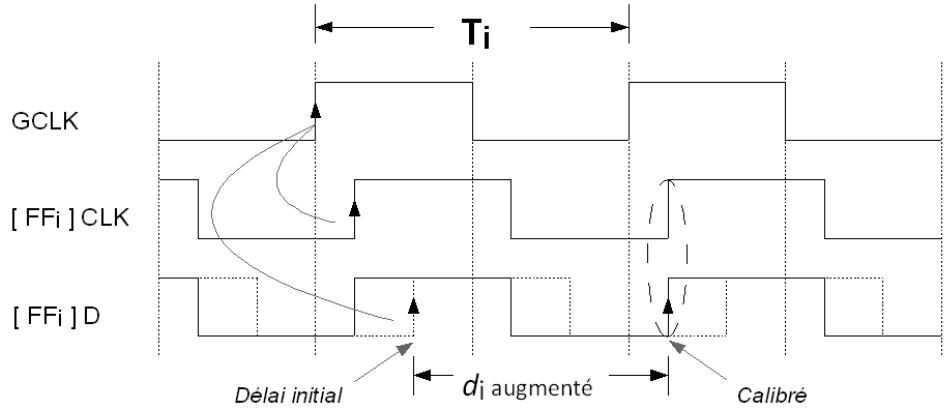

Ce travail de recherche porte sur l'implémentation d'un convertisseur numérique de temps sur un FPGA reconfigurable dynamiquement. À sa plus simple expression, la reconfiguration dynamique, ou reconfiguration active partielle, consiste à reconfigurer une partie du circuit lors de son opération. Normalement, un FPGA est configuré avant sa mise en opération, mais certains supportent également la reconfiguration partielle en cours d'opération. La première contribution de ce travail est de proposer une méthode, tirant profit du système d'interconnexions programmables, permettant de réaliser des lignes à délais programmables avec une résolution de 1ps sur une plage d'environ 3ns. Une extension de cette méthode consiste en la réalisation d'un oscillateur en anneau à fréquence variable dont la période est précise à +/-1ps sur une plage de 60ns. La deuxième contribution de ce travail est de proposer une nouvelle architecture de TDC basée sur l'utilisation de lignes à délais programmables, ainsi qu'un processus de calibration, utilisant un oscillateur à fréquence variable. Cette approche, basée sur la reconfiguration dynamique d'un FPGA, présente 3 avantages intéressants :

- Le processus de calibration tient compte des variations de températures ainsi que des variations physiques liées au procédé de fabrication, qui affectent tous deux les délais des interconnexions.

- Le processus de calibration n'est pas affecté par le biais de l'arbre d'horloge, utilisé dans l'implémentation de l'architecture proposée, lors de l'ajustement des délais.

- Les résolutions atteignables avec l'architecture proposée sont limitées par la finesse à laquelle peuvent être ajustés les délais du circuit, plutôt que les délais minimaux du circuit.

Il est possible d'établir un parallèle entre la méthodologie proposée et l'exemple des appareils photos présenté plus tôt. Dans cet exemple, afin de prendre 30 photos par seconde, les appareils avaient été reliés en série par un fil. En considérant la situation où le temps de propagation sur le fil du signal de capture, d'un appareil à l'autre, est supérieur à 1/30 de seconde, un problème se pose. En fait, dans une telle situation, cette approche ne permet pas d'atteindre les performances visées. Cela s'apparente à

l’importance des délais dans un FPGA comparativement à ceux d’un circuit dédié (de même procédé). La méthodologie proposée permet de contourner ce problème, sous l’hypothèse d’une capacité d’ajuster précisément le délai d’un fil, même si ce dernier ne peut être réduit sous sa valeur minimale. Plutôt que de relier les appareils en série avec un long fil, nous proposons simplement d’utiliser 30 fils parallèles. Ainsi, afin d’obtenir les 30 photos par seconde, il suffit d’ajuster les délais de sorte à ce que les différences entre ceux-ci correspondent à 1/30 de secondes, les unes après les autres (voir Figure 1.2).

FIGURE 1.2 Illustration de l’approche proposée appliquée à l’exemple des appareils photographiques.

Avec la méthodologie et l’architecture proposée, nous avons réalisé un convertisseur numérique de temps fonctionnant à une résolution de 50ps avec une précision de 45ps. De plus, les résultats expérimentaux obtenus montrent que la méthodologie peut être utilisée pour atteindre des résolutions aussi fines que 10ps. À notre connaissance, cette résolution est la meilleure atteinte à ce jour sur FPGA. En troisième lieu, notre méthodologie basée sur l’ajustement fin des délais est appliquée à une architecture préexistante de TDC. Les résultats ainsi obtenus montrent une certaine amélioration par rapport à ceux proposés dans la littérature.

Le présent document est divisé en 5 chapitres. Afin de bien situer ce travail dans l’état de l’art, le deuxième chapitre présente une revue de la littérature en matière d’implémentation de convertisseurs numériques de temps sur FPGA. Le troisième chapitre de ce travail est consacré à la méthodologie proposée, tirant profit de la reconfiguration dynamique pour réaliser des délais programmables à fine résolution, ainsi qu’à l’architecture novatrice de TDC basée sur l’ajustement fin des délais et son

processus de calibration. Ce même chapitre présente également l'application du savoir-faire développé à une architecture de TDC basée sur l'utilisation de deux oscillateurs à fréquences légèrement différentes. Le chapitre 4 rapporte les résultats expérimentaux obtenus, tandis que le chapitre 5 vient conclure et suggérer de futures directions à ce travail.

# Chapitre 2

## REVUE DE LITTÉRATURE

### 2.1 Introduction

L'aube des premières implémentations sur FPGA de convertisseurs numériques de temps (TDC) à haute résolution remonte à la fin des années 90. Depuis, le sujet a été considérablement étudié et les implémentations de pointe offrent des résolutions et précisions sous les 20ps. Ce progrès est également lié à celui de la technologie FPGA, qui a été fulgurant lors de la dernière décennie. Néanmoins, les implémentations de TDC sur circuits dédiés surpassent toujours les implémentations programmables. Par exemple, dans l'implémentation proposée par Lee et Abidi (2008) une résolution de 1,25ps est obtenue en utilisant un procédé de fabrication à 90nm. Il est toutefois intéressant d'observer que dans un appareil de mesure de pointe tel le *U1050A* d'Agilent Technologies offrant des résolutions de 50ps à 5ps, bien que le TDC soit un circuit dédié, le circuit d'acquisition de l'appareil est implémenté dans un FPGA (Virtex-II Pro de Xilinx).

Certaines méthodes de conception de TDC font usage de circuits analogiques, tel un convertisseur analogique à numérique, et par conséquent ne permettent pas une intégration sur FPGA. Il existe 3 méthodes de conception numériques qui reviennent fréquemment dans la littérature : la méthode du vernier avec deux oscillateurs, la méthode de la ligne à délais simple « sur écoute », et la méthode des lignes à délais avec vernier. Ces méthodes, développées initialement pour les circuits dédiés sont ainsi applicables aux circuits programmables. L'implémentation FPGA de chacune de ces méthodes pose différents problèmes qui lui sont spécifiques. Dans ce chapitre, nous proposons au lecteur une revue des différentes architectures et implémentations FPGA de convertisseurs numériques de temps. Bien que cette dernière ne soit pas exhaustive, l'étude de l'état de l'art proposée expose les différents problèmes spécifiques à l'implémentation FPGA de chacune des trois méthodes mentionnées, et explore les

solutions développées afin de les adresser.

Les convertisseurs numériques de temps mesurent des intervalles de temps, typiquement définis par les moments d'arrivées d'une impulsion de départ et d'une impulsion d'arrêt. Bien qu'un compteur rapide d'oscillations ne soit pas une solution viable au problème, afin d'obtenir de bonnes résolutions pour de longs intervalles, un compteur grossier est typiquement utilisé. Afin d'augmenter la résolution offerte par ce compteur, de tels TDC comprennent également un *interpolateur fin* de temps, pour « interpoler » le temps entre les valeurs données par ce compteur. Il en découle que l'interpolateur fin est le circuit critique d'un TDC, déterminant pour sa résolution.

Dans ce chapitre, nous débutons par une discussion générale sur les termes et définitions utilisés dans la littérature afin de caractériser la qualité d'un instrument de mesure. La pertinence d'une telle section provient de l'existence de certaines ambiguïtés dans la terminologie. Nous poursuivons ensuite avec la présentation des critères de performances relatifs aux convertisseurs numériques de temps. Une fois ces caractéristiques permettant d'apprécier la qualité d'un convertisseur numérique de temps présentées, nous présentons une méthode d'interpolation fréquemment employée dans la littérature, consistant à utiliser un compteur binaire conjointement avec un interpolateur fin. À ce point, les 3 méthodes les plus fréquemment utilisées pour réaliser ces interpolateurs fins (sur FPGA) sont présentées, ainsi que les résultats obtenus pour différentes implémentations FPGA.

## 2.2 Résolution, Précision, et Exactitude

Dans cet ouvrage, les termes *résolution*, *précision*, et *exactitude* (*accuracy*) sont utilisés avec un sens bien précis. Néanmoins, les définitions de ces termes comportent certaines ambiguïtés. C'est ainsi que cette section propose une brève analyse des définitions de ces termes telles que retrouvées dans deux dictionnaires de renommé internationale (Merriam-Webster (2009), Kaplan (2004)). La pertinence d'une telle section, loin d'être anodine, est d'exposer les différents sens donnés à ces termes et de mettre en évidence certaines ambiguïtés quant à leurs définitions. L'objectif ainsi poursuivi est de permettre au lecteur d'apprécier pleinement les distinctions importantes qui existent entre ces termes, tels qu'employés dans ce travail.

Dans un premier lieu, voici les définitions des termes *precision* (précision), *resolution* (résolution), et *accuracy* (exactitude) tirées du dictionnaire de la langue anglaise Merriam-Webster (2009) :

**precision** : **1** : the quality or state of being precise : EXACTNESS.

**2 a** : the degree of refinement with which an operation is performed or a measurement stated – compare ACCURACY **2 b** : the accuracy (as in binary or decimal places) with which a number can be represented usually expressed in terms of the number of computer words available for representation <double precision arithmetic permits the representation of an expression by two computer words>. [...]

**precise** : **1** : exactly or sharply defined or stated. **2** : minutely exact.

**3** : strictly conforming to a pattern, standard, or convention. [...]

**exact** : **1** : exhibiting or marked by strict, particular, and complete accordance with fact or a standard. **2** : marked by through consideration or minute measurement of small factual details.

**sharp** : **1** : adapted to cutting or piercing : as **a** : having a thin keen edge or fine point **b** : briskly or bitingly cold [...]. **6 a** : terminating in a point or edge <sharp features> [...]

**resolution** : **1** : the act or process of resolving : as [...] **6 a** : the process or capability of making distinguishable the individual parts of an object, closely adjacent optical images, or sources of light. **b** : a measure of the sharpness of an image usually expressed as the total number or density of pixels in the image <a resolution of 1200 dots per inch>

**accuracy** : **1** : freedom from mistake or error : CORRECTNESS. **2 a** : conformity to truth or to a standard or model : EXACTNESS **b** : degree of conformity of a measure to a standard of a true value – compare PRECISION 2a.

Merriam-Webster (2009)

En deuxième lieu, les définitions de ces termes, tirées du dictionnaire sur l'ingénierie électrique et électronique Kaplan (2004), sont les suivantes :

**precision** : **1.** A measure of the repeatability of a given result or procedure, such as measurement. For example, a measurement made several times in which the same, or nearly the same value is obtained, indicates precise measurement. This does not necessarily mean that such measurement specify or approximate a real value, thus a precise measurement may not be accurate. Still, even in technical usage the term is often used synonymously with **accuracy**. **2.** The number of significant digits provided in a measurement or other value. The more significant digits, the more precise. [...]

**resolution** : Its abbreviation is **res**. **1.** The minimum difference between two values, quantities, or entities, which can be distinguished by, separated, or acted upon, by a detector, sensor, measuring device, or the like. Also, such differentiation. **2.** The smallest detail which can be distinguished by, or acted upon, by a detector, sensor, measuring device, or the like. Also, such differentiation. [...] **6.** The precision with which a quantity or value can be measured or indicated. [...]

**accuracy** : The extent to which a measured or calculated value approximates the real value. May be expressed as a percentage, as in accurate within 2%.

Kaplan (2004)

Ironiquement peut-être, le terme dont le sens semble être le moins précis est la précision. Dans le premier sens donné au mot dans le dictionnaire *Merriam Webster*, on indique que la précision est définie comme étant quelque chose d'exactement défini, ce qui renvoie directement à la notion d'exactitude (*accuracy*), ou alors comme quelque chose de défini de manière pointue, ce qui renvoie plutôt à la notion de chiffres significatifs. Cette notion correspondant au deuxième sens donné au terme précision dans Kaplan (2004). En définissant le terme précision comme quelque chose de défini de manière pointue, la définition est également en accord avec le premier sens donné au terme précision dans Kaplan (2004). Dans le deuxième sens donné au mot précision dans le dictionnaire *Merriam Webster*, en 2.a) on indique le degré de raffinement avec lequel une opération est réalisée ou une mesure est énoncée, ce qui renvoie en quelques sortes à la notion d'incertitude compatible avec le premier sens donné au terme précision dans Kaplan (2004). En 2.b), on définit la précision comme

l'exactitude avec laquelle un nombre peut être représenté (précision double ou simple en calcul sur ordinateur par exemple). On observe ainsi que la définition du terme précision dans Merriam-Webster (2009) renvoie aussi bien à la notion de précision telle que définie dans Kaplan (2004), qu'à la notion d'exactitude. Tout cela explique bien pourquoi ces deux termes sont souvent utilisés comme synonymes.

Pour ce qui est de la définition du terme résolution, le sens 6.a) donné dans Merriam-Webster (2009) apparaît être en accord avec les deux premiers sens tirés de Kaplan (2004), faisant référence au plus petit détail pouvant être distingué. Le mot résolution possède toutefois plusieurs sens qui ne sont pas de nature scientifique ou technologique.

Bien qu'une ambiguïté liée à l'utilisation des termes *précision* et *résolution* puisse exister, dans le domaine de la métrologie il apparaît dans la littérature (Webster (1999a), Webster (1999b), AFNOR (1994)) que ces termes sont employés avec leur premier sens, tels qu'énoncés dans Kaplan (2004). À cet effet, une analogie pour illustrer la signification de ces termes au moyen d'une cible est fréquemment employée. La figure 2.1 illustre une telle analogie, où la résolution est représentée par la largeur des anneaux de la cible. La figure 2.1(a) illustre une bonne précision (fidélité) des mesures puisque ces dernières sont fortement regroupées. Or, bien que les valeurs obtenues dans ce cas d'une mesure à l'autre soient très similaires, en moyenne la valeur est considérablement éloignée du centre de la cible. La figure 2.1(b) illustre le concept de *justesse*. C'est à dire qu'en moyenne, la valeur obtenue est centrée sur

FIGURE 2.1 Analogie de la cible pour représenter la précision (a), la justesse (b) et l'exactitude (c) d'un instrument de mesure.

la cible (croix), mais sans pour autant que la précision soit bonne, de sorte que les mesures individuelles diffèrent fortement les unes des autres. L'exactitude est finalement représentée à la figure 2.1(c), par une combinaison de justesse et de précision, de sorte à ce que d'une mesure à l'autre, l'erreur avec le centre de la cible est faible.

## 2.3 Critères de performance d'un TDC

Un convertisseur numérique de temps est caractérisé par plusieurs paramètres, et comme c'est généralement le cas pour tout circuit électronique, certains avantages sont souvent obtenus au détriment d'une dégradation de certains autres paramètres. Il importe donc de bien comprendre leurs significations pour en avoir une appréciation juste. Les caractéristiques les plus importantes et les plus fondamentales d'un convertisseur numérique de temps sont les suivantes :

- La résolution (du bit le moins significatif)

- La précision des mesures

- L'exactitude des mesures

- La non-linéarité, différentielle et intégrale

- Le temps mort

- La durée maximale d'une mesure

- La largeur minimale d'impulsion

Sans surprises, les termes résolution, précision, et exactitude se retrouvent parmi les critères de performance les plus fondamentaux d'un TDC. Puisque le TDC est un instrument de mesure, ce travail utilise ces termes avec leurs sens tel que couramment utilisés dans le domaine de la métrologie (illustrés par l'analogie avec la cible de la Figure 2.1). Bien que le sens donné à chacun de ces mots dans ce travail ait été exposé à la section précédente, la signification de ces termes dans le cas précis de la caractérisation d'un TDC est ici présentée, en plus des définitions des autres paramètres mentionnés ci-haut.

La *résolution* du bit le moins significatif détermine le pas de quantification de l'interpolateur de temps utilisé. La résolution correspond ainsi au plus petit interval de temps pouvant être **théoriquement** résolu par un TDC pour une mesure donnée. Typiquement la précision d'un TDC devrait être meilleure que sa résolution, sans

quoi le seul intérêt lié à la haute-résolution est une erreur de quantification réduite (voir Kalisz, 2003).

La *précision* est définie par l'écart type des mesures réalisées en mesurant des temps d'arrivées d'impulsions équidistantes. La précision est fortement liée à la qualité du circuit, ainsi qu'à la qualité de l'horloge de référence qui est utilisé par ce dernier, notamment lorsque les intervalles de temps sont grands. En effet, en mesurant des impulsions équidistantes, une certaine variation est observée, ce qui est attribuable en partie à la gigue de l'horloge, mais également à d'autres phénomènes aléatoires (non-contrôlables) comme le bruit thermique par exemple. On prend ainsi généralement l'écart type par rapport à la moyenne comme critère de précision d'un TDC. La précision est également utilisée afin de déterminer le plus petit interval de temps pouvant être **réellement** résolu par un TDC pour une mesure donnée (chiffres significatifs).

L'*exactitude* d'un TDC définit l'erreur séparant la valeur d'une mesure de la quantité réelle qui est mesuré. L'exactitude est ainsi affectée par les variations aléatoires autour d'une valeur moyenne (précision), en plus de la présence d'erreurs systématiques occasionnant un biais entre la valeur de la moyenne mesurée et la valeur réelle qui est mesurée (justesse). L'exactitude peut ainsi être considérablement améliorée par compensation des erreurs systématiques, suite à un processus de calibration.

La *non-linéarité différentielle* du TDC mesure la déviation d'un pas de quantification par rapport à la valeur idéale correspondant à celle du bit le moins significatif. Par exemple, dans un TDC avec une résolution de 100ps, il est peu probable que chacun des bits soit distancé d'exactement 100ps. On aurait certains espacement de 110ps, d'autres de 90ps, ce qui correspondrait à des non-linéarités différentes de  $\pm 10\text{ps}$  pour ces bits respectifs. Afin de mesurer la non-linéarité différentielle, une méthode très répandue consiste à injecter des impulsions dont les espacements temporels sont pseudo-aléatoires. Considérant un nombre élevé d'impulsions, la taille des sous-divisions peut être estimée en observant le nombre d'impulsions ayant été détectées dans chacune des divisions de l'interpolateur par rapport au nombre total d'impulsions.

La *non-linéarité intégrale* fait plutôt référence à la déviation par rapport à la droite idéale qui représente la relation d'entrée et sortie de l'interpolateur (voir Dyer, 2001). Cette dernière est simplement obtenue en intégrant les erreurs différentielles des divisions.

Le *temps mort* indique le taux maximal auquel les impulsions peuvent se présenter à l'entrée du convertisseur (voir Hewlett Packard, 1997). Dans le cas d'un convertisseur mesurant le temps entre une impulsion de départ et une impulsion d'arrêt, le temps mort correspond au temps qui doit séparer l'arrivée d'une impulsion d'arrêt avec l'arrivée de la prochaine impulsion de départ.

La *durée maximale d'une mesure* correspond simplement à la distance maximale séparant deux impulsions qui peut être mesurée. Lorsque le convertisseur fonctionne avec un signal de départ et d'arrêt, ce paramètre indique le temps maximal pouvant être mesuré entre ces deux impulsions.

La *largeur minimale d'impulsion* correspond à la plus petite taille d'une impulsion qui peut être perçue par le circuit de conversion. Ce paramètre est important car toute impulsion de taille inférieure sera ou pourrait être ignorée, faussant aussi les mesures.

## 2.4 Méthode d'interpolation

Afin de réaliser des mesures qui s'étendent sur une longue période de temps avec de fines résolutions et de hautes précisions, une méthode d'interpolation de temps consiste à utiliser un compteur binaire offrant une résolution grossière et une grande portée, conjointement avec un ou des interpolateurs fins offrant de très fines résolution sur de courtes portées. La méthode la plus fréquemment employée est la méthode de Nutt (voir Dyer, 2001), illustrée en Figure 2.2, utilisant 2 interpolateurs fins. Le premier interpolateur est utilisé pour mesurer le court temps  $T_1$  séparant l'arrivée du signal de départ avec le front d'horloge montant suivant. Sur ce même front, le compteur binaire mesure le temps  $T_{12}$  jusqu'au prochain front montant d'horloge qui suivra l'arrivée du signal d'arrêt. Le deuxième interpolateur est utilisé pour mesurer le temps  $T_2$  séparant l'arrivée du signal d'arrêt avec ce dernier front d'horloge. On

obtient alors que le temps de mesure entre l'arrivée des signaux de départ et d'arrêt est donné par :

$$T = T_1 + T_{12} - T_2 \quad (2.1)$$

Cette méthode permet ainsi d'étendre la portée de mesure d'un interpolateur fin tout en conservant sa résolution et précision. Toutefois, d'autant plus que les mesures sont grandes, l'influence de la gigue (*jitter*) de l'horloge pourra réduire la précision de ces dernières.

FIGURE 2.2 Méthode d'interpolation de Nutt, utilisant un compteur binaire et deux interpolateurs fins.

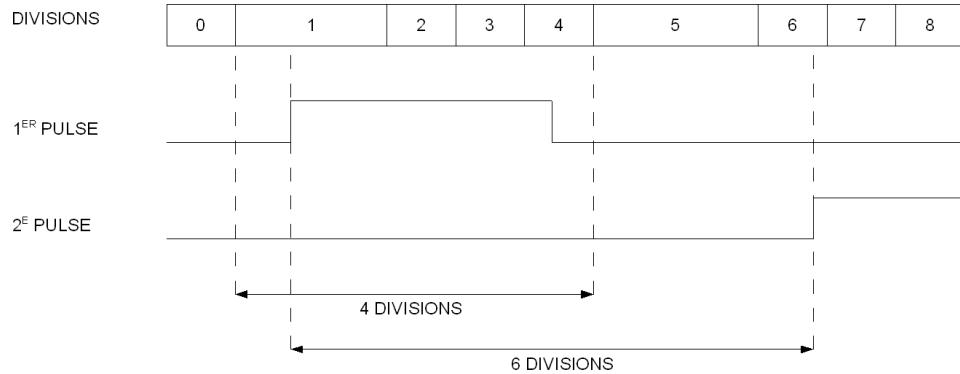

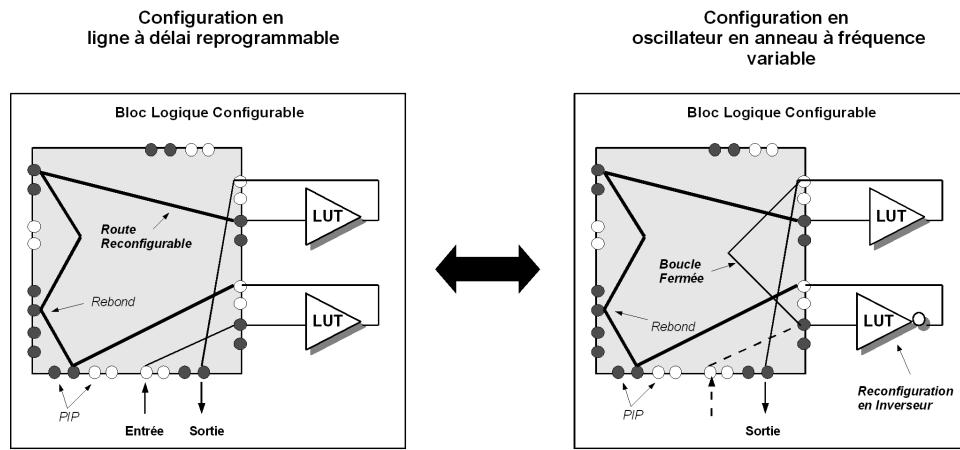

## 2.5 Architecture basée sur la méthode du vernier avec deux oscillateurs

Afin de produire une interpolation avec une fine résolution, la méthode du vernier se base sur l'utilisation de deux oscillateurs pouvant être démarrés et arrêtés, dont les périodes sont sensiblement différentes. La résolution qu'il est possible d'atteindre avec cette méthode correspond en fait à la différence entre les périodes des deux oscillateurs. Tel qu'illustré à la Figure 2.3b, chacun de ces oscillateurs est connecté à un compteur binaire, de même qu'à un circuit pouvant détecter la coïncidence des fronts montants des horloges produites par chaque oscillateur.

Lors de son opération, le signal de départ vient activer l'oscillateur le plus lent tandis que le signal d'arrêt vient activer l'oscillateur le plus rapide. Ainsi, lorsqu'une coïncidence est détectée entre les fronts montants des deux oscillateurs, ceux-ci sont

FIGURE 2.3 Diagrammes temporels (a), et architecture (b) de l'interpolator basé sur la méthode du vernier avec deux oscillateurs.

désactivés de sorte à arrêter l'incrémentation des compteurs binaires. Maintenant, soit  $\tau_1$  et  $\tau_2$  les périodes des oscillateurs, avec  $\tau_1 < \tau_2$ , et  $n_1, n_2$  les valeurs des compteurs binaires, il est possible de montrer (Figure 2.3a) que le temps mesuré sera :

$$T = (n_1 - 1)\tau_1 - (n_2 - 1)\tau_2 \quad (2.2)$$

De même, lorsque les mesures réalisées sont inférieures à  $\tau_2$ ,  $n_1 = n_2$  et le temps mesuré est donné par :

$$T = (n_1 - 1)(\tau_1 - \tau_2) \quad (2.3)$$

On peut alors remplacer le circuit de détection de coïncidences par un détecteur de changement de phase, et se contenter d'un seul compteur binaire. Ainsi lorsque

le signal d'horloge rapide, initialement en retard, devance l'horloge plus lente, les oscillateurs sont arrêtés et la mesure est donnée par l'Équation 2.3.

Un des grands avantages offert par cette méthode est sans contredit sa simplicité ainsi que le faible coût matériel qui lui est associé, résultant en un circuit de très petite taille. Cependant cette méthode possède certains inconvénients. D'abords, il est essentiel que les oscillateurs employés soient stables, sans quoi la fiabilité des mesures ne peut être assurée, surtout lorsque les mesures s'étendent sur une longue durée (longue durée séparant l'arrivée des impulsions de départ et d'arrêt). Un autre inconvénient majeur avec cette approche est le temps mort du convertisseur. En effet, pour des périodes  $\tau_1$  et  $\tau_2$ , on obtient que dans le pire cas (voir Kalisz, 2003), le temps de conversion est donné par :

$$T = \frac{(\tau_1\tau_2)}{(\tau_1 - \tau_2)} \quad (2.4)$$

En observant que le dénominateur correspond à la résolution, on voit qu'il existe un compromis entre la résolution et le temps de conversion.

Utilisant cette approche, des chercheurs de l'université Kun Shan de Taiwan ont publié en 2006 des résultats quant à la réalisation de deux oscillateurs à anneau modifiés avec des différences de périodes aussi faibles que 30ps (voir Lin *et al.*, 2006). Afin de pouvoir en contrôler le départ et l'arrêt, ces oscillateurs sont conçus avec des portes de type ou-exclusif plutôt que des inverseurs, tel qu'illustré à la Figure 2.4, et leurs périodes se situent autour de 4ns. L'obtention de telles différences de périodes se base sur l'utilisation astucieuse des contraintes de placement et les différences de délais produits lors de la phase de placement et routage avec les outils de synthèse de Xilinx en ciblant les FPGA Spartan-3 et Virtex-4. Les auteurs proposent également un circuit pour la détection de phase, cependant aucun résultat expérimental supplémentaire d'implémentation pour le convertisseur numérique de temps n'est présenté.

Dans une conférence sur la science nucléaire, en 2007, une équipe de chercheurs de l'Institut de Technologie Industrielle de Corée à également publié des résultats de travaux similaires (voir Jin et Moon, 2007). Les deux oscillateurs produits avec des périodes de 2,25ns et 2,34ns permettent d'obtenir une résolution inférieure à 100ps. En activant les oscillateurs, une détection de coïncidence à lieu toutes les 61ns, les compteurs binaires indiquant alors des valeurs de 26 et 27.

FIGURE 2.4 Oscillateur à anneau utilisant une porte XOR proposé par Lin *et al.* (2006).

## 2.6 Architecture basée sur la ligne à délais simple

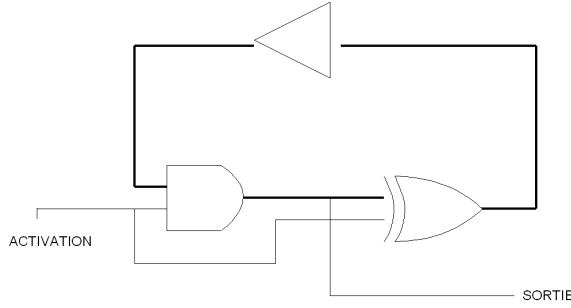

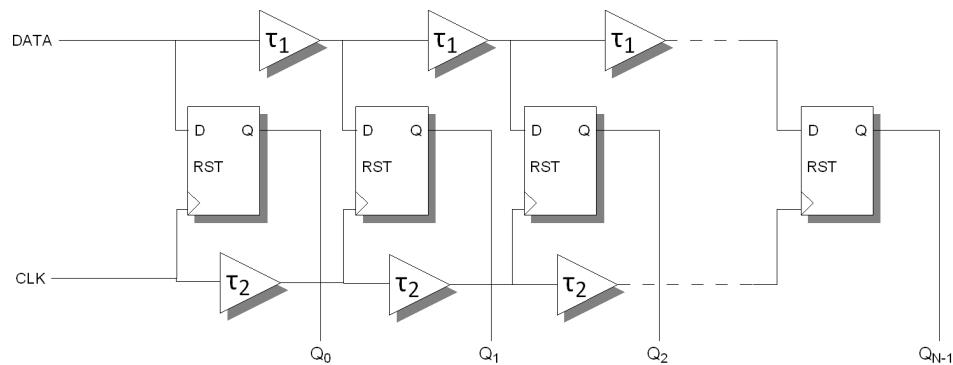

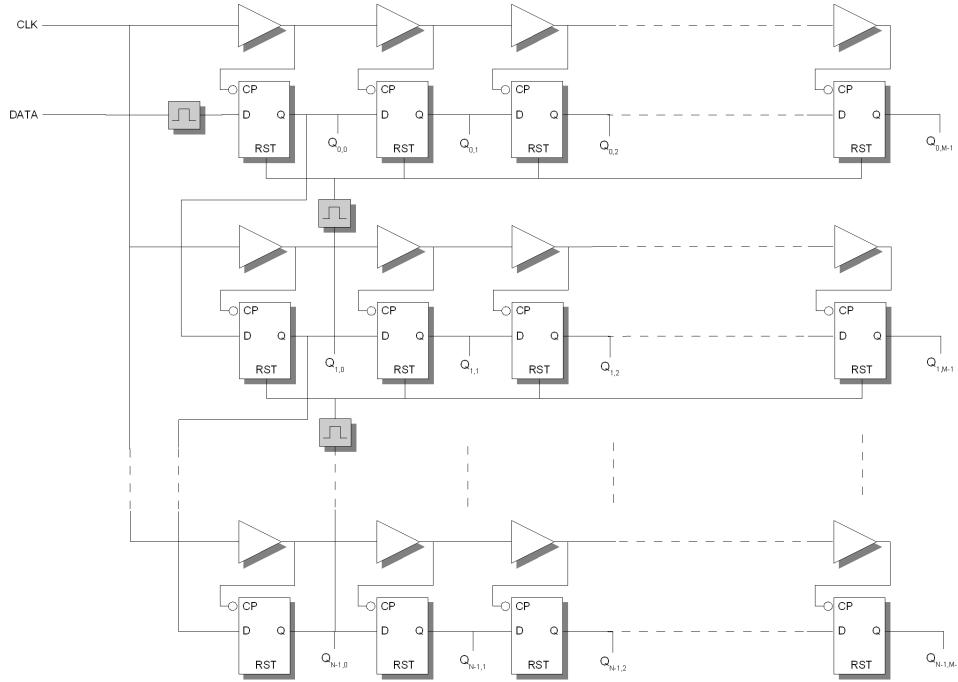

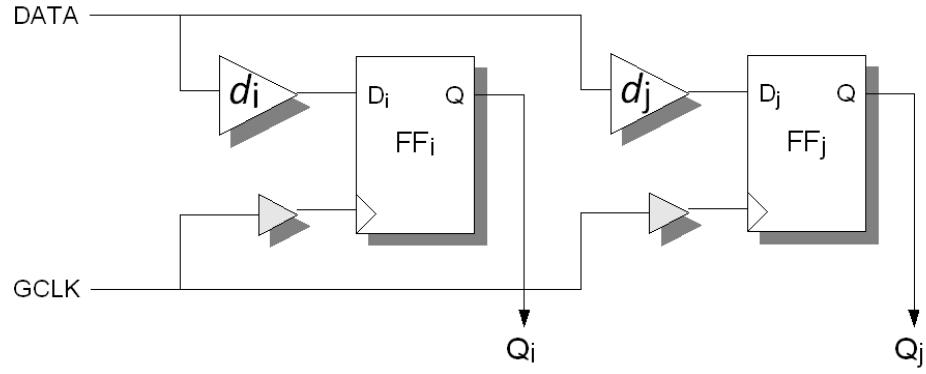

La méthode d’interpolation basée sur la ligne à délais simple « sur écoute » est sans aucun doute la plus intuitive. En plus d’être la méthode la plus utilisée, c’est celle qui produit les meilleurs résultats d’implémentations FPGA. L’idée consiste à diviser une ligne à délais en  $N$  délais égaux de sorte à produire autant de copies retardées du signal. En échantillonnant ces copies au même moment avec une horloge par exemple, on mémorise alors différents points (Figure 2.5) équidistants les uns des autres du signal source. Pour autant que la ligne à délais produise un retard total au moins aussi grand que la période d’horloge, on parvient effectivement à accroître la résolution d’échantillonnage d’un facteur  $N$ . La Figure 2.6 illustre un circuit permettant ce type d’interpolation fine. Dans un convertisseur numérique de temps fonctionnant avec des signaux de départ et d’arrêt, il serait suffisant de remplacer le signal data de la figure par le signal de départ, et de remplacer l’horloge par le signal d’arrêt. Une autre variante de ce circuit est de placer la ligne à délais chaînés sur le signal d’horloge plutôt que le signal de donnée, ce qui est équivalent d’un point de vue fonctionnel.

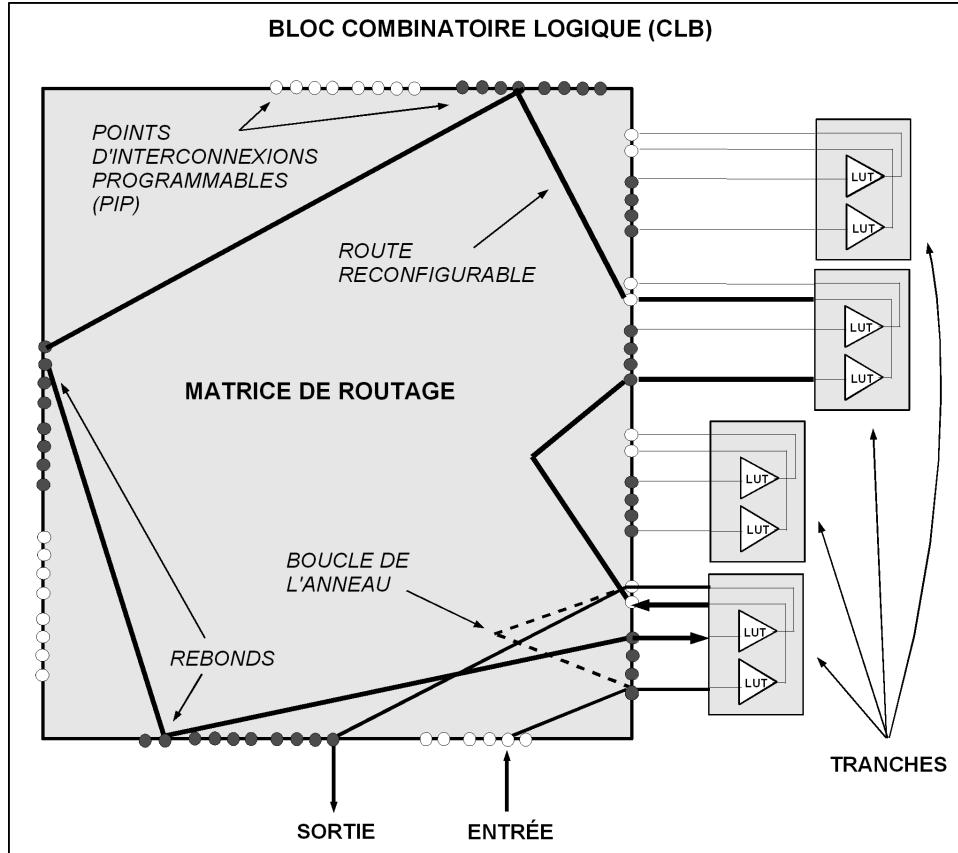

Dans une telle architecture d’interpolator, la résolution obtenue correspond au délai d’un maillon de la chaîne. Dans un FPGA, l’utilisation de tampons (*buffers*) dans la chaîne pose toutefois problème puisque ceux-ci, réalisés au moyen de tables de correspondances, possèdent alors un délai de l’ordre de quelques centaines de picosecondes, sans compter le délai de routage des connexions entre ces derniers. Un des problèmes importants avec les délais liés au routage entre les éléments logiques d’un FPGA est que ces derniers sont généralement produits de manière imprévisible

FIGURE 2.5 Échantillonnage de copies régulièrement retardées d'un même signal pour augmenter la fréquence d'échantillonnage efficace.

(hors du contrôle de l'usager) par les outils de synthèses, pouvant ainsi entraîner d'importantes irrégularités. Cela s'explique notamment par le fait qu'il existe un nombre important de routes pouvant servir à relier une sortie d'un élément logique à l'entrée d'un autre via le système d'interconnexions programmables. Il est bien entendu possible de router manuellement ces interconnexions, mais l'effort associé en sera d'autant plus important, et cette approche ne permet toujours pas de tenir compte des variations de délais dues au procédé de fabrication et à la température. De plus, le routage au travers d'un système d'interconnexion programmable entraîne des délais non-négligeables pouvant limiter la résolution atteignable, puisque cette programmabilité est elle-même obtenue par une multitude de multiplexeurs.

Il existe toutefois des types d'interconnexions dédiées dans les FPGA modernes permettant de chainer la logique avec des délais réduits. Deux exemples répandus et bien connus sont la chaîne de sommes de produit, et la chaîne de retenues qui peut aussi bien être utilisée pour la logique arithmétique que pour l'expansion de produits. Du point de vue du concepteur de ligne à délais chaînés, ces structures présentent un double avantage : d'une part, ces structures dédiées permettent d'obtenir de plus faibles délais que ceux obtenus au travers du système d'interconnexions program-

FIGURE 2.6 Architecture d'un interpolateur basé sur une ligne à délais sur écoute.

mables, et d'autre part, puisqu'elles ne sont pas programmables, elles permettent d'obtenir une meilleure régularité. Une conception soignée, ciblant ces structures de routage pour l'implémentation d'une ligne à délais chainés, peut ainsi mener à des résolutions intéressantes dans un FPGA.

Utilisant cette approche, en 2003 une équipe de chercheurs du laboratoire de l'accélérateur national de Fermi (*Fermilab*) a développé un convertisseur numérique de temps avec une résolution de 400ps et une erreur maximale sur les mesures de 300ps (voir Wu *et al.*, 2003). Leur implémentation se base sur la chaîne d'expansion logique rapide présente dans le FPGA ACEX 1K d'Altera, divisée en 48 chainons. Les tests ont ensuite été effectués avec le convertisseur cadencé à des fréquences d'horloges de 35MHz et 70MHz. La précision mesurée se situe à moins de 0,5 LSB (bit le moins significatif), toutefois le graphe de non-linéarité différentielle présente des pics réguliers (0,5 à 0,6 LSB) toutes les 8 divisions. Cette observation est facilement expliquée par les sauts entre les différents blocs logiques (Logic Array Block) qui impliquent un délai plus long.

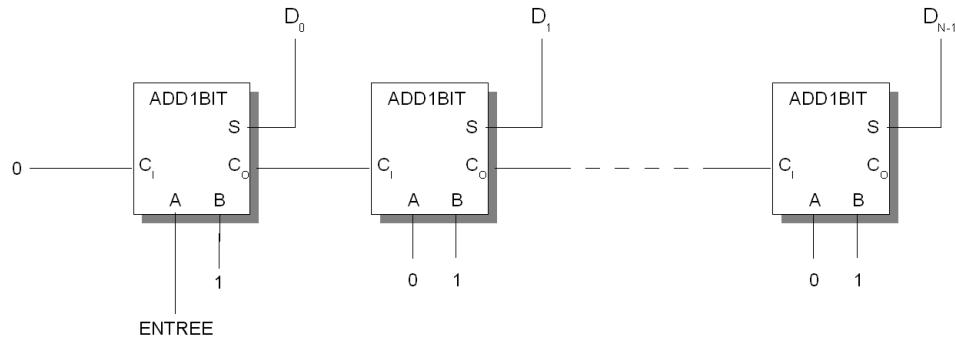

En 2006, une équipe de recherche du laboratoire d'électronique rapide de l'Université de Science et Technologie de Chine (USTC) publie une autre architecture intéressante (voir Song *et al.*, 2006). L'idée consiste à utiliser la chaîne de retenue rapide d'un additionneur afin de produire la ligne à délais (Figure 2.7). La résolution ainsi obtenue est équivalente au délai de propagation de la retenue au travers un additionneur complet de 1bit. L'architecture de l'interpolator proposé a été implémenté dans un FPGA ACEX 1K d'Altera ainsi que dans un Virtex-II de Xilinx.

Avec l'implémentation sur le FPGA d'Altera, la résolution obtenue est de 112,5ps avec une précision (déviation standard) de 129,4ps, soit de 91,5ps rms. En observant le graphe de non-linéarité différentielle obtenu, on retrouve le même phénomène de pics périodiques et cette dernière est comprise entre -0,416 et +0,783 divisions. La non-linéarité intégrale est ainsi comprise entre -0,567 et +0,687 divisions. Pour l'implémentation sur le FPGA de Xilinx, la taille d'une division est de 69,5ps et la précision obtenue est de 93,1ps, soit 65,8ps rms. En ce qui a trait aux graphes de non-linéarité différentielle et intégrale, le premier offre un écart de -0,954 à +1,051 divisions, et le deuxième un écart allant de -2,003 à +1,855 divisions. Sur les deux implémentations, le temps mort peut être réduit à un seul cycle d'horloge, soit 5ns où 10ns respectivement.

FIGURE 2.7 Implémentation d'une ligne à délais sur écoute avec la chaîne de retenue d'un additionneur proposée par Song *et al.* (2006).

En 2009, une équipe de l'École Polytechnique de Lausanne a publié des résultats d'une implémentation d'un TDC basée sur la chaîne de retenue d'un FPGA fabriqué en technologie 65nm (Virtex-5) (voir Favi et Charbon, 2009). Leurs résultats font état d'une résolution de 17ps avec une précision d'au moins 25ps. La ligne à délais contient 207 divisions et le circuit opère à une fréquence de 300MHz. À cette résolution, la non-linéarité différentielle observée se situe entre -1 et 3,55 divisions, tandis que la non-linéarité intégrale est comprise entre -3 et 2,58 divisions. Ces résultats mettent en évidence une des grandes forces de cette architecture : l'implémentation bénéficie directement des nouveaux procédés de fabrication des FPGA modernes, qui offrent typiquement des délais réduits (portes logiques et interconnexions) et des fréquences d'opération supérieures (requiert une portée dynamique réduite).

Voulant s'attaquer au problème de non-linéarité des architectures basées sur les structures d'interconnexions dédiées pour le chaînage de logique sur FPGA, en 2008 des chercheurs du laboratoire Fermi ont publié une méthode originale permettant de sous-diviser les divisions relativement larges qui apparaissent périodiquement dans ces implémentations (voir Wu et Shi, 2008). La méthodologie dénommée *Wave Union* (union d'onde) consiste en l'envoi d'un train d'impulsions dont l'espacement est connu plutôt que d'une seule impulsion, avec pour objectif d'assurer qu'une de ces impulsions voit systématiquement sa transition avoir lieu dans une des divisions plus fine. La Figure 2.8 illustre le principe avec un train de 2 impulsions, on y voit bien qu'en ajustant soigneusement la distance entre les impulsions du train, considérant la présence périodique de grandes divisions, si une des impulsions tombe dans une division plus large, alors l'autre a lieu dans une division normale.

FIGURE 2.8 Méthode d'union d'onde attaquant le problème des divisions larges.

Ainsi cette méthode permet de sous-diviser les divisions très larges, ou alors d'améliorer la sensibilité du convertisseur numérique de temps. Il est important de noter toutefois que cette amélioration de la résolution se fait au dépend du temps mort du convertisseur, puisque pour la mesure du temps d'arrivée de chaque impulsion en entrée, la ligne à délais doit être monopolisée par chacun des « wagons » du train d'impulsions émis en substitution. Donc, l'accroissement du nombre d'impulsions augmente la résolution des mesures en même temps qu'il augmente le temps mort du convertisseur. Ainsi les auteurs présentent deux variantes de leur architecture : la première utilise un train de 2 impulsions et la deuxième un train de 16 impulsions.

Dans leur première implémentation sur un FPGA Cyclone II d'Altera, le train d'impulsions se répète à une fréquence de 53,11MHz, alors que le convertisseur numérique est cadencé à 400MHz et fonctionne avec 64 divisions. Au départ, la résolution obtenue se situe à 60ps, et la précision atteinte est de 58ps. En employant la technique d'union d'ondes, la résolution efficace est réduite à aussi peu que 30ps avec une précision de 25ps, mais le temps mort passe de 2,5ns à 5ns. Dans leur deuxième implémentation, en augmentant le nombre d'impulsions la précision est réduite à 10ps, alors que le temps mort passe de 2,5ns à 45ns.

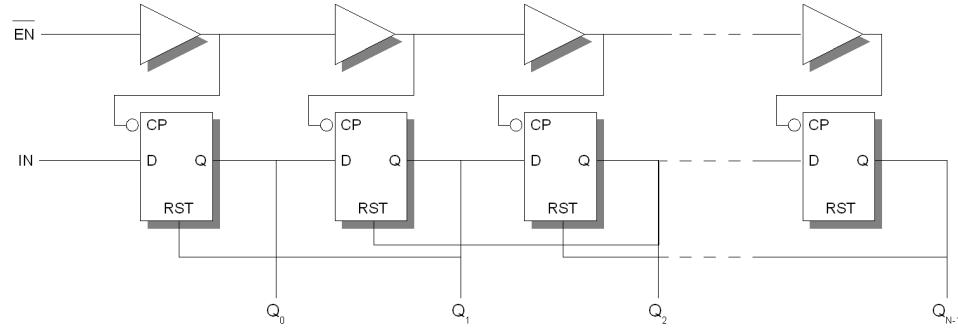

## 2.7 Architecture basée sur les lignes à délais de type vernier