**Titre:** Modèle de placement pour les architectures nano-composantes

Title:

**Auteur:** Maimouna Amadou

Author:

**Date:** 2009

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Amadou, M. (2009). Modèle de placement pour les architectures nano-composantes [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/237/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/237/>

PolyPublie URL:

**Directeurs de recherche:** Gabriela Nicolescu, & Hanifa Boucheneb

Advisors:

**Programme:** Génie informatique

Program:

UNIVERSITÉ DE MONTRÉAL

**MODÈLE DE PLACEMENT POUR DES ARCHITECTURES NANO -

COMPOSANTES**

MAIMOUNA AMADOU

DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

DÉCEMBRE 2009

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

MODÈLE DE PLACEMENT POUR LES ARCHITECTURES NANO-COMPOSANTES

présenté par : AMADOU Maimouna

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. BOIS Guy, Ph. D., président

Mme NICOLESCU Gabriela, Doct., membre et directrice de recherche

Mme BOUCHENEH Hanifa, Doctorat., membre et codirectrice de recherche

M. DAVID Jean-Pierre, Ph. D., membre

## DÉDICACE

*A mes parents

Amadou garba & ramatou moussa*

## **REMERCIEMENTS**

J'aimerais, en premier lieu, remercier chaleureusement ma directrice de recherche, Professeur Gabriela Nicolescu. Je lui suis très reconnaissante pour m'avoir accueillie dans son laboratoire de recherche. Ses orientations et son encadrement m'ont permis de travailler sur ce projet qui n'aurait pas aussi bien abouti sans son aide précieuse. J'ai énormément apprécié sa patience, sa compréhension et la confiance qu'elle a placée en moi.

Mes sincères remerciements vont également à ma co-directrice, professeur Hanifa Boucheneb pour m'avoir accueillie, conseillée et guidée depuis mon arrivée à l'école polytechnique. J'ai apprécié son encadrement, son écoute et sa compréhension.

Je voudrai remercier le professeur Ian O'Connor pour l'intérêt qu'il a accordé à mes travaux. Il m'a réservé un accueil chaleureux au sein de son laboratoire et a mis à ma disposition toutes les ressources nécessaires pour mener à bien ce projet. J'ai beaucoup apprécié son encouragement, son encadrement et son aide tout au long de ces travaux.

Je suis très reconnaissante envers les professeurs Guy Bois et Jean-Pierre David pour avoir accepté de faire partie de ce jury.

Je remercie vivement Alain, Azzedine, Bruno, Luiza, Sébastien et Taieb, mes collègues du groupe PIM, pour leurs suggestions, encouragements et conseils en tout genre.

Mes derniers remerciements, mais pas les moindres, vont à ce à qui je dois tout : mes parents, frères (Mahamadou, Boubacar) et sœurs (Fatouma, Mariama, Aminata, Rabiatou, Halimatou) ainsi que mes amis (Florence, Sidy Kounta, Gerry, Mayi, William, Fatoumata). Ils m'ont toujours soutenue, appuyée et poussée en avant tout au long de ce projet.

## RÉSUMÉ

Depuis la création de l'industrie des transistors CMOS, on assiste à un développement sans précédent de la miniaturisation. La ITRS prévoit la limite des technologies basées sur le CMOS en 2020. Dans ce contexte, apparaît de nouvelles disciplines, au cœur de la nanotechnologie, qui permettent de définir de nouvelles technologies permettant de compléter et/ou remplacer les transistors CMOS. Ces nouveaux transistors ouvrent la voie vers un nouveau paradigme *d'architectures nano-composantes*. Ces architectures ont trois principales caractéristiques :

- (i) Les cellules logiques sont dynamiquement reconfigurables. Ce qui donne la possibilité d'exécuter en pipeline plusieurs fonctions différentes;

- (ii) La granularité est très fine. Ceci impose de considérer l'extensibilité des outils qui permettront l'exploitation de ces architectures;

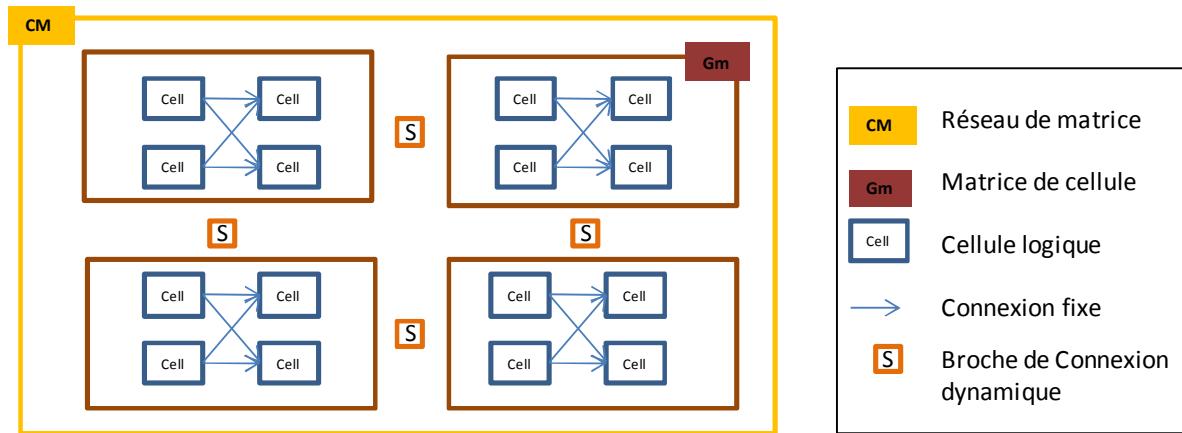

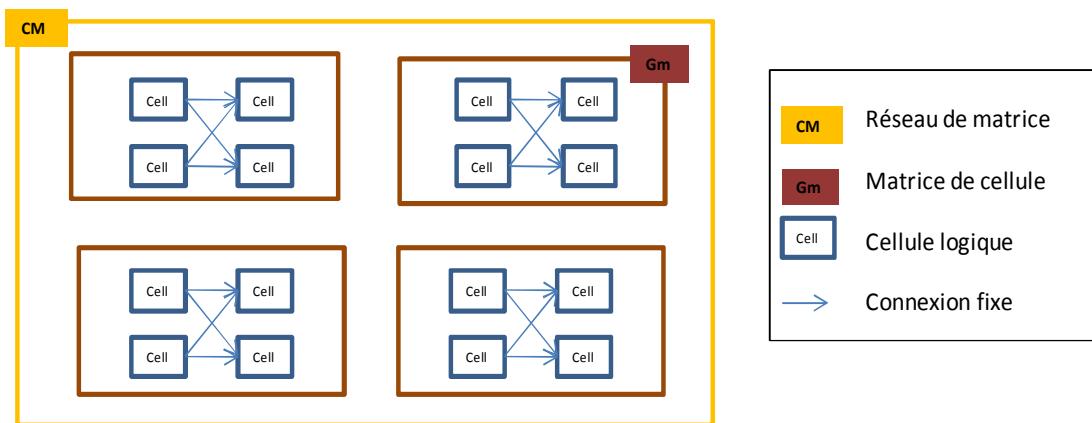

- (iii) Elles ont une structure hiérarchique particulière : Dans les architectures nano-composantes les cellules logiques sont organisées en matrices avec des connexions statiques et les matrices en réseau de matrices avec des connexions dynamiques. Ces architectures peuvent alors être paramétrées en fonction de la taille des matrices (nombre de cellules) et de la taille du réseau (nombre de matrices).

Pour prouver l'efficacité des architectures nano-composantes, il va falloir envisager la réalisation physique de systèmes complexes très performants basés sur ces technologies ainsi que l'utilisation de ces nano-systèmes. Comme l'accès au prototypage est très difficile et qu'il est souhaitable de réduire le temps de production des systèmes, la définition de nouveaux outils de conception assistée par ordinateur (CAO) s'avère nécessaire. Plusieurs outils CAO permettant la définition de systèmes basés sur les architectures conventionnelles existent. Cependant, ces outils ne prennent pas en compte les caractéristiques des architectures nano-composantes.

L'objectif de ce projet de recherche est d'aider à la conception de systèmes basés sur les architectures nano-composantes plus spécifiquement de définir un modèle de placement qui permettra :

- (i) de placer des applications sur les architectures nano-composantes;

- (ii) d'explorer l'espace de solutions de conception défini par les paramètres des architectures, et

- (iii) d'optimiser quatre métriques importantes : le temps d'exécution de l'application, le coût de communication, le coût de reconfiguration et le nombre de cellules inactives.

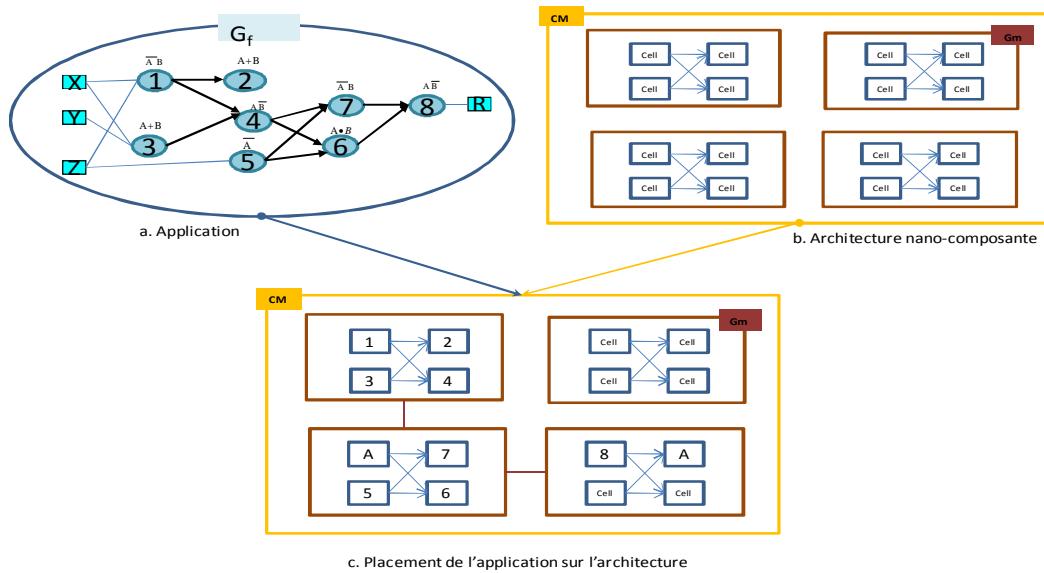

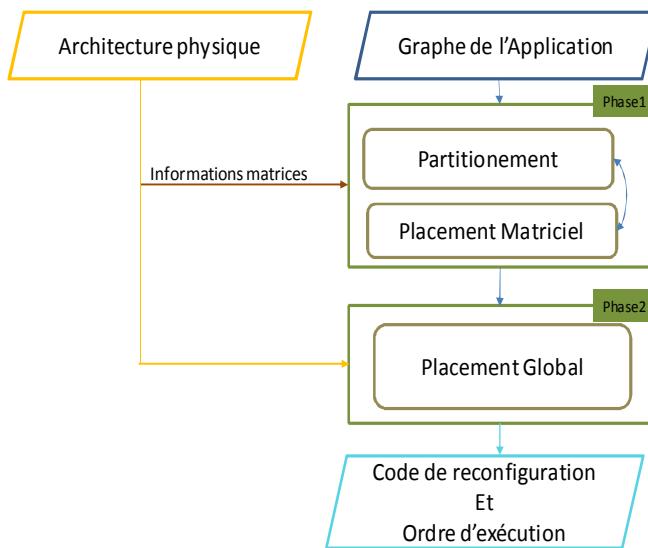

Le modèle proposé, dans ce travail, a été défini en utilisant la théorie des graphes et les algorithmes génétiques. Il est réalisé en deux parties utilisant trois méthodes. Dans la première partie, l'application à placer est divisée en sous-fonctions en utilisant une méthode de partitionnement définie avec les concepts de théorie des graphes, puis la transposition de chaque sous-fonction sur une matrice est estimée en utilisant une méthode d'assignation matricielle définie avec les concepts de théorie des graphes. La seconde partie du modèle consiste à déterminer le placement global de toutes les sous-fonctions sur le réseau de matrices en utilisant une méthode de placement global exploitant les algorithmes génétiques.

Dans ce mémoire, le modèle de placement a été testé sur sept cas de test. L'analyse des résultats obtenus a permis de voir qu'on peut atteindre, en moyenne, 60 % de taux d'occupation globale pour un partitionnement sur des architectures ayant des matrices de 16 cellules. L'expérimentation de placement global nous a permis d'optimiser le temps d'exécution des applications. Nous avons également pu définir des relations entre les différentes métriques de manière à aider dans les choix de compromis entre les métriques lors du paramétrage des architectures.

## ABSTRACT

International Technology Roadmap for Semiconductors (ITRS) predicts that CMOS devices will reach their limits in 2022. Consequently, new devices and more efficient technologies are required. In this context, many efforts have been made to extend or replace conventional, CMOS devices. Some devices based on Field Effect Transistor (FET) nanotechnology such as the Dual Gate Carbon NanoTube FET (DG-CNTFET), the Nano Wire FET (NWFET) or the Grapheme FET (GFET) are promising candidates to replace CMOS devices. They lead to define new paradigm of non-conventional architectures (so called *nano-component architecture*). Nano-component architectures have three main characteristics:

- (i) The logic cells are dynamically reconfigurable. This characteristic allows performing pipeline on several different functions;

- (ii) The granularity is ultra-fine (at most 2-bit operation). This characteristic implies to take into consideration scalability to exploit those architectures;

- (iii) The logic cells are organized with hierarchical structure and connectivity restrictions. In this structure, cells are organized in matrix and the matrices are organized in cluster.

Exploiting those characteristics, nanoarchitecture are expected, compared to conventional architectures, to reduce the area and the cost and to improve the performance of a broad range of applications. In order to explore the potential of nano-architecture, new CAD tools are required. Those tools must take into account many parameters in nano-architecture definition: the number of cell in matrices, the number of matrices in cluster, the hierarchical structure, the connectivity restrictions, the fine granularity, the high reconfiguration, the pipeline and parallel execution. Although many CAD tools defined for conventional architecture have been proposed, they do not take into consideration nano-architecture parameters.

This research project aims to explore the system-level potential for nano-architectures; more specifically the aim is to define a mapping model that enables:

- (i) An automatic application partitioning and mapping for nano-architecture;

- (ii) The exploration of the design space defined by the nano-architecture parameters;

- (iii) The optimization of several metrics: the computation speed, the communication cost, the reconfiguration cost and the number of non-used logical cells.

The proposed model is defined using the theory of graph and genetic algorithm. It is performed in two main parts accomplished through three complementary methods. In the first part, the application to map is partitioned into a set of sub-functions using a *partitioning method*. Each sub-graph resulting from the partitioning is mapped onto a matrix using a *matrix mapping method*. The second part of the proposed model, maps the set of sub-functions onto the cluster of matrices using a *global mapping method*.

In this work, seven test cases have been studied to validate the mapping model. Our results illustrate that application partitioning allows exploiting, in average, 60% of 16 cell matrix. We also observe that the application of global mapping enable a great optimization of the metrics (it gives the best execution time). Finally, the relations between metrics have been discussed in order to make a good compromise when performing application mapping onto nano-architectures.

## TABLE DES MATIERES

|                                                                                      |      |

|--------------------------------------------------------------------------------------|------|

| DÉDICACE .....                                                                       | III  |

| REMERCIEMENTS .....                                                                  | IV   |

| RÉSUMÉ .....                                                                         | V    |

| ABSTRACT .....                                                                       | VII  |

| TABLE DES MATIERES .....                                                             | IX   |

| LISTE DES TABLEAUX .....                                                             | XII  |

| LISTE DES FIGURES .....                                                              | XIII |

| LISTE DES SIGLES ET ABRÉVIATIONS .....                                               | XV   |

| LISTE DES ANNEXES .....                                                              | XVI  |

| INTRODUCTION .....                                                                   | 1    |

| CHAPITRE 1. REVUE DE LITTÉRATURE .....                                               | 4    |

| 1.1    Les heuristiques de placement spécifiques aux architectures à grain fin ..... | 5    |

| 1.1.1.    La construction incrémentale (cluster growth) .....                        | 5    |

| 1.1.2.    Le placement basé sur le partitionnement .....                             | 6    |

| 1.2    Le placement basé sur les paradigmes d'optimisation générale .....            | 8    |

| 1.2.1.    Le placement basé sur le recuit simulé .....                               | 8    |

| 1.2.2.    Le placement basé sur les algorithmes génétiques .....                     | 9    |

| 1.3    Travaux de recherches et méthodes de placement existantes .....               | 11   |

| 1.3.1.    Travaux de base .....                                                      | 11   |

| 1.3.2.    Situation du modèle de placement .....                                     | 12   |

| 1.4    Résumé .....                                                                  | 15   |

| CHAPITRE 2. CONCEPTS DE BASE .....                                                   | 16   |

| 2.1    Les architectures nano-composantes .....                                      | 16   |

| 2.1.1.    Le transistor à nanotube de carbone double grille (DG-CNTFET) .....        | 17   |

| 2.1.2.    Les cellules logiques dynamiquement reconfigurables .....                  | 18   |

| 2.1.3.    Les matrices à intra-connexions fixes .....                                | 19   |

|                                                               |                                                                             |    |

|---------------------------------------------------------------|-----------------------------------------------------------------------------|----|

| 2.1.4.                                                        | Les caractéristiques des architectures nano-composantes .....               | 21 |

| 2.2                                                           | Les concepts de théorie de graphes utilisés .....                           | 22 |

| 2.2.1.                                                        | Les graphes acycliques orientés .....                                       | 23 |

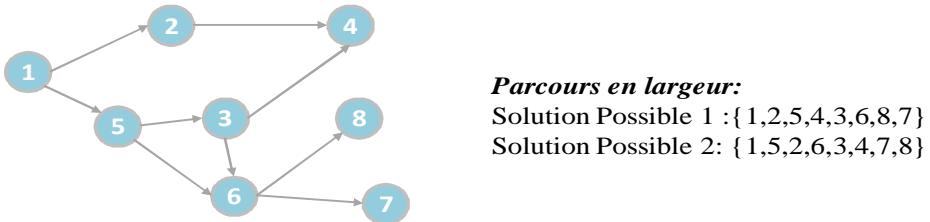

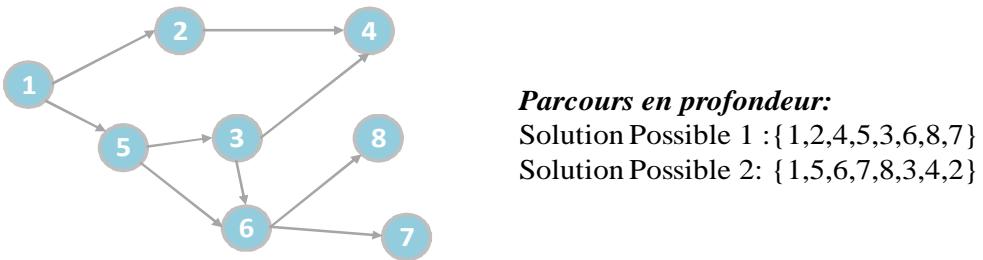

| 2.2.2.                                                        | Les algorithmes de parcours des graphes .....                               | 24 |

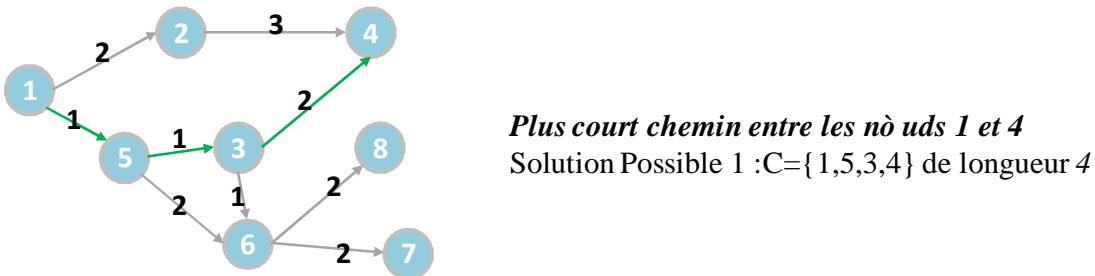

| 2.2.3.                                                        | Les algorithmes de plus courts chemins .....                                | 26 |

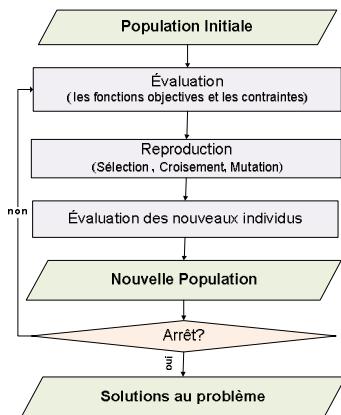

| 2.3                                                           | Les Algorithmes génétiques.....                                             | 27 |

| 2.3.1.                                                        | Fonctionnement général.....                                                 | 27 |

| 2.3.2.                                                        | Formulation du problème d'optimisation.....                                 | 28 |

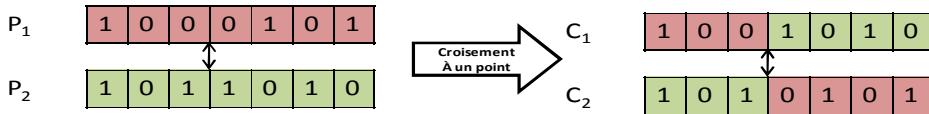

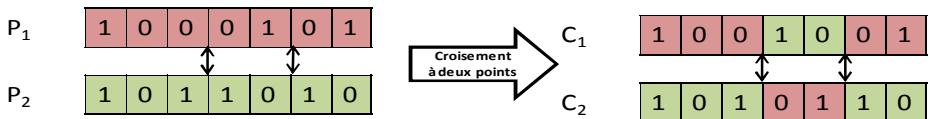

| 2.3.3.                                                        | Opérateurs génétiques.....                                                  | 29 |

| 2.3.4.                                                        | Gestion des solutions dans les Algorithmes Génétiques multi-objectifs ..... | 32 |

| 2.4                                                           | Résumé.....                                                                 | 36 |

| <br>CHAPITRE 3. MODÈLE DE PLACEMENT PROPOSÉ .....             |                                                                             | 37 |

| 3.1.                                                          | La formulation du placement.....                                            | 38 |

| 3.1.1.                                                        | L'architecture physique .....                                               | 38 |

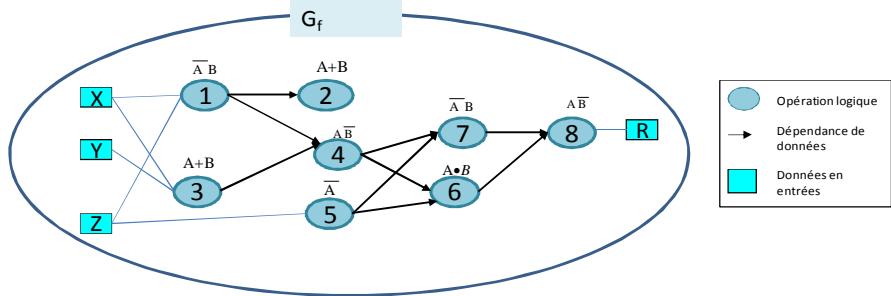

| 3.1.2.                                                        | L'application logique .....                                                 | 39 |

| 3.1.3.                                                        | Objectif de placement .....                                                 | 40 |

| 3.2.                                                          | Description du modèle de placement.....                                     | 41 |

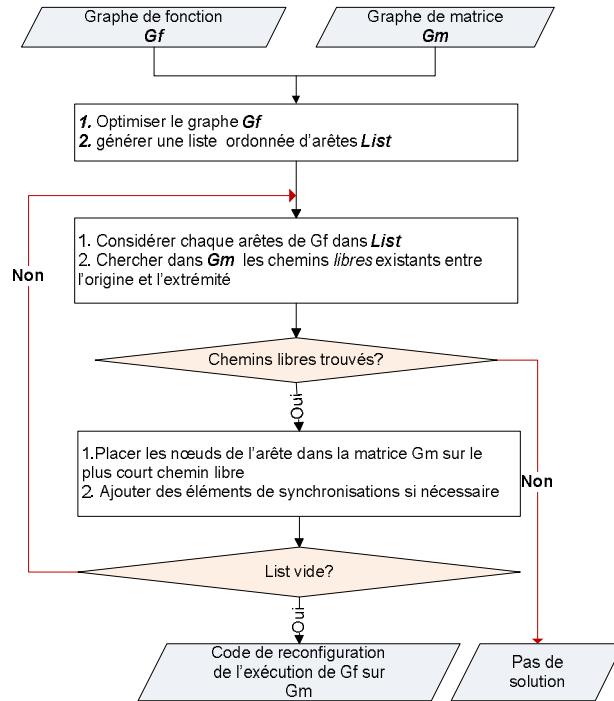

| 3.3.                                                          | La méthode d'assignation matricielle .....                                  | 42 |

| 3.3.1.                                                        | Objectif de l'assignation matricielle .....                                 | 43 |

| 3.3.2.                                                        | Fonctionnement de l'assignation matricielle.....                            | 43 |

| 3.4.                                                          | La méthode de partitionnement .....                                         | 47 |

| 3.4.1.                                                        | Objectif du partitionnement.....                                            | 47 |

| 3.4.2.                                                        | Fonctionnement du partitionnement .....                                     | 47 |

| 3.5.                                                          | La méthode de placement global .....                                        | 53 |

| 3.5.1.                                                        | Objectif du placement global .....                                          | 53 |

| 3.5.2.                                                        | Fonctionnement du placement global .....                                    | 54 |

| 3.6.                                                          | Résumé.....                                                                 | 61 |

| <br>CHAPITRE 4. IMPLÉMENTATION, RÉSULTATS ET DISCUSSION ..... |                                                                             | 63 |

| 4.1.                                                          | Environnements d'implémentation .....                                       | 63 |

| 4.2.                                                          | Description de l'implémentation .....                                       | 64 |

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| 4.3. Bancs de test .....                                                  | 66 |

| 4.4. Résultats et discussions .....                                       | 67 |

| 4.4.1. Résultats du partitionnement et de l'assignation matricielle ..... | 68 |

| 4.4.2. Résultats du placement global .....                                | 74 |

| 4.5. Résumé .....                                                         | 82 |

| CONCLUSION .....                                                          | 83 |

| BIBLIOGRAPHIE .....                                                       | 85 |

| ANNEXE .....                                                              | 90 |

## **LISTE DES TABLEAUX**

## LISTE DES FIGURES

|              |                                                                                    |    |

|--------------|------------------------------------------------------------------------------------|----|

| Figure 1. 1  | Situation des travaux du mémoire .....                                             | 5  |

| Figure 1. 2  | Méthodes météahuristiques .....                                                    | 14 |

| Figure 2. 1  | Image de la vue transversale d'un CNTFET à double-grille (Lin, et al., 2005) ..... | 17 |

| Figure 2. 2  | Structure d'une cellule CNT_DRC_7T (Liu, et al., 2007) .....                       | 18 |

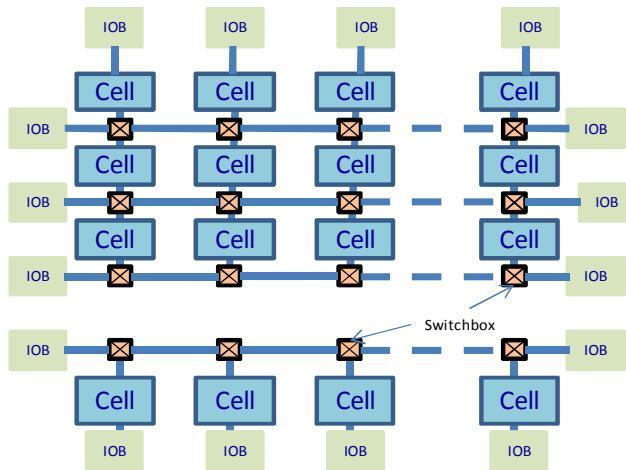

| Figure 2. 3  | Approche conventionnelle de connexion de cellules .....                            | 19 |

| Figure 2. 4  | Approche matricielle de connexion des cellules DG_CNTFET .....                     | 20 |

| Figure 2. 5  | Symbole de la cellule logique DG_CNTFET .....                                      | 21 |

| Figure 2. 6  | Exemple de topologie .....                                                         | 21 |

| Figure 2. 7  | Hiérarchie des architectures nano-composantes .....                                | 22 |

| Figure 2. 8  | Exemple de graphe non orienté et de sous-graphe .....                              | 23 |

| Figure 2. 9  | Graphe orienté cyclique et acyclique.....                                          | 24 |

| Figure 2. 10 | Parcours en largeur .....                                                          | 25 |

| Figure 2. 11 | Parcours en profondeur.....                                                        | 25 |

| Figure 2. 12 | Plus court chemin.....                                                             | 26 |

| Figure 2. 13 | Fonctionnement des algorithmes génétiques .....                                    | 27 |

| Figure 2. 14 | Codage des solutions .....                                                         | 28 |

| Figure 2. 15 | Sélection par tournoi.....                                                         | 30 |

| Figure 2. 16 | Sélection par roulette .....                                                       | 30 |

| Figure 2. 17 | Croisement à un point.....                                                         | 31 |

| Figure 2. 18 | Croisement à deux points .....                                                     | 31 |

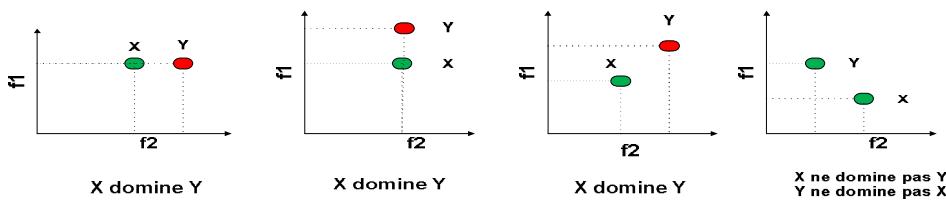

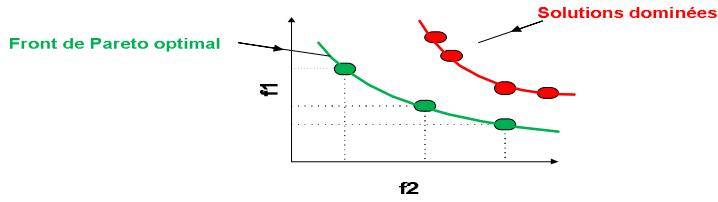

| Figure 2. 19 | Notion de dominance.....                                                           | 33 |

| Figure 2. 20 | Front de Pareto .....                                                              | 34 |

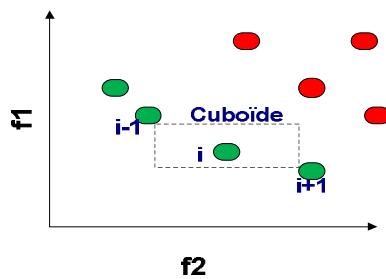

| Figure 2. 21 | Calcul de $i_{distance}$ (Deb, et al., 2002) .....                                 | 35 |

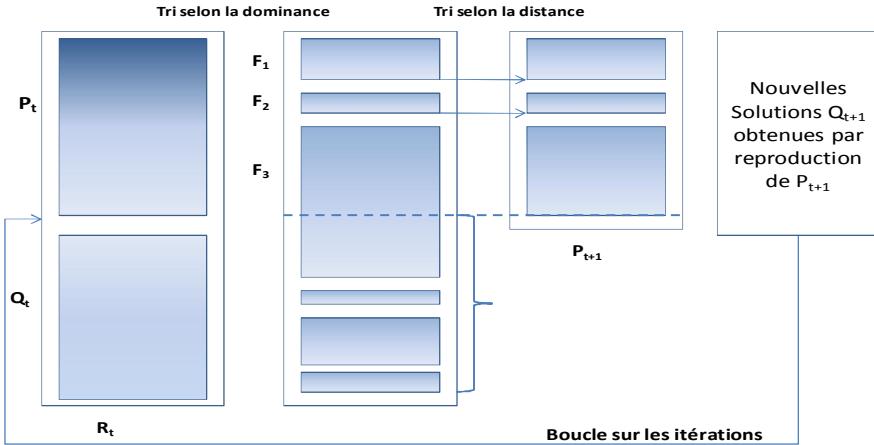

| Figure 2. 22 | Gestion des solutions par NSGA-II .....                                            | 36 |

| Figure 3. 1  | Formulation de l'architecture physique .....                                       | 38 |

| Figure 3. 2  | Formulation de l'application.....                                                  | 39 |

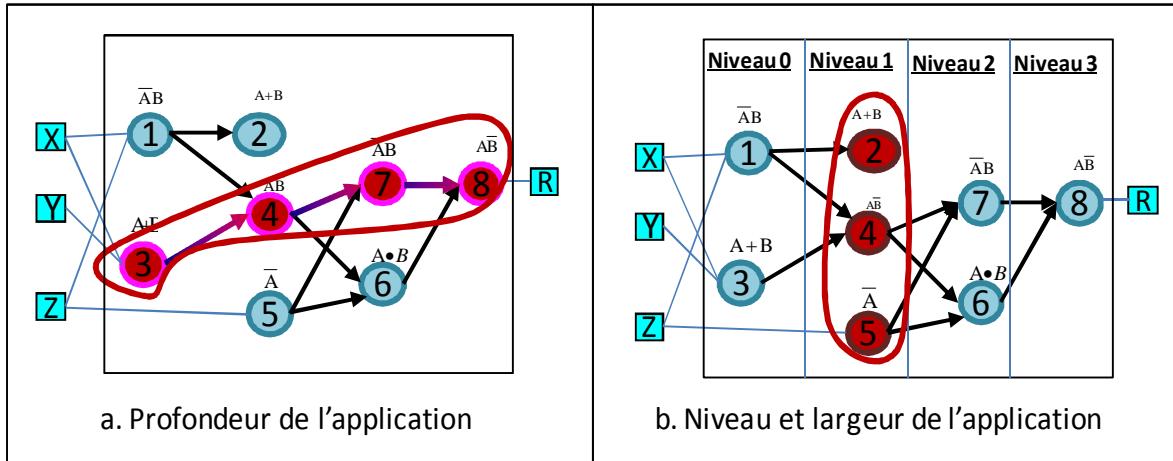

| Figure 3. 3  | Caractéristiques de l'application .....                                            | 40 |

| Figure 3. 4  | Objectif de placement.....                                                         | 40 |

| Figure 3. 5  | Modèle de placement proposé.....                                                   | 42 |

|                                                                                              |    |

|----------------------------------------------------------------------------------------------|----|

| Figure 3. 6 Fonctionnement de l'assignation matricielle .....                                | 44 |

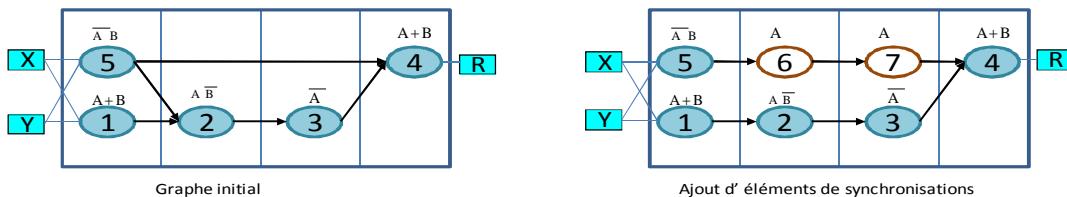

| Figure 3. 7 Ajout d'éléments de synchronisations .....                                       | 44 |

| Figure 3. 8 Liste ordonnée.....                                                              | 45 |

| Figure 3. 9 Assignation sur une matrice de topologie Oméga-modifiée .....                    | 46 |

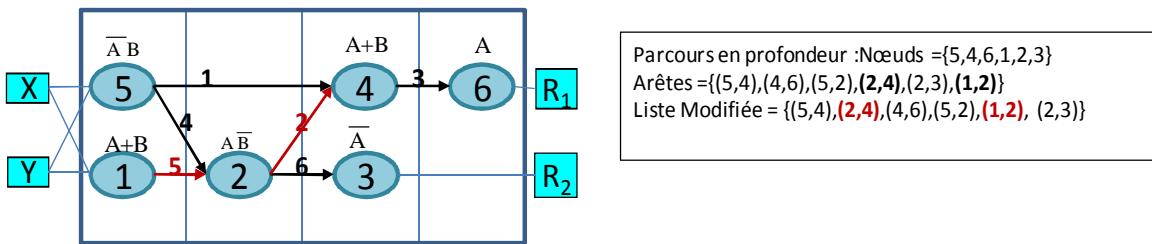

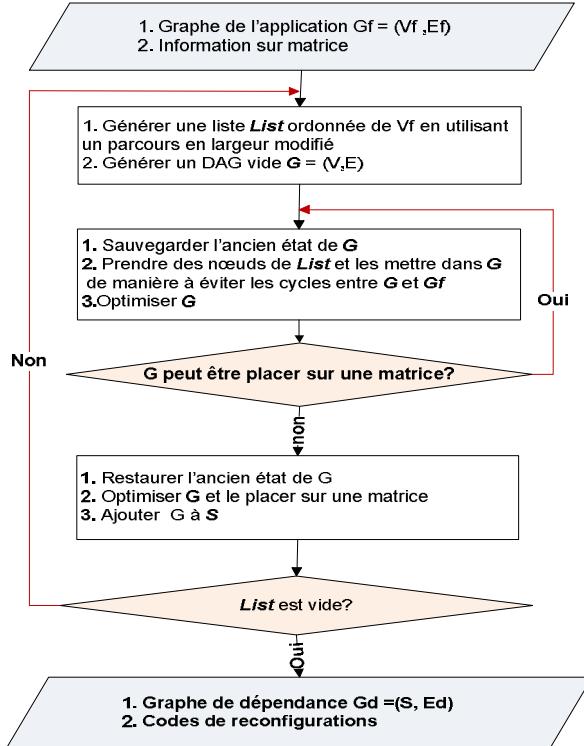

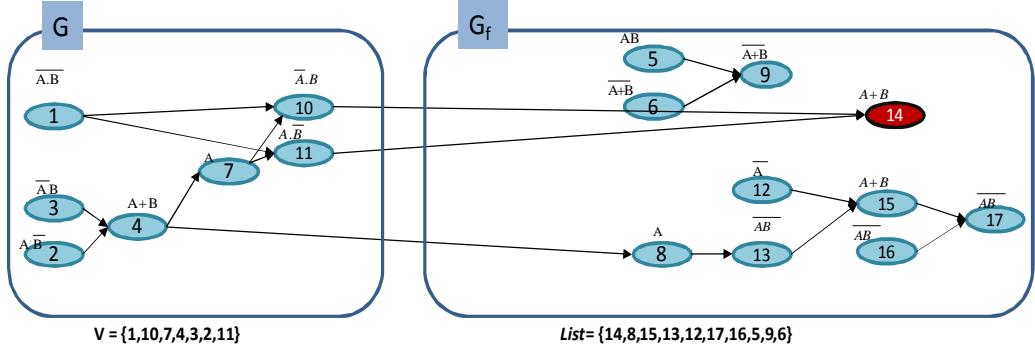

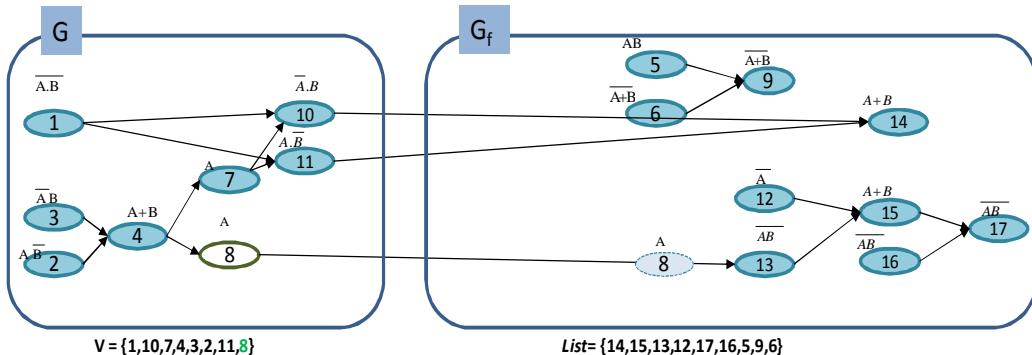

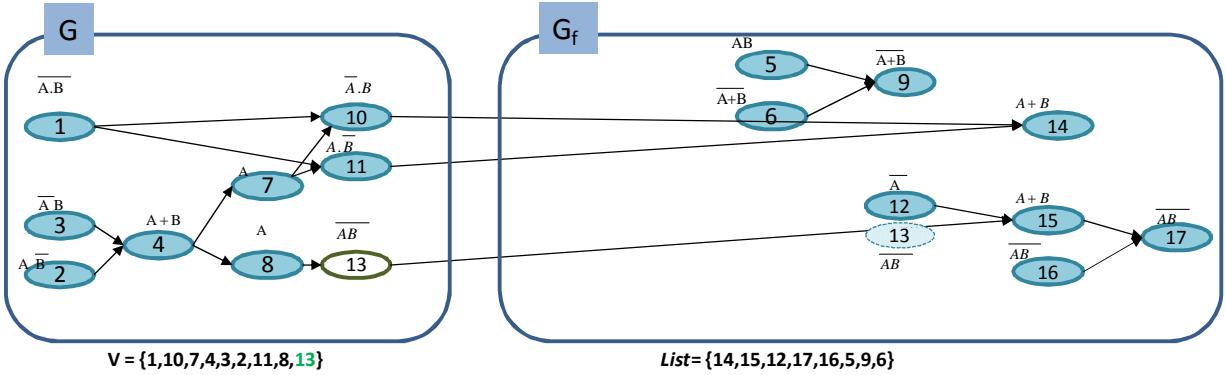

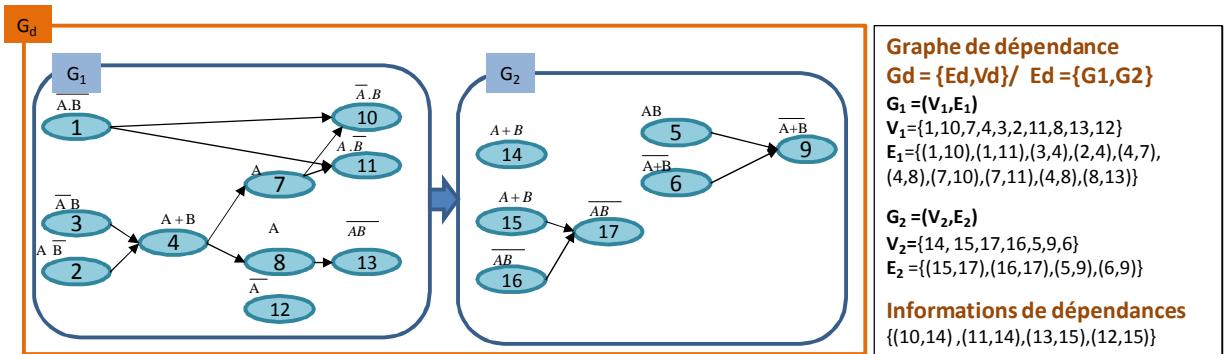

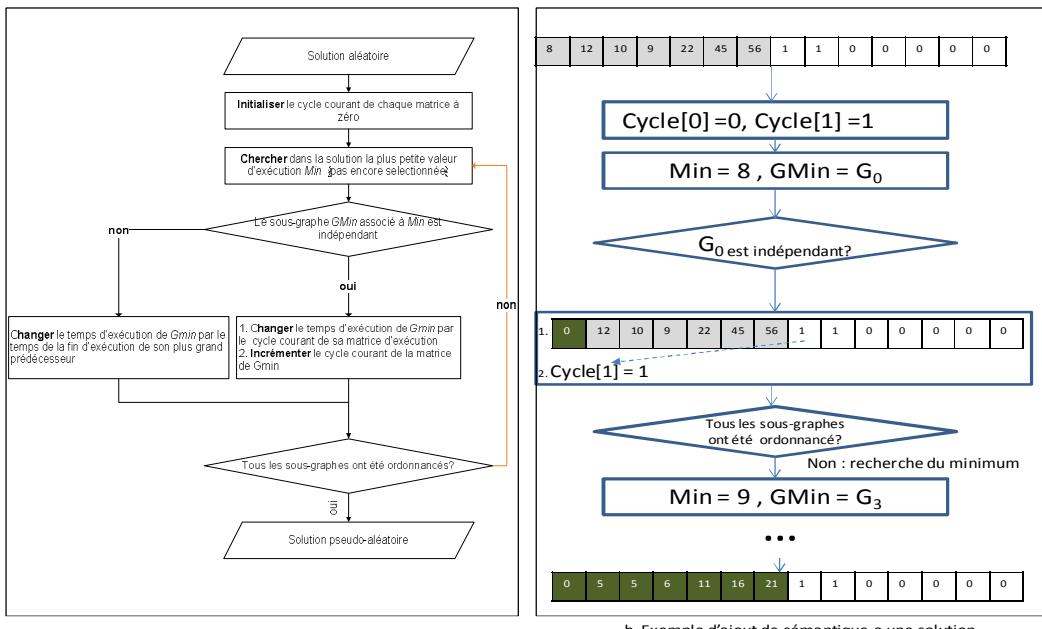

| Figure 3. 10 Organigramme de la méthode de partitionnement.....                              | 48 |

| Figure 3. 11 Exemple d'application logique et de liste triée .....                           | 49 |

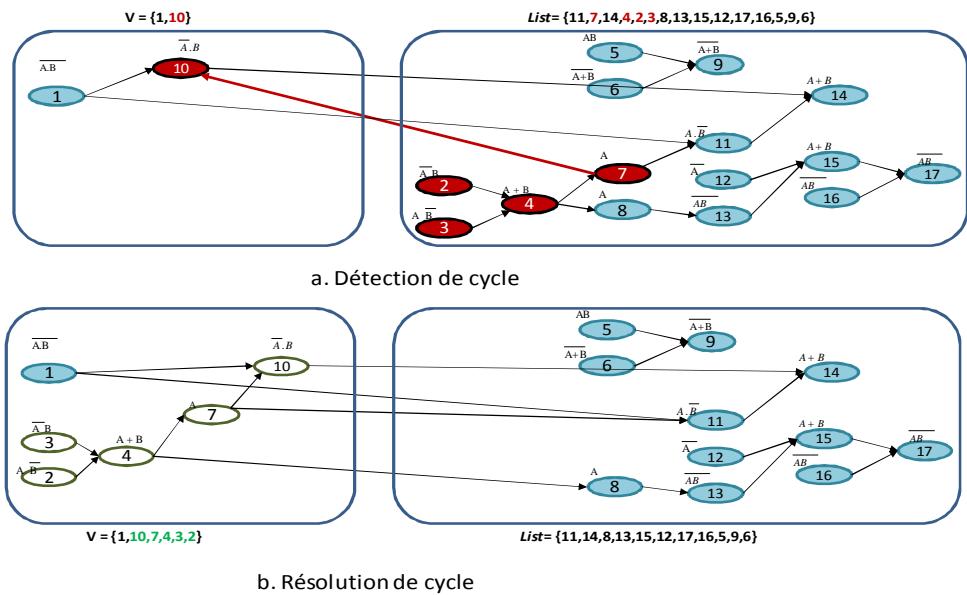

| Figure 3. 12 Détection et correction de cycle lors du partitionnement.....                   | 50 |

| Figure 3. 13 Niveau de nœud plus grand que la profondeur des matrices .....                  | 51 |

| Figure 3. 14 Nœud sans cycle et sans dépassement de largeur et de profondeur .....           | 51 |

| Figure 3. 15 Inter-change de nœuds.....                                                      | 52 |

| Figure 3. 16 Sorties de la méthode de partitionnement .....                                  | 52 |

| Figure 3. 17 Coût de reconfiguration (chargement des cellules) .....                         | 54 |

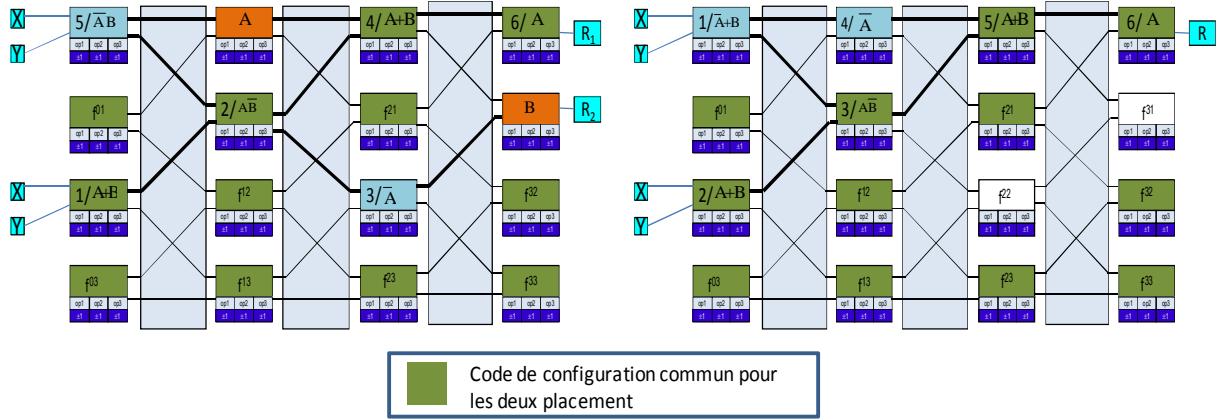

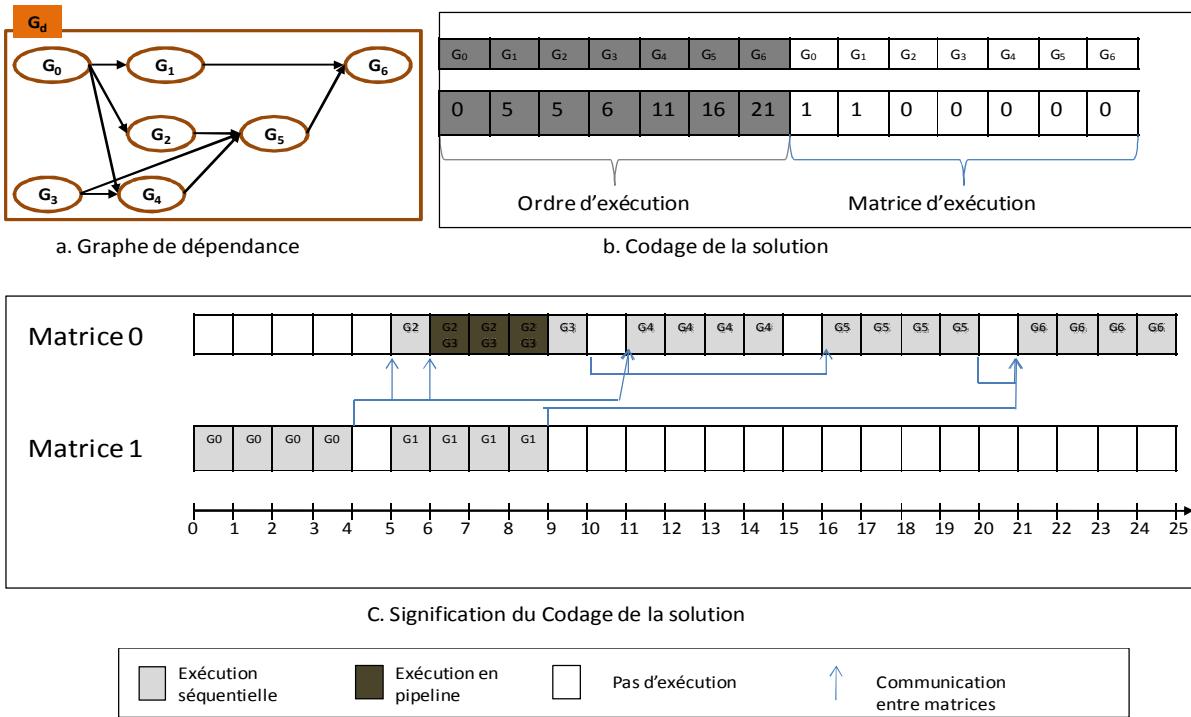

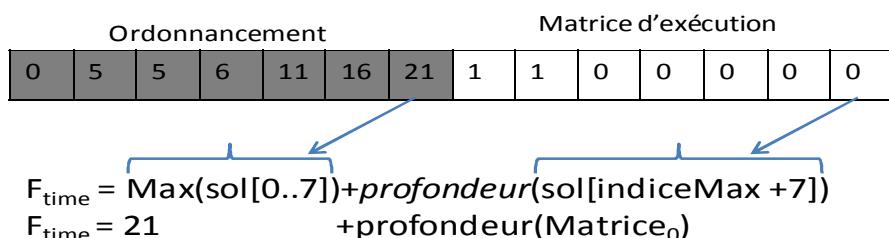

| Figure 3. 18 Codage des solutions de placement.....                                          | 55 |

| Figure 3. 19 Identification du dernier sous-graphe exécuté .....                             | 56 |

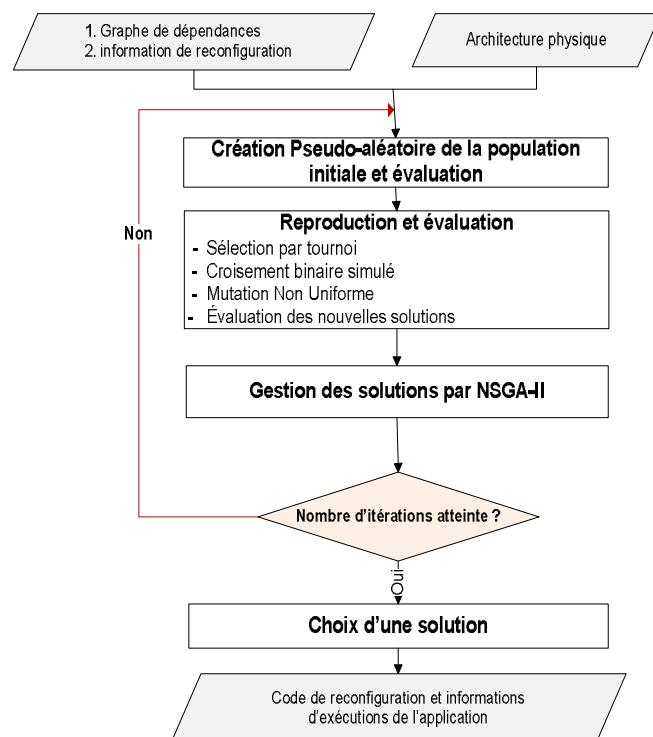

| Figure 3. 20 Algorithme génétique pour le placement global.....                              | 58 |

| Figure 3. 21 Traitement sémantique des solutions.....                                        | 59 |

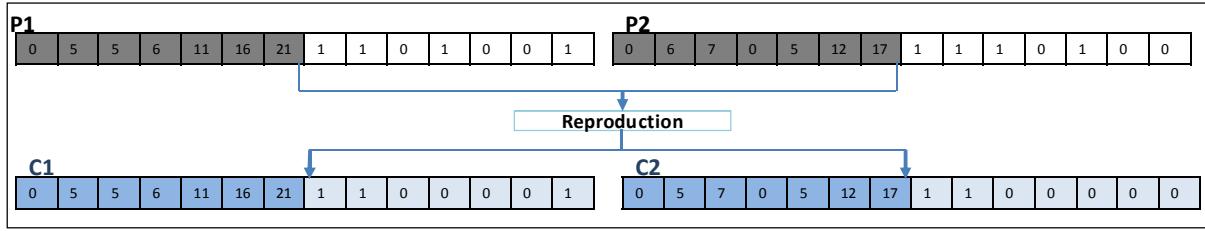

| Figure 3. 22 Reproduction de solutions.....                                                  | 61 |

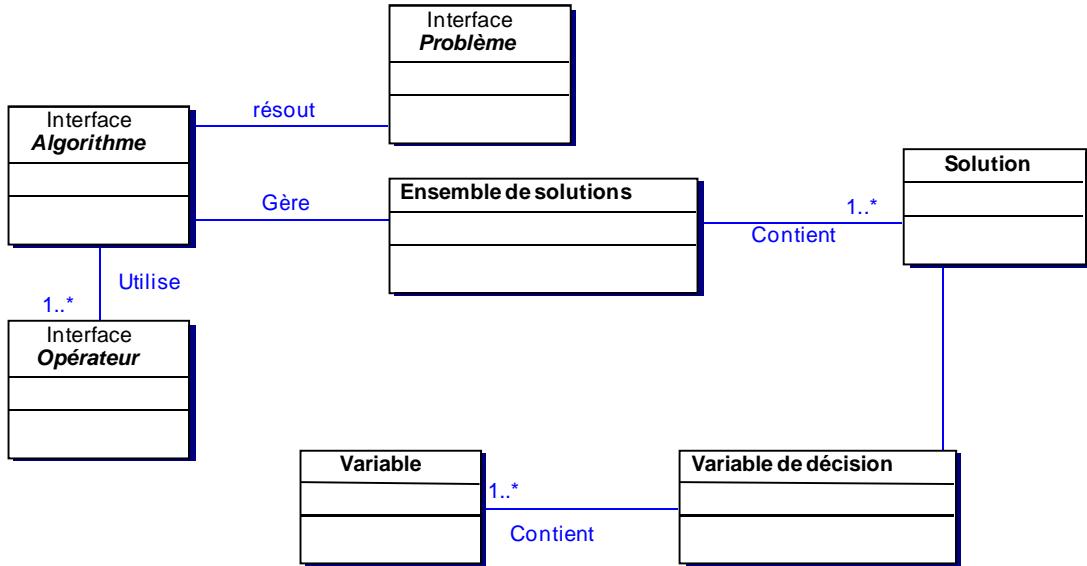

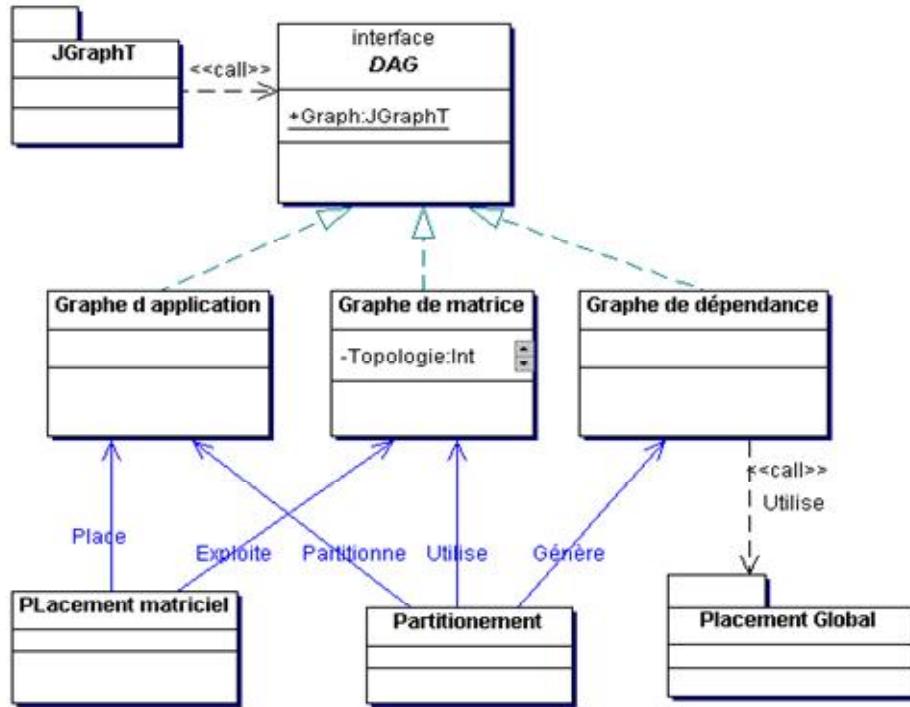

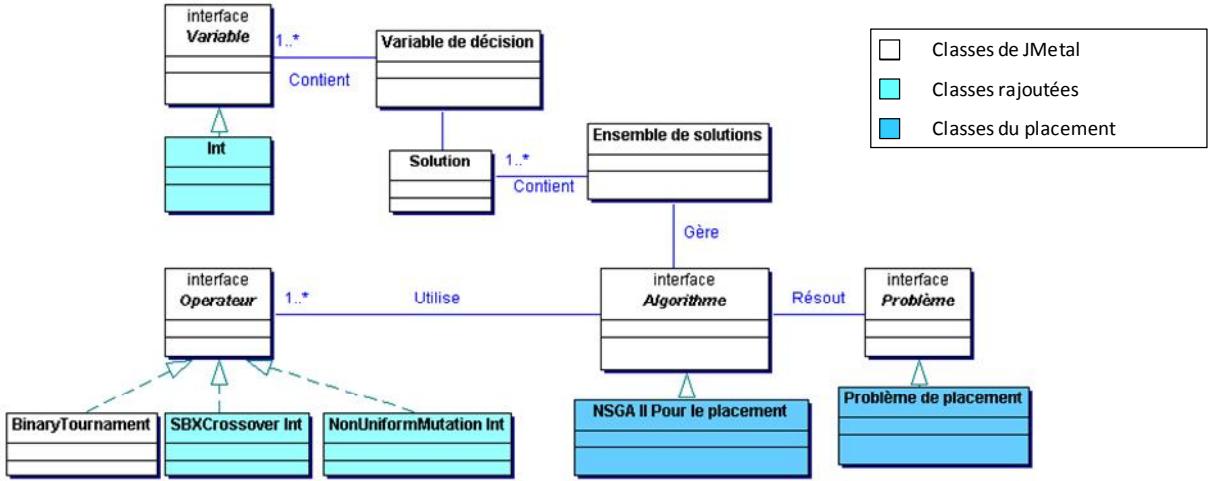

| Figure 4. 1 Classes de base de JMetalí í í í í í í í í í í í í í í í í ..                    | 64 |

| Figure 4. 2 Diagramme de classes du modèle de placement.....                                 | 65 |

| Figure 4. 3 Le paquetage du placement global.....                                            | 66 |

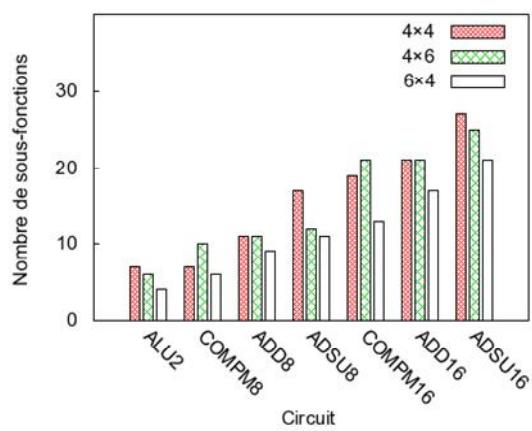

| Figure 4. 4 Évolution de nombre de sous-fonctions par rapport aux tailles des matrices ..... | 72 |

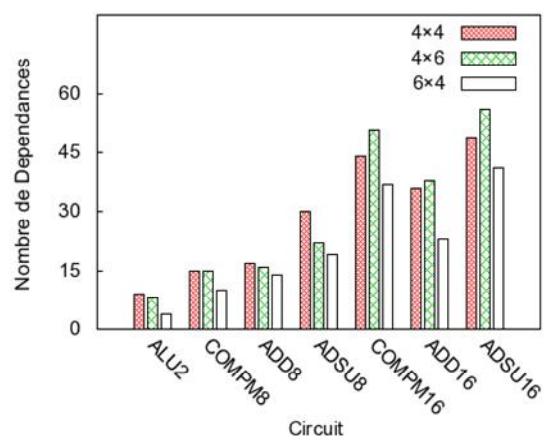

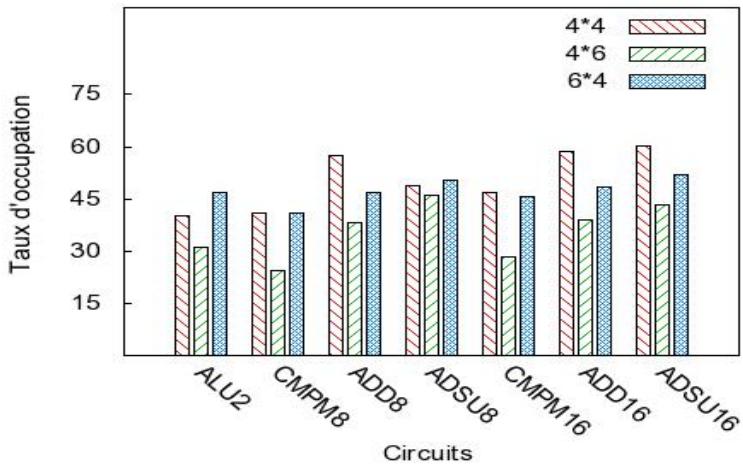

| Figure 4. 5 Performances globales en fonction des matrices .....                             | 73 |

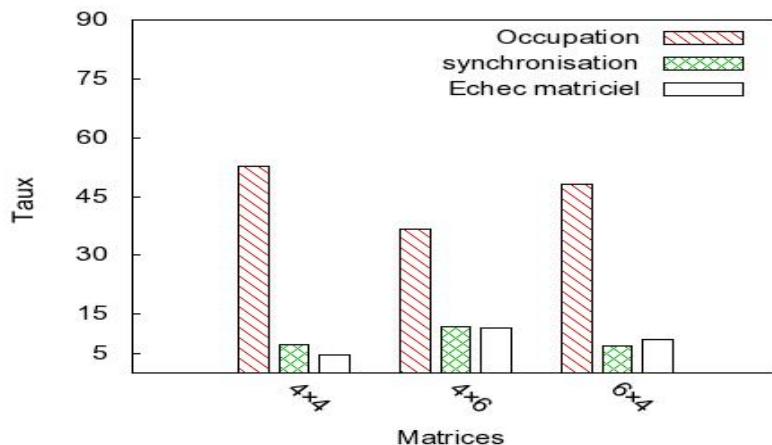

| Figure 4. 6 Taux d'occupation par banc de test.....                                          | 74 |

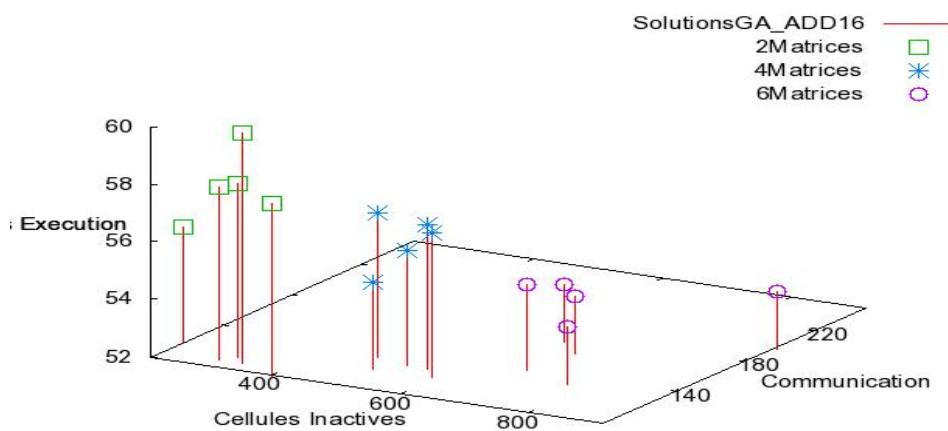

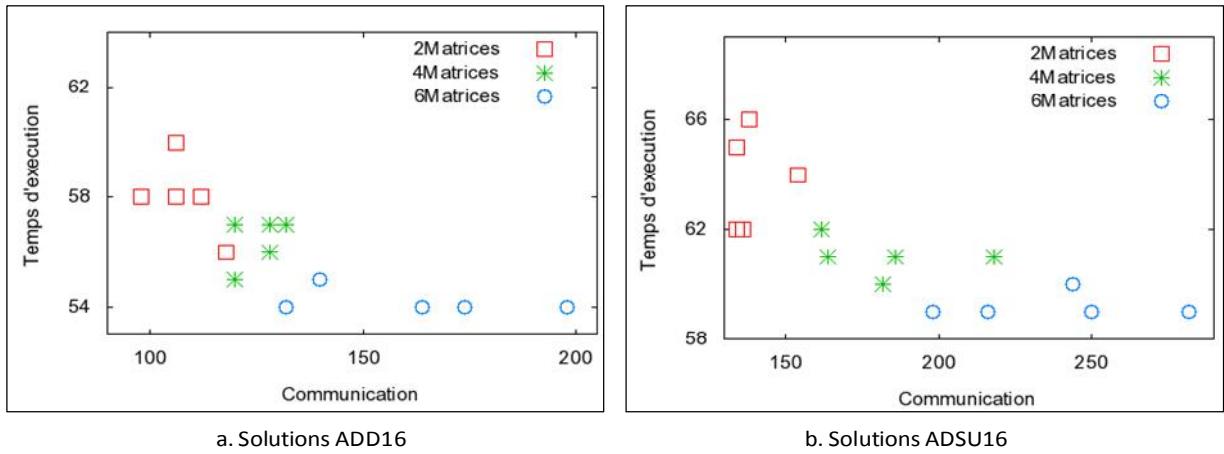

| Figure 4. 7 Évolution des solutions ADD16 en fonction du nombre de matrices .....            | 76 |

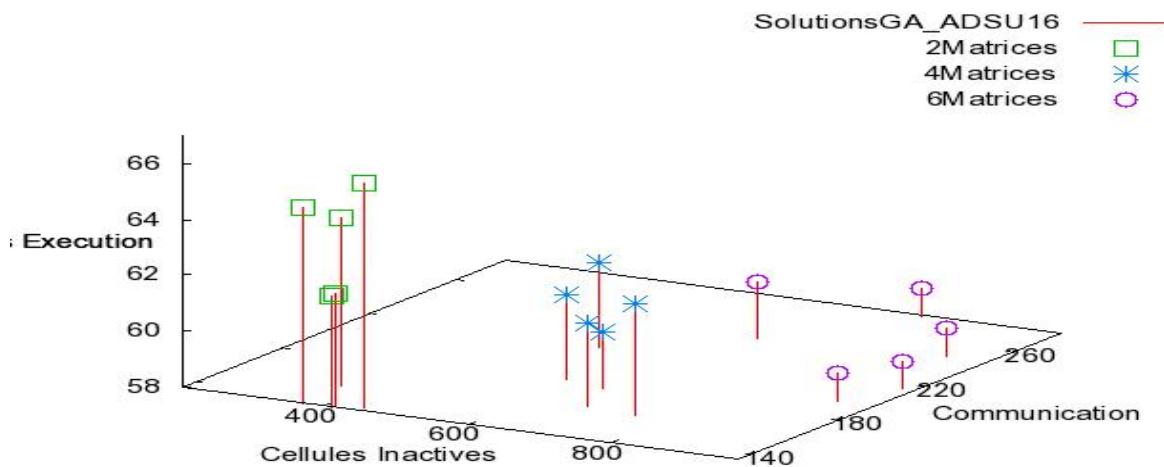

| Figure 4. 8 Évolution des solutions ADSU16 en fonction du nombre de matrices .....           | 77 |

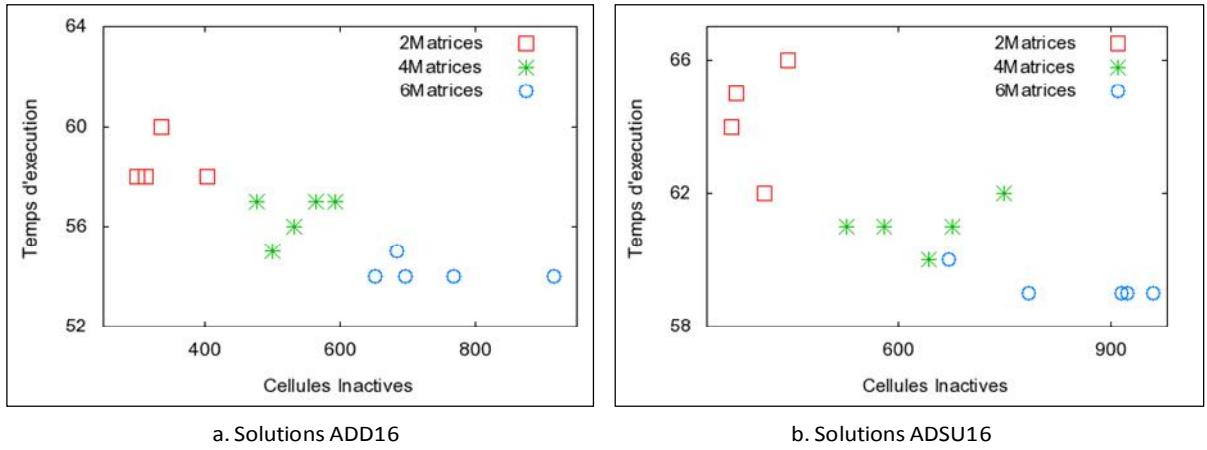

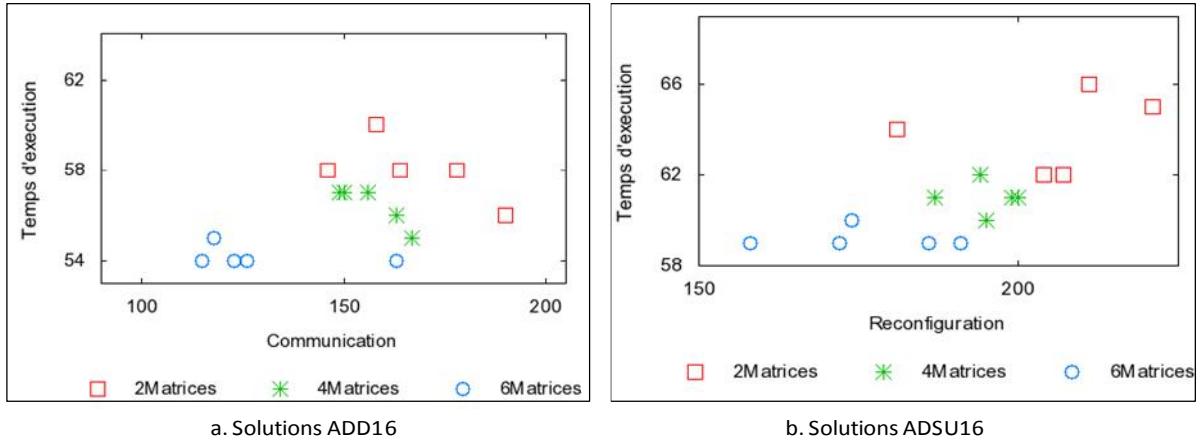

| Figure 4. 9 Impacts sur le temps d'exécution et le nombre de cellules inactives.....         | 78 |

| Figure 4. 10 Impacts sur le temps d'exécution et la communication .....                      | 78 |

| Figure 4. 11 Impacts sur le temps d'exécution et la reconfiguration .....                    | 79 |

| Figure 4. 12 Relation profondeur et temps d'exécution.....                                   | 80 |

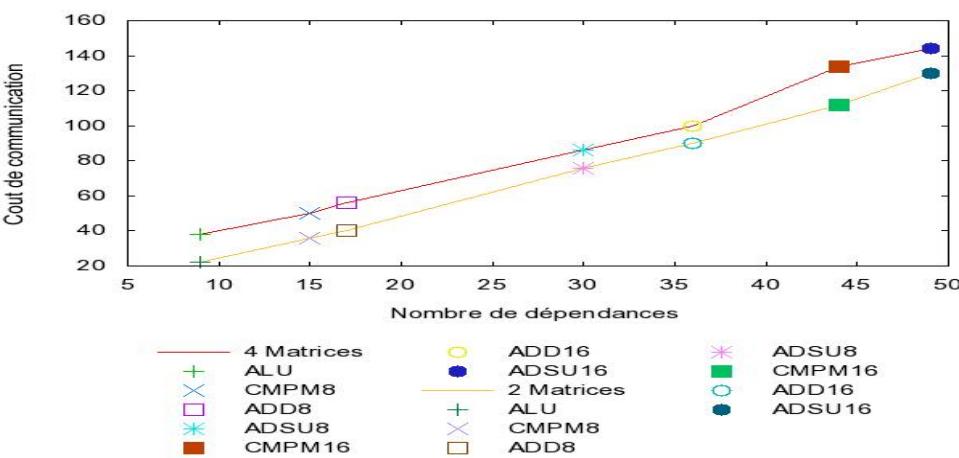

| Figure 4. 13 Relation dépendances et coût de communication .....                             | 80 |

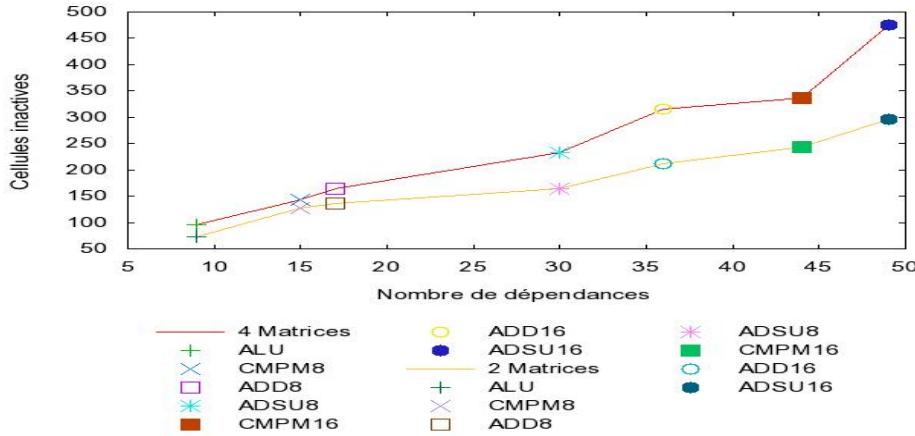

| Figure 4. 14 Relation entre les dépendances et les cellules inactives.....                   | 81 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|                |                                                     |

|----------------|-----------------------------------------------------|

| ADD8/ADD16     | Additionneur 8 bits/16 bits                         |

| ADSU8/ADSU16   | Additionneur/soustracteur 8 bits/16 bits            |

| AG             | Algorithme Génétique                                |

| ALU2           | Arithmetic and Logic Unit 2-bits                    |

| CAO            | Conception Assistée par Ordinateur                  |

| CMOS           | Complementary Metal Oxide Semiconductor             |

| CNT            | Carbon NanoTube                                     |

| CNT_DRC_7T     | Dynamic Reconfigurable Cell 7 Transistors           |

| COMPM8/COMPM16 | Comparateur 8bits/16bits                            |

| DAG            | Directed acyclic graph                              |

| DG_CNTFET      | Dual_Gate Carbone NanoTube Field Effect Transistor  |

| ESP            | Evolution Simulation Placement                      |

| FAFPGA         | Genetic Algorithm for FPGA                          |

| FPGA           | Field-Programmable Gate Array                       |

| GASP           | Genetic Algorithm Standard cell Placement           |

| GFET           | Graphene Field Effect Transistor                    |

| ITRS           | International Technology Roadmap for Semiconductors |

| NSGA           | Non-dominated Sorting Genetic Algorithm             |

| NSGA-II        | Fast Non-dominated Sorting Genetic Algorithm        |

| NWFET          | Nano Wire Field Effect Transistor                   |

| SDK            | Sun Development Kit                                 |

| SBX            | Simulated Binary Croisement                         |

| VEGA           | Vector Evaluated Genetic Algorithm                  |

| VHDL           | VHSIC Hardware Description Language                 |

| VHSIC          | Very High Speed Integrated Circuit                  |

| VPR            | Versatile Packing, Placement and Routing            |

## **LISTE DES ANNEXES**

|                                               |    |

|-----------------------------------------------|----|

| ANNEXE I TRANSFORMATION DES CAS DE TEST ..... | 90 |

|-----------------------------------------------|----|

## INTRODUCTION

En 1965, Gordon Moore a énoncé que le nombre transistors dans les circuits intégrés doublera tous les 12 mois (Moore, 1965). L'énoncé de Moore s'est avéré justifié puisqu'on a assisté ces dernières décennies à une évolution technologique exponentielle. Ce phénomène est caractérisé par deux variables : le coût et le nombre de transistors (Hutchison, 2009). D'un point de vue économique, on s'attend toujours à des composants de plus en plus performants et miniaturisés sans qu'il y ait une inflation de prix. Ce qui conduit non seulement à une grande production de transistors, mais aussi à leur miniaturisation pour pouvoir les exploiter à grand nombre. En effet, le transistor CMOS a franchi 12 ordres de grandeur physique depuis la création de l'industrie (Hutchison, 2009). Dans ce contexte de miniaturisation, l'ITRS (International Technology Roadmap for Semiconductors) prévoit la limite des transistors CMOS à 2022 (ITRS, 2007). Pour atteindre la performance et la miniaturisation nécessaires aux technologies futures, il est important de définir de nouvelles technologies qui permettront de compléter voire même remplacer le transistor CMOS. Pour ce faire, plusieurs domaines sont en cours d'exploration. Le domaine de la nanotechnologie semble être l'un des plus prometteurs. Il a permis de définir de nouveaux transistors miniaturisés, notamment le transistor à base de graphène (GFET), le transistor à base de nanotube de carbone (DG-CNTFET), le transistor à base de nano fil (NWFET)... Ces transistors ouvrent la voie à un nouveau paradigme d'architectures non conventionnelles à granularité fine : *les architectures nano-composantes*. Ces architectures ont trois caractéristiques spécifiques :

- Les cellules logiques faites à base de nano-transistors sont dynamiquement reconfigurables c.-à-d. qu'elles peuvent être reconfigurées lors de l'exécution;

- Les architectures sont caractérisées par une granularité fine, c.-à-d. les cellules logiques traitent des opérations logiques prenant deux entrées codées sur un bit chacune;

- Les architectures ont une structure particulière à deux niveaux : les cellules sont organisées en matrices et sont connectées entre elles par des interconnexions fixes. Les matrices, à leur tour, sont organisées en réseau de matrices et communiquent entre elles par des connexions dynamiques.

Afin de prouver le potentiel des architectures nano-composantes pour la conception des systèmes électroniques performants, une évaluation exhaustive s'impose. Ceci implique des outils permettant l'exploration automatique de l'espace de conception.

De plus, étant donné que ces technologies sont très nouvelles l'accès et le coût pour le prototypage représentent des réels défis.

Pour résoudre ces problèmes, la définition des outils de conception assistée par ordinateur (CAO) est incontournable. Ces outils devront relever plusieurs défis :

- Accélérer la mise sur le marché des nouvelles technologies en réduisant le temps de conception;

- Faciliter l'accès au prototypage en permettant les prototypages virtuels;

- Faciliter la synthèse physique et garantir des systèmes de faible consommation;

- Permettre une bonne interaction entre les concepteurs niveau systèmes et les concepteurs niveau physique.

La conception des outils CAO, dans le domaine de la nanotechnologie, devra aussi prendre en compte les effets physiques liés à la réduction des dimensions et également définir des stratégies d'intégration et de traitement de l'information pour les nano-systèmes (Robert, 2004).

L'objectif principal de ce projet est de proposer une approche pour aider à la conception des systèmes basés sur les architectures nano-composantes. Plus spécifiquement, il s'agit de définir un modèle de placement qui permettra d'exécuter des applications sur les architectures nano-composantes. Le modèle doit prendre en compte les caractéristiques de ces architectures. Il doit également permettre d'optimiser leurs ressources tout en exploitant les performances qu'elles offrent.

Ce travail a principalement permis de développer un des premiers modèles de placement prenant en considération les caractéristiques des architectures nano-composantes. Plus spécifiquement il a permis de :

- Définir une méthode de partitionnement, utilisant la théorie de graphe, qui permet de diviser automatiquement une application en sous-fonctions;

- Développer une méthode d'assignation matricielle, utilisant la théorie de graphe, qui permet de placer une sous-fonction sur une *matrice*;

- Définition d'une méthode de placement globale, utilisant les algorithmes génétiques, pour permettre un placement global de toutes les sous-fonctions sur *le réseau de matrice*;

- Exploiter les performances de ces architectures tout en optimisant l'utilisation des ressources ;

- Faciliter l'exploration pour la définition des systèmes nano-composants.

Ce travail marque son originalité non seulement dans la nouveauté du domaine et du paradigme sur lequel nous travaillons, mais aussi sur les contributions qu'il apporte dans ce domaine. En effet ce projet de recherche contribue à la définition de nouvelles architectures candidates au remplacement des architectures conventionnelles (CMOS). Il fournit un outil qui aidera au prototypage de ces architectures tout en permettant leur exploitation.

Ce mémoire est organisé en quatre chapitres. Le premier chapitre présente les différentes techniques de placement, les travaux existants sur les architectures nano-composantes ainsi que le positionnement de notre projet par rapport à ces travaux. Le deuxième chapitre décrit les caractéristiques des architectures nano-composantes. Il décrit également les concepts de bases sur la théorie des graphes et les algorithmes génétiques exploités dans ce mémoire. Le modèle de placement ainsi que les différentes méthodes qui le composent sont expliqués dans le chapitre trois. Enfin le quatrième chapitre, présente l'implémentation et les résultats obtenus.

## CHAPITRE 1. REVUE DE LITTÉRATURE

Dans ce chapitre, nous présenterons les travaux existants sur les méthodes de placement pour des architectures à granularité fine (reconfiguration niveau porte logique). Il existe plusieurs techniques de placement définies pour ce type d'architectures (heuristiques spécifiques). Parmi ces méthodes, on peut citer la méthode de constructions incrémentale et la méthode de placement par partitionnement (min-cut).

- **La construction incrémentale** est une méthode intuitive qui consiste à associer itérativement les opérations logiques (nœuds, modules) d'une application aux cellules logiques (locations) de l'architecture;

- **Le placement par partitionnement** consiste à réduire le problème de placement en partitionnant l'application à placer en sous-fonctions puis à effectuer le placement de ces sous-fonctions. Les méthodes de placement par partitionnement diffèrent, les unes des autres, par les algorithmes de partitionnement utilisés. Dans ce chapitre nous allons parler des algorithmes de partitionnement utilisés par les méthodes de placement par partitionnement.

Par ailleurs, le problème de placement étant un problème NP-Complet, les paradigmes d'optimisation générale permettent d'avoir de bons résultats de placement. Les plus utilisés pour le placement sont le recuit simulé et les algorithmes génétiques.

- **Le recuit simulé** permet une méthode de recherche locale qui part d'une solution initiale qu'elle améliore en plusieurs itérations;

- **Les algorithmes génétiques** permettent une recherche globale. Il utilise une approche qui part d'un ensemble de solutions qui sont diversifiées afin de rapprocher de la solution optimale.

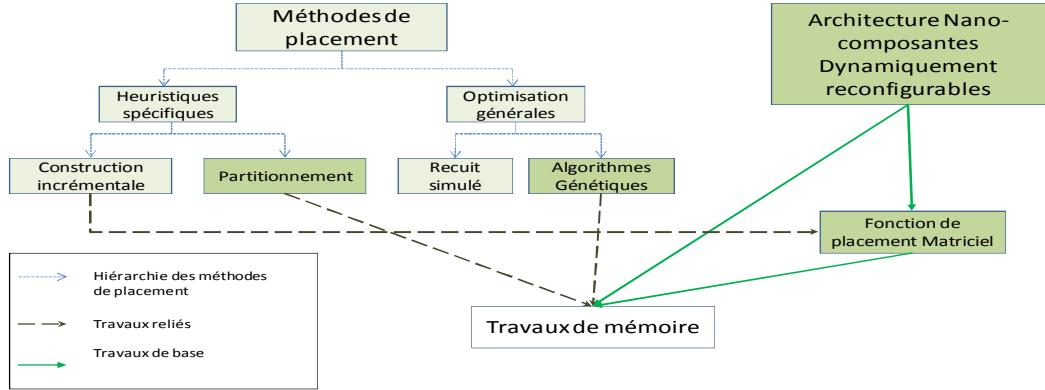

Toutes ces techniques sont complémentaires et peuvent être combinées dans les méthodes de placement. Dans ce chapitre on présente chaque méthode de placement existante, à travers la technique qui la caractérise le mieux. La figure 1.1 décrit la relation entre les travaux existants et les travaux effectués dans ce mémoire. L'organisation de ce chapitre y apparaît également. La première section présente les travaux existants sur les heuristiques spécifiques dédiées aux architectures à grain fin. Les méthodes existantes basées sur les paradigmes d'optimisation générale sont présentées dans la seconde section. La troisième section est consacrée aux travaux

sur lesquels nous nous sommes basés ainsi qu'à la situation du modèle de placement proposé parmi les méthodes de placement existantes. La quatrième partie résume le chapitre.

Figure 1. 1 Situation des travaux du mémoire

## 1.1 Les heuristiques de placement spécifiques aux architectures à grain fin

Cette section présente les méthodes de placement dédiées aux architectures à grains fins. La première sous-section présente les méthodes basées sur la construction incrémentale alors que la seconde sous-section présente les algorithmes de partitionnement utilisés dans les méthodes de placement par partitionnement.

### 1.1.1. La construction incrémentale (cluster growth)

Hanan et al (Hanan, et al., 1978) ont présenté une méthode de placement qui est incrémentale. Elle sélectionne les modules (nœuds ou opérations logiques de base) un à la fois en se basant sur une fonction d'évaluation qui permet de déterminer quel module sélectionné et où le placer. Une fois que le module est sélectionné et positionné, il ne peut pas être déplacé. La fonction de sélection définie dans cette méthode consiste à choisir le module qui a le plus de connexions avec les modules déjà placés. Ce processus est répété jusqu'à ce que tous les modules soient placés.

Ramineni et al (Ramineni, et al., 1993) ont proposé une méthode de placement incrémentale dont la fonction de sélection est basée sur la possibilité de routage. La méthode était adressée à des architectures spécifiques ayant une restriction de connectivité (Concurrent logic

CLi6000/AMTEL). Dans cette méthode, un module est sélectionné si il existe une connectivité pour le placer.

Kang (Kang, 1983) a proposé une méthode de placement basée sur un ordonnancement de tous les modules de la fonction logique. Une liste des modules, pas encore placés, est créée de manière incrémentale par ordre décroissant de coût de connexions. À chaque itération, l'ordonnancement est mis à jour jusqu'à ce que tous les modules soient placés. Cette méthode est intéressante dans le sens où elle facilite la sélection du module à placer.

**Résumé :** La méthode de construction incrémentale est très rapide. Elle donne de bons résultats pour le placement de petites applications, mais plus l'application est grande plus le résultat n'est pas nécessairement optimal.

### 1.1.2. Le placement basé sur le partitionnement

La méthode de placement par partitionnement consiste à diviser l'application à placer en ensemble de modules en leur réservant de l'espace sur l'architecture physique. Chaque ensemble de modules qui ne peut pas être placé est divisé récursivement jusqu'à ce qu'on puisse placer toute sous-fonction résultante du partitionnement. Une fois que le partitionnement est fait, on peut choisir n'importe quelle technique de placement pour placer les sous-fonctions qui vont devenir les unités atomiques à placer. On parle en général de méthode de placement, mais dans cette approche, les performances de la méthode dépendent beaucoup de l'algorithme de partitionnement utilisé. Dans cette sous-section, nous présentons différents algorithmes de partitionnement utilisés lors du placement par partitionnement.

Kernighan et al (Kernighan, et al., 1970) ont défini une méthode de partitionnement dont l'objectif est de réduire le coût de connexion et de routage de données. Ils ont défini un bloc comme un ensemble de modules. L'algorithme effectue un premier partitionnement aléatoire qui est amélioré par la suite en utilisant une méthode itérative de changement de modules entre les blocs. Le changement de modules consiste en une permutation des modules entre deux blocs c.-à-d. si on a deux modules  $n_1$  et  $n_2$  et que  $n_1$  se trouve dans le bloc  $b_1$  et  $n_2$  dans le bloc  $b_2$ , le changement de modules consiste à mettre  $n_1$  dans  $b_2$  et  $n_2$  dans  $b_1$ .

L'auteur de (Breuer, 1977) a proposé une méthode de placement basée sur le partitionnement de Keringhan et coll. Le bloc peut être partitionné par une coupure horizontale

ou verticale. Le partitionnement de Keringhan a été modifié de manière à prendre en compte deux nouveaux aspects :

- Certains modules ne peuvent pas être déplacés lors de la phase d'amélioration;

- Au lieu de partitionner une connexion entre deux modules, le partitionnement se fait entre deux blocs.

Dans leurs travaux, Fiduccia et al (Fiduccia, et al., 1982) ont défini une méthode itérative pour améliorer l'algorithme de Keringhan. Ils ont rajouté un nouveau critère qui consiste à assurer l'équilibre entre les deux blocs partitionnés (ensemble de modules dans chaque bloc). Ils définissent un concept de « gain de module » qui est utilisé pour déplacer un module d'un bloc à un autre. La valeur de ce gain est calculée par rapport au critère d'équilibre et au nombre d'interconnexions.

Cox et al (Cox, et al., 1986) ont défini une méthode de placement spécifique à l'architecture STAR (Standard Transistor Array). Cette architecture a été définie par Gould et al (Gould, et al., 1980). Ils la présentent comme un ensemble de transistors CMOS superposés dans un réseau. 22 cellules standards qui facilitent la conception de circuit à partir de cette architecture y ont été définies. L'objectif de placement sur ces architectures est de réduire le nombre de connexions et le coût de routage. Pour cela, la méthode utilise l'ordonnancement linéaire pour partitionner les fonctions. Cela permet de bien organiser les modules d'un même bloc de manière à ce qu'ils soient placés dans le plus petit bloc physique possible. Cet ordonnancement doit aussi permettre de réduire le nombre de connexions et réduire le coût du routage.

Les algorithmes de partitionnement présentés ci-dessus prennent en compte la connexion entre deux modules ou deux blocs (ensemble de modules), mais ne prennent pas en compte le sens de la connexion. En effet le sens de la connexion est très important, car il permet d'éviter les partitionnements cycliques. Lorsque deux blocs résultant d'un partitionnement forment un cycle, cela rajoute beaucoup les communications et donc le coût de routage de données. Ce qui n'est pas souhaité, car l'un des plus grands objectifs du placement est de réduire le routage de données.

Les auteurs de (Cong, et al., 1994) et (Cong, et al., 1995) ont proposé une méthode de partitionnement qui exploite la dépendance logique afin d'éviter les retours cycliques après le partitionnement. Dans cette méthode, le partitionnement se fait dès le départ en plusieurs blocs

(au lieu de deux blocs dans les méthodes précédentes). Ils utilisent également la méthode de changement de modules pour améliorer l'algorithme défini. À ce niveau, même si un échange permet d'améliorer un partitionnement en termes de nombre de connexions, il n'est valide que s'il ne crée pas de cycles entre les partitions.

**Résumé :** Les méthodes de partitionnement donnent de bons résultats, cependant, elles peuvent être couteuses en temps d'exécution puisque d'une part elles utilisent une fonction de sélection quelles évaluent à chaque itération et de l'autre, elles utilisent des méthodes d'inter-changes pour améliorer le partitionnement. L'avantage de l'utilisation du partitionnement pour le problème de placement est qu'il permet d'éviter les problèmes d'explosion combinatoire puisque les placements se font à un niveau de granularité fine. Ils sont beaucoup utilisés lors de placement basé sur les paradigmes d'optimisation générale puisqu'ils permettent de réduire le problème et de réduire ainsi l'espace de recherche.

## 1.2 Le placement basé sur les paradigmes d'optimisation générale

Les méthodes d'optimisation métaheuristique permettent d'optimiser une large gamme de problèmes différents avec des recherches itératives successives. Ces approches peuvent prendre beaucoup de temps d'exécution, mais donnent d'excellents résultats (Shahookar, et al., 1991). Les paradigmes les plus utilisés sont ceux du recuit simulé et de l'algorithme génétique.

### 1.2.1. Le placement basé sur le recuit simulé

Cette approche est beaucoup utilisée pour le placement. L'idée de base est que l'algorithme prend en entrée un placement initial et essaye de le modifier en faisant des inter-changements entre les modules. Un paramètre  $T$  appelé température, qui tend vers zéro avec le temps, est utilisé pour déterminer la probabilité d'un mauvais mouvement.

Dans leurs travaux, Sechen et al (Sechen, et al., 1986), (Sechen, 1986) ont développé, Timberwolf, un outil de placement et routage très performant et très utilisé pour les architectures à cellules standards. L'objectif du placement est de minimiser le coût d'interconnexion pour le routage des données. Le placement des cellules est simulé de manière à minimiser les liens d'interconnexion (en estimations) en utilisant un algorithme de recuit simulé. À chaque itération on modifie le placement soit en inter-changeant deux modules ou en changeant de location

(cellule) à un module. La fonction objective est composée de deux valeurs indépendantes : la première est le coût d'interconnexion et la seconde une évaluation de pénalités qui consiste à identifier si la location accordée à une cellule est adéquate ou non.

Les auteurs de (Betz, et al., 1997) ont défini un outil VPR (Versatile Packing, Placement and Routing) pour les FPGA dont la méthode de placement est basée sur l'approche du recuit simulé. L'objectif est de minimiser le coût de routage de données. Ils ont exploré plusieurs fonctions objectives et ont misé sur une fonction qui fait la sommation du coût de toutes les interconnexions du circuit. La recherche par recuit simulé commence par un placement généré aléatoirement. À chaque itération, une permutation des modules, déjà placés, est effectuée. Le paramètre température est réévalué lorsqu'on constate que l'algorithme converge lentement. Ce qui permet d'améliorer la méthode en réduisant de temps d'exécution.

Wakabayashi et al (Wakabayashi, et al., 2002) ont développé un placement basé sur le partitionnement et l'approche de recuit simulé. L'objectif est de faire un placement qui permettra de regrouper au maximum les modules afin de réduire le coût d'interconnexion et d'optimiser l'utilisation de l'espace dans l'architecture. L'approche de recuit simulé est utilisée pour placer des blocs sur des modules physiques réservés. Elle consiste à la permutation des différents blocs afin de trouver le placement ayant le moins de coûts en connexions.

**Résumé :** Les méthodes de placement par recuit simulé donnent d'excellents résultats. Cependant, elles sont très couteuses en temps d'exécution. Aussi le recuit simulé fait évoluer une seule solution. Lorsque le problème de placement est multi-objectif, le recuit simulé fournit alors comme résultat une seule solution en essayant de l'optimiser. Ce qui représente un inconvénient puisqu'il existe dans ce cas une multitude de solutions qui ne se dominent pas (compromis entre les objectifs).

### 1.2.2. Le placement basé sur les algorithmes génétiques

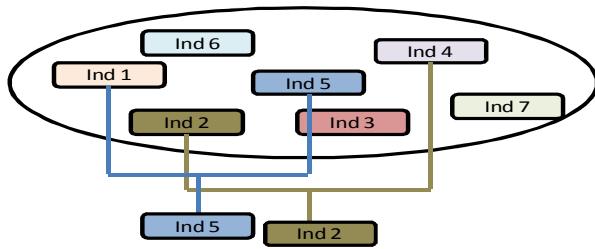

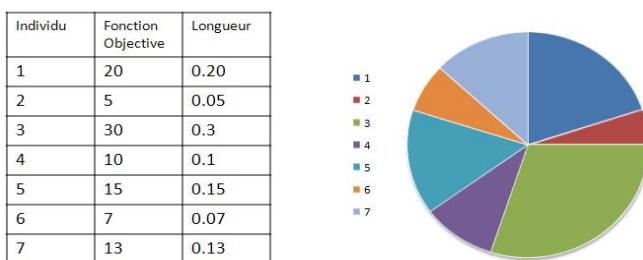

Les algorithmes génétiques sont beaucoup utilisés pour les problèmes d'optimisations. L'idée de base est de suivre la loi de l'évolution naturelle. Chaque solution est représentée comme un individu et l'ensemble de solutions, comme une population. À chaque itération des opérateurs génétiques (sélection, croisement, mutation) sont utilisés pour diversifier la

population. La méthode de placement se diffère par la formulation du problème de placement et le choix des opérateurs.

Kling et al (Kling, et al., 1987) ont défini un outil de placement ESP (Evolution Simulation Placement) pour les architectures à cellules standards. L'objectif du placement est de réduire le coût d'interconnexions. L'algorithme commence par définir un placement initial. Chaque solution représente un placement (association modules-locations). La fonction objective associée à chaque placement est le coût d'interconnexion.

Shahookar et al (Shahookar, et al., 1990) ont développé GASP (Genetic Algorithm Standard cell Placement), un algorithme génétique pour résoudre le problème de placement. L'objectif du placement est aussi de réduire le coût d'interconnexions. Il diffère de l'ESP par les opérateurs utilisés et la manière de gérer le placement. La population initiale de l'algorithme génétique est définie aléatoirement. Chaque individu de la population est représenté par un tableau dont chaque élément contient un ensemble de quatre entiers (numéro de cellule, coordonnée de placement, numéro séquentiel). La fonction d'évaluation est le coût de connexion.

Les auteurs de (Venkataramana, et al., 1993) ont défini un algorithme génétique pour le partitionnement de circuits à placer sur FPGA (FAFPGA). Étant donné un circuit logique, l'objectif est de le partitionner en sous-circuits de manière à ce que le nombre d'entrées pour chaque sous-circuit ne dépasse pas une certaine valeur  $k$  et le nombre de dépendances entre les sous-circuits est minimisé. La population initiale est générée aléatoirement et chaque individu de la population est représenté sur deux chaines de caractères. La première représente le point de partitionnement et la seconde l'état du bloc. Deux fonctions objectives sont utilisées pour évaluer les deux objectifs.

**Résumé :** Le placement par algorithme génétique donne d'excellents résultats, même lorsque le problème est multi-objectif, il permet d'avoir des solutions globales avec des compromis. Cependant, il peut être coûteux en temps d'exécution. Les auteurs de (Kling, et al., 1987) ont comparé l'outil ESP (algorithmes génétiques) à Timberwolf3.2, les résultats ont montré que pour la même qualité de placement l'outil ESP est plus rapide. La comparaison de Timberwolf3.2 et de GASP a montré qu'ils utilisaient globalement le même temps d'exécution pour la même qualité de placement.

Le tableau 1.1 présente une analyse comparative des différentes techniques présentées. Trois métriques ont été comparées : la qualité des résultats (optimalité), la capacité de la technique à réduire le risque d'explosion combinatoire (extensibilité) et la capacité de la technique à gérer les problèmes multi-objectifs (multi-objectifs). Ces métriques sont très importantes pour la définition du modèle de placement. Les algorithmes génétiques sont les plus adaptés pour les problèmes multi-objectifs. Les meilleures solutions de placement sont trouvées au niveau du recuit simulé et des algorithmes génétiques. Lorsqu'on parle d'architecture à grain fin, il faut toujours prévoir des risques d'explosion combinatoire. La méthode de partitionnement est la plus adaptée pour réduire ce risque.

Tableau 1.1 Analyse comparative des techniques de placement

| Technique de placement      | Optimalité | Extensibilité | Multi-Objectif |

|-----------------------------|------------|---------------|----------------|

| Construction incrémentale   | **         | *             | *              |

| Partitionnement (Placement) | **         | ***           | *              |

| Recuit simulé               | ***        | *             | **             |

| Algorithmes génétiques      | ***        | *             | ***            |

\* Pauvre                    \*\* Moyen                    \*\*\* Excellent

### 1.3 Travaux de recherches et méthodes de placement existantes

Cette section est composée de deux sous-sections. La première présente les travaux qui ont permis de définir les architectures nano-composantes. Dans la seconde sous-section, on situe le modèle de placement proposé dans ce mémoire par rapport aux travaux existants.

#### 1.3.1. Travaux de base

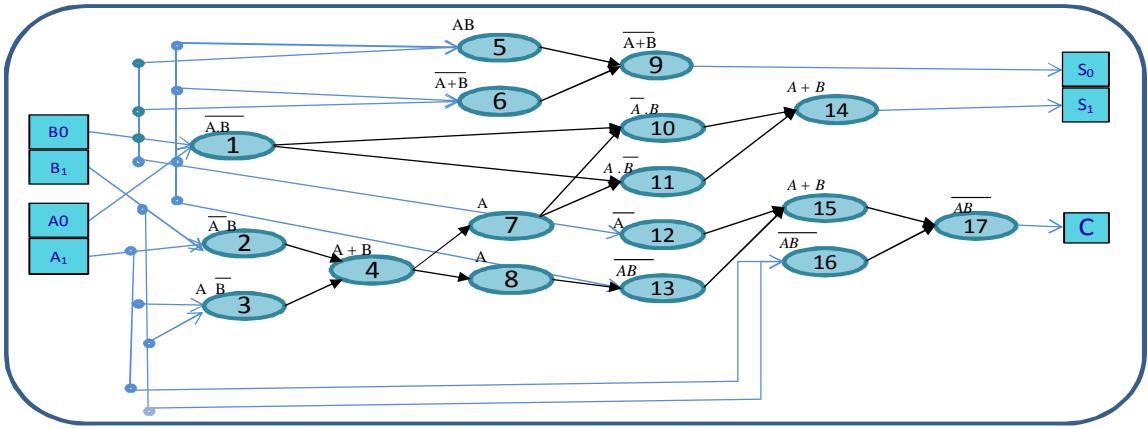

Nos travaux de recherches sont basés sur ceux de O'Connor et al (Liu, et al., 2007) , (O'Connor, et al., 2008). Ils ont défini des architectures nano-composantes à granularité très fine et à caractère dynamiquement configurable. Ces caractéristiques ont été obtenues en utilisant des transistors à nanotube de carbone deux grilles (DG\_CNTFET : Dual\_Gate Carbone NanoTube Field Effect Transistor). Il a été utilisé pour définir une famille de cellules nano-composantes

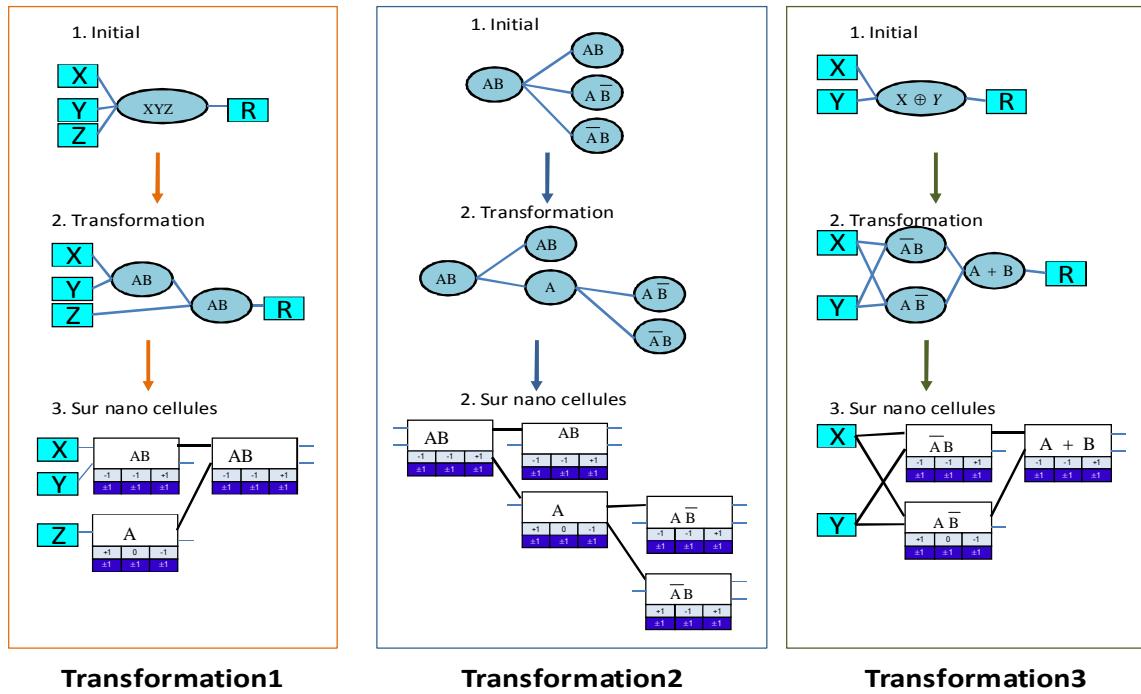

dynamiquement reconfigurables. Ces cellules ont été regroupées dans une structure hiérarchique à deux niveaux pour donner les architectures nano-composantes. Dans le premier niveau, les cellules sont regroupées dans une matrice et interconnectées avec des connexions fixes, dans le second niveau les matrices sont regroupées dans un réseau de matrices dynamiquement interconnectées. Une méthode a été définie (O'Connor, et al., 2008) pour permettre de placer une fonction sur une matrice. Cette méthode consiste à transformer structurellement la fonction de manière à ce qu'elle s'adapte à la structure de la matrice sur laquelle elle va être placée puis de faire l'assignation de cellules aux modules de la fonction. Ils utilisent la méthode de construction incrémentale pour ce placement. La méthode définie cible seulement les fonctions qui peuvent être placées sur une matrice. Dans ce travail, on s'intéresse à comment placer des applications complexes sur ces architectures.

### **1.3.2. Situation du modèle de placement**

Parmi les méthodes de placement présentées ci-dessus, certaines ciblent les architectures à cellules standards et d'autres, les architectures à cellules programmables. Les premières caractérisent l'architecture physique comme un ensemble de locations interconnectées sans prendre en compte plus de caractéristiques structurelles. Les méthodes qui ciblent les architectures FPGA prennent en compte plus de caractéristiques sur les architectures. Cependant, ces caractéristiques sont moins restrictives que celle des architectures nano-composantes que nous ciblons. Dans les architectures nano-composantes les cellules sont connectées de manière statique selon une topologie définie. Aussi la granularité très fine de ces architectures est due au fait qu'une cellule logique traite seulement les opérations qui prennent des entrées codées sur 1 bit. Nos travaux sont alors différents de ceux cités plus haut puisqu'ils ciblent les architectures nano-composantes.

Ainsi, le modèle de placement défini dans nos travaux doit prendre en compte les caractéristiques de reconfiguration dynamique et la structure de ces architectures. Il prend également en compte le concept d'exécution en pipeline (possible grâce à la caractéristique de reconfiguration dynamique) et en parallèle des matrices de l'architecture (possible grâce à la structure de l'architecture). Les objectifs du placement sont de réduire le coût de communication, le nombre de cellules inactives, le coût de configuration et le temps d'exécution. Il s'agit d'un

problème de placement multi-objectif et les méthodes les plus adaptées, pour le résoudre, sont celles des paradigmes d'optimisations métaheuristiques.

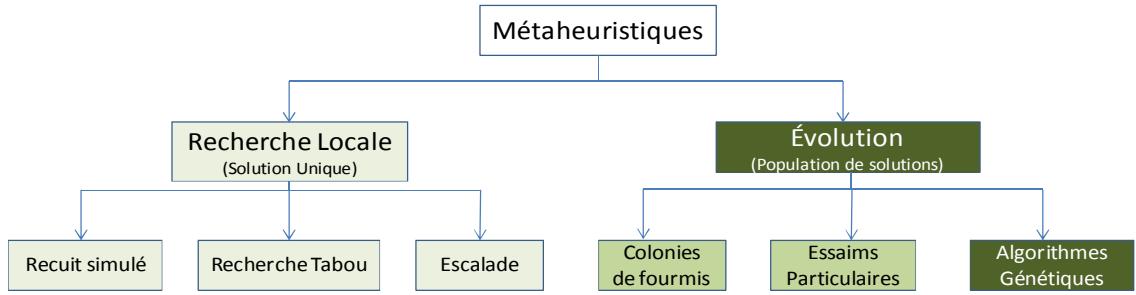

Dans les travaux cités plus haut, on a discuté de deux paradigmes d'optimisation générale : le recuit simulé et les algorithmes génétiques. Il existe cependant plusieurs méthodes d'optimisations pouvant être utilisées pour les problèmes multi-objectifs. Les plus utilisées sont regroupées en deux classes :

- **Les méthodes de recherches locales avec la notion de voisinage et de mouvement** Il s'agit du recuit simulé, la recherche Tabou, recherche par escalade (Hill climbing). Ces méthodes traitent une seule solution en essayant de l'optimiser, lorsqu'il s'agit de problèmes multi-objectifs, il est plus pertinent d'avoir un ensemble de solutions qui permettront de faire des compromis entre les objectifs. Le recuit simulé a fait ses preuves dans le domaine du placement, mais compte tenu de cet inconvénient, il ne représente pas la meilleure solution pour notre problème;

- **Les méthodes de recherche globale basée sur les populations** Il s'agit des algorithmes génétiques, des colonies des fourmis, des essaims particulaires, etc. Ces méthodes traitent un ensemble de solutions et permettent l'utilisation du concept de front de pareto. La colonie de fourmis et les essaims particulaires se basent sur le concept d'auto-organisation (la majorité se dirige vers les bonnes solutions) ces méthodes peuvent facilement converger vers un optimum local ou un état bloqué puisque le résultat suit l'évolution de la masse.

La figure 1.2 illustre la classification des méthodes d'optimisation citées plus haut. Nous croyons que la méthode idéale qui permettra de faire un placement multi-objectif, en gérant un ensemble de solutions et en évitant les états bloqués, est celle des algorithmes génétiques. Elle a déjà fait ses preuves pour la résolution des problèmes de placement et offre un grand espace de solutions tout en permettant d'utiliser le concept de front de pareto.

Figure 1.2 Méthodes métaheuristiques

Néanmoins, pour le problème de placement traitant des fonctions logiques complexes, il peut y avoir des problèmes d'explosion combinatoire. Le tableau 1.1 montre que le partitionnement permet de réduire le risque d'explosion combinatoire. Pour éviter l'inconvénient d'explosion combinatoire nous allons réduire le problème en partitionnant la fonction à placer en sous-fonctions. Aussi, comme (Cong, et al., 1994), nous considérons le sens des dépendances entre les modules afin d'éviter des retours cycliques.

Le modèle de placement va consister donc dans un premier temps à partitionner une fonction en sous-fonctions acycliques, puis à placer les sous-fonctions sur l'architecture nano-composante. Pour que cela puisse être possible, il va falloir au préalable placer chaque sous-fonction sur une matrice nano-composante. O'Connor et al (O'Connor, et al., 2008) ont déjà défini une fonction à cet effet. Dans ce travail, nous avons repris la même méthode en utilisant la théorie des graphes pour faire la similitude entre la fonction et la matrice et faire la restructuration lors du placement en tenant compte des interconnexions.

Comparer aux modèles de placement présentés plus haut, notre modèle à deux contributions importantes :

- Le modèle de placement prend en compte les caractéristiques des architectures nano-composantes pour y placer des fonctions complexes.

- Le modèle de placement combine les algorithmes génétiques et le partitionnement. Ce qui permet d'avoir de bons résultats tout en réduisant, au préalable, le risque d'explosion combinatoire et les coûts de communications.

## 1.4 Résumé

Dans ce chapitre, les travaux reliés à notre domaine de recherche ont été présentés.

Les méthodes de placements ont été présentées par classes de techniques de placement. La liste des techniques présentées n'est pas exhaustive, mais elle regroupe les principales techniques de placement à savoir la construction incrémentale, le placement par partitionnement, le recuit simulé et les algorithmes génétiques. Les techniques utilisées dans ce travail ont été positionnées par rapport à la littérature existante. Les travaux sur lesquelles est basé notre modèle ont aussi été présentés. Il s'agit d'un nouveau paradigme d'architecture nano-composantes dynamiquement reconfigurables. Ce paradigme va être décrit plus en détail dans le chapitre suivant.

## CHAPITRE 2. CONCEPTS DE BASE

Ce chapitre décrit les concepts sur lesquels nous nous sommes basés pour définir le modèle de placement. En occurrence les architectures nano-composantes, quelques concepts de la théorie de graphes et les algorithmes génétiques.

Les méthodes de placement prennent toujours, en entrées, une application et la plateforme d'exécution (architecture). Dans ce travail, les architectures considérées pour le placement sont basées sur un nouveau paradigme d'architectures à granularité très fine et dynamiquement reconfigurables. Ce paradigme d'architecture a été conçu par le groupe «Conception microélectronique hétérogène» de l'Institut de Nanotechnologie de Lyon. Une étude de ces architectures a été faite dans ce travail afin de mieux les comprendre et pour prendre en compte leurs caractéristiques dans le modèle de placement. Par ailleurs, pour des raisons de flexibilité, nous avons modélisé le problème de placement en utilisant des graphes. Plusieurs concepts de la théorie de graphes ont été exploités afin de définir le modèle de placement. Enfin, le problème de placement traité dans ce mémoire est un problème multi-objectif. Pour le résoudre, nous avons choisi le concept des algorithmes génétiques qui est bien adapté pour ce genre de problèmes.

Le chapitre est organisé en quatre sections. La première décrit les architectures nano-composantes. Les concepts, de la théorie de graphes, utilisés sont présentés dans la seconde section. La troisième section est consacrée aux algorithmes génétiques. Enfin, un résumé conclut le chapitre.

### 2.1 Les architectures nano-composantes

Dans le but de poursuivre la loi de Moore, plusieurs dispositifs ont été définis en vue de compléter voire même remplacer les transistors CMOS. Parmi ces dispositifs, ceux de la nanoélectronique semblent être très prometteurs (Transistors à nano fils NWFET, transistors à nanotube de carbone DG-CNTFET,<sup>1</sup>). Ils ont ouvert la voie vers de nouvelles familles d'architectures nano-composantes à caractères dynamiquement reconfigurable. Dans ce travail, nous allons nous concentrer sur les architectures faites à base de nanotube de carbone double grilles (DG-CNTFET). Les architectures nano-composantes peuvent être définies comme un ensemble de cellules logiques dynamiquement reconfigurables faites à base de transistors à

nanotube de carbone (DG-CNTFET). Cette section décrit ces architectures et leurs caractéristiques.

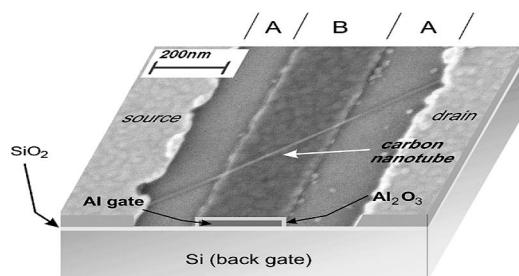

### 2.1.1. Le transistor à nanotube de carbone double grille (DG-CNTFET)

Le transistor DG-CNTFET présente une propriété ambivalente. Cela signifie qu'il peut opérer soit en transistor N-type (porteur de charges négatives) ou P-type (Porteur de charges positives). Comme son nom l'indique il est composé de deux grilles (au lieu d'une dans les transistors en général) : une grille aluminium qui est celle qui a été rajoutée et une grille silicium qui est la grille arrière. La grille aluminium est celle qui régit le transport de charge par le nanotube. La grille arrière quant à elle régit le comportement du transistor :

- Lorsque son potentiel est suffisamment négatif, le dispositif fonctionne en P-type ;

- Lorsque son potentiel est suffisamment positif, le dispositif fonctionne en N-type ;

- Lorsque son potentiel est flottant, le dispositif est dans un état d'arrêt.

Cette ambivalence du transistor DG-CNTFET a été exploitée pour définir des cellules logiques dynamiquement reconfigurables.

La figure 2.1 est une image de Lin et al (Lin, et al., 2005) qui présente une vue transversale d'un CNTFET double grilles. La grille aluminium (grille avant/région B) est placée sous le nanotube de carbone entre la source et le drain (région A). La grille silicium est placée à l'arrière.

Figure 2. 1 Image de la vue transversale d'un CNTFET à double-grille (Lin, et al., 2005)

## 2.1.2. Les cellules logiques dynamiquement reconfigurables

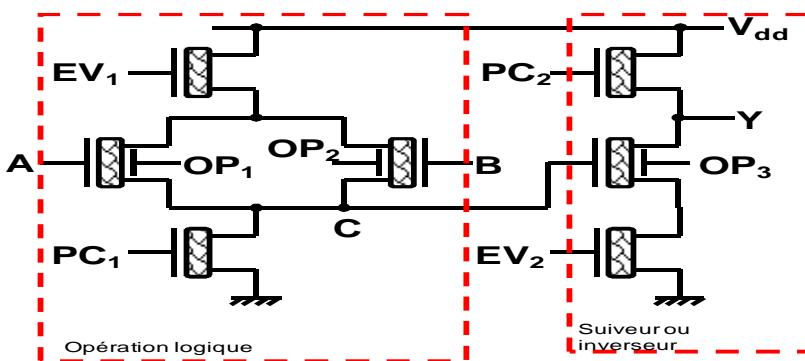

Dans leurs travaux, Liu et al (Liu, 2008) ont développé des cellules logiques dynamiquement reconfigurables : CNT\_DRC\_7T (Dynamic Reconfigurable Cell 7 Transistors).

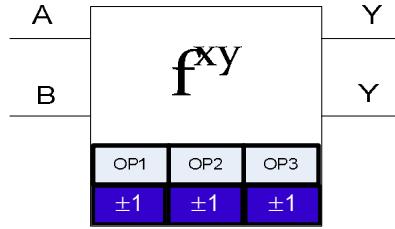

La structure de ce type de cellules est représentée à la figure 2.2. Elle est composée de 7 transistors DG-CNTFETs organisés en deux couches : la première permet de faire une opération logique élémentaire et la seconde sert soit de suiveur ou d'inverseur pour acheminer le résultat. Toutes les variables impliquées dans le fonctionnement de la cellule sont représentées à la figure 2.1

- La cellule logique prend deux entrées booléennes A et B sur lesquelles se font une opération logique ;

- L'opération à faire dépend des trois entrées de contrôle OP<sub>1</sub>, OP<sub>2</sub> et OP<sub>3</sub> qui représentent des potentiels des grilles arrières de 3 des 7 transistors ;

- Quatre signaux d'horloge non chevauchants sont utilisés pour le pré-chargement (PC<sub>1</sub>, PC<sub>2</sub>) et l'évaluation (EV<sub>1</sub>, EV<sub>2</sub>) ;

- Y représente la sortie du circuit qui peut être dupliquée.

Figure 2.2 Structure d'une cellule CNT\_DRC\_7T (Liu, et al., 2007)

Cette cellule peut exécuter 14 opérations logiques différentes selon les valeurs données aux entrées de contrôle pour déterminer le comportement des transistors correspondants : i) +V tension positive pour un comportement P-Type de transistor; ii) 0 tension nulle pour un comportement flottant; iii) -V négative pour un comportement N-Type. Le tableau 2.1 présente la table de vérité associée.

Tableau 2.1 Table de vérité de la cellule CNT\_DRC\_7T

| Configuration |     |     | Opération              |

|---------------|-----|-----|------------------------|

| Op1           | OP2 | OP3 | Y                      |

| +V            | +V  | +V  | $\overline{A+B}$       |

| +V            | +V  | -V  | $A+B$                  |

| +V            | 0   | +V  | $\overline{A}$         |

| -V            | -V  | +V  | $A \cdot B$            |

| -V            | -V  | -V  | $\overline{A \cdot B}$ |

| +V            | -V  | +V  | $\overline{A} \cdot B$ |

| +V            | -V  | -V  | $A+\overline{B}$       |

| 0             | +V  | +V  | $\overline{B}$         |

| 0             | 0   | 0   | 1                      |

| 0             | 0   | -V  | 0                      |

| -V            | +V  | +V  | $A \cdot \overline{B}$ |

| -V            | +V  | -V  | $B+\overline{A}$       |

| +V            | 0   | -V  | A                      |

| 0             | +V  | -V  | B                      |

### 2.1.3. Les matrices à intra-connexions fixes

Figure 2.3 Approche conventionnelle de connexion de cellules

Une des questions encore ouvertes sur les architectures nano-composantes est la manière de connecter les cellules pour les exploiter efficacement. Si l'approche conventionnelle est

utilisée, les cellules seront connectées entre elles par des broches de connexions (switchbox) comme à la figure 2.3. Cette connexion est couteuse puisqu'on parle de cellules nano-composantes et qu'elles sont relativement petites par rapport aux broches de connexion (Liu, et al., 2007).

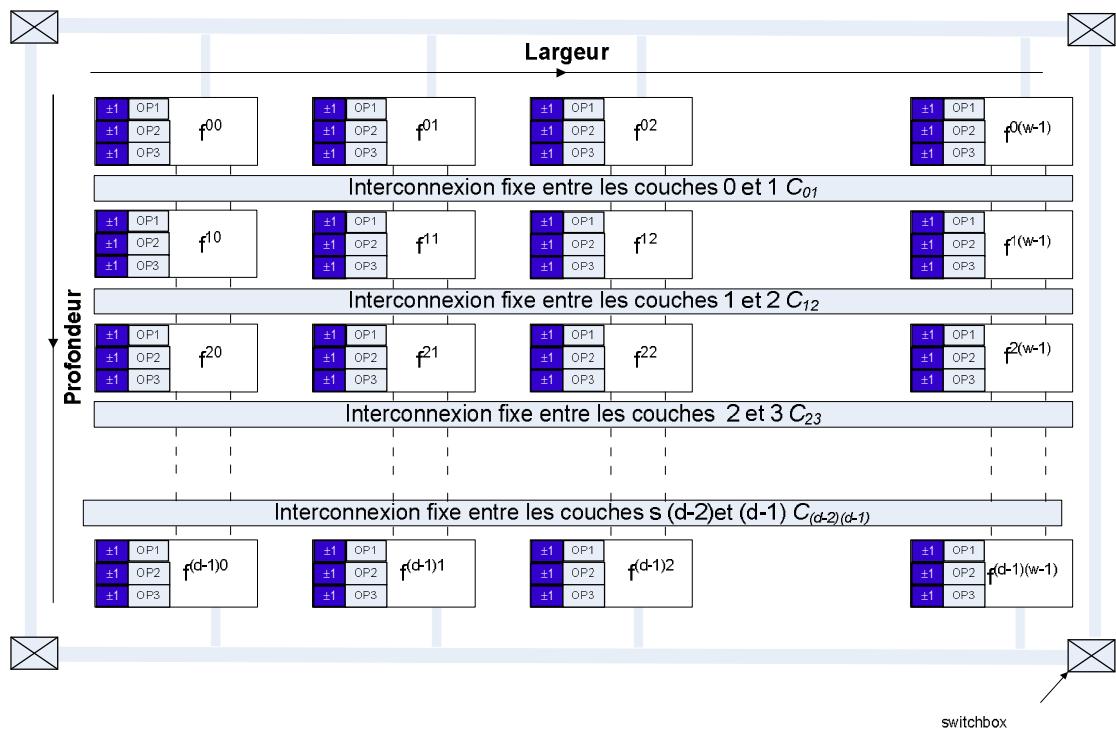

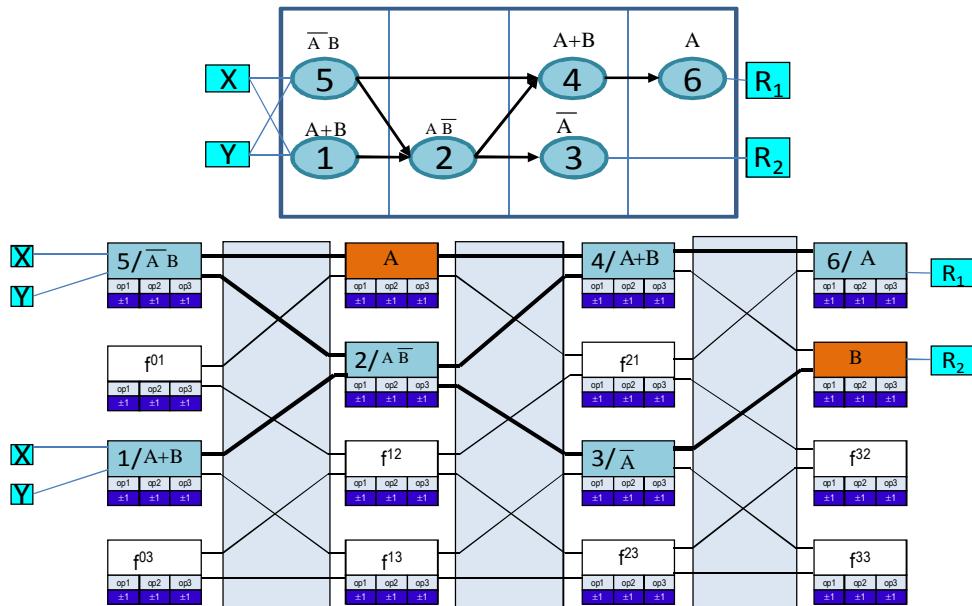

Liu et al (Liu, et al., 2007) ont défini une solution pour des cellules DG\_CNTFET. Il s'agit d'une approche matricielle où les cellules seront regroupées dans des matrices. À l'intérieur des matrices, les cellules sont connectées avec des connexions fixes. Les matrices quant à elles seront connectées avec les broches de connexion. La figure 2.5 montre la structure de l'approche matricielle. Une matrice est alors caractérisée par ses dimensions *Largeur* × *Profondeur* et le type de topologie qui définit les interconnexions intra-matrice. Chaque cellule est caractérisée par sa position (couche x et la position dans la couche y).

Figure 2.4 Approche matricielle de connexion des cellules DG\_CNTFET

Le symbole de la cellule CNT est représenté dans la figure 2.5. On y met en évidence les entrées booléennes A et B, les entrées de contrôles OP1, OP2, OP3 et la sortie dupliquée Y.  $f^{xy}$  représente ses coordonnées (x, y) dans la matrice.

Figure 2.5 Symbole de la cellule logique DG\_CNTFET

Les cellules sont organisées par *couches*, les cellules d'une même couche  $i$  ne communiquent pas entre elles. Elles sont dépendantes des cellules de la couche supérieure  $i+1$  (si elle existe) et les cellules de la couche  $i-1$  (si elles existent) dépendent d'elles.

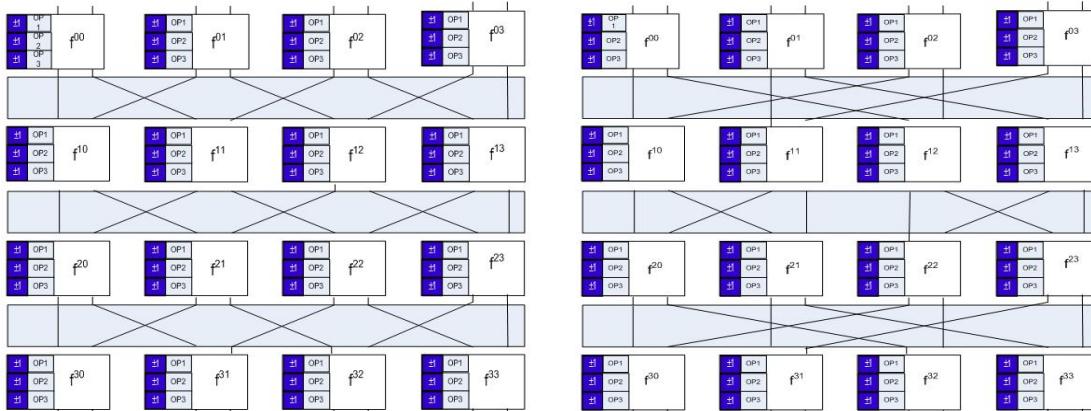

La figure 2.6 présente des exemples de topologies fixes pour les matrices. Dans la topologie Omega, la cellule  $f^{01}$ , par exemple, reçoit toujours les données de  $f^{00}$  et  $f^{02}$  et transmet ses résultats à  $f^{20}$  et  $f^{22}$ . Dans la topologie Banyan, la même cellule recevra ses données de  $f^{01}$  et  $f^{03}$  et transmettra ses résultats à  $f^{20}$  et  $f^{21}$ .

Figure 2.6 Exemple de topologie

#### 2.1.4. Les caractéristiques des architectures nano-composantes

Le paradigme d'architectures nano-composantes présente trois principales caractéristiques :

- ✓ Les architectures ont un caractère de reconfigurations dynamiques ultrafines. Cela signifie que les cellules logiques de cette famille d'architecture peuvent être reconfigurées lors des exécutions.

- ✓ La granularité des architectures est très fine, car les cellules logiques traitent des opérations ayant des entrées codées sur 1 bit;

- ✓ La structure des architectures est particulière et favorise l'exécution en parallèle des matrices. Il s'agit d'une structure à deux niveaux (figure 2.6) :

- Le niveau cellule (Matrices) : Les cellules sont interconnectées par des connexions fixes ;

- Niveau matrice (Réseau de matrices) : Les matrices sont connectées de manières dynamiques.

Figure 2. 7 Hiérarchie des architectures nano composantes

Les architectures nano-composantes dépendent alors de trois paramètres : le nombre de cellules dans les matrices, les topologies d'interconnexion dans les matrices et le nombre de matrices dans le réseau.

## 2.2 Les concepts de théorie de graphes utilisés

La théorie de graphes est utilisée dans divers domaines pour modéliser des situations concrètes comme les interconnexions routières, ferroviaires ou aériennes, les connexions dans les circuits électroniques, les structures chimiques, etc.

Cette section décrit les différents concepts de théorie de graphes utilisés dans le cadre de ce mémoire. La première sous-section définit les graphes acycliques orientés ainsi que leurs utilisations. La seconde sous-section présente deux algorithmes différents pour parcourir un graphe. La dernière sous-section est consacrée aux algorithmes de plus courts chemins.

### 2.2.1. Les graphes acycliques orientés

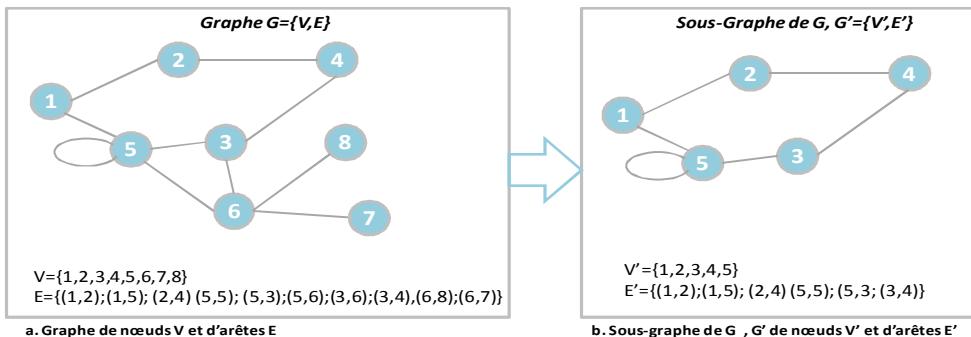

**Définition 2.1 :** Un *graphe*  $G$  permet de représenter des objets (nœuds) et leurs relations (arêtes). Il est défini par le couple  $G = (V, E)$  tel que :

- $V$  est un ensemble fini de nœuds (sommets) ;

- $E$  est un ensemble d'arêtes  $E : V \times V$  reliant des nœuds de  $V$ .

**Définition 2.2 :** Un graphe  $G_0 = (V_0, E_0)$  est dit *sous-graphe* de  $G = (V, E)$  si  $V_0$  est inclus dans  $V$  et  $E_0$  est l'ensemble des arêtes de  $E$  dont les deux nœuds se trouvent dans  $V_0$

La figure 2.8.a présente un exemple de graphe  $G$  avec ses nœuds  $V$  et ses arêtes  $E$ . Un sous-graphe de  $G$  est également présenté dans la figure 2.8.b.

Figure 2.8 Exemple de graphe non orienté et de sous-graphe

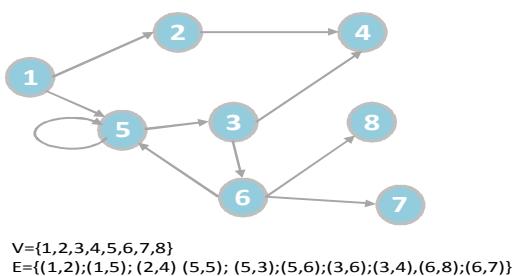

**Définition 2.3 :** Un graphe  $G = (V, E)$  est dit *orienté* lorsque, pour une arête  $(x, y)$ , le sommet  $y$  est en relation avec  $x$  sans que  $x$  soit nécessairement en relation avec  $y$ . L'arête est alors appelée *arc*  $(x, y)$  où le sommet  $x$  est l'origine de l'arc et  $y$  l'extrémité. La figure 2.9.a présente un graphe orienté cyclique qui contient un cycle élémentaire c.à.d. une boucle d'un nœud sur lui-même  $(5,5)$ .

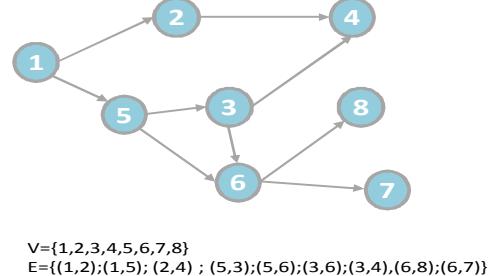

**Définition 2.4 :** Un nœud  $x$  est *voisin* d'un autre nœud  $y$  dans un graphe  $G=(E, V)$  si et seulement si, il existe une *arête*  $(x, y)$  dans  $V$ . Par exemple, dans la figure 2.9.b les *voisins* du nœud 6 sont 5-3-8-7.

**Définition 2.5 :** Un nœud  $x$  est *prédecesseur* d'un autre nœud  $y$  dans un graphe  $G=(E, V)$  si et seulement si, il existe un *arc*  $(x, y)$  dans  $V$ . Par exemple, dans la figure 2.9.b le *prédecesseur* du nœud 6 est 3.

**Définition 2.6 :** Un nœud  $x$  est *successeur* d'un autre nœud  $y$  dans un graphe  $G=(E, V)$  si et seulement si, il existe un *arc*  $(y, x)$  dans  $V$ . Par exemple, dans la figure 2.9.b les *successeurs* du nœud 6 sont 5-8-7.

**Définition 2.7 :** On définit par *graphe acyclique orienté* (de l'anglais Directed Acyclic Graph : DAG), un graphe orienté  $G= (V, E)$  qui ne contient pas de cycle c.-à-d. pour tout sommet  $x$  de  $V$  il n'existe pas des arêtes qui permettent directement ou indirectement de le relier à lui-même. Un graphe acyclique orienté est présenté dans la figure 2.9.b.

a. Graphe orienté cyclique

b. Graphe orienté acyclique

Figure 2. 9 Graphe orienté cyclique et acyclique

La notation DAG est souvent utilisée en informatique pour représenter la théorie de langages, les modèles par couches, les architectures informatiques, les applications informatiques, etc.

## 2.2.2. Les algorithmes de parcours des graphes

Un parcours de graphe consiste à explorer le graphe par ses nœuds ou ses arcs et à les ordonner pour effectuer des traitements. Selon l'ordre souhaité, plusieurs algorithmes de parcours existent. Les plus courants sont le parcours en largeur et le parcours en profondeur.

### 2.2.2.1. Le parcours en largeur

Le parcours en largeur d'un graphe  $G= (V, E)$  consiste à partir d'un nœud  $x$  de  $V$ , de traverser tout nœud  $y$  de  $V$ , directement accessible à partir de  $x$  à condition que tous les arcs

entrants à y aient été visités. Le parcours se fait ainsi récursivement jusqu'à ce que tous les nœuds de V soient traversés. La figure 2.10 montre un exemple de solutions possibles du parcours en largeur en commençant par le nœud 1 du graphe. Les nœuds accessibles à partir de 1 sont 2 et 5, l'itération suivante va « découvrir » les nœuds accessibles à partir de 2 : 4 et à partir de 5 : 3 et 6. Les successeurs de 3 ayant déjà été explorés, la dernière itération va découvrir les successeurs de 6 : 8 et 7.

Figure 2. 10 Parcours en largeur

### 2.2.2.2. Le parcours en profondeur

Contrairement au parcours en largeur, le parcours en profondeur explore à fond un nœud x pour découvrir tous les nœuds qui sont accessibles *directement ou indirectement* à partir de x. L'exploration se fait ainsi jusqu'à ce qu'on tombe sur un nœud qui n'a plus de successeurs non explorés, puis on fait un retour en arrière vers le nœud père pour reprendre l'exploration à partir d'un autre nœud. La figure 2.11 illustre un exemple de solutions pour le graphe DAG présenté plus haut. Le parcours commence par le nœud 1, on prend un de ses successeurs le nœud 2 par exemple et on explore aussi les voisins du nœud 4. Le nœud 4 n'ayant pas de successeurs on revient à 1 pour prendre le nœud 5. On prend un de ses successeurs le nœud 3 par exemple. Le nœud 4 ayant déjà été exploré, on parcourt le nœud 6 puis ses successeurs 8 et 7.

Figure 2. 11 Parcours en profondeur

### 2.2.3. Les algorithmes de plus courts chemins

Le cheminement est un problème très courant pour minimiser ou maximiser directement ou indirectement les coûts des fonctions économiques (temps, argent, ressources). On le retrouve notamment dans les domaines de transport, le routage de paquet dans les réseaux, les interconnexions de communications, etc. L'objectif est de trouver un chemin entre une source et une destination afin d'optimiser une fonction économique.

**Définition 2.8 :** On appelle un *chemin* C dans un graphe  $G = \{V, E\}$ , une liste de nœuds appartenant à V,  $C = \{x_1, x_2, \dots, x_k\}$ , telle que pour tout couple  $(x_i, x_{i+1})$ , il existe une arête correspondante dans E.

Le plus court chemin entre deux nœuds  $x_1$  et  $x_k$  est calculé dans un graphe pondéré c.-à-d. toutes les arêtes du graphe ont une valeur. La longueur d'un chemin est alors la somme des poids des arêtes/arcs qui le composent.

$$\text{Longueur } (C = \{x_1, x_2, \dots, x_k\}) = \sum_{i=1}^{k-1} (x_i, x_{i+1})$$

Le plus court chemin entre deux nœuds est le chemin dont la longueur est la plus petite. Dans le graphe de la figure 2.12, le plus court chemin entre le nœud 1 et le nœud 4 est le chemin de longueur 4 passant par 5,3.

Figure 2. 12 Plus court chemin

Plusieurs algorithmes ont été définis pour déterminer le plus court chemin entre deux nœuds  $n_1, n_2$  dans un graphe pondéré. Le plus utilisé est celui de Djikstra. L'idée est d'explorer le graphe et de calculer, au fur à mesure, les distances des nœuds parcourus de  $n_1$  jusqu'à atteindre  $n_2$ .

Un algorithme appelé *K-plus courts chemins (K-Shortest paths)* permet d'avoir en sortie K différents courts chemins ordonnés par ordre décroissant de longueur de chemins (Lau, 1989). Il donne en sortie K plus courts chemins siels existent sinon il donne les plus courts chemins existants. Par exemple dans la figure 2.12, pour les plus courts chemins entre les nœuds 1 et 4, même si le paramètre K est supérieur à 2, on aura en sortie que les deux chemins existants dans l'ordre suivant : { {1, 5, 3, 4} ; {1, 2, 4} }.

## 2.3 Les Algorithmes génétiques

Cette section est consacrée aux algorithmes génétiques. La première sous-section décrit le fonctionnement général des algorithmes génétiques. La seconde est consacrée aux différents aspects d'un problème qui doivent être formulés pour appliquer les algorithmes génétiques. Les opérateurs génétiques sont présentés dans la troisième sous-section. La dernière sous-section décrit la manière dont les algorithmes génétiques gèrent les solutions dans les problèmes multi-objectifs.

### 2.3.1. Fonctionnement général

Figure 2. 13 Fonctionnement des algorithmes génétiques

L'algorithme génétique commence avec une population initiale dont les individus sont évalués en fonction des objectifs et des contraintes du problème à résoudre. Cette population est ensuite diversifiée en utilisant des opérateurs génétiques (sélection, croisement, mutation) pour reproduire les individus. La reproduction est faite à plusieurs reprises jusqu'à ce que le critère

d'arrêt (nombre d'itérations en général) de l'algorithme soit atteint. La figure 2.13 résume le fonctionnement général des algorithmes génétiques.

### 2.3.2. Formulation du problème d'optimisation