| <b>Titre:</b><br>Title:                                                                                                                                           | Linc transmitter for linear amplification systems |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| Auteur:<br>Author:                                                                                                                                                | Ying Tian                                         |  |

| Date:                                                                                                                                                             | 2005                                              |  |

| Туре:                                                                                                                                                             | Mémoire ou thèse / Dissertation or Thesis         |  |

| <b>Référence:</b> Tian, Y. (2005). Linc transmitter for linear amplification systems [Master's thes<br>Citation: Citation: https://publications.polymtl.ca/23619/ |                                                   |  |

# **Document en libre accès dans PolyPublie** Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/23619/ |

|------------------------------------------|----------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Fadhel M. Ghannouchi                   |

| Programme:<br>Program:                   | Unspecified                            |

### UNIVERSITÉ DE MONTRÉAL

### LINC TRANSMITTER FOR LINEAR AMPLIFICATION SYSTEMS

#### YING TIAN

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE MAÎTRISE EN SCIENCES (GÉNIE ÉLECTRIQUE) APRIL 2005

© Ying Tian, 2005

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire est intitulée :

### LINC TRANSMITTER FOR LINEAR AMPLIFICATION SYSTEMS

présenté par : Ying Tian

En vue de l'obtention du diplôme de : Maîtrise en Sciences Appliquées

A été dûment accepté par le jury d'examen constitué de :

KE WU, Ph.D., président <u>FADHEL M. GHANNOUCHI</u>, Ph.D., membre et directeur de recherche <u>AMMAR B. KOUKI</u>, Ph.D., membre

# DEDICATE

To my husband Shi, Jiang chuan

And my son Shi, Bo wen

### ACKNOWLEDGEMENTS

This research project of my master's degree of applied sciences has been studied from January 2002 to May 2004 at Centre de Recherches Avancées en Micro-ondes et Électronique Spatiale, Département de génie électrique et de génie informatique, École Polytechnique de Montréal. It is my great pleasure to express sincere gratitude to all these who have contributed to this research work in PolyGRAMES research center.

I have a deep gratitude to Professor Fadhel M. Ghannouchi, project director, who gives me a chance to carry out this research work. In his constant support, invaluable advice, guidance, and warm encouragement, I had completed this project. At the meantime, his technical suggestions and criticisms are appreciated and important throughout the whole work.

I would like to express the thankfulness to Dr. Slim Boumaiza, who supplies his assistance for digital SCS in this project and my colleagues Mr. Taijun, Liu and Ms. Jing Li, who have offered me many technical advices and discussions about DSP and program code. Other colleagues Mr. Hammi Oualid and Mr. Bouchaib Hraimel who give me help.

I am also thankful to Mr. Dube Steve for his contribution in circuit fabrication and Mr. Rene Archambault for his assistance in computer software.

Finally, my thanks go to my husband Jiangchuan Shi who gives me understanding, support and cares in daily life. And my lovely son, Bowen Shi, he can study by himself consciously without my more attentions.

V

### **ABSTRACT**

This project is dedicated to develop and implement a practical linear amplification with nonlinear components (LINC) transmitter for modern wireless communication systems. Several aspects of design for the digital signal component separator (DSCS) and high performance high efficiency power combiner are presented in this thesis.

A crucial function of LINC is the signal component separator (SCS). A modern version, using a standard DSP device, was first evaluated. It has two major disadvantages: low bandwidth and high power consumption. Next, a new digital signal separation (NDSCS) architecture, based on an FPGA (Field-Programmable Gate Array), is presented and used to enhance the flexibility and the speed of the signal processing. An FPGA provides a means of arranging the arithmetic blocks and registers to fit the algorithms, and to choose an arbitrarily word length so as to significantly reduce power consumption and increase bandwidth. Two effective solutions were implemented: a one-dimensional look-up table and a square-root function block. Both were designed using an Altera Quartus II FPGA kit, which uses a pipelining technique that improves speed. The equivalent designs were also simulated in MATLAB's Simulink. These simulations provide design verification. The experimental results demonstrate that this new architecture is effective and efficiently combines flexibility and performance. Also shown is that the LUT method used is more precise but has less speed than the square-root function block.

Next, a new combiner is proposed. Two of the basic power combiners' (isolated

and non-isolated) voltage / current models are analyzed and a variable reactive termination combiner (VRTC) is proposed, developed and implemented. The proposed model's load impedance, presented to the power amplifiers, is varied according to the amplitude of the input signal in a way that optimizes the LINC transmitter's efficiency. With this new power combiner, unlike most past designs, it is possible to obtain high power-added efficiencies (PAE) at the full dynamic output power range of the amplifier. The prototype is constructed with a balun transformer and two reactive terminations in which the shunt susceptance is varied parametrically with the degree of phase shift in the modulation. It is shown that this approach can improve the overall efficiency in the LINC system.

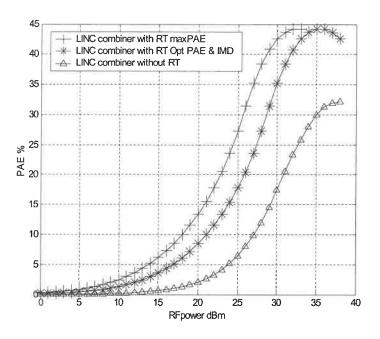

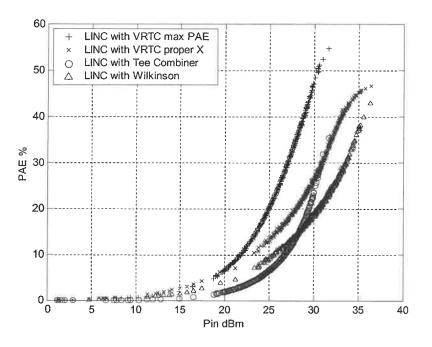

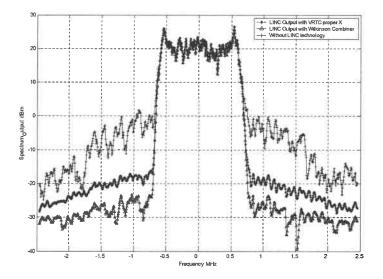

Agilent's advanced design system (ADS) software is used to compare this new combiner's effect on linearity and efficiency with three other classical power combiners. A two-tone signal and an IS-95 signal were used for the comparison. The results indicate that the new combiner is more effective than the others in improving the efficiency and does so with a lesser degradation in linearity. Using a transmitter with class AB power amplifiers having 23.5% efficiency at 2.14 GHz, the overall average efficiency of LINC system using the new combiner is 17.6%, whereas it is only 9.1% using a Wilkison combiner. The linearity was more intact with some of the classical, but less efficient, combiners, but the best compromise between efficiency and linearity was struck with this design. Suggestions for future work on this subject is also described.

# RÉSUMÉ

Ce projet est consacré au développement d'un transmetteur LINC et à son implantation dans les systèmes modernes de communication sans fil tels que le IS95, le WCDMA et le CDMA2000. Plusieurs aspects de la conception du diviseur de signal (SCS) numérique, ainsi qu'un combineur de puissance à rendement élevé et à haute performance sont présentés dans cette thèse.

L'élément clé du transmetteur LINC est le diviseur de signal (SCS). La technologie de traitement du signal numérique (DSP) utilisée dans le diviseur de signal du transmetteur LINC s'avère le meilleur choix. Tout d'abord une version moderne du diviseur de signal utilisant un dispositif DSP standard a été évaluée. Ce dernier dispositif comporte deux désavantages importants: une faible largeur de bande et une consommation d'énergie élevée. Ensuite, un nouveau diviseur de signal numérique a été développé. Celui-ci comprend un FPGA (Field-Programmable Gate Array), qui améliore la flexibilité des algorithmes, augmente la vitesse du traitement des signaux et réduit la consommation d'énergie. Il représente une solution efficace pour réaliser le diviseur de signal numérique. Il nous donne la possibilité de manipuler les blocs et les registres arithmétiques pour mieux adapter les algorithmes, et permet de choisir une longueur de mot pour répondre à nos spécifications. L'apport en termes d'économie d'énergie et d'augmentation de la largeur de bande, est significatif.

Deux designs ont été implantés au FPGA (un Altera Quartus II FPGA kit) ; le premier comprend une table unidimensionnelle (look-up-table) et le seconde, un bloc de fonction de racine carrée. La technique "pipelining" est employée dans les deux designs pour améliorer le temps de calcul. Elle a été utilisée fréquemment dans les systèmes nécessitants des calculs intensifs. Les simulations faites dans Simulink de Matlab ont servies à vérifier ces deux designs.

Le diviseur de signal numérique (FPGA) a été réalisé avec la carte de développement APEX DSP d'Altera. Les mesures de ce signal démontrent que cette nouvelle architecture est plus flexible, précise et performante qu'une conception utilisant un dispositif DSP. En plus, la version du 'look-up-table' était plus précise mais moins rapide que celle du bloc de fonction de racine carrée.

Ensuite, deux catégories de combineurs de puissance, (isolée et non isolée) ont été comparées selon une analyse de voltage / courant. L'impédance de charge, vue de l'amplificateur de puissance, varie en fonction de l'amplitude du signal. La valeur de réactance de shunt du nouveau combinateur s'adapte aux signaux pour améliorer l'efficacité énergétique pour tous les niveaux de puissance sortant du transmetteur. Par conséquent, l'efficacité du système est maximisée. Le combineur a été élaboré en utilisant un transformateur "balun", qui a un faible coût et de petites dimensions. Deux terminaisons réactives ont été réalisées avec des circuits LC où la valeur de la susceptance de shunt varie en fonction de la phase modulée.

La simulation des quatre différents combineurs a été exécutée avec ADS (Advanced Design System) d'Agilent, en utilisant un signal à deux fréquences et un signal IS-95. Les résultats obtenus indiquent que le nouveau combineur, contrairement au trois autres, améliore davantage l'efficacité sans dégrader pour autant la linéarité. Deux amplificateurs de puissance de classe AB ayant une efficacité de 23.5% (fréquence centrale 2.14 GHz), ont été utilisés. Avec le nouveau combineur, une efficacité de system moyenne de 17.6% est atteinte pour une linéarité équilibrée, comparée à 9.1% en utilisant un combinateur classique de Wilkinson. Le meilleur compromis entre l'efficacité énergétique et la linéarité du signal a été obtenu avec ce nouveau combinateur.

Les travaux futurs sur ce sujet sont décrits.

### **CONDENSE EN FRANÇAIS**

# TRANSMETTEUR LINC POUR LES SYSTÈMES D'AMPLIFICATIONS LINÉAIRES

#### 0.1 Introduction

Les systèmes de communication modernes exigent des techniques efficaces telles que des types de modulation sophistiqués, des algorithmes complexes de démodulation et une détection des erreurs d'une très haute qualité. Ainsi, il est possible d'obtenir des canaux de transmission à rendement élevé et sans perte. Cependant, ces types de modulation sophistiqués génèreront des signaux d'enveloppe variable et de crête sensiblement plus élevée que la moyenne de sorte qu'un amplificateur de puissance RF linéaire est requis. Il est donc nécessaire de linéariser un amplificateur de puissance nonlinéaire pour rencontrer à la fois les exigences de haute linéarité et de faible consommation de puissance.

Bon nombre de techniques de linéarisation sont disponibles pour les applications commerciales. Certaines de ces techniques visent les systèmes à bande étroite tandis que d'autres, tel que la post-compensation, sont prometteuses pour les systèmes à large bande. Il n'est pas encore possible d'identifier des solutions économiques ayant toute les caractéristiques requises mais de telles solutions viendront dans le futur.

Les techniques appropriées de linéarisation sont la boucle cartésienne, la boucle polaire, la prédistortion adaptative en bande de base, la technique d'élimination et de restauration de l'enveloppe (EER), l'amplification linéaire par technique d'échantillonnage (LIST), le modulateur universel combiné à boucle verrouillée (CALLUM), et l'amplification linéaire par composants non-linéaires (LINC) qui fait d'ailleurs l'objet de cette thèse. Les techniques de pré- et post-compensation peuvent opérer sur de larges bandes. Cependant, à ce jour aucune technique ne permet d'atteindre à la fois les exigences de linéarité et d'efficacité sur une bande de fréquence suffisamment large.

La technique LINC est l'une des techniques par sommation de vecteurs permettant de réaliser des amplificateurs de puissance RF à efficacité élevée tout en ayant, en théorie, une très bonne linéarité. Le principe consiste à prendre une forme d'onde modulée et de la décomposer en deux signaux à enveloppe constante, mais déphasés, qui alimentent ensuite des amplificateurs de puissance non-linéaires très efficaces. Il n'y a alors pas de distorsion d'intermodulation en raison de l'amplitude constante de ces signaux. En conséquence, des amplificateurs efficaces, mais non-linéaires, peuvent être utilisés pour remplacer les amplificateurs linéaires de d'autres architectures. Suite à l'amplification et la recombinaison, une version amplifiée du signal d'entrée est obtenue en sortie.

#### 0.2 Séparation des composants du transmetteur LINC

Le transmetteur LINC permet d'obtenir une grande efficacité énergétique et les signaux indésirables sont réduitsde l'ordre de 30-60 dBc. Cependant, il est limité par la sensibilité du processus de conception pour obtenir deux amplificateurs parfaitement balancés. Cette sensibilité est principalement provoquée par le composant séparateur de

signal (Signal Component Separator) qui divise le signal de la source en deux signaux constants modulés en phase. La mise en application du SCS a été un des problèmes principaux dans le transmetteur LINC. Un premier article a suggéré une solution complètement analogique qui n'a pas eu un réel succès. Il est aujourd'hui possible d'implanter le SCS au niveau logiciel par les techniques de traitement numérique des signaux et l'utilisation d'un dispositif DSP standard permettant une précision suffisante au prix de contraintes de largeur de bande et de consommation de puissance. Cette solution est supportée par des conceptions fondées sur un processeur de signal numérique (DSP) ayant des restrictions dues au temps de calcul, au temps de conversion des convertisseurs A/N et N/A, au bruit de quantification et au coût.

Puisque la plupart des fabricants fournissent des logiciels d'aide à la conception pour leurs propres puces, la conception initiale, le coût et le délai d'arrivée sur le marché sont réduits et flexibles. Le FPGA (Field-Programmable Gate Array) est le meilleur choix pour les applications flexibles car il permet d'apporter des changements à la conception sans exiger de changements physiques au circuit imprimé, et ce aussi longtemps que les fonctions révisées sont compatibles avec l'espace disponible sur la même puce programmable. Dans ce projet, une nouvelle architecture numérique de séparation des composants du signal à base de FPGA permet d'avoir une architecture, une structure de bus et une mémoire adaptée aux besoins spécifiques de chaque utilisateur, et ce, à moindre coût et pour de bonnes performances. Le dispositif à haute vitesse FPGA qui remplace le DSP standard traitera tous les algorithmes avec plus de flexibilité. Nous pouvons améliorer la largeur de bande et réduire la consommation d'énergie si nous choisissons des convertisseurs A/N et N/A avec un taux d'échantillonnage élevé.

#### 0.3 Techniques de combinaison du transmetteur LINC

Simultanément, la réalisation d'un combineur pouvant atteindre une efficacité de puissance ajoutée (PAE) élevée est un autre facteur pivot pour obtenir une efficacité élevée avec une bonne linéarité.

Deux catégories de combineurs de puissance, isolés et non isolés, peuvent être utilisées dans les transmetteurs LINC. Le combineur de puissance isolé, tel le combineur Wilkinson, a une faible efficacité énergétique car la partie non utilisée du signal est dissipée par une charge passive. Même si des amplificateurs très efficaces étaient utilisés, une efficacité globale supérieure à 10% serait difficile à atteindre. Le combineur non isolé, tel le combineur à terminaison réactive variable, présenté dans ce travail, améliore l'efficacité puisque la variation de l'impédance dans le temps altère la consommation de puissance DC lorsque la puissance de sortie varie. Donc, l'efficacité globale de l'amplificateur LINC reste suffisamment élevée sur la majeure partie de la plage de puissance de sortie. Il y a une grande opportunité pour accroître significativement l'efficacité si les erreurs de phase et d'amplitude produites par cette approche peuvent être suffisamment bien contrôlées.

Pour réaliser la modulation de la charge en fonction du niveau de puissance de sortie désiré, les vecteurs doivent être des signaux représentant le courant ou la tension. Un système LINC fondé sur des sources de tension idéales peut être quelque peu indépendant du niveau de puissance de sortie et de l'efficacité. Ce travail fournit un moyen qui optimise l'efficacité du transmetteur LINC en fonction des statistiques de modulation d'amplitude. Il est démontré que l'ajout d'une susceptance parallèle à la source de tension améliore grandement le ratio d'efficacité crête à la moyenne. L'efficacité moyenne de plusieurs signaux modulés en amplitude est déterminée en fonction de la réactance parallèle. La sélection de la réactance parallèle correspondant aux signaux permet de maximiser l'efficacité à une puissance de sortie donnée. Ce combineur est utilisé pour générer une porteuse modulée en amplitude en combinant deux porteuses de même fréquence, modulées en phase et d'enveloppe constante. De plus, il peut être construit en utilisant des éléments purement réactifs de sorte qu'aucune énergie n'est dissipée.

Typiquement, les systèmes déphasés Chireix [19] représentés par un circuit sommant coupleur-transformateur et un coupleur en ligne de transmission avec une réactance parallèle, permettent d'appliquer des variations conjuguées de charge aux amplificateurs de puissance non linéaires. Cependant, le maximum d'efficacité est atteint pour un niveau de sortie spécifique car la valeur de la réactance parallèle est fixe. Par conséquent, un des objectifs majeurs est d'implanter une nouvelle architecture de recombinaison pour obtenir une efficacité énergétique plus élevée aux sorties. Ce circuit peut être construit avec un transformateur d'impédance et des terminaisons réactives variables. En choisissant de façon appropriée la valeur de la réactance parallèle, il sera possible au combineur LINC d'atteindre son efficacité énergétique maximale. De plus, la réactance peut être optimisée pour rencontrer à la fois les critères d'efficacité et de linéarité. Pour augmenter l'efficacité moyenne de modulation ayant un haut ratio crête par rapport à la moyenne, la terminaison réactive et le circuit de combinaison sont appliqués pour atteindre à la fois une efficacité élevée et une bonne linéarité.

#### 0.4 La mise en application d'un transmetteur LINC

Ce travail de recherche développe et réalise un transmetteur LINC pratique fondé sur des techniques de traitement de signal numérique et des technologies efficaces de combinaison. Des améliorations de ces deux technologies fournissent des solutions pour le compromis difficile entre efficacité et linéarité élevée du transmetteur LINC.

#### 0.4.1 Nouveau séparateur numérique de composants

Le séparateur de composants du signal décompose le signal source S(t) en deux signaux d'amplitude constante modulés en phase et décalés de  $\pm \theta$ , S<sub>1</sub>(t) et S<sub>2</sub>(t). Ces signaux modulés sont le signal en phase I<sub>1</sub>(t) / I<sub>2</sub>(t) et le signal en quadrature Q<sub>1</sub>(t) / Q<sub>2</sub>(t). Ils permettent d'obtenir l'enveloppe constante des signaux modulés en phase et en quadrature.

Un nouveau séparateur numérique de composants du signal (NDSCS) basé sur la technologie FPGA nous fournit une solution pour sélectionner arbitrairement la longueur des mots et minimiser le taux d'échantillonnage de sorte à rencontrer nos critères de conception. En effet, par rapport au processeur DSP, le FPGA devient la solution de

choix pour réaliser un séparateur numérique des composants d'un signal pour un transmetteur LINC en raison de la personnalisation de la conception.

Le NDSCS est mis en application sur une carte de développement Altera APEX DSP. Elle permet d'éviter les longs mots peu pratiques, les faibles taux d'échantillonnage, et les lents temps d'exécution lors du traitement du signal. Elle fournit également une architecture polyvalente pour accélérer les performances en plus d'avoir davantage de puissance de traitement des données brutes qu'un processeur DSP standard. Une réalisation matérielle peut être modélisée avec Simulink de MATLAB pour l'analyse et la vérification du concept. Le choix d'un dispositif FPGA qui s'adapte à tous les algorithmes permet d'obtenir rapidement un prototype. En outre, il est nécessaire de choisir des convertisseurs analogique-numérique (A/N) et numérique-analogique (N/A) ayant des taux d'échantillonnage suffisant. Ainsi, les exigences des conceptions des systèmes de traitement de signal à haut débit sont satisfaites.

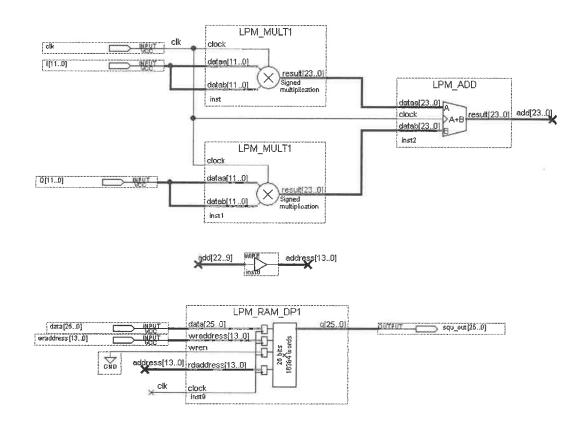

Autant les méthodes utilisant le principe des tables unidimensionnelles (Look-Up-Table) que celles utilisant des blocs de fonctions en racine carrée ont été conçues dans Quartus II, le logiciel de conception du FPGA. Une LUT unidimensionnelle sans mémoire, qui est adressée I-carré plus Q-carré ( $I^2 + Q^2$ ) avec des mots de 14 bits, stocke 26 bits de données calculées dans une mémoire à accès aléatoire (RAM). Deux bascules « flip-flops » paramétrables de type D sont employées comme blocs à délai temporel pour synchroniser les données afin d'obtenir la sortie correspondante.

Une méthode alternative est de créer en VHDL (Very High Speed Integrated circuit Hardware) un bloc de fonction dédié en racine carrée qui aurait un temps

d'exécution faible et présenterait de bonnes performances. La technique dite de "Pipelining" est nécessaire pour améliorer les performances. La combinaison de l'architecture registre-amélioré et de la connaissance du délai est une alternative attrayante aux FPGAs pour la mise en application de conceptions canalisées complexes dans des CPLDs, et avec de meilleures performances. Toutes les conceptions ont été simulées avec Simulink de Matlab pour valider le concept.

De plus, des mesures expérimentales démontrent que ce nouveau séparateur numérique de signal peut minimiser la longueur des mots avec une précision acceptable de sorte à réduire la consommation d'énergie et augmenter la largeur de bande.

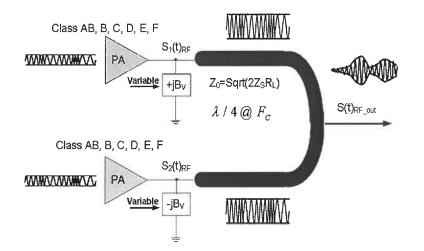

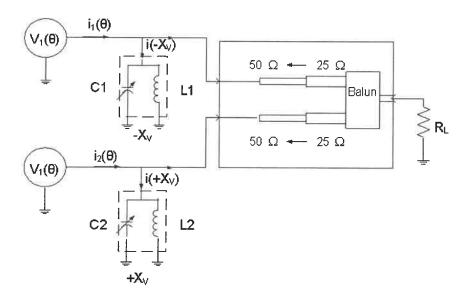

#### 0.4.2 Combineur à terminaison réactive variable

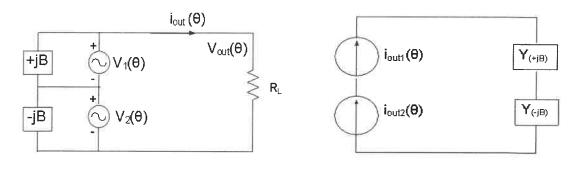

Le combineur à terminaisons réactives variables consiste en un transformateur d'impédance et deux éléments variables en parallèle sur deux branches. En comparaison avec un système à déphasage Chireix, ce modèle a deux susceptances parallèles, +Bv et – Bv, pour optimiser l'efficacité globale au lieu de la susceptance de compensation fixe  $\pm B$ .

Le choix de la valeur des suceptances correspondant aux signaux peut améliorer l'efficacité à une amplitude de sortie donnée. L'impédance des éléments réactifs varie alors selon le décalage en phase,  $\theta$ , entre les deux signaux S<sub>1</sub> et S<sub>2</sub>. Donc, la tension de sortie peut être en phase avec le courant. La satisfaction de ce critère est le meilleur choix pour la combinaison LINC.

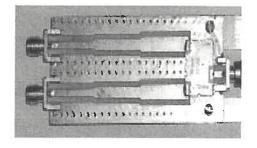

Le combineur pratique est construit à l'aide d'un transformateur d'impédance non isolé et d'éléments purement réactifs de sorte qu'aucune énergie ne soit dissipée. Les terminaisons réactives sont alors réalisées en combinant des condensateurs variables et des inductances fixes en parallèle. L'admittance est variée avec le décalage en phase  $\theta$  en changeant la valeur du condensateur ou de l'inductance. Un transformateur balancé à non balancé (balun) miniature, à faible coût et de performance suffisante est utilisé pour convertir l'impédance du port balancé au port non balancé en sortie. Ce combineur LINC amélioré n'utilise que des éléments réactifs et présente une charge n'ayant aucune partie imaginaire aux deux amplificateurs d'enveloppe constante pour tous les niveaux de la sortie modulée. Ainsi, le courant et la tension sont en phase au niveau de la charge.

Les éléments réactifs du circuit LC ont respectivement une susceptance capacitive +jBv et inductive -jBv. Ils ajustent le courant lorsque les signaux sont recombinés dans le combineur non isolé suivit de la charge désirée R<sub>L</sub>. Si la réactance de la terminaison est choisie de façon appropriée, le courant sera additionné au courant de sortie de sorte que le courant total  $i_1/i_2$  sera en phase avec la tension.

La réactance X est fonction de la phase modulée  $\theta$ . Lorsque X( $\theta$ ) est négatif, -X indique un élément capacitif et sera infini si  $\theta$  est égale à zéro ou 90°. Pour le cas où  $\theta$ =45°, X aura une réactance capacitive (-k\*R<sub>L</sub>).

Lorsque X( $\theta$ ) devient positif, +X indique une réactance inductive (+k\*R<sub>L</sub>) à  $\theta$ =45° et sera infinie si  $\theta$  égale 0° ou 90°.

Les circuits réactifs peuvent être ajustés pour obtenir des valeurs de réactance allant de l'infini à  $\pm k R_L$  (inductif or capacitif). Nous considérons que les inductances L<sub>1</sub> et L<sub>2</sub> ont la même valeur et que les condensateurs C<sub>1</sub> et C<sub>2</sub> peuvent être ajustés selon l'écart de phase  $\theta$ . Les circuits sont ajustés pour résonner à la fréquence porteuse ce qui produit une réactance infinie. Lorsque la valeur du condensateur surpasse le point de résonance, le circuit devient capacitif. Inversement, lorsque la valeur du condensateur se situe sous la valeur de résonance, le circuit devient inductif.

Le module 3W525 de Anaren (fréquence 1.8-2.5 GHz) est utilisé en tant que transformateur d'impédance non isolé dans ce combineur. Il s'agit d'un transformateur « balun » mince dans un boîtier « surface-mount » ayant des impédances non balancée et balancée de 50 $\Omega$  et de 25 $\Omega$ , respectivement. Le combineur à terminaisons réactives variables permet, en théorie, 100% de modulation d'amplitude du signal à la charge de sorte que l'efficacité peut être maximisée en tout temps. Ces résultats de validation ont été obtenus par simulation dans ADS.

#### 0.5 Conclusion

Le transmetteur LINC composé d'un nouveau séparateur numérique de composants du signal (NDSCS) et d'un nouveau combineur peut être utilisé comme amplificateur linéaire pour les modulations GSM, CDMA et WCDMA. Dans ce projet, deux contributions majeures ont été apportées dans la fabrication d'un transmetteur LINC. Premièrement, un nouveau séparateur numérique de composants du signal a été conçu et réalisé en utilisant une trousse de développement FPGA de Altera selon deux méthodes : la table unidimensionnelle (Look-Up-Table) et le bloc de fonction racine carré. Ces deux méthodes minimisent la longueur de mot tout en permettant une précision acceptable, ce qui réduit la consommation de puissance et accroît la largeur de bande.

Deuxièmement, un nouveau combineur à terminaison réactive améliore substantiellement l'efficacité de puissance ajoutée.

Le prototype du transmetteur LINC a été fabriqué et simulé avec un signal d'entrée IS-95 de largeur de bande 1.2288 MHz, un canal inférieur ACPR -89.4 dBc et un décalage de 885 kHz entre les canaux supérieur et inférieur. Le ratio global de la valeur crête par rapport à la moyenne était de 9.340dB.

Les résultats expérimentaux montrent que l'efficacité de ce transmetteur LINC est en moyenne de 17.6% pour des amplificateurs de puissance fonctionnant en classe AB et ayant une efficacité de 23.5% à la fréquence centrale 2.14 GHz. La sélection de la susceptance parallèle appropriée  $\pm Bv$  peut donc optimiser l'efficacité et la linéarité tel que le démontre les résultats ci-dessous :

- L'efficacité moyenne est de 15.5% en utilisant un combineur à terminaison réactive variable avec susceptance parallèle. Le ACPR est de -57 dBc à 885 kHz de décalage.

En ce qui concerne le niveau de puissance global de sortie, le ratio crête à la moyenne est de 8.3 dB.

- L'efficacité moyenne est de 13.6 % en utilisant un combineur à déphasage Chireix.

Le ACPR est de -61 dBc à 885 kHz de décalage. Le ratio crête à la moyenne est de 8.6 dB.

- L'efficacité moyenne est de 10.2 % en utilisant un combineur en T sans susceptance.

Le ACPR est de -63 dBc à 885 kHz de décalage. Le ratio crête à la moyenne est de 9.2 dB.

L'efficacité moyenne est de 9.1% en utilisant un combineur Wilkinson. Le ACPR en sortie est de -65 dBc à 885 KHz de décalage. Le ratio crête à la moyenne est de 9.3 dB.

En conclusion, le combineur isolé, tel le Wilkinson, ne permet pas une impédance de charge variable et la puissance du signal en quadrature entraîne une consommation de puissance. Donc, l'amplificateur n'atteint son maximum d'efficacité d'opération qu'à la puissance maximale de sortie. Son efficacité décroît alors linéairement avec la diminution de la puissance de sortie. Ce comportement de l'efficacité est similaire à celui des amplificateurs en classe A qui ont une faible efficacité globale. Un combineur isolé avec pertes peut cependant préserver la linéarité de la puissance RF de l'amplificateur.

Un combineur non isolé est plus efficace qu'un combineur isolé mais souffre d'une moins bonne linéarité. La terminaison réactive parallèle est une méthode puissante selon laquelle un combineur non isolé peut améliorer l'efficacité énergétique. Cependant, l'utilisation de ces terminaisons réactives variables entraîne une erreur de gain ou de phase dans les deux branches et, conséquemment, une dégradation de la linéarité. Il est donc nécessaire de balancer l'efficacité et la linéarité en sélectionnant une valeur appropriée de réactance parallèle de sorte à maintenir le meilleur compromis entre l'amélioration de l'efficacité et la dégradation de la linéarité.

# **TABLE OF CONTENTS**

| DEDICATE                   | IV    |

|----------------------------|-------|

| ACKNOWLEDGEMENTS           | V     |

| ABSTRACT                   | VI    |

| RÉSUMÉ                     | VIII  |

| CONDENSE EN FRANÇAIS       | XI    |

| TABLE OF CONTENTS          |       |

| LIST OF TABLES             | XXVII |

| LIST OF FIGURES            |       |

| ABBREVIATIONS AND ACRONYMS | XXX   |

| CHAPTER 1                                                 |  |  |

|-----------------------------------------------------------|--|--|

| NTRODUCTION1                                              |  |  |

| 1.1 RF LINEARIZATION TECHNIQUES                           |  |  |

| 1.2 LITERATURE REVIEW AND BACKGROUND FOR LINC TRANSMITTER |  |  |

| 1.2.1 ANALOG SOLUTIONS IN LINC TRANSMITTERS               |  |  |

| 1.2.2 DIGITAL SOLUTIONS IN LINC TRANSMITTERS              |  |  |

| 1.3 RESEARCH GOALS                                        |  |  |

| 1.4 THESIS ORGANIZATION                                   |  |  |

|                                                           |  |  |

| 2HAPTER 2                                                 |  |  |

| HE SIGNAL COMPONENT SEPARATOR AND ITS IMPLEMENTATION      |  |  |

| 2.1 INTRODUCTION                                          |  |  |

| 2.1.1 BASIC ANALYSIS OF THE SCS                           |  |  |

### xxiv

|     | 2.1.2 | LINC VECTORS IN THE CARTESIAN COORDINATE SYSTEM                     |

|-----|-------|---------------------------------------------------------------------|

|     | 2.1.3 | UNSOLVED PROBLEMS IN SCS                                            |

| 2.2 | NEW I | DIGITAL SIGNAL COMPONENT SEPARATOR (NDSCS)                          |

|     | 2.2.1 | Advantages of an FPGA device                                        |

|     | 2.2.2 | BASIC NDSCS DESIGN                                                  |

|     | 2.2.3 | CHALLENGES IN THE NDSCS DESIGN                                      |

|     |       | 2.2.3.1 A KEY IN NDSCS DESIGN PIPELINING TECHNIQUE                  |

|     |       | 2.2.3.2 ANOTHER KEY IN NDSCS DESIGN DELAY TECHNIQUE                 |

| 2.3 | DESIG | N DETAILS FOR NDSCS                                                 |

|     | 2.3.1 | Analysis of two methods for implementing $SR\_Part24$               |

|     | 2.3.2 | DESIGN ENVIRONMENT                                                  |

|     | 2.3.3 | METHOD 1 LUT IMPLEMENTATION                                         |

|     | 2.3.4 | METHOD 2 SQUARE ROOT FUNCTION BLOCK (SRFB)                          |

|     | 2.3.5 | COMBINATION IN BASEBAND                                             |

| 2.4 | DESIG | N IN SIMULINK OF MATLAB                                             |

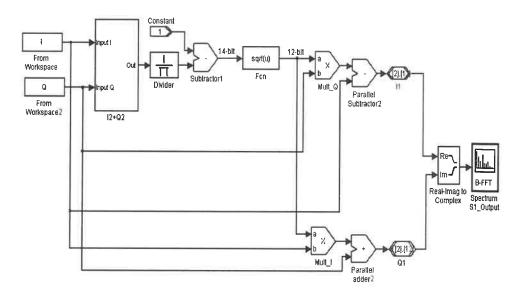

|     | 2.4.1 | METHOD 1 LUT IMPLEMENTATION                                         |

|     | 2.4.2 | METHOD 2 SQUARE ROOT FUNCTION BLOCK                                 |

| 2.5 | SIMU  | LATION RESULTS IN SIMULINK                                          |

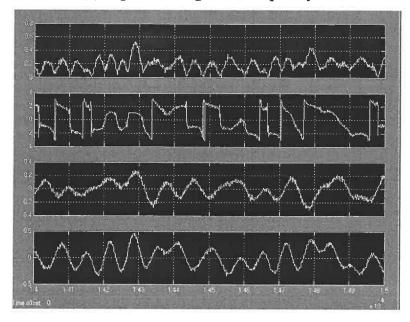

|     | 2.5.1 | INPUT SIGNAL IN SIMULINK                                            |

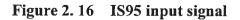

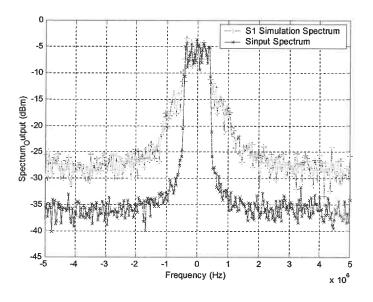

|     | 2.5.2 | SPECTRUM OF CONSTANT ENVELOPE PHASE MODULATED SIGNALS IN            |

|     |       | SIMULINK                                                            |

|     | 2.5.3 | Constant envelope phase modulated signal in time domain39           |

|     | 2.5.4 | $s_1 \mbox{ and } s_2 \mbox{ combination at baseband in Simulink }$ |

|     | 2.5.5 | Two methods comparison in Simulink41                                |

| 2.6 | Exper | RIMENTAL RESULTS FOR VERIFYING QUARTUS II DESIGN                    |

|     | 2.6.1 | MEASUREMENT SETUP                                                   |

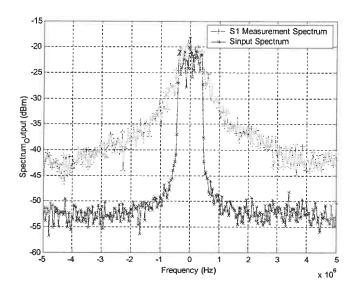

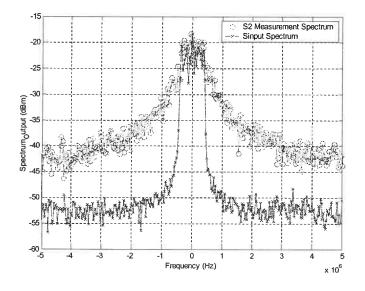

|     | 2.6.2 | Measurement results for $\mathrm{S}_1$ and $\mathrm{S}_2$           |

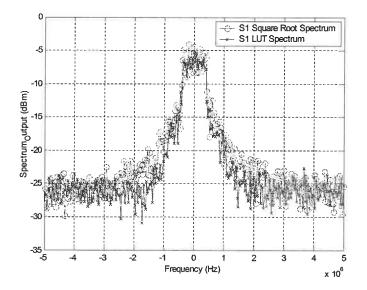

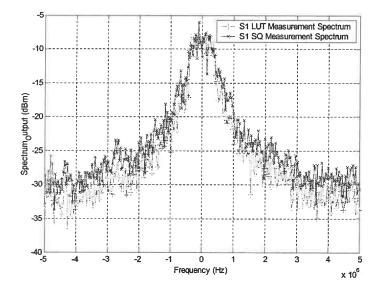

|     | 2.6.3 | Two methods comparison from measurement46                           |

| 2.7 | COMP  | ARISON BETWEEN SIMULATION AND MEASUREMENT                           |

| 2.8 | CONCL | USIONS                                                              |

| CHAPTER 3                                |                        |                                                                |  |

|------------------------------------------|------------------------|----------------------------------------------------------------|--|

| COMBINER TECHNIQUES IN LINC TRANSMITTERS |                        |                                                                |  |

| 3.1                                      | EFFICIENCY DEFINITIONS |                                                                |  |

| 3.2                                      | DIFFEI                 | RENT COMBINER STRUCTURES                                       |  |

|                                          | 3.2.1                  | CATEGORY 1 THE ISOLATED COMBINER                               |  |

|                                          | 3.2.2                  | CATEGORY 2 THE UNISOLATED COMBINER                             |  |

|                                          |                        | 3.2.2.1 SIMPLIFIED VOLTAGE /CURRENT SOURCE MODEL IN UNISOLATED |  |

|                                          |                        | COMBINER                                                       |  |

|                                          |                        | 3.2.2.2 SIMPLIFIED REACTIVE SOURCES MODEL                      |  |

| 3.3                                      | DIFFEI                 | RENT MODELS ANALYSIS OF UNISOLATED COMBINER                    |  |

|                                          | 3.3.1                  | LOSSLESS TEE COMBINER                                          |  |

|                                          | 3.3.2                  | THE CHIREIX OUTPHASING COMBINER                                |  |

|                                          | 3.3.3                  | VARIABLE REACTIVE TERMINATION COMBINER (VRTC)65                |  |

|                                          |                        | 3.3.3.1 VRTC IMPLEMENTATION                                    |  |

|                                          |                        | 3.3.3.2 REACTANCE XV ANALYSIS IN VRTC                          |  |

|                                          |                        | 3.3.3.3 VARIABLE CAPACITORS IN VRTC                            |  |

|                                          |                        | 3.3.3.4 IMPLEMENTATION OF IMPEDANCE TRANSFORMER IN VRTC 69     |  |

|                                          |                        | 3.3.3.5 Advantage of variable reactive termination combiner70  |  |

| 3.4                                      | SIMUL                  | ATIONS IN ADS                                                  |  |

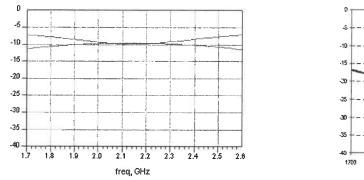

|                                          | 3.4.1                  | EFFICIENCY RESULTS USING TWO-TONE SIGNAL                       |  |

|                                          | 3.4.2                  | EFFICIENCY RESULTS USING CDMA IS95 INPUT SIGNAL72              |  |

|                                          |                        | 3.4.2.1 AVERAGE COMBINER EFFICIENCY USING IS95 INPUT SIGNAL73  |  |

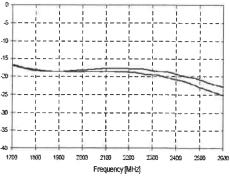

|                                          | 3.4.3                  | LINEARITY RESULTS USING IS95 INPUT SIGNALS                     |  |

|                                          | 3.4.4                  | LINEARITY AND EFFICIENCY USING IS-95 INPUT SIGNAL77            |  |

|                                          |                        |                                                                |  |

| CHAPTER                                  | R 4                    |                                                                |  |

| CONCLUS                                  | SIONS.                 |                                                                |  |

4.1

XXV

### xxvi

|     | 4.2   | FUTURE WORKS                                | 82 |

|-----|-------|---------------------------------------------|----|

| REF | EREN  | ICES                                        | 84 |

| APF | ENDI  | X A                                         | 88 |

| DEI | LAY B | LOCK IN VHDL                                | 88 |

| APF | ENDI  | X B                                         | 89 |

| SQU | JARE  | ROOT FUNCTION BLOCK WITH PIPELINING IN VHDL | 89 |

### xxvii

## LIST OF TABLES

| Table 2. 1 | Processing speed and accuracy comparison from the Quartus II 4.2 | 49 |

|------------|------------------------------------------------------------------|----|

| Table 3. 1 | Average combiner efficiency                                      | 74 |

| Table 3. 2 | Comparison results : overall_PAE , ACPR, Peak-to-ave ratio       | 78 |

# LIST OF FIGURES

| Figure 1.1   | RF amplifier linearization techniques2                                                    |

|--------------|-------------------------------------------------------------------------------------------|

| Figure 1.2   | Analog LINC transmitter                                                                   |

| Figure 1.3   | LINC transmitter with digital signal component separator                                  |

| Figure 1.4   | LINC transmitter using DSP technique7                                                     |

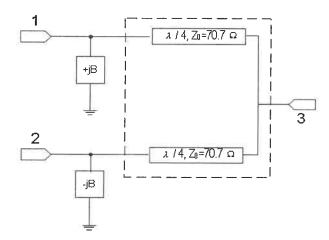

| Figure 1.5   | Variable reactive termination combiner                                                    |

| Figure 2.1   | Basic schematic diagram of the LINC transmitter                                           |

| Figure 2. 2  | Decomposition of signals in the signal component separator                                |

| Figure 2.3   | Vector diagram illustrating relationship between components 14                            |

| Figure 2. 4  | LINC implementation with a new DSCS architecture                                          |

| Figure 2. 5  | A combinatorial design and a pipeline design                                              |

| Figure 2. 6  | Multiple-stage synchronizer                                                               |

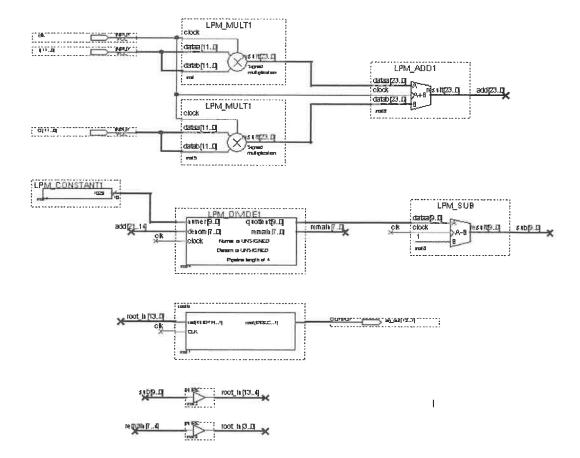

| Figure 2. 7  | Method 1LUT design block diagram                                                          |

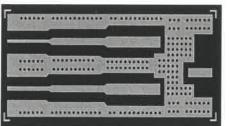

| Figure 2.8   | LUT 16384 design block in Quartus II 2.0                                                  |

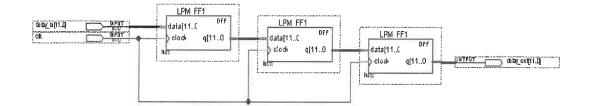

| Figure 2. 9  | Three LPM_FF block for a three clock cycle delay                                          |

| Figure 2. 10 | Top level design for I <sub>1</sub> (n) & Q <sub>1</sub> (n) with LUT in Quarus II 2.0 29 |

| Figure 2.11  | Method 2 - Square-Root Function Block design diagram                                      |

| Figure 2.12  | SR_Part implementation of SRFB in the Quartus II 2.0                                      |

| Figure 2.13  | Top level design for $I_1(n)$ with SRFB in the Quartus II 2.0                             |

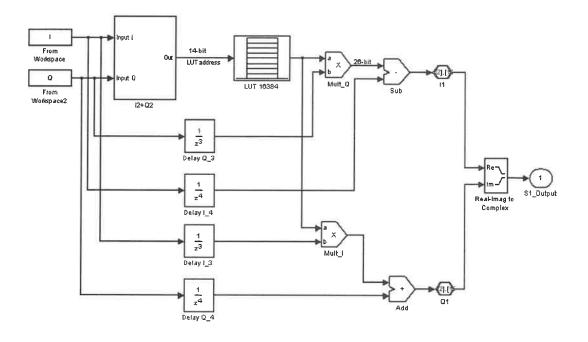

| Figure 2. 14 | Top level design for S <sub>1</sub> in Simulink method 1 LUT                              |

| Figure 2.15  | Top level design for S <sub>1</sub> in Simulink method 2 SRFB                             |

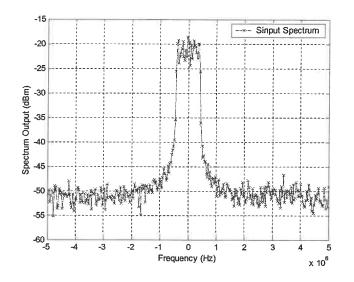

| Figure 2.16  | IS95 input signal                                                                         |

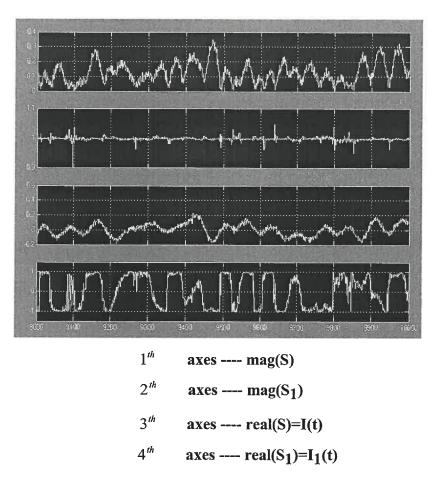

| Figure 2.17  | Simulation results in Simulink                                                            |

| Figure 2. 18 | S and $S_1$ in time domain of Simulink                                                    |

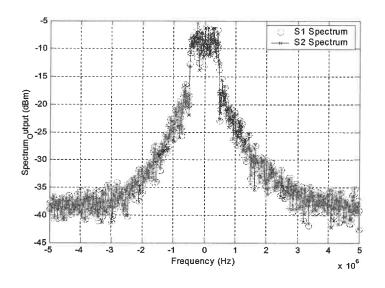

| Figure 2.19  | Recombination spectrum in Simulink 41                                                     |

| Figure 2. 20 | S <sub>1</sub> spectrum comparison between LUT and SRFB                                   |

| Figure 2. 21 | Measurement set-up                                                                        |

### xxix

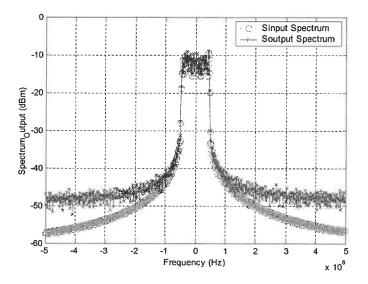

| Figure 2. 22 | Output and input spectrum from measurement 4                  | 5 |

|--------------|---------------------------------------------------------------|---|

| Figure 2. 23 | S <sub>1</sub> spectrum between LUT and SRFB from measurement | 6 |

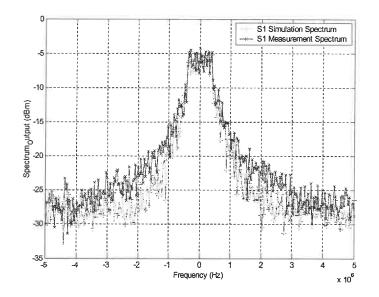

| Figure 2. 24 | Spectrum comparison between simulation and measurement 4      | 7 |

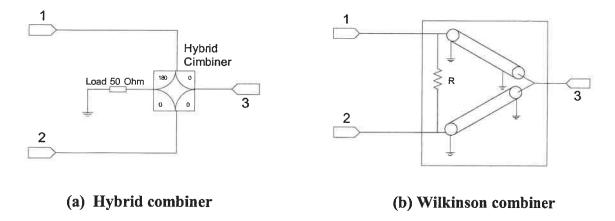

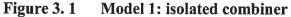

| Figure 3. 1  | Model 1: isolated combiner                                    | 4 |

| Figure 3. 2  | Model 2: unisolated combiner 5                                | 6 |

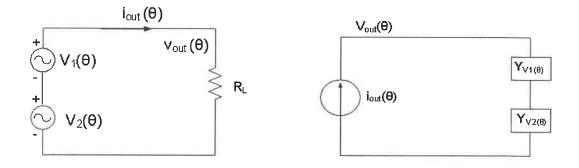

| Figure 3. 3  | LINC combiner realized voltage / current sources              | 7 |

| Figure 3. 4  | Voltage and current models with shunt susceptances            | 9 |

| Figure 3. 5  | Lossless combiner analysis                                    | 1 |

| Figure 3. 6  | Chireix outphasing system with shunt susceptances             | 2 |

| Figure 3. 7  | Chireix outphasing system analysis                            | 3 |

| Figure 3. 8  | Variable reactive termination combiner                        | 5 |

| Figure 3. 9  | Implementation of variable reactive termination combiner      | 6 |

| Figure 3. 10 | Combiner return loss                                          | 9 |

| Figure 3. 11 | Enhanced unisolated combiner design in ADS                    | 9 |

| Figure 3. 12 | PAE $\eta$ (%) vs Pin (dBm) with two-tone signal              | 2 |

| Figure 3. 13 | PAE curves with IS95 signal                                   | 3 |

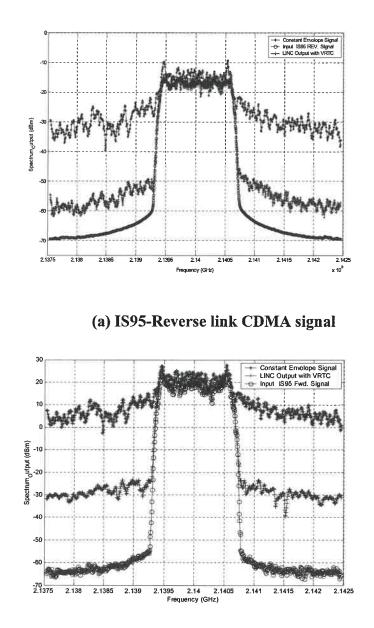

| Figure 3. 14 | LINC output spectrum using an IS95 REV signal7                | 5 |

| Figure 3. 15 | Spectrums using IS95 signal                                   | 6 |

# **ABBREVIATIONS AND ACRONYMS**

| 3G       | third generation mobile system                    |

|----------|---------------------------------------------------|

| ACPR     | adjacent channel power ratio                      |

| ADC      | analog to digital converter                       |

| AHDL     | Altera's hardware description language            |

| ASDSP    | application specific digital signal processing    |

| CALLUM   | combined analogue locked-loop universal modulator |

| CDMA     | code division multiple access                     |

| CDMA2000 | code division multiple access 2000                |

| CPLDs    | complex programmable logic devices                |

| DAC      | digital to analog converter                       |

| DSCS     | digital signal component separator                |

| DSP      | digital signal processing                         |

| EER      | envelope elimination and restoration              |

| FPGA     | field-programmable gate array                     |

| GSM      | global system for mobile communications           |

| HDL      | hardware description language                     |

| IEEE     | Institute of Electrical and Electronics Engineers |

| IMD      | inter-modulation distortion                       |

| IP       | intellectual property                             |

| IS-95    | digital cellular standard IS-95                   |

| LEs   | logic elements                                          |

|-------|---------------------------------------------------------|

| LINC  | linear amplification with non-linear components         |

| LIST  | linear amplification by sampling techniques             |

| LO    | local oscillator                                        |

| LUT   | look-up table                                           |

| MAC   | multiply accumulate                                     |

| NCO   | numerically controlled oscillator                       |

| NDSCS | new digital signal component separator                  |

| PA    | power amplifier                                         |

| PAE   | power-added efficiency                                  |

| PEP   | peak output Power                                       |

| PLLs  | phase locked loops                                      |

| QAM   | quadrature amplitude modulation                         |

| RAM   | random access memory                                    |

| ROM   | read only memory                                        |

| PCS   | personal communication system                           |

| RF    | radio frequency                                         |

| SCS   | signal component separator                              |

| SOPC  | system on a programmable chip                           |

| SRFB  | square-root function block                              |

| VHDL  | very high speed integrated circuit hardware description |

|       | Language                                                |

xxxi

xxxii

| VRTC  | variable reactive termination combiner |

|-------|----------------------------------------|

| WCDMA | wideband code division multiple access |

# CHAPTER 1 INTRODUCTION

1

#### 1.1 **RF** Linearization techniques

For cellular mobile, wireless and other modern communication systems, more spectral efficient techniques are required to accommodate high-rate data transmission in a limited bandwidth. Various modulation schemes such as QAM, CDMA2000 and WCDMA have been introduced to improve spectral efficiency for different applications. However, these advanced modulation schemes generate non-constant envelope signals which often have high peak-to-average ratios which require very linear RF power amplifiers. Traditionally, class A amplifiers were operated with very high back-off, resulting in very poor efficiency. Hence a more efficient power amplifier is desired to replace the traditional class A amplifier. But due to the inherent non-linearity of these more efficient RF power amplifiers that generate significant in-band intermodulation distortion and out-of-band interference, they need to be linearized to meet today's stringent requirements for high linearity and low power consumption.

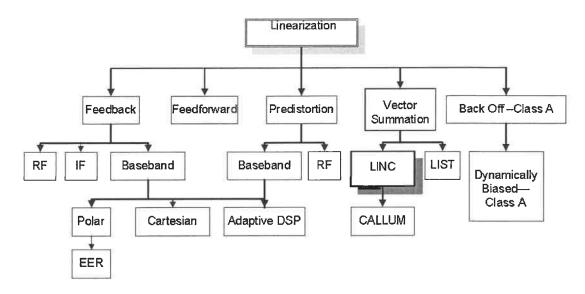

The aim of the various linearization techniques is to eliminate undesired in band distortion components and to avoid interference in adjacent channels. These techniques are challenging and complicated. They have been developed in areas such as multicarrier base-stations, fixed point-to-point microwave radio links, satellite communications, etc.. Whatever the application, the goal is the same: to sufficiently improve linearity while sacrificing the least amount of efficiency. The wide-range of the linearization techniques can be divided into a number of approaches [1]. Figure 1.1 shows graphically how the various linearization techniques are related.

Figure 1.1 RF amplifier linearization techniques

A number of linearization techniques are available for commercial applications, some for narrowband systems, and others, such as the feedforward technique, are promising for the broadband systems. It is not yet possible to find economical solutions to cover all the requirements. Appropriate linearization techniques include Cartesian loop, polar loop, Adaptive baseband predistortion, Envelope Elimination and Restoration (EER), LInear Amplification with Nonlinear Components (LINC) which is studied in this project, and Combined Analogue Locked-Loop Universal Modulator (CALLUM), LInear amplification by Sampling Techniques (LIST). They are the most suitable techniques for narrow band applications, while feedforward and predistorsion techniques can operate over wider bandwidths. However, there is no technique so far that can promise both high efficiency and very good linearity simultaneously over a sufficiently wide band.

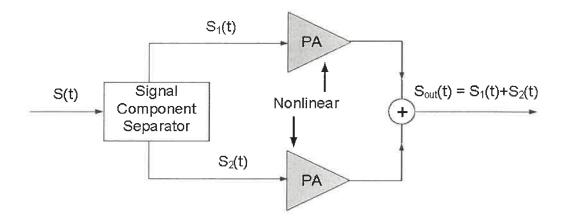

Linear amplification using Non-linear Components (LINC) is a vector summation technique [2] for achieving a highly efficient RF power amplifier with very good linearity [3]. In this technique two constant envelope but varying phase signals are produced that are amplified and added (combined) to reform the desired varying envelope and varying phase signal at the output. For amplification of constant envelope signals it is not necessary to use a very linear amplifier; hence, more efficient amplifiers can be used to replace the linear (and less efficient and more expensive) amplifiers. The LINC transmitter can be applied to today's complex base station and portable applications. It takes the envelope modulated bandpass waveform and resolves it into two "out-phased" constant envelope signals, which are then applied to two highly efficiency and nonlinear power amplifiers. No intermodulation distortion is produced because the amplitudes of the signals handled by the two amplifiers are constant. After recombination (vector summation), a linearly amplified input signal is obtained at the output.

#### 1.2 Literature review and background for LINC transmitter

The LINC radio frequency (RF) power amplifier was derived from the outphasing modulation technique developed in 1935 by H. Chireix [4]. Two power amplifiers were driven by a phase-modulated carrier and combined to produce a highly linear and efficient AM transmission at the carrier frequency. In 1974, Donald Cox first

proposed the "LINC" amplifier concept [5] which became the well- known acronym 'LInear amplification with Nonlinear Components', in which the input signal is decomposed into two phase-modulated signals. Then narrow-band linear amplification is achieved using efficient constant amplitude nonlinear amplifiers.

There were two major challenges in LINC transmitter systems: component signal separation and recombination. Many previous papers concentrate on LINC transmitters such as a VHF implementation of a LINC amplifier [6][7], an inverse-sine modulator for use in a decomposition circuit [8], an in-phase/quadratic processor for LINC [9], a broad-band combiner for LINC [10], a digital signal processor for LINC component separation, and the effect of imbalances and modulation on LINC performance [11]. They mainly consist of two solutions: analog or digital .

#### **1.2.1** Analog solutions in LINC transmitters

Outphasing modulation can be used to obtain an AM signal by the use of counter-phase modulation and vector summation of two RF signals, which was marketed by RCA under the trade name "Ampliphase"[12]. This technique used two class C RF power amplifiers in parallel, fed by a phasing network that uses the envelope of the drive signal to control the relative phase of the RF signal fed to each amplifier. At low signal amplitudes, the power amplifiers are fed limited versions of the input signal that are nearly 180 degree out of phase, so they nearly cancel out at the amplifier output. At high signal amplitudes, the amplifiers are fed nearly in phase signals.

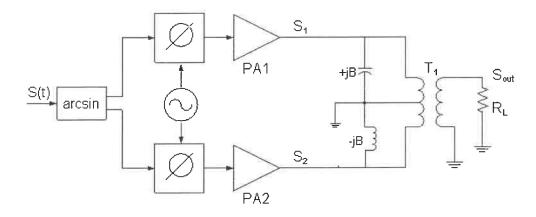

Figure 1.2 Analog LINC transmitter

An outphasing transmitter produces an amplitude modulated signal by combining two constant envelope signals with different time-varying phases in the analog modulation. The inverse sine of the envelope S(t) produces the phase modulation  $+\phi$  and -  $\phi$  for the two PAs, shown in figure 1.2. Basically, the phase modulation causes the instantaneous vector sum of the two PA outputs to follow the desired signal amplitude [5][9].

Cox achieved this complete analogue solution for component separation, but it suffered from bandwidth limitations and distortions that were caused by factors, in the phase modulator, limiter and envelope detector. For broad-band applications, system complexity prevented this analog technique from becoming widely accepted [13][14].

#### 1.2.2 Digital solutions in LINC transmitters

Today, digital signal processing techniques make it possible to implement the signal component separator (SCS) in a standard DSP device with software which can provide sufficient accuracy [15][16]. However, it suffered from some constraints in

terms of bandwidth and power consumption. This solution executed by digital signal processor based designs which have some limitations in processor computing-time, A/D, D/A conversion time, quantization noise and price [17].

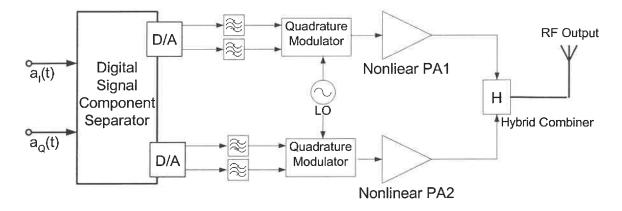

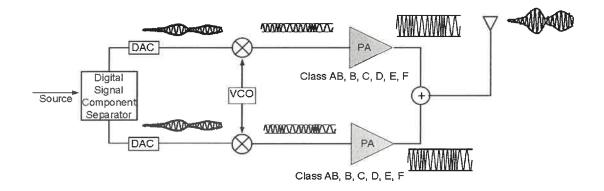

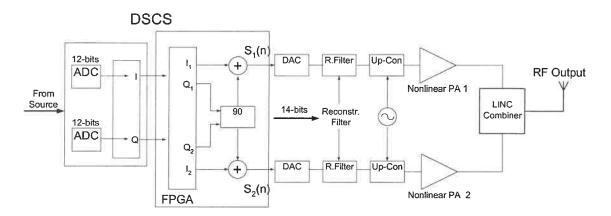

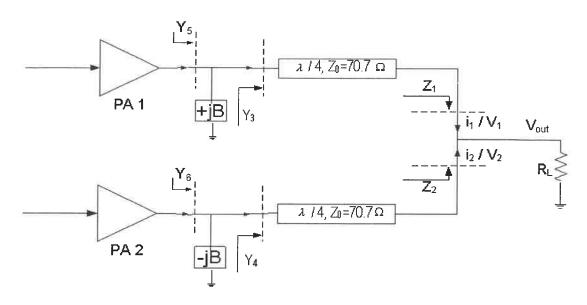

Figure 1.3 LINC transmitter with digital signal component separator

With this scheme all processing is executed at baseband. See figure 1.3. The digital signal component separator generates two constant-envelope phase-modulated signals which are up-converted by a pair of quadrature modulators to translate the baseband signals to the desired carrier frequency. They are then amplified by two well-matched non-linear amplifiers, and then summed in the combiner. All undesired out-of-band components of the complex signals are in antiphase and therefore cancel at the output.

The difficulties with this method are in the production of the complex phasemodulated signals, the design of two well-matched amplifiers and the combination of the two high-power signals from the amplifiers.

#### 1.3 Research goals

LINC technology is proposed to improve the linearity of power amplifier and enhance the power efficiency. There are many papers reporting clever implementations that have been studied and developed in the past years. The improvements of both efficiency and linearity were stated, but the inherent tradeoffs between these two parameters remain unresolved.

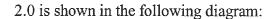

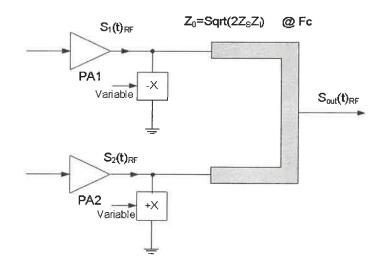

This research work develops and implements a practical linear transmitter for today's complex base station and portable applications. Improvements in digital signal processing and combining are providing solutions for the difficult task in achieving both high efficiency and linearity. A practical LINC transmitter is based on applying digital signal processing techniques, efficient combining technology and highly efficient non-linear power amplifiers such as class AB, B, C, as well as the switch-mode class E and class F. See figure 1.4.

Figure 1.4 LINC transmitter using DSP technique

This linear transmitter can achieve high efficiency and its spurious performance can be reduced in the order of 30-60 dBc [18]. However, one of its limitations is the sensitivity of the design to the balance between the two amplifiers. This is mainly caused by signal component separator (SCS) that splits the source signal into the two individual constant envelop phase-modulated signals. The implementation of the SCS has been one of the major problems in the LINC transmitter.

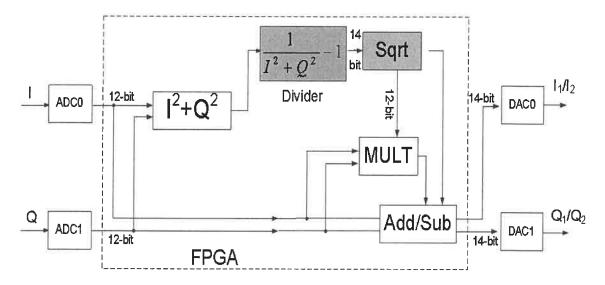

A new digital signal processing architecture based on FPGA (Field-Programmable Gate Array) allows the design to have a customized architecture, bus structure and memory in a cost-effective, high-performance digital signal processing scheme. High-speed FPGA devices process all algorithms more flexibly than a standard DSP device so that we can improve the bandwidth and reduce the power consumption. A/D and D/A converters having a significantly high sampling rate should also be selected.

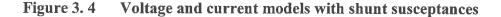

In order to obtain high efficiency and good linearity performance simultaneously, the implementation of combiner that can achieve a high power-added efficiency (PAE) is a pivotal factor. Typically, Chireix outphasing systems [19] which has a transformer coupler summing circuit with shunt reactances result in conjugate output load variations applied to the nonlinear power amplifiers. But it only achieves the maximized efficiency at one specific output level because of the fixed shunt reactances. Hence, another major objective is on on implementing a new recombination architecture with variable shunt susceptance in order to obtain high power efficiency at variable output levels. It can be constructed with an impedance transformer and reactive terminations with tuning elements as shown in figure 1.5. Dynamically and accurately selecting the shunt reactances would make it possible for the LINC combiner to achieve maximum efficiency for all output levels.

Figure 1.5 Variable reactive termination combiner

#### **1.4** Thesis organization

The remainder of this thesis is organized as described below.

In Chapter 2, the principle of the signal component separator (SCS) is analyzed in detail. The essential elements of our approach with an in-depth analysis is discussed. Moreover, it presents key techniques needed to implement this signal component separator. The new digital signal component separator (NDSCS) is based on an FPGA device which has been designed to achieve a higher performance of digital signal processing. All of the designs and experimental measurements using a Quartus II platform are validated by simulations in MATLAB's Simulink.

Chapter 3 analyzes LINC combination technologies and its voltage/ current model. The discussions and comparisons of the two main combiner types, represented in

four classical models, are analyzed in detail. The new combiner architecture is constructed using a balun transformer and variable reactive elements and is optimized for obtaining a suitable balance between efficiency and linearity. ADS simulations suggest that variable reactive terminations increase the efficiency significantly with only a reasonable loss of linearity.

The final chapter summarizes the major contributions of this work. Possible future work is suggested.

# CHAPTER 2

# THE SIGNAL COMPONENT SEPARATOR AND ITS IMPLEMENTATION

LINC is a technique that uses signal processing to produce linear amplification of bandpass signals with nonlinear components. The most two important signal processing functions of LINC are: 1) forming two constant envelope phase-modulated signal components from a band limited input signal. 2) recombinating the amplified components to produce an amplified replica of the input signal. Hence, the signal component separator is a significant objective of this research. It will be analyzed theoretically, and its practical and theoretical implementations will be described in this chapter and then some conclusions will be presented.

# 2.1 Introduction

The basic principle of the LINC transmitter is shown in figure 2.1 [3][13][14][16][17][18][19]. The source signal S(t) is decomposed by the signal component separator (SCS) into two constant amplitude phase modulated signals, S<sub>1</sub>(t) and S<sub>2</sub>(t). The constant amplitude signals are separately translated from baseband to RF by a carrier frequency in the quadrature modulators and then amplified by the nonlinear power amplifiers. After amplification the signals are recombined to form an amplified replica of the source signal. Since the amplitude of the two signals are constant, and therefore no distortion will be generated, the amplifiers can be nonlinear. Ideally the LINC transmitter is insensitive to nonlinear characteristics of the amplifiers.

Figure 2.1 Basic schematic diagram of the LINC transmitter

# 2.1.1 Basic analysis of the SCS

The source signal translated from baseband [20], can be representated as

$$S(t) = r(t) * e^{j\phi(t)}$$

;  $0 \le r(t) \le r_{\max}$  (2.1)

This input signal with envelope r(t) and instantaneous phase variation  $\phi(t)$  can be split into two signals,  $S_1(t)$  and  $S_2(t)$ , having modulated phases and constant amplitudes:

$$2 * S(t) = S_1(t) + S_2(t) \tag{2.2}$$

$$|S_1(t)| = |S_2(t)| = r_{\max}$$

(2.3)

where  $S_1(t)$  and  $S_2(t)$  are composed of the in-phase and quadrature phase components as shown in figure 2.2.

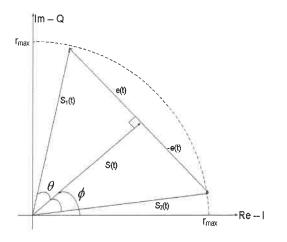

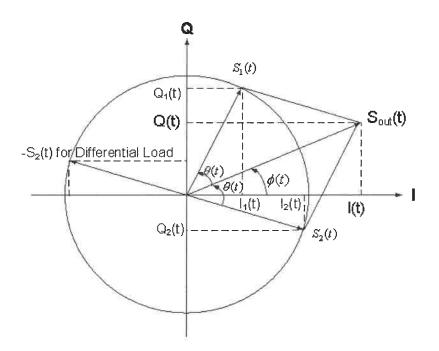

Figure 2. 2 Decomposition of signals in the signal component separator

Both phasors  $S_1(t)$  and  $S_2(t)$  can be obtained by summing the input signal with the vector +e(t) and -e(t) [15][20][21][22][23].

$$S_{1}(t) = S(t) + e(t) = r_{\max} e^{j[\phi(t) + \theta(t)]}$$

(2.4)

$$S_{2}(t) = S(t) - e(t) = r_{\max} e^{j[\phi(t) - \theta(t)]}$$

(2.5)

where

$$\theta(t) = \cos^{-1} \left[ \frac{r(t)}{r_{\text{max}}} \right]$$

phase offset (0°- 90°) (2.6)

$r_{\text{max}}$  is the maximum value of r(t), and e(t) is a signal that is in quadrature to the source signal S(t). Its equation is:

$$e(t) = j * S(t) * \sqrt{\frac{r^2_{\max}}{r^2(t)} - 1}$$

,  $|e(t)| \le r_{\max}$  (2.7)

The quadrature signal e(t), is calculated and added / subtracted from S(t) respectively so as to obtain two constant envelope signals. When the separated signal components are recombined after amplification, the source signal part of each component is added in-phase, whereas the wideband signals cancel each other out.

It can be easily understood from (2.4), (2.5) that if the two signal branches are

perfectly matched, e(t) will ideally cancel its anti-phase counterpart, - e(t), and leave only the amplified source signal at the transmitter output. A small gain and/or phase imbalance would make this cancellation imperfect and result in IMD products. To attain high linearity in LINC transmitters, there must be a high degree of gain and phase matching between the two branches [20][21].

Figure 2.3 Vector diagram illustrating relationship between components

#### 2.1.2 LINC vectors in the Cartesian coordinate system

We can also analyze the LINC signal component vectors in a Cartesian system [23][24]. Figure 2.3 is a vector diagram illustrating the signal separation. The desired signal S(t) is decomposed into two equal amplitude signals  $S_1(t)$  and  $S_2(t)$ .

$$S_1(t) = I_1(t) + j * Q_1(t)$$

(2.8)

$$S_2(t) = I_2(t) + j^* Q_2(t)$$

(2.9)

$$S_{out}(t) = I(t) + j * Q(t) = [I_1(t) + j * Q_1(t)] + [I_2(t) + j * Q_2(t)]$$

(2.10)

Two modulated signals consist of the in-phase components  $I_1(t) / I_2(t)$  and the quadrature components  $Q_1(t) / Q_2(t)$ . Their relationship is described below:

$$I_{1}(t) = I(t) - Q(t)\sqrt{\frac{1}{I^{2}(t) + Q^{2}(t)} - 1}$$

(2.11)

$$Q_{1}(t) = Q(t) + I(t)\sqrt{\frac{1}{I^{2}(t) + Q^{2}(t)} - 1}$$

(2.12)

$$I_{2}(t) = I(t) + Q(t) \sqrt{\frac{1}{I^{2}(t) + Q^{2}(t)}} - 1$$

(2.13)

$$Q_{2}(t) = Q(t) - I(t) \sqrt{\frac{1}{I^{2}(t) + Q^{2}(t)}} - 1$$

(2.14)

There is a common part in equations (2.11) to (2.14), named here as SR Part.

$$SR_Part = \sqrt{\frac{1}{I^2 + Q^2} - 1}$$

(2.15)

It allows a means to obtain the constant envelope, phase modulated signals represented by their in-phase and quadrature phase components.

#### 2.1.3 Unsolved problems in SCS

Previous analog approaches [5][9][13], where the SCS works at an intermediate frequency (IF) or at a carrier frequency, suffered from system complexity. Although various feedback [25][26] techniques were proposed to overcome these problems, there were bandwidth limitations due to the loop delay. Digital signal processing techniques were later introduced to produce the SCS in baseband using a standard DSP device [14][15][26]. Look-up tables were used which simplified SCS implementation.

However, two serious limitations in this type of DSP solution were : bandwidth and power consumption.

The first is because the word-lengths in DSP devices cannot be chosen arbitrarily and are either 16 or 32 bits, which are longer than required by the SCS. The second is because the sampling rate must be appropriately considered because the power consumption is proportional to the clock frequency. Hence, reduced bandwidth and increased power consumption occurred when a high speed DSP and D/A converters are used.

By minimizing the sampling rate we can minimize the clock frequency of the DSP described in [21], and by adapting a topology of registers and arithmetic function bocks to fit the algorithms, the word-length can be reduced. Therefore, for a standard DSP device, which typically operates using long word-lengths some constraints occur in terms of the bandwidth due to how well the algorithms suit the DSP architecture. And, in using high performance DSP devices to alleviate this, the power consumption rises.

On the basis of these problems, this work presents a new digital signal component separation architecture on FPGA which can improve bandwidth and reduce power consumption. The accuracy of signal separation processing which is taken into account also meet the requirement of SCS.

#### 2.2 New digital signal component separator (NDSCS)

A new DSCS based on FPGA (Field-Programmable Gate Array) technology gives us a solution to choose a word length arbitrarily and to minimize the sampling rate so as to meet our requirements.

#### 2.2.1 Advantages of an FPGA device

Many digital signal processing applications can be implemented by DSP devices, but its hardware architectures are not flexible. Although DSP processors are programmable with software, they are limited by a fixed hardware architecture such as bus performance variation, memory, the number of multiply accumulate (MAC) blocks and hardware accelerator blocks, and as well as having a fixed data-width. For certain applications, such as customized digital signal implementation, like an SCS, a fixed hardware architecture is not advantageous.

An FPGA provides us with a reconfigurable solution for implementing digital signal processing applications [28]. It also has more power than DSP processors as far as raw data processing goes. At the same time, the FPGA can be reconfigured in hardware. It offers complete hardware customization for different applications. The customized architecture, bus structure, memory, hardware accelerator blocks, and a variable number of MAC (Multiply ACcumulate) blocks all can be implemented in FPGA devices which are an advantage when creating customized designs.

This flexible hardware which can implement the hardware design using a suitable hardware description language (HDL), such as VHDL or Verilog HDL, can implement the complete system inside a high-density FPGA. Furthermore, it can use the embedded silicon to form embedded memory, DSP blocks, and embedded processors. At the same time, accumulation, addition/subtraction, and summation blocks which are commonly used for the arithmetic operations are offered in a digital signal processing block library.

A DSP processor can supply only a limited number of multipliers. The most important factor in the overall bandwidth limitation of digital signal processing is the multiplier bandwidth- FPGA devices offer much higher multiplier bandwidths than DSP processors. For example, Altera's FPGA device can deliver 70 GMACS of digital signal processing throughput and DSP processors only deliver maximum 4.8 GMACS. Altera FPGAs also have 10 Mbits of embedded memory to meet large amounts of data processing.

Embedded processors in the FPGA provide integration and flexibility for many digital systems. We can implement the system's software components in the embedded processors and implement the hardware components in the FPGA's general logic resources. The Nios embedded processor used in this FPGA provides us with a means to decrease the complexity of some inherently complicated arithmetic operations.

To sum up, it is difficult for DSP processors to trade-off the size and performance when they choose a variable bus on the chip. And DSP performance is limited by the predefined hardware accelerator blocks. However, FPGA devices can accelerate performance functions in hardware under a flexible platform. Hence, FPGAs become the best choice to implement a digital signal component separator in LINC transmitters, rather than a DSP processor, because of their ability for accommodating customized designs. They achieve the best performance due to hardware acceleration.

#### 2.2.2 Basic NDSCS design

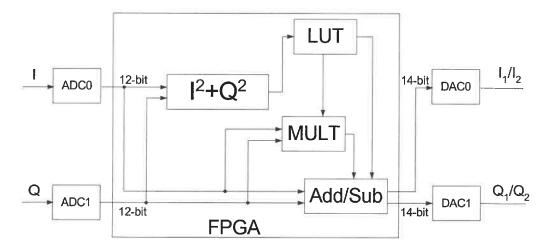

FPGA devices consist of logic elements (LEs) and memory that can be configured to operate in different modes according to functionality. The new DSCS configuration on the FPGA device processes all vector arithmetic. See figure 2.4.

First of all, it is important for us to know how accurate the SCS has to be when we choose a FPGA device. Moreover, the bandwidth of the phasors are substantially larger than that of the original input signal. FPGA devices and A/D, D/A converters operate with sampling rates at least 15-20 times the bandwidth of the input signal.

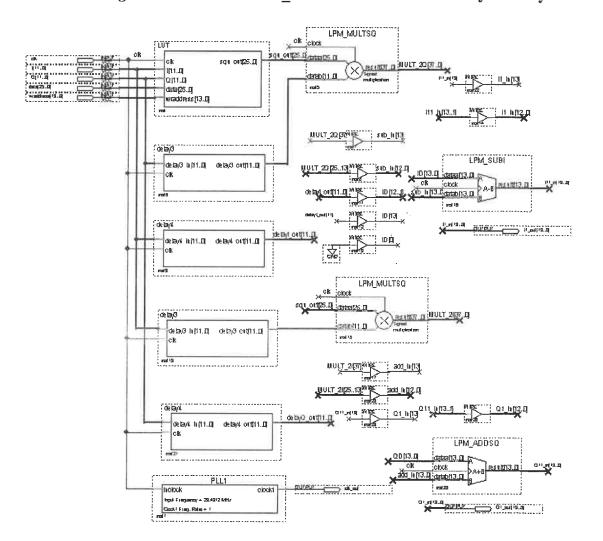

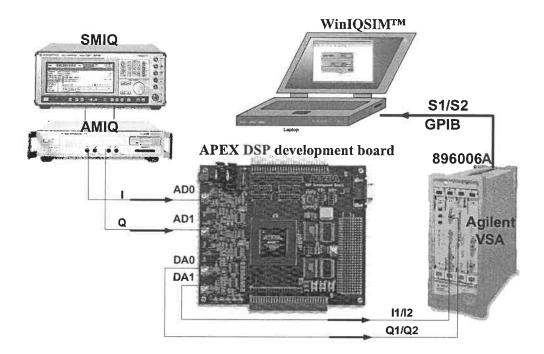

Figure 2.4 LINC implementation with a new DSCS architecture

The source signal S(t) at baseband is decomposed during demodulation into I(t) and Q(t) components which are applied to the inputs of two A/D converters. Both 12-bit binary data I(n) and Q(n) after A/D conversion are then transmitted to the FPGA for digital arithmetic processing. Then two pairs of binary digit data, in-phase components  $I_1(n) / I_2(n)$  and quadrature components  $Q_1(n) / Q_2(n)$  are obtained in the FPGA. The components  $I_1(n) / I_2(n)$  are added to  $Q_1(n) / Q_2(n)$  which have been 90° phase shifted,

to form  $S_1(n) / S_2(n)$ .

$$S_1(n) = I_1(n) + jQ_1(n)$$

(2.16)

$$S_2(n) = I_2(n) + jQ_2(n)$$

(2.17)

Subsequently, the resulting constant amplitude digital signals  $S_1(n)$  and  $S_2(n)$  are converted to analog by two D/A converters. The outputs of the D/A converters pass through low-pass filters to remove unwanted high-frequency components. The signals are then translated to RF by two up-converters having the same local oscillator (LO). Finally, the RF signals are amplified by two non-linear high efficiency power amplifiers and summed in the LINC combiner to obtain a linear amplified RF signal at the output.

#### 2.2.3 Challenges in the NDSCS design

The most difficult part is in the realization of a square root block that includes

division and the square root arithmetic calculation for  $SR_Part = \sqrt{\frac{1}{I^2 + Q^2} - 1}$  (2.15).

These operations are usually avoided, when possible, because they are very timeconsuming. Previous digital techniques used two-dimensional look-up tables to realize SR\_Part. It was addressed by the real and imaginary parts of the input signal [21][22] and have large table sizes. This was a unique solution implementing the square root function block this past year.

Clock synchronization is another important factor for data processing. Every arithmetic block inherently causes a clock delay, which can result in data asynchronization in the various calculation stages. In order to obtain correct data, it is necessary to synchronize the clock so as to ensure that all required data are acquired during the same clock period in each processing stage.

Two techniques are introduced to solve this problem: pipelining and delay blocks. Implementing SR\_PART (2.15) in the FPGA using pipelining techniques reduces the table size and increases the processing throughput. Delay blocks make it possible to synchronize data at each stage.

### 2.2.3.1 A key in NDSCS design --- pipelining technique

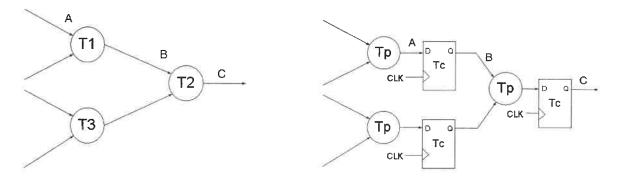

In a computational system, pipelined design techniques are used when building a functional block for CPLDs (Complex Programmable Logic Devices) [28] in different digital applications. To Pipeline a design, registers are inserted in every stage of the circuit. A K-stage pipeline is an acyclic circuit having exactly K registers (one register for every stage of the path) from input to output.

(b) After adding the registers

#### Figure 2.5 A combinatorial design and a pipeline design

Figure 2.5 shows a combinatorial design that includes two stages and a pipelined design. In figure 2.5 (a), where  $T_1$  or  $T_3$  are the delay for the first stage,  $T_2$  for the

second stage. The maximum  $T_1$  or  $T_3$  plus  $T_2$  will form the propagation delay obtained from a computation result.

In the pipelined design, see figure 2.5 (b), the sum of  $T_1$  or  $T_3$  and the  $T_c$  (clock to output time) of the register is the total delay for the first stage. The second stage of registers has a similar delay of  $T_2$  and  $T_c$ .

- >  $(T_1 \text{ or } T_3) + T_c = \text{delay of the first stage}$

- >  $T_2 + T_c$  = delay of the second stage

The overall clock period of the pipelined design will be the maximum sum of  $[max(T_1,T_3)+T_c]$  and  $(T_2+T_c)$ .

>  $[\max(T_1,T_3)+T_c]+(T_2+T_c) = \text{overall delay of the pipelined design}$

The advantage of pipeline design is the increased throughput. However, it takes two clock cycles here to obtain the very first computation result. The initial clock cycles required to obtain the first result is called the latency. The propagation delay,  $T_p$  is assumed the same for  $T_1$ ,  $T_3$  and  $T_2$ . Hence,  $2*T_p$  is the delay for the combinatorial design and the sum of  $T_p$  and  $T_c$  is for the pipelined design.

The latency is the amount of time for the initial or longest path. Throughput is the amount of time required after repeated operation. In the case of a combinatorial design, the latency and throughput will be the same at  $2^*T_p$ . But for the pipelined design, the latency and throughput are different at  $2^*(T_p+T_c)$  and  $(T_p+T_c)$  respectively. If  $T_c$  is faster than  $T_p$ , determined by the CPLD hardware, then the pipelined design will have a faster throughput than the combinatorial design.

In order to implement a high performance, complex, and pipelined design in CPLDs, a register-rich architecture having predictable delays, available in FPGAs, offers a desirable solution.

From the above analysis, pipelining technology is key to increasing throughput, and thus performance. Furthermore, available register-rich architectures makes it possible to implement computationally intensive functions.

# 2.2.3.2 Another key in NDSCS design --- delay technique

We also have to pay close attention to the cycle times which determine the maximum delay through a given pipelined segment; and also to the processing-delays of the arithmetic function blocks. Delay blocks can be used to realize synchronous functions and to avoid undesirable asynchronous affects.

Figure 2. 6 Multiple-stage synchronizer

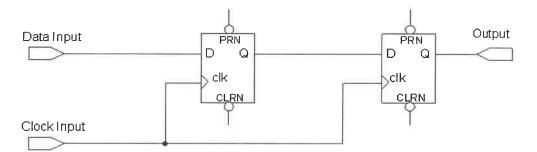

Designing a delay block is presented in two ways. The first is implemented using D-type flipflops. Several parameterized D-type flipflops are operated as timing-delays to synchronize the data and obtain the correctly timed output data. In figure 2.6, two D-type flipflops are cascaded to form two stages in a synchronizer to delaying the timing by two cycles.

A D-type flip-flop, also called a D-type bistable, is a subsystem having two stable states. Using appropriate input signals, we can trigger the flip-flop from one state to the other. The logic state at the DATA input is transferred to the Q output on the rising edge of the CLOCK signal. Hence, it can be used to delay timing cycles.

The second way is in coding a delay block in Very high speed intergrated circuit Hardware Description Language (VHDL), to synchronize the processing data. Function block LPM\_DFF is coded to operate as the frame of the delay block. Inside of LPM\_DFF, some parameters, such as width, determines the size of the input and output, and the depth, which presents the delay time that can be selected by the designer, depending on the design needs. See appendix A.

#### 2.3 Design Details for NDSCS

### 2.3.1 Analysis of two methods for implementing SR\_Part