**Titre:** Conception d'un système de test et de configuration numérique tolérant aux pannes pour la technologie WAFERIC

Title: tolérant aux pannes pour la technologie WAFERIC

**Auteur:** Yan Basile-Bellavance

Author:

**Date:** 2009

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Basile-Bellavance, Y. (2009). Conception d'un système de test et de configuration numérique tolérant aux pannes pour la technologie WAFERIC [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/235/>

**Document en libre accès dans PolyPublie**

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/235/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Yves Blaquieres

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

CONCEPTION D'UN SYSTÈME DE TEST ET DE CONFIGURATION NUMÉRIQUE

TOLÉRANT AUX PANNES POUR LA TECHNOLOGIE WAFERIC

YAN BASILE-BELLAVANCE

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU

DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2009

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

CONCEPTION D'UN SYSTÈME DE TEST ET DE CONFIGURATION NUMÉRIQUE

TOLÉRANT AUX PANNEES POUR LA TECHNOLOGIE WAFERIC

présenté par : BASILE-BELLAVANCE Yan

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. DAVID, Jean-Pierre, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. BLAQUIÈRE Yves, Ph. D., membre et codirecteur de recherche

M. BOIS, Guy, Ph. D., membre

## DÉDICACE

*Je dédie ce mémoire à mes parents qui n'ont jamais cessé de m'encourager à poursuivre mes études et à faire preuve de persévérance.*

## **REMERCIEMENTS**

En premier lieu, je veux remercier Yvon Savaria mon directeur de recherche et directeur du département de génie électrique de l'École Polytechnique Montréal. Je garde une grande reconnaissance envers Yvon Savaria, car il a su me faire confiance pour faire partie de l'équipe du projet DreamWafer. En deuxième lieu je veux remercier Yves Blaquièvre, mon codirecteur, pour sa contribution dévouée et généreuse à ma formation d'ingénieur. M. Blaquièvre était toujours disponible pour discuter de mon travail même s'il a un emploi du temps chargé en tant que directeur des programmes en microélectronique de l'Université du Québec à Montréal.

Je me suis senti privilégié d'avoir 2 excellents mentors durant mes études à la maîtrise. Yves Blaquièvre et Yvon Savaria ne m'ont pas seulement formé au niveau technique, mais au niveau humain pour m'aider à atteindre un niveau d'excellence qui fera une différence dans ma vie professionnelle.

En troisième lieu, je tiens à remercier Richard Prytula, président de TechnoCap Inc., le partenaire industriel du projet DreamWafer, pour deux raisons. Premièrement, au niveau humain pour sa gestion exigeante et audacieuse du projet, pour les nombreux conseils qu'il nous a donnés sur le démarrage et la gestion de projet technologique. Deuxièmement pour sa contribution financière et son courage pour avoir eu foi en l'équipe DreamWafer sans quoi le projet n'aurait jamais pu voir le jour.

Il ne faut pas oublier Richard Norman qui, le premier, a eu la vision du projet DreamWafer. Sans M. Norman, le projet n'aurait jamais vu le jour aussi rapidement. Sa vision ambitieuse à long terme du projet DreamWafer nous a permis de rester motivés même dans les moments les plus difficiles et incertains. Plusieurs discussions passionnantes avec R. Norman m'ont permis de développer une vision unique et avant-gardiste de la microélectronique.

De plus, je veux remercier mes principaux coéquipiers et amis : Étienne Lepercq, Olivier Valorge et Nicolas Laflamme-Meyer. Il faut spécialement remercier Étienne Lepercq, car son incroyable efficacité au travail m'a poussé à me surpasser sans cesse. Et un merci à Étienne pour toutes les fois qu'il m'a aidé à résoudre certains problèmes techniques rencontrés sur mon chemin. Je dois remercier Olivier Valorge pour les conseils techniques en microélectronique avancée qu'il m'a donnés depuis le tout début du projet et Nicolas Laflamme-Mayer pour son support ponctuel et indispensable qu'il m'a offert généreusement dans le domaine des PCBs.

L'équipe DreamWafer a vu passer beaucoup de monde. Je tiens à remercier tous les étudiants qui ont contribué au projet : Youssef El Alaoui, Marc-André Daigneault, Moufid Radji et Anh Tuan Nguyen.

Un grand merci à Réjean Lepage pour son soutien technique informatique rapide et efficace. Réjean Lepage a aussi été un ami et je voudrais le remercier pour son humour et sa gentillesse. Sans oublier Ghislaine Éthier qui a toujours été là pour s'occuper de nous. Je ne veux pas oublier de remercier les collègues du département de génie électrique avec qui j'ai passé mes études à la maîtrise : Gilbert Kowarzyk, Sébastien Éthier, Jaouad El Fouladi, Philippe Aubertin, David Bafumba-Lokilo, Moufid Radji, Louis-Francois Tanguay, Étienne Boulais, Roula Ghannoum et Mame Maria Mbaye.

Finalement, je dois remercier mes parents Donald Bellavance et Marie-Jeanne Basile pour leur soutien moral constant, eux qui ont toujours su m'encourager à aller loin dans mes études.

## RÉSUMÉ

L'objectif principal du projet de recherche est de concevoir, planter et vérifier un système de programmation JTAG tolérant aux pannes pour un circuit intégré à l'échelle de la tranche (WSIC, *Wafer Scale Integrated Circuit*). Le projet comprend la conception de l'interface logicielle/matérielle, l'implantation en VHDL du système, la conception de l'environnement de vérification SystemC ainsi qu'une étude sur la “diagnosabilité” du WaferIC un circuit WSIC au cœur d'un système configurable applicable au prototypage rapide.

Une nouvelle approche face à la conception de bancs de test programmable pour le test de circuits numériques est en cours de développement dans plusieurs universités québécoises, dont l'École Polytechnique Montréal dans le cadre du projet “DreamWafer<sup>TM</sup>”. Ce nouveau système de prototypage rapide de circuits numériques a pour but de mettre au point un réseau intégré d'interconnexions configurables, nommé WaferNet. Ce réseau d'interconnexions est déployé sur un circuit intégré à l'échelle de la tranche. Ainsi, le projet “DreamWafer<sup>TM</sup>” vise à développer un système équivalent à un “PCB reconfigurable” permettant de prototyper des circuits intégrés numériques discrets (FPGA, processeurs, DSP...), ceux-ci étant déposés à sa surface. Ce circuit intégré contient une matrice comportant des milliers de cellules identiques, chacune comportant un centre de contrôle logique, un crossbar configurable et un ensemble de “plots” de quelques dizaines de micromètres de large (points de contact avec les composants déposés). Cette matrice de cellules se nomme le WaferIC.

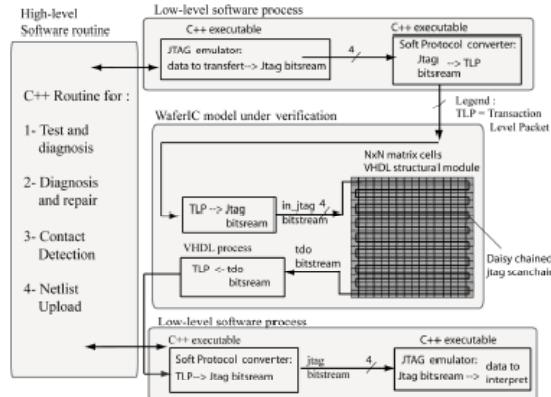

Ce projet de maîtrise porte spécifiquement sur la conception d'un système de configuration tolérant aux pannes pour le WaferIC, en la mise au point d'un environnement de simulation et de vérification matérielle codé en SystemC et en VHDL, à concevoir l'interface logicielle/matérielle pour le contrôle de la configuration basée sur le protocole JTAG et la conception d'une méthodologie de test et de diagnostic du système de configuration et du

WaferNet. La tolérance aux pannes est importante dans le cadre de cette application spécifique pour des raisons économiques et pour atteindre le niveau de qualité requis pour cette application.

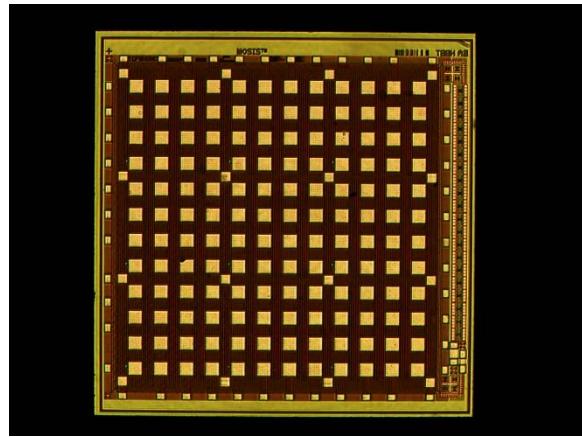

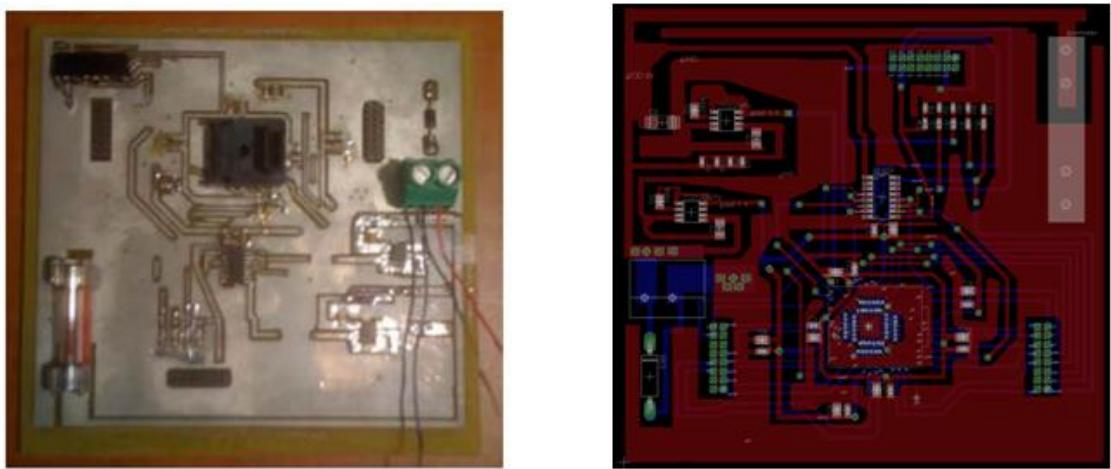

Parmi les résultats publiés dans ce document figurent le bilan du plan de vérification, les résultats de test et diagnostic du premier prototype “ASIC” du circuit fabriqué par l’entremise de CMC Microsystems, réalisé en technologie CMOS 0.18 µm. La réalisation et la vérification de ce premier prototype ASIC a été possible grâce à un système de test de circuit adapté à notre situation particulière de test. Ce système a été mis en place par une équipe de chercheurs dont l’auteur a fait parti.

## ABSTRACT

The goal of this master project is to design, implement and validate a new system able to control the WaferIC, a Wafer Scale Integrated Circuit (WSIC). More specifically, the project objective was to design the software/hardware interface, design and implement an embedded fault-tolerant control system and implement from scratch an environment in SystemC for functional verification. Moreover, the ASIC synthesis is applied on the VHDL code to fabricate a test chip to validate the circuit.

A new approach for rapid prototyping of digital systems is in development at several universities, including École Polytechnique de Montréal, through the “DreamWafer™” project. The goal of this new system is to interconnect all the digital pins of a set of discrete chip at the system level by using a reconfigurable network called WaferNet. This interconnection network is deployed over the active surface of a whole wafer. This wafer scale integrated system called WaferIC aims at implementing a form of reconfigurable PCB that is able to reconnect the digital pins of discrete chips at will. User’s ICs deposited on the active surface of the wafer are detected by an array of tiny reconfigurable “NanoPads” that can redirect the signals in the WaferIC’s internal network or feed the user’s IC pins with data and power.

The specific contribution of this master project consists of designing a fault-tolerant system to test and configure the WaferIC, to implement a verification environment coded in a mixed language SystemC/VHDL. This environment implements a software/hardware interface for the WaferIC and the design of a new test and diagnosis methodology for the reconfigurable network. Fault tolerance is an important issue for this class of circuit for economic reasons, and to reach the quality required for this application.

This document reports results obtained while testing and validating a test chip ( $1 \times 1 \text{ mm}^2$ ) that has been fabricated. Those results proved that the WaferNet concept works properly and the fault tolerant test and configuration system works as expected.

## TABLE DES MATIÈRES

|                                                                                                     |      |

|-----------------------------------------------------------------------------------------------------|------|

| DÉDICACE .....                                                                                      | III  |

| REMERCIEMENTS .....                                                                                 | IV   |

| RÉSUMÉ .....                                                                                        | VI   |

| ABSTRACT .....                                                                                      | VIII |

| TABLE DES MATIÈRES .....                                                                            | X    |

| LISTE DES FIGURES.....                                                                              | XIII |

| LISTE DES ANNEXES.....                                                                              | XVI  |

| INTRODUCTION .....                                                                                  | 1    |

| CHAPITRE 1. REVUE DE LITTÉRATURE .....                                                              | 7    |

| 1.1    L'évolution des systèmes sur puce (SoC) .....                                                | 7    |

| 1.2    Les limitations des systèmes sur PCB.....                                                    | 9    |

| 1.3    L'avènement des systèmes sur wafer (SoW) .....                                               | 12   |

| 1.4    Le WaferBoard.....                                                                           | 13   |

| 1.5    Les bases technologiques des contributions de ce mémoire .....                               | 23   |

| 1.5.1    Les systèmes de chaîne de balayage “niveau système” .....                                  | 23   |

| 1.5.2    Architecture de test .....                                                                 | 25   |

| 1.5.3    Le diagnostic de pannes dans un système d'interconnexions .....                            | 30   |

| 1.6    Conclusion .....                                                                             | 34   |

| CHAPITRE 2. COMMUNICATION SÉRIELLE TOLÉRANTE AUX PANNES.....                                        | 35   |

| 2.1    Introduction .....                                                                           | 35   |

| 2.2    L'architecture à base de chemins inter-cellulaires reconfigurables<br>unidirectionnels ..... | 39   |

| 2.2.1    La tolérance aux pannes du système UCIC.....                                               | 45   |

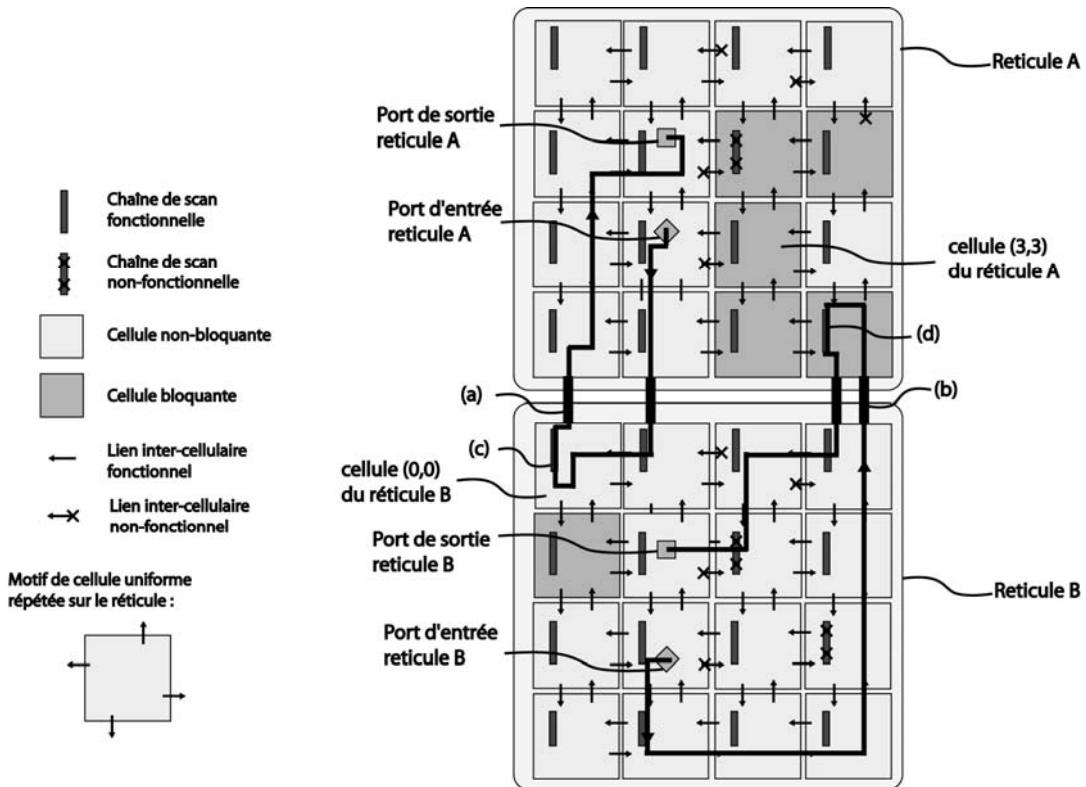

| 2.2.2    Les liens inter-réticulaires et la tolérance aux pannes de UCIC .....                      | 47   |

| 2.2.3    Diagnostic des liens inter-cellulaires UCIC .....                                          | 49   |

| 2.3    Variation : bidirectionnalité .....                                                          | 53   |

| 2.4    Conclusion .....                                                                             | 57   |

|                                                                                       |     |

|---------------------------------------------------------------------------------------|-----|

| CHAPITRE 3. LE DIAGNOSTIC DU WAFERNET .....                                           | 58  |

| 3.1    Introduction .....                                                             | 58  |

| 3.1.1    Description détaillée de la structure du WaferNet .....                      | 59  |

| 3.2    Description de l'algorithme “walking-one” appliqué au WaferNet .....           | 63  |

| 3.3    Méthodes d'optimisation appliquées au diagnostic du WaferNet .....             | 68  |

| 3.3.1    Modèle de performance du diagnostique du WaferNet .....                      | 68  |

| 3.3.2    Optimisation de l'insertion de la séquence de test .....                     | 70  |

| 3.3.3    Optimisation de l'extraction des résultats du test .....                     | 72  |

| 3.3.4    Estimation du gain de performance .....                                      | 74  |

| 3.4    Conclusion .....                                                               | 75  |

| CHAPITRE 4. IMPLANTATION ET VÉRIFICATION DU SYSTÈME .....                             | 76  |

| 4.1    Description fonctionnelle du WaferIC .....                                     | 76  |

| 4.1.1    Le système de configuration interne par le protocole JTAG .....              | 76  |

| 4.2    Description détaillée de l'architecture matérielle .....                       | 77  |

| 4.2.1    Le niveau WaferIC .....                                                      | 78  |

| 4.2.2    Le niveau Réticule .....                                                     | 79  |

| 4.2.3    Le niveau Cellule .....                                                      | 80  |

| 4.2.4    Le niveau NanoPad .....                                                      | 83  |

| 4.3    L'environnement de covérification .....                                        | 84  |

| 4.4    Conclusion .....                                                               | 86  |

| CHAPITRE 5. RÉSULTATS DU TESTCHIP V1.0 .....                                          | 87  |

| 5.1    Introduction .....                                                             | 87  |

| 5.2    Environnement de vérification pour les technologies associées au WaferIC ..... | 87  |

| 5.3    Test du circuit d'essai v1 .....                                               | 90  |

| 5.3.1    Résultat du test fonctionnel du TestChip .....                               | 92  |

| 5.3.2    La configuration du WaferNet <sup>TM</sup> et des NanoPads .....             | 94  |

| CONCLUSION .....                                                                      | 96  |

| RÉFÉRENCES .....                                                                      | 101 |

|                                                                   |     |

|-------------------------------------------------------------------|-----|

| ANNEXE A – FLOT DE TRAVAIL POUR LA VÉRIFICATION DU TESTCHIP ..... | 104 |

| ANNEXE B – PLAN DE TEST DU TESTCHIP V1.0.....                     | 115 |

| ANNEXE C – “FLOWCHART” ET AUTRES SCHÉMAS.....                     | 117 |

| ANNEXE D – PRINCIPAUX SCHÉMAS BLOCS.....                          | 121 |

| ANNEXE E – ARTICLES DE CONFÉRENCES .....                          | 124 |

| ANNEXE F – TEST DE RÉGRESSION .....                               | 132 |

| ANNEXE G – RÉSUMÉ DU STANDARD IEEE1149.1 .....                    | 135 |

## LISTE DES FIGURES

|                                                                                         |    |

|-----------------------------------------------------------------------------------------|----|

| 1-1 La plate-forme Zebu-XXL .....                                                       | 11 |

| 1-2 La plate-forme de développement NanoBoard <sup>TM</sup> .....                       | 12 |

| 1-3 Exemple de WaferBoard. Image tirée du brevet [1].....                               | 14 |

| 1-4 Structure hiérarchique du WaferBoard <sup>TM</sup> et du WaferIC .....              | 19 |

| 1-5 Structure du réseau WaferNet, extrait du brevet [1].....                            | 20 |

| 1-6 Exemple de l'effet de la procédure de détection de court-circuits .....             | 22 |

| 1-7 Utilisation des ressources des cellules voisines, extrait du brevet [1].....        | 23 |

| 1-8 Principales classes d'architecture de scan.....                                     | 25 |

| 1-9 Exemple d'architecture JTAG.....                                                    | 29 |

| 1-10 Exemple de diagnostic en utilisant les capacités de reconfiguration du FPGA.....   | 33 |

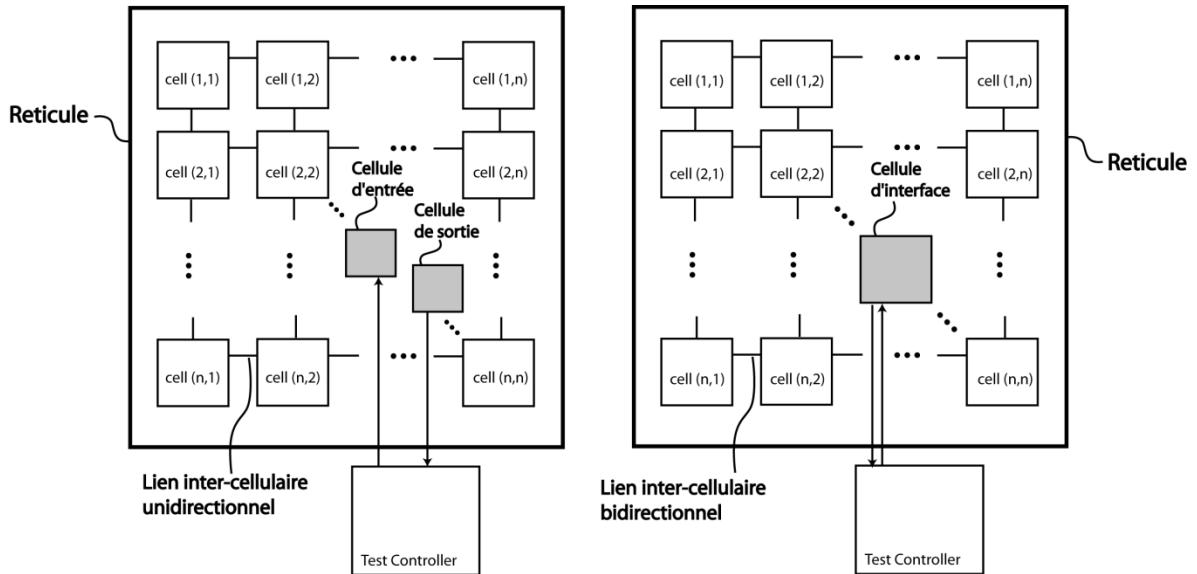

| 2-1 Schéma bloc niveau réticule du système de communication uni/bidirectionnel .....    | 37 |

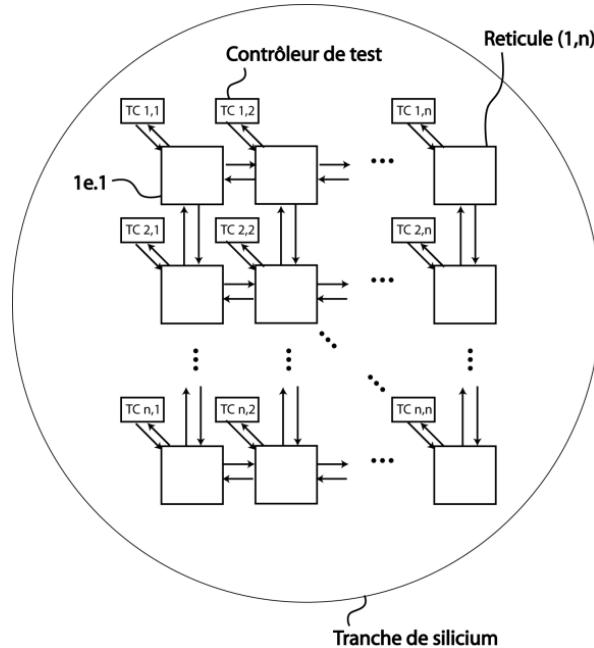

| 2-2 Vue globale du système de communication WaferIC avec les contrôleurs de test .....  | 38 |

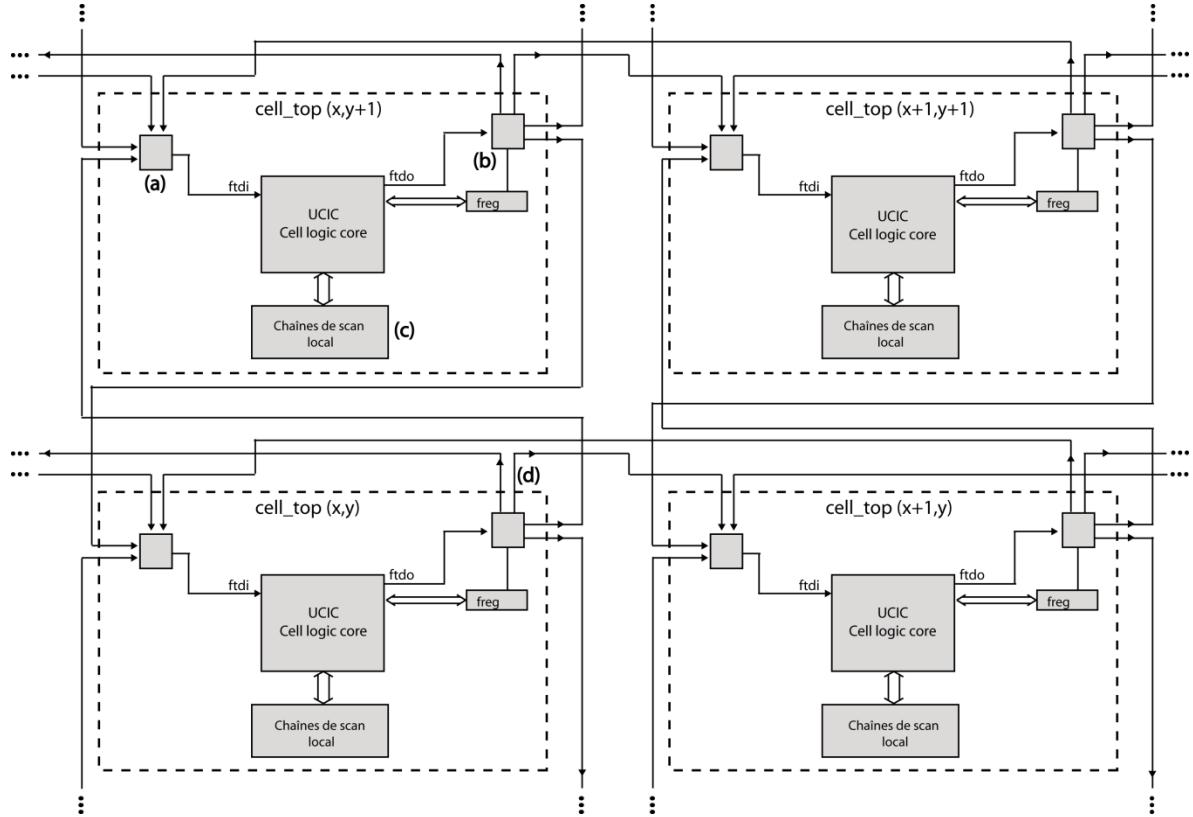

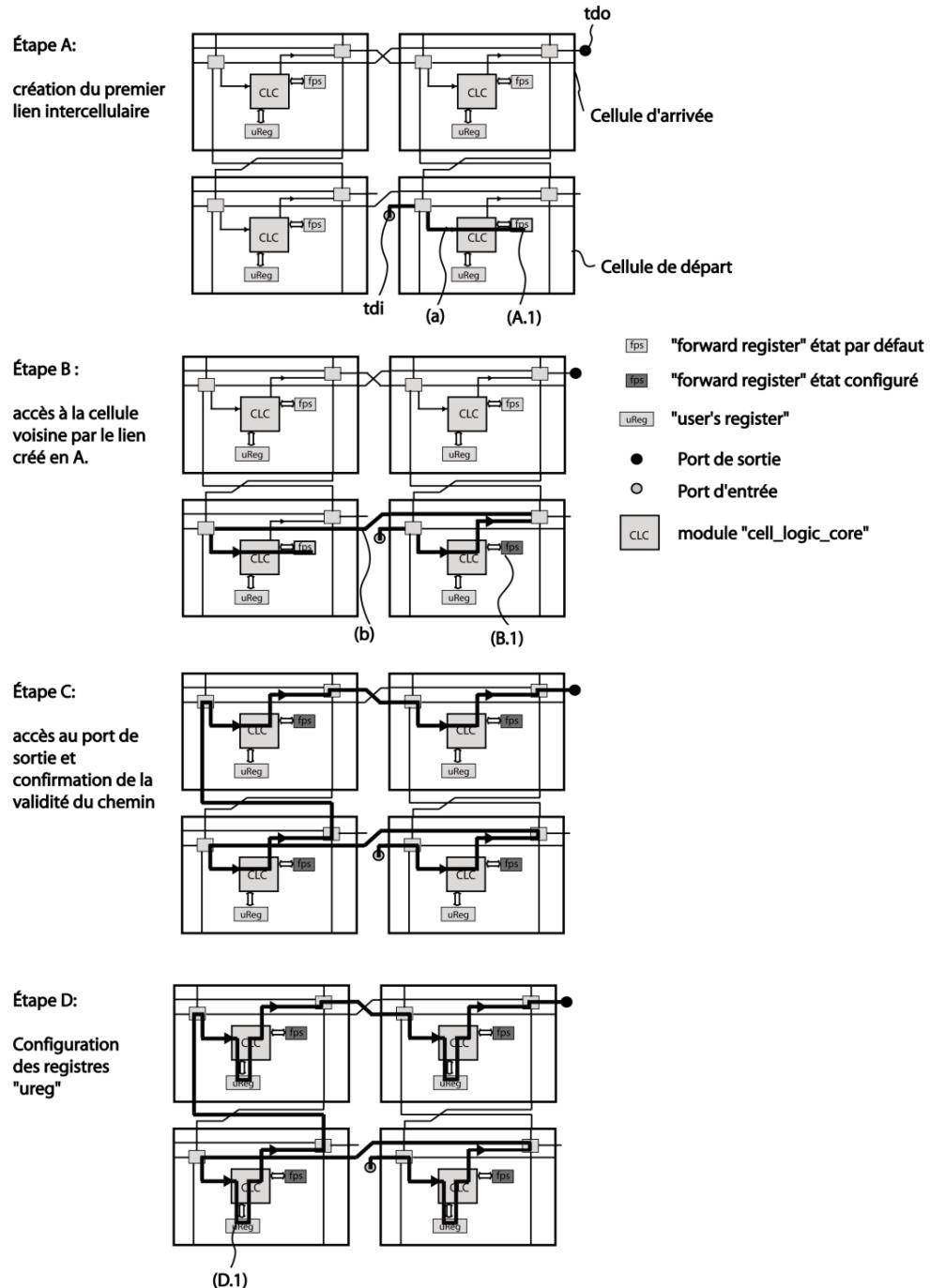

| 2-3 Architecture du système de communication unidirectionnel inter-cellulaire UCIC..... | 40 |

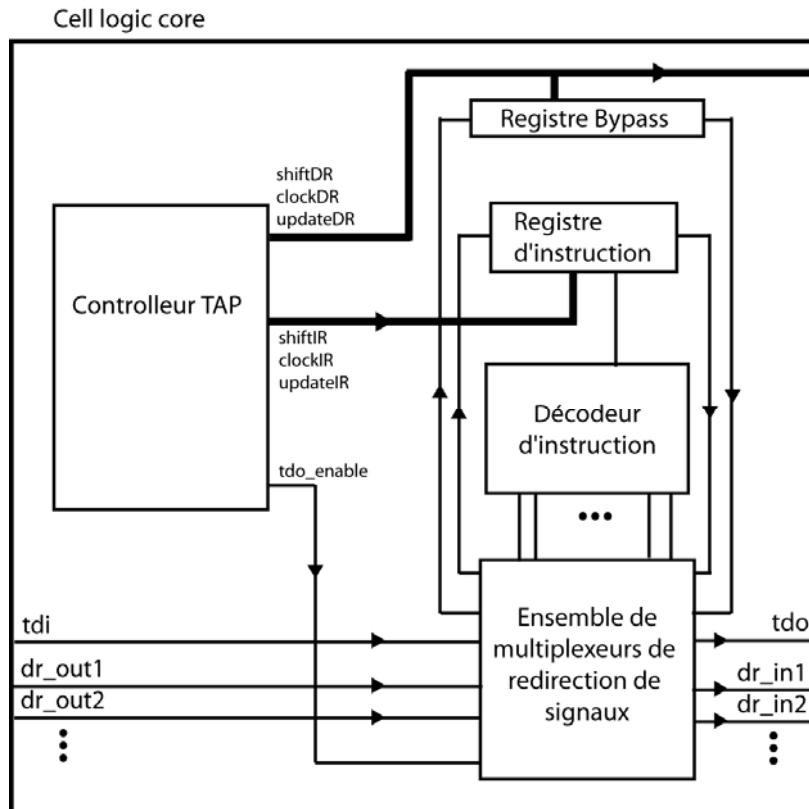

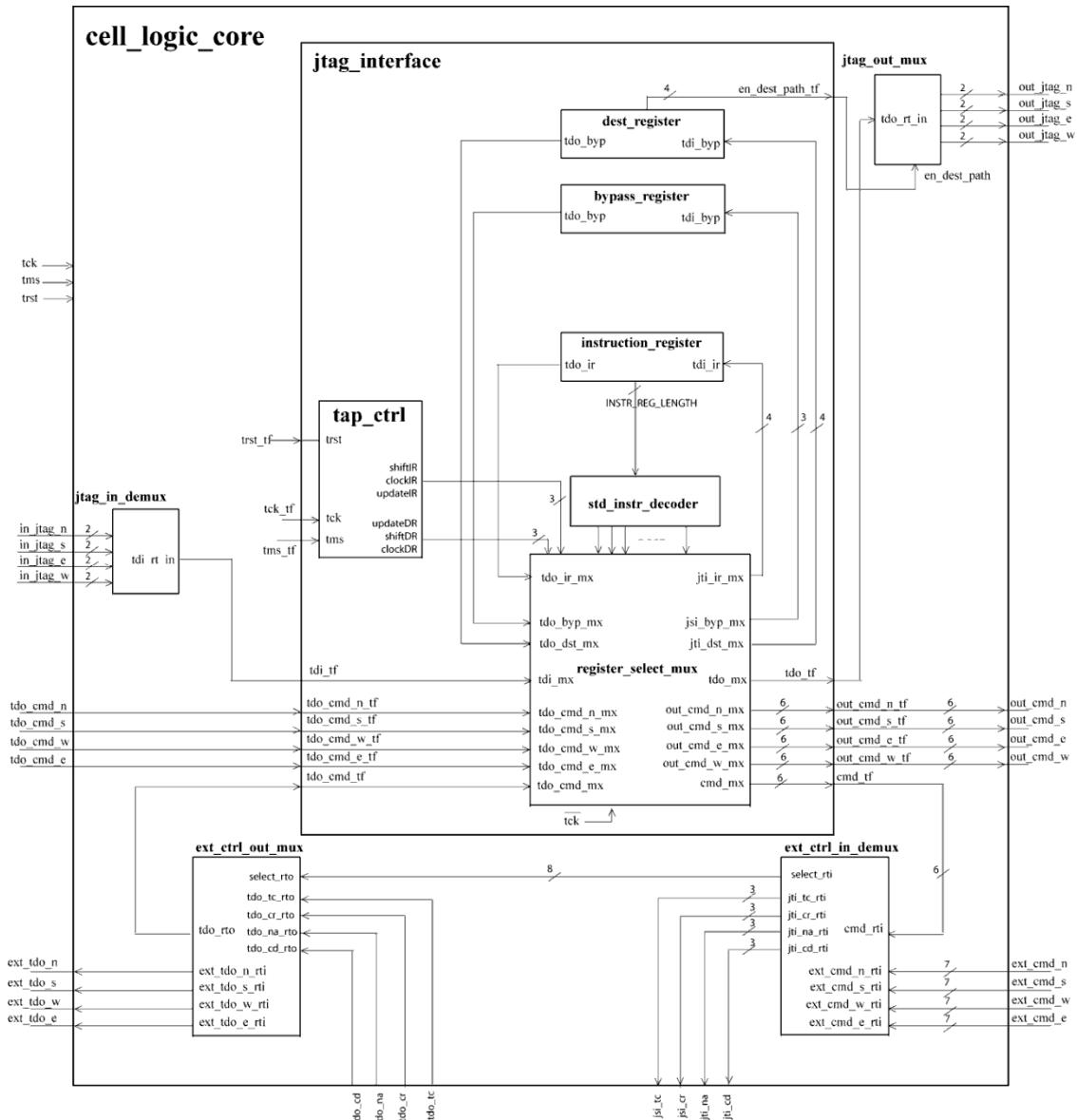

| 2-4 Architecture interne du "cell logic core" pour le système UCIC.....                 | 41 |

| 2-5 Les capacités de tolérance aux fautes pour l'architecture UCIC.....                 | 46 |

| 2-6 Exemple de communication sérielle entre deux réticules voisins .....                | 48 |

| 2-7 L'architecture interne du "cell logic core" pour le système BCIC .....              | 54 |

| 2-8 Les capacités de tolérance aux fautes de l'architecture BCIC .....                  | 56 |

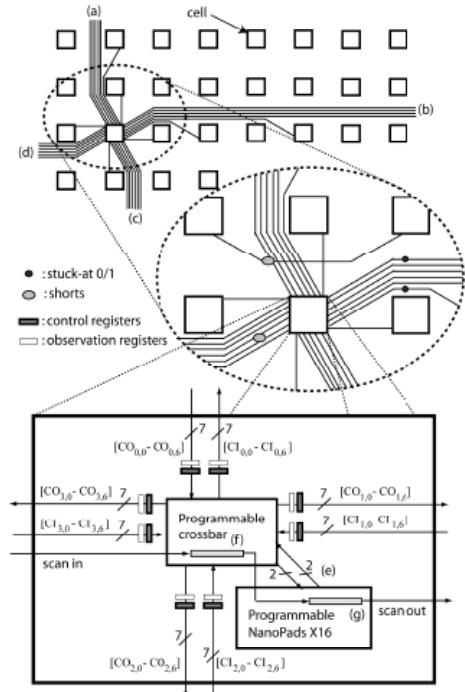

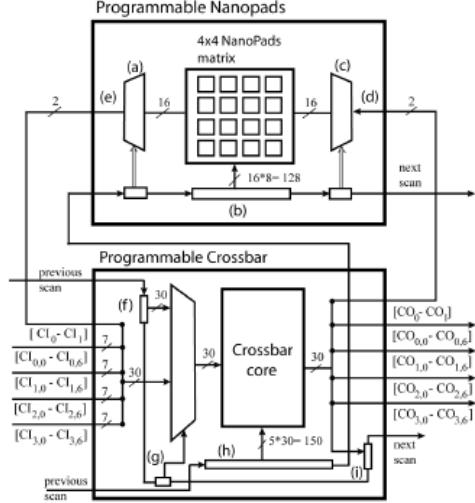

| 3-1 Schéma bloc de l'interaction Nanopads vs Crossbar .....                             | 60 |

| 3-2 Exemple de défaut diagnosticable dans le WaferNet .....                             | 61 |

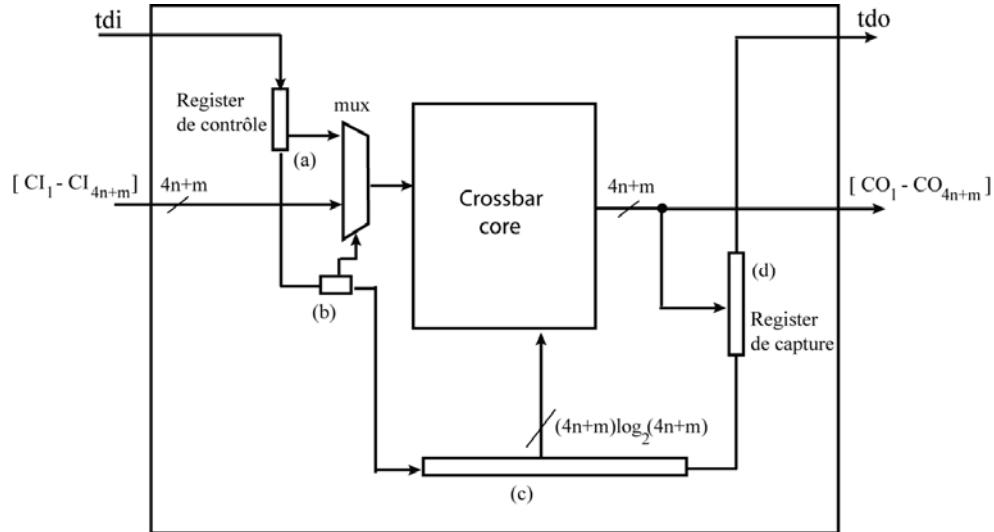

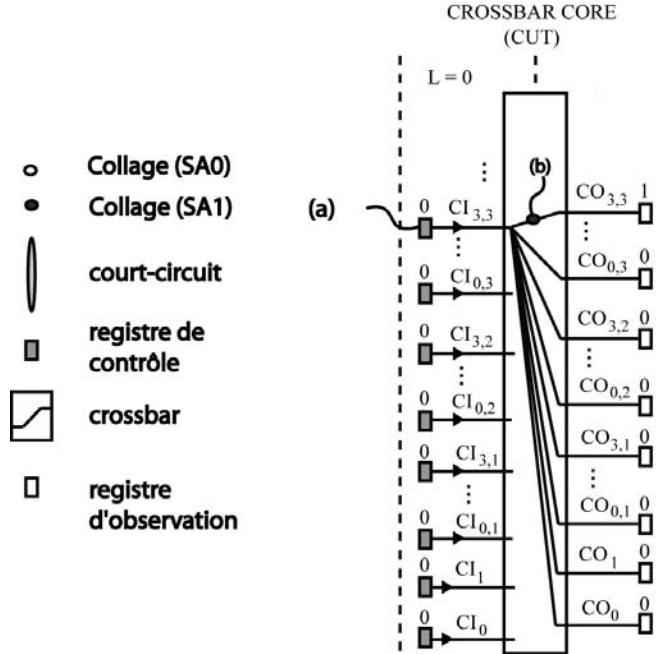

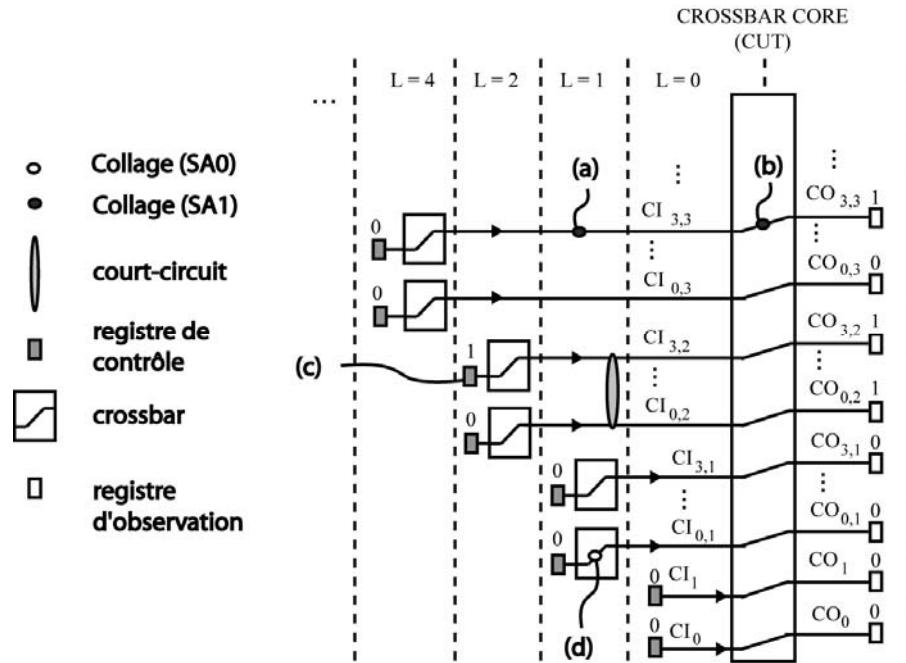

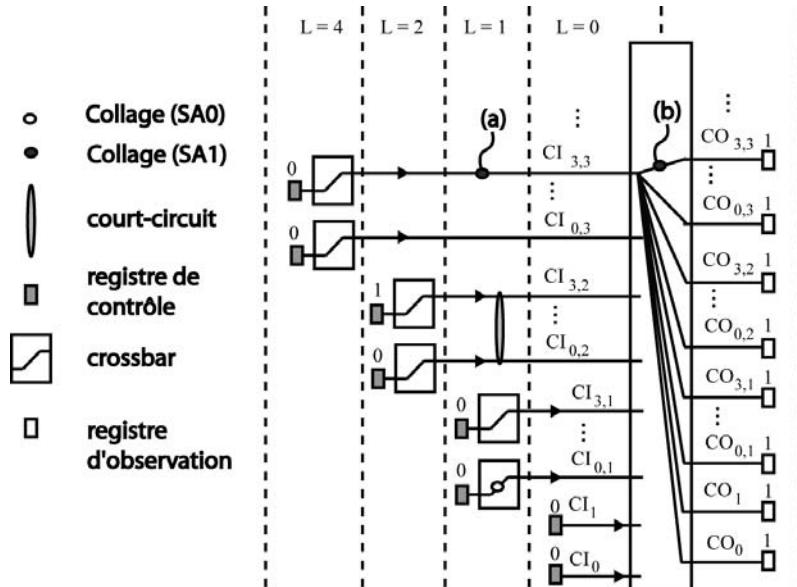

| 3-3 Architecture de test et de diagnostic pour le crossbar .....                        | 62 |

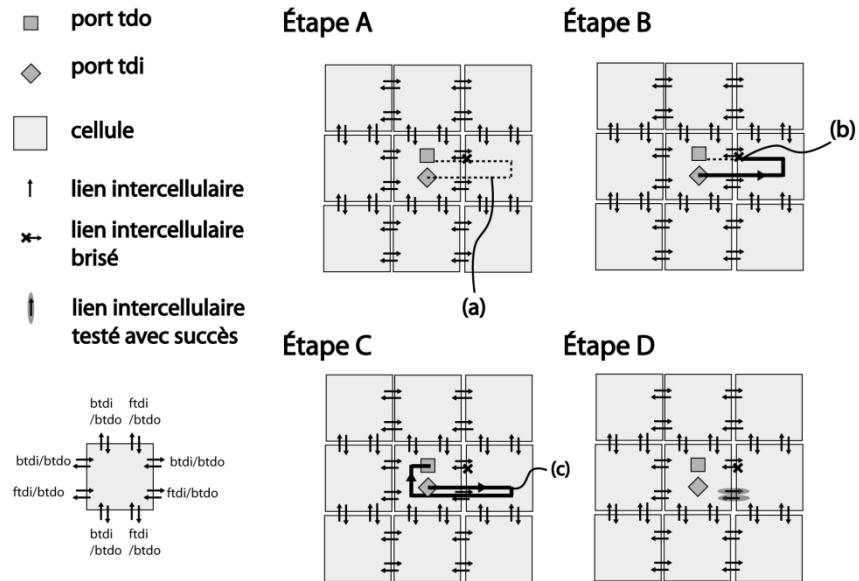

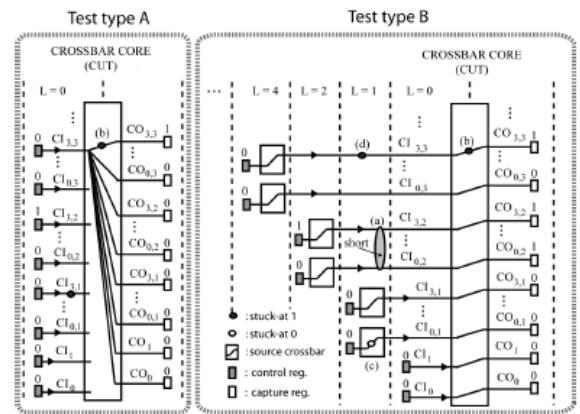

| 3-4 Diagnostic avec le test de type A.....                                              | 63 |

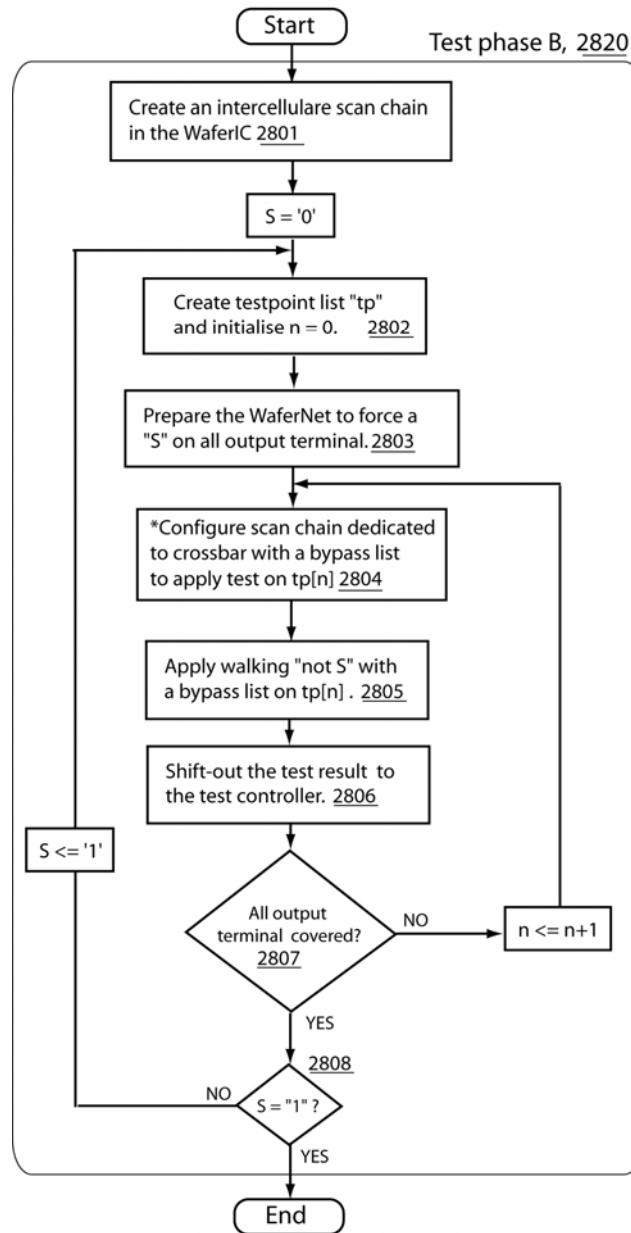

| 3-5 Diagnostic avec le test de type B .....                                             | 65 |

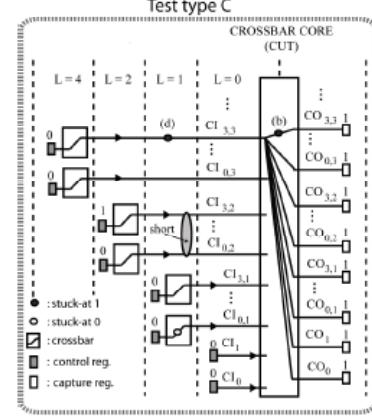

| 3-6 Diagnostic avec le test de type C .....                                             | 66 |

| 3-7 La résolution du diagnostic.....                                                    | 67 |

| 3-8 Les capacités de la chaîne reconfigurable pour le diagnostic .....                  | 71 |

| 3-9 La dynamique de la zone d'influence des court-circuits dans le WaferNet .....       | 72 |

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

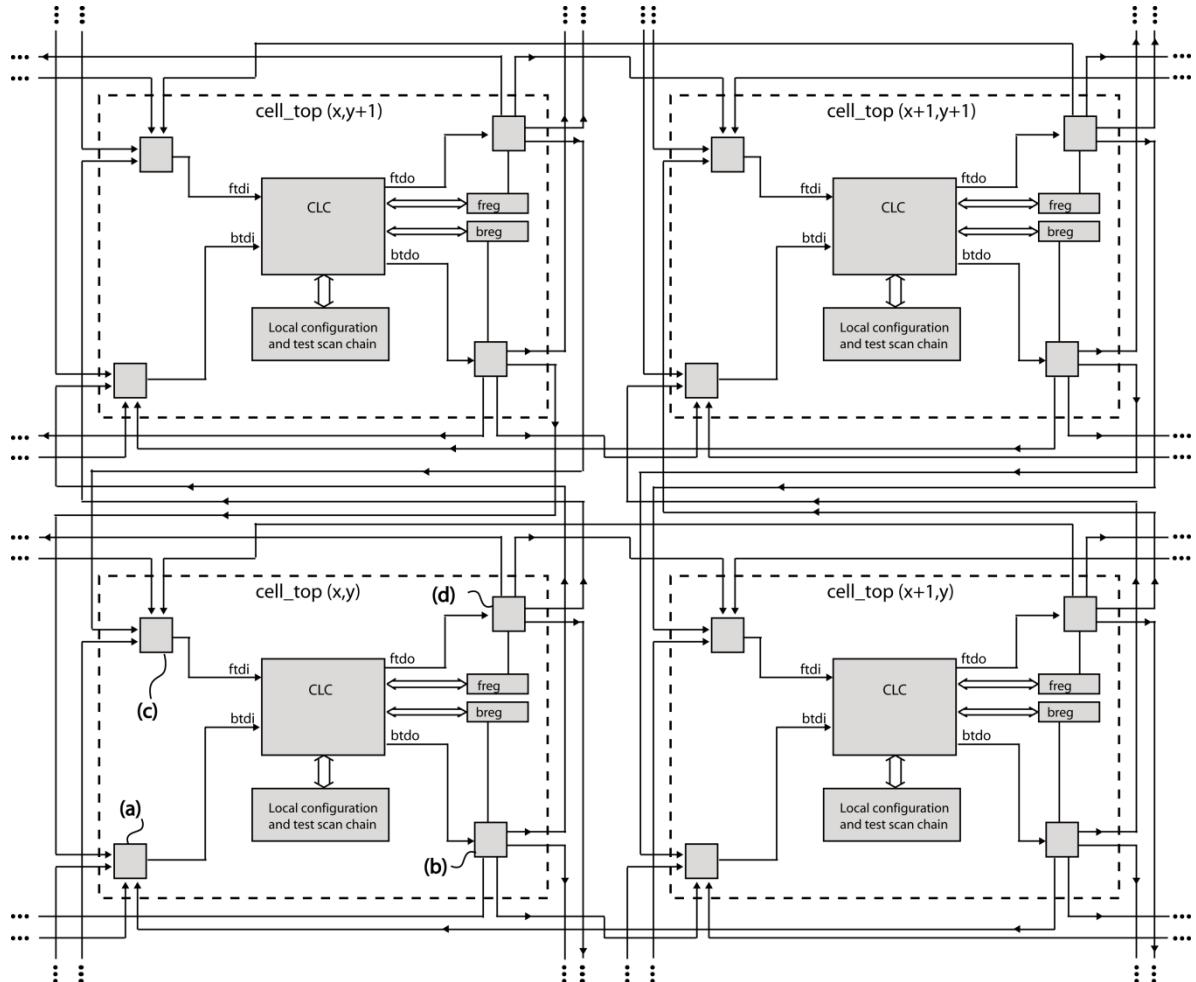

| 4-1 Structure de la chaîne inter-cellulaire .....                              | 79  |

| 4-2 Structure interne du réticule.....                                         | 80  |

| 4-3 Architecture interne de la cellule.....                                    | 81  |

| 5-1 Photo du TestChip V1.0 avant le "packaging" .....                          | 91  |

| 5-2 Vue XY du PCB fabriqué (gauche) et du layout (droite) .....                | 91  |

| 5-3 Propagation du signal dans le WaferNet du TestChip V1.0.....               | 95  |

| C.1 Architecture intercellulaire BCIC.....                                     | 118 |

| C.2 Exemple de diagnostic pour l'architecture BCIC.....                        | 119 |

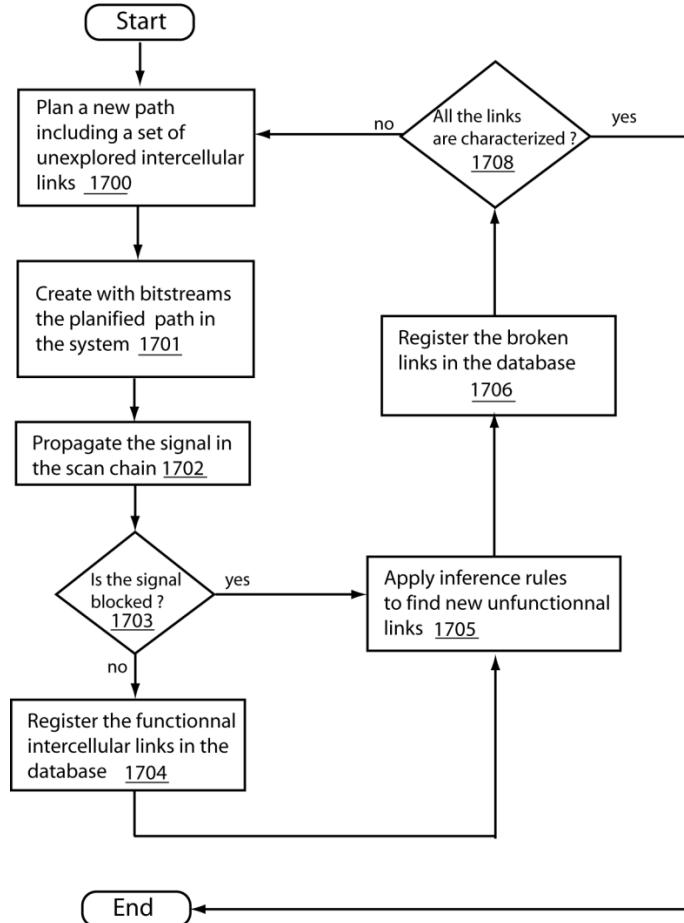

| C.3 Algorithme de diagnostic de fautes dans les liens intercellulaires .....   | 120 |

| C.4 Algorithme optimisé pour le diagnostic de fautes dans le WaferNet.....     | 121 |

| D.1 Description structurale détaillée (VHDL) de l'entité cell_logic_core ..... | 122 |

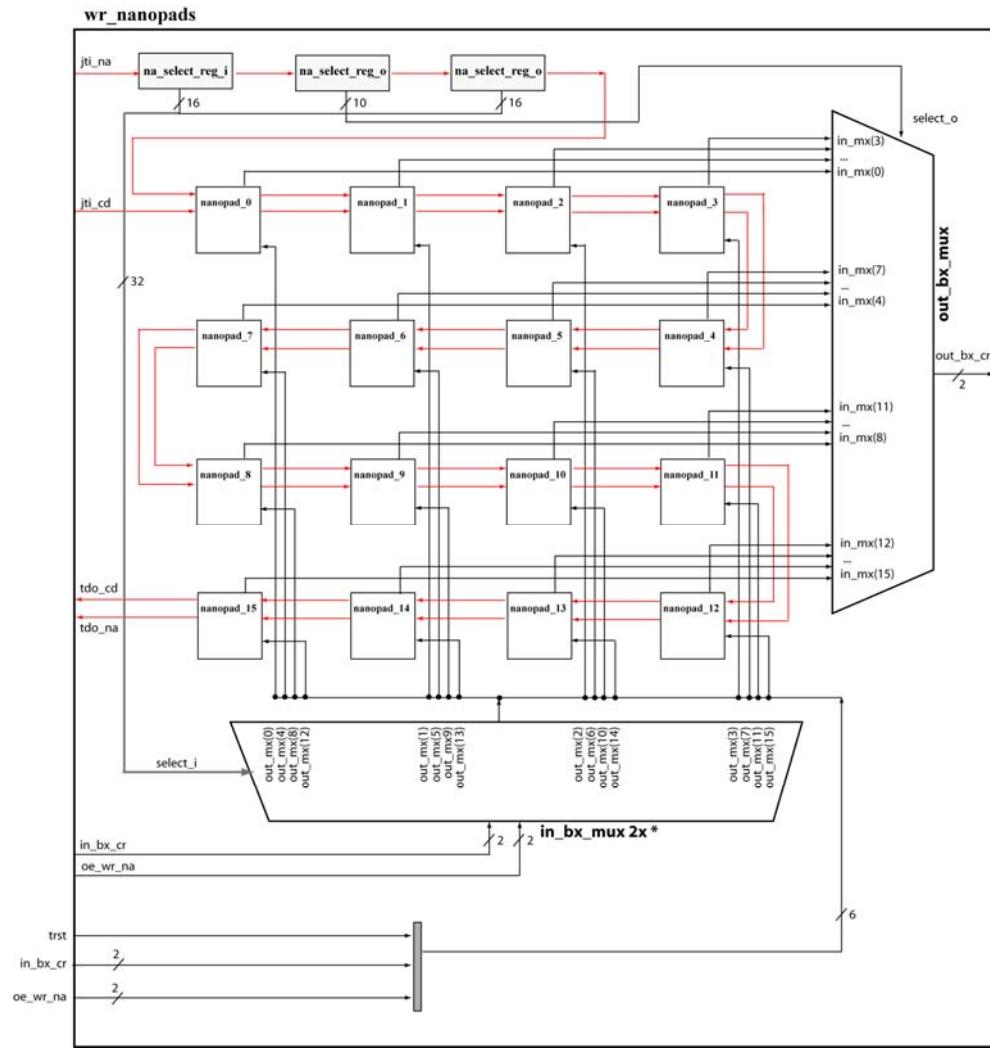

| D.2 Description structurale détaillée (VHDL) de l'entité wr_nanopads.....      | 123 |

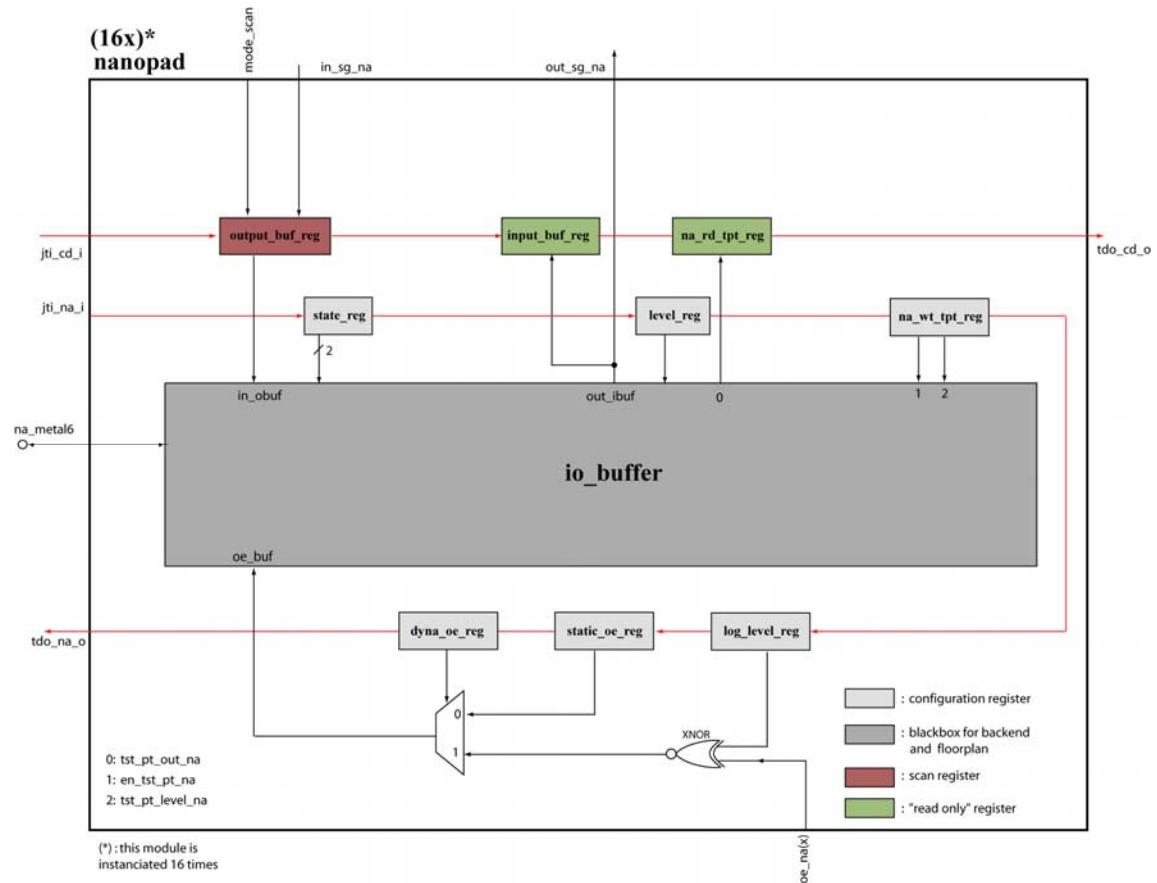

| D.3 Description structurale détaillée (VHDL) de l'entité NanoPad .....         | 124 |

| G.1 Exemple d'application du protocole JTAG.....                               | 136 |

| G.2 Machine à état du “Tap Controller” .....                                   | 137 |

## **LISTE DES SIGLES ET ABRÉVIATIONS**

|       |                                                                   |

|-------|-------------------------------------------------------------------|

| ASIC  | Application Specific Integrated Circuit                           |

| BIST  | Built-In Self-Test                                                |

| BSDL  | Boundary Scan Description Language                                |

| CDSP  | Circuit Discret (sur la surface du WaferIC) Sous Prototypage      |

| CLB   | Configurable Logic Block                                          |

| CUT   | Cell Under Test                                                   |

| DFD   | Design For Diagnosis                                              |

| DFT   | Design For Testability                                            |

| DUT   | Device Under Test                                                 |

| FPGA  | Field Programmable Gate Array                                     |

| JTAG  | Joint Test Action Group                                           |

| LFSR  | Linear Feedback Shift Register                                    |

| MISR  | Multiple Input Signature Register                                 |

| MTG   | Multi-Threaded Graph                                              |

| NoC   | Network on Chip                                                   |

| NoW   | Network on Wafer                                                  |

| PCB   | Printed Circuit Board                                             |

| RTL   | Register Transfer Level                                           |

| SA0/1 | Stuck-At zero/one                                                 |

| SiP   | System in Package                                                 |

| SoC   | System on Chip                                                    |

| SoW   | System on Wafer                                                   |

| TC    | Test Controller                                                   |

| ULSI  | Ultra Large System Integration                                    |

| VHDL  | Very high speed integrated circuits Hardware Description Language |

| VLSI  | Very Large System Integration                                     |

| WSI   | Wafer Scale Integration                                           |

## **LISTE DES ANNEXES**

|                                                                    |            |

|--------------------------------------------------------------------|------------|

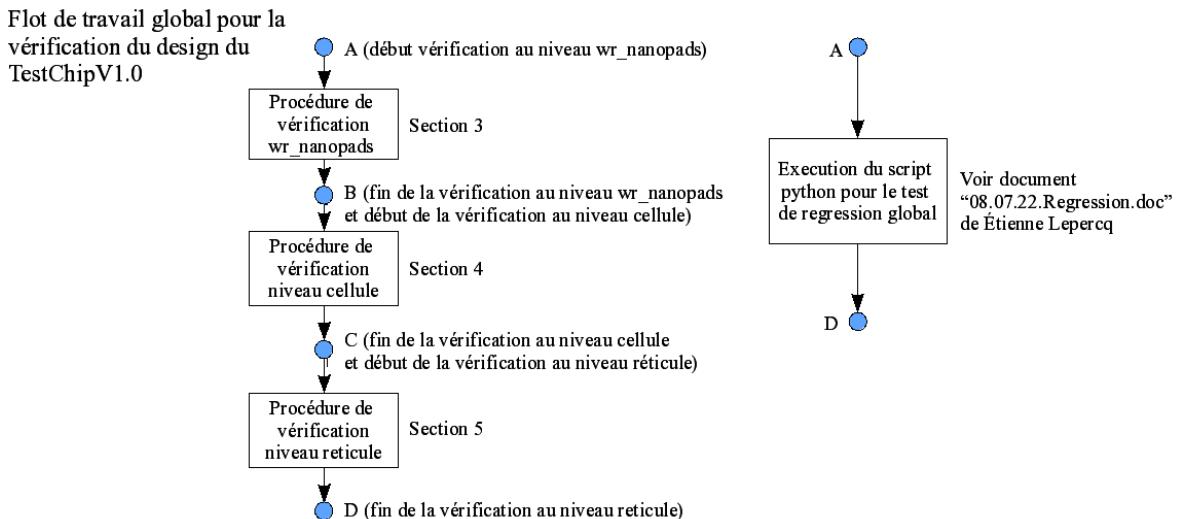

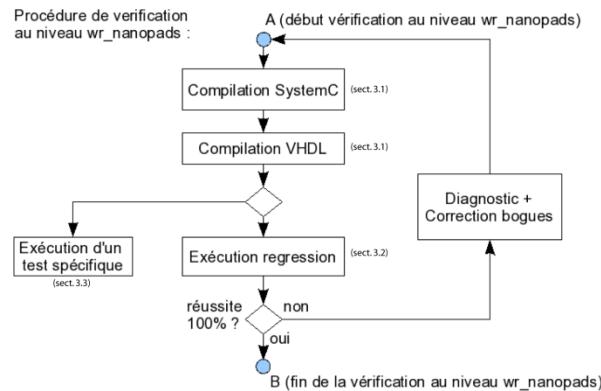

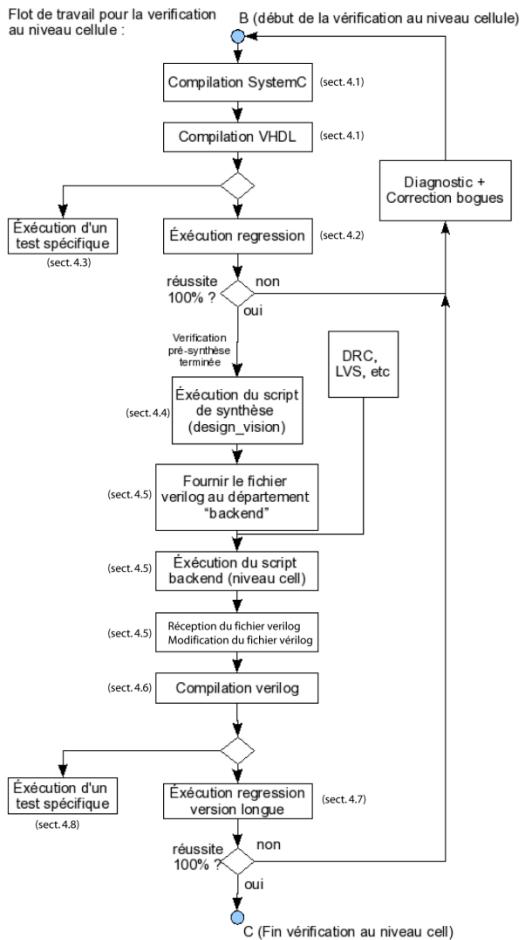

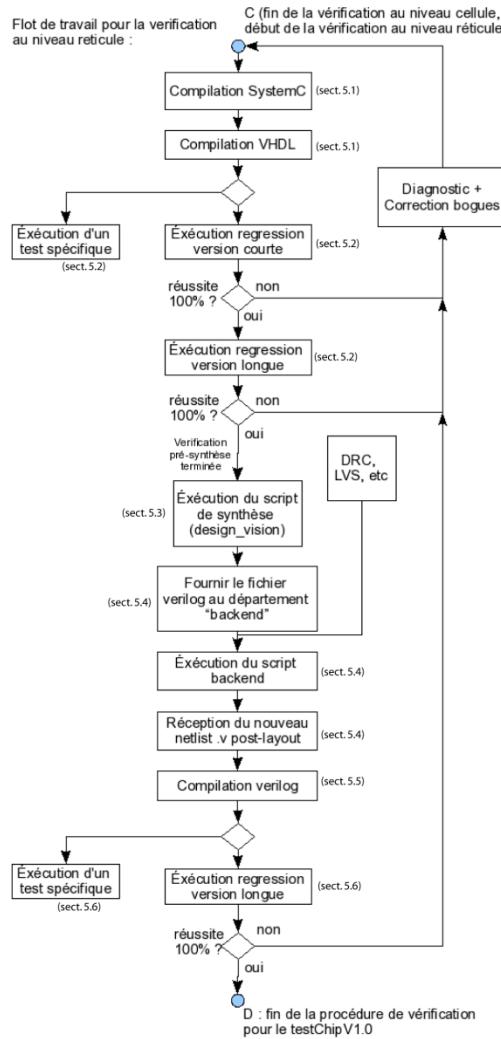

| <b>ANNEXE A – FLOT DE TRAVAIL POUR LA VÉRIFICATION DU TESTCHIP</b> |            |

| <b>V1.0.....</b>                                                   | <b>106</b> |

| <b>ANNEXE B – PLAN DE TEST DU TESTCHIP V1.0.....</b>               | <b>117</b> |

| <b>ANNEXE C – “FLOWCHART” DES PRINCIPAUX ALGORITHMES .....</b>     | <b>118</b> |

| <b>ANNEXE D – PRINCIPAUX SCHÉMAS BLOC .....</b>                    | <b>122</b> |

| <b>ANNEXE E – ARTICLES DE CONFÉRENCES .....</b>                    | <b>123</b> |

| <b>ANNEXE F – TEST DE RÉGRESSION .....</b>                         | <b>133</b> |

| <b>ANNEXE G – RÉSUMÉ DU STANDARD IEEE1149.1 .....</b>              | <b>136</b> |

## INTRODUCTION

Il est bien connu que la miniaturisation et la performance des circuits intégrés s'accroît à un rythme exponentiel. Cette progression s'est maintenue pendant plusieurs décennies, mais depuis quelques années, un ensemble d'obstacles et de problèmes se pointer à l'horizon. Ces obstacles pourraient compromettre cette progression. Beaucoup de ces nouveaux problèmes ne sont pas causés par les circuits intégrés eux-mêmes, mais par les PCB (*printed circuit board*), c'est-à-dire des cartes imprimées qui supportent et relient les circuits intégrés. En effet, la conception d'un système électronique composé de circuits intégrés à la fine pointe de la technologie n'est pas une tâche facile. Plusieurs problèmes attendent les concepteurs qui s'aventurent dans le domaine de la conception de cartes électroniques à haute fréquence et à grande densité. Parmi ces problèmes figure la densité d'interconnexion qui amène des problèmes de routage et de validation.

Présentement, le problème de routage est géré de trois façons qui consistent à :

- 1- Amincir les traces d'interconnexions sur le PCB. Cette solution est rapidement limitée par les procédés de fabrication. En effet, la vitesse de miniaturisation des circuits intégrés dépasse celle de la miniaturisation des interconnexions des PCB.

- 2- Augmenter le nombre de couches d'interconnexion sur le PCB, ce qui augmente le coût de fabrication des systèmes électroniques.

- 3- Augmenter la fréquence des signaux propagés sur les lignes pour augmenter la quantité d'information qui peut transiter entre les circuits. Cette solution est aussi très coûteuse, car bien que possible, cela s'avère requérir une grande expertise de concepteurs de circuits hyperfréquences qui est rare et dispendieuse.

L'augmentation de la densité d'interconnexions des PCB crée un autre problème, celui de la validation. Puisque la densité et le nombre de broches des boîtiers de circuits intégrés ne cesse d'augmenter, la densité des interconnexions des PCB, donc le nombre de couches augmente, complique le test quand il est temps d'accéder à des points de test particuliers

qui sont sous des boîtiers de circuits intégré de type BGA (Ball Grid Array) ou profondément enfouis dans des PCB pouvant comporter plus de 20 couches.

Une autre difficulté qui émerge de la densification des cartes électroniques vient du principe que plus un design est complexe, plus il est difficile de résoudre les bogues matériels et logiciel ainsi que ceux qui résultent de leur interaction. Ce problème est aggravé par l'accroissement de l'utilisation de systèmes embarqués gérés par des systèmes d'exploitation de complexité croissante. Par exemple, pour certains designs dans le domaine des télécommunications, il est possible de rencontrer des bogues qui n'apparaissent qu'après plusieurs milliards de cycles exécutés, ce qui rend le déverminage encore plus ardu. Les problèmes peuvent être autant au niveau logiciel que matériel et il faut être capable de diagnostiquer efficacement un problème pour le résoudre.

Ainsi, le temps de test et de validation de chaque prototype soumis à la fabrication amène des coûts et des efforts non négligeables pour l'industrie électronique. Sans compter les coûts associés au fait qu'il faut souvent plusieurs itérations avec le fabricant de PCB pour arriver à un système fonctionnel. Ceci est problématique quand une ronde de prototypage d'un PCB coûte plus de 10000\$, qu'elle implique des délais de fabrication d'un mois à chaque ronde de correction d'erreur et que ces PCB sont *populés* de composants coûteux et souvent rares dans la phase de développement d'un système. C'est pour répondre à ces problèmes qu'il existe sur le marché toute une gamme de produits visant à permettre la conception rapide et efficace d'un prototype de systèmes électroniques sur PCB. Parmi ces produits figurent les cartes de développement pour CPU ou microcontrôleur, les "*breadboard*", les FPGA et les équipements spécialisés de validation et de test. Un système de prototypage rapide de systèmes numériques idéal aurait les caractéristiques suivantes :

- 1- Capacité à tester le circuit sous test à la fréquence nominale d'opération du circuit prototypé.

- 2- Le circuit prototypé peut être modifié à volonté pendant qu'il est en fonction.

- 3- Le circuit prototypé doit être facile et rapide à modifier.

- 4- Une observabilité et une contrôlabilité de tous les points d'opérations d'intérêt du circuit.

Ainsi, une équipe de conception de système électronique à haute densité et à haute vitesse aurait un avantage indéniable en ayant à sa disposition un système de prototypage rapide de systèmes numériques capable de répondre à toutes ces exigences. Par contre, il n'existe encore aucun système de prototypage rapide de système numérique idéal capable de répondre à toutes les exigences citées plus haut.

Puisque “la nécessité est la mère de toute invention”, un nouveau type de circuit intégré a été inventé pour répondre aux besoins grandissants du marché des PCB et fait l’objet de ce mémoire de maîtrise. Cette invention de monsieur Richard Norman [27] apporte une solution élégante et viable au problème du prototypage de PCB. La conception de ce circuit est réalisée dans le cadre d'un projet de recherche auquel contribuent plusieurs universités (École Polytechnique Montréal, UQAM, UQO et McGill) et soutenu par un partenaire industriel, Gestion TechnoCap Inc. Ce projet se nomme DreamWafer. Le brevet écrit par Richard Norman[27], qui participe intensivement au projet, décrit en détail un nouveau type de circuit intégré à l'échelle de la tranche qui pourrait à terme avoir une application commerciale dans le domaine du prototypage rapide de systèmes numériques. Le circuit intégré à l'échelle de la tranche est un circuit qui se déploie sur toute la surface active d'une tranche de silicium plutôt que sur un seul dé comme avec les circuits classiques. Le propriétaire du brevet est la compagnie Gestion TechnoCap Inc. Cette technologie brevetée se nomme WaferBoard™.

L'idée de base consiste à créer un réseau reprogrammable sur substrat à l'échelle de la tranche. Cela signifie qu'un circuit permet de reprogrammer les interconnexions d'un réseau pour créer un circuit unique correspondant au schéma du circuit (“netlist”) soumis par l'usager. Pour interconnecter entre eux les circuits intégrés d'un système, un système de

configuration doit être conçu avec un pont de communication entre le logiciel et le substrat programmable.

Le circuit intégré à l'échelle de la tranche qui a été conçu et en voie d'être breveté dans le cadre du projet DreamWafer a été baptisé WaferIC. Il contient une matrice de plusieurs millions de plots (appelés NanoPads) de quelques dizaines de micromètres de dimension. Ces plots sont en fait des étages d'entrées/sorties configurables connectés entre eux par un réseau d'interconnexion (WaferNet) reconfigurable. La grande densité de plots évite d'avoir à aligner les broches des circuits intégrés avec les NanoPads. Cela permet d'installer facilement et rapidement un ensemble de puces sur la surface du WaferIC et de configurer dynamiquement leurs interconnexions.

À terme, le WaferBoard<sup>TM</sup> permettra de rabaisser à quelques jours de travail ce qui prenait plusieurs mois avec des prototypes sur PCB conventionnels. Non seulement on y trouve un gain de productivité, mais il y a une économie sur les coûts de prototypage. En effet, sous-traiter la fabrication d'un prototype sur PCB peut coûter très cher. Chaque aller-retour avec le fabricant de PCB implique un coût. De ce fait, on abaisse sensiblement le coût de développement d'un nouveau produit électronique (économie sur les salaires d'ingénieurs et sur l'utilisation d'équipement de test). De plus, le temps d'arrivée sur le marché ("*time-to-market*") est un aspect économique important qui est pris en compte par les acteurs de l'industrie de l'électronique.

Une petite équipe interuniversitaire (Polytechnique-UQAM-UQO) s'est formée pour la conception et la réalisation d'un circuit prototype à petite échelle (4 étudiants à la maîtrise, 4 professeurs, 1 post-doctorant). Certains membres de l'équipe se concentrent plus sur l'aspect analogique. Olivier Valorge qui vient de compléter son stage postdoctoral a travaillé à résoudre des problèmes au niveau de l'alimentation en puissance, de l'intégrité du signal, de la propagation rapide des signaux et du design physique. Nicolas Laflamme-

Mayer, étudiant à la maîtrise, travaille sur un système distribué de régulateurs de tension et de puissance pour le WaferIC. Étienne Lepercq, étudiant à la maîtrise, contribue au WaferNet, principalement au niveau logiciel sur la méthodologie de travail nécessaire pour automatiser le travail des concepteurs matériels qui utiliseront le DreamWafer. Moufid Radji, aussi étudiant à la maîtrise, travaille sur l'aspect micro-fabrication et “post-traitement” du WaferIC.

Les sujet de recherche de cette maîtrise couvre la conception du système de communication numérique entre le logiciel et le WaferIC. La partie spécifique de mon projet de maîtrise consiste en la conception d'un système de configuration tolérant aux pannes pour le WaferIC, en la mise au point d'un environnement de simulation et de vérification matérielle codé en SystemC et en VHDL, à la conception de l'interface logicielle/matérielle pour le contrôle de la configuration basé sur le protocole JTAG[28] et la conception d'une méthodologie de test et diagnostic du système de configuration.

Pour accéder aux fonctionnalités du WaferIC, il faut un système de programmation tolérant aux pannes, que l'on peut reconfigurer en fonction des zones mortes du circuit. Une zone morte est un endroit défini dans le circuit où il est connu qu'une défaillance fonctionnelle existe. Cette défaillance crée par effet domino d'autres défaillances sur des zones déterminées du circuit. Tout élément contenu dans ces zones ne doit donc pas être utilisé par le système. Ce système a été basé sur le protocole IEEE 1149.1 JTAG. Pour commander le WaferIC à partir d'un ordinateur, il faut mettre au point un émulateur JTAG adapté aux besoins spécifiques du circuit. Un environnement de vérification a été codé en C++ et en SystemC pour tester et vérifier l'interface logicielle/matérielle et pour vérifier la validité des fonctionnalités internes de chaque cellule. Un plan de vérification a été rédigé et plusieurs cas de test ont été développés pour valider le WaferIC, ainsi que l'émulateur logiciel du JTAG. De plus, il est important de rendre le WaferIC testable et diagnosticable, en prenant en compte le protocole JTAG.

Parmi les résultats publiés dans ce mémoire figure le bilan du plan de vérification, ainsi que les résultats de test et diagnostic du premier prototype “ASIC” d'un sous-ensemble du WaferIC fabriqué par l'entremise de CMC Microsystèmes en technologie CMOS 0.18 µm. Ce premier prototype ASIC a été testé grâce à un système de test de circuit adapté à notre situation particulière de test. Mes contributions au développement du système de test du circuit sont décrites dans le reste du mémoire.

Le mémoire est organisé en 5 chapitres :

- Une revue de la littérature et un bref résumé du brevet de R. Norman sur le WaferBoard et le WaferIC sont présentés au chapitre 1.

- De nouvelles solutions matérielles au problème de la configuration JTAG tolérante aux défectuosités sont présentées au chapitre 2.

- La méthode de test et de diagnostic à base de logiciel du WaferNet sont décrites au chapitre 3.

- L'implantation matérielle de la solution et sa vérification sont présentées au chapitre 4.

- Les résultats de la validation de notre solution sur un ASIC de test et divers résultats connexes sont présentés au chapitre 5.

## CHAPITRE 1. REVUE DE LITTÉRATURE

Le présent chapitre est composé de 5 parties. Les deux premières parties visent à décrire les tendances dans l'évolution et les limites des systèmes sur puce (SoC) et des systèmes sur PCB. Ensuite, la troisième partie vise à décrire la technologie et le paradigme des systèmes sur tranche (SsT) qui devraient à terme dépasser en complexité les deux précédentes familles de systèmes électroniques (SoC et PCB). En quatrième partie, un effort particulier doit être investi dans la description du WaferIC qui se veut une nouvelle famille de circuit intégré. Le WaferIC est un concept en voie d'être breveté par Richard Norman. En effet, un brevet a été déposé avant le début du projet DreamWafer. Finalement en cinquième partie, les fondements technologiques sur lesquels se basent les contributions de ce mémoire sont décrits. Ces fondements sont la tolérance aux pannes dans les chaînes de balayage, et le diagnostic de pannes dans un réseau sur puce.

### 1.1 L'évolution des systèmes sur puce (SoC)

Dès les débuts de la commercialisation des processeurs intégrés sur puce comportant des périphériques intégrés sur le même substrat, l'industrie est entrée dans l'ère des systèmes sur puce, généralement connue selon son nom anglais de “System-On-Chip” (SoC)[30]. Les systèmes sur puce intègrent sur un même substrat de semiconducteur les fonctionnalités de plusieurs types de circuits, pour créer un composant capable d'effectuer des fonctions complexes, effectuées auparavant par des systèmes électroniques entiers comportant plusieurs puces discrètes. Les systèmes sur puces peuvent contenir des circuits numériques, analogiques/mixtes et souvent ils contiennent des circuits radio-fréquence.

L'inclusion de tous ces types de modules sur un seul circuit intégré a nécessité un effort de recherche et développement très intensif. Cet effort continue de se maintenir pour améliorer plusieurs aspects des SoC. Avec leur évolution, il se dessine des limitations techniques

difficiles à contourner qui devraient ralentir la progression de cette technologie dans les années à venir.

Voici une liste non exhaustive de ces limitations :

- 1- *La consommation en puissance*** : À mesure que les procédés de fabrication avancent vers des niveaux de miniaturisation de plus en plus proches du nanomètre, de nouveaux problèmes physiques apparaissent. À des échelles bien plus petites que le micromètre (inférieures à 45 nm), le phénomène de courant de fuite devient de plus en plus significatif et même nuisible. Ceci crée des circuits plus rapides et plus petits, mais parfois beaucoup moins efficaces énergétiquement. Des solutions peuvent s'appliquer pour contourner le problème. Par exemple, des techniques modernes de gestion dynamique de la puissance permettent d'adapter dynamiquement le niveau de tension ou de fréquence en fonction des besoins.

- 2- *L'accroissement de la complexité*** : La surface maximale occupée par un circuit intégré est actuellement limitée par un grand nombre de facteurs, parmi lesquels figurent les erreurs de lithographie associées à la méthode de fabrication des circuits, la pureté des matériaux et des produits chimiques, etc. Pour rendre cette technologie rentable, il est obligatoire de couper la tranche de silicium en “dés” et d’encapsuler ces “dés” dans un boîtier pour être fixés sur un PCB et pour être connecté à d’autres circuits intégrés.

- 3- *Le rendement de production*** : La taille d’un circuit intégré n’affecte pas seulement le coût de fabrication en utilisant plus de silicium, mais elle affecte surtout la probabilité de retrouver une défectuosité de fabrication sur sa surface. À mesure que la surface du circuit s’accroît pour atteindre la grandeur de la tranche de silicium qui le constitue, la probabilité de trouver une défectuosité s’accroît rapidement vers un.

C'est pour cette raison que les méthodes standards de conception de circuit ne permettent pas de fabriquer des circuits à l'échelle de la tranche (WSI : wafer scale integration).

- 4- *La photo-répétition et la taille des réticules :*** Une autre limitation de la grandeur des circuits intégrés vient de la méthode de la photolithographie elle-même. Les circuits intégrés sont fabriqués à partir de la répétition d'image essentiellement carrée sur une tranche de silicium par le principe de la photo-lithographie [23]. La structure 'imprimée' de façon répétitive sur la surface de la tranche est communément appelé un réticule et son empreinte sur la surface de la tranche n'excède typiquement pas 2,5 cm de coté. La taille du réticule proprement dit est généralement plus grande que l'image réticulaire par un facteur déterminé (comme 5X par exemple). Par conséquent, tout design de circuit intégré à l'échelle de la tranche de silicium doit normalement être composé d'un agencement de cellules régulier à l'échelle de l'image d'un réticule, sans quoi il faudrait disposer d'autant de jeux de masque que d'images distinctes, ce qui bien que théoriquement possible devient prohibitif.

## 1.2 Les limitations des systèmes sur PCB

Les systèmes sur PCB ne cessent de se complexifier. La bande passante demandée entre les circuits intégrés ne cesse d'augmenter, à mesure que les capacités de calcul et de traitement des circuits intégrés s'améliorent.

Cette augmentation de la complexité cause plusieurs problèmes, dont les deux cités ici.

- 1- La complexité croissante des PCB rend le test et le débogage au niveau système ardu.** La miniaturisation des boîtiers et des broches («pins» en anglais)

qu'ils possèdent pour relier des puces au reste d'un système électronique ne cesse de s'améliorer avec le temps. Le diamètre d'une des balles métalliques qui sertit un boîtier de circuit intégré atteint 200 µm en 2009. Cette progression entraîne une augmentation de la densité d'interconnexion des traces (lignes électriques) sur le PCB pour atteindre une largeur de 85 à 100 µm cette année (2009) [17]. Les circuits de la classe FPGA utilisent des matrices de plots d'une densité linéaire de 45 plots par cm et cette densité ne cesse d'augmenter [33]. L'augmentation de la densité des traces entraîne des difficultés pour les concepteurs de PCB, car les méthodes traditionnelles de test telles que le "bed of nails" (test sous pointe) deviennent de plus en plus difficiles et coûteuses à appliquer. Dans certains types de circuits sur PCB très dense, des portions du circuit deviennent même impossibles à tester avec ces méthodes, car les points d'accès sont parfois cachés par plusieurs couches de métallisation et d'isolation et le réseau d'interconnexions du circuit qu'ils implémentent est très dense.

**2- La complexité croissante des PCB rend de plus en plus important l'accroissement de productivité des concepteurs.** Beaucoup de technologies alternatives ont été développées pour améliorer quelques-uns des inconvénients. Parmi ces solutions alternatives, il y a les MCM (multi-chip module) pour les systèmes à haute performance. Une autre solution est d'empiler des puces ("stacked chip"), mais elle ne peut supporter aujourd'hui qu'un nombre limité de puces empilées.

Une foule d'outils ont été conçus pour tenter de résoudre ces problèmes. Parmi les solutions existantes, deux ont retenu notre attention comme étant suffisamment proches de la technologie WaferBoard pour être décrites dans ce document.

## 1- Le modèle Zebu XXL

Le ZebuXXL **Erreur ! Source du envoi introuvable.** est un émulateur de système capable de tester des FPGA ou des ASIC en relation avec le système global qui les entoure. Ainsi, le ZebuXXL peut être configuré rapidement et facilement pour émuler le comportement du système global sous test. Il a été conçu pour être utilisé au niveau de la vérification logiciel-matériel à l'étape finale de l'intégration de toutes les parties d'un système. De cette façon, les concepteurs logiciels et matériels peuvent partager un même environnement de développement et de vérification, ce qui permet d'améliorer la productivité d'une équipe de travail.

**ZeBu-XXL**

1-1 La plateforme Zebu-XXL.

Cette technologie utilise une approche différente de la technologie WaferBoard pour faire du prototypage rapide de systèmes numériques. Le ZebuXXL peut émuler le comportement numérique d'un SoC à partir d'une description RTL synthétisable, si cette description RTL a une complexité inférieure à ce que l'émulateur peut gérer.

## 2- Le modèle NanoBoard

Le NanoBoard est un des premiers systèmes de prototypage rapide de système numérique qui a été offert sur le marché [13]. Ce système n'est pas un émulateur comme le modèle ZebuXXL, mais un véritable système permettant d'augmenter la vitesse de prototypage de système numérique. La technologie a été développée par Altium, une compagnie très innovatrice et ancienne qui a, entre autres, été la première à commercialiser un logiciel CAO pour la conception de circuits imprimés. Continuant à innover dans son domaine

d'excellence, Altium a développé un système d'aide à la conception pour les systèmes intégrés qui comprend à la fois un logiciel CAO et un environnement de développement matériel qui permettent d'accélérer la conception de systèmes électroniques complexes.

1-2 La plate-forme de développement NanoBoard<sup>TM</sup>.

Les circuits intégrés qui sont au cœur du système à concevoir sont soudés sur une carte imprimée spéciale dite “daughter-board” qui est capable de se connecter à l'environnement de développement. Une fois connectés, tous les circuits qui sont sur le “daughter-board” peuvent être testés et vérifiés avec l'aide des logiciels CAO fournis avec le NanoBoard pour accélérer dramatiquement le développement du produit. Le NanoBoard peut ainsi déverminer des circuits numériques reprogrammables (FPGA) et de petites cartes de développement tout en supportant une interaction temps réel avec le système en cours de conception.

### **1.3 L'avènement des systèmes sur wafer (SoW)**

La demande pour une intégration croissante de modules hétérogènes dans des volumes de plus en plus petits a amené la création du principe de SiP (System in Package) [22]. Ce type de puce est dite “3D” parce qu'elle permet d'empiler verticalement des circuits intégrés dans un même boîtier. Ce type de circuit est principalement utilisé dans le domaine des cellulaires et autres circuits électroniques portables. Puisque le marché des cellulaires est en pleine croissance, il existe un grand nombre d'usines de fabrication capables de produire à

grande échelle des SiP et la croissance de ce segment du marché se mesure avec un taux de croissance à 2 chiffres.

Comme alternative au SiP (ou comme solution compétitrice), un nouveau concept a été proposé en 2009 sous le nom de “System on Wafer” (SoW) par une équipe de recherche française, le LETI-CAE [29]. Cette approche consiste à souder des circuits intégrés “flip-chip” sur un wafer complet avant de le découper et l'enfermer dans un boîtier. Cette méthode permet d'empiler 2 étages de circuits. Le principal avantage de cette approche est d'utiliser un substrat de silicium comme interconnexions et support mécanique entre les “flip-chip”. Cette technologie permet d'ajouter une foule de circuits actifs CMOS au système existant. Ces circuits peuvent servir comme circuit de test, circuit de reconditionnement de signal, etc. Même si on n'intègre pas de circuit actif CMOS dans le substrat, le procédé de fabrication peut tout de même atteindre des résolutions d'un ordre de grandeur supérieur à ce qui peut se faire de mieux dans le domaine des PCB, ce qui permet de faciliter les routages denses entre les flip-chips du SoW.

C'est dans ce contexte qu'est apparu le brevet de R. Norman [27] décrivant les bases de la technologie WaferIC. La section suivante vient décrire la technologie telle qu'elle a été conçue par R. Norman en 2007. De plus, une revue des plus récents développements du projet et des articles publiés sur le sujet est effectuée.

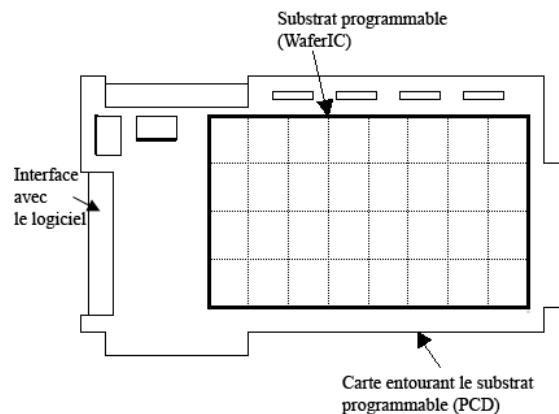

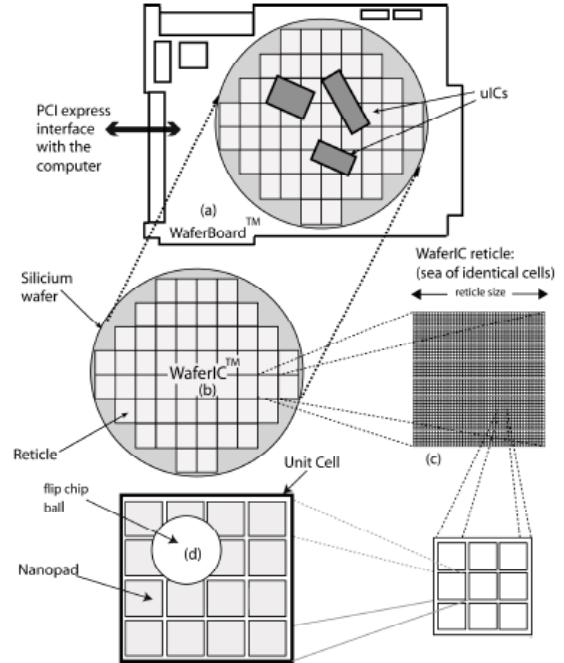

#### 1.4 Le WaferBoard

Le WaferBoard<sup>TM</sup> est un système de prototypage rapide pour les circuits numériques. Le système est conçu à partir d'un SST et permet de tester, valider rapidement des circuits au niveau système. Une carte électronique comprend principalement un substrat programmable (le WaferIC) et une interface rapide pour se connecter à un ordinateur (voir fig. 1-3). Le substrat programmable est un circuit électronique de type “*wafer scale IC*”, c'est-à-dire un circuit intégré au niveau de la tranche de silicium. Cette technologie permet la communication de données entre plusieurs réticules d'une même tranche. Ces données

sont propagées directement par les couches de métallisation intégrées sur la tranche de silicium. Le substrat programmable est connecté à une carte PCI express par le dessous de la tranche et échange des données avec un ordinateur hôte pour l'auto-test, la configuration, la programmation, le test du système conçu par l'usage en cours de prototypage. Les données fournies par l'ordinateur sont des bits de configuration pour permettre au substrat programmable d'adapter sa topologie de connexions internes pour implémenter une “*netlist*” représentant les interconnexions voulues par un ingénieur procédant au design d'un système numérique.

Par exemple, les données transmises à l'ordinateur sont des lectures de points de contact entre les broches des circuits discrets et la surface du substrat. Les circuits discrets déposés à la surface du WaferIC seront appelés dans ce document des CDSP (circuit discret sous prototypage).

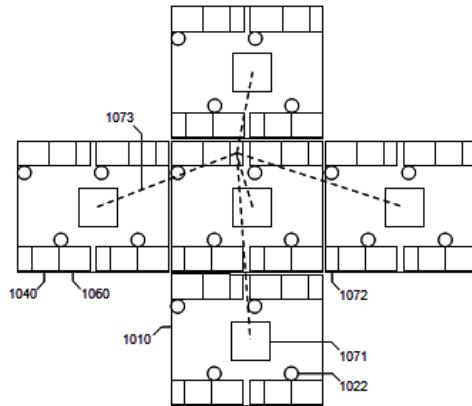

1-3 Exemple de WaferBoard. Image tirée du brevet [27].

Le WaferBoard est par conséquent un système de prototypage rapide capable d'interconnecter rapidement un ensemble de composants électroniques. C'est en quelque sorte un PCB reprogrammable supportant une densité d'interconnexion supérieure aux PCB multicouches conventionnels. Le *Wafer Integrated Circuit* (WaferIC) est le nom donné au substrat actif qui peut être beaucoup plus grand qu'un circuit intégré conventionnel. Ce

substrat actif dépasse la taille limite d'un réticule et il peut occuper la surface complète d'une tranche de silicium. Une expression utilisée couramment dans ce document est "substrat programmable" pour exprimer l'idée qu'un substrat qui peut couvrir une tranche entière de silicium, peut être programmé pour réaliser les interconnexions désirées à l'échelle du système. À partir d'un WaferIC, il est possible de concevoir une nouvelle famille de circuits intégrés capable d'attaquer des problèmes difficiles à résoudre avec les familles de circuits intégrés de la taille d'un réticule assemblés sur PCB ou MCM .

Le WaferBoard peut réduire le temps de développement et les coûts qui sont associés au développement de systèmes impliquant un PCB et plusieurs circuits digitaux discrets. Par analogie, les FPGA ont contribué à réduire le temps de développement de circuits intégrés par rapport aux ASIC en permettant l'utilisation d'un tissu logique programmable pré-manufacturé, capable d'émuler le comportement d'une fonction logique complexe.

L'analogie entre les FPGA et le WaferBoard peut être poussée jusqu'au niveau de la production. Tout comme les ASIC ont un coût de production inférieur aux FPGA pour de grands volumes, un design fait à l'aide d'un PCB aurait un coût de production inférieur à un WaferBoard pour un design vendu en grande quantité. Par contre, il est connu qu'un système réalisé à l'aide de FPGA peut rivaliser en termes de coût de production avec les ASIC pour les produits complexe vendus en volume modéré.

Pour être compétitif sur le marché, les systèmes électroniques (avec PCB ou MCM) actuels doivent incorporer des circuits intégrés discrets d'une complexité croissante, tout en rencontrant des contraintes de plus en plus exigeantes au niveau de la consommation de puissance et de la taille. Quelques-unes des principales difficultés ne viennent pas des composants discrets mais de leurs interconnexions. En effet, les outils de simulation et de CAO dédiés au domaine du design de PCB sont tous très matures et la fiabilité des designs à ce niveau est très bonne.

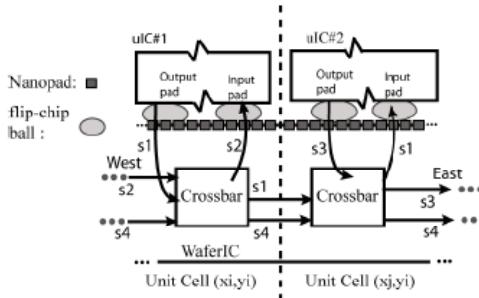

Dans le cas du WaferBoard, les composants électroniques sont simplement déposés manuellement sur une surface active qui a la capacité de détecter les contacts entre elle-même et ces composants. Cela signifie que le WaferIC permet un placement insensible à l'alignement contrairement aux PCB dont les circuits discrets doivent être soigneusement alignés sur des plots avant de les souder. Le WaferIC envoie les informations sur le placement des circuits intégrés ce qui permet par la suite au système d'afficher le résultat de cette détection sur un écran d'ordinateur. La “netlist” représentant l’interconnexion des broches du système à concevoir est envoyée au WaferIC, qui les interconnecte pour permettre le transfert des signaux. Ces connexions sont programmées par un port JTAG d'une manière similaire aux FPGA. Les signaux passent à travers des répéteurs pour en préserver l'intégrité sur les longues interconnexions.

Une approche d'intégration à l'échelle de la tranche (“WSI, *Wafer Scale integration*”) offre deux avantages : 1- elle permet d'avoir une grande densité de contacts, capables de supporter l'interconnexion des puces les plus miniaturisées ; 2 – elle permet une densité d'interconnexions suffisante pour mettre en place des systèmes de grande complexité. Cette approche permet donc de créer une plate-forme de prototypage de circuits digitaux unique en son genre.

Le principal avantage du WaferIC n'est pas d'atteindre une plus grande puissance de calcul, comme proposé dans certains travaux antérieurs sur le WSI [8][19]. Il s'agit en fait d'obtenir une surface suffisamment grande pour interconnecter de manière dense un ensemble de puces discrètes pour créer un système électronique de complexité supérieure en un temps de conception raccourci. Déjà en 1989, des chercheurs tels que Brewer [8], pionnier du domaine du WSI, ont démontré la faisabilité du concept d'intégration à l'échelle de la tranche et plusieurs règles de conception ont été définies dans un travail ultérieur [20]. Beaucoup de ces règles de conception font appel au concept de régularité de

la structure pour gérer le problème de la limitation en surface causée par les masques lithographiques, mais aussi pour gérer le problème des défectuosités inévitables en utilisant des stratégies de tolérance aux fautes.

La technologie CMOS 180 nm est considérée en date de dépôt de ce mémoire comme une technologie mature et les coûts de fabrication qu'elle implique rendent envisageable de concevoir une tranche de silicium entièrement dédiée à un seul système. Les usines qui offrent une technologie CMOS 180 nm produisent des tranches de silicium de grandeur 6 à 8 pouces.

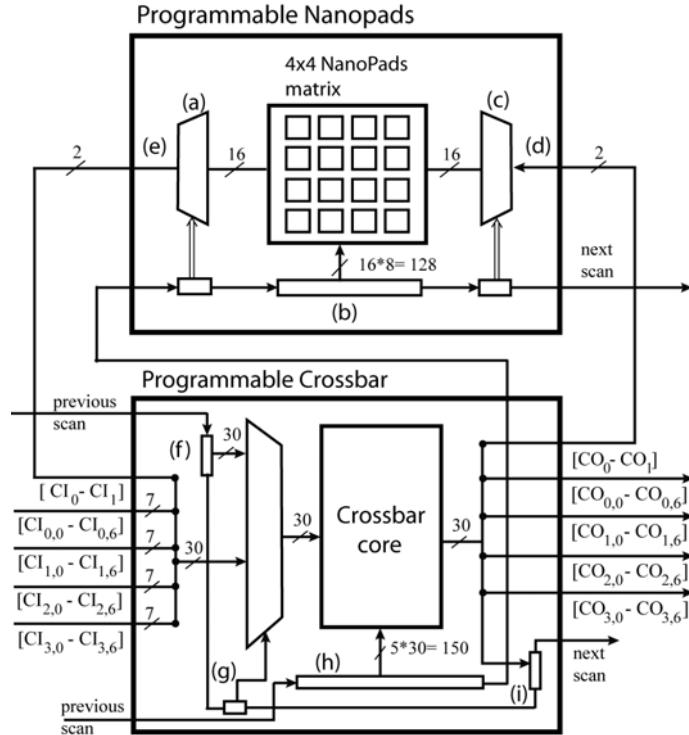

La structure de la surface du WaferIC comprend une matrice de plots très fins (de l'ordre de 100 µm) réalisée avec la dernière couche de métallisation du circuit intégré. Une couche spéciale est ajoutée par-dessus le circuit intégré. Cette couche est assimilable à un tissu qui protège la surface de l'usure. Ce mince tissu composé à la base d'un polymère flexible qui permet la conduction électrique selon son épaisseur, aussi appelé axe Z (d'où le nom "Z-axis film"). Les meilleurs tissu-axe-Z présentement disponibles sur le marché ont une épaisseur d'environ 300 microns Chaque plot sur le WaferIC est appelé "NanoPad". La matrice de plots est suffisamment dense pour permettre le contact entre les NanoPads et les broches d'une puce déposée sur la surface du tissu-axe-Z. Les NanoPads sont connectés au réseau interne reconfigurable du WaferIC appelé WaferNet.

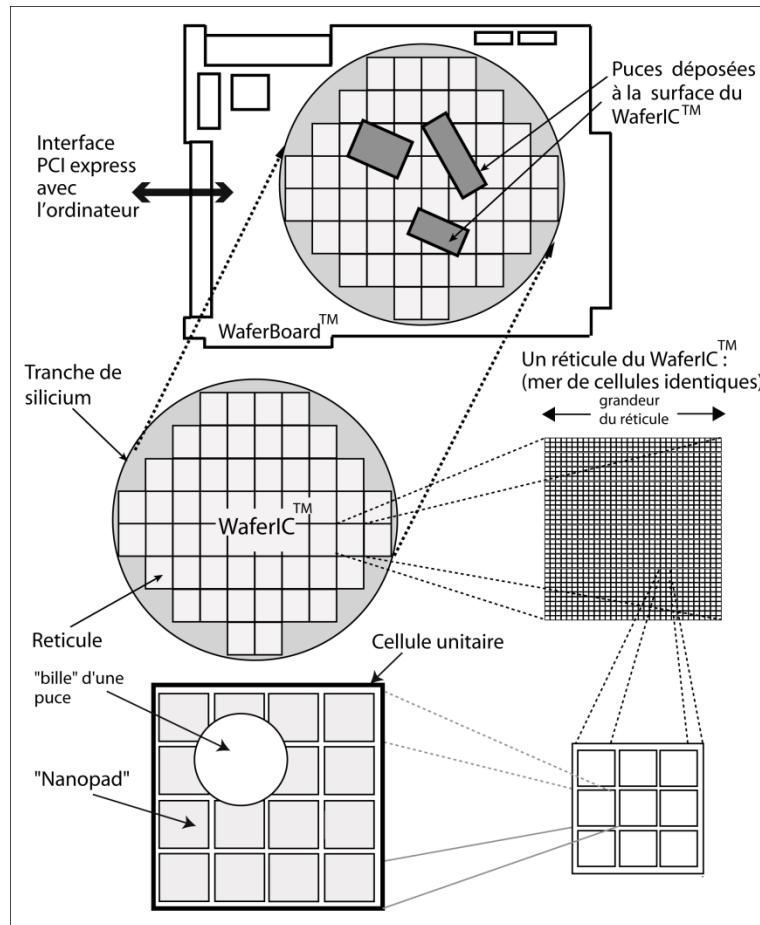

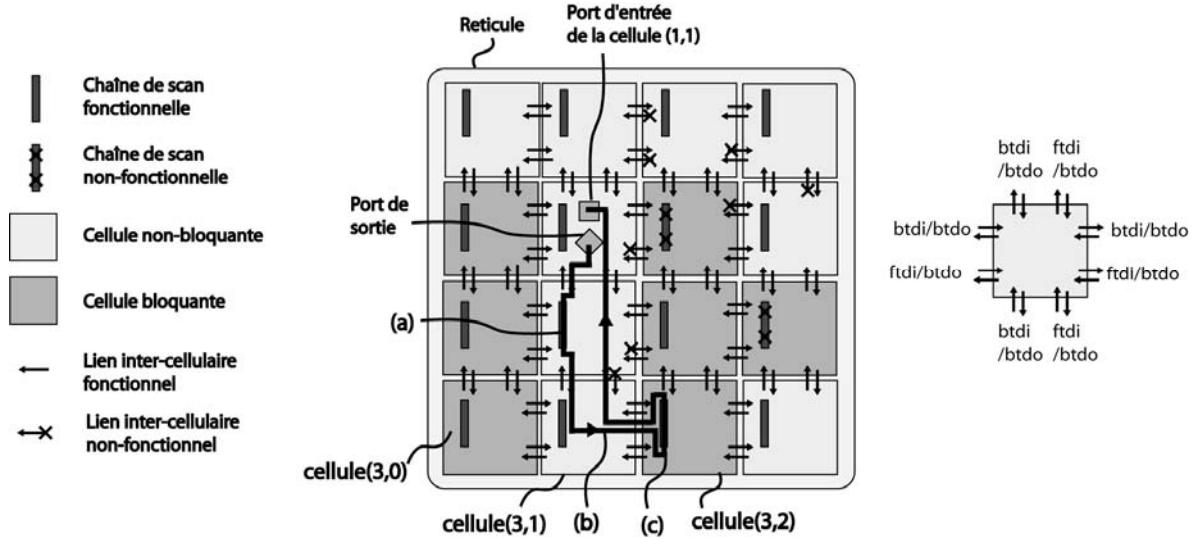

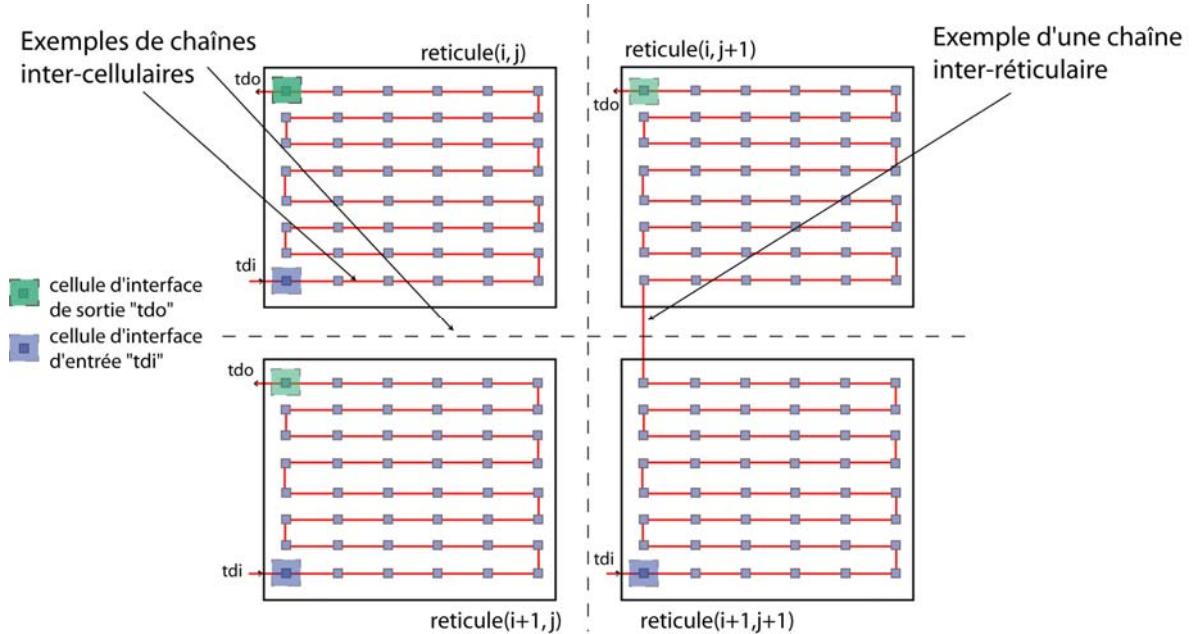

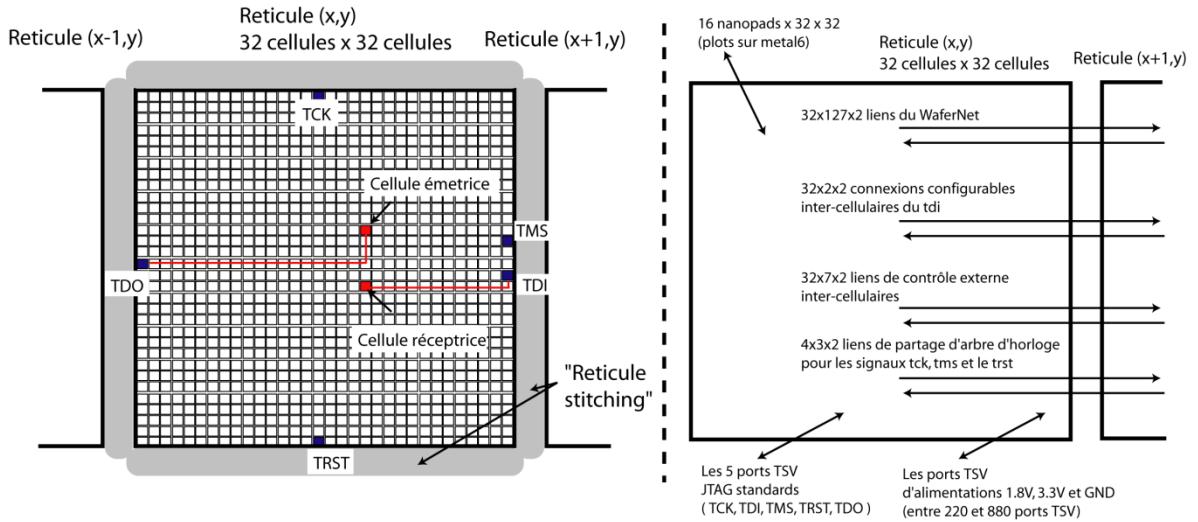

Le WaferIC est constitué d'une mer de cellules identiques et régulières. Concevoir l'architecture du WaferIC à base de cellules identiques permet d'en simplifier dramatiquement le design. La cellule de base du WaferIC est appelée dans ce document simplement la "cellule unitaire". Ces cellules sont collées les unes à côté des autres en une matrice à l'intérieur de la surface maximale limitée par le réticule. Contrairement aux procédés usuels de fabrication, les "dés" (les cellules) constituant la tranche ne sont pas coupés et empaquetés dans un contenant de plastique. Les "dés" sont plutôt interconnectés

pour créer diverses fonctionnalités essentielles au WaferBoard. D'où le nom “*wafer scale integrated circuit.*” Pour assurer une communication entre les réticules, une nouvelle étape du procédé de fabrication doit être mise au point pour tracer des lignes électriques entre les réticules (“reticle stitching”). Ainsi, le WaferIC est une mer de cellules connectées ensemble par un réseau reconfigurable d'interconnexions couplé à une matrice très dense de NanoPads.

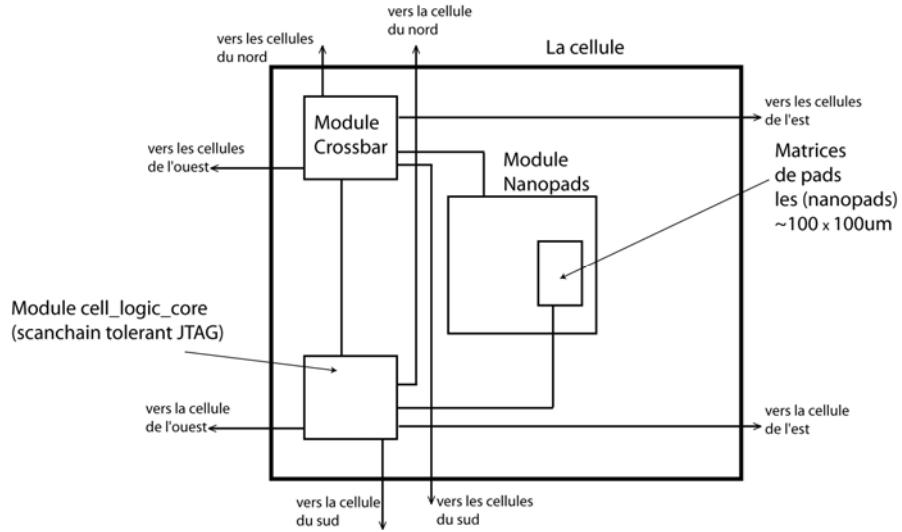

Le WaferIC est en fait une matrice de cellules identiques au niveau physique. Les cellules sont différenciées par le contenu de leur mémoire interne une fois le circuit configuré. La mémoire interne sert à configurer un crossbar permettant de définir la topologie du système. Cela permet de configurer le mode NanoPads (VDD, IN, OUT, GND) et d'autres fonctionnalités. Parmi ces fonctionnalités figurent des senseurs de courants, tensions, structure de test, etc. Cela suffit pour permettre à une matrice de cellules de créer un “PCB reconfigurable”. Cette méthode de conception est conforme aux méthodes proposées par les travaux antérieurs [8][20] de pionniers du domaine WSI, où la tolérance aux pannes et la régularité structurale doivent être maintenues.

La figure 1-4 montre la hiérarchie du système. Chaque cellule possède une dimension de 540x540 µm. Elle contient 16 NanoPads, ce qui donne une résolution suffisante pour isoler chaque broche de chaque puce d'un système électronique et évite les courts-circuits entre les broches des puces.

1-4 Structure physique hiérarchique du WaferBoard™ et du WaferIC™.

Voici les fonctionnalités internes supportées par chaque cellule du circuit :

- 1- Le système de configuration tolérant aux pannes des NanoPads et du crossbar commandé par le protocole JTAG.

- 2- Le système de détection de contact.

- 3- Le crossbar.

- 4- Support interne au diagnostic pour la tolérance aux pannes.

- 5- Les pads bidirectionnels configurables (les NanoPads).

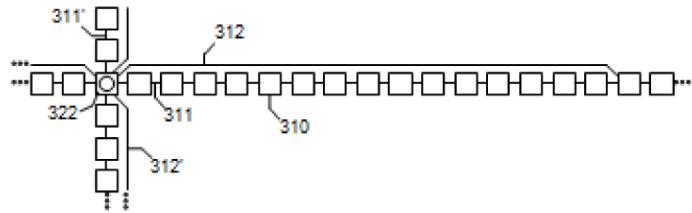

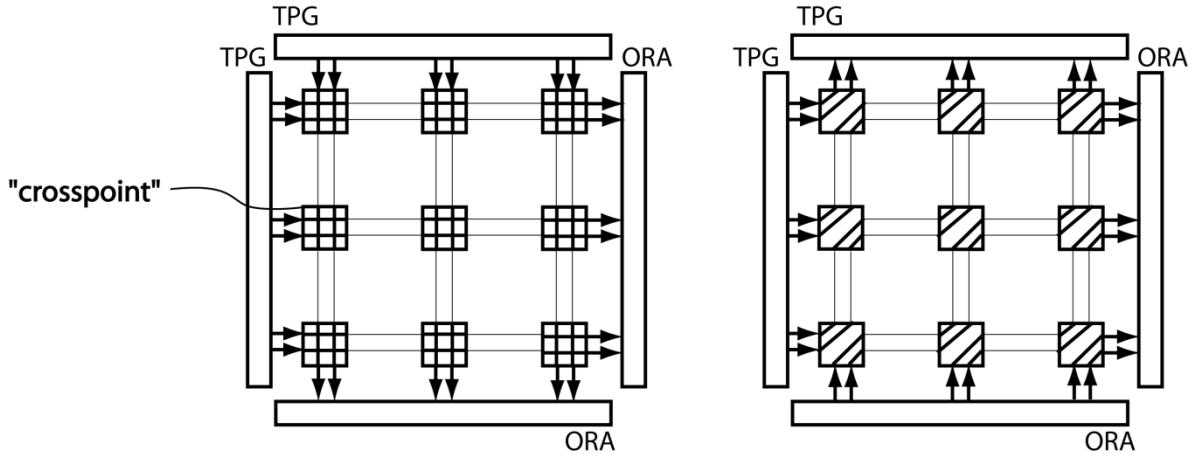

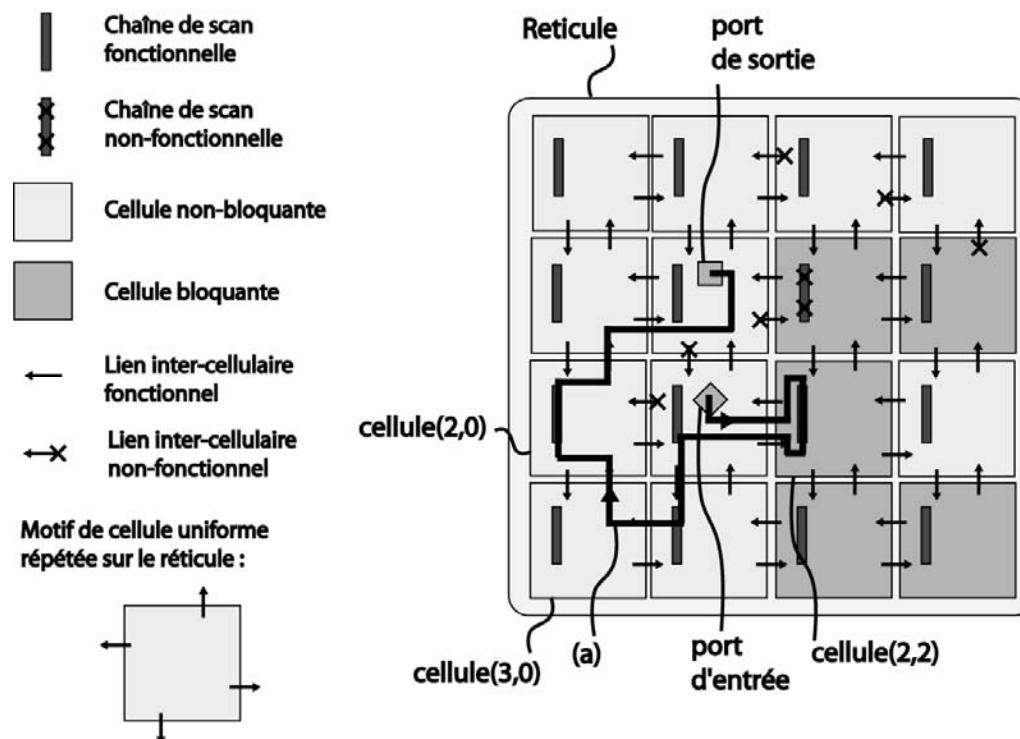

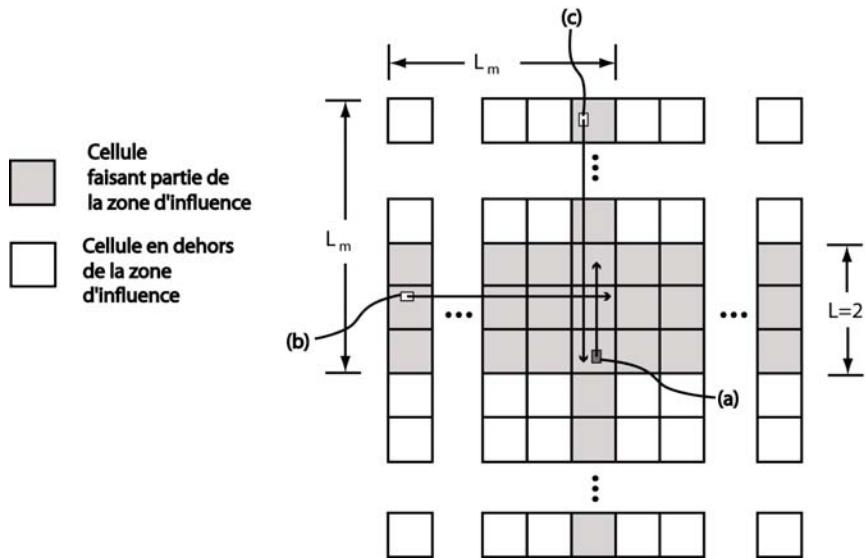

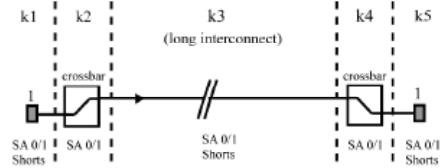

**Le réseau d’interconnexion sur Wafer : le WaferNet** (figure 1-5) : Il existe plusieurs types de réseaux configurables tels que le réseau “hypercube” [15] ou bien le réseau de type “Benes” [9]. Le WaferNet est différent( voir figure 1-5). Il ne s’agit pas d’un simple maillage, mais d’un maillage multidimensionnel régulier. Chaque cellule est connectée à ses 4 voisins, mais aussi à ses voisins distants de plusieurs cellules. Chaque cellule inclut un crossbar de grande dimension pour connecter les liens entrants provenant des 4 directions vers les liens sortants se dirigeant vers les 4 directions. Les cellules sont connectées aux 4 voisins immédiats dans les 4 directions, mais sont aussi en connexion directe avec les voisins distants de 2, 4, 8, 16..., etc. cellules. Dans la première implantation, des lignes relient directement des cellules éloignées jusqu’à 64 cellules. Chaque cellule unitaire contient des répéteurs pour propager efficacement les signaux numériques. Ces longues interconnexions nécessitent des répéteurs distribués dans chaque cellule pour minimiser le temps de propagation des signaux.

1-5 Structure du réseau WaferNet, extrait du brevet [27] .

L’architecture en maille multidimensionnelle permet non seulement d’améliorer la densité de routage, mais elle permet aussi d’obtenir une tolérance aux pannes dans le réseau. En effet, puisqu’il y a plus de liens que nécessaire, il est possible d’utiliser les ressources d’interconnexions non utilisées comme liens de remplacement. Par contre, pour être capable d’éviter une panne, il est essentiel de connaître son emplacement. Pour les trouver, il faut des techniques de diagnostic du réseau.

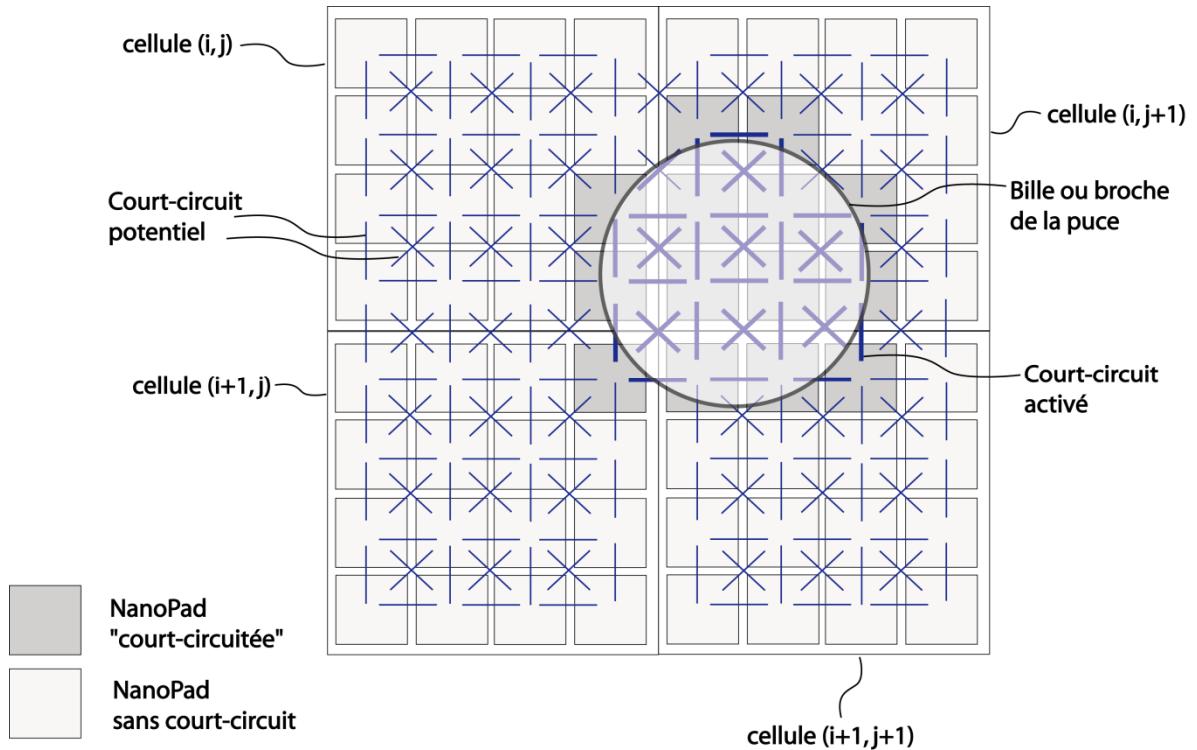

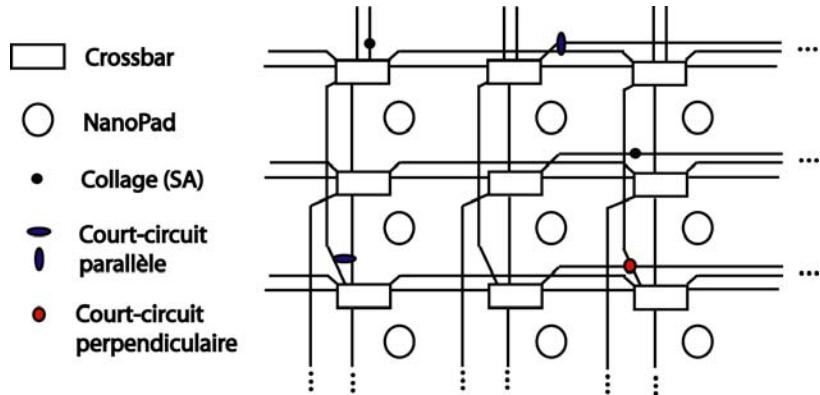

**La détection de contact :** Une fonction essentielle du WaferIC est de détecter un contact entre une broche de circuit intégré et un ou plusieurs NanoPads. Il existe plusieurs techniques qui ont été documentées dans le brevet de Norman [27] et les papiers antérieurs [12]. Ces techniques se basent sur deux classes de méthodes. La première utilise le changement de capacité observé sur le NanoPad lorsqu'il est en contact avec une broche du circuit intégré. Cette technique n'a pas encore été validée expérimentalement.

La deuxième classe de méthodes se base sur l'utilisation de détection de court-circuit entre les NanoPads. Puisque les broches des puces doivent être obligatoirement conductrices d'électricité et que les NanoPads sont plus petits que les broches, alors une broche qui repose sur le WaferIC créera obligatoirement un court-circuit. Il s'agit donc de créer un circuit analogique de détection de court-circuits entre les NanoPads pour détecter les points de contact "broches-NanoPads" du circuit. Une illustration de la mécanique de détection de contacts est montrée à la figure 1-6. Une bille de puce est montrée sur la figure 1-6. Les lignes représentent des liens potentiels reliant les NanoPads entre eux. Tous les liens potentiels reliant les NanoPads entre eux ne sont pas représentés.

Un court-circuit entre 2 NanoPads est montré avec une ligne plus foncée sur la figure. Les NanoPads flottants sont montrés en blanc. Après l'étape de détection de contact effectué par les circuits de détection de court-circuit, le système transmet le résultat du test vers l'extérieur, d'où une image des contacts peut être recréée pour donner à l'utilisateur la possibilité d'interconnecter les "broches" des circuits intégrés du système à prototyper.

1-6 Exemple de l'effet de la procédure de détection de courts-circuits.

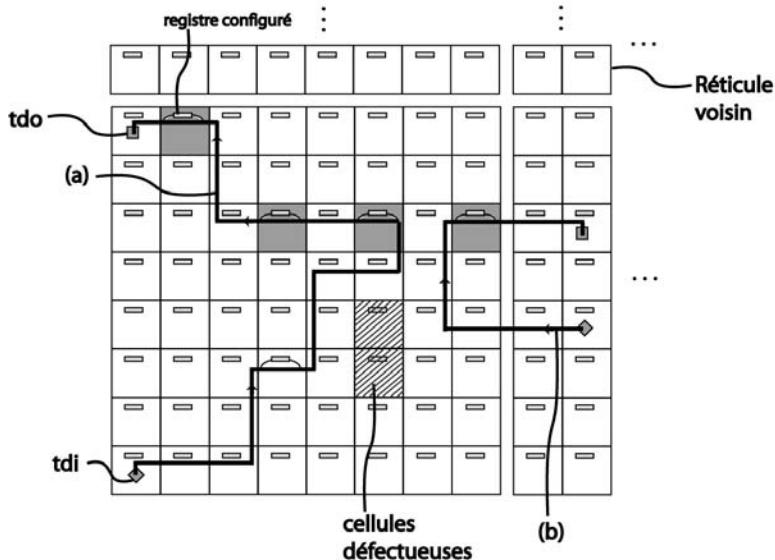

### Tolérance aux pannes par contrôle externe

Le concept illustré à la figure 1-7 est le suivant : tous les cellules peuvent être contrôlées par les cellules voisines. Cela permet d'obtenir une configuration redondante nécessaire au remplacement des cellules défectueuses. Cette propriété améliore la tolérance globale aux pannes, car les fonctions des cellules saines voisines peuvent être utilisées par une cellule défectueuse pour lui permettre de rester fonctionnelle. En reliant les cellules voisines, les fonctionnalités non utilisées des cellules voisines peuvent être considérées comme des modules de rechange en cas de panne.

Une autre méthode de tolérance aux pannes bien connue est la tolérance basée sur l'utilisation des cellules voisines comme le montre la figure ci-dessous tirée du brevet de R. Norman [27] :

**FIG. 10B**

1-7 Utilisation des ressources des cellules voisines (indiquées en pointillé)[27].

## 1.5 Les bases technologiques des contributions de ce mémoire

Cette section présente les bases technologiques des principales contributions originales de ce mémoire qui se rapporte audiagnostic de pannes dans un réseau de maillage multidimensionnel (le WaferNet) et une méthodologie de tolérance aux fautes.

### 1.5.1 Les systèmes de chaîne de balayage “niveau système”

Le design pour la testabilité (“*DFT, design for testability*”) est la discipline de la microélectronique s'intéressant aux techniques de test de circuits numériques modernes. Une bonne stratégie de test permet de tester le circuit à un coût et avec une surface de silicium tous deux minimum. De plus, il faut que la couverture du test soit maximale et qu'elle soit effectuée le plus rapidement possible. Une des principales techniques pour tester les circuits numériques est l'insertion de registres à décalage (appelés dans ce document chaîne de balayage) dans le circuit pour obtenir une contrôlabilité ou une observabilité des modules numériques internes. Tel qu'expliqué précédemment, le

diagnostic des défectuosités est à la base des techniques de tolérance aux pannes privilégiées dans la technologie “WaferIC”. Or, diagnostiquer un circuit, c'est l'art de localiser les pannes détectées par le test du système numérique. Les techniques de test sont donc à la base du diagnostic. Puisque les techniques de diagnostic pour la tolérance aux pannes se basent sur une architecture spéciale de chaîne de balayage il est donc pertinent de faire une revue des techniques d'insertion de chaîne de balayage.

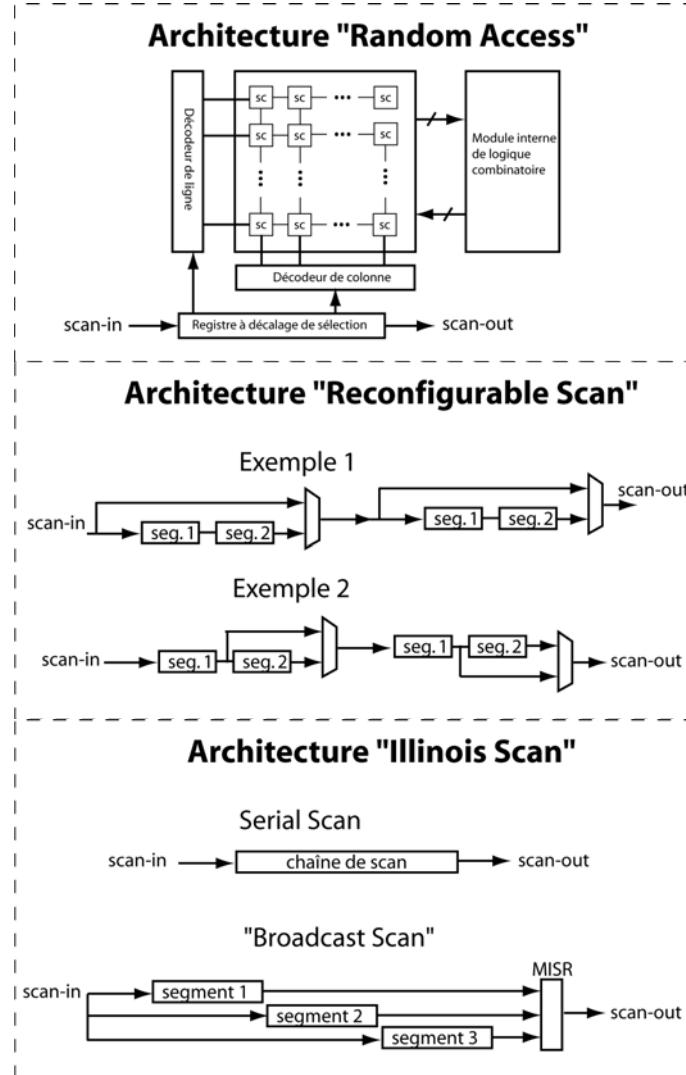

Il existe un grand nombre de types de chaîne de balayage. La chaîne de balayage la plus élémentaire est une simple suite de registres reliés entre eux pour créer un registre à décalage. La figure 1-8 montre schématiquement les principaux types de système de chaîne de balayage. Par exemple, avec une chaîne de balayage de type “RASC : *random access scan chain*” il est possible de créer une matrice de registres accessibles à l'aide de décodeurs de colonnes et de lignes [3]. L'avantage de ce type d'architecture est d'accélérer le temps de test et la puissance consommée durant le test. Par contre, il nécessite beaucoup de ressources matérielles et de routage pour être réalisé dans un circuit numérique. Il est aussi possible de créer un système de chaîne de balayage à l'aide de chaînes de balayage reconfigurables [25]. L'idée principale est d'utiliser des multiplexeurs configurables pour contourner les registres les moins souvent utilisés durant une séquence de test pour minimiser la longueur de la chaîne de balayage. Cette technique permet d'accélérer le temps de test avec l'utilisation d'un minimum de ressources matérielles supplémentaires.

Une autre méthode est la technique d'insertion de chaînes de balayage de type “Illinois”, aussi connue sous le nom de *broadcast scan chain* [16]. Ce type de chaîne de balayage permet d'appliquer parallèlement la même séquence de vecteurs de test sur une structure régulière indépendante. La chaîne de type “Illinois” peut passer d'une chaîne de balayage élémentaire en une chaîne de balayage de type “*broadcast*”. Ce changement de mode est utilisé pour gérer les situations où il est possible d'appliquer des cas de test unique sur une série de modules parallèles (mode “*broadcast*”) et le mode élémentaire est utilisé pour les

situations où un vecteur de test unique doit être appliqué à chaque module sous test. Une MISR (*Multiple Input Signature Register*) est ajoutée à la sortie des chaînes de balayage pour comprimer le volume de données en sortie du circuit sous test.

1-8 Principales classes d'architecture de scan.

### 1.5.2 Architecture de test

Le présent mémoire porte principalement sur le système de programmation tolérant aux défectuosités du WaferIC et sur le diagnostic du WaferIC. Il est donc pertinent de procéder

à un survol rapide des principales architectures de test de circuits intégrés et de PCB. Le système de programmation et de diagnostic du WaferIC est basé sur le protocole de test IEEE 1149.1.

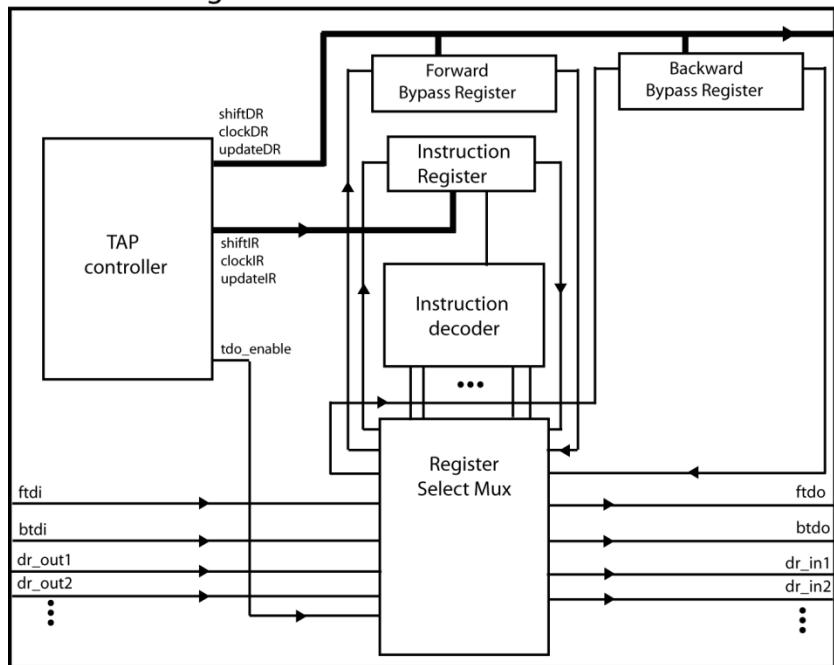

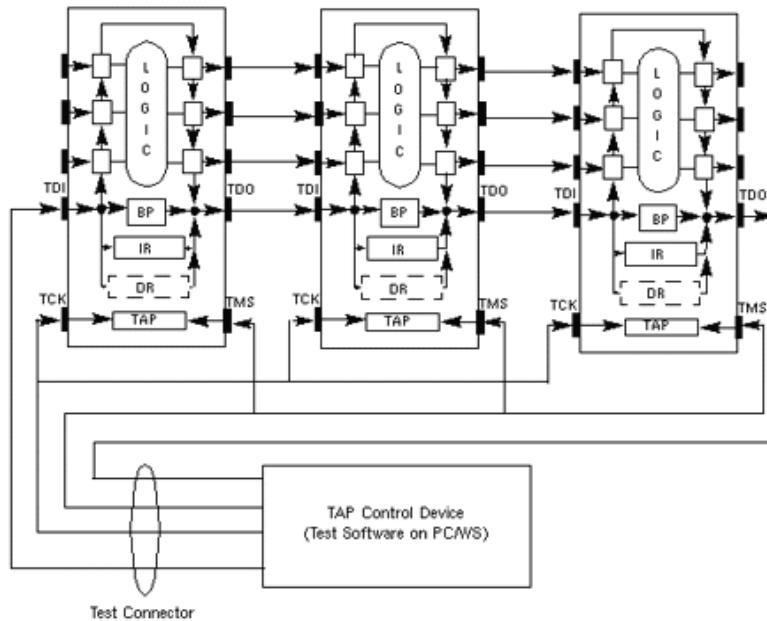

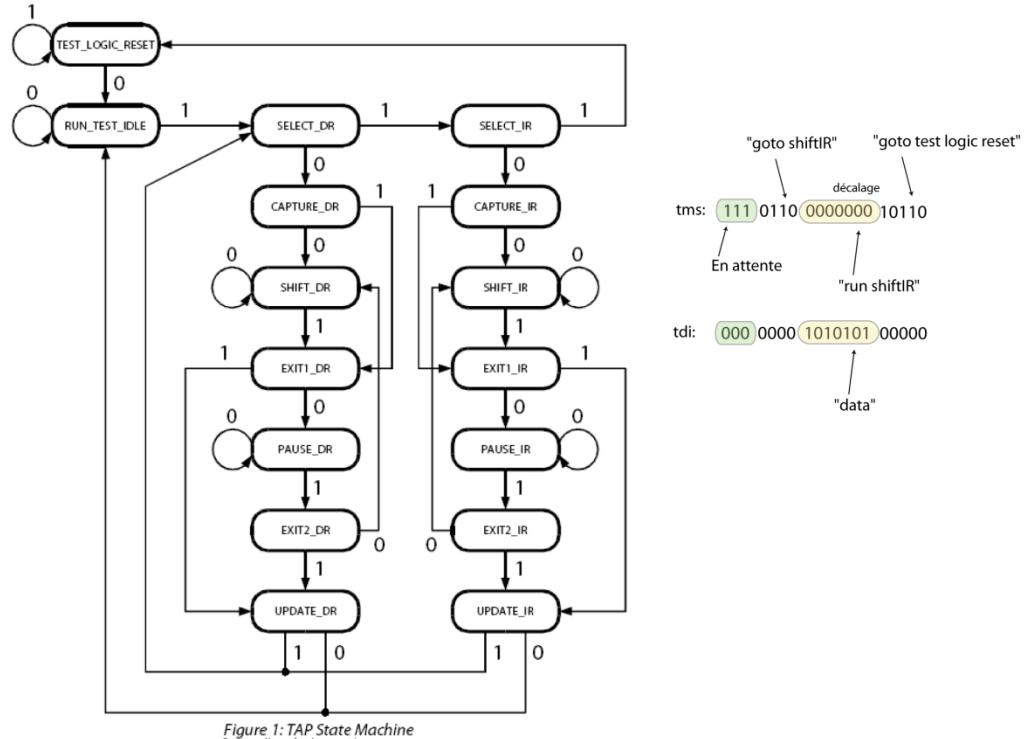

La norme 1149.1 définit un protocole d'accès pour le test [28]. Elle définit un ensemble d'architectures “*boundary scan*” pour le test de circuits numériques. La figure 1- montre un exemple de *boundary scan* sur un DUT (“*device under test*”) où chaque entrée/sortie de la puce est reliée à une cellule “*boundary scan*” qui est chaînée à ses cellules voisines pour former une chaîne globale accessible par un seul port JTAG plus étroit. Chaque cellule est en fait un registre de capture et de contrôle des broches de la puce. À travers cette chaîne, les entrées/sorties deviennent contrôlables et observables. Ce qui permet de tester à la fois la logique interne du circuit et les interconnexions sur le PCB.

En comparaison du test d'un système, le test de circuit intégré pris d'une manière indépendante est relativement facile, car toutes les entrées/sorties du circuit sont accessibles. Nous insistons ici sur le mot relatif, car en fait, ce problème relativement facile peut s'avérer très difficile dans l'absolu! Par contre, une fois que la puce est intégrée et soudée sur un PCB, le problème du test de la puce devient plus complexe. Les entrées/sorties des puces du système sur PCB ne sont généralement pas directement accessibles. Une technique populaire consiste à utiliser un protocole de communication série pour obtenir un accès à toutes les broches de tous les circuits intégrés d'un système au travers d'un port d'accès de largeur minimale. Le protocole IEEE 1149.1 propose une solution élégante à ce problème. Ce protocole de test porte plusieurs noms. Il peut être appelé selon le contexte “*boundary scan*” ou bien simplement “*JTAG*” (*Joint Test Access Group*). Initialement, cette norme a été conçue pour le test de cartes électroniques (PCB). Mais le succès et l'élégance du protocole de communication en ont permis un élargissement rapide à une gamme d'applications complexes reliées au test de circuits intégrés de grande dimension, à la programmation de circuits intégrés et au diagnostic des systèmes

électroniques, etc. Une description détaillée du protocole de communication et de test JTAG serait trop volumineuse et est facilement disponible au lecteur intéressé à approfondir le sujet [28][31]. De plus, une connaissance de base du protocole JTAG est requise pour comprendre les concepts et principes énoncés dans les sections et chapitres ultérieurs de ce document. Une petite annexe résumant le protocole JTAG a été ajouté en annexe G. Plusieurs architectures de test sont possibles. Voici une énumération des principales architectures tirée du livre de Wang [31] :

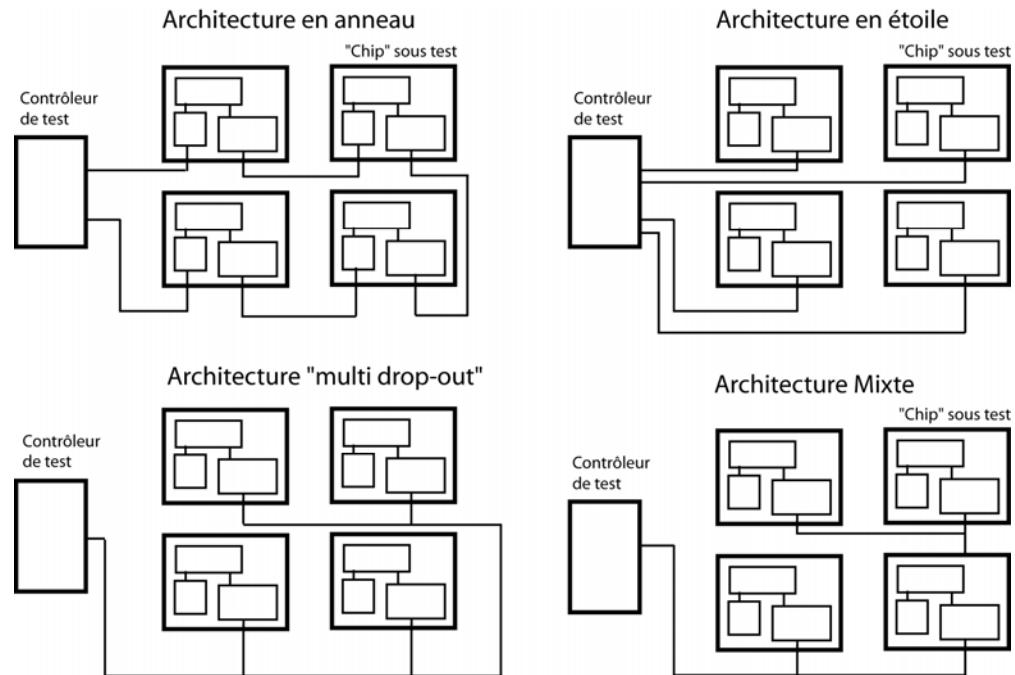

*Architecture JTAG de base* : Dans chaque système JTAG, il y a le contrôleur de test (TC, Test controller) et l'unité sous test (UUT, unit under test). Une unité sous test peut être n'importe quelle puce, PCB, SoC ou bien un système WSI sous test. La même architecture de base peut être utilisée pour une unité sous programmation. Par conséquent, l'expression “unité sous test” réfère à tout système configurable ou bien programmable avec un port JTAG. Cette simplification permet d'alléger le texte. Les UUT sont stimulés à l'aide de vecteurs de test et la réponse est évaluée par le contrôleur de test pour décider si le système est fonctionnel ou pas. Le contrôleur de test peut être un logiciel ou bien un système embarqué capable de contrôler l'émission et la réception des flux de bits JTAG et aussi d'interpréter les résultats. L'interprétation des résultats peut être un simple constat d'échec ou de réussite à un test électronique ou bien le TC peut être capable à l'aide d'un logiciel approprié d'émettre des diagnostics.

*Architecture JTAG en anneau* : La figure 1-9 représente une autre architecture JTAG bien connue sous le nom de “daisy chain” où chaque chaîne de balayage de chaque UUT est reliée pour former un anneau. Un seul signal TMS est envoyé à chaque cellule pour contrôler le test. Le premier et le dernier UUT sont les seules cellules en contact direct avec le contrôleur de test. Cette architecture offre un accès efficace tout en utilisant un minimum de broches dédiées uniquement aux tests. À noter que les différentes puces peuvent recevoir des instructions de test différentes même s'ils ont le signal de contrôle TMS. Puisque la position de chaque puce dans la chaîne est connue, il est possible de donner une instruction

JTAG et des vecteurs de tests uniques à chaque puce faisant partie de la chaîne. Par contre, la structure en anneau possède une vulnérabilité majeure : si seulement un seul UUT n'est pas fonctionnel, l'anneau en entier devient impossible à tester, impossible à configurer.

*Architecture JTAG en étoile* : La figure 1-9 représente une autre architecture bien connue où chaque TC est directement en contact avec chaque UUT. Par conséquent, s'il y a " $n$ " UUT dans le système sous-test, il faut entre  $4n$  et  $5n$  ports dédiés au test dans le système. Si le signal JTAG de reset trst\*(optionnel) est utilisé dans chaque cellule le nombre de ports dédiés au test sera de  $5n$ . Cette architecture apporte un accroissement de la rapidité du test, car le test des cellules se fait en parallèle au prix d'un plus grand nombre de ports de test. De plus, cette architecture résout la vulnérabilité apportée par les chaînes en anneau.

*Architecture JTAG de type "Multi drop-out module"* : Une solution hybride entre la solution en anneau (sériel) et la solution en étoile (parallèle) est la solution décrite à la figure 1-9. Dans une architecture "multi drop-out", chaque cellule est reliée par un bus de communication bidirectionnel et relié en une seule colonne de cellules de mémoire, comme dans une puce de mémoire RAM. Une adresse est spécifiée à un décodeur d'adresse donne accès aux données qui peuvent transiter directement entre le TC et l'UUT choisis. De même, les résultats de test provenant des UUT peuvent être acheminés vers le TC à partir du même bus en un schéma de communication "one-to-one". Cette solution est très désirable, car elle offre un accès étroit aux UUTs et elle permet d'accélérer le test. De plus, cette solution apporte un certain niveau de tolérance aux pannes. Si un seul UUT fait défaut, le système entier peut rester testable et diagnosticable, donc réparable. Par contre, si une panne arrive sur le bus de communication, les composants connectés sur ce bus deviennent non-testables, donc dysfonctionnels.

*Architecture JTAG mixte* : Une architecture de test JTAG mixte [7] utilise et combine de manière hiérarchique les 3 méthodes précédentes (anneau, étoile, multi-drop out). Plusieurs combinaisons d'architecture deviennent possibles. Par exemple, un PCB complexe pourrait

utiliser un système multi-drop out pour accéder à plusieurs puces du système, mais un seul SoC du même PCB pourrait ensuite contenir une architecture interne de test de type "anneaux" pour accéder aux fonctionnalités internes du SoC. La figure 1- montre un exemple d'architecture mixte hiérarchique. De plus, le brevet [21] vient décrire en détail et protéger une architecture mixte particulièrement adaptée aux tests de systèmes complexes qui doivent être testés rapidement et efficacement.

1-9 Exemples d'architectures JTAG.

*Les architectures JTAG tolérantes aux fautes :* Un dernier type de chaîne de balayage étudié dans ce mémoire est la chaîne de balayage tolérante aux fautes conçue par Lu et Savaria en 2003 [24]. Cette technique utilise l'approche connue sous le nom de "TMR, Triple Modular Redundancy" pour ajouter une tolérance aux pannes. Cette approche consiste à utiliser en parallèle 3 systèmes qui sont évalués par un quatrième module qui a pour but de sélectionner en sortie des données fiables sans fautes. Ce quatrième module fait "voter" les 3 systèmes et seulement la réponse de la majorité (2 sur 3) est acceptée comme

réponse en sortie. Si une panne ponctuelle arrive dans le système, la probabilité qu'elle arrive en même temps sur 2 des 3 systèmes est très basse, ce qui améliore la fiabilité du module global. De même, si une panne permanente existe dans l'un des 3 modules, les 2 autres pourront prendre le relais et permettre au système de fonctionner en présence de cette faute. La technique proposée dans [24] consiste à renforcer la chaîne de balayage en appliquant un chemin de balayage qui est triplé.

### **1.5.3 Le diagnostic de pannes dans un système d'interconnexions**

En partant d'un circuit qui a échoué à un test fonctionnel, le diagnostic logique (simplement appelé diagnostic pour alléger le texte) consiste à cerner dans une région de plus en plus petite du circuit les régions possibles où peut se trouver une défectuosité, ce qui permet d'en estimer les causes possibles. En cernant autant que possible les causes de défectuosités, on peut souvent trouver la cause première d'un syndrome de panne, soit au niveau du design ou bien au niveau de la production en série. Le diagnostic efficace de circuits intégrés peut donc contribuer à raccourcir leur temps de développement (déverminage matériel) et à améliorer les rendements de fabrication. Cette sous-section présente un résumé des principales techniques de diagnostic qui sont reliées à celles exploitées dans ce document. Toutes les méthodes de diagnostic originales présentées dans les chapitres 2 et 3 représentent soit des améliorations ou des adaptations à la technologie WaferIC inspirées de techniques de diagnostic qui ont été appliquées à des PCB ou à des FPGA.

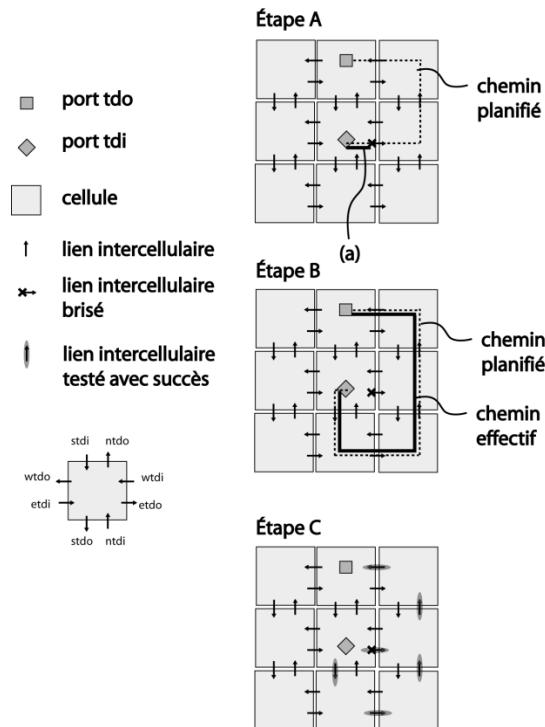

*Méthodes de diagnostic de réseau d'interconnexion exploitées dans les PCBs* : le diagnostic des interconnexions dans un PCB consiste non seulement à tester, mais à localiser exactement quelles traces sont défectueuses et à localiser les défauts de soudure entre les puces et le PCB. Ce genre de test peut être effectué à partir d'une chaîne de balayage pouvant soit observer ou contrôler les signaux de toutes les broches d'un PCB. Cette méthode a été standardisée à travers le BSDL (Boundary scan description langage) et le JTAG. Les architectures JTAG pour le test et le diagnostic ont déjà été couvertes dans ce

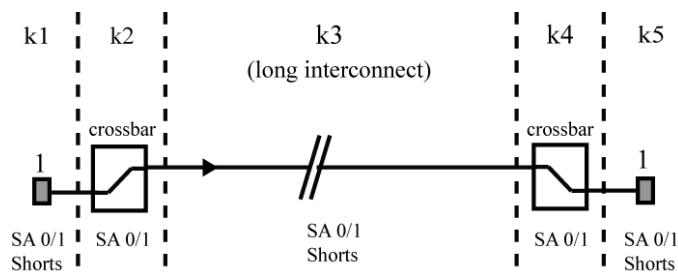

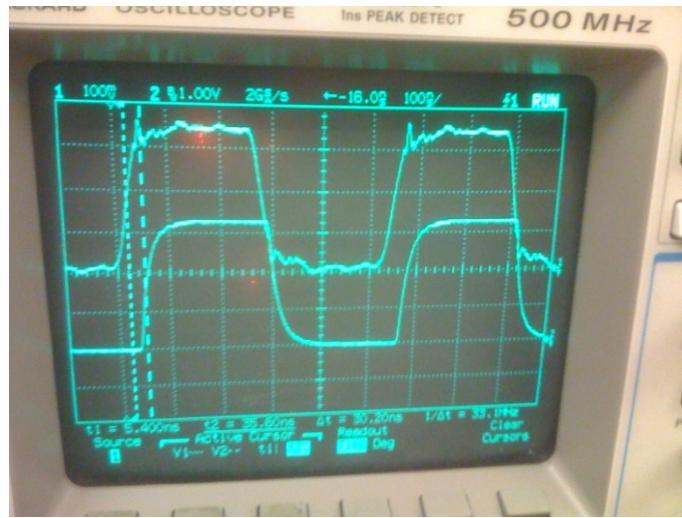

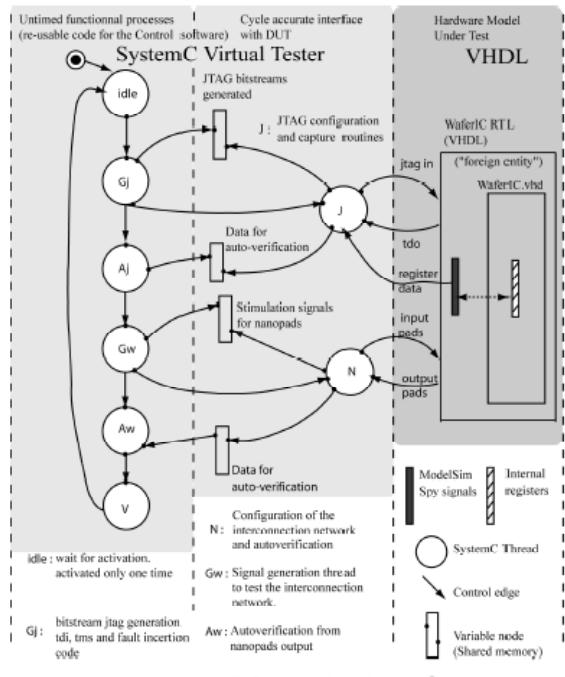

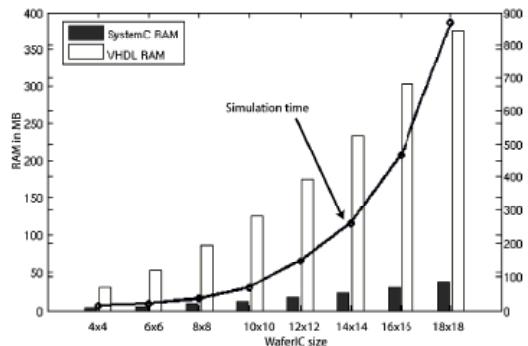

chapitre, mais pas la méthode pour diagnostiquer la défectuosité. Si l'ordre des cellules de balayage est connu par un logiciel de test et si ce logiciel peut générer des modèles de vecteurs de test, il devient possible de localiser et de détecter les principales pannes, comme les courts-circuits, les collages (“SA, stuck-at”) et les circuits ouverts. Le modèle de test le plus connu et le plus facile à générer par du matériel embarqué sur la carte sous test est l’envoi d’un “*walking-one*” [14]. Pour ce faire, il est possible d’utiliser un simple compteur connecté en sortie à une porte NOR (OR). La sortie résultante génère automatiquement une série de bits 10000... (01111...). Cette série de bits est ensuite décalée dans la chaîne JTAG pour faire ressortir les pannes d’interconnexion du PCB. En connaissant l’emplacement exact de chaque pin dans les chaînes de balayage, il devient possible de faire un diagnostic très précis en un temps d’ordre  $O(n^2)$ .