**Titre:** Intégration dans un flot de conception système d'un outil de traduction assistée de code C pour la création de coprocesseurs matériels

Title:

**Auteur:** Arnaud Desaulty

Author:

**Date:** 2016

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Desaulty, A. (2016). Intégration dans un flot de conception système d'un outil de traduction assistée de code C pour la création de coprocesseurs matériels

Citation: [Master's thesis, École Polytechnique de Montréal]. PolyPublie.

<https://publications.polymtl.ca/2285/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/2285/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois

Advisors:

**Programme:** Génie informatique

Program:

UNIVERSITÉ DE MONTRÉAL

INTÉGRATION DANS UN FLOT DE CONCEPTION SYSTÈME D'UN OUTIL DE

TRADUCTION ASSISTÉE DE CODE C POUR LA CRÉATION DE COPROCESSEURS

MATÉRIELS

ARNAUD DESAULTY

DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

JUILLET 2016

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

INTÉGRATION DANS UN FLOT DE CONCEPTION SYSTÈME D'UN OUTIL DE

TRADUCTION ASSISTÉE DE CODE C POUR LA CRÉATION DE COPROCESSEURS

MATÉRIELS

présenté par : DESAULTY Arnaud

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. BELTRAME Giovanni, Ph. D., président

M. BOIS Guy, Ph. D., membre et directeur de recherche

M. LANGLOIS J. M. Pierre, Ph. D., membre

## REMERCIEMENTS

Je tiens tout d'abord à remercier ma famille et mes amis, qui malgré l'éloignement géographique, ont su me donner le courage et la motivation nécessaires.

Je remercie aussi tout particulièrement mon directeur de recherche M. Bois et son équipe dans les locaux de SpaceCodesign, pour la patience dont ils ont fait preuve et les conseils qu'ils m'ont prodigués.

Je remercie également mes collègues de laboratoire, Étienne et Mathieu, qui étaient toujours là pour me soutenir et pour d'incroyables discussions autour d'un café.

Enfin, je tiens à remercier l'intégralité des personnes que j'ai rencontrées ici au Québec, expatriés ou natifs. Votre gentillesse et votre style de vie resteront toujours ancrés dans ma mémoire. Merci tout particulièrement à mes colocataires, Gavin et Sebastian pour les bons moments passés ensemble.

## RÉSUMÉ

Depuis les débuts de la conception de systèmes électroniques, un des buts de la recherche est de fournir des outils et méthodes de travail de plus en plus puissants et rapides. Ceci est illustré très explicitement dans le fossé qui sépare la croissance du nombre de transistors par puce de la croissance du nombre de transistors intégrés par ingénieur par mois. Au cours des années se sont alors développées des méthodes permettant à un concepteur d'abstraire de plus en plus son travail afin de faciliter l'intégration et la distribution de composantes matérielles. À ces abstractions de description viennent s'ajouter des outils automatisant certaines parties du travail d'un concepteur. C'est par exemple le cas de la synthèse haut-niveau, qui permet de synthétiser des algorithmes de manière guidée. Enfin, de nombreux flots de travail ont aussi vu le jour afin de fournir une méthodologie dans la conception de systèmes électroniques. Le flot que nous retiendrons est le flot niveau système électronique (ESL) qui décrit une méthode de développement incrémentale partant d'une description la plus abstraite possible. Les abstractions sont itérativement relâchées pour finalement arriver à une description matérielle.

Toutefois, il n'existe pas d'outil complet intégrant toutes les étapes du flot ESL. Nous proposons donc un outil de traduction assistée de code C afin de compléter un flot de conception ESL dans le cadre de la création de coprocesseurs matériels. L'outil proposé, C2Space, permet la transition d'un code C séquentiel vers un code organisé en modules SpaceStudio de manière rapide et configurable. Cet outil de traduction, basé sur le transpilateur Clang, procède à l'analyse statique du code pour effectuer les choix de traduction appropriés. C2Space permet l'intégration en amont du flot d'une solution d'analyse dynamique de code C, appelée Pareon Profile. Pareon permet une première analyse du code séquentiel afin de repérer rapidement les portions du code susceptibles de profiter d'un passage sur coprocesseur (de par leur potentiel de parallélisme et leur poids dans l'exécution séquentielle). Une fois la traduction effectuée, le reste du flot est supporté par l'environnement de codéveloppement SpaceStudio, qui permet alors de procéder à l'exploration architecturale du code traduit. Il est alors possible de tester différents schémas d'allocation des modules aux ressources matérielles (processeurs, coprocesseurs). Les modules alloués en matériel sont alors synthétisés à l'aide d'un logiciel de synthèse haut-niveau. Le système complet peut ensuite être exporté vers une des plateformes matérielles supportées (par exemple, pour FPGA Xilinx).

Nous avons confronté ce flot à un algorithme de détection de contours (filtre de Canny) afin d'en tester l'efficacité. Les résultats montrent que l'approche proposée permet un raffinement rapide de l'algorithme, de sa définition logique jusqu'à son implémentation. Nous n'avons pu accélérer, comme envisagé initialement, la vitesse d'exécution de l'algorithme, mais nous avançons plusieurs pistes pour expliquer ces résultats. Nous proposons une série de recommandations visant à améliorer à la fois C2Space et le flot proposé. Nous décrivons notamment l'utilisation d'une nouvelle métrique très tôt dans le flot de conception mettant en relation (1) le potentiel de parallélisme d'un segment de code, (2) la portion du temps d'exécution global de ce segment, (3) le coût de communications processeur/coprocesseur pour ce segment et (4) le temps d'exécution logiciel de cette même portion de code.

## ABSTRACT

Since the beginning of Electronic System Design, one of the main goals pursued in research has been to provide smarter and faster tools and workflows. This is clearly shown in the gap that separates the number of transistor per chip and the number of transistor that can be integrated by an engineer in a month. Over the years, many methods allowing a designer to abstract more and more his design came to fruition. In addition to those methods, automatization of certain tedious and repetitive tasks in the design process appeared. For instance, the tools of High Level Synthesis allow a high level specification to be automatically translated into a working Register Transfer level design. Finally, numerous workflows arose to provide more definite framework in Electronic System Design. The workflow that we will tackle is the Electronic System Level Flow (ESL), which describe an incremental method that starts from the most abstract specification possible. Abstraction is then released in small increments until a fully hardware specification is obtained.

However, there is no comprehensive tool incorporating all stages of the ESL flow. We therefore propose an assisted translation tool for C code in order to complete an ESL design flow as part of creating hardware coprocessors. The proposed tool, C2Space, allows the transition of a sequential C code to a code organized in SpaceStudio modules in a fast and configurable way. This translation tool, based on the transpiler Clang, performs static analysis of the code to perform the appropriate translation choices. C2Space allows the integration, upstream of the flow, of a dynamic code analysis solution for C, called Pareon Profile. Pareon allows a first analysis of the sequential code to quickly identify sections of code that could benefit from a passage on coprocessor (by their potential parallelism and their weight in the sequential execution). Once the translation is done, the rest of the workflow is supported by the co-design environment SpaceStudio, which allows for architectural exploration of the translated code. It is then possible to test different mappings of the modules to the hardware resources (processors, coprocessors). Modules that are allocated material are then synthesized using a high-level synthesis software. The complete system can then be exported to one of the supported hardware platforms (e.g., for Xilinx FPGAs).

We compared this flow to an edge detection algorithm (Canny filter) to test its effectiveness. The results show that the proposed approach enables rapid refinement of the algorithm, from the logic definition to its implementation. We have not been able to accelerate, as originally envisioned, the execution speed of the algorithm but we are offering several possible explanations for these results.

We provide a series of recommendations to improve both C2Space and the proposed workflow. We describe in particular the use of a new metric early in the design flow linking (1) the potential parallelism of a code segment, (2) the portion of the total execution time of this segment, (3) the cost of communications between processor and coprocessors for this segment and (4) the software runtime of that same piece of code).

## TABLE DES MATIÈRES

|                                                                           |      |

|---------------------------------------------------------------------------|------|

| REMERCIEMENTS .....                                                       | III  |

| RÉSUMÉ.....                                                               | IV   |

| ABSTRACT .....                                                            | VI   |

| LISTE DES TABLEAUX.....                                                   | XI   |

| LISTE DES FIGURES .....                                                   | XII  |

| LISTE DES EXTRAITS DE CODE.....                                           | XIV  |

| LISTE DES SIGLES ET ABRÉVIATIONS .....                                    | XV   |

| LISTE DES ANNEXES .....                                                   | XVII |

| <br>CHAPITRE 1 INTRODUCTION .....                                         | 1    |

| 1.1    Les langages de description de matériel (HDL) .....                | 3    |

| 1.2    La synthèse haut-niveau (HLS).....                                 | 3    |

| 1.3    Le niveau « système électronique » (ESL) .....                     | 5    |

| 1.4    Problématique.....                                                 | 14   |

| 1.5    Objectifs .....                                                    | 16   |

| 1.6    Résumé des contributions.....                                      | 17   |

| 1.7    Organisation du mémoire .....                                      | 17   |

| <br>CHAPITRE 2 PRÉSENTATION DU FLOT .....                                 | 18   |

| 2.1    Présentation générale.....                                         | 18   |

| <br>CHAPITRE 3 C2SPACE : UN OUTIL DE TRADUCTION ASSISTÉE .....            | 25   |

| 3.1    Les transpilateurs.....                                            | 25   |

| 3.1.1    L'infrastructure de compilation ROSE .....                       | 27   |

| 3.1.2    Clang : Une partie frontale C/C++ pour le compilateur LLVM ..... | 28   |

| 3.1.3    Choix du transpilateur .....                                     | 30   |

|                                                                                  |           |

|----------------------------------------------------------------------------------|-----------|

| 3.1.4 Fonctionnement de Clang.....                                               | 31        |

| 3.2 Présentation de C2Space .....                                                | 39        |

| 3.2.1 Capacités de l'outil.....                                                  | 41        |

| 3.2.2 Problématiques de la traduction .....                                      | 43        |

| 3.2.3 Contraintes sur la source .....                                            | 56        |

| 3.2.4 L'architecture de C2Space .....                                            | 57        |

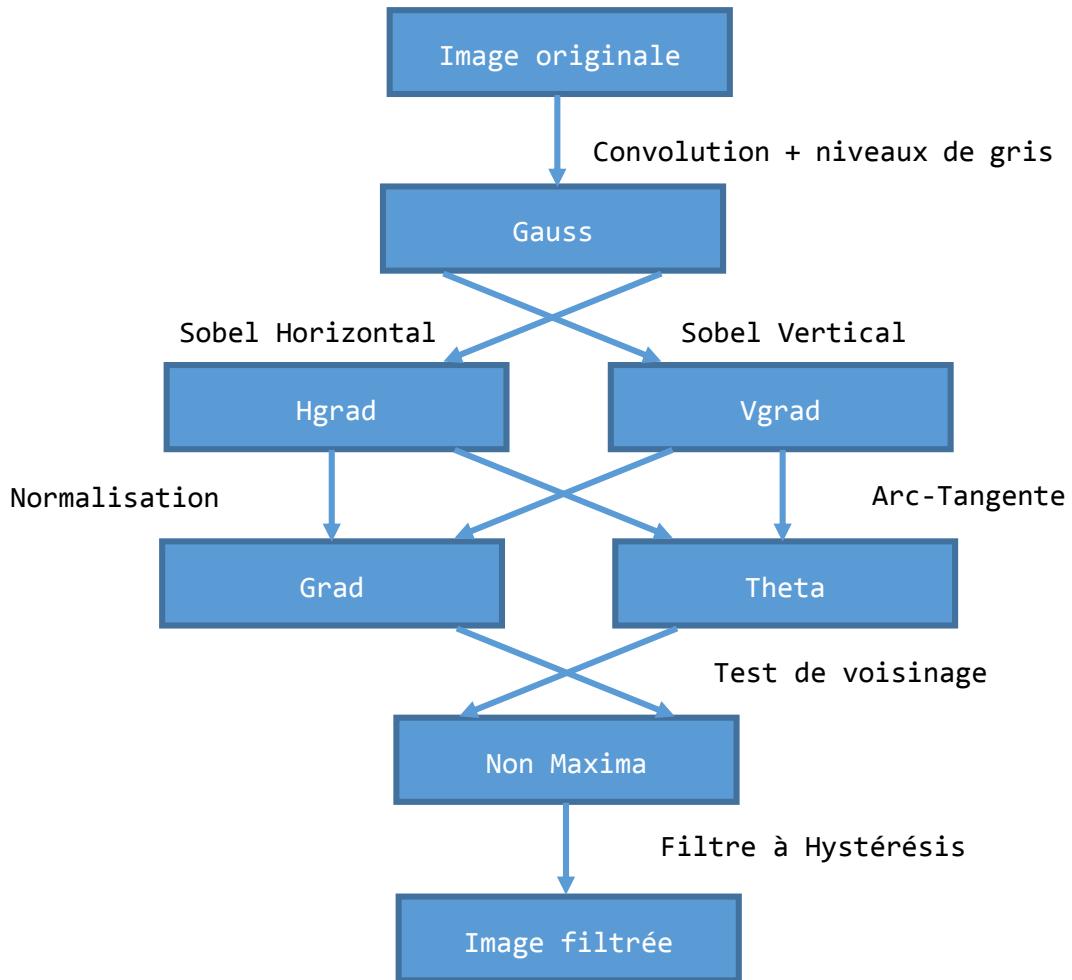

| <b>CHAPITRE 4 EXPÉRIMENTATION DU FLOT : FILTRE DE CANNY .....</b>                | <b>58</b> |

| 4.1 Spécifications et modélisation de l'algorithme .....                         | 58        |

| 4.1.1 Explication de l'algorithme .....                                          | 58        |

| 4.1.2 Implémentation C .....                                                     | 62        |

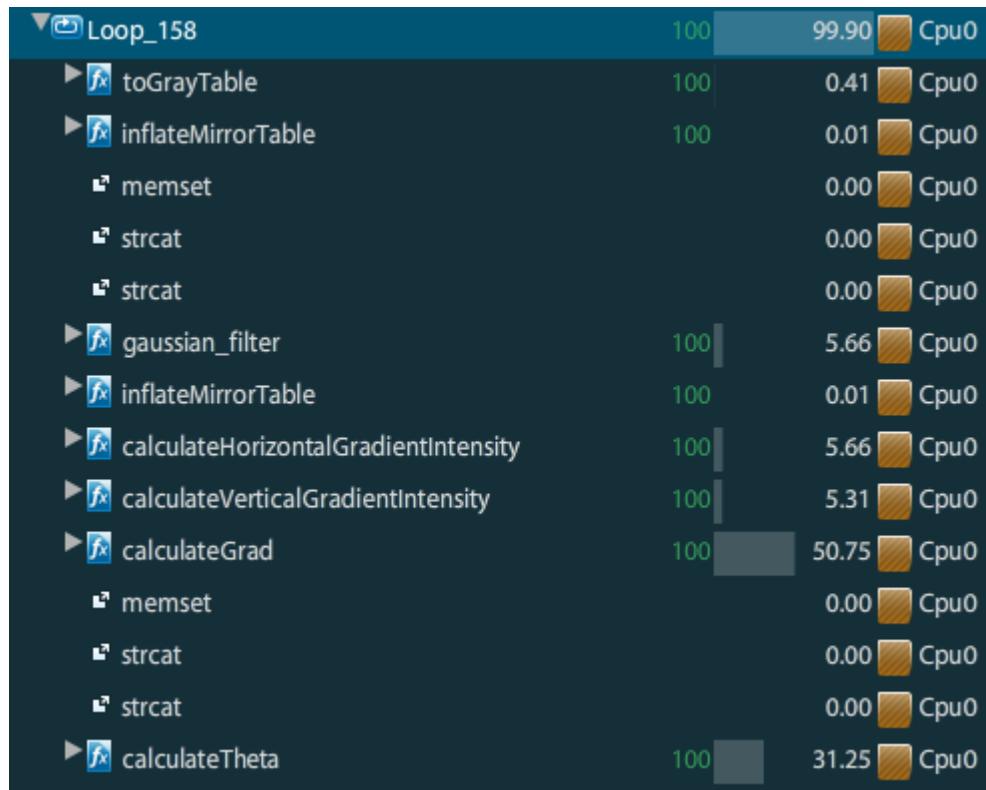

| 4.2 Analyse prépartitionnement avec Pareon .....                                 | 63        |

| 4.2.1 Conditions de test .....                                                   | 64        |

| 4.2.2 Analyse du potentiel de parallélisme .....                                 | 64        |

| 4.2.3 Analyse du potentiel d'optimisation des parties intensives en calcul ..... | 68        |

| 4.3 Traduction assistée du code avec C2Space .....                               | 73        |

| 4.4 Partitionnement, analyse et débogage avec SpaceStudio et HLS Vivado.....     | 74        |

| 4.4.1 Flot de travail sous SpaceStudio .....                                     | 74        |

| 4.4.2 Optimisation du module matériel sous HLS Vivado .....                      | 78        |

| 4.5 Discussion des résultats.....                                                | 82        |

| 4.5.1 Productivité .....                                                         | 82        |

| 4.5.2 Performances .....                                                         | 82        |

| <b>CHAPITRE 5 CONCLUSION ET RECOMMANDATIONS .....</b>                            | <b>89</b> |

| 5.1 Récapitulatif .....                                                          | 89        |

| 5.2 Recommandations .....                                                        | 90        |

|       |                                |    |

|-------|--------------------------------|----|

| 5.2.1 | Le flot de conception ESL..... | 90 |

| 5.2.2 | Le traducteur C2Space .....    | 91 |

|       | BIBLIOGRAPHIE .....            | 93 |

|       | ANNEXES .....                  | 96 |

## LISTE DES TABLEAUX

|                                                                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 4.2-1 : Résultats de la première analyse de potentiel de parallélisme .....                                                                 | 68 |

| Tableau 4.2-2 : Résultats finaux de l'analyse prépartitionnement .....                                                                              | 72 |

| Tableau 4.3-1 : Liste des configurations générées par C2Space .....                                                                                 | 74 |

| Tableau 4.4-1 : Temps d'exécution de différentes configurations avant ajout des temps d'exécution matériels .....                                   | 76 |

| Tableau 4.5-1 : Résultats finaux de temps d'exécution en fonction des différentes directives d'optimisation du module matériel .....                | 83 |

| Tableau 4.5-2 : Valeurs de temps d'exécution, réajustées pour prendre en compte la modification du code source lors de la synthèse haut niveau..... | 84 |

## LISTE DES FIGURES

|                                                                                                                                                                                              |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1-1 : Évolution de l'intégration de transistors sur puces de 1960 à 2010. Courtoisie de Computer History Museum : Revolution Exhibition [1].....                                    | 1  |

| Figure 1.1-2 : Illustration des écarts de productivité avec la croissance du nombre de composants à disposition .....                                                                        | 2  |

| Figure 1.3-1 : Les enjeux d'un projet de création de systèmes électroniques.....                                                                                                             | 6  |

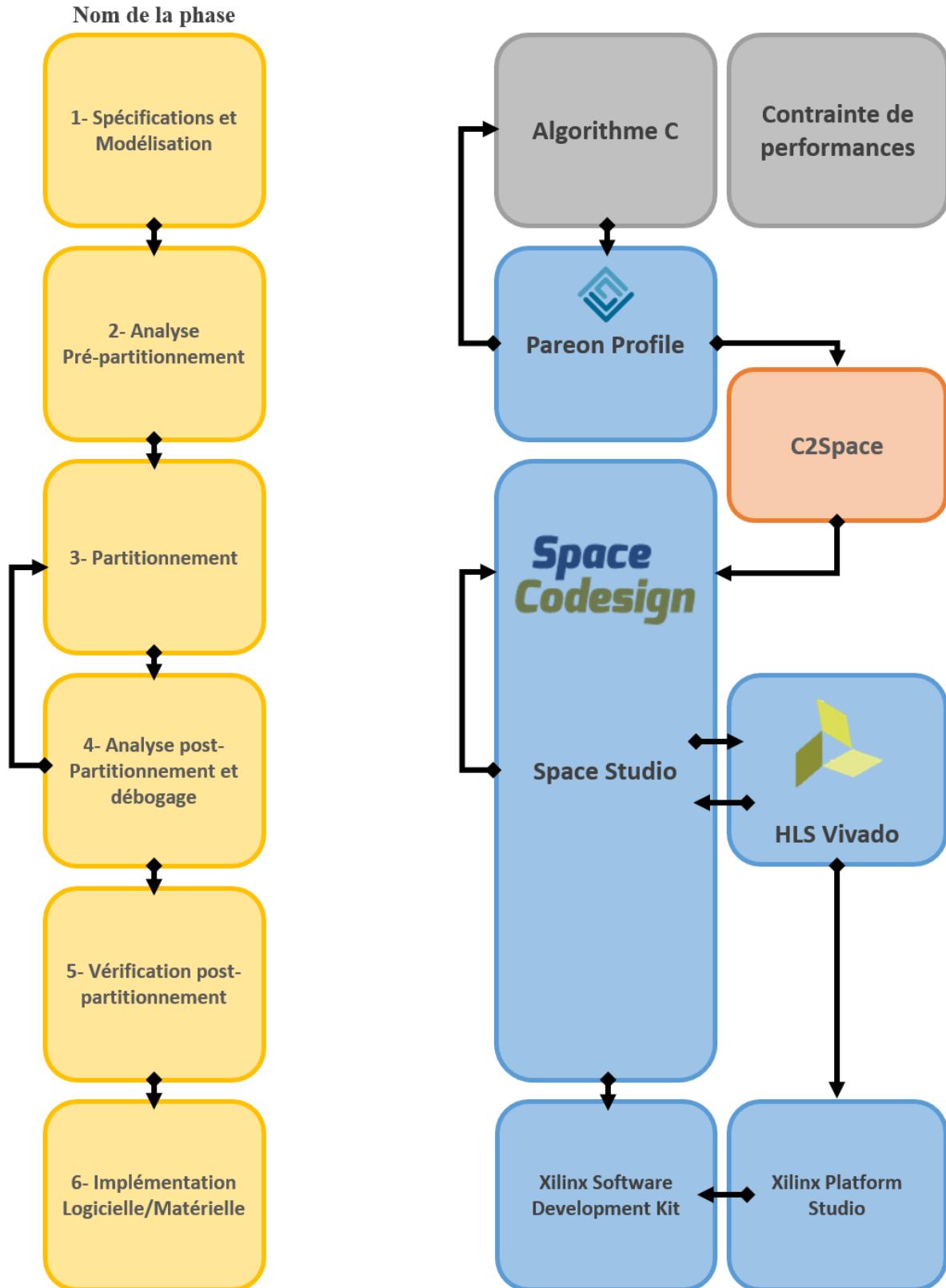

| Figure 1.3-2 : Flot ESL .....                                                                                                                                                                | 8  |

| Figure 2.1-1 : Comparaison entre le flot ESL et le flot présenté .....                                                                                                                       | 19 |

| Figure 2.1-2 : Réduction de l'espace de solution dans notre méthodologie .....                                                                                                               | 22 |

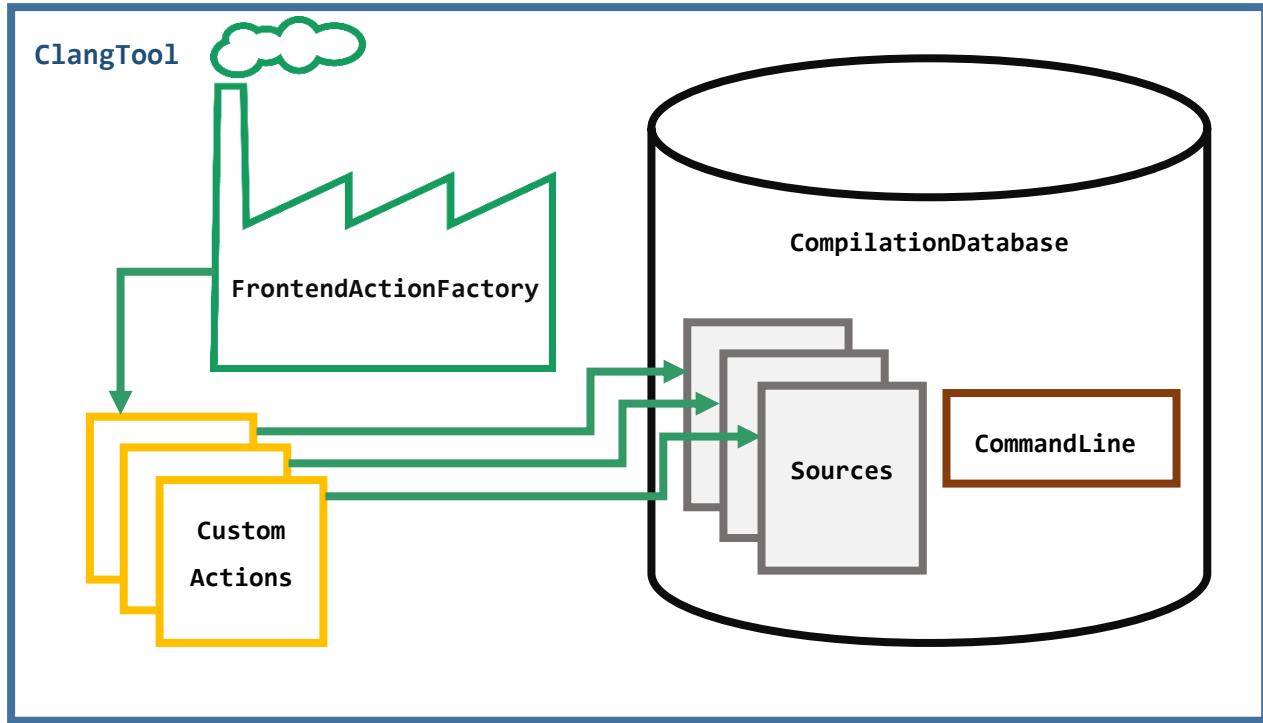

| Figure 3.1-1 : Illustration de la structure de la classe <code>ClangTool</code> .....                                                                                                        | 34 |

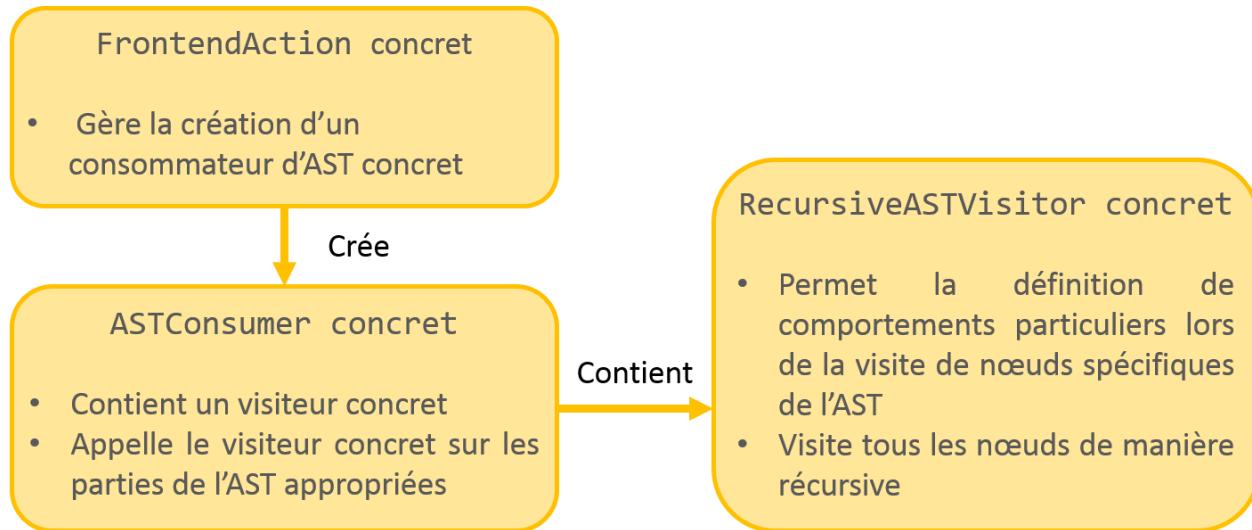

| Figure 3.1-2 : Schéma simplifié de la solution de traversée basée sur le consommateur .....                                                                                                  | 35 |

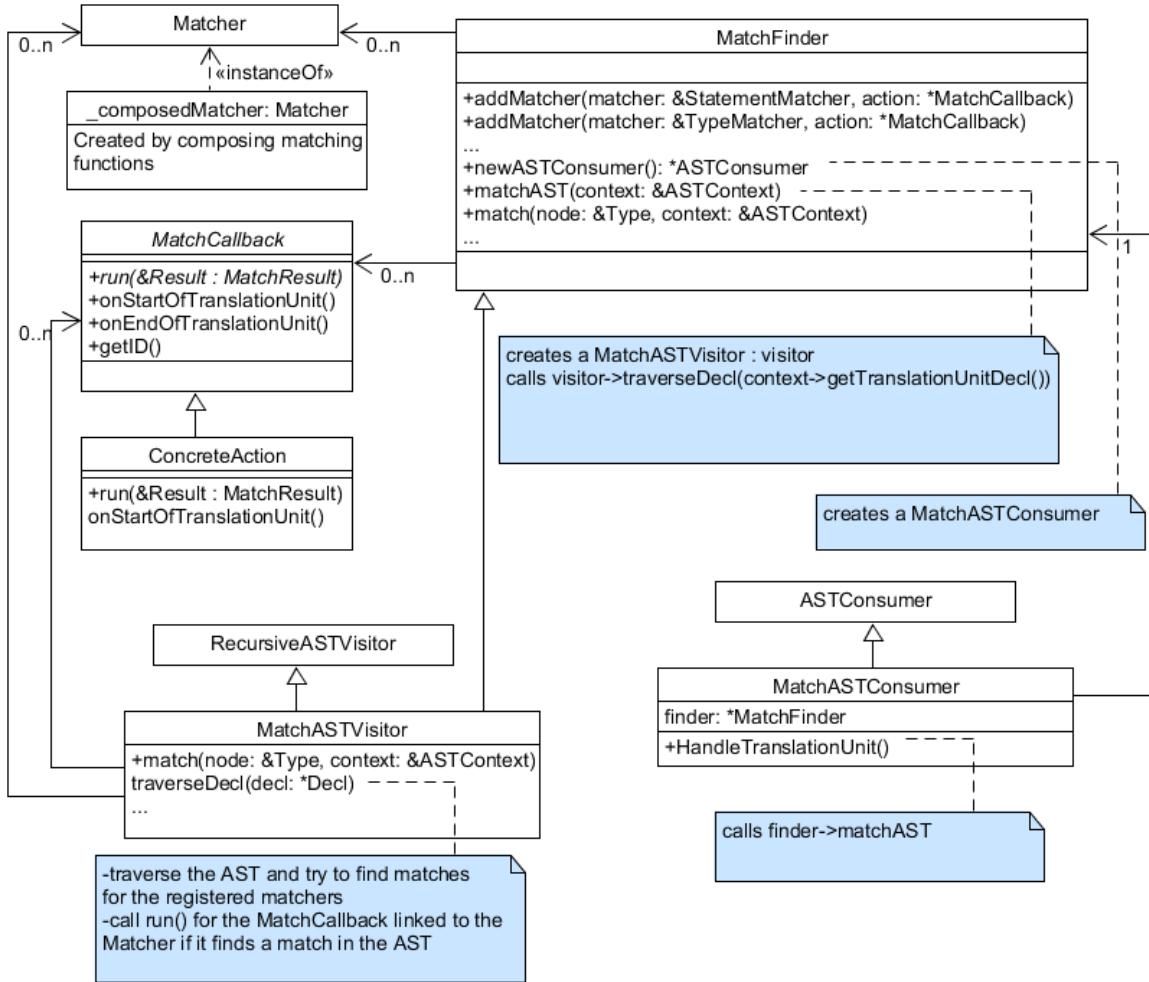

| Figure 3.1-3 : UML simplifié de l'architecture des patrons de correspondance.....                                                                                                            | 38 |

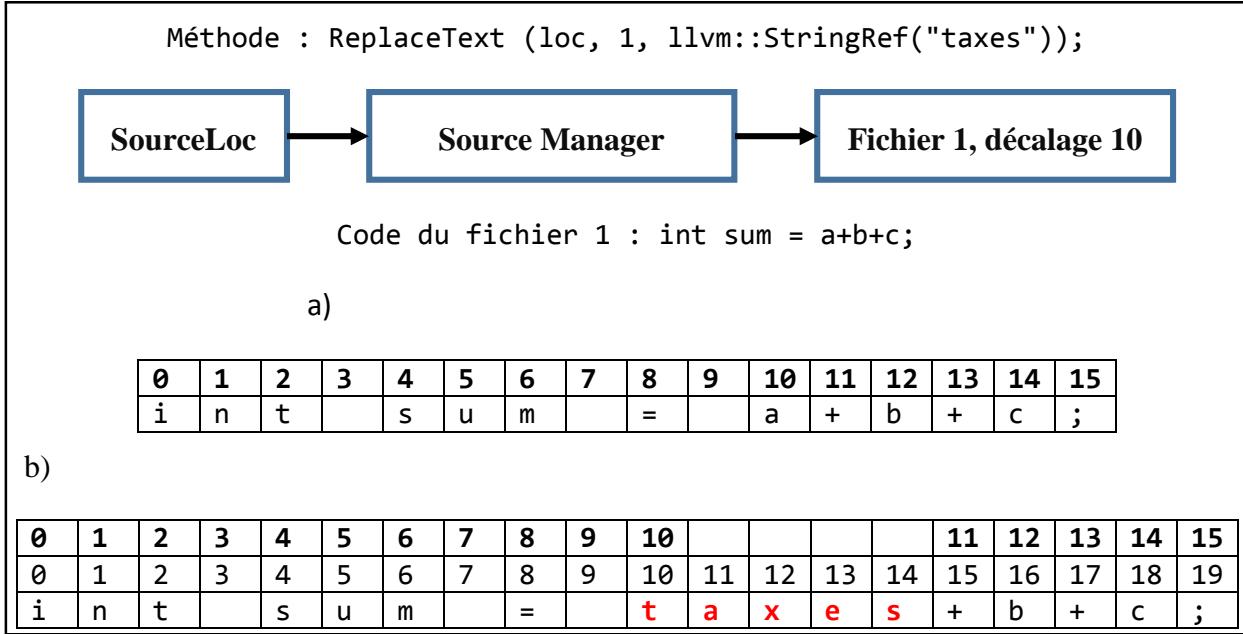

| Figure 3.1-4 : Illustration du fonctionnement interne de la classe Rewriter. a) tampon de la source du fichier 1. b) tampon de réécriture après la méthode de modification de la source..... | 39 |

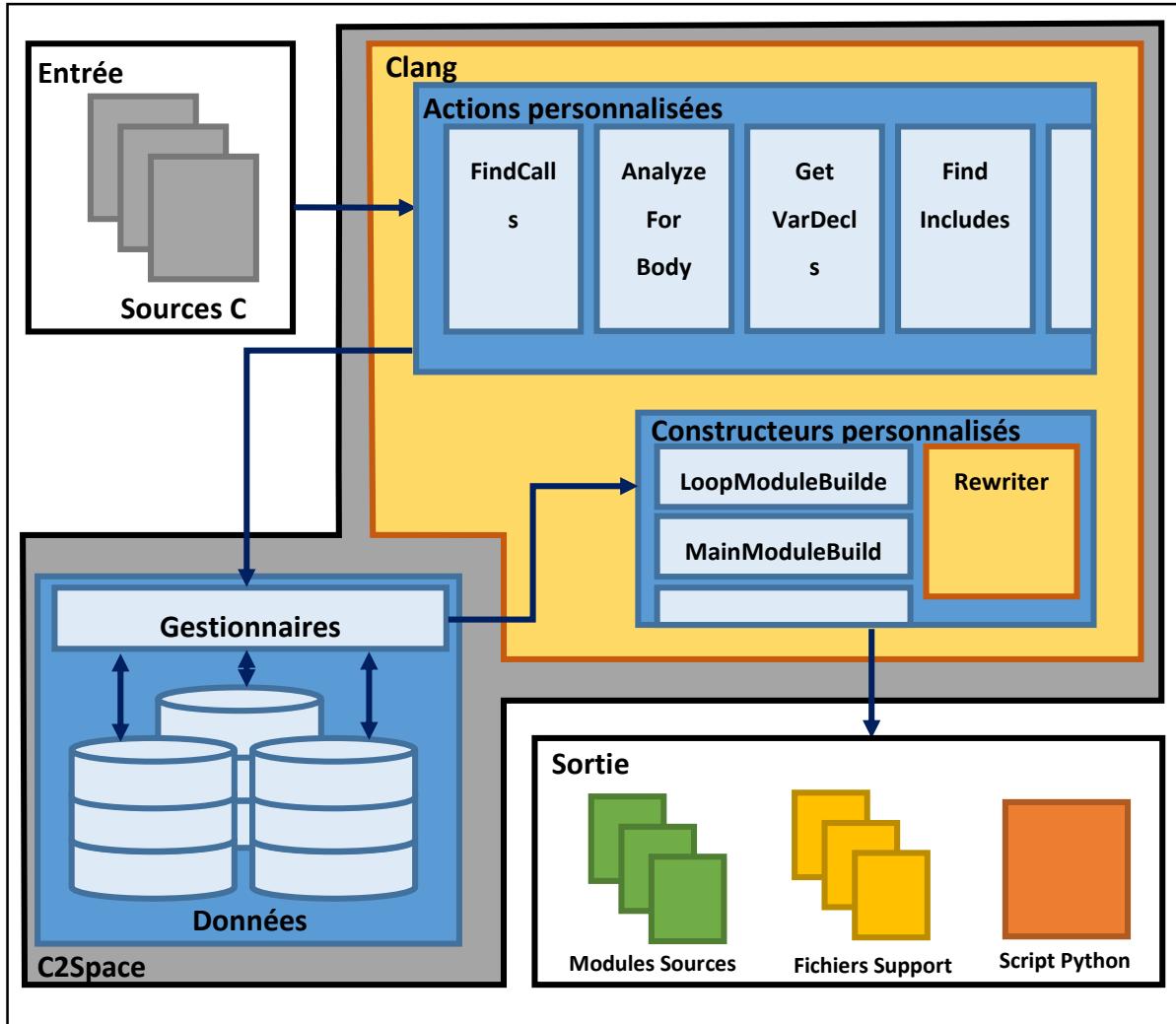

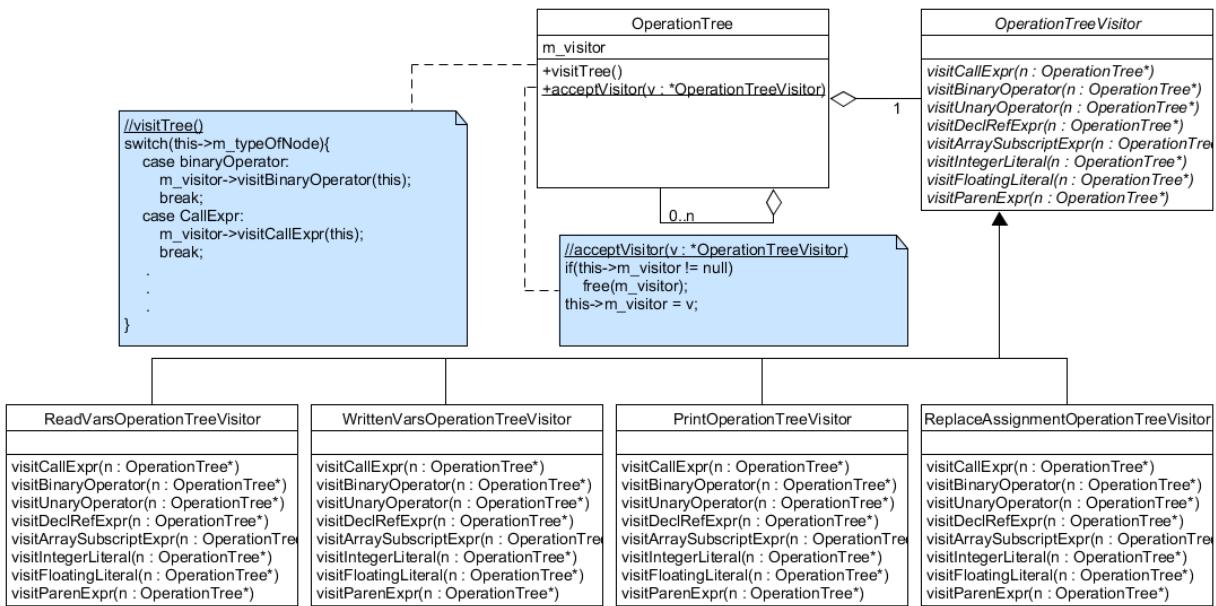

| Figure 3.2-1 : Organisation de CtoSpace .....                                                                                                                                                | 43 |

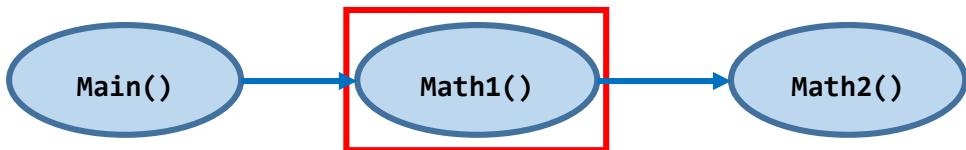

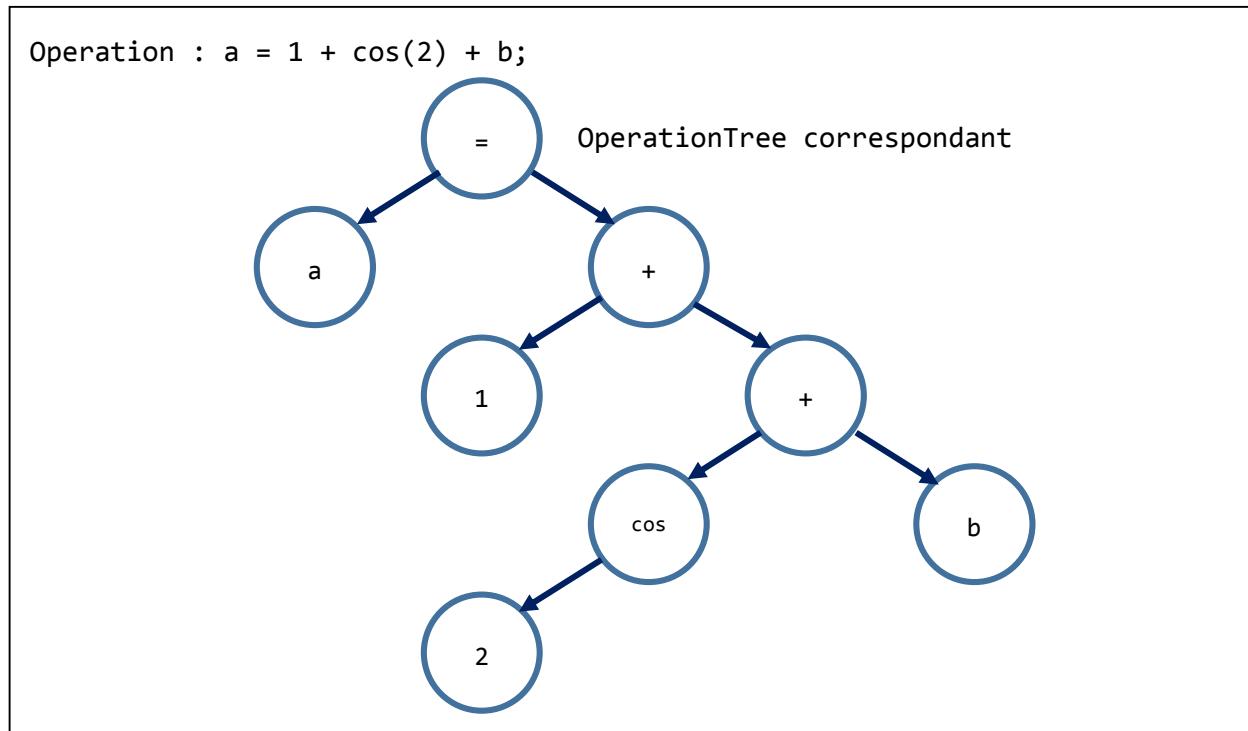

| Figure 3.2-2 : Exemple de graphe d'appel .....                                                                                                                                               | 44 |

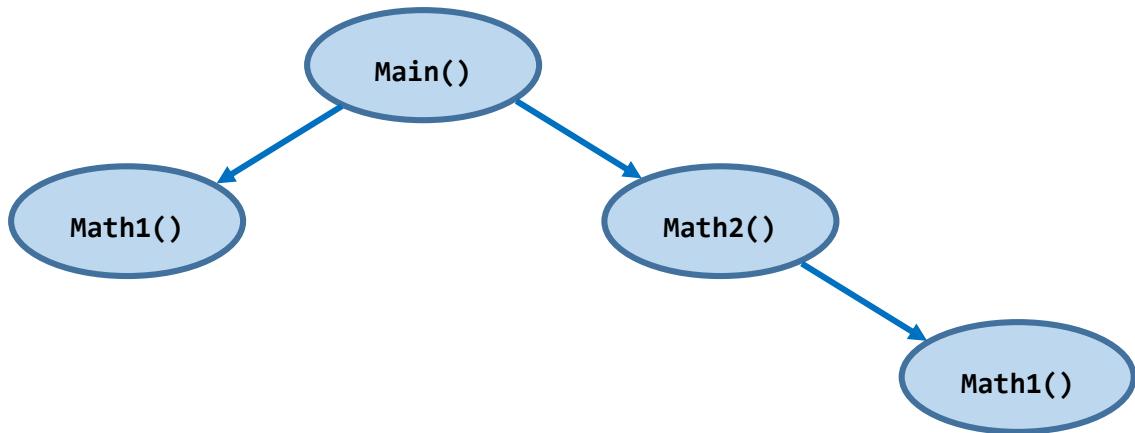

| Figure 3.2-3: Graphe d'appel pour multiples appellants .....                                                                                                                                 | 50 |

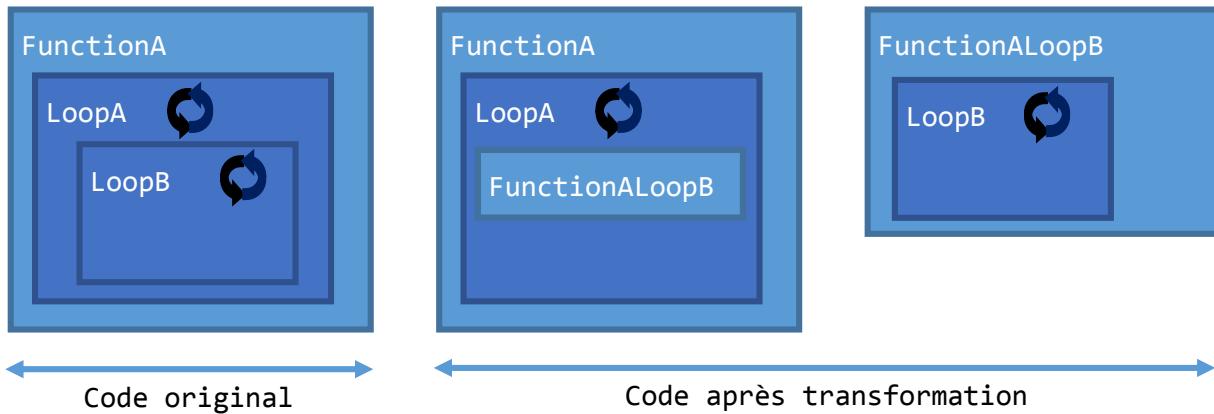

| Figure 3.2-4 : Séparation d'un corps de boucle du reste de la fonction .....                                                                                                                 | 56 |

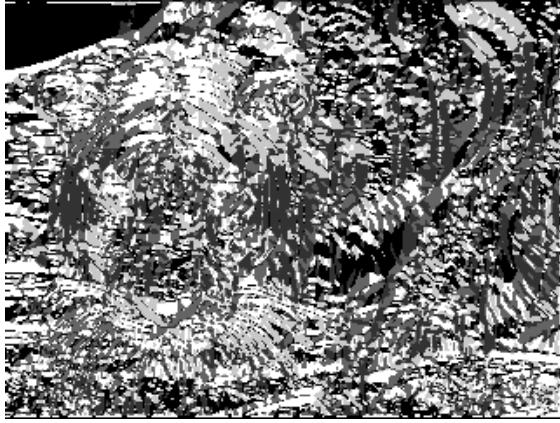

| Figure 4.1-1 : image originale $\mathcal{I}$ .....                                                                                                                                           | 58 |

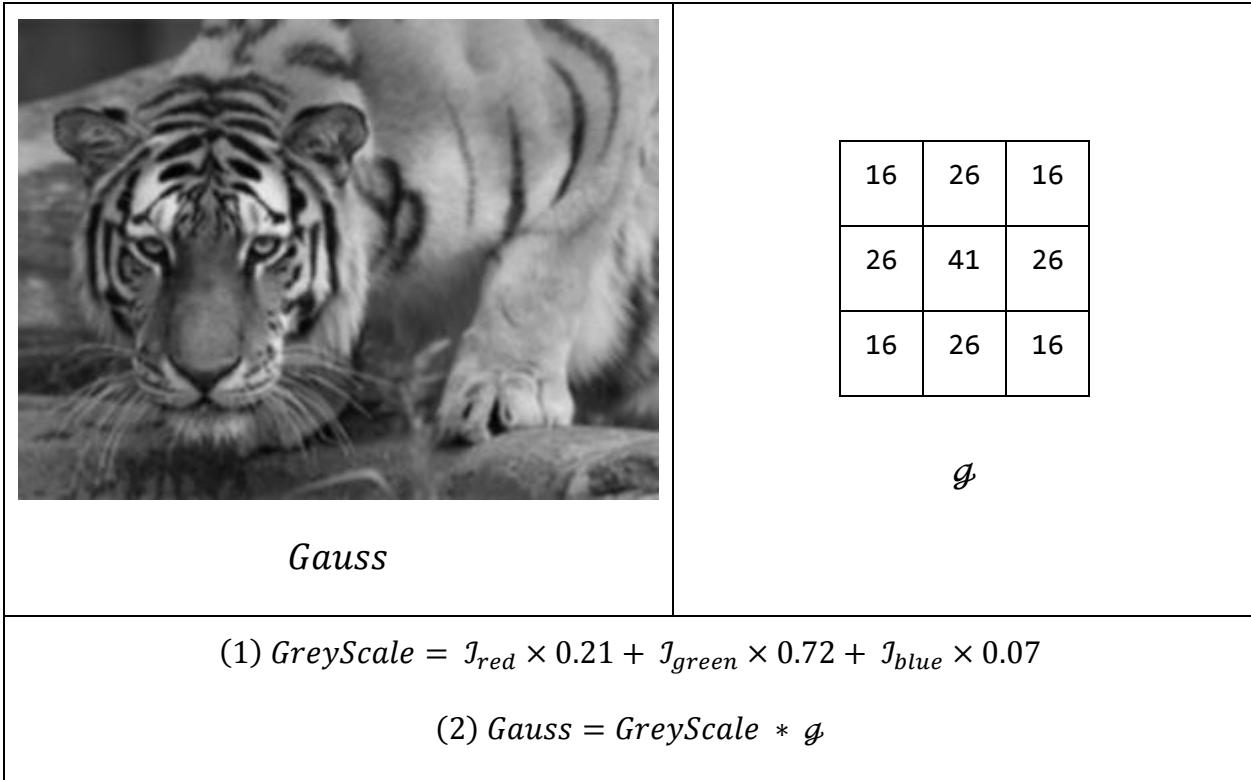

| Figure 4.1-2 : Étape 1 : Application du flou gaussien.....                                                                                                                                   | 59 |

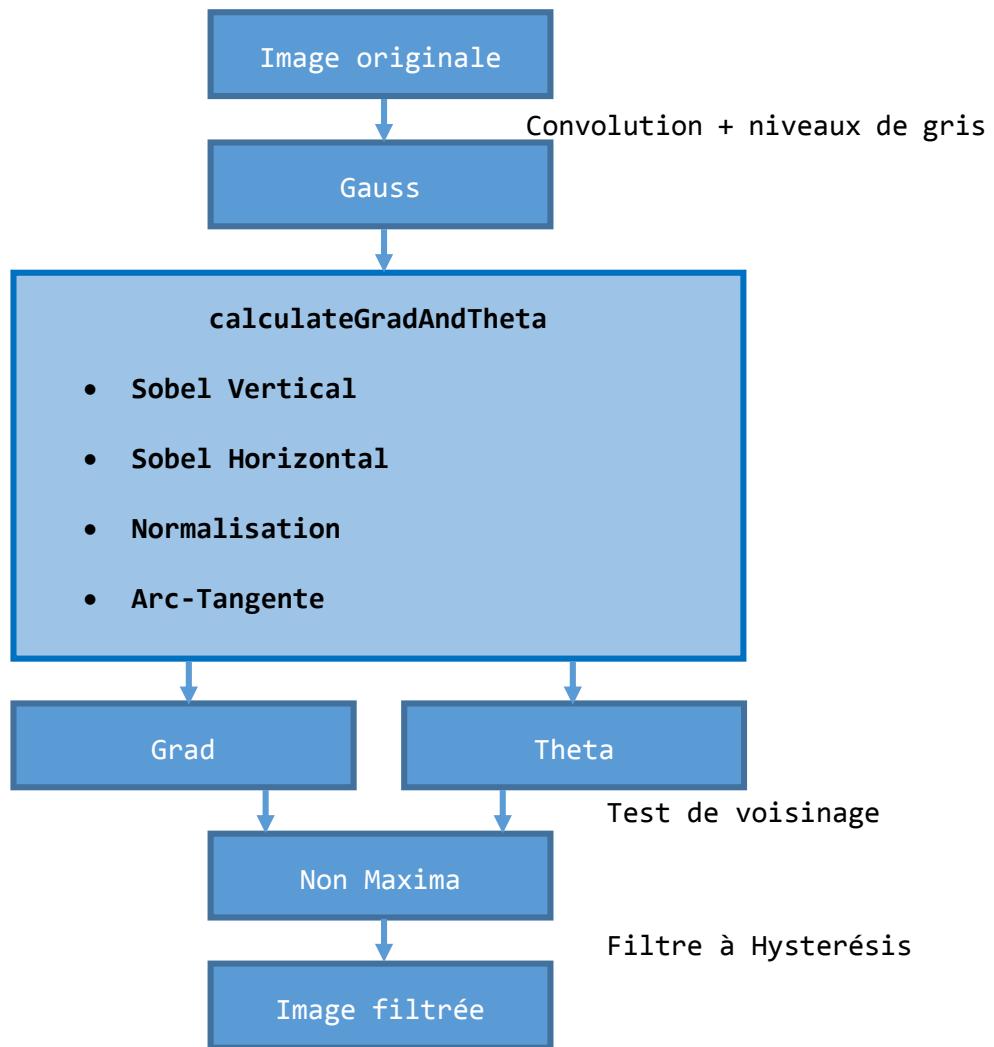

| Figure 4.1-3 : Étape 2 : Génération de la carte des gradients et de l'orientation des gradients .....                                                                                        | 60 |

| Figure 4.1-4 : Étape 3 : Suppression des non-maximums .....                                                                                                                                  | 61 |

| Figure 4.1-5 : Étape finale : filtre à hystérosis .....                                                                                                                                      | 61 |

| Figure 4.1-6 : Premier flot de données .....                                                                                                                                                 | 62 |

|                                                                                                                                                                     |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.2-1 : Protocole d'expérimentation pour l'analyse prépartitionnement .....                                                                                  | 64 |

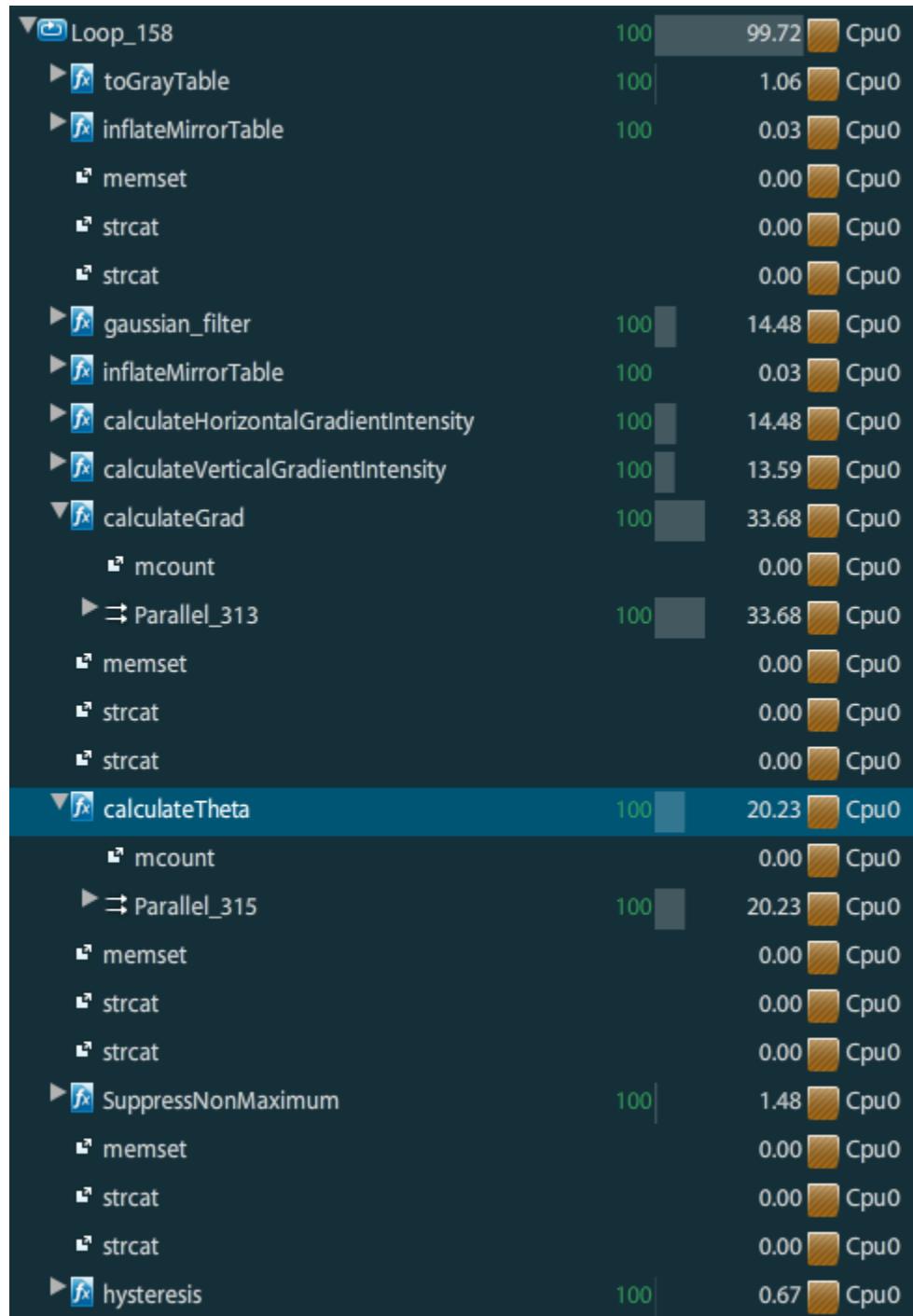

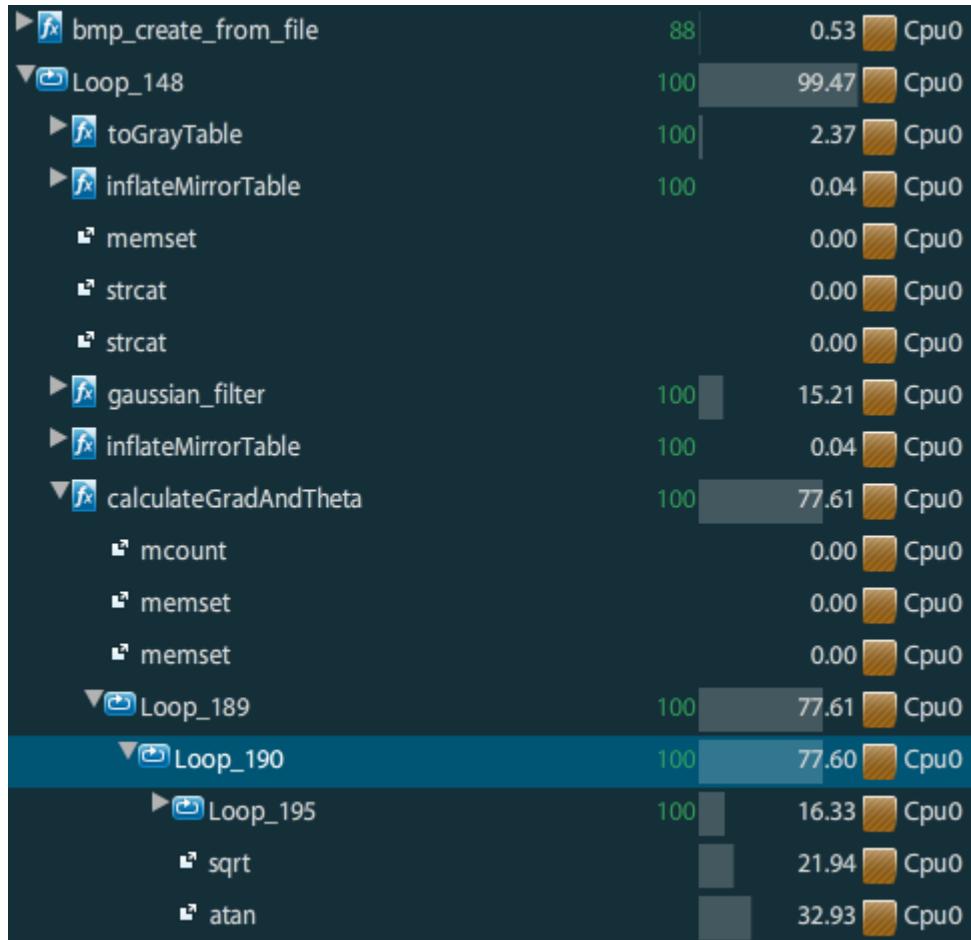

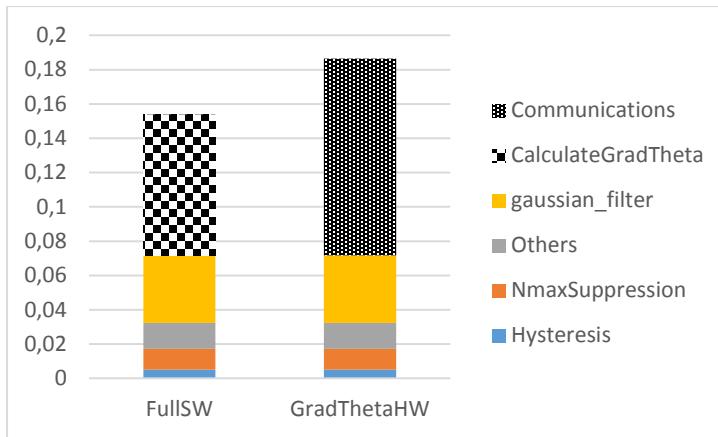

| Figure 4.2-2 : Liste des portions de temps d'exécution principales de l'implémentation .....                                                                        | 65 |

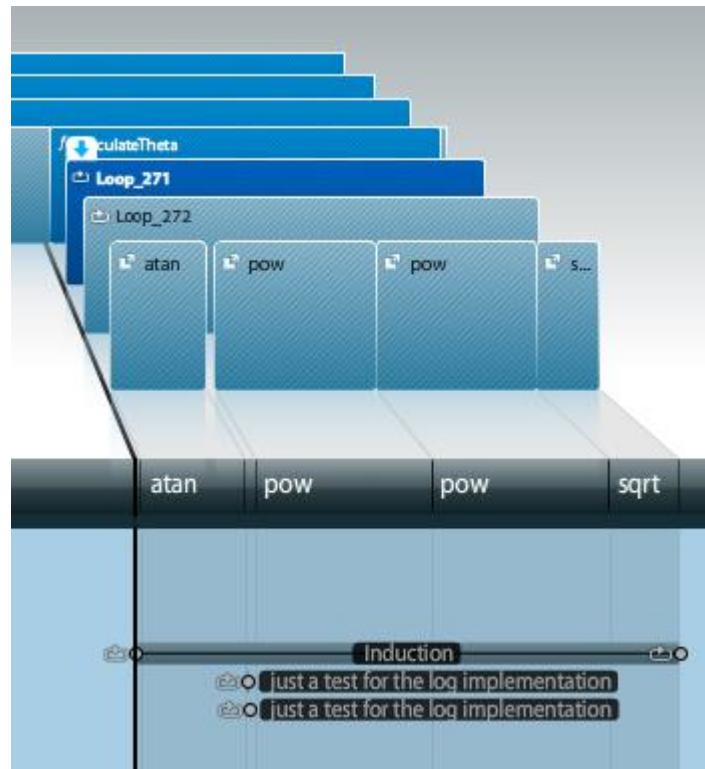

| Figure 4.2-3 : Dépendances de données dans la boucle 271 .....                                                                                                      | 66 |

| Figure 4.2-4 : Répartition du temps d'exécution après parallélisation (x4) des segments calculateTheta et calculateGrad .....                                       | 67 |

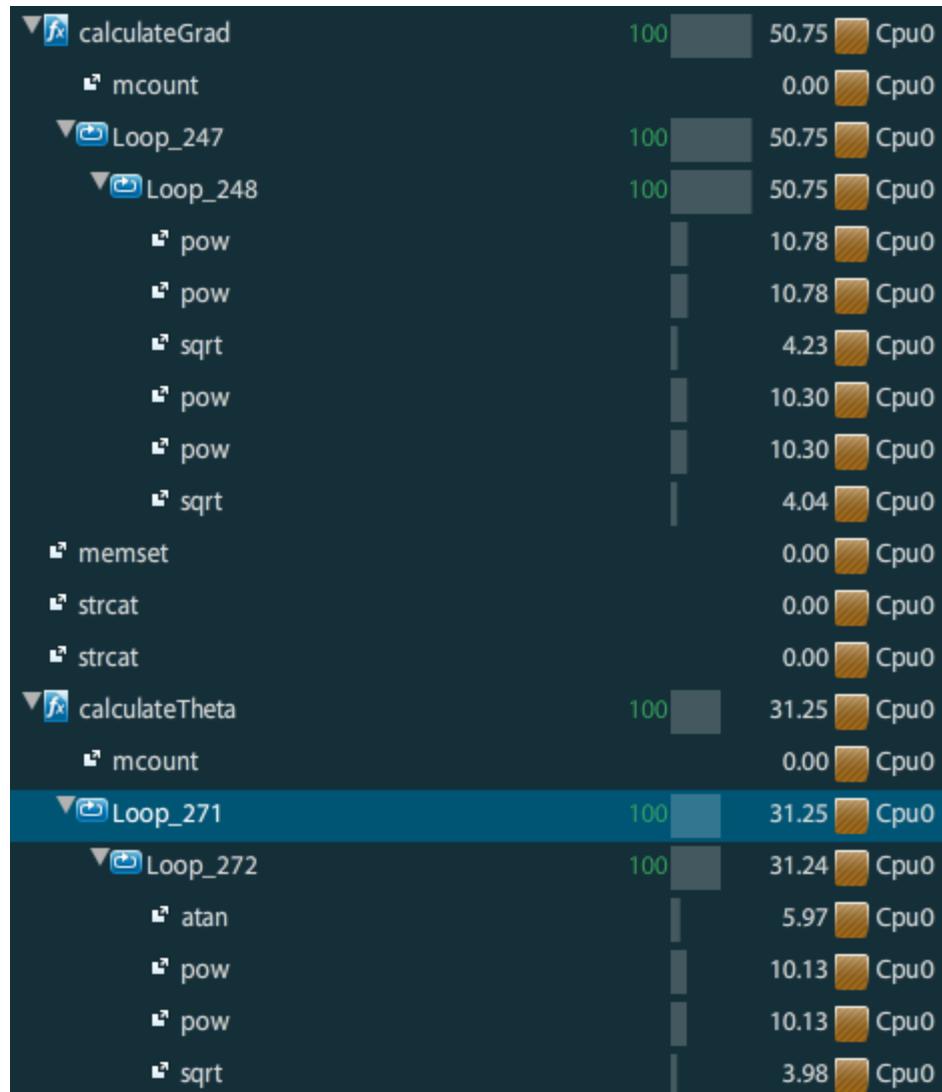

| Figure 4.2-5 : Temps d'exécution des fonctions de la bibliothèque standard .....                                                                                    | 69 |

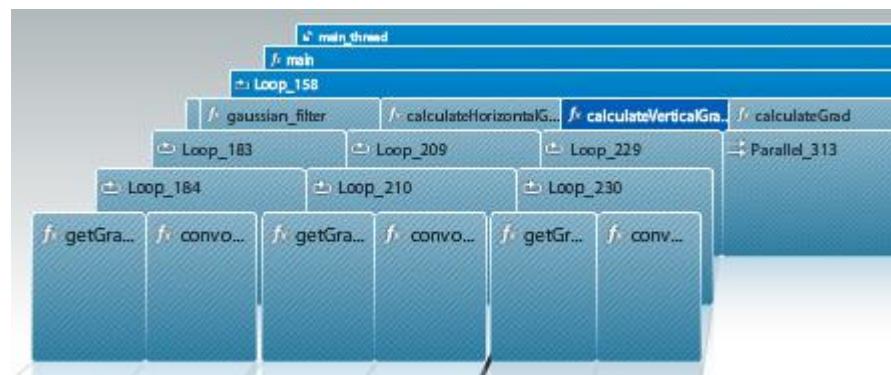

| Figure 4.2-6 : Dépenses engendrées par les fonctions getGrayWindow() et convolutionAbs() ....                                                                       | 69 |

| Figure 4.2-7 : Nouvelle implémentation de l'algorithme.....                                                                                                         | 70 |

| Figure 4.2-8 : Postes de dépenses de la nouvelle implémentation (temps d'exécution : 0.601s) ..                                                                     | 71 |

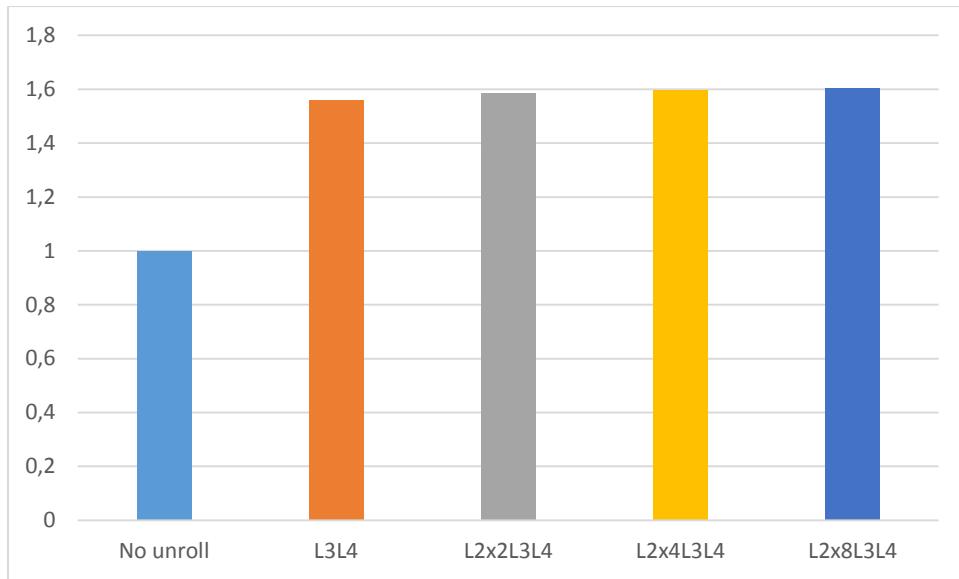

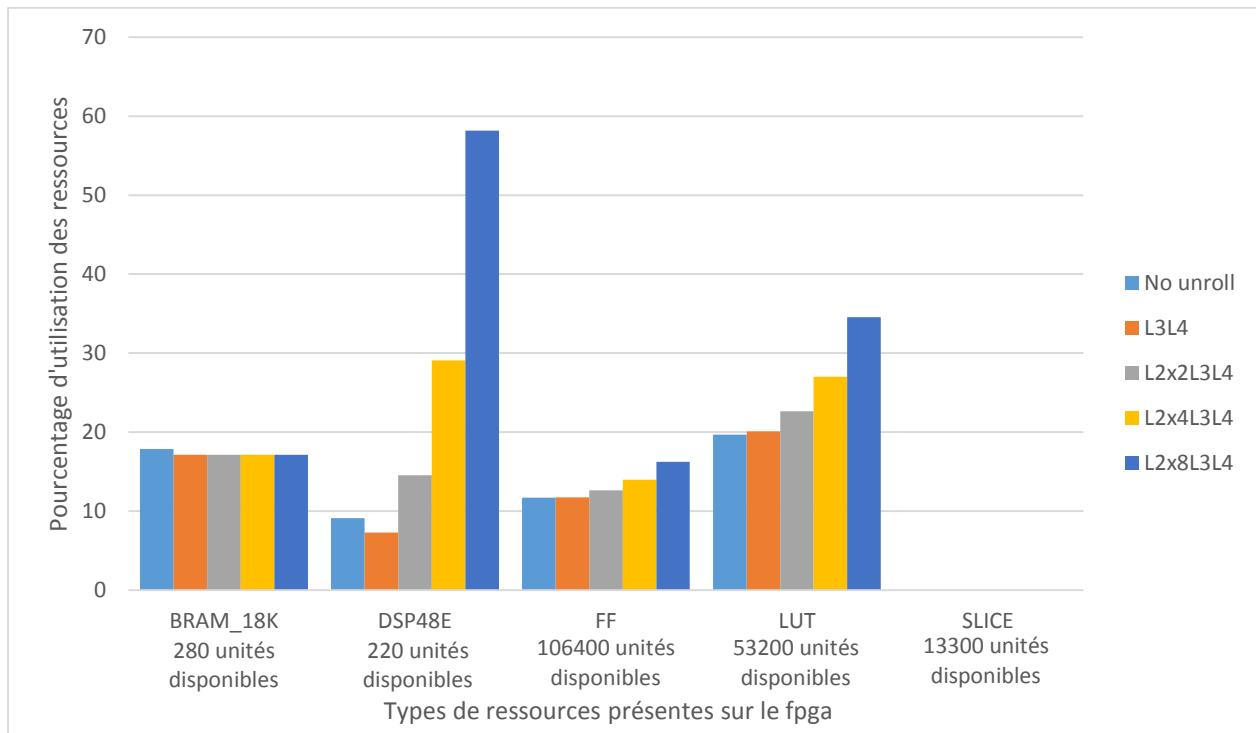

| Figure 4.4-1 : Accélération du module matériel en fonction des directives d'optimisation (temps original : 3.99ms).....                                             | 81 |

| Figure 4.4-2 : Comparaison de la consommation des ressources du FPGA zinq-7000 pour les différents scénarios d'optimisation.....                                    | 81 |

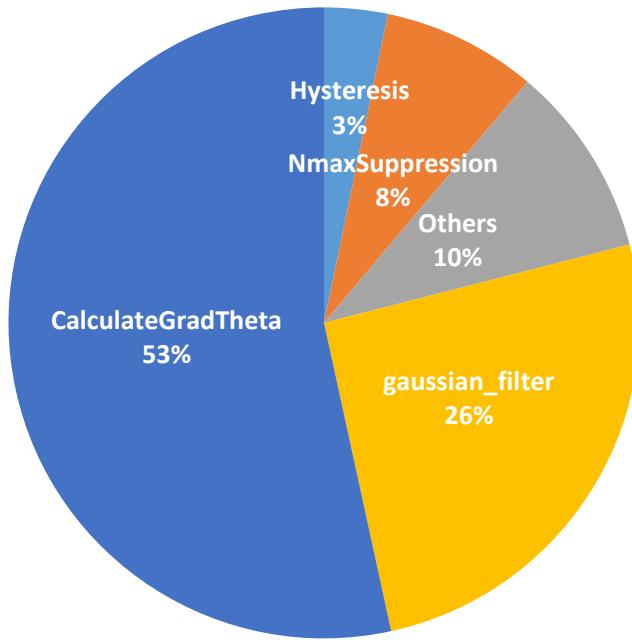

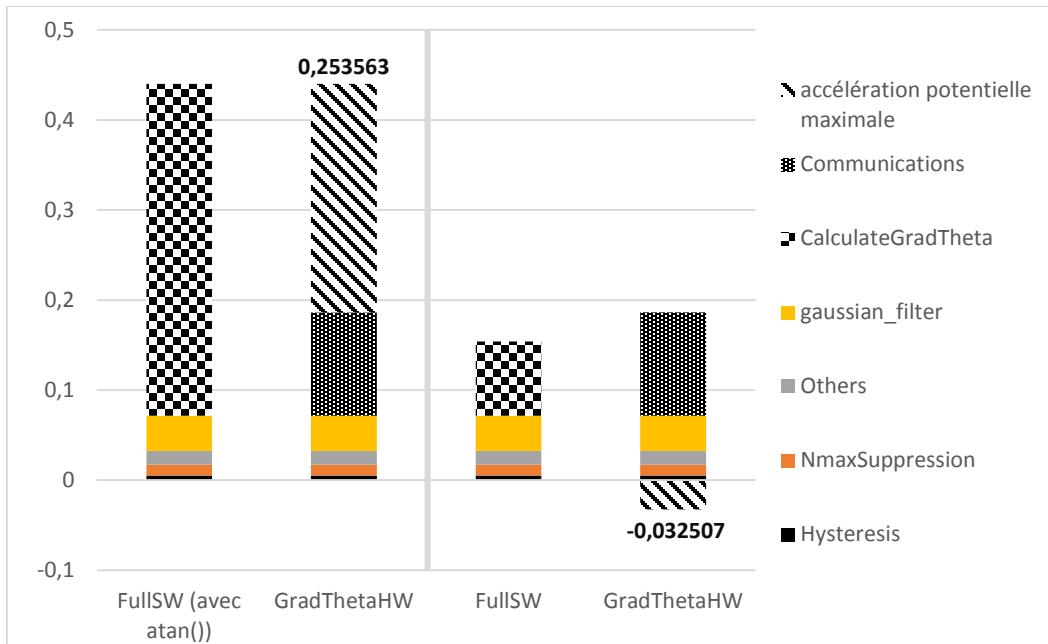

| Figure 4.5-1 : Répartition du temps d'exécution de la cosimulation dans les fonctions principales de l'implémentation entièrement logicielle sous SpaceStudio ..... | 85 |

| Figure 4.5-2 : Postes de dépense du temps d'exécution de la solution entièrement logicielle contre la solution avec partition matérielle.....                       | 86 |

| Figure 4.5-3 : Accélération potentielle du partitionnement avant et après retrait de la fonction atan() de la solution logicielle .....                             | 87 |

## LISTE DES EXTRAITS DE CODE

|                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------|----|

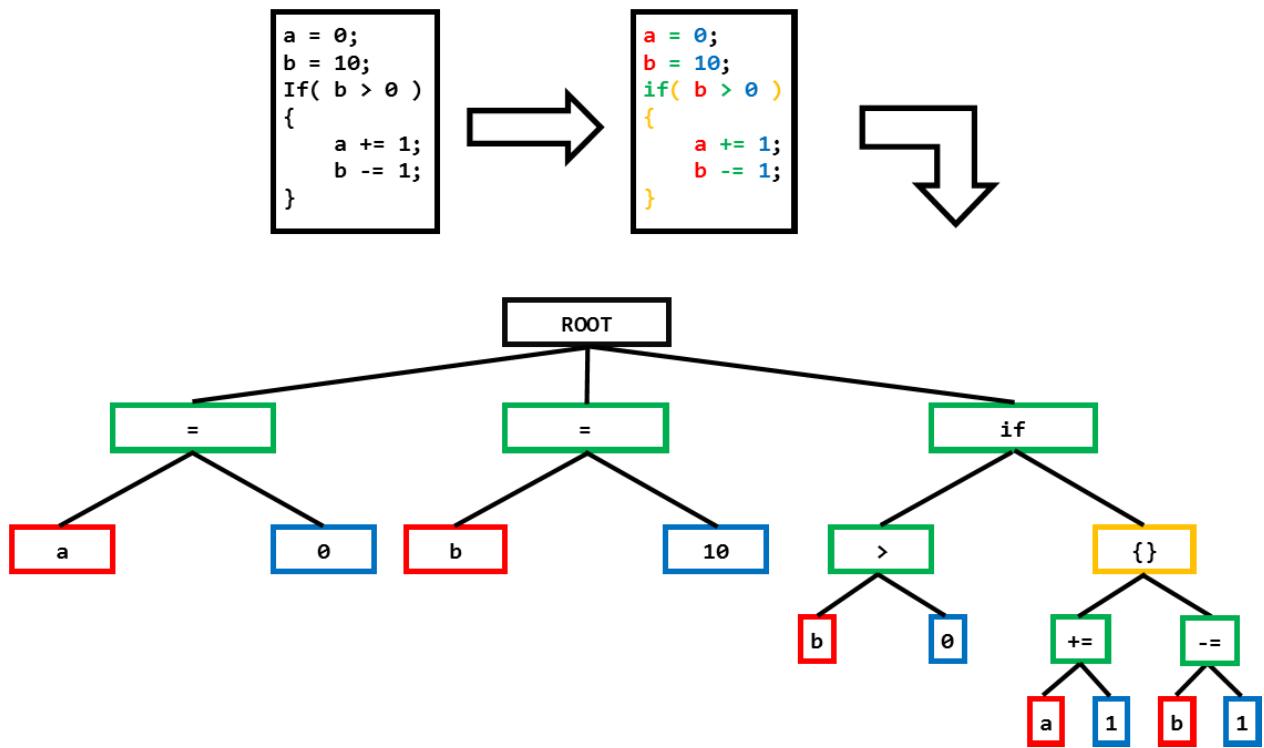

| Extrait 3.1-1 : Illustration de l'exhaustivité de l'AST de Clang .....                                       | 31 |

| Extrait 3.1-2 : code exemple tiré des tutoriels Clang .....                                                  | 33 |

| Extrait 3.1-3 : AST du code exemple de l'extrait 3.2-2 .....                                                 | 33 |

| Extrait 3.1-4 : Patrons de correspondance – Fonctions de correspondance .....                                | 35 |

| Extrait 3.1-5 : Patrons de correspondance – Fonctions de spécification.....                                  | 35 |

| Extrait 3.1-6 : Patrons de correspondance – Fonctions de traversée.....                                      | 36 |

| Extrait 3.1-7 : Patrons de correspondance – Méthodes d'association.....                                      | 36 |

| Extrait 3.2-1 : Deux fonctions à modulariser .....                                                           | 45 |

| Extrait 3.2-2 : Module SpaceStudio générique minimal (entête).....                                           | 46 |

| Extrait 3.2-3 : thread générique.....                                                                        | 47 |

| Extrait 3.2-4: méthode action générique .....                                                                | 47 |

| Extrait 3.2-5 : Interaction Fonction analysée/Fonction DAM appelée .....                                     | 48 |

| Extrait 3.2-6 : méthodes send et read génériques.....                                                        | 49 |

| Extrait 3.2-7: Exemple de thread avec plusieurs modules appelants .....                                      | 51 |

| Extrait 3.2-8 : Définition de la classe Module à boucle .....                                                | 52 |

| Extrait 3.2-9 : Méthode d'action d'un Module à boucle .....                                                  | 53 |

| Extrait 3.2-10 : Protocole de remplacement d'un appel d'une fonction DAM à boucles .....                     | 54 |

| Extrait 4.4-1 : Étiquetage des corps de boucle de la fonction d'action du module<br>calculateGradTheta ..... | 78 |

| Extrait 4.4-2 : Modification de la fonction atan() .....                                                     | 80 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|        |                                                       |

|--------|-------------------------------------------------------|

| AADL   | Architectural Analysis Description Language           |

| ALAP   | As Late As Possible                                   |

| ASAP   | As Soon As Possible                                   |

| AST    | Abstract Syntax Tree                                  |

| BRAM   | Block Random Access Memory                            |

| BSP    | Board Support Package                                 |

| CFDG   | Control-Flow Data Graph                               |

| CMU-DA | Carnegie Melon University Design Automation           |

| DAM    | Destinée À être Modularisée                           |

| DMA    | Direct Memory Access                                  |

| DSP    | Digital Signal Processing                             |

| EDA    | Electronic Design Automation                          |

| EDK    | Embedded Development Kit                              |

| ELF    | Executable and Linkable Format                        |

| FIFO   | First In First Out                                    |

| FPGA   | Field Programmable Gate Array                         |

| GPU    | Graphical Processing Unit                             |

| HDL    | Hardware Description Language                         |

| HLS    | High Level Synthesis                                  |

| IP     | Intellectual Property                                 |

| JSON   | JavaScript Object Notation                            |

| MCSE   | Méthodologie de Conception des Systèmes Électroniques |

| PBD    | Platform Based Design                                 |

|      |                              |

|------|------------------------------|

| RTL  | Register Transfer Level      |

| RTM  | Register Transfer Modules    |

| SoC  | System on Chip               |

| TLM  | Transaction Level Model      |

| VLSI | Very Large Scale Integration |

| XPS  | Xilinx Platform Studio       |

**LISTE DES ANNEXES**

|                                          |    |

|------------------------------------------|----|

| Annexe A – Architecture de C2SPace ..... | 96 |

|------------------------------------------|----|

## CHAPITRE 1 INTRODUCTION

Le domaine du design de puces destinées à différents systèmes informatiques, comme les circuits intégrés pour application spécifique, les processeurs d'utilisation générale ou encore les processeurs de traitement de signal numérique, comporte de nombreux défis, tel qu'énoncé par le carnet de route international de la technologie des semi-conducteurs. Parmi ceux-ci, le problème des fossés entre la croissance de la productivité, la vérification des ingénieurs système et la quantité de composantes à intégrer dans une architecture reste un des grands efforts de recherche de ce champ d'applications.

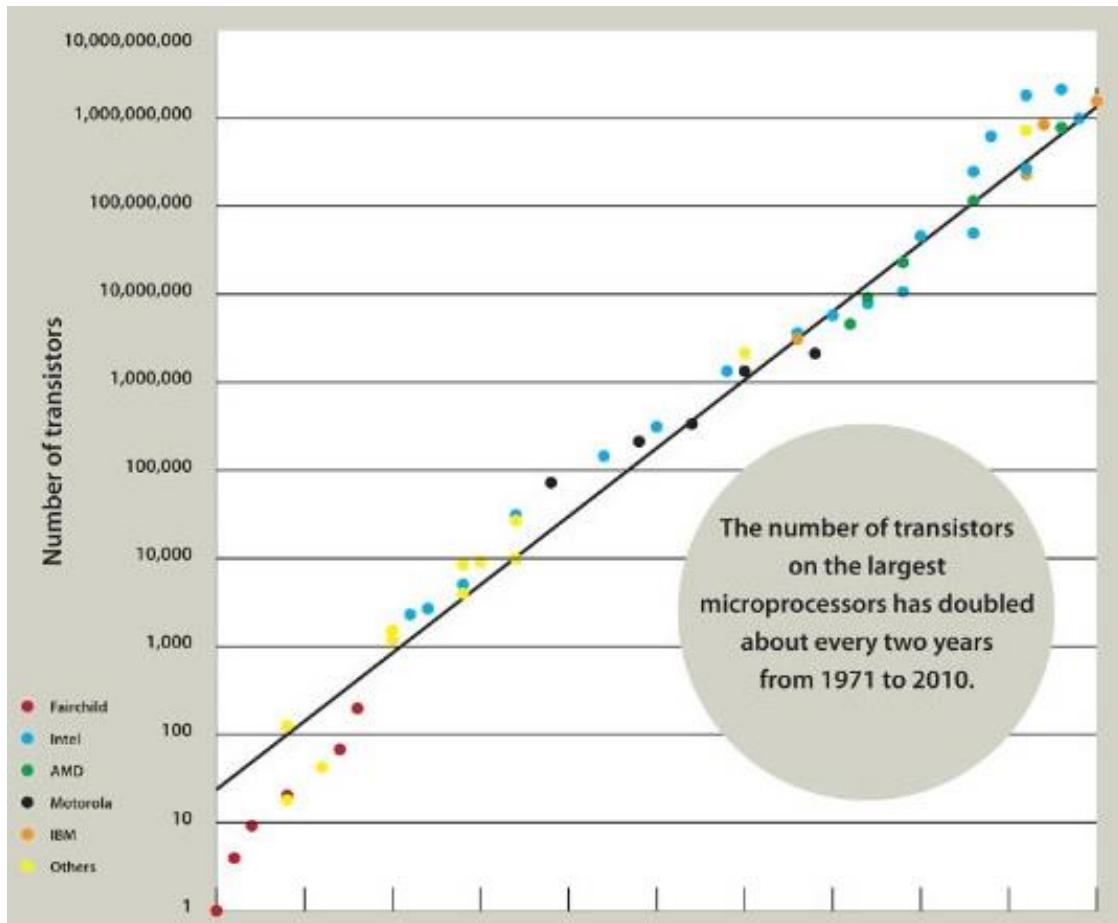

La loi de Moore [1] énonce que la quantité de transistors intégrés dans les puces double tous les ans. Elle découle d'une observation de cette tendance entre les années 59 et 65. Cette prédition s'est avérée correcte pour les dix années suivantes. Moore révisa sa loi lors des années 80, en

Figure 1.1-1 : Évolution de l'intégration de transistors sur puces de 1960 à 2010.

Courtoisie de Computer History Museum : Revolution Exhibition [1]

énonçant cette fois une multiplication par deux de la complexité des circuits tous les deux ans [2]. Depuis 1975, cette tendance s'est maintenue (fig. 1.1-1) et plusieurs experts soutiennent que la loi de Moore restera pertinente pour la prochaine décennie.

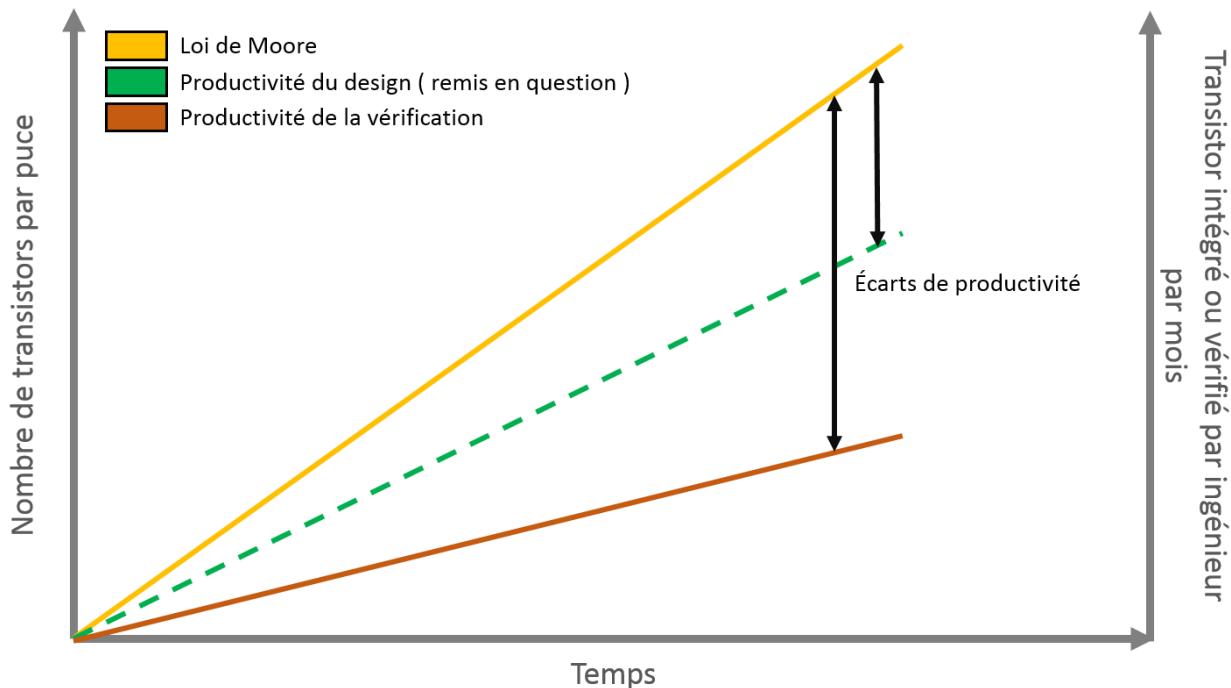

Toutefois, un des aspects non développés dans cette croissance de la complexité des circuits est la capacité dans un temps raisonnable de concevoir un système tirant parti de ces capacités grandissantes. Ce problème, qui émerge en 1997 dans un rapport de SEMATECH, stipule que la croissance énoncée dans la loi de Moore surpassé largement la croissance de la capacité d'intégration de transistors par ingénieur par mois et que, si ce fossé n'est pas comblé, l'industrie sera sévèrement bridée dans sa capacité d'intégration et dans ses temps de mise sur le marché.

Certaines recherches plus récentes estiment que ce fossé n'a jamais eu lieu grâce à la création d'outils de plus en plus efficaces mais commencent à s'inquiéter d'un autre problème de productivité lié à la vérification [3]. En effet, la croissance de la complexité des puces électroniques implique une augmentation des efforts de vérification pour mener un projet à terme. Ainsi en 2012, le temps alloué à la vérification d'un système représentait en moyenne 56 % du temps total d'un projet, alors qu'en 2007, ce temps n'était que de 49 %. La figure 1.1-2 résume ces constats.

Figure 1.1-2 : Illustration des écarts de productivité avec la croissance du nombre de composants à disposition

Pour résoudre cette problématique, l'effort de recherche a abouti au cours du temps à plusieurs améliorations incrémentales du flot de développement des systèmes matériels. La suite de cette revue va résumer et classifier ces différentes améliorations.

## 1.1 Les langages de description de matériel (HDL)

Dès les années 80, avec la montée croissante de l'adoption de l'intégration à très grande échelle (VLSI) au détriment des puces spécifiques, ce n'est plus quelques centaines de composants qui doivent être interconnectés, mais bien plusieurs centaines de milliers. Le besoin d'une vue à plus haut niveau et de réutilisabilité dans de tels systèmes se fait alors sentir [4]. Les langages de description de matériel (HDL) commencent alors à apparaître. Ces langages ont un but principal : la création d'un standard de communication dans le domaine de la description de systèmes matériels. Un tel standard permet la communication entre les différentes équipes, mais aussi la diffusion de modèles standards d'une entreprise à une autre. Ainsi, un langage de description doit être capable de capturer plusieurs aspects d'un design : sa fonctionnalité (aspect procédural), son architecture (aspect structurel) et la façon dont les données transitent (aspect flot de données) [5]. L'autre avantage d'une standardisation des représentations est de permettre le développement des outils d'automatisation du design électronique (EDA) basés sur ces standards. Aujourd'hui, deux HDLs dominent le marché : VHDL et Verilog HDL. Ces deux HDL possèdent à quelques différences près les mêmes capacités techniques, comme la description haut-niveau de l'algorithme modélisé (procédural), la liste des composants bas-niveau nécessaire (structurel) ainsi que les éléments de synchronisation (flot de données). Ce qui motive le choix pour l'un ou l'autre de ces outils sera plutôt la préférence personnelle du développeur, l'environnement EDA qui est à sa disposition ou encore différentes raisons économiques [6].

## 1.2 La synthèse haut-niveau (HLS)

Durant la même période, un nouveau paradigme de conception de systèmes sur puce (SoC) commence à apparaître. Les travaux préliminaires de Barbacci et Siewiorek montrent qu'il est possible de convertir une description de niveau transfert de registre (RTL) comportementale en une implémentation structurelle composée de blocs spécifiques appelés modules niveau transfert registre (RTM) [7]. Ces premiers résultats donnent naissance à l'outil Carnegie-Mellon University Design Automation (CMU-DA) [8]. Celui-ci est décrit comme un flot de conception assistée par

ordinateur permettant d'accompagner la transformation d'une spécification haut-niveau de système complexe jusqu'à la création de masques qui seront utilisés pour la production de celui-ci. Ce flot prend en entrée un langage décrivant le comportement du système et fournit en sortie une description du point de vue de la RTL. Ces premiers résultats déclenchent un fort intérêt de la recherche dans le domaine de l'EDA et on voit apparaître une première génération d'outils HLS, autant académiques qu'industriels. Toutefois, cette première vague d'outils a du mal à s'imposer et à devenir une norme dans le milieu de la conception de SoC, car les techniques de synthèse RTL sur lesquelles reposent les outils HLS de l'époque ne sont pas encore fonctionnelles et adoptées. Ces premiers outils sont en plus encore considérés comme trop simplistes et conduisent à une qualité de résultats peu encourageante [9].

C'est avec l'utilisation croissante des standards HDLs VHDL et Verilog que la nouvelle génération d'HLS trouve un second essor dans les années 90 [10]. De plus, la recherche permet aux outils de synthèse RTL de devenir plus performants, conduisant ainsi à l'adoption de ceux-ci par l'industrie. Dans [11], Camposano présente les aspects principaux de la synthèse haut niveau. Le flot présenté prend comme point de départ une description comportementale VHDL puis applique dans l'ordre trois transformations sur celle-ci. La première passe appelée « compilation » a pour but de transformer le code en une représentation mieux adaptée à la passe suivante, en l'occurrence, une paire Graphe du flot de contrôle/Graphe du flot de données. En ceci, cette première passe ressemble beaucoup à l'action qu'aurait un compilateur logiciel non-optimisant. La seconde passe de l'outil consiste à appliquer des transformations haut niveau sur la sortie de la première passe. Certaines de ces optimisations sont communes à celles qu'un compilateur aurait pu effectuer tandis que d'autres sont spécifiques au domaine matériel (par exemple le déroulement de boucle ou la création de concurrence). Ces modifications affectent la forme des deux structures précédemment créées (contrôle et données). Enfin, la troisième phase du flot consiste en l'ordonnancement et l'allocation des ressources aux éléments des graphes. Plusieurs algorithmes permettent d'arriver à différents résultats. On peut citer pour l'ordonnancement les algorithmes aussitôt que possible (ASAP) et aussi tard que possible (ALAP). Une fois un ordonnancement choisi, on passe à l'allocation des ressources matérielles. Cette étape est intimement liée à l'étape d'ordonnancement et peut être résolue avec, par exemple, des algorithmes de colorations de graphes. On notera que le résultat final de ce flot peut être très variable et nécessite encore l'intervention d'un designer pour effectuer des décisions. En effet, certains de ces algorithmes étant NP-complets, l'exploration de l'espace

entier de solution n'est pas possible et le designer est sollicité pour diriger l'exploration avec des contraintes.

Ces nouveaux outils HLS demandent toutefois une connaissance des langages HDL pour créer la première description comportementale à haut niveau, ce qui freine l'adoption de ceux-ci auprès de la communauté des ingénieurs systèmes et des ingénieurs logiciels, qui préfèrent décrire leurs algorithmes à l'aide de langages haut niveau comme C++ ou C.

C'est pourquoi, depuis les deux dernières décennies, une nouvelle génération d'outils voit le jour. Ces outils permettent le passage d'une description fonctionnelle dans un langage haut niveau comme C/C++, SystemC ou encore OpenCL vers une description RTL à l'aide d'un corpus de contraintes. On peut identifier plusieurs raisons à cette évolution du paradigme. La première est, comme cité plus haut, le besoin d'un langage facile à apprendre et peu différent des langages utilisés par les ingénieurs logiciels afin de permettre un gain de productivité ainsi que de faciliter l'adoption d'un tel outil par une entreprise. La seconde, et peut-être la plus importante, est l'apparition de processeurs de plus en plus puissants, créant un nouveau domaine d'applications dans la création de systèmes informatiques : le codéveloppement logiciel/matériel [12] (*Hardware/Software codesign*). L'apparition de nouveaux processeurs permettant d'exporter une grande partie des fonctionnalités d'un système du domaine matériel au domaine logiciel crée alors deux chemins de développement parallèles, la partition matérielle et la partition logicielle. Un besoin d'uniformité dans la manière de décrire les parties logicielles et matérielles se fait donc sentir et la synthèse haut niveau paraît alors la solution de choix afin de partir d'une description fonctionnelle semblable pour tous les éléments (qu'ils soient matériels ou logiciels) pour ensuite développer automatiquement les descriptions matérielles des éléments estimés critiques.

### **1.3 Le niveau « système électronique » (ESL)**

le terme ESL apparaît aux alentours des années 2000 [13] et est défini de nombreuses manières, mais chacune de ces définitions gravite autour de la même idée : une méthodologie de développement de systèmes électroniques à haut niveau d'abstraction. Les auteurs proposent une définition :

L'utilisation appropriée d'abstraction dans le but d'augmenter la compréhension d'un système, et d'améliorer les chances d'une implémentation réussie des fonctionnalités de manière rentable, tout en respectant les contraintes nécessaires. (Martin, Bailey et Piziali, 2010, p.3)

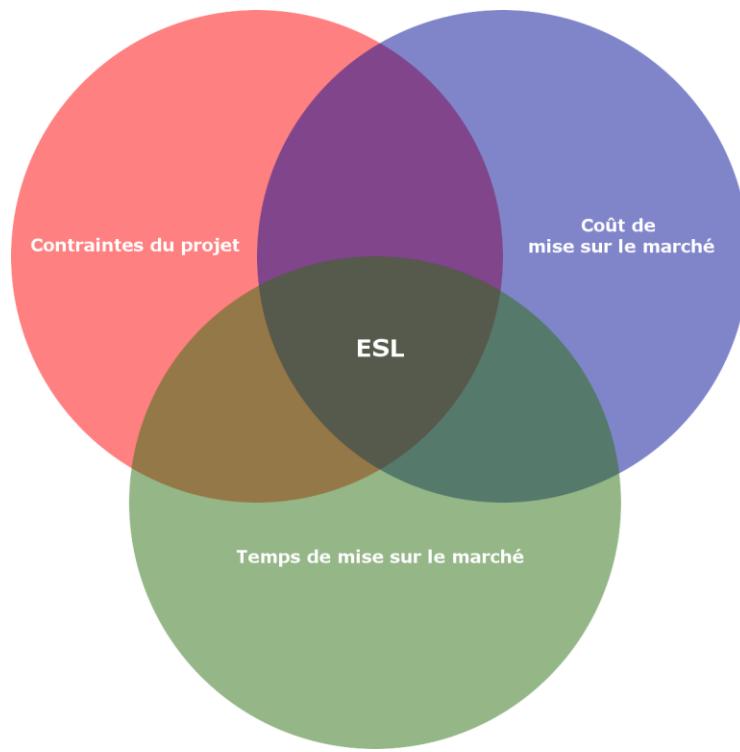

Ainsi, l'ESL est une méthodologie qui formalise la création de systèmes électroniques en prenant en compte les différents enjeux du projet, comme représenté sur la figure 1-3.1. De plus, cette définition implique que le système en question pourra être composé d'éléments logiciels comme matériels (par le biais de l'utilisation du terme « fonctionnalité » qui ne fait pas de postulats sur le type d'implémentation). Enfin, cette définition met en évidence le besoin d'abstraction pour parvenir à ces objectifs.

Figure 1.3-1 : Les enjeux d'un projet de création de systèmes électroniques

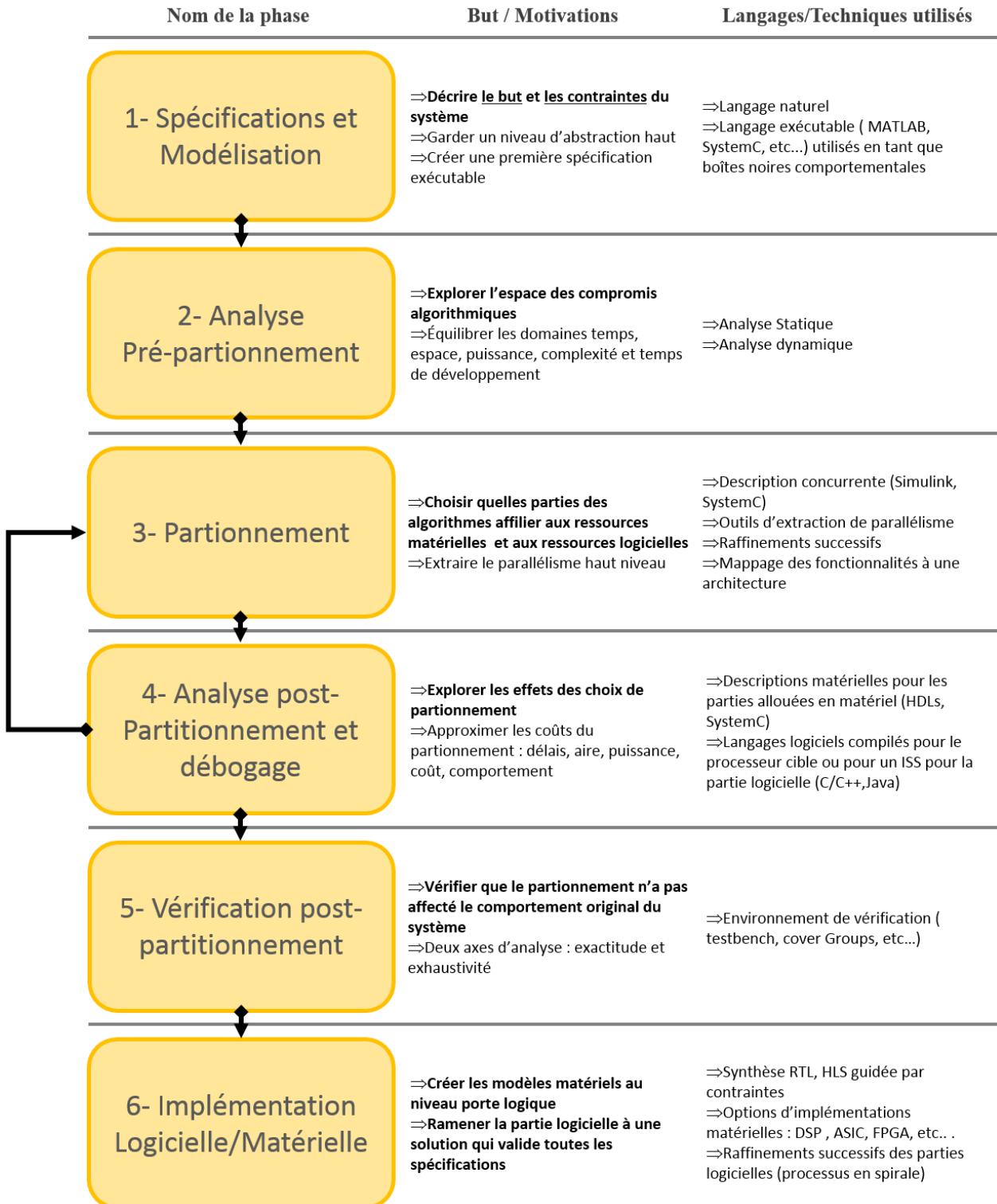

Le but de cette approche est donc de permettre d'accélérer le processus de développement d'un système électronique en travaillant à haut niveau d'abstraction afin de pouvoir valider les étapes de développement plus rapidement et de procéder à des vérifications incrémentales des fonctionnalités. Le flot ESL peut être décomposé en six grandes étapes résumées dans la figure 1.3-2. La première étape traite de la création des spécifications nécessaires à la création du système

électronique. Durant cette étape, les spécifications pourront être écrites dans un langage naturel (description, cahier des charges, etc.) ou dans un langage exécutable sous forme de boîtes opaques. Pour cette étape, une des motivations principales est l'abstraction. En effet, il est important de maintenir un niveau d'abstraction très haut afin de ne pas supposer l'implémentation, d'où l'utilisation d'un modèle descriptif ou boîte noire. Il faut bien comprendre qu'une segmentation du système en sous-systèmes est déjà à l'œuvre dans cette première phase. Il est important de garder à l'esprit ce constat, car si l'équipe de développement souhaite par la suite réutiliser des blocs déjà construits ou bien des Propriétés Intellectuelles (IP), il doit prévoir d'en prendre compte dans sa phase de spécifications.

La seconde phase, l'analyse de prépartitionnement, consiste en une première exploration de l'espace de solutions. Cette exploration est purement algorithmique et va permettre de dresser un tableau préliminaire des compromis possibles entre les différents domaines d'exploration de la conception de systèmes embarqués : temps, taille, puissance, complexité et temps de mise sur le marché. En effet, certains algorithmes sont par nature plus parallèles que d'autres, tandis que certains consomment plus de mémoire pour mener à bien leurs opérations. Afin d'analyser ces compromis, plusieurs outils peuvent être utilisés, notamment des outils d'analyse dynamique comme la bibliothèque Valgrind [14], qui permet d'obtenir des informations sur l'exécution de la spécification comme le nombre d'invocations de chaque fonction, le nombre de fils d'exécution, les dépendances ainsi que les accès en lecture/écriture et le nombre de fautes de caches. Ces informations sont ensuite utilisées pour profiler l'algorithme sélectionné. Des outils d'analyse statique peuvent aussi être utilisés comme l'analyseur ASTRÉE [15], qui permet d'assurer la validité d'un algorithme dans tous les cas d'utilisation à la compilation, et ce, pour des programmes complexes. À l'issue de cette phase, un premier niveau d'abstraction de l'implémentation est levé par le choix des algorithmes.

La troisième phase, le partitionnement, est une des phases les plus critiques du flot ESL. En effet, c'est lors de cette phase que nous décidons comment allouer les ressources matérielles disponibles (processeur, coprocesseur, FPGA) aux différentes parties de la spécification. Cette phase peut être décomposée en sous-phases :

Figure 1.3-2 : Flot ESL

- Décomposition des fonctions : Cette première étape vise à décomposer les fonctionnalités en blocs afin de faire apparaître un parallélisme d'application. Une des méthodes pour

parvenir à ce résultat est l'utilisation d'outils automatiques d'extraction de parallélisme à partir d'un code séquentiel. Ces outils doivent être en mesure d'exposer les dépendances de données afin de proposer des choix de parallélisation cohérents. C'est le cas de Pareon [16], qui est un outil d'analyse dynamique permettant d'exposer le parallélisme de boucle dans un contexte d'applications multitâches (*multithreaded*).

- Description de l'architecture : Afin de pouvoir effectuer une allocation à haut niveau d'abstraction, il est nécessaire d'avoir une description de l'architecture ciblée sous forme de blocs. Ces blocs représentent des éléments haut niveau du système (FPGA, GPU, DSP, bus, mémoire). Le langage de description et d'analyse architecturale (AADL) permet la modélisation de ce genre de système à plus ou moins haut niveau d'abstraction et peut être utilisé en tant que cadre de travail pour des méthodologies du haut vers le bas (*top-down*) [17].

- Partitionnement : Une fois les fonctions décomposées et l'architecture définie à haut niveau, on peut passer à l'allocation des fonctions à des éléments de l'architecture. Cette étape peut être appréhendée de deux manières. La première est d'utiliser un langage permettant un raffinement itératif de la solution fonctionnelle vers la solution finale. Le raffinement aura pour but de préciser les minutages de communication et de calcul. Le langage SystemC illustre parfaitement cette catégorie de solutions avec son système de modules et d'interfaces de communications permettant de créer un modèle fonctionnel sans traces de minutage, puis de le raffiner élément par élément tout en surveillant le respect de la fonctionnalité. La deuxième manière est d'utiliser un langage ou une plateforme permettant le mappage des fonctionnalités aux éléments architecturaux de manière explicite. Par exemple, Space Studio [18] est une plateforme utilisant un sous-ensemble de SystemC afin de créer une description des fonctionnalités sous forme de modules. Ces modules communiquent ensuite à l'aide de simples fonctions d'envois et de réceptions et peuvent être associés à une architecture matérielle définie par l'utilisateur (comprenant FPGA et GPU). La gestion des communications est entièrement prise en charge par l'environnement et les minutages peuvent être raffinés à l'aide de fonctions permettant d'ajouter des délais d'exécution aux modules matériels.

Au cours de la phase d'Analyse Post-Partitionnement, les modèles développés au cours de l'étape précédente sont raffinés pour coïncider avec les choix de partitionnement. Ainsi, les éléments associés à la partie logicielle sont compilés pour l'architecture du processeur ou bien sont exécutés sur des machines virtuelles émulant le comportement du processeur cible, par exemple QEMU [19], une machine virtuelle qui permet de faire fonctionner différents systèmes d'exploitation depuis un autre système d'exploitation (Windows, Linux). De plus, QEMU permet d'émuler sur sa machine virtuelle plusieurs architectures de processeurs différentes (x86, ARM, SPARC). La partie matérielle est décrite dans un langage de description matérielle (comme SystemC, VHDL ou encore System Verilog). Cette description peut être effectuée à la main par des ingénieurs ou bien automatisée dans une certaine mesure par des outils HLS. Une fois le raffinement effectué, il est possible de procéder à l'analyse proprement dite. On va chercher à préciser les approximations faites lors de la phase deux grâce aux informations supplémentaires apportées par le partitionnement. Des outils d'analyse du système modelé doivent être utilisés pour déterminer les performances des modules matériels, des modules logiciels, et des interfaces de communications les liant. Comme dans la seconde phase, les préoccupations majeures de cette analyse sont les aspects temps, taille, puissance, complexité. Cette phase peut être répétée conjointement avec la phase trois jusqu'à obtenir une solution acceptable. Ce cycle est appelé Exploration de l'espace de design ou exploration architecturale.

Le but de la cinquième phase, la vérification post-partitionnement, est de s'assurer que les spécifications comportementales créées lors de la première phase sont encore respectées à la suite du partitionnement de la solution. Afin de pouvoir créer une routine de vérification qui sera valide du plus haut niveau d'abstraction jusqu'au plus bas, il est nécessaire de planifier celle-ci sous la forme d'un plan de vérification. Ce plan doit permettre, au cours de raffinements successifs, de passer d'un ensemble de contraintes données par la spécification à un ensemble de scénarios de test de couverture. Une fois le plan de vérification effectué, on utilise un environnement de test (formel ou dynamique). System Verilog [20] est un bon exemple d'environnement de test dynamique. Il permet la création de bancs d'essai qui fournissent des stimuli au design testé. La réponse à ces stimuli est enregistrée dans un tableau des scores. Il est de plus possible de définir des assertions, conditions qui doivent rester valides tout au long de l'exécution du code. Ces résultats sont ensuite analysés par les ingénieurs pour s'assurer que le code a été testé de la manière la plus complète possible ainsi que pour s'assurer qu'aucun cas ne cause d'erreur.

Lors de la dernière phase, l'implémentation matérielle/logicielle, les éléments matériels doivent être définis jusqu'au niveau porte logique afin de pouvoir réaliser les masques pour la gravure des puces dans le cas d'un circuit intégré pour application spécifique (ASIC). Pour les autres supports matériels, d'autres types de description peuvent être nécessaires (comme un *bitstream*, dans le cas d'une implémentation sur FPGA). Les processus d'automatisation du design électronique permettent de s'exempter de la définition au niveau porte logique en utilisant des outils de synthèse niveau transfert registre (RTL synthesis) ou bien en synthétisant directement des modèles comportementaux à l'aide des techniques de synthèse haut niveau. La phase d'implémentation logicielle quant à elle, a pour but de générer tous les artefacts logiciels nécessaires au bon fonctionnement du système. Dans le cadre du flot ESL complet, une grande partie de ce travail a déjà été effectuée avec les raffinements successifs de la partie algorithmique. Il ne reste qu'à créer la logique d'interfaçage avec le reste des éléments du système et l'utilisateur. Une démarche classique de développement logiciel peut être utilisée (flot en cascade ou en spirale).

Il est important de prendre en considération que le flot présenté ici représente le flot idéal du développement ESL. Dans la réalité, les solutions qui proposent un flot ESL peuvent n'implémenter qu'une partie du flot discuté ici. De plus, l'ordre du flot peut être altéré par plusieurs facteurs, comme, par exemple, l'utilisation d'une plateforme prédéfinie par les spécifications ou bien l'obligation d'utiliser une IP particulière. Enfin, dans ce flot, chacune des étapes est censée se succéder (excepté pour les étapes 3 et 4 qui peuvent s'alterner), mais dans la réalité, il est parfois nécessaire de reprendre une étape précédente.

Par exemple, l'outil présenté dans [21] remplit entièrement les fonctionnalités attendues de l'étape quatre de la méthodologie ESL présentée ci-dessus. Cet outil basé sur une approche de design axé plateforme (PBD), permet de faire des estimations de minutages et de puissance à haut niveau d'abstraction d'un système hétérogène complet. Les éléments fonctionnels sont spécifiés sous forme de code SystemC et interconnectés par le standard TLM2 (modèle au niveau transactionnel). Une fois un partitionnement de la spécification effectué, chaque élément, selon qu'il soit matériel, logiciel ou bien privé (IP) fait l'objet d'une analyse dynamique qui permet une rétroannotation dans le code fonctionnel des informations de minutage et de puissance. Le code destiné au logiciel est compilé pour le processeur cible puis fait l'objet d'une analyse bas niveau des délais et performance. Chacune des instructions assembleur est ensuite associée aux lignes du code source et une annotation est ajoutée dans le code SystemC afin de simuler avec précision ces données dans

le cadre du système complet. Le code matériel personnalisé est quant à lui analysé à l'aide de techniques de synthèse haut niveau. Le code source est transformé en graphe de flot-contrôle de données (CFDG), puis subit les transformations habituelles d'un flot HLS (ordonnancement, allocation et mappage) afin de donner une description RTL. Puisque la phase HLS a modifié en profondeur l'agencement du code source, il n'est pas possible de rétroannoter le code source, mais une version C++ du code RTL avec les informations de minutage et de puissance est générée et vient remplacer le code source lors de la simulation. Enfin, les blocs privés étant des boîtes noires, il n'est pas possible d'accéder directement aux informations de puissance (les informations de minutage étant généralement fournies par le constructeur). Pour remédier à cela, les auteurs créent un moniteur surveillant les transactions de l'IP avec le reste du système et génèrent à partir de sa documentation une machine de puissance à états. Chaque état correspond à un scénario d'utilisation de l'IP dont la consommation est connue. Les changements d'état sont dictés par le moniteur et il devient ainsi possible de tracer un graphe de puissance au cours du temps de simulation. Une fois toutes ces analyses terminées, l'outil se montre capable d'exécuter le système virtuel annoté pour obtenir des approximations de puissance et de minutage avec une erreur de 4 % par rapport à la simulation au niveau porte logique avec un facteur de simulation de moins de 200 (simulation 200 fois plus lente que l'exécution du même système réel).

Dans l'article [22], il est présenté une méthodologie qui couvre les phases trois à six du flot ESL. Cette méthodologie tire parti des solutions HLS proposées par Xilinx et permet un prototypage rapide de système embarqué afin de répondre aux contraintes de productivité et de performance. En utilisant les outils Vivado HLS et l'environnement de développement de systèmes embarqués Xilinx EDK, le flot proposé permet d'amener une solution basée sur le langage C jusqu'à une implémentation sur FPGA. Pour faire un parallèle avec le flot ESL, les phases trois et quatre sont assurées par association des éléments partitionnés sur une architecture connue, grâce à l'interface graphique Xilinx Platform Studio, qui permet de visualiser une description matérielle de la plateforme choisie. Les éléments logiciels sont développés en C dans l'environnement de développement logiciel de Xilinx, EDK, et sont ensuite importés sous forme de fichiers ELF. Les éléments matériels sont générés à partir d'un code comportemental C qui est traité par le logiciel de synthèse haut-niveau Vivado HLS. Ce traitement est guidé par des directives exprimant la volonté de l'ingénieur (pipeliner une boucle, dérouler, etc.). Les descriptions matérielles générées sont elles aussi importées dans XPS afin de générer le fichier de configuration final (*bitstream*)

dédié à la programmation du FPGA. Les coûts du partitionnement peuvent alors être calculés à bas niveau en exécutant le système. Une fois un partitionnement satisfaisant atteint, on peut alors passer aux vérifications de post-partitionnement et à l'implémentation finale. Les auteurs ont testé leur méthodologie sur deux algorithmes et obtiennent des accélérations répondant aux contraintes tout en assurant une productivité et une réutilisabilité importante grâce aux techniques de synthèse haut-niveau.

Dans [23], les auteurs présentent une méthodologie ESL basée sur leur propre suite logicielle SpaceStudio. Cet outil permet la spécification du système à haut niveau d'abstraction (ce qui correspond à la phase 1 du flot ESL). La bibliothèque basée sur SystemC et le modèle de communication TLM-2 permettent la description fonctionnelle d'un système sous forme de blocs appelés modules. Lors de la phase de partitionnement (phase 3), il est possible d'associer ces modules à des ressources matérielles, auquel cas ces blocs sont alors passés dans un outil de synthèse haut niveau, HLS Vivado, permettant de recibler le code SystemC vers une description matérielle pour FPGA (phase 6). Les modules logiciels sont quant à eux compilés pour le processeur choisi lors de la phase de description de l'architecture (processeur dur ou présynthétisé, avec ou sans système d'exploitation). Le système complet peut alors être exporté vers une plateforme d'architecture matérielle (XPS) à partir de laquelle le fichier de configuration menant à l'implémentation finale sur FPGA peut être généré. Des outils de vérification intermédiaires sont mis à disposition dans la suite SpaceStudio permettant la simulation fonctionnelle (phase 1), puis la cosimulation matérielle/logicielle (phase 4) du système complet afin d'obtenir les premières estimations de taille, performance et puissance à différents moments du processus de développement.

La suite logicielle Intel Cofluent Studio [24] propose elle aussi une méthodologie d'exploration haut niveau de la fonctionnalité et de l'architecture d'un système électronique. L'outil permet de décrire le système grâce à une interface graphique. Les modules, qu'ils représentent la plateforme ou les fonctionnalités, sont représentés sous la forme de diagrammes blocs interconnectés par des canaux et synchronisés par événements. Chacun de ces blocs peut alors posséder des propriétés comme le temps d'exécution ou la puissance consommée. De plus, les fonctionnalités peuvent être implémentées sous la forme de code C/C++ afin de pouvoir observer le fonctionnement du système lors de la simulation. Cofluent est de plus capable d'effectuer des simulations du système à deux niveaux d'abstraction. Le premier niveau est l'abstraction fonctionnelle pure, où l'architecture

cible n'est pas prise en compte et où il est possible de s'assurer du bon fonctionnement du système. Le second est la simulation niveau plateforme, où la vue plateforme est mappée à la vue fonctionnelle du système. Les estimations de cette simulation peuvent être recalculées de nombreuses fois en faisant varier les blocs fonctionnels et architecturaux afin de procéder à une véritable exploration architecturale avant de s'aventurer plus loin dans la conception du système et ainsi éviter les écueils lors de l'implémentation de fonctionnalités. Enfin, le logiciel permet de générer une description du système à haut niveau d'abstraction (TLM-2) en SystemC. La méthodologie Cofluent est basée sur un flot intitulé MCSE [25] qui se déroule en 4 étapes : Spécification, Description fonctionnelle, Spécification de l'implémentation et Réalisation. De ces 4 étapes, Cofluent en implémente deux, la description fonctionnelle et la spécification de l'implémentation. Il est facile de rapporter ces deux étapes aux étapes deux, trois et quatre de la méthodologie ESL présentée plus haut. L'outil ne permet toutefois pas de passer à l'implémentation.

## 1.4 Problématique

Cette brève revue de littérature nous a permis de dégager plusieurs évolutions importantes du domaine de la création de systèmes embarqués.

Tout d'abord, la complexité croissante des systèmes électroniques, que ce soit de par le nombre de plus en plus important de composants à intégrer ou bien de par l'hétérogénéité grandissante des systèmes, qui peuvent maintenant être constitués de plusieurs processeurs, coprocesseurs, puces dédiées ou encore FPGA, a créé un besoin d'abstraction et d'automatisation dans le processus de développement. Ce besoin s'est traduit par des créations successives de représentations de plus en plus abstraites : RTL, VHDL, SystemC, etc. L'adoption de ces représentations a engendré des outils d'automatisation du développement afin de raffiner ces représentations haut niveau : synthèse RTL et HLS. Ces langages et techniques ont permis l'amélioration de la productivité des équipes de développement. Toutefois, d'autres facteurs sont à prendre en compte.

En effet, afin d'améliorer l'efficacité du développement des systèmes embarqués, un besoin de standardisation s'est aussi beaucoup fait ressentir. Dans un premier temps, la standardisation des représentations a permis un essor de la réutilisabilité des descriptions matérielles (grâce aux deux normes HDL : VHDL et Verilog) sous la forme de composants protégés appelés IP. Depuis,

certaines entreprises se sont spécialisées dans la vente d'IP et l'utilisation de tels blocs dans un design est monnaie courante, ce qui permet aux équipes de se concentrer sur les quelques éléments du design qui seront spécialement développés pour l'application, réduisant les coûts et les temps de mise sur le marché. Dans un second temps, le domaine du développement de systèmes électroniques a aussi été marqué par le manque de méthodes claires afin d'amener un projet du cahier des charges jusqu'à l'implémentation finale. Un autre segment de la recherche dans le domaine a donc été dirigé vers la création de méthodologies visant à créer un cadre de travail. On a alors vu l'apparition de méthodes « du haut vers le bas », « du bas vers le haut », orientées plateforme, etc. Parmi ces méthodes, le flot ESL semble l'un des plus complets et englobe les concepts énoncés dans la plupart des autres flots. Cela est dû au fait que l'ESL représente un cadre assez « relâché » et constitue plus un guide de bonnes pratiques qu'une méthode à suivre à la lettre. C'est pour cela que beaucoup d'outils privés actuels peuvent être comparés au flot ESL. Comme cité dans le paragraphe précédent, le besoin d'abstraction croissant a aussi eu un impact sur les méthodologies développées, qui se définissent maintenant comme une série de raffinements visant à réduire de manière incrémentale le niveau d'abstraction d'un modèle. C'est à cause de nouveau paradigme de développement qu'une autre problématique se développe.

La méthodologie ESL, contrairement à une méthodologie classique de développement logiciel, le développement en cascade, ne peut se permettre d'attendre la moitié du cycle de développement avant de passer dans la phase de vérification. De ce fait, un troisième domaine important de la recherche en conception de systèmes embarqués apparaît, celui de la vérification. En effet, le flot ESL entrecoupe ses phases de raffinement de phases de vérification en gardant en tête les préoccupations principales que sont le coût, les performances, la surface, la puissance, et le temps de mise sur le marché. Il est donc important de développer des outils permettant de générer des estimations de ces paramètres à tous les stades de la conception afin de guider l'exploration. Les outils dynamiques impliquent des environnements de simulation à différents niveaux d'abstraction ainsi que des suites d'analyse, ce que proposent des outils comme SpaceStudio, HLS Vivado, ou encore Cofluent. Le fait d'introduire la vérification à haut niveau a donc deux avantages : réduire l'espace d'exploration de manière incrémentale et repérer les impasses qui pourraient mener à l'échec d'un projet le plus tôt possible.

La plupart des solutions proposées par la recherche répondent à des parties de ces problèmes, toutefois, au meilleur de nos connaissances, il n'existe aucune méthode qui implémente l'intégralité

du flot ESL dans le domaine du système embarqué. C'est pourquoi le but de ce travail de recherche est d'étendre un flot de conception déjà existant afin de répondre à l'intégralité des étapes de la méthodologie ESL. La contribution principale de ce travail est la création d'un outil logiciel permettant le passage d'un code séquentiel C vers un format modulaire propice à l'exploration des compromis de partitionnements.

## 1.5 Objectifs

Afin de répondre à la problématique énoncée ci-dessus, le travail a été décomposé en plusieurs objectifs ou axes de développement :

- Analyser un ensemble de logiciels, privés ou non, disponibles sur le marché afin de construire le flot ESL.

- Analyser les parties du flot encore à concevoir et réaliser une solution logicielle capable de lier ensemble les différentes parties du flot déjà conçues ensemble.

- Permettre un accès facilité à un flot de codesign logiciel/matériel en proposant un point d'entrée codé en C et des outils pour guider la traduction vers la bibliothèque orientée système SystemC.

- Tester l'efficacité du flot de conception en le mettant à l'épreuve sur une application.

Puisque la contribution majeure de cette maîtrise est le développement d'un outil logiciel, il est important de définir des sous-objectifs liés à cette tâche. La conception logicielle portera sur la création d'un traducteur permettant la transformation d'une spécification logicielle vers une spécification propice au partitionnement. Cet outil devra répondre à ces objectifs de conception :

- Permettre une traduction assistée du code.

- Présenter une interface claire à l'utilisateur.

- Produire un code de sortie clair.

- Ne pas modifier la fonctionnalité du code source.

- Imposer un ensemble le plus restreint possible de contraintes sur le format du code d'entrée.

## 1.6 Résumé des contributions

Afin de composer ce flot de conception, plusieurs étapes auront été nécessaires :

- Premièrement, une analyse en profondeur d'ouvrages de référence a été effectuée. Cette analyse a permis de créer une vue d'ensemble du domaine de la conception de systèmes embarqués et a aidé à comprendre les enjeux du domaine afin d'affiner la problématique et les objectifs de cette maîtrise.

- Dans un second temps, une recherche documentaire a permis d'examiner les solutions propriétaires disponibles sur le marché ainsi que celles offertes à Polytechnique Montréal. Suite à cette recherche, une sélection d'outils a été effectuée afin de composer le flot ESL.

- Lors d'une troisième étape, une solution logicielle a été développée afin de compléter le flot ESL proposé. Cette solution permet la transition d'un code C fonctionnel vers une architecture modulaire propice à l'exploration architecturale.

- Dans une dernière étape, la méthodologie complète a été mise à l'épreuve sur un exemple de traitement d'image : un filtre de Canny (détecteur de contours).

## 1.7 Organisation du mémoire

L'organisation de la suite de ce mémoire est présentée dans cette section.

Dans le chapitre 2, un survol du flot vous sera présenté : les différents outils choisis et leur intégration dans le flot ESL présenté dans l'introduction. Une fois ce premier survol effectué, une description plus détaillée de chaque étape du flot sera effectuée.

Le chapitre 3 expliquera le développement et le fonctionnement du logiciel conçu lors de ce projet de maîtrise et nommé dans ce qui suit *C2Space*, permettant la jonction entre les analyses menées par l'outil Pareon et le code d'entrée de SpaceStudio.

Un test du flot complet sera détaillé lors du chapitre 4 afin d'évaluer la validité du flot

Le test donnera lieu à une discussion dans le chapitre 5 afin de présenter l'intérêt des résultats et donner quelques pistes d'amélioration de la solution.

## CHAPITRE 2 PRÉSENTATION DU FLOT

### 2.1 Présentation générale

La solution présentée dans ce mémoire repose sur un flot de conception basé sur le flot ESL présenté en introduction. Afin de répondre aux différentes étapes de ce flot théorique, nous utilisons différentes solutions.

La figure 2-1-1 représente comment ces différentes solutions viennent s'intégrer au flot ESL.

Le point d'entrée de notre méthodologie est une application logicielle décrite en C. L'intérêt de choisir un tel point d'entrée est de permettre aux utilisateurs du flot d'accélérer rapidement une application purement logicielle en faisant passer certains de ses noyaux de calculs dans le domaine matériel. Bien que le but soit de permettre un passage le plus rapide possible d'une spécification C à un modèle de codéveloppement logiciel/matériel, nous avons décidé d'imposer un ensemble de contraintes au code C afin de rendre possible la traduction du code par l'outil C2Space. Ainsi, certaines constructions propres au langage C doivent être enlevées du code. Ces conditions seront décrites en détail dans la troisième section de ce mémoire. Afin de guider l'exploration du design, le code C doit être accompagné d'un ensemble de contraintes propres au domaine des systèmes embarqués (consommation de puissance, rapidité d'exécution, temps de développement et quantité de ressources utilisées). Ces contraintes permettront tout au long du flot de vérifier que les solutions retenues respectent bien l'intention originale de développement.

Cette démarche vient s'inscrire dans la phase un du flot ESL. Le code C représente une spécification exécutable fonctionnelle du système que nous voulons implémenter. Cette représentation est, comme le recommande la méthodologie, la plus exempte possible d'artefacts d'implémentation, en cela qu'elle ne fait encore aucun postulat sur la manière dont l'application va être scindée entre les ressources matérielles et logicielles. Elle permet de s'assurer de la fonctionnalité du système. On notera toutefois quelques concessions faites à la méthodologie ESL, qui préconise normalement une première étape la plus dénuée possible d'artefacts logiciels, de par la modification du code pour permettre l'utilisation de C2Space ainsi que par l'utilisation d'une spécification fonctionnelle, qui représente une première implémentation algorithmique.

Figure 2.1-1 : Comparaison entre le flot ESL et le flot présenté

Dans la suite du flot, nous amenons notre spécification C dans l’outil développé par Vector Fabrics, Pareon Profile [16] afin d’effectuer une première analyse dynamique de l’application. Pareon fournit un compilateur instrumentant le code et permettant d’effectuer une analyse des dépendances de données lors de l’exécution en scrutant les accès mémoire. Toutes les informations récupérées lors de l’exécution sont alors compilées dans un fichier lisible dans l’interface graphique de Pareon. Ce rapport permet au développeur de naviguer dans l’arbre d’exécution du code et de rechercher les opportunités de parallélisme des différentes boucles composant le système. Si une boucle présente une opportunité de parallélisme, le logiciel calcule l’accélération attendue basée sur une exécution multicœur et la loi d’Amdahl. Le but de cette analyse est de guider la segmentation du code C séquentiel en partant du principe qu’une section du code présentant une opportunité d’accélération sur un processeur multicœur présentera aussi une grande opportunité d’accélération en tant que coprocesseur matériel.

Cette étape d’exploration de l’algorithme coïncide parfaitement avec la phase 2 de la méthodologie ESL, car elle permet d’éliminer une partie de l’espace de solutions sans trop compromettre l’abstraction de la spécification. Des modifications peuvent être rajoutées au code C afin de découvrir plus de parallélisme ou il peut être décidé de changer complètement d’algorithme si aucune opportunité de parallélisme n’est découverte (sans sacrifier la fonctionnalité attendue par le cahier des charges). À l’issue de cette phase, nous obtenons une implémentation algorithmique présentant des opportunités de parallélisme, qui vont servir à guider C2Space.

C2Space ne fait pas à proprement parler partie du flot ESL, mais sert à lier les différents éléments du flot. Cela répond à plusieurs objectifs. Tout d’abord, cela permet de lier deux outils qui n’ont aucune interface commune (SpaceStudio et Pareon Profile) sans intervention majeure du développeur. De plus, l’utilisation de cet outil permet de réaliser un des objectifs de ce mémoire qui est de rendre accessible le design de systèmes embarqués à des ingénieurs ayant peu d’expérience dans le domaine matériel. En effet, la bibliothèque C++ utilisée dans SpaceStudio est dérivée de SystemC, qui est une bibliothèque orientée système et qui introduit des notions telles que les modules et les communications et synchronisations intermodules. L’idée derrière C2Space est de traduire l’algorithme séquentiel précédemment analysé en un ensemble de modules SpaceStudio et de générer toutes les communications nécessaires entre le logiciel et le matériel afin de conserver la fonctionnalité originale du code séquentiel. C2Space a été développé en C++ et utilise à sa base la bibliothèque Clang [26], une façade (*frontend*) C++ du compilateur LLVM, afin

d'effectuer une analyse statique du code source. Au cours de l'analyse, l'utilisateur doit fournir certaines informations afin de guider le découpage du code source en modules (ces informations découlent des résultats de l'analyse de Pareon). Une fois les informations compilées, C2Space procède alors à une réécriture intelligente du code. Le résultat de cette phase consiste en un ensemble de fichiers contenant les modules, des fichiers supports ainsi qu'un script python permettant la génération du projet sous SpaceStudio.

Dans la suite du flot de développement, nous reprenons le résultat généré par C2Space pour procéder à l'exploration architecturale du design. Suite à la phase précédente, le code source est maintenant séparé en modules SpaceLib (la bibliothèque basée sur SystemC de SpaceStudio). Le flot interne de SpaceStudio suit alors son cours. SpaceStudio cible, à l'heure actuelle, les plateformes basées sur les FPGA Xilinx. Ainsi, le flot classique est axé sur le partitionnement des modules entre les différentes ressources présentes sur les plateformes.

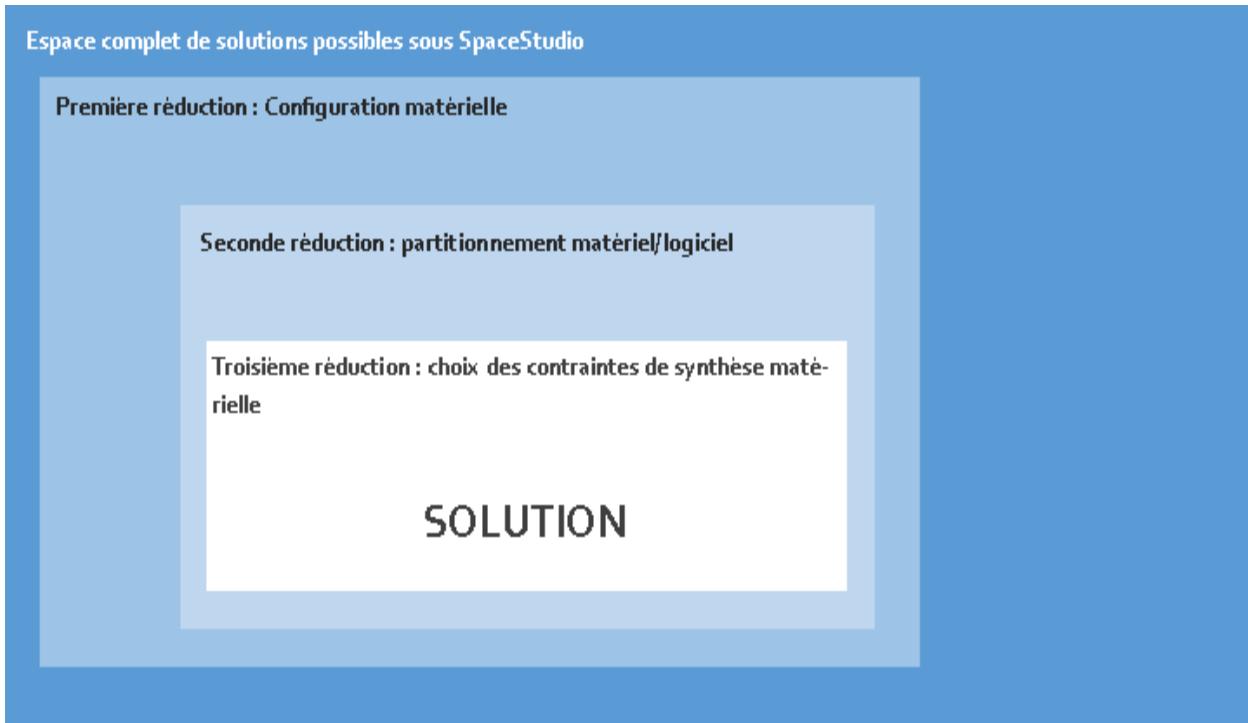

Dans notre flot, il est possible d'influencer trois catégories de paramètres afin de générer un partitionnement. La première catégorie est la configuration matérielle. Il est possible de définir quels éléments nous voulons voir présents dans notre configuration. Ainsi, nous pouvons spécifier des processeurs (ARM, microBlaze), mais aussi des IP prédéfinies (comme des minuteries, des banques mémoires). La seconde catégorie est bien évidemment le partitionnement lui-même, c'est-à-dire l'allocation des ressources matérielles aux blocs applicatifs. Enfin, la troisième façon d'influencer le design est le guidage de la synthèse haut niveau des modules matériels. Selon les contraintes de synthèse, les modules matériels n'exhiberont pas les mêmes propriétés en termes d'espace utilisé, de puissance et de performance. L'approche d'exploration sélectionnée est basée sur une réduction progressive de la complexité de l'espace de solutions tel qu'illustre à la figure 2.1-2.

Une fois le partitionnement effectué, il est possible de simuler le fonctionnement du système à haut niveau pour vérifier le respect des fonctionnalités. La simulation donne aussi accès à beaucoup d'informations comme le taux d'utilisation des processeurs disponibles, l'utilisation des bus et le temps pris par les communications intermodules. Les informations concernant l'utilisation des ressources du FPGA (pour les modules destinés à devenir des coprocesseurs) deviennent disponibles par la suite du flot et peuvent être réintégrées aux diagnostics fournis par SpaceStudio pour avoir un premier aperçu global des compromis du partitionnement.

Figure 2.1-2 : Réduction de l'espace de solution dans notre méthodologie

Ces informations sont générées par HLS Vivado, après que celui-ci ait procédé à l'optimisation des modules par le biais son interface. SpaceStudio permet l'importation des modules destinés à être spécifiés pour le FPGA directement dans HLS Vivado. Une fois cette transition faite, il est possible de donner des consignes d'optimisation au synthétiseur afin de générer un artefact matériel plus ou moins imposant. L'utilisation de ces contraintes permet d'équilibrer performance, espace et puissance requise afin de rencontrer les contraintes de la spécification. Les constats effectués lors de l'analyse algorithmique sont utilisés ici pour guider facilement le développeur vers l'optimisation des boucles ou nids de boucles possédant un fort potentiel de déroulement et/ou de pipelinage.

Si les résultats obtenus ne sont pas suffisants pour rencontrer les contraintes, l'exploration architecturale continue. Il est alors possible de créer une liste de configurations afin de créer différents compromis en termes de vitesse, coût, surface, puissance.

Ces phases d'exploration menées par SpaceStudio représentent les phases trois à cinq du flot de développement ESL. Durant ces étapes, nous sélectionnons un partitionnement de nos éléments logiciels (les modules) vers nos ressources matérielles (processeurs ou coprocesseurs). Une phase d'exploration des différentes combinaisons dans un simulateur nous permet d'obtenir rapidement

un espace de compromis architecturaux. Il est important de noter qu'une partie de l'abstraction de la solution est abandonnée dès lors que nous utilisons SpaceStudio, car le choix de ce logiciel limite le nombre de plateformes matérielles que nous pouvons sélectionner (en l'occurrence des plateformes basées sur les FPGAs de Xilinx comme la Zedboard [27] de Avnet). Toutefois, la flexibilité des FPGAs permet d'obtenir des résultats satisfaisants et le développement basé sur une plateforme permet de réduire les temps de mise sur le marché d'une solution.

Une fois cette phase d'exploration terminée, et qu'une solution répondant au cahier des charges a été validée en simulation, on peut passer à la dernière phase du flot : l'implémentation. Le passage du projet SpaceStudio vers une implémentation est géré en deux parties distinctes. Les éléments logiciels de la configuration sont compilés pour le processeur ciblé et sont prêts à être utilisés. La logique de communication, les pilotes (*drivers*) et le Paquetage de Support de Plateforme (BSP) sont générés automatiquement par SpaceStudio. Les éléments matériels quant à eux passent à nouveau dans la suite de synthèse haut-niveau Vivado, en spécifiant les contraintes qui avaient été précédemment sélectionnées. Les descriptions matérielles de ces éléments sont alors générées et intégrées en tant qu'IP dans la suite de visualisation de plateforme XPS. Une fois la plateforme entièrement générée, le fichier de configuration de la plateforme (*bitstream*) est créé et l'intégralité du système est unifié dans l'environnement de développement EDK. Il est alors possible de passer aux tests de l'implémentation en téléversant le fichier de configuration du FPGA ainsi que les différents fichiers applicatifs (drivers, modules logiciels, etc.) dans la carte de développement. On peut alors déboguer le système en conditions réelles à l'aide des outils de débogage présents dans l'environnement de développement. Si le flot a été bien respecté, cette étape de vérification ne devrait pas être trop chronophage, car la majorité des problèmes doivent déjà avoir été repérés aux différents niveaux d'abstraction.

Cette dernière étape de vérification clôt notre flot. La situation présentée ici est la situation optimale, dans laquelle tout se passe bien. Toutefois, il est possible que pour certains projets il faille reprendre une étape précédente, si l'exploration se heurte à un mur (non-respect des contraintes). Il peut être nécessaire d'avoir recours à un autre algorithme de base ou encore de raffiner les communications afin de rencontrer les contraintes.

Bien qu'un retour en arrière puisse être requis, ce flot essaye de faire apparaître les problèmes à haut niveau, afin de pouvoir les résoudre lorsque l'abstraction est encore grande, et que les modifications peuvent encore être rapidement implémentées et testées.

## CHAPITRE 3 C2SPACE : UN OUTIL DE TRADUCTION ASSISTÉE

Ce chapitre présente la contribution majeure de ce mémoire, à savoir C2Space, un outil de traduction semi-automatisée de code C, basé sur la bibliothèque Clang, la partie frontale du compilateur source à source (aussi appelé transpilateur) LLVM.