**Titre:** Conception au niveau système de l'application de protocole sans fil

Title: WIMAX

**Auteur:** Fatoumata Lamaranah Bah

Author:

**Date:** 2009

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Bah, F. L. (2009). Conception au niveau système de l'application de protocole sans fil WIMAX [Master's thesis, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/227/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/227/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois, & Gabriela Nicolescu

Advisors:

**Programme:** Génie informatique

Program:

UNIVERSITÉ DE MONTRÉAL

CONCEPTION AU NIVEAU SYSTÈME DE L'APPLICATION DE PROTOCOLE

SANS FIL WIMAX

FATOUMATA LAMARANAH BAH

DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

DÉCEMBRE 2009

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

CONCEPTION AU NIVEAU SYSTÈME DE L'APPLICATION DE PROTOCOLE

SANS FIL WIMAX

présenté par: BAH Fatoumata Lamaranah

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. PIERRE Samuel, Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

Mme. NICOLESCU Gabriela, Doct., membre et codirectrice de recherche

M. BOLAND Jean-François, Ph.D., membre

Je dédie ce mémoire à mes parents pour leur amour et leur soutien indéfectible. Je dédie également ce travail à la mémoire de mon oncle Aliou Badra Diallo décédé en 2007 d'un cancer et qui fut mon répétiteur en Mathématiques et en Physique durant mes études secondaires. Qu'il repose en paix.

## REMERCIEMENTS

Après deux années de recherche, ma maîtrise s'achève fermant ainsi un chapitre de ma vie et m'ouvrant de nouvelles perspectives. Ces deux années ont été pleines de joie, de frustrations, d'espoir. Mais je n'en serais jamais venue au bout sans l'aide de plusieurs personnes que je souhaiterai remercier.

Tout d'abord, un grand merci à mes professeurs Guy Bois et Gabriela Nicolescu qui m'ont permis d'effectuer mes recherches dans un domaine très porteur que sont les Systèmes embarqués et temps réels, merci pour leur patience et compréhension. Merci aux membres du Jury qui ont bien voulu évaluer le travail réalisé.

J'aimerais remercier également toute l'équipe du Circus, l'équipe au sein de laquelle j'ai effectué mes recherches. Je remercie infiniment Marc-André Cantin qui m'a conseillée et guidée tout au long de mon travail. Un grand merci aussi à Laurent, Sébastien LeBeux, Luc, Maxime, Benoît pour l'aide précieuse qu'ils m'ont apportée. Un grand Merci à Bruno Girodias pour toute l'aide qu'il m'a apportée ainsi qu'à Alain. Merci à Nicolas pour son soutien, à mes collègues de bureau Sébastien, Karim ainsi qu'aux autres membres de Circus Lam, Sylvain, Michel pour leurs encouragements.

J'aimerais remercier aussi mes amis, en particulier Maïmouna qui m'a encouragée et soutenue dans les moments difficiles, Ibrahima mon ami de toujours, Kefil, Franklin et enfin Hassatou.

Je ne serai pas celle que je suis sans ma famille, alors je souhaiterais lui rendre hommage à travers ce mémoire. Un grand merci à mes parents, à mes frères Ismaël et Abder-Rahman, à ma cousine Hawa et au reste de ma famille.

## RÉSUMÉ

Communiquer est le principe même de l'homme. Au fil des siècles les modes de communication ont beaucoup évolué passant d'un simple échange vocal entre deux personnes à un échange via des appareils (téléphones, ordinateurs,...) d'où la naissance des systèmes de télécommunication. La technologie sous-jacente tient à l'implantation de réseaux de communication qui sont les noyaux de la communication. C'est ainsi que de nos jours on a des réseaux internet, de téléphonie, de télévision, etc. Avec l'évolution des civilisations et l'expansion démographique, on cherche désormais à minimiser la surface occupée par ces réseaux tout en maintenant la même qualité de service. On assiste ainsi à l'émergence de nouveaux réseaux de communication sans aucune interconnexion filaire.

Le **Wimax** est l'une de ces technologies émergeantes. Grâce à ses techniques de modulation telles que l'OFDM, elle permet une meilleure qualité de service que les réseaux existants. Elle est ainsi utilisée pour de nombreuses applications telles que la communication par vidéo conférence (VoIP), un accès étendu à internet, aux hotspot wifi et aux réseaux cellulaires .

Le problème qui se pose est de savoir comment planter de nouveaux réseaux de façon rapide et efficace tout en respectant les contraintes de coûts et de temps de conception liées au marché.

La réponse à ces problèmes se trouve au niveau des méthodes de conception des systèmes de traitement de signaux complexes et hétérogènes. Les applications de réseau sans fil sont généralement destinées à être implémentées dans des systèmes sur puce (SOC) tels les ASICs ou les FPGAs. Les méthodes classiques de conception d'application de traitement de signal consistent à réaliser d'abord un modèle algorithmique de simulation à partir duquel un modèle bas niveau de simulation est

généré. Ce modèle est par la suite implémenté puis validé. Cela rend la conception très fastidieuse, car le modèle bas niveau est en général difficile à modifier.

La solution privilégiée consiste à travailler à un niveau intermédiaire afin de tester toutes les performances du système avant de générer le modèle bas niveau. Cette solution basée sur l'ESL (electronic system level) consiste à ramener au niveau système (c'est à dire pas sur la puce) la conception afin de gérer à la fois les spécifications et contraintes logicielles et matérielles.

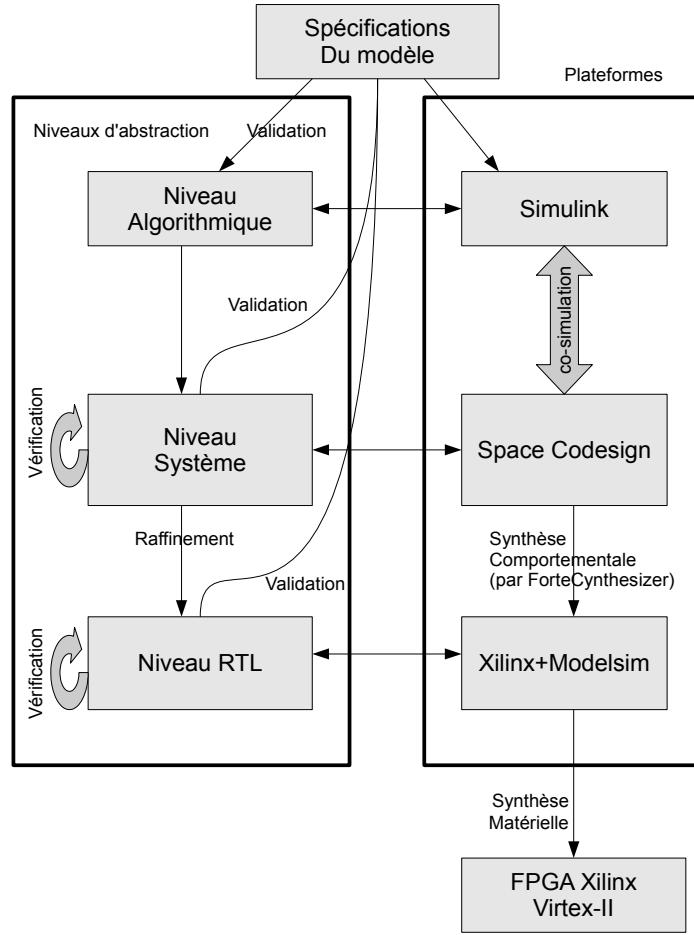

Ainsi un flot de conception efficace serait de partir d'un modèle algorithmique réalisé à l'aide d'outil visuels de simulation qui évaluerait les performances générales du modèles; par la suite ce modèle serait ramené à un niveau système qui se chargerait de l'estimation d'un partitionnement logiciel/matériel adéquat et du choix d'une architecture optimale à réaliser; enfin la conception se terminerait par l'évaluation d'un modèle bas niveau RTL obtenu à partir du modèle système et évaluant les performances spécifiques voulue par le concepteur telles que la taille occupée sur la puce ou la vitesse de transfert des données.

Étant donné ces différents niveaux de conception, un environnement de conception idéal serait une plateforme permettant l'accès à ces trois niveaux sans aucun effort particulier de la part du concepteur.

La plateforme *Space Codesign* réalisée l'équipe du groupe de recherche **Space** offre un environnement de conception au niveau système. À travers des outils de profilage et de simulation, elle permet d'obtenir un partitionnement optimal de l'architecture finale à implémenter sur puce. De plus, grâce à des outils intégrés de génération de code RTL, elle fournit une architecture RTL complète du modèle à implémenter sur un FPGA de *Xilinx* faisant ainsi le lien avec le niveau RTL. La plateforme suit le schéma classique de conception selon l'ESL. A partir des spécifications du système, on définit un modèle de base de l'application. Ensuite à travers la plateforme ESL et ses outils, on parcours différents niveaux d'abstraction de plus en plus précis et bas jusqu'à l'obtention de l'architecture finale sur puce. Les outils permettent

d'automatiser les étapes de création et de modification des modèles tout au long de la conception et permettent également de faire abstraction des détails d'implémentation de l'architecture. De plus grâce aux outils intégrés de raffinement, elle permet de bâtir de façon rapide et efficace une implémentation du système obtenu sur FPGA (système sur puce).

L'objectif de notre travail consiste d'une part , à concevoir à partir d'une plateforme ESL de partitionnement logiciel/matériel une architecture de réseau sans fil c'est à dire la couche physique OFDM de la norme IEEE 802.16 correspondant **Wimax** et de l'autre à l'interfacer avec l'environnement de développement algorithmique *Matlab-Simulink* afin d'obtenir ainsi un flot de conception entier.

Dans ce mémoire, nous présentons le flot de conception complet de la physique OFDM de la norme IEEE 802.16 que nous appelerons **Wimax** pour simplifier. Au cours de ce travail, trois modèles du **Wimax** ont été réalisés: le premier au niveau algorithmique a été fait sous *Matlab-Simulink*, ensuite le second a été réalisé à l'aide de la plateforme *Space Codesign* et pour finir le modèle RTL obtenu par synthèse du second a été analysé et validé après simulation et synthèse sur FPGA de *Xilinx*. De plus une interface entre la plateforme *Space Codesign* et l'environnement *Matlab-Simulink* a été réalisée afin d'intégrer le modèle système au modèle algorithmique pour une comparaison des deux modèles.

## ABSTRACT

Now a days, Wireless systems are everywhere. They had a tremendous growth in recent years. From personnal area networks like bluethooth to local networks like Wifi, most of the communications systems contains wireless systems which have differents networks and users. A major problem of these systems is the interoperability and deployment of wireless networks. This is why a lot of research are made to find solutions and Wimax is one of them. Wimax (wireless interoperability for microwave access) is a metropolitan area network which use different transmission mode for pmp or mesh links to portable access due to OFDM modulation. With the improvement of Wireless technology and because of the tight costs and time-to-market constraints, the main challenge is to get fast and efficient design method. To meet these requirements, a method of conception, ESL is mainly used.

In this report, a design process of the physical layer of the IEEE 802.16 standard with the OFDM modulation using an ESL Eclipse-based platform of software/hardware platform is presented. This ESL environment, with his integrated tools, build embedded applications and architectures by refining the transaction-level communications to some pin and cycle-accurate protocols as well as the generation of synthesizable hardware from the system-level specifications. Those tools automate creation and modification of modules in an ESL design flow and make abstraction of all the implementation details to built an ESL architecture.

The main contribution of this work is the multilevel design on baseband of the PHY-OFDM layer of the IEEE 802.16 standard using an ESL (electronic system Level) environnement of software/hardware partitionning and the use of a multi-system cosimulation technique between the ESL model built with the SpaceStudio platform and a model built on Simulink for validation through cosimulation interfaces of heterogeous systems.

The conception flow of the application is declined on 3 part : the first part is the conception of a Simulink model which is used as a Testbench. The second part which is the core of our work represent the ESL based model. The third and last part is the FPGA implementation of the architecture created by the ESL platform.

This report is organized as follows: Chapter 1 discusses related work, Chapter 2 present the physical OFDM based layer of the IEEE 802.16 standard, Chapter 3 present the implementations of differents models, Chapter 4 discusses the results, the last Chapter present a conclusion of the report.

The results show how an ESL platform can provide an early mock-up of a design to refine it for an FPGA implementation and how it can use a cosimulation method for validation.

## TABLE DES MATIÈRES

|                                                                  |      |

|------------------------------------------------------------------|------|

| DÉDICACE . . . . .                                               | iii  |

| REMERCIEMENTS . . . . .                                          | iv   |

| RÉSUMÉ . . . . .                                                 | v    |

| ABSTRACT . . . . .                                               | viii |

| TABLE DES MATIÈRES . . . . .                                     | x    |

| LISTE DES FIGURES . . . . .                                      | xi   |

| LISTE DES ACRONYMES . . . . .                                    | xii  |

| LISTE DES TABLEAUX . . . . .                                     | xiii |

| LISTE DES ANNEXES . . . . .                                      | xiv  |

| INTRODUCTION . . . . .                                           | 1    |

| CHAPITRE 1 REVUE DE LITTÉRATURE . . . . .                        | 9    |

| 1.1 Conception des DSP : Un exemple, le Wimax . . . . .          | 10   |

| 1.1.1 Des ASICs aux FPGAs . . . . .                              | 10   |

| 1.1.2 Des niveaux d'abstraction de plus en plus hauts . . . . .  | 11   |

| 1.2 L'ESL: un choix de conception plus approprié . . . . .       | 13   |

| 1.2.1 Les sous-niveaux d'abstraction du TLM . . . . .            | 16   |

| 1.2.2 Réutilisation et automatisation de la conception . . . . . | 18   |

| 1.2.3 Méthodologie de Conception dans Space Codesign . . . . .   | 20   |

| 1.2.3.1 Notions de bases : ports, signaux . . . . .              | 20   |

| 1.2.3.2 Librairies de Space Codesign . . . . .                   | 21   |

|                                                                                           |                                                                     |    |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----|

| 1.2.3.3                                                                                   | Exploration architecturale . . . . .                                | 22 |

| 1.2.3.4                                                                                   | Profilage . . . . .                                                 | 24 |

| 1.2.4                                                                                     | Vers un modèle RTL dans EDK . . . . .                               | 25 |

| 1.3                                                                                       | Validation haut niveau : La cosimulation SystemC/Simulink . . . . . | 27 |

| 1.4                                                                                       | Conclusion . . . . .                                                | 31 |

| CHAPITRE 2 ÉTUDE DE LA COUCHE OFDM-PHY . . . . .                                          |                                                                     | 32 |

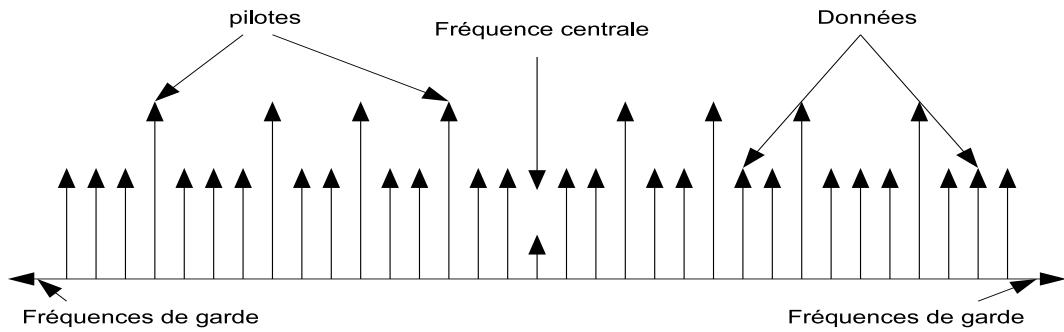

| 2.1                                                                                       | Conceptes de base . . . . .                                         | 33 |

| 2.1.1                                                                                     | Modulation OFDM . . . . .                                           | 33 |

| 2.1.2                                                                                     | Paramètres . . . . .                                                | 36 |

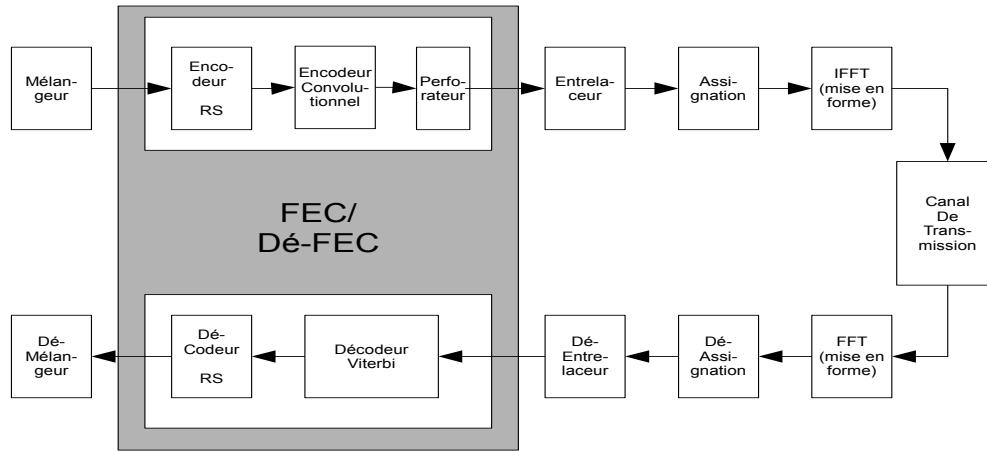

| 2.2                                                                                       | Chaine de codage . . . . .                                          | 37 |

| 2.2.1                                                                                     | Mélangeur/De-Mélangeur . . . . .                                    | 37 |

| 2.2.2                                                                                     | Encodage FEC (Forward Error Correction) . . . . .                   | 40 |

| 2.2.2.1                                                                                   | Encodeur REED-SOLOMON . . . . .                                     | 40 |

| 2.2.2.2                                                                                   | Encodeur Convolution-Perforation . . . . .                          | 42 |

| 2.2.3                                                                                     | Entrelacement/De-Entrelacement . . . . .                            | 43 |

| 2.2.4                                                                                     | Assignation . . . . .                                               | 48 |

| 2.2.5                                                                                     | Décodeur FEC . . . . .                                              | 49 |

| 2.2.5.1                                                                                   | Décodeur Viterbi . . . . .                                          | 49 |

| 2.2.5.2                                                                                   | Décodeur REED-SOLOMON . . . . .                                     | 53 |

| 2.3                                                                                       | Conclusion . . . . .                                                | 61 |

| CHAPITRE 3 IMPLÉMENTATION DE LA COUCHE PHYSIQUE OFDM<br>DE LA NORME IEEE 802.16 . . . . . |                                                                     | 62 |

| 3.1                                                                                       | Vers un modèle en bande de base . . . . .                           | 63 |

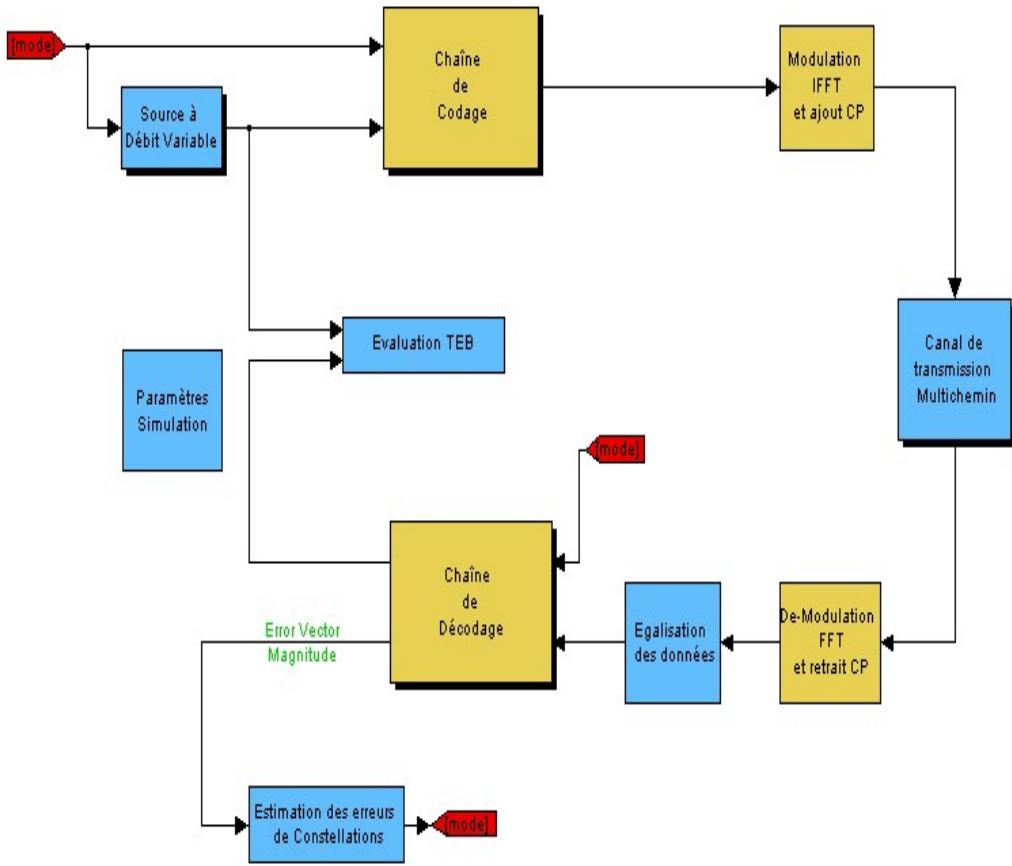

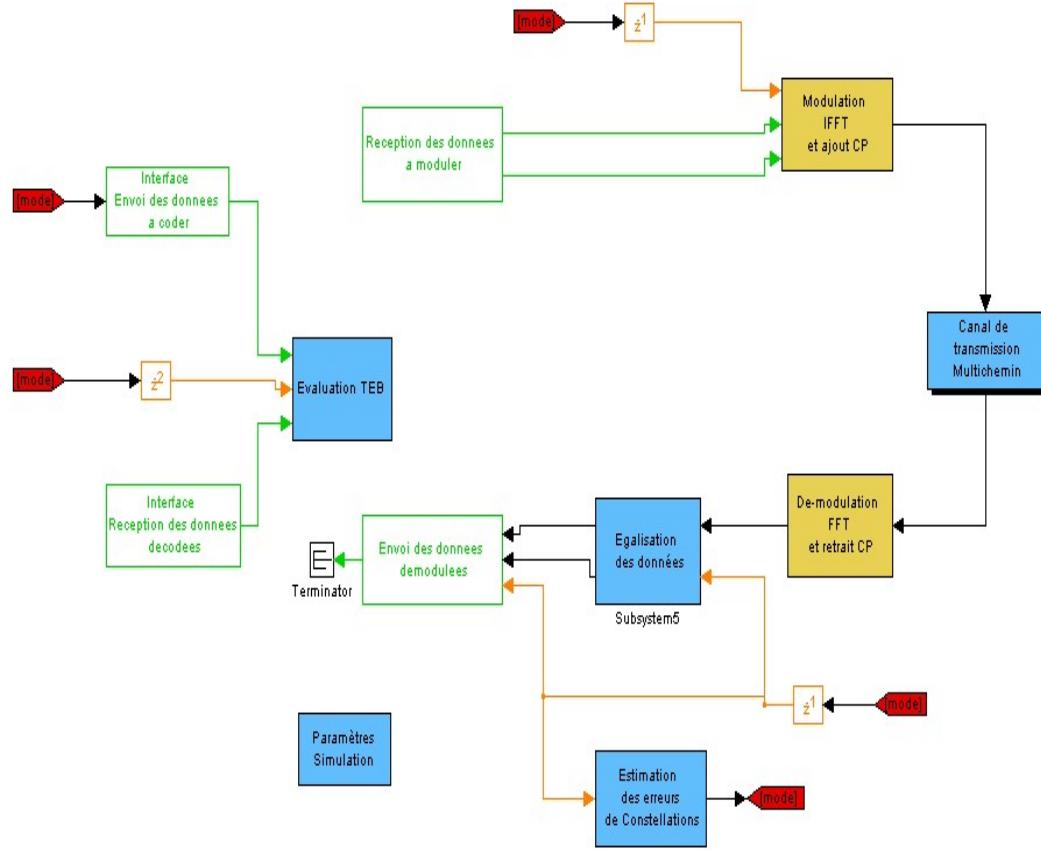

| 3.2                                                                                       | Modèle Simulink . . . . .                                           | 65 |

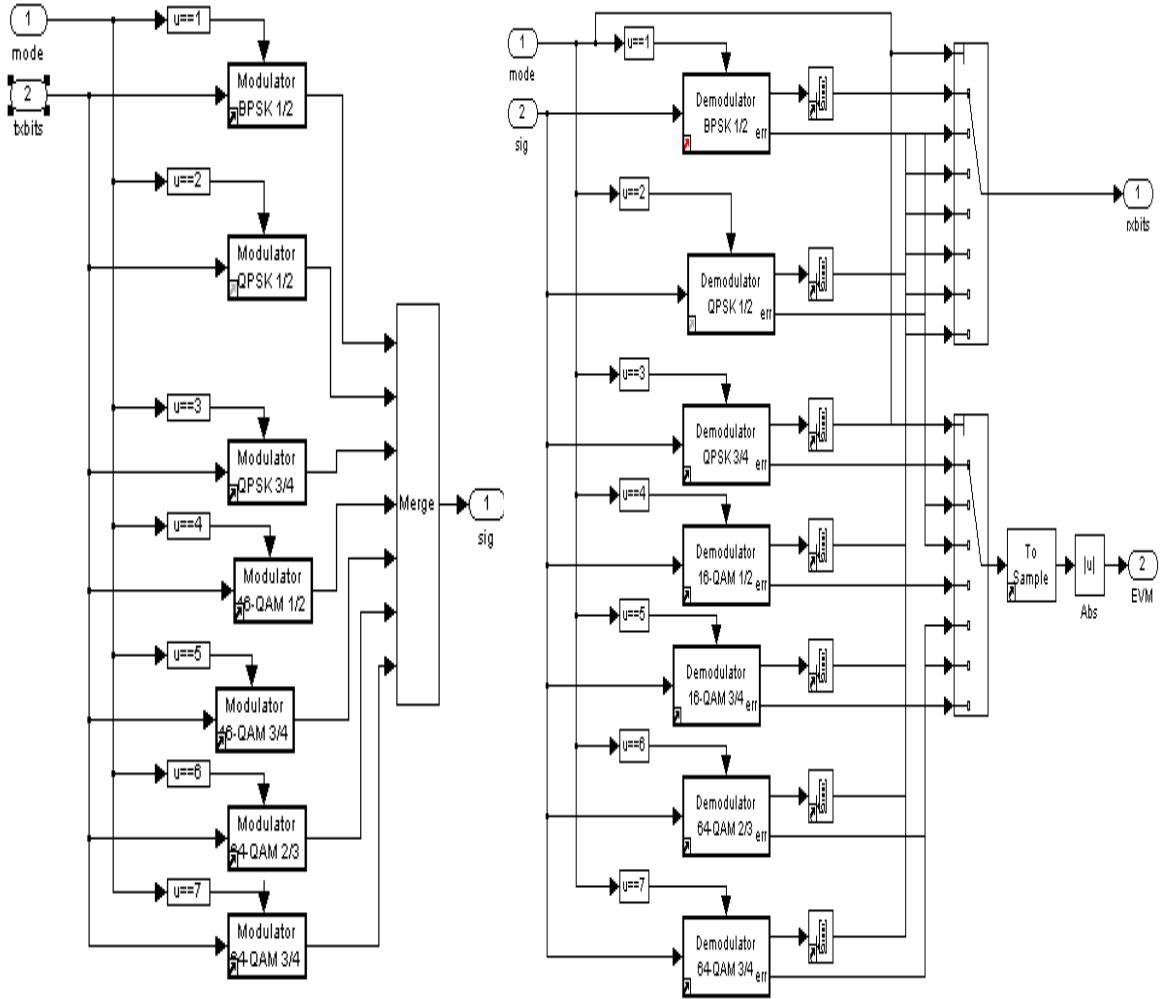

| 3.2.1                                                                                     | Envoi et Réception des données . . . . .                            | 66 |

| 3.2.2                                                                                     | Codage et décodage des données . . . . .                            | 68 |

| 3.2.3                                                                                     | Modulation et transmission des données . . . . .                    | 69 |

|                                              |                                                                                           |     |

|----------------------------------------------|-------------------------------------------------------------------------------------------|-----|

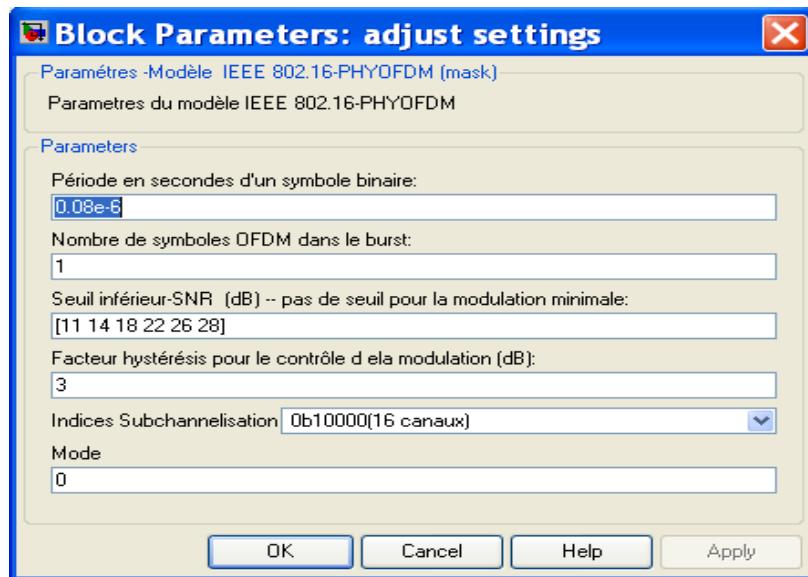

| 3.2.4                                        | Réglages dans Simulink . . . . .                                                          | 71  |

| 3.3                                          | Modèle sous Space Codesign . . . . .                                                      | 71  |

| 3.3.1                                        | Méthodologie de Conception . . . . .                                                      | 72  |

| 3.3.1.1                                      | Implémentation des modules . . . . .                                                      | 72  |

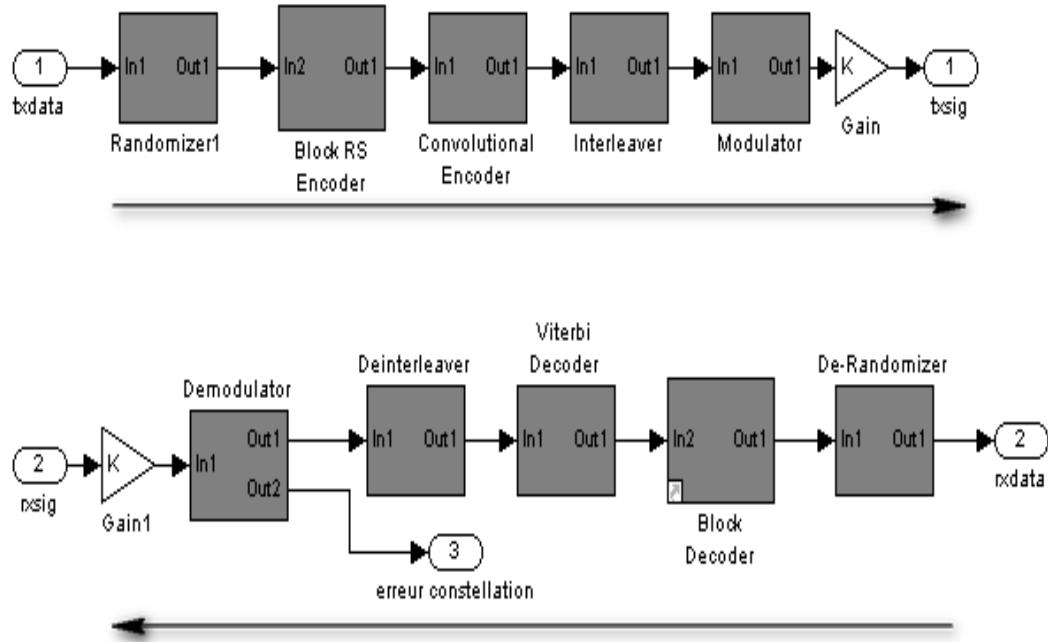

| 3.3.1.2                                      | Paramétrage des modules . . . . .                                                         | 73  |

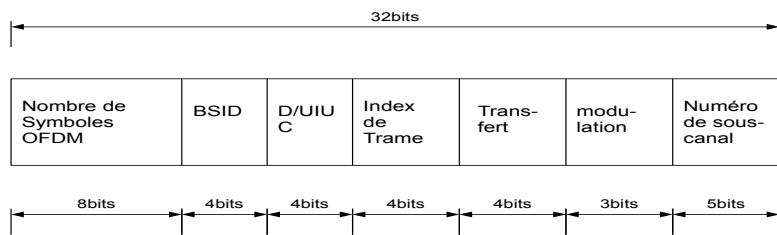

| 3.3.1.3                                      | Architectures du modèle . . . . .                                                         | 75  |

| 3.4                                          | Modèle de Co-simulation Space/Simulink . . . . .                                          | 77  |

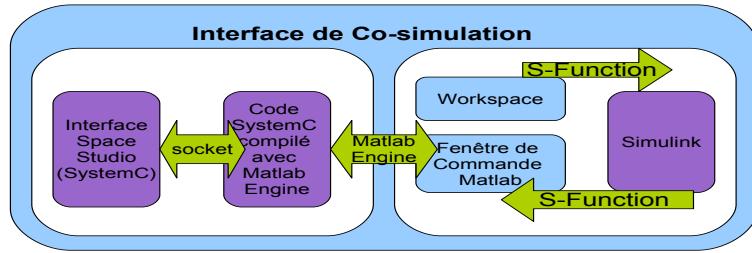

| 3.4.1                                        | Interface entre Space Codesign et Visual Studio . . . . .                                 | 78  |

| 3.4.2                                        | Interface entre Visual Studio et Matlab . . . . .                                         | 79  |

| 3.4.3                                        | Interface entre Matlab et Simulink . . . . .                                              | 80  |

| 3.5                                          | Modèle RTL . . . . .                                                                      | 81  |

| 3.5.1                                        | Du modèle systemC au modèle RTL . . . . .                                                 | 83  |

| 3.5.2                                        | Génération des éléments de synthèse FPGA . . . . .                                        | 84  |

| 3.6                                          | Conclusion . . . . .                                                                      | 85  |

| CHAPITRE 4 RÉSULTATS ET DISCUSSION . . . . . |                                                                                           | 86  |

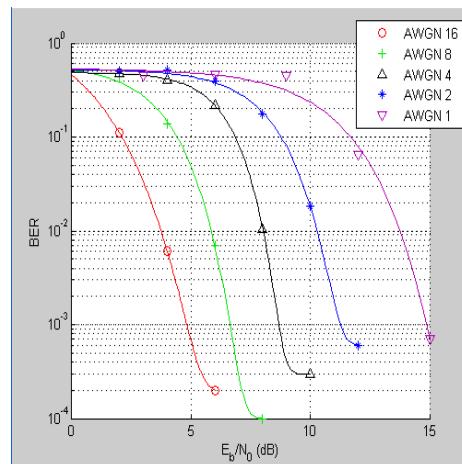

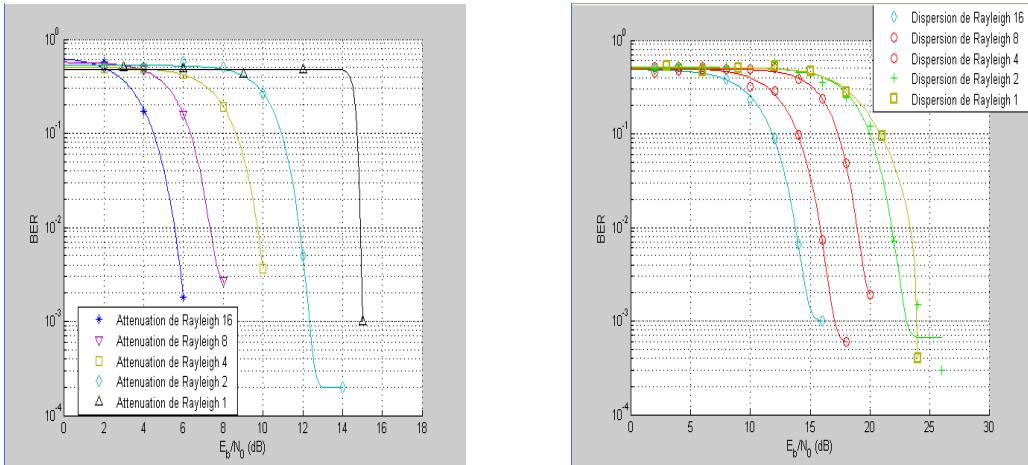

| 4.1                                          | Performances au niveau algorithmique . . . . .                                            | 86  |

| 4.2                                          | Processus de co-simulation . . . . .                                                      | 90  |

| 4.3                                          | Exploration architecturale et synthèse . . . . .                                          | 91  |

| 4.3.1                                        | Résultats de simulation selon le type de modulation et le nombre de sous-canaux . . . . . | 92  |

| 4.3.2                                        | Profilage du modèle système . . . . .                                                     | 93  |

| 4.3.3                                        | Résultats de synthèse . . . . .                                                           | 97  |

| CONCLUSION ET TRAVAUX FUTURS . . . . .       |                                                                                           | 100 |

| ANNEXES . . . . .                            |                                                                                           | 103 |

## LISTE DES FIGURES

|             |                                                            |    |

|-------------|------------------------------------------------------------|----|

| Figure 1    | Les réseaux sans fil . . . . .                             | 2  |

| Figure 1.1  | Approches de Conception . . . . .                          | 14 |

| Figure 1.2  | Eléments de Communication . . . . .                        | 16 |

| Figure 1.3  | Orthogonalité Calculs/Communications . . . . .             | 17 |

| Figure 1.4  | Communication dans SystemC . . . . .                       | 20 |

| Figure 1.5  | Communications Elix et Simtek dans Space . . . . .         | 22 |

| Figure 2.1  | Symbole OFDM dans le domaine fréquentiel . . . . .         | 34 |

| Figure 2.2  | Transmission à travers un canal de communication . . . . . | 38 |

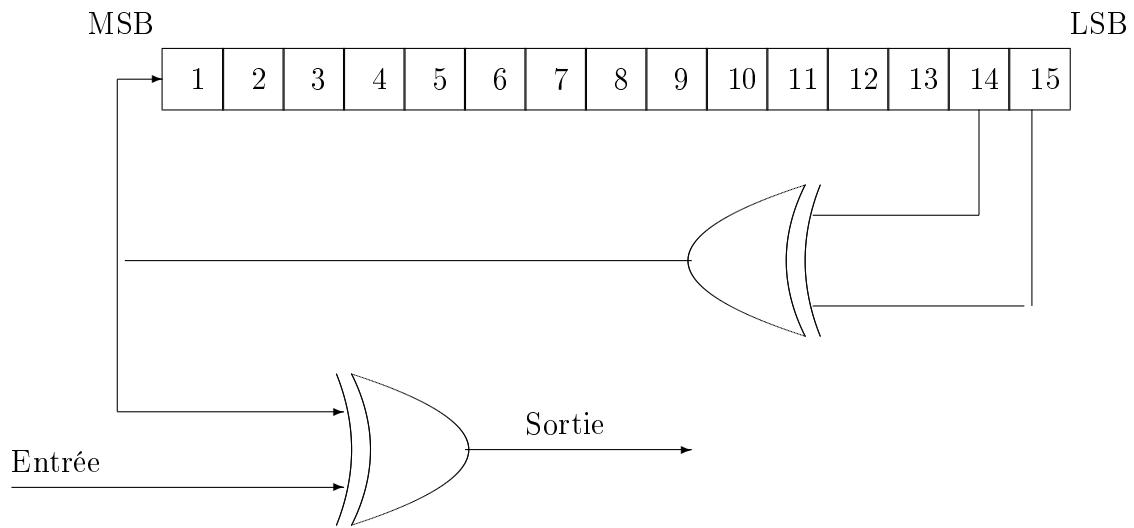

| Figure 2.3  | PRBS pour le <b>Mélangeur</b> . . . . .                    | 39 |

| Figure 2.4  | Initialisation des rafales en mode ascendant . . . . .     | 39 |

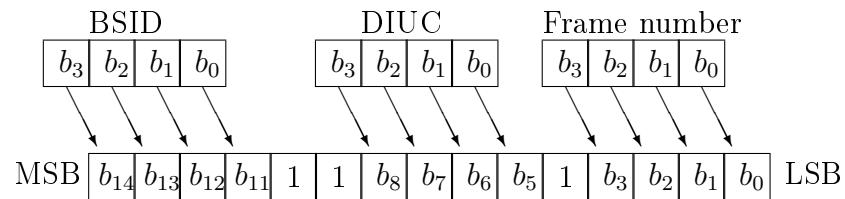

| Figure 2.5  | Schéma de codage du Reed-Solomon . . . . .                 | 42 |

| Figure 2.6  | Mot code envoyé . . . . .                                  | 43 |

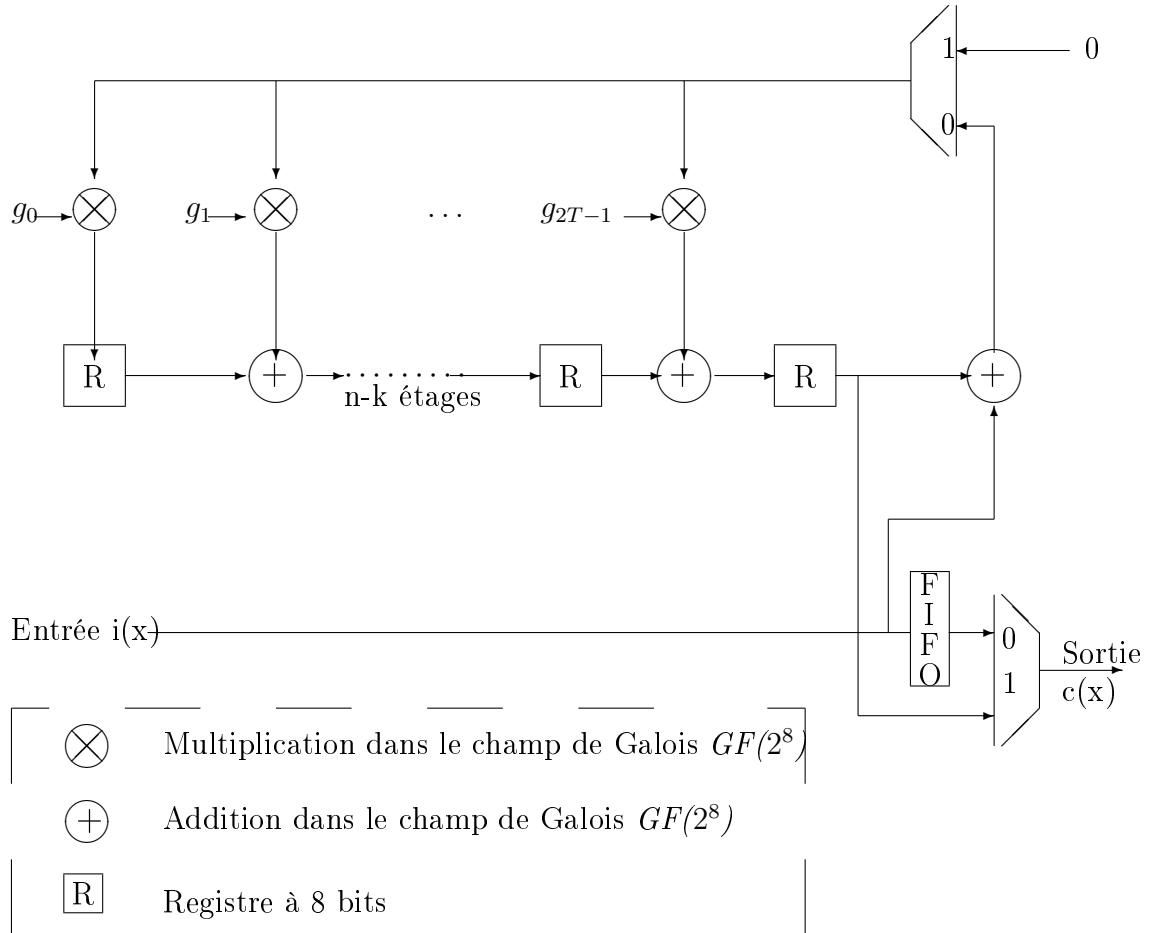

| Figure 2.7  | Convolution à rendement de 1/2 et de longueur 7 . . . . .  | 44 |

| Figure 2.8  | Entrelacement à 1 sous-canal et 16-QAM : Avant permutation | 47 |

| Figure 2.9  | Entrelacement à 1 sous-canal et 16-QAM : Après permutation | 47 |

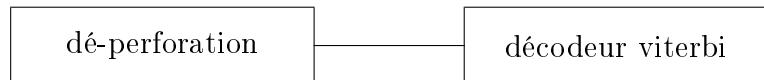

| Figure 2.10 | Décodage d'un code convolutif perforé . . . . .            | 51 |

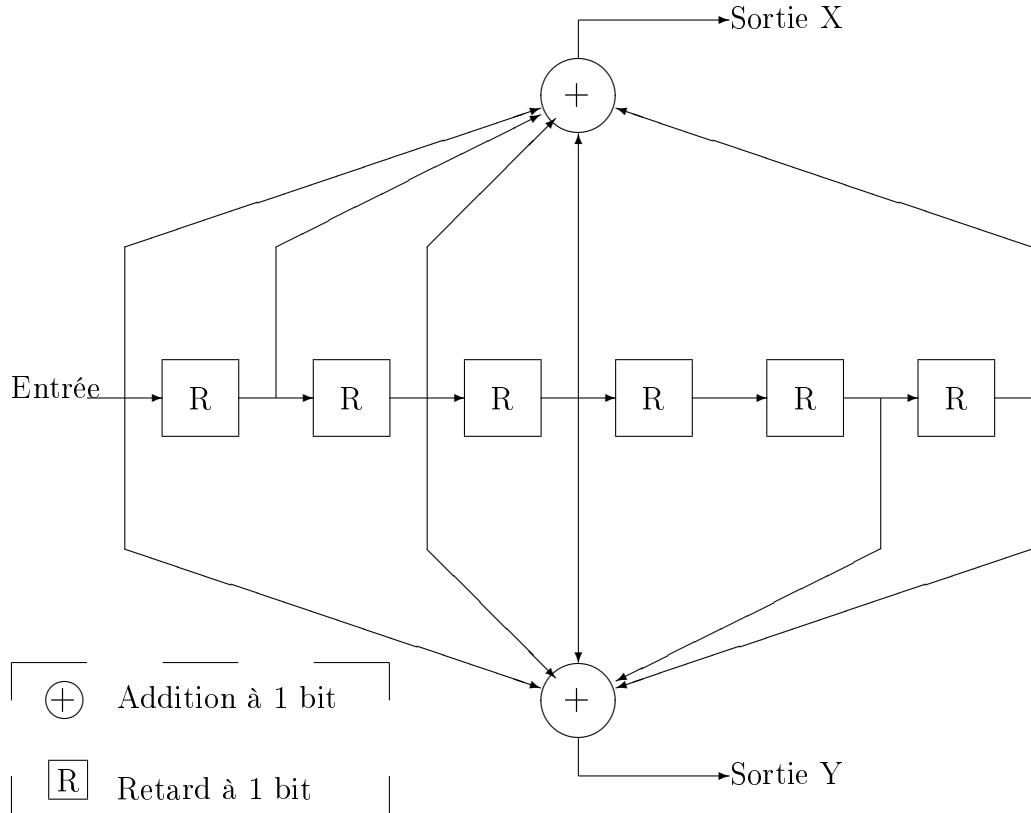

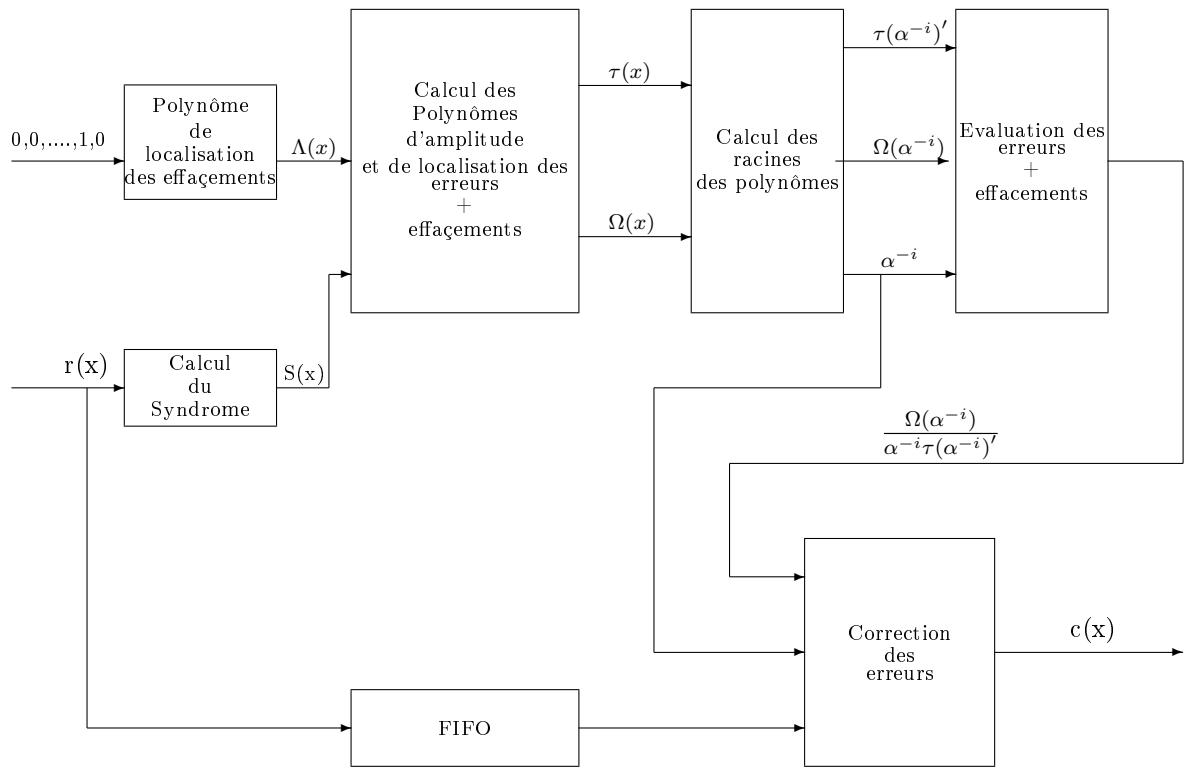

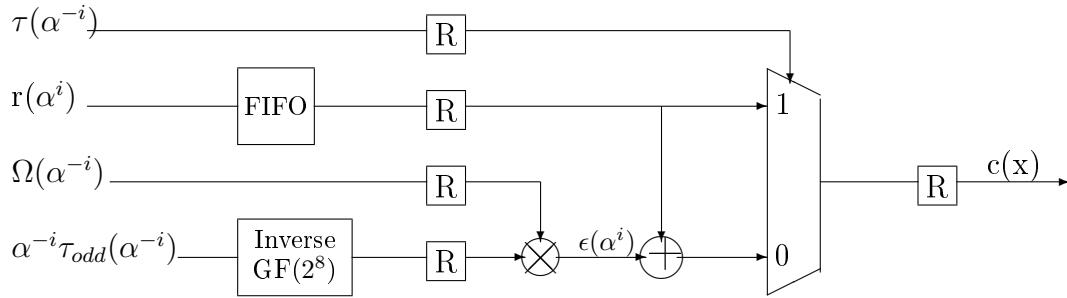

| Figure 2.11 | Schéma de décodage de codes de Reed-Solomon . . . . .      | 55 |

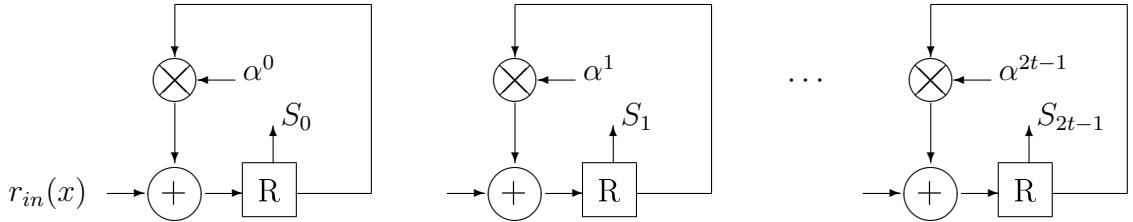

| Figure 2.12 | Calcul du Syndrome . . . . .                               | 57 |

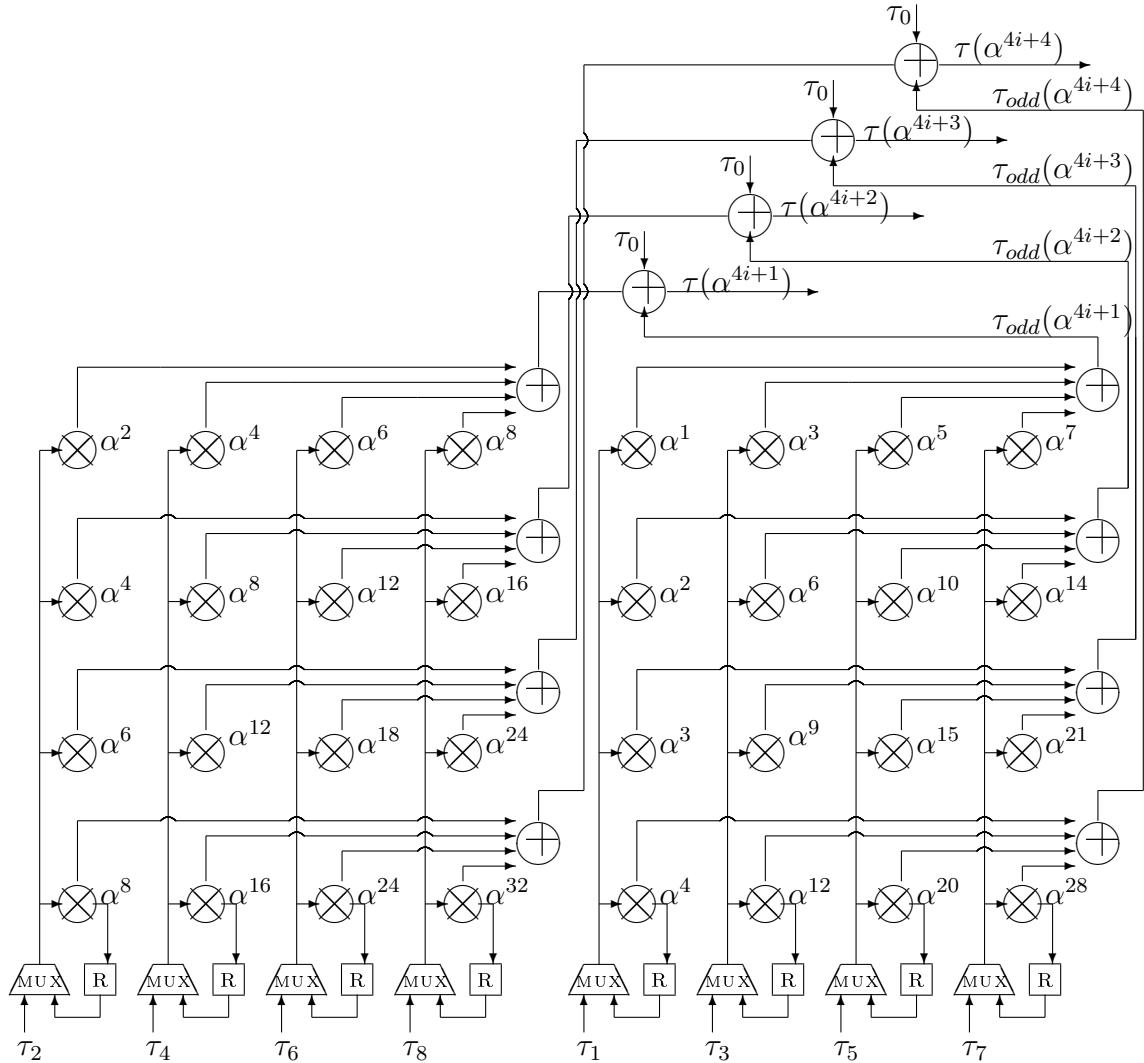

| Figure 2.13 | Architecture parallèle du Chien Search . . . . .           | 60 |

| Figure 2.14 | Architecture de Forney + Correction des erreurs . . . . .  | 61 |

| Figure 3.1  | Flot de conception du modèle de couche-PHY-OFDM . . . . .  | 64 |

| Figure 3.2  | Modèle Simulink . . . . .                                  | 66 |

| Figure 3.3  | Bloc des paramètres . . . . .                              | 67 |

| Figure 3.4  | Bloc des modulations . . . . .                             | 69 |

| Figure 3.5  | Bloc FEC+Assignation/De-FEC+DeAssignation . . . . .        | 70 |

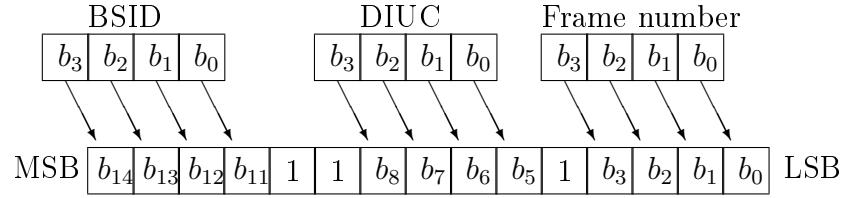

| Figure 3.6  | Format des données de paramètres . . . . .                 | 74 |

|              |                                                                                                                                                              |     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.7   | Architecture synthétisée par ForteCynthesizer . . . . .                                                                                                      | 76  |

| Figure 3.8   | Interface de co-simulation SpaceStudio-Simulink . . . . .                                                                                                    | 78  |

| Figure 3.9   | Modèle de co-simulation SpaceCodesign-Simulink . . . . .                                                                                                     | 82  |

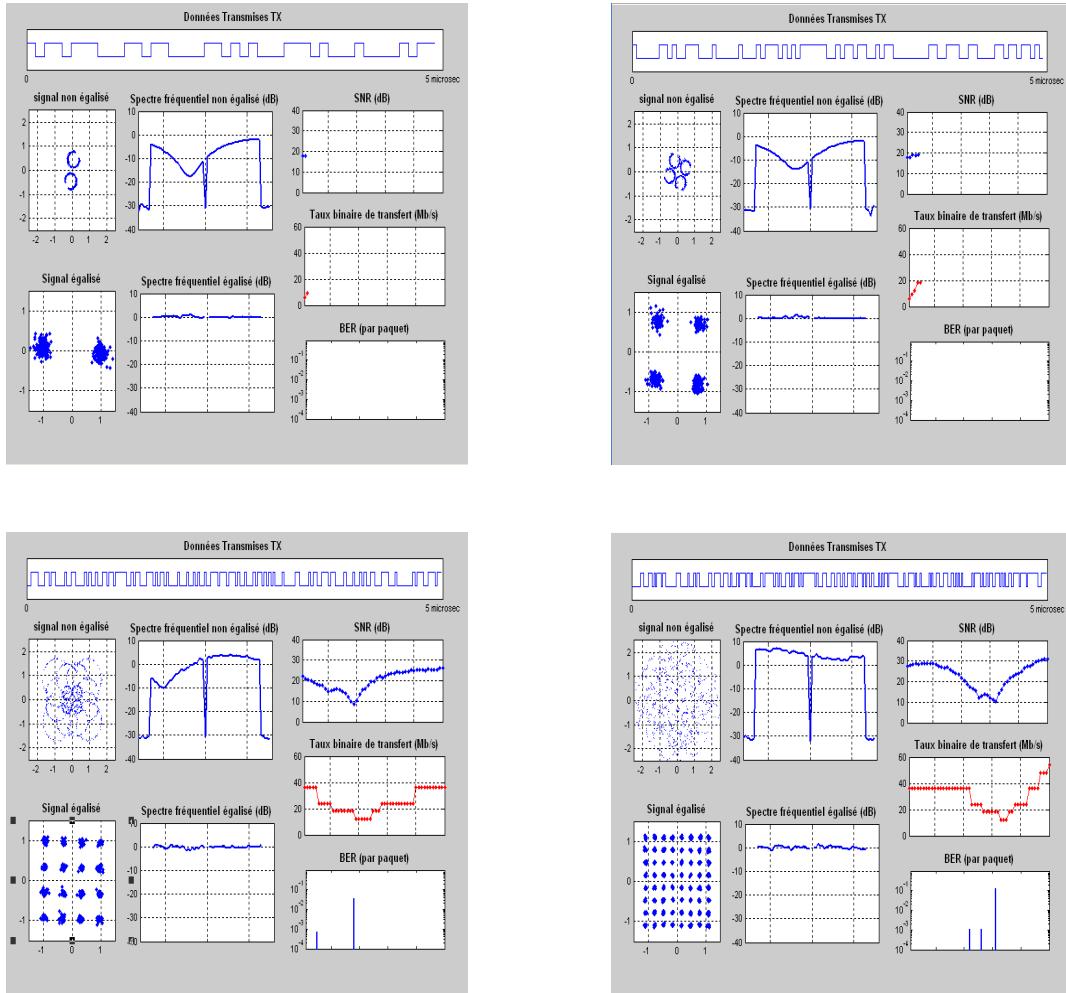

| Figure 4.1   | BER pour un canal AWGN avec une modulation adaptive pour<br>16, 8, 4, 2 et canaux . . . . .                                                                  | 87  |

| Figure 4.2   | BER pour canal Rayleigh atténuant et un canal Rayleigh<br>dispersif avec une modulation adaptive pour 16, 8, 4, 2 et canaux                                  | 88  |

| Figure 4.3   | Visualisation des signaux reçus pour une modulation adaptative<br>selon BPSK, QPSK, 16-QAM, 64-QAM pour un canal bruité,<br>dispersif et atténuant . . . . . | 89  |

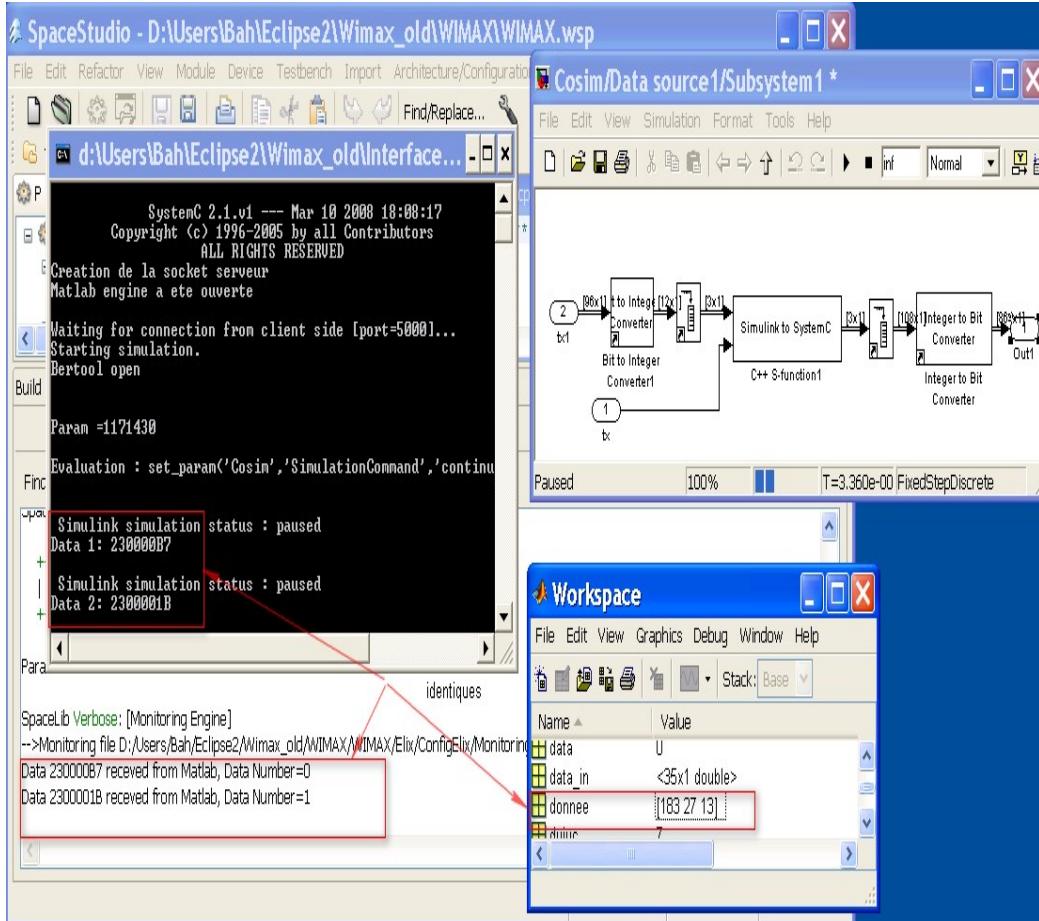

| Figure 4.4   | Vue d'une co-simulation entre Space Studio-Visual Studio-<br>Matlab-Simulink . . . . .                                                                       | 91  |

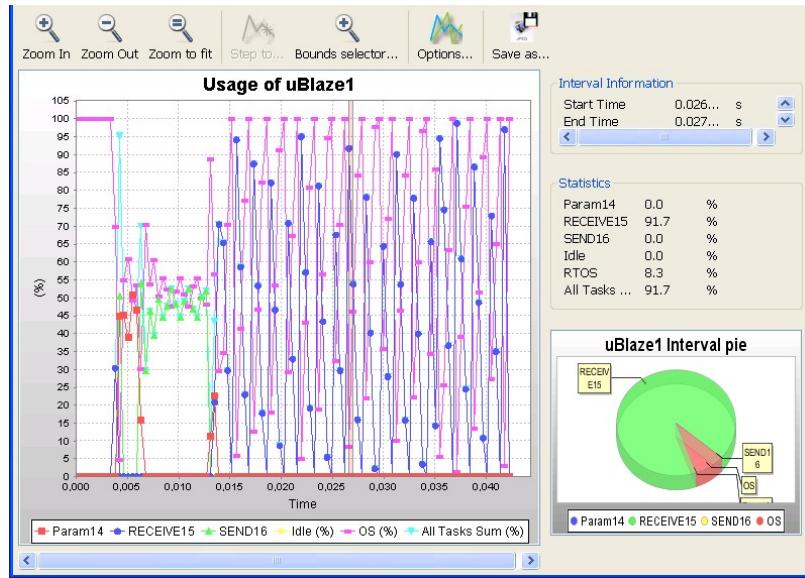

| Figure 4.5   | Utilisation du processeur . . . . .                                                                                                                          | 94  |

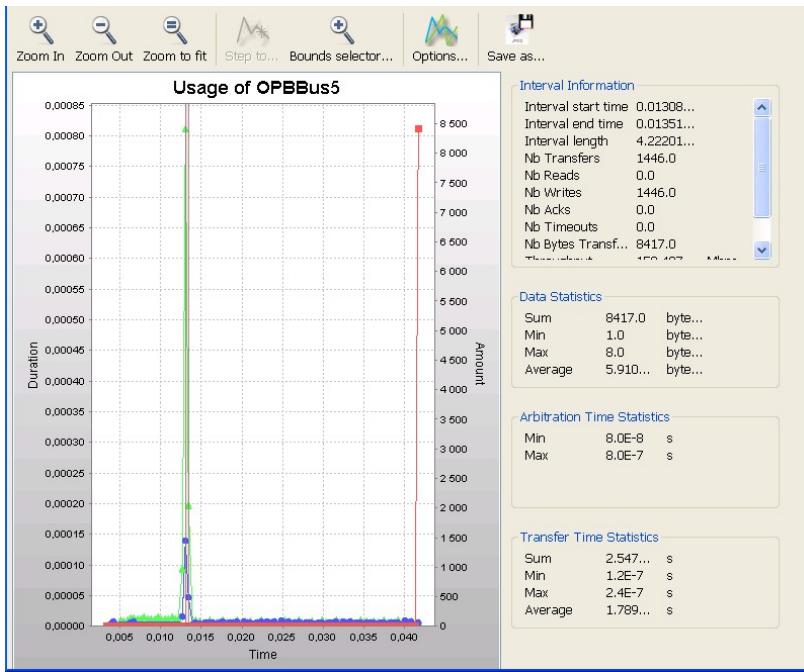

| Figure 4.6   | Utilisation du bus . . . . .                                                                                                                                 | 95  |

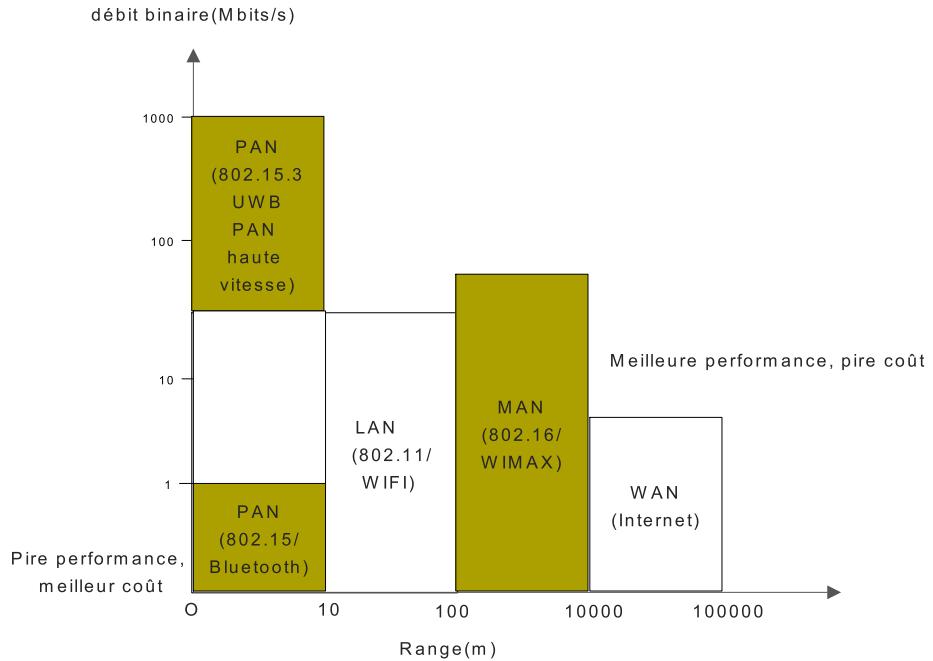

| Figure I.1   | Catégories de réseaux sans fil . . . . .                                                                                                                     | 104 |

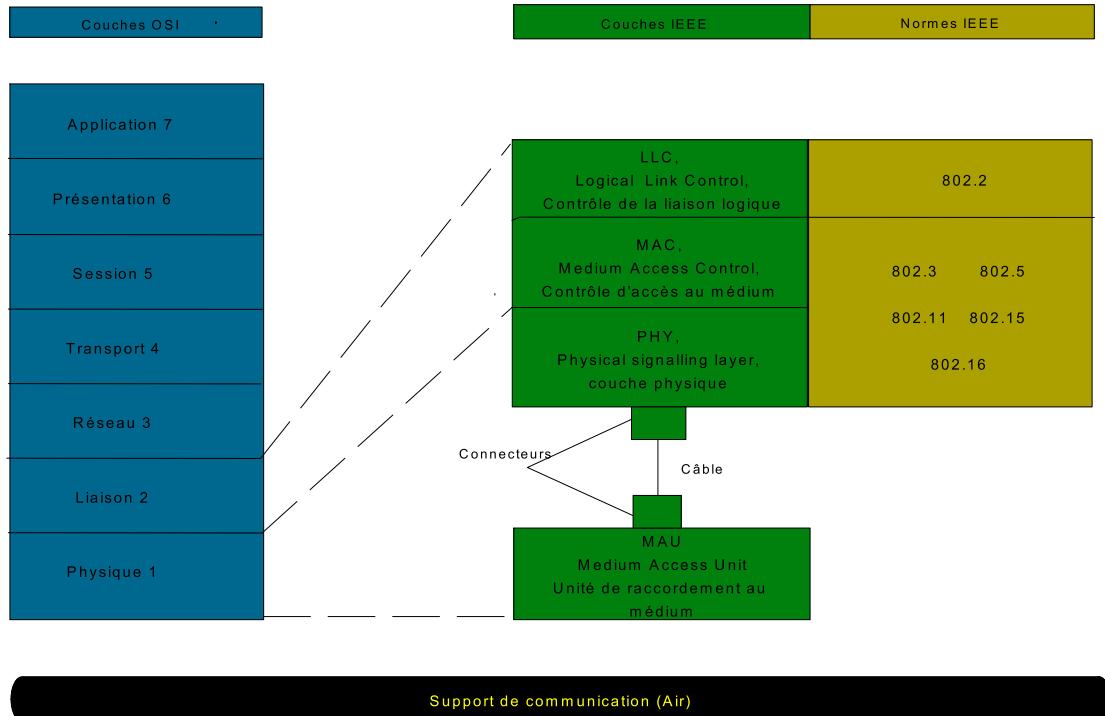

| Figure I.2   | Correspondance OSI-IEEE . . . . .                                                                                                                            | 112 |

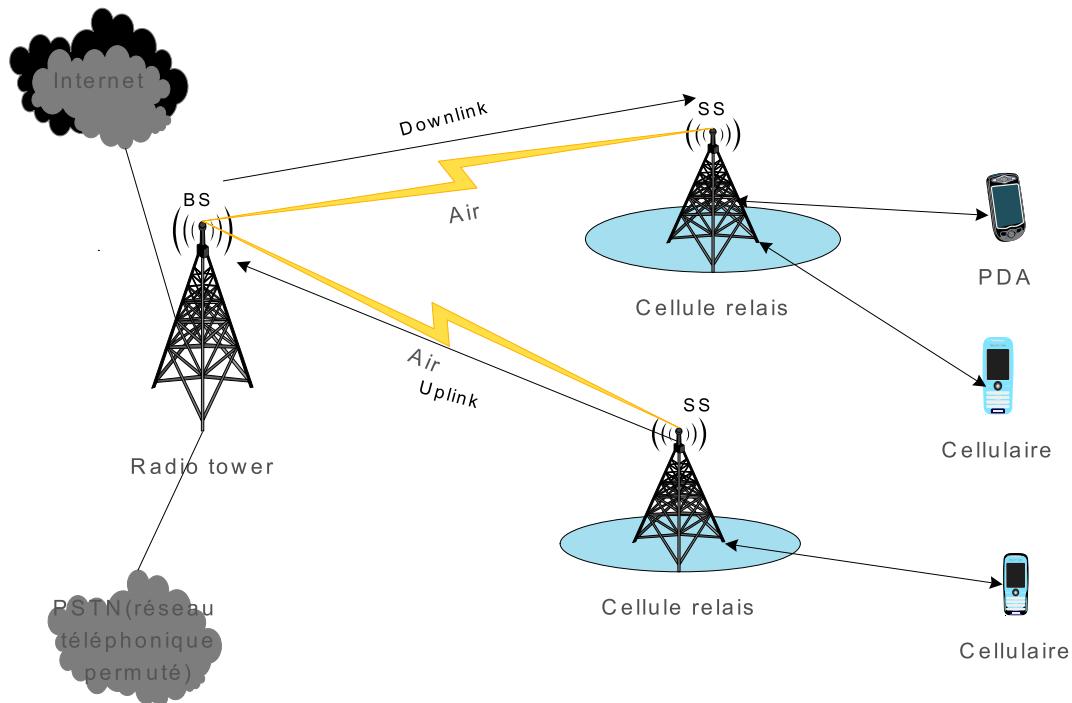

| Figure I.3   | Communication Wimax . . . . .                                                                                                                                | 113 |

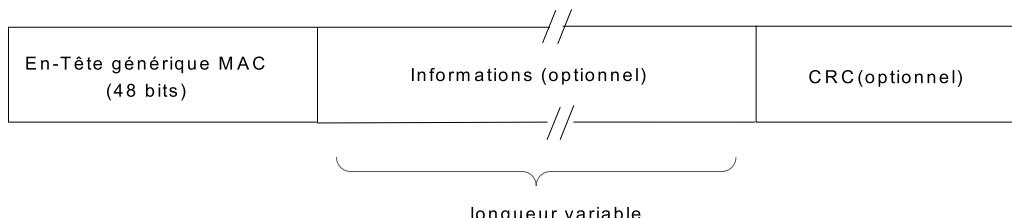

| Figure I.4   | Structure d'un PDU MAC . . . . .                                                                                                                             | 113 |

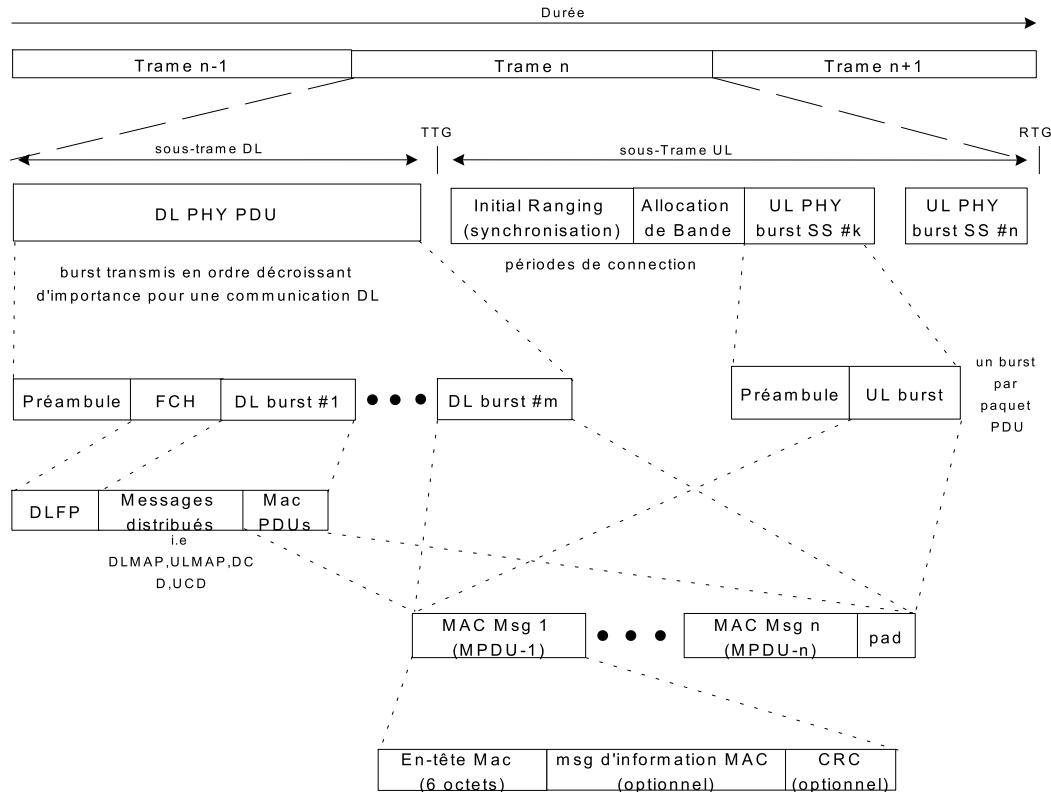

| Figure I.5   | Structure de trame TDD pour architecture PMP . . . . .                                                                                                       | 116 |

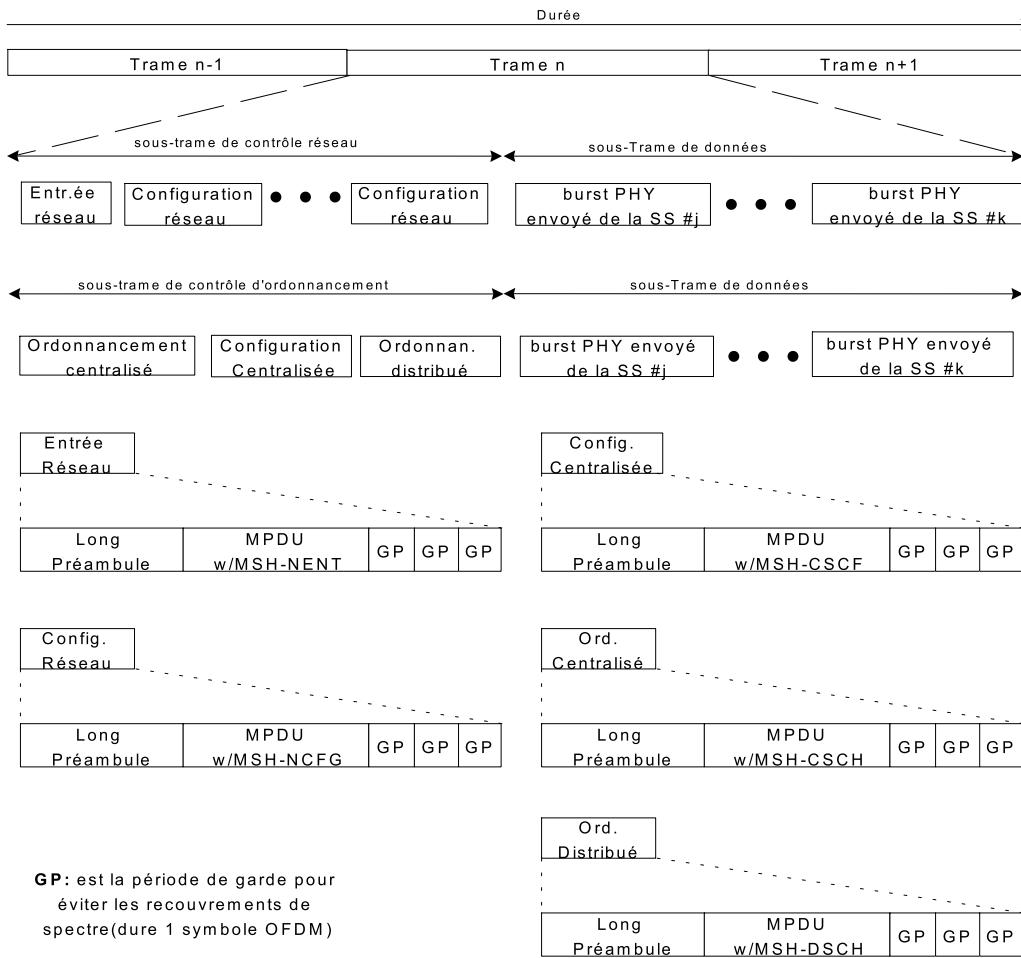

| Figure I.6   | Structure de trame TDD pour architecture Mesh . . . . .                                                                                                      | 117 |

| Figure I.7   | Initialisation de la trame descendante . . . . .                                                                                                             | 122 |

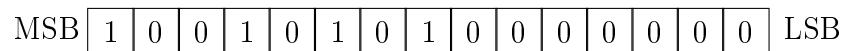

| Figure I.8   | Initialisation des rafales en mode descendant . . . . .                                                                                                      | 123 |

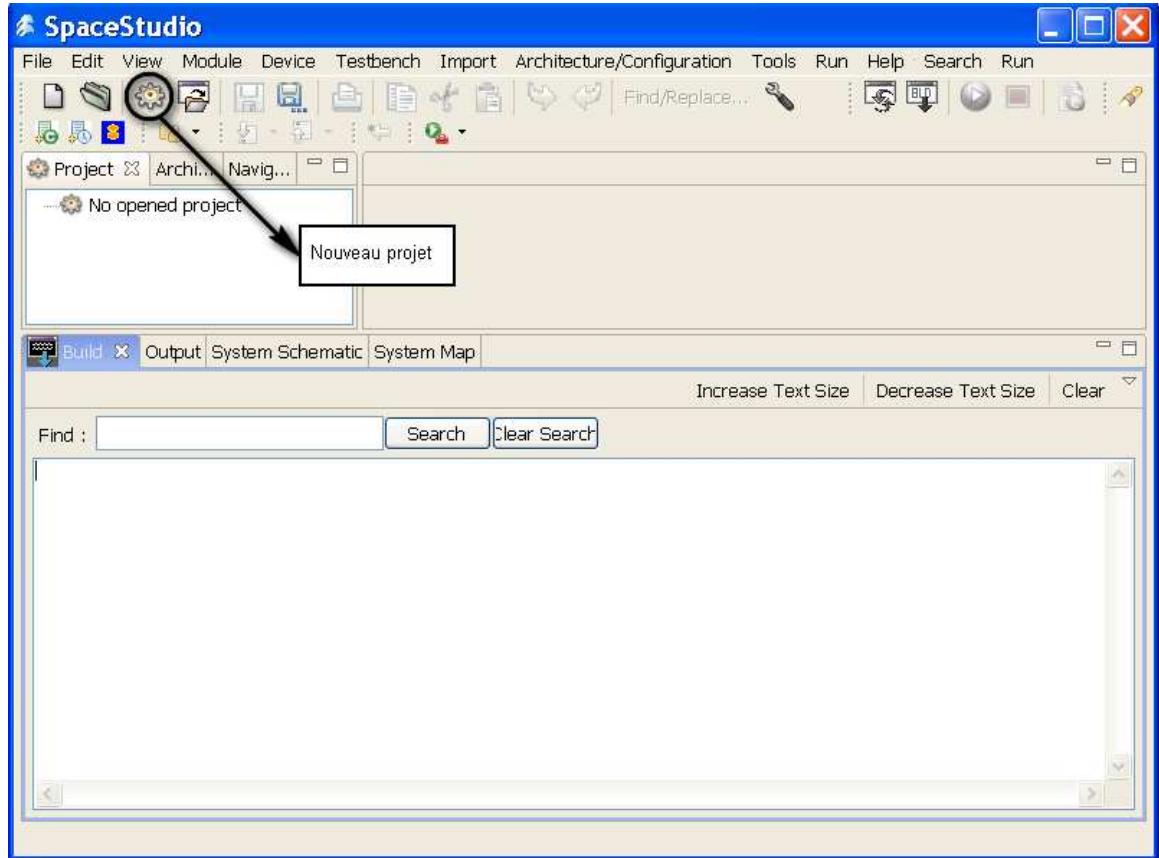

| Figure III.1 | Vue de la plateforme SpaceStudio . . . . .                                                                                                                   | 140 |

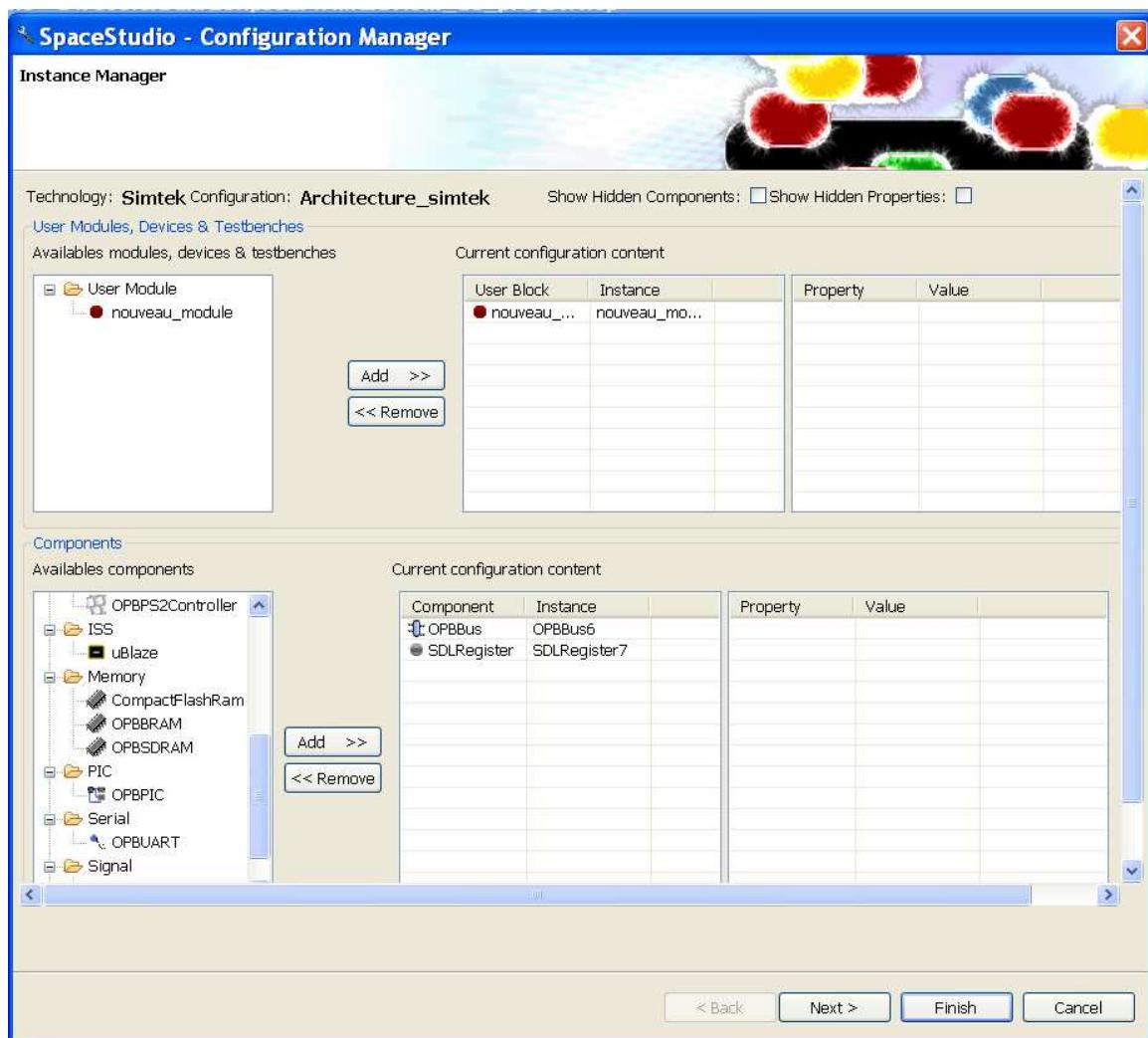

| Figure III.2 | Configuration de l'architecture . . . . .                                                                                                                    | 143 |

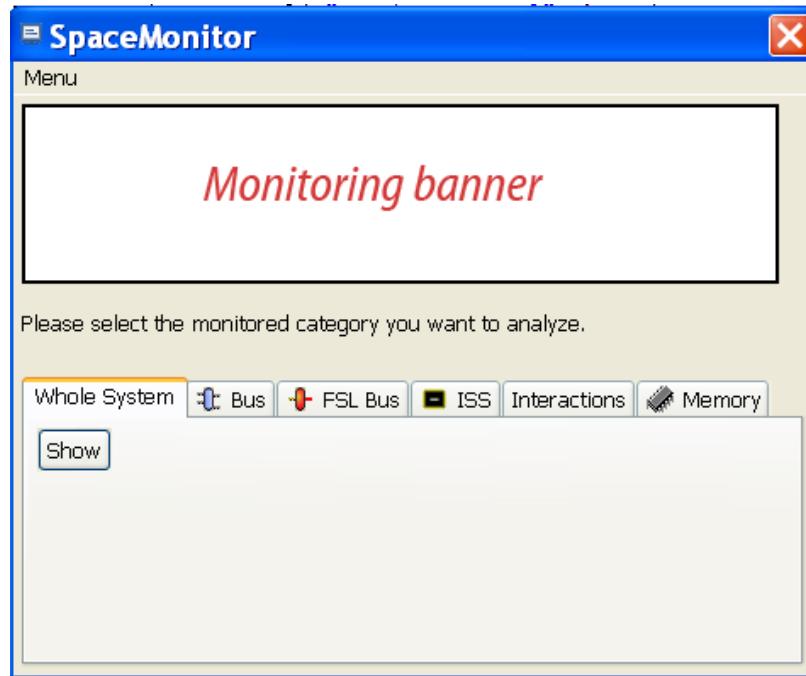

| Figure III.3 | Vue de SpaceMonitor . . . . .                                                                                                                                | 144 |

## LISTE DES ACRONYMES

|              |                                                                                         |

|--------------|-----------------------------------------------------------------------------------------|

| <b>BS</b>    | <b>B</b> ase <b>S</b> tation                                                            |

| <b>BWA</b>   | <b>B</b> roadband <b>W</b> ireless <b>A</b> ccess                                       |

| <b>CS</b>    | <b>C</b> onvergence <b>S</b> ublayer                                                    |

| <b>CPS</b>   | <b>C</b> ommon <b>P</b> art <b>S</b> ublayer                                            |

| <b>FDD</b>   | <b>F</b> requency <b>D</b> ivision <b>D</b> uplexing                                    |

| <b>FDM</b>   | <b>F</b> requency <b>D</b> ivision <b>M</b> ultiplexing                                 |

| <b>OFDM</b>  | <b>O</b> rthogonal <b>F</b> requency <b>D</b> ivision <b>M</b> ultiplexing              |

| <b>OFDMA</b> | <b>O</b> rthogonal <b>F</b> requency <b>D</b> ivision <b>M</b> ultiple <b>A</b> ccess   |

| <b>PDU</b>   | <b>P</b> rotocol <b>D</b> ata <b>U</b> nit                                              |

| <b>PHY</b>   | <b>C</b> ouche <b>P</b> hysique                                                         |

| <b>Qos</b>   | <b>Q</b> uality <b>O</b> f <b>S</b> ervice                                              |

| <b>RTL</b>   | <b>R</b> egister <b>T</b> ransfert <b>L</b> evel                                        |

| <b>SAP</b>   | <b>S</b> ervice <b>A</b> ccess <b>P</b> oint                                            |

| <b>SDU</b>   | <b>S</b> ervice <b>D</b> ata <b>U</b> nit                                               |

| <b>SS</b>    | <b>S</b> ubscriber <b>S</b> tation                                                      |

| <b>TDD</b>   | <b>T</b> ime <b>D</b> ivision <b>D</b> uplexing                                         |

| <b>TDM</b>   | <b>T</b> ime <b>D</b> ivision <b>M</b> ultiplexing                                      |

| <b>WIMAX</b> | <b>W</b> orldwide <b>I</b> nteroperability <b>f</b> or <b>M</b> icrowave <b>A</b> ccess |

| <b>WLAN</b>  | <b>W</b> ireless <b>L</b> ocal <b>A</b> rea <b>N</b> etwork                             |

| <b>WMAN</b>  | <b>W</b> ireless <b>M</b> etropolitan <b>A</b> rea <b>N</b> etwork                      |

| <b>WPAN</b>  | <b>W</b> ireless <b>P</b> ersonal <b>A</b> rea <b>N</b> etwork                          |

| <b>WWAN</b>  | <b>W</b> ireless <b>W</b> ide <b>A</b> rea <b>N</b> etwork                              |

## LISTE DES TABLEAUX

|              |                                                                                           |     |

|--------------|-------------------------------------------------------------------------------------------|-----|

| Tableau 2.1  | Vecteurs de perforation . . . . .                                                         | 45  |

| Tableau 2.2  | Taille des blocs d'entrelacement . . . . .                                                | 45  |

| Tableau 4.1  | Temps d'exécution en ms selon le nombre de sous-canaux et le type de modulation . . . . . | 93  |

| Tableau 4.2  | Cycles de Simulation par module et pour un Symbole OFDM                                   | 96  |

| Tableau 4.3  | Résultats de temps d'exécution par configuration . . . . .                                | 97  |

| Tableau 4.4  | Nombre de Slices par module . . . . .                                                     | 98  |

| Tableau I.1  | Comparaison Wifi-Wimax . . . . .                                                          | 110 |

| Tableau I.2  | Tableau des paramètres des symboles OFDM . . . . .                                        | 121 |

| Tableau I.3  | Seuils d'erreurs de constellation . . . . .                                               | 122 |

| Tableau I.4  | Nombre d'octets requis par modulation . . . . .                                           | 123 |

| Tableau II.1 | Eléments de GF( $2^8$ ) . . . . .                                                         | 129 |

| Tableau II.2 | Tableau des constellations BPSK,QPSK, 16QAM,64QAM . .                                     | 136 |

| Tableau II.3 | Durée de Trames admises . . . . .                                                         | 138 |

| Tableau IV.1 | Fonctions de communication SystemC/Matlab/Simulink . .                                    | 149 |

## LISTE DES ANNEXES

|            |                                                                         |     |

|------------|-------------------------------------------------------------------------|-----|

| ANNEXE I   | RÉSEAUX SANS FIL . . . . .                                              | 103 |

| I.1        | Des réseaux sans fil au Wimax . . . . .                                 | 103 |

| I.2        | Définitions . . . . .                                                   | 105 |

| I.3        | Wimax versus Wifi . . . . .                                             | 108 |

| I.4        | Principe de fonctionnement du Wimax . . . . .                           | 109 |

| I.5        | Processus de communication . . . . .                                    | 111 |

| I.6        | Processus d'identification d'une BS et d'une SS . . . . .               | 114 |

| I.7        | Structure des données échangées . . . . .                               | 115 |

| I.8        | Paramètres OFDM . . . . .                                               | 119 |

| I.9        | Seuils d'erreurs SNR . . . . .                                          | 122 |

| I.10       | Format des vecteurs d'initialisation pour une communication descendante | 122 |

| I.11       | Nombre d'octets obligatoire par modulation . . . . .                    | 123 |

| ANNEXE II  | CODES CORRECTEURS D'ERREURS . . . . .                                   | 124 |

| II.1       | Codes systématiques . . . . .                                           | 124 |

| II.2       | Théorie de Galois . . . . .                                             | 125 |

| II.3       | Polynôme primitif . . . . .                                             | 127 |

| II.4       | Multiplication dans $GF(2^8)$ . . . . .                                 | 127 |

| II.5       | constellations . . . . .                                                | 136 |

| II.6       | Durée des Trames . . . . .                                              | 138 |

| ANNEXE III | CONCEPTION DANS SPACE CODESIGN . . . . .                                | 139 |

| III.1      | Présentation de Space Codesign . . . . .                                | 139 |

| III.2      | SpaceMonitoring . . . . .                                               | 144 |

| III.3      | Section GenX . . . . .                                                  | 145 |

| III.4      | Bancs d'Essai . . . . .                                                 | 145 |

|           |                                      |     |

|-----------|--------------------------------------|-----|

| ANNEXE IV | UTILISATION DE SIMULINK . . . . .    | 148 |

| IV.1      | Simulation . . . . .                 | 148 |

| IV.2      | S-Functions . . . . .                | 149 |

| IV.3      | Interfaces de cosimulation . . . . . | 151 |

## INTRODUCTION

### **Présentation du mémoire**

La communication sans fil remonte à l'origine de l'humanité. Depuis toujours l'Homme cherche à transmettre des informations. Pour cela il a développé des codes, langages, alphabets; il a utilisé tous les moyens à sa portée pour véhiculer ses messages: tam-tam, fumée, signaux sonores, etc....

En 1896<sup>1</sup> Giuliano Marconi établit la première liaison de téléphonie sans fil quelques années après l'invention du téléphone par Graham Bell. Les travaux de G.Marconi ont mené à la première conversation radio entre deux bateaux en 1915 [?] établissant ainsi le premier réseau sans fil. Le terme réseau définissant un ensemble d'éléments (ordinateur, pda, téléphones, etc...) connectés entre eux par des liens physiques (fibre optique, paires torsadées, air) et échangeant des données numériques. Dans la communication sans fil, ces données sont soumises à un ensemble de traitements appelés traitement de signal afin de les transmettre sans encombre à travers le support utilisé qu'est l'air.

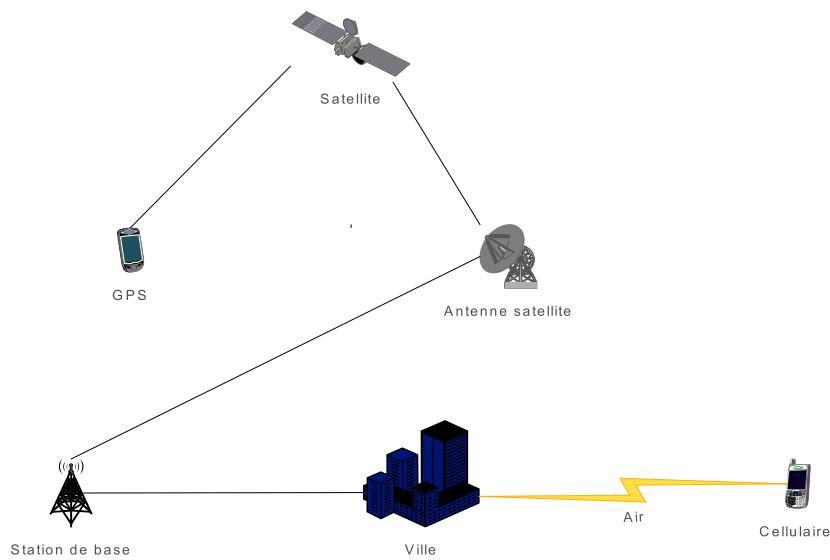

De nos jours, l'industrie des télécommunications a pris un grand essor grâce aux réseaux sans fil; les systèmes de communication sans fil tels que les cellulaires, les téléphones sans fil, satellites, les ordinateurs portables sont de plus en plus indispensables à notre société (voir figure 1). Les réseaux mobiles permettent de passer d'un endroit à un autre sans interruption de la communication. Ils permettent également de réduire les coûts d'établissement de réseaux. Cela est fort utile pour les pays en voie de développement où il n'y a presque pas de réseaux filaires. Du fait de sa croissance exceptionnelle, les acteurs de l'industrie veulent donc développer rapidement et à faible coût des systèmes sans fil dont la flexibilité permet de répondre

---

<sup>1</sup>voir <http://www.httr.ups-tlse.fr/pedagogie/cours/intro/histo.htm>

à l'importante demande en termes de largeur de bande et de débit. De tels systèmes tel que le **Wimax**[?] qui fait l'étude de ce projet, sont très utiles pour le déploiement de réseau dans des zones à accès difficiles, interdits ou temporaires. Néanmoins, cette extension des réseaux sans fil entraîne l'accroissement des problèmes d'interférences dus à la nature électromagnétique des signaux transmis.

Figure 1 Les réseaux sans fil

En effet, en 1905 Albert Einstein<sup>2</sup> a développé la théorie des photons qui explique que les ondes électromagnétiques contiennent de petites particules appelées photons; lesquelles déterminent l'amplitude de l'onde par leur nombre et la fréquence de l'onde par leur énergie. Toutefois cette transmission électromagnétique entraîne des problèmes d'interférence qui constituent le grand désavantage de ce type de communication par rapport aux réseaux filaires. Cela entraîne un taux d'erreur binaire élevé qu'on essaie de minimiser à l'aide de mécanismes de protection des

---

<sup>2</sup>source Wikipédia

données. Pour diminuer les risques d’interférence, on assigne des bandes de fréquences aux utilisateurs dans lesquelles ils peuvent émettre et recevoir des informations. et on utilise des techniques de multiplexage des données telles que l’OFDM afin de limiter ces interférences et de minimiser le délai de propagation du signal induit (selon qu’il rencontre un obstacle ou non). Le **Wimax** tel que spécifié dans sa norme propose différents modèles de couches physiques utilisant différents types de modulation pour le transfert des informations. Ainsi, notre choix de conception s’est porté sur **la couche physique-OFDM de la norme IEEE 802.16<sup>3</sup>** qui utilise la modulation OFDM.

**Problématique** La nécessité d’implanter ce type de système complexe et hétérogène pose le problème de la méthode de conception à utiliser afin de remplir les exigences en terme de coûts production et de temps de conception. Ainsi, de nouvelles techniques de conception de SOCs ont été développées pour atteindre ces conditions. Ces techniques consistent à travailler à des niveaux d’abstraction de plus en plus haut et de plus en plus précis pour respecter les spécifications du système.

Toutes les applications reposant sur un support matériel étaient conçues au départ à l’aide de processeurs d’usage général. Ces processeurs s’avérant trop lents pour des applications nécessitant des débits de transfert très élevé, la solution a été de leur associer des circuits intégrés, les ASICs (Application Specific Integrated Circuits) permettant ainsi d’accélérer ces systèmes.

Cependant, les ASICs offrant peu de flexibilité en terme de reprogrammabilité et limitant les possibilités de réutilisation des modèles précédents, de nouveaux circuits intégrés appelés systèmes sur puce (SOCs) reconfigurables tels que les FPGA (Field Programmable Gate Array) sont apparus. Ces systèmes combinent les avantages d’un processeur à usage général (offrant une grande flexibilité de développement)

---

<sup>3</sup>Rq:Pour des raisons de simplicité nous utiliserons le terme **Wimax** pour désigner la norme IEEE 802.16

et ceux des ASICs à travers un partitionnement logiciel/matériel. Ils sont également conçus pour optimiser les implémentations des systèmes et fournir toutes les ressources permettant de remplir les fonctionnalités de ces systèmes. Ils permettent au concepteur de paralléliser les algorithmes en allouant autant de ressources que possible et ainsi de réaliser les performances requises du système.

Au cours des dernières années, le domaine des circuits intégrés a donc subi une croissance phénoménale; désormais il est possible d'intégrer sur une même puce jusqu'à un million de transistors par millimètres carrés. La loi de Moore [?] établie en 1965 nous prédit en effet que leur nombre doublera tous les 18 mois ce qui offre des possibilités incroyables d'intégration de systèmes embarqués sur puce (par exemple, la possibilité d'avoir sur une même puce plusieurs réseaux wireless).

Une première avancée a été le passage du niveau des portes logiques à celui du transfert de registre (RTL). La simulation à ce niveau est plus rapide tout en restant efficace car permettant de représenter les comportements des signaux et registres et fournit une modélisation du circuit à partir de laquelle les câblages réels peuvent être dérivés. De plus, ce niveau offre des possibilités de synthèse automatique et de modularité de l'application permettant de réduire les erreurs inévitables de conception.

Toutefois la conception à ce niveau nécessitant beaucoup trop d'efforts pour la conversion des algorithmes DSP en un langage de description du matériel (VHDL, Verilog) en rendant l'application dépendante de la plateforme RTL; l'une des solutions privilégiée des concepteurs est de travailler au niveau algorithmique puis de raffiner jusqu'au niveau RTL. Le niveau algorithmique n'offrant aucune information sur le comportement réel de l'application du fait de son niveau d'abstraction, il s'agit de le ramener au niveau système qui par des raffinages successifs aboutit à l'implémentation RTL.

L'ESL (Electronic System Level) [?], [?] à travers l'un de ses dérivés le TLM (Transaction Level Modeling) [?], [?] est apparue pour pallier ces inconvénients en permettant de travailler à des niveaux d'abstraction (UTF/TF et BCA) plus élevés que le RTL mais supportant toutes les spécifications logicielles et matérielles des composants de ce niveau. Les auteurs[?] ont développé une approche ESL de conception logicielle/matérielle basée sur une plateforme virtuelle nommée Space Codesign. Cette plateforme comprend un ensemble de processeurs, liens de communications, mémoires et modules IP modélisés par des appels de fonctions, des accès mémoire et transfert de données ainsi qu'une représentation des instructions du processeur. Cette méthodologie basée sur quatre étapes principales : spécification du système, exploration, analyse et intégration combinée aux atouts des plateformes virtuelles tels que le développement au niveau système, l'analyse et l'optimisation des résultats de simulation ainsi que leur vérification et validation offre d'énormes avantages en matière de conception d'applications complexes.

Un autre moyen de respecter les exigences de développement se trouve au niveau de la vérification. En effet, cette étape cruciale est très coûteuse en temps et en moyen. Dans l'industrie, on estime que cette étape correspond à environ 70% du temps total de conception et donc nécessite des méthodes très rapides et efficaces. Plusieurs techniques de vérification existent selon les domaines d'application. Selon l'approche ESL, la vérification du système suit une étape Top-Down (de haut en bas) c'est-à-dire que l'on effectue une validation entre différents niveaux d'abstraction à travers la création d'interfaces de cosimulation.

Que se soit donc pour la conception ou la vérification du système, il s'avère donc que l'accélération du temps de développement nécessite de travailler à différents niveaux d'abstraction, d'être le plus haut possible et indépendant de la plateforme d'implémentation et enfin d'automatiser le processus de passage d'un niveau à un autre. Ainsi, pour une conception plus efficace, il faudrait pouvoir valider un modèle

conçu à un certain niveau avec le niveau adjacent. La plateforme *Space Codesign* étant associée à la plateforme *EDK* de *Xilinx*, cela permet une validation entre les modèles système et RTL. Un moyen de valider le modèle système au modèle algorithmique serait d'associer à la plateforme *Space Codesign* l'environnement *Matlab-Simulink* en lui associant des interfaces de cosimulation.

**Objectif :** Notre travail s'est porté sur la conception de la couche physique OFDM de la norme IEEE 802.16 par l'utilisation d'une plateforme ESL, nommée *Space Codesign*, afin de respecter les requis du cycle de développement, puis l'amélioration de la méthode de conception à travers l'utilisation de la cosimulation pour la vérification entre le niveau algorithmique conçu à l'aide de l'environnement *Matlab-Simulink* et le niveau système réalisé au niveau de la plateforme *Space Codesign*. Le modèle réalisé au niveau de *Space Codesign* a été raffiné en modèle RTL qui représente le modèle final à implémenter sur FPGA. *Space Codesign* intègre différents outils qui facilitent la création, la modification des modèles et permet de générer toutes les composantes matérielles de l'architecture à implémenter sur FPGA. D'autre part, une librairie de traitement de signal étant disponible sur *Matlab-Simulink*, il s'agit de réutiliser les blocs existants afin de bâtir le modèle algorithmique utilisé à des fins de validation. L'environnement *Simulink* est bâti sur la plateforme algorithmique *Matlab*.

**Contribution:** Les apports de ce travail peuvent se décliner en 2 parties.

La première est la réalisation des trois modèles correspondant aux trois niveaux d'abstraction de la conception : le niveau algorithmique, le niveau système et le niveau RTL. Ces modèles ont été conçus de façon à respecter tous les requis obligatoires de l'application.

- Un premier modèle a été entièrement conçu sous *Simulink* afin de valider les spécifications de l'application telles que définies dans la norme IEEE 802.16. Cette architecture fonctionnelle a été réalisée uniquement à l'aide de blocs **Simulink** et ne tient pas compte des contraintes temporelles liées à l'implémentation matérielle du modèle.

- Le second modèle, correspondant au cœur de ce projet a été construit à partir de la plateforme ESL Space Codesign qui offre différents niveaux de conception (Elix, Simtek) correspondant aux niveaux d'abstraction du TLM. Les éléments de l'architecture ont été entièrement réalisés en *SystemC* [?] sous forme de modules selon l'approche ESL. Ces modules ont été réalisés de façon à optimiser le volume des calculs et des communications. La plateforme Space Codesign comprend différentes composantes électroniques (microprocesseurs, contrôleurs, mémoires, bus, timers) sur une même puce et nécessaires à l'implémentation sur FPGA. Durant cette étape, un partitionnement logiciel/matériel optimal a été défini grâce aux outils de la plateforme à partir des informations collectées sur le temps de calcul et de communication des composants du système.

- Finalement le dernier modèle situé au niveau RTL et obtenu à partir du partitionnement a été implémenté sur le FPGA. Les éléments matériels de ce modèle ont été obtenus par synthèse comportementale [?] ou à partir des librairies de la plateforme *Xilinx* d'implémentation du FPGA. Les éléments de l'application non fournis par cette plateforme ont été codés manuellement.

La deuxième contribution représente l'intégration de la co-simulation au modèle ESL à des fins de vérification et de validation. La technique de cosimulation utilisée existant au préalable, elle a été adaptée à la plateforme Space Codesign. Cette technique utilise la librairie fournie par l'outil *Matlab-Simulink* permettant une cosimulation entre deux systèmes hétérogènes et appliquée au domaine du traitement du signal.

## Plan du mémoire

Ce mémoire comporte 4 chapitres (sans compter les chapitres d'introduction et de Conclusion). Le premier chapitre présente la revue de littérature du mémoire. Il aborde les travaux relatifs au Wimax , à la cosimulation *SystemC-Matlab-Simulink* et à la technologie de conception ESL. Le chapitre 2 présente les spécifications de la couche physique OFDM du Wimax telles que définies dans la norme 802.16 de IEEE ainsi que les éléments non spécifiés nécessaires à la construction du modèle complet. Le chaptire 3 nous donne l'implémentation de la couche physique à l'aide des outils présentés au chapitre 1. Le chapitre 4 présente les résultats de simulation et de synthèse des modèles implémentés au chapitre 3. Finalement le dernier chapitre conclut ce projet et nous présente les possibilités de recherche futures du modèle.

## CHAPITRE 1

### REVUE DE LITTÉRATURE

Le terme **Télécommunications** désigne l'ensemble des moyens techniques (ondes électromagnétiques) permettant l'acheminement (transmission et commutation) fidèle et fiable d'informations entre deux points quelconques pour un coût raisonnable<sup>1</sup>; ce coût (appelé qualité de service) est mesuré en terme de débit ou largeur de bande, taux d'erreur, durée d'établissement de la communication. L'information peut prendre diverses formes : son (paroles, musique), textes (retraitables ou non), données, images (fixes ou animées). L'ensemble des moyens physiques utilisables par des usagers qui bénéficient d'un même service s'appelle un réseau. Au départ, les informations transmises étaient principalement des signaux sonores pour la téléphonie et la télévision, qui étaient codés puis acheminés à travers des procédés de transmission analogique.

Toutefois les progrès en informatique (internet) ont vu la nécessité de relier ces signaux sonores à des équipements numériques donnant ainsi accès à plus d'applications (textes, images, données, etc..). La coexistence des deux techniques comportant des coûts, on a donc cherché à définir des réseaux purement numériques. Ainsi, une découverte majeure des télécommunications a été celle des réseaux sans fil dont le support de transmission est l'air contrairement aux réseaux filaires utilisant des câbles ou fibres optiques.

Cette évolution des techniques et du support de transmission a complètement bouleversé le domaine des télécommunications en ouvrant de nombreux horizons par l'association des techniques informatiques à celles des télécommunications.

---

<sup>1</sup>voir <http://www.volle.com/ENSPTT/introtcom.htm>

## 1.1 Conception des DSP : Un exemple, le Wimax

L'émergence de nouveaux réseaux sans fil tels que le **Wimax** pose la nécessité d'améliorer les méthodes de conception afin de produire dans des délais très courts des systèmes opérationnels et surtout extensibles. Le grand engouement provoqué par le Wimax au niveau des industries de télécommunication (Sprint, Nortel) ont mené à de nombreux travaux [?], [?] relatifs à son déploiement et entraîné de nombreuses réalisations effectuées par les sociétés de conception de systèmes sur puces tels que les FPGA.

### 1.1.1 Des ASICs aux FPGAs

En effet, l'évolution des réseaux sans fil a mis en évidence les limites des méthodes classiques de conception utilisant des processeurs d'usage général et les ASICs (niveau portes logiques). Les applications de réseaux sans fil nécessitant une énorme puissance de traitement difficile à réaliser à partir des processeurs classiques; un grand nombre de vendeurs d'outils de conception (*Altera, Xilinx, Coware*) sont donc arrivés à la conclusion qu'il est nécessaire d'utiliser un autre type de plateforme, en l'occurrence les FPGAs (niveau RTL). Ces systèmes sur puce (SOCs) permettent un degré très élevé de parallélisme des calculs (multiplications, additions,...). De plus, l'apparition en 1980 des langages de description du matériel tels que le Vérilog et le VHDL permettent de décrire entièrement des SOCs au niveau RTL en spécifiant l'architecture matérielle des applications au niveau des registres sans avoir à détailler les composantes logiques. Les applications du domaine des télécommunications communément appelées DSP (applications de traitement du signal) sont généralement conçues à partir d'algorithmes d'encodage/décodage et de modulation des données. Afin de remplir leurs contraintes en terme de temps de mise sur le marché, les concepteurs préfèrent se concentrer sur la conception des algorithmes et minimiser le temps d'implémentation

du matériel.

Le développement au niveau RTL d'applications telles que la couche physique OFDM de la norme IEEE 802.16 [?], [?], [?] comporte toutefois certaines limitations.

En effet, les conceptions volumineuses et complexes de systèmes tels que les algorithmes des télécommunications rendent difficile la mise en oeuvre efficace des méthodologies classiques. Bien que le niveau d'abstraction du RTL soit suffisamment élevé pour une conception matérielle, il n'est cependant pas adapté à du logiciel et ne permet donc pas d'exploiter un possible partitionnement logiciel/matériel optimal pour des algorithmes complexes et volumineux. En effet, convertir des algorithmes DSP en un langage tel que le Véritog ou VHDL peu s'avérer très fastidieux et susciter des erreurs sans compter que l'architecture FPGA reste dépendante de la plateforme FPGA. Cela peut donc rendre difficile la mise en oeuvre optimale et efficace de l'application dont le but principal est la portabilité et l'interopérabilité entre différents opérateurs des télécommunications car de simples modifications apportées à l'algortihme au niveau système peuvent avoir d'immenses répercussions sur la mise en oeuvre FPGA.

### 1.1.2 Des niveaux d'abstraction de plus en plus hauts

L'utilisation de bibliothèques DSP indépendantes de la technologie contribue de manière significative à la productivité du concepteur. Une conception constituée de fonctions DSP génériques ne comporte pas les paramètres architecturaux qui risqueraient d'encombrer inutilement les premières phases de la conception.

On retrouve de nombreux exemples de conception au niveau algorithmique de la couche physique étudiée, réalisés principalement à partir d'outils de simulation tels

que *Matlab-Simulink*<sup>2</sup> ou labview [?]. L'intérêt principal de ce type de conception vient du fait que ces outils possèdent déjà des librairies entières dédiées aux systèmes de traitement de signal ou de réseaux de télécommunication. L'architecture de la couche physique étant constituée d'une partie codage/décodage et d'une partie modulation/démodulation de données, il s'agit d'un système hétérogène comportant un aspect numérique et un autre analogique. Les différents blocs de la librairie correspondent aux différentes étapes du processus de transmission des données. Les systèmes sont généralement représentés en bande de base étant donné la nature des signaux numériques et la partie analogique peut être représentée par des blocs prédéfinis de la librairie. De plus les nombreux éléments de visualisation qu'offrent ces outils [?], [?], [?] permettent une bonne estimation des performances (taux d'erreur binaire, rapport signal sur bruit selon les modulations supportées) des systèmes. Les modèles de la couche physique simulés à partir d'outils comme *Matlab-Simulink* utilisent un découpage du système en blocs qui communiquent entre eux à travers des signaux. Ce niveau constitue une représentation graphique de la spécification du système et permet de valider les paramètres du système à réaliser. Toutefois, bien que très avantageux du point de vue souplesse de conception, ce niveau ne permet pas de représenter la réalité physique du système c'est à dire les délais de transmission entre les différents signaux, le temps d'exécution des opérations des différents blocs ainsi que la vitesse d'exécution du système qui est destiné à être porté sur une puce et donc représenté physiquement.

Il existe des systèmes permettant de combler l'écart entre le niveau algorithmique et le niveau RTL et certains concepteurs privilégient cette approche plus simpliste. Dans certains cas, la plateforme matérielle [?], [?] intègre des outils de synthèse matérielle de blocs algorithmiques de librairies comme celles de *Matlab-Simulink*. Ces méthodes nécessitent toutefois le re-codage des différents blocs algorithmiques en un langage de description tel que *VHDL/Vérilog* ou *SystemC* car ces plateformes ne fournissent

---

<sup>2</sup>voir Annexe IV

que les interfaces de communication entre les simulateurs algorithmiques/matériels. Ainsi le seul avantage de ces méthodes par rapport au niveau RTL est la possibilité d'effectuer les ajustements au niveau algorithmique avant la synthèse RTL car en réalité le système réalisé est dépendant de la plateforme RTL de conception et l'automatisation de la synthèse n'est pas prise en compte.

Afin de pallier à ces inconvénients, une nouvelle approche de conception, l'ESL est apparue. Elle consiste à travailler au niveau système et représente un intermédiaire entre le niveau algorithmique et le niveau RTL. En effet, à travers l'un de ses dérivés, le TLM, elle permet de s'assurer que le passage d'un niveau supérieur à un niveau inférieur ne requiert que peu d'efforts et que le système final peut être validé de manière rapide et efficace.

## 1.2 L'ESL: un choix de conception plus approprié

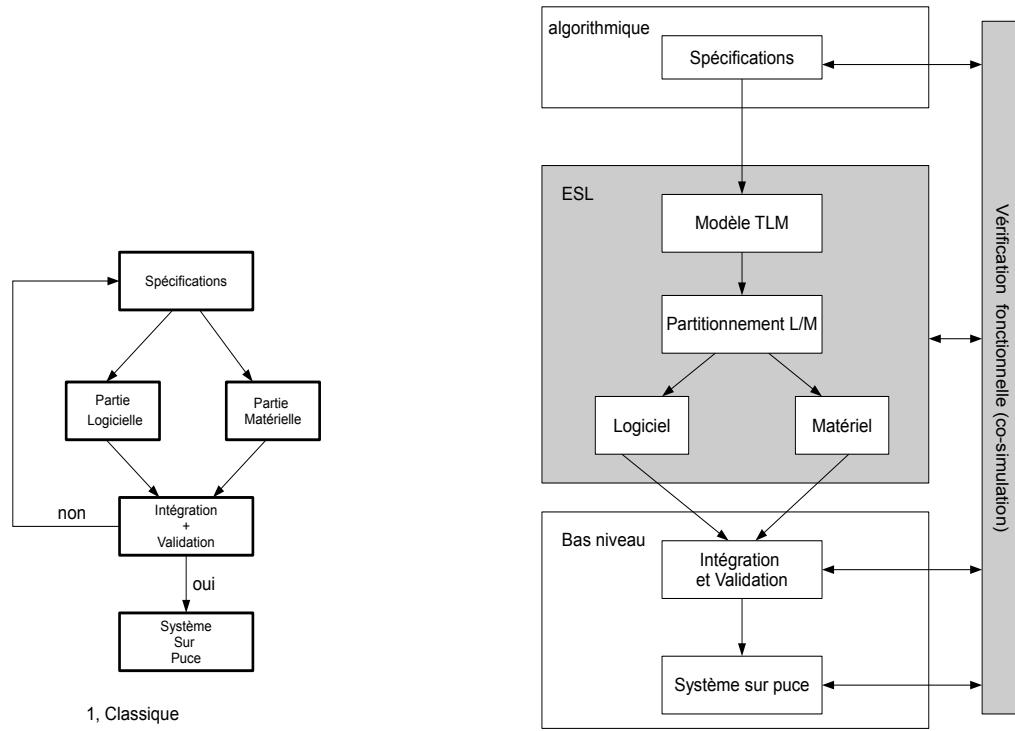

Il s'agit d'une méthodologie de conception à différents niveaux d'abstraction et permettant la réutilisation à travers le concept de plateforme. Dans l'approche classique de conception d'une application telle que le Wimax (voir partie 1 figure 1.1), on effectue dès le départ un partitionnement logiciel/matériel à partir des spécifications. Le développement logiciel étant totalement indépendant du développement matériel, c'est seulement après intégration des deux parties que l'on peut se rendre compte des modifications à apporter au système initial. Cela rend donc le développement très fastidieux et coûteux en terme de temps et d'argent. À travers l'ESL (voir partie 2 figure 1.1), bien qu'un partitionnement logiciel/matériel soit effectué le développement des deux parties se fait en collaboration grâce à l'insertion d'un modèle transactionnel entre l'étape des spécifications et celle du partitionnement.

De plus, l'ESL offre de nombreuses possibilités :

- création de la plateforme de simulation contenant les processeurs et co-

Figure 1.1 Approches de Conception

processeurs, canaux de communication, mémoires et périphériques à différents niveau d'abstraction.

- création de modèles fonctionnels de vérification et exploration architecturale selon l'architecture choisie

- raffinement à bas niveau au cycle d'horloge près (par ex. RTL ) pour des implémentations matérielles.

L'ESL [?] permet aussi d'obtenir une analyse des performances du système à travers l'intégration de différents simulateurs et outils graphiques et l'utilisation de langages de programmation tels que C/C++, *SystemC* (basé sur le C/C++), SystemVerilog. L'un de ses dérivés très utilisé, le TLM est principalement axé sur l'abstraction des communications et donc des transactions afin d'accélérer les simulations et de fournir une analyse la plus précise du système. Cette approche de modélisation consiste à découper le système à concevoir en modules qui communiquent entre eux

sous forme de transactions; on peut y voir une certaine analogie avec un réseau de télécommunication qui se définit par un ensemble d'éléments qui communiquent entre eux via des canaux de communication. Dans notre cas les éléments sont des modules et les canaux des bus.

Ainsi, l'avantage de l'ESL réside dans la conception de modèles transactionnels lesquels sont par la suite partitionnés et implémentés grâce à de nombreux mécanismes d'abstraction et de réutilisation. Cela permet d'accélérer le processus de conception, de simulation et de vérification et donc de développement du système.

Les modèles transactionnels utilisent un découpage en blocs du système à partir des spécifications. Ces blocs appelés modules communiquent entre eux par des canaux via des processus transactionnels. Dans chaque communication inter-modules, il y a un initiateur et une cible. L'initiateur appelé Maître de la communication effectue une requête qui est traitée par la cible appelée Esclave. Le canal de communication se charge d'arbitrer et donc de gérer le transfert de l'un à l'autre à travers des appels de fonctions. La figure 1.2 présente les éléments de communication à différents niveaux d'abstraction.

La modélisation transactionnelle (TLM) permet d'améliorer le processus de conception en permettant une validation du système à chaque étape sans avoir à attendre l'étape d'intégration comme c'est le cas dans l'approche classique. La validation est effectuée soit par simulation des différents niveaux ou par comparaison entre un niveau transactionnel et un autre par le biais des interfaces de communication, cela permet ainsi une exploration architecturale des possibilités d'implémentation du système. Le découpage en module permet un parallélisme d'applications de type flot de données telles que celle qui fait l'objet de notre étude. De plus, la communication des modules s'effectuant à l'aide de canaux, cela permet une communication des modules à travers des appels de fonction contrairement aux

Figure 1.2 Eléments de Communication

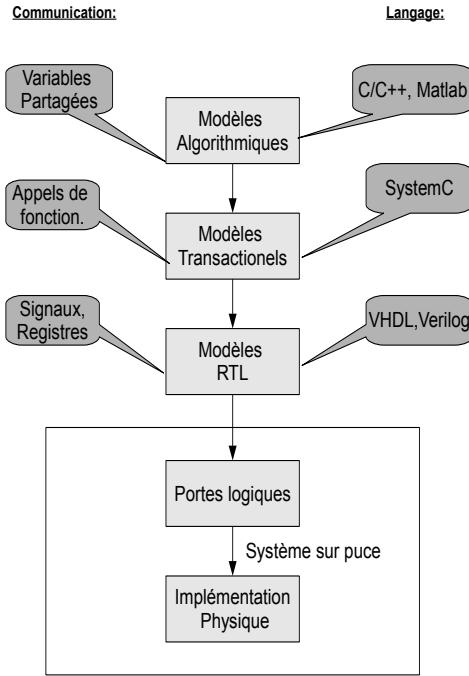

modèles RTL qui communiquent par signaux. C'est cette abstraction qui représente le principal intérêt du TLM car on peut ainsi passer d'un haut niveau (presque au niveau des spécifications) à un bas niveau (presque au niveau RTL) sans avoir à détailler la communication.

### 1.2.1 Les sous-niveaux d'abstraction du TLM

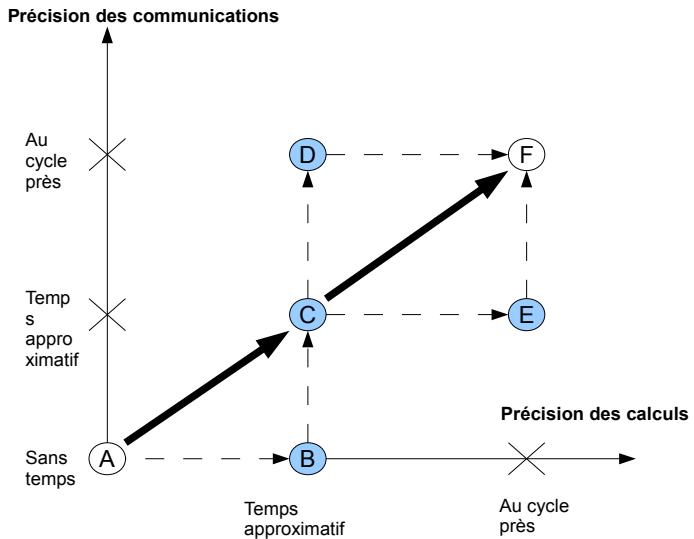

Les modèles transactionnels [?] peuvent être classifiés en fonction des calculs et des communications. En effet, le niveau le plus précis correspond à celui où les calculs et les communications sont évalués au cycle près tandis que le niveau le moins précis correspond à celui où on décrit les fonctionnalités du système sans tenir compte de leur temps d'évaluation. Lorsqu'on observe la figure 1.3, on constate une orthogonalité entre la précision des calculs et celle des communications.

Figure 1.3 Orthogonalité Calculs/Communications

Ces niveaux peuvent être regroupés en trois grandes catégories : A correspondant aux spécifications, B, C et D représentant les sous-niveaux transactionnels et F et E le niveau FPGA.

- La première catégorie correspond au niveau A et ne tient compte d'aucune notion de temps au niveau des calculs et des communications. Ce niveau sert uniquement à décrire les fonctionnalités du système.

- La seconde catégorie correspond aux niveaux B, C et D. Le niveau B est presque identique au niveau A excepté qu'on effectue une approximation du temps des calculs (pour une conception classique d'une application comme le Wimax, il pourrait s'agir d'un modèle *Simulink*). Cela nécessite donc d'évaluer le temps de simulation de chaque module du système. Les niveaux C et D font intervenir les canaux de communications représentés par des bus et nécessitant donc une arbitration des communications. Les temps de calcul sont approximatifs à ces niveaux; quant aux temps de communication, ils sont approximatifs

pour le niveau C et au cycle près pour le niveau D permettant ainsi de se rapprocher d'un modèle RTL synthétisable sur FPGA. Cette catégorie offre un bon compromis entre la précision des simulations et la rapidité de simulation et de développement permettant ainsi d'explorer différentes architectures selon le type de communication (bus, liens directs, etc..) et le choix de partitionnement logiciel/matériel.

- La dernière catégorie, représente les niveaux E et F quasiment identiques au modèle RTL excepté que le niveau E est moins raffiné au niveau des communications. Les transactions sont estimées au cycle près que ce soit au niveau des calculs ou au niveau des communications. Cela permet ainsi de faire une simulation au niveau RTL tout en faisant abstraction des signaux et des ports. La simulation est ainsi plus rapide tout en restant aussi précise. De plus des outils de synthèse comportementale tels que ForteCynthesizer [?] permettent de transcrire les langages des niveaux transactionnels tel que *SystemC*, en langage de matériel tels que Vérlog ou VHDL synthétisable sur FPGA. On peut ainsi valider très rapidement des architectures à différents niveaux d'abstraction tout en réduisant les erreurs induites par le passage d'un niveau à un autre.

Ce découpage en niveaux d'abstraction, grâce à l'orthogonalité des calculs et des communications, permet ainsi de raffiner progressivement l'architecture choisie en ayant un partitionnement optimal qui peut être modifié selon les résultats obtenus sans avoir à attendre l'étape d'intégration du processus. Cela représente la base du codesign qui est la méthode choisie pour la réalisation de la couche physique OFDM de la norme IEEE 802.16.

### 1.2.2 Réutilisation et automatisation de la conception

Un autre avantage de la modélisation transactionnelle est la possibilité de réutilisation qu'elle offre grâce au découpage en modules de l'application et la séparation des

communications et du traitement. Cela est très pratique pour des applications de réseaux sans fil où les protocoles sont en général étendus d'une norme à une autre. On peut ainsi réutiliser des blocs réalisés pour des applications similaires en changeant uniquement les paramètres de simulation. De plus, le code étant réalisé de façon indépendante de la plateforme d'implémentation, cela le rend indépendant et donc très portable ce qui est très utile pour des applications de réseaux sans fil où on veut pouvoir passer d'une plateforme donnée à une autre avec un minimum d'efforts. On peut également appliquer à l'ESL des mécanismes d'automatisation permettant de passer d'un niveau d'abstraction à un autre.

Il existe de nombreux outils permettant d'automatiser le passage d'un niveau algorithmique au niveau RTL (par ex.[?]) ou d'un niveau transactionnel au niveau RTL[?],[?]. Au niveau algorithmique, des outils graphiques (e.g. *Simulink*, *Labview*) permettent de visualiser les architectures et les simulations. De nombreux outils de conception bas niveau tels que *XPS* de *Xilinx*, *Quartus II* de *Altera* permettent d'automatiser la synthèse sur FPGA des éléments RTL des systèmes tout en intégrant des outils visuels de simulation des échanges de processus et de signaux au niveau RTL comme c'est le cas de l'outil Modelsim qui supporte les langages VHDL et Vérilog.

Un environnement optimal [?] serait donc celui offrant des interfaces de communication avec les outils visuels algorithmiques et les outils de synthèse RTL tout en offrant des outils graphiques de simulation au niveau transactionnel. *Space Codesign* à travers ses outils de profilage et de simulation associé à des outils intégrés de génération de code RTL, fournit une architecture RTL complète du modèle à implémenter sur un FPGA de *Xilinx* faisant ainsi le lien avec le niveau RTL. De plus, en lui intégrant des interfaces de co-simulation avec l'environnement *Matlab-Simulink*, on obtient une passerelle entre le niveau algorithmique et le niveau système.

### 1.2.3 Méthodologie de Conception dans Space Codesign

*Space Codesign* est une plateforme ESL de conception au niveau système, basée sur le langage de description *SystemC* permettant une modélisation de systèmes au niveau comportemental. Bien que souvent considéré comme un langage, *SystemC* [?] est en fait un ensemble de librairies C++(classes, fonctions, macros) permettant une modélisation au niveau système. Il permet de représenter les signaux, ports et intègre la notion de processus concurrents tels que les modules et threads associés très utiles pour une modélisation matérielle, mais également purement logicielle.

#### 1.2.3.1 Notions de bases : ports, signaux

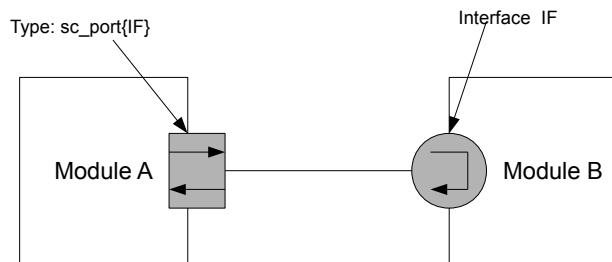

Un module *SystemC* est généralement représenté comme une boîte comportant des ports ou des interfaces de communication. Dans une communication *SystemC*, il y a généralement un maître qui envoie les données et une cible qui les reçoit ou vice-versa. Ce type de communication est généralement appelé une transaction (voir figure 1.4). Ainsi le premier module est connecté au second et peut faire des appels de fonctions à partir de ses ports qui implémentent les interfaces du second module ou l'inverse. De plus le code source du moteur de simulation étant accessible, il est possible de

Figure 1.4 Communication dans SystemC

l'étendre et de l'adapter selon des besoins spécifiques tel que c'est le cas dans *Space Codesign*.

### 1.2.3.2 Librairies de Space Codesign

La plateforme *Space Codesign* [?] se subdivise en deux parties : la librairie *SpaceLib* et l'environnement virtuel de développement *SpaceStudio*. La librairie *SpaceLib* comprend tous les éléments de base nécessaires à une modélisation transactionnelle sous *Space Studio*

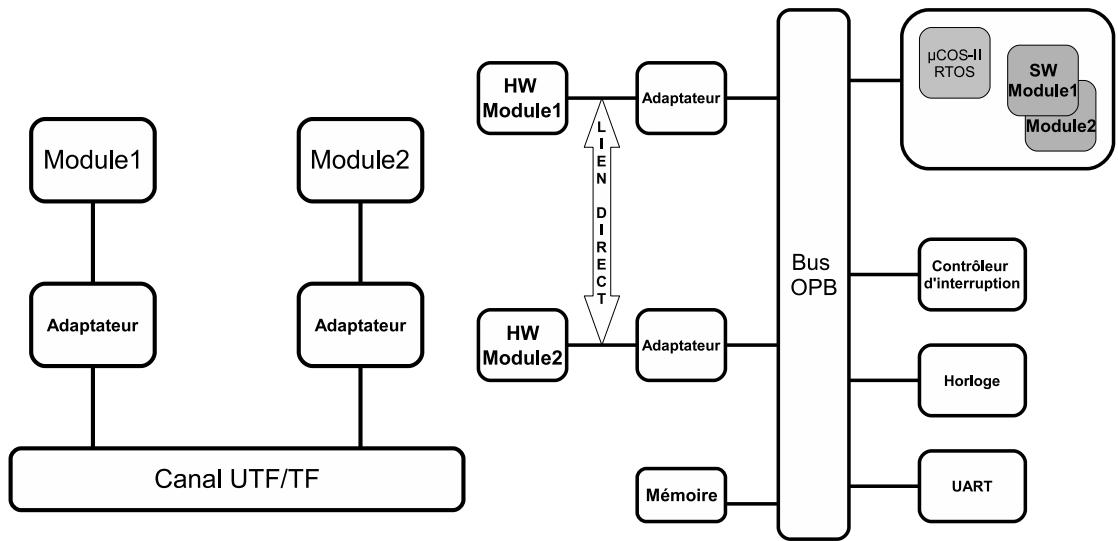

Ainsi, une application sous *Space Codesign* sera divisée en modules comportant un thread principal et des fonctions. Tous les aspects de communications des modules (ports, interfaces, bus, mémoires, timers, signaux,...) sont gérés par les librairies de *Space Codesign*. Dans *Space Codesign* deux modules peuvent communiquer soit à travers un bus ou par des liens directs. La communication se fait par un mécanisme de rendez-vous (transaction), c'est à dire que chaque module écrit et/ou lit dans un autre module des messages. Lorsqu'il s'agit d'une communication par bus, les modules sont associés à des adaptateurs recevant les messages et les stockant dans des files (fifos); ce sont les adaptateurs qui s'occupent de tous les aspects de communication avec le bus tels que le protocole de bus associé, la disponibilité du bus, la synchronisation des transferts, etc... Cela permet ainsi d'abstraire l'application de l'implémentation. Il existe deux niveaux d'abstraction dans la plateforme. Le niveau Elix et le niveau Simtek. Le premier niveau est le nivau fonctionnel (avec ou sans la présence du temps) correspondant à la première catégorie TLM; il permet de réaliser l'aspect algorithmique du système sans rentrer dans les détails d'implémentation (mémoires, processeurs, bus, etc..). Le deuxième quant à lui est situé juste au dessus du niveau RTL (circuits logiques) correspondant aux catégories 2 et 3 du TLM. C'est le niveau BCA (Bus Cycle Accurate) faisant intervenir le temps et la simulation au cycle

d'horloge près. Au niveau Elix, le protocole de bus associé n'est pas défini de même que les éléments associés tel que le microprocesseur, les mémoires, les contrôleurs d'interruptions, les UART etc. C'est au niveau Simtek que l'exploration architecturale est effectuée (voir figure 1.5).

Figure 1.5 Communications Elix et Simtek dans Space

### 1.2.3.3 Exploration architecturale

La plateforme supporte plusieurs protocoles de bus dont le bus OPB(On-chip Peripheral Bus) et le bus PLB (Processor Local Bus) de IBM CoreConnect. Étant donné que la plateforme *Space Codesign* est conçue de telle sorte à générer des composantes nécessaires à une implémentation dans la plateforme *EDK* de *Xilinx*, elle supporte également les processeurs MicroBlaze et PowerPC associés. De plus, des adaptateurs permettant d'encapsuler les modules (de les abstraire) ainsi que les composantes architecturales telles que les mémoires, les contrôleurs de bus, les interrupteurs, les timers et les simulateurs de jeux d'instruction des processeurs sont

automatiquement générés permettant ainsi une exploration architecturale efficace du système. L'exploration architecturale peut ainsi être décomposée en 3 parties :

1. Partitionnement logiciel/matériel.

À ce niveau, on détermine les modules implémentés en matériels et ceux implémentés en logiciel (c'est-à-dire dans le processeur)

2. Allocation et instantiation des tâches du processeur.

On détermine le nombre de processeurs du système et on lie chaque tâche définie au processeur correspondant.

3. Alllocation des bus et instantiation des composantes matérielles.

On détermine le nombre de bus du système auxquels on lie les éléments matériels (modules et composantes architecturales).

D'autre part, les messages échangés dans *Space Codesign* sont de deux sortes: bloquants ou non-bloquants en lecture ou en écriture et chaque module est muni d'un identifiant permettant ainsi de faciliter les communications. Lorsqu'un module envoie un message bloquant à un module ou composant, il ne peut continuer son processus qu'une fois que le receveur lit le message envoyé ce qui n'est pas le cas si l'opération est non-bloquante. Les opérations effectuées sur les messages sont des lectures et écritures. Le format d'une opération dans *Space Codesign* est du type suivant:

```

status = operation(ID destinataire ,

priorité du message ,

type ,

pointeur vers le message

);

où :

priorité du message : la variable SPACE_NORMAL_PRIORITY

type : SPACE_BLOCKING ou SPACE_NON_BLOCKING

ID destinataire : identifiant du module destinataire.

```

En plus d'offrir une librairie complète permettant une exploration architecturale, *Space Codesign* permet l'accès à des outils graphiques de simulation tel que *SpaceMonitor* [?]. Ce logiciel facilite l'évaluation des performances des configurations des architectures définies.

#### 1.2.3.4 Profilage

L'analyse des résultats est basée sur une observation continue et de façon non-intrusive des calculs et des communications au niveau matériel et logiciel. De cette façon, le temps de simulation interne n'est pas perturbé et le code ne nécessite aucune modification de la part du concepteur.

Au cours d'une simulation, des évènements sont envoyés au contrôleur *SystemC* sous forme de notifications. Celui-ci évalue et collecte les informations qui sont stockées dans un fichier ou envoyés vers un générateur de métriques externe à la simulation. Ce dernier évalue les performances et émet des statistiques qui sont par la suite envoyées soit vers une interface graphique (GUI) ou vers un programme d'analyse (API). La plateforme se charge de générer des macros permettant l'observation et l'analyse de ces résultats.

De plus, les modules matériels n'influencent pas le temps de simulation alors que

dans les modules logiciels, les instructions sont exécutées cycle par cycle sur l'ISS (processeur) et peuvent de ce fait modifier le temps global de simulation. Ainsi, la plateforme s'assure de préserver le temps de simulation en générant de façon automatique les macros chargées de collecter les données générées lors de la simulation. À travers ces données, on obtient des informations sur le degré de parallélisme du système permettant ainsi de déterminer son orientation de type flot de données (matériel) ou contrôle (logiciel) ce qui détermine le choix du partitionnement logiciel/matériel destiné à être intégré sur un FPGA..

#### **1.2.4 Vers un modèle RTL dans EDK**

La plateforme fournit toute l'architecture matérielle destinée à la plateforme *EDK* (Embedded Development Kit) de *Xilinx*. Elle inclut tous les outils nécessaires à une implémentation au niveau RTL. L'outil Forte Cynthesizer, intégré à *Space Codesign*, permet de passer du niveau système au niveau RTL. Il peut synthétiser les opérations arithmétiques et logiques , le flot de contrôle, les boucles, les appels de fonctions, les tableaux de même que les structures définies par le concepteur. Toutefois, l'allocation dynamique de mémoire n'est pas supportée ce qui fait que les modules TLM et les générateurs des communications doivent supporter ces restrictions. De plus, les modules synthétisés par l'outil occupent généralement plus de ressources que ceux qui auraient pu être faits manuellement, car ces derniers sont optimisés de façon spécifique pour chaque module alors que les optimisations sous Forte Cynthesizer sont générales à tous les modules.

Le passage de la plateforme *Space Codesign* à la plateforme RTL *EDK* est assurée par l'outil GenX de Space Codesign. Il remplace tous les modèles fonctionnels des bus, adaptateurs, processeurs, mémoires et périphériques par leurs équivalents RTL

existant dans la plateforme.