|                         | A Wireless, High-Voltage Compliant, and Energy-Efficient Visual<br>Intracortical Microstimulator                                                                                                                                                                                          |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Md Hasanuzzaman                                                                                                                                                                                                                                                                           |

| Date:                   | 2016                                                                                                                                                                                                                                                                                      |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                                 |

| Référence:<br>Citation: | Hasanuzzaman, M. (2016). A Wireless, High-Voltage Compliant, and Energy-<br>Efficient Visual Intracortical Microstimulator [Thèse de doctorat, École<br>Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/2245/">https://publications.polymtl.ca/2245/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/2245/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Mohamad Sawan, & Rabin Raut           |

| Programme:                               | génie électrique                      |

## UNIVERSITÉ DE MONTRÉAL

# A WIRELESS, HIGH-VOLTAGE COMPLIANT, AND ENERGY-EFFICIENT VISUAL INTRACORTICAL MICROSTIMULATOR

# MD HASANUZZAMAN DÉPARTEMENT DE GÉNIE ÉLECTRIQUE POLYTECHNIQUE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE PHILOSOPHIÆ DOCTOR (GÉNIE ÉLECTRIQUE) JUIN 2016

## UNIVERSITÉ DE MONTRÉAL

# POLYTECHNIQUE MONTRÉAL

## Cette thèse intitulée :

# A WIRELESS, HIGH-VOLTAGE COMPLIANT, AND ENERGY-EFFICIENT VISUAL INTRACORTICAL MICROSTIMULATOR

présentée par : HASANUZZAMAN MD

en vue de l'obtention du diplôme de : <u>Philosophiæ Doctor</u> a été dûment acceptée par le jury d'examen constitué de :

- M. SAVARIA Yvon, Ph. D., président

- M. SAWAN Mohamad, Ph. D., membre et directeur de recherche

- M. <u>RAUT Rabin</u>, Ph. D., membre et codirecteur de recherche

- M. LESAGE Frédéric, Ph. D., membre

- M. LIAN YONG Peter, Ph. D., membre externe

## **DEDICATION**

$To\ my\ parents,\ grandparents,\ sisters,\ brother-in-laws,\ nephews,\ uncles,\ aunts,\ and\ cousins.$

. . .

#### ACKNOWLEDGMENTS

All praise and glory for our Creator, The Almighty God (Allah (subhanu ta'ala)) for granting me life. I have the deepest gratitude to Him for bestowing me with pure knowledge without which I would not be able to read, write, and learn. Then I have my heartfelt gratefulness to my supervisor Dr. Mohamad Sawan for giving me the opportunity to pursue my Ph.D. program under his supervision, mentoring and helping me in research throughout my journey to achieve my goal in Polytechnique Montreal. I would also like to express my gratitude to him for entitling me in his team to work on an exciting and promising project. My heartfelt gratitude also goes for my co-supervisor Dr. Rabin Raut for his counsel and help in my endeavor.

I express my sincere thanks and gratitude to Dr. Yvon Savaria, Dr. Frédéric Lesage, Dr. Yong Lian, and Dr. Julien Cohen-Adad for agreeing to be members of the examination board of my Ph.D. thesis.

Several people in the Polystim Neurotech team have been of invaluable assistance at one time or another for a long time. I specially thank LASEM laboratory co-ordinator Laurent Mouden for his technical help in the assembly of my developed system. Next, I thank Rejean Lepage, Jean Bouchard, Jacques Girardin, and Brian Tremblay for their technical supports. I thank the secretaries, especially Marie-Yannick Laplante and others of the Electrical Engineering Department for their cooperation.

I also thank Faycal Mounaim, Goutam Chandra Kar, Bahareh Ghane-Motlagh, Meghan Watson, Ahmad Hassan, Aref Tregui, Moez Bouali, Sreenil Saha, Sami Hached, Arash Moradi, Ghazal Nabovati, and others. I thank my other friends in laboratories M-5304, M-5306, M-5308, Polystim, and GR2M for being kind to me.

I earnestly want to express my deepest gratitude to my parents, grandparents, sisters and their families, my uncles, and aunts for their encouragements in my higher education.

I also would like to acknowledge the financial support from the Canada Research Chair in smart medical devices, the National Science and Engineering Research Council (NSERC) of Canada, and Fonds de la recherche québécoise sur la nature et les technologies (FRQNT), without which I could not accomplish my research and study.

In the end, my thank goes for CMC Microsystems for supporting me with their design tools and integrated circuits manufacturing facilities.

## RÉSUMÉ

L'objectif général de ce projet de recherche est la conception, la mise en œuvre et la validation d'une interface sans fil intracorticale implantable en technologie CMOS avancée pour aider les personnes ayant une déficience visuelle. Les défis majeurs de cette recherche sont de répondre à la conformité à haute tension nécessaire à travers l'interface d'électrode-tissu (IET), augmenter la flexibilité dans la microstimulation et la surveillance multicanale, minimiser le budget de puissance pour un dispositif biomédical implantable, réduire la taille de l'implant et améliorer le taux de transmission sans fil des données. Par conséquent, nous présentons dans cette thèse un système de microstimulation intracorticale multi-puce basée sur une nouvelle architecture pour la transmission des données sans fil et le transfert de l'énergie se servant de couplages inductifs et capacitifs.

Une première puce, un générateur de stimuli (SG) éconergétique, et une autre qui est un amplificateur de haute impédance se connectant au réseau de microélectrodes de l'étage de sortie. Les 4 canaux de générateurs de stimuli produisent des impulsions rectangulaires, demi-sinus (DS), plateau-sinus (PS) et autres types d'impulsions de courant à haut rendement énergétique. Le SG comporte un contrôleur de faible puissance, des convertisseurs numérique-analogiques (DAC) opérant en mode courant, générateurs multi-forme d'ondes et miroirs de courants alimentés sous 1.2 et 3.3V se servant pour l'interface entre les deux technologies utilisées. Le courant de stimulation du SG varie entre 2.32 et  $220\mu$ A pour chaque canal.

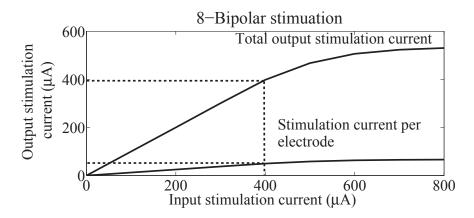

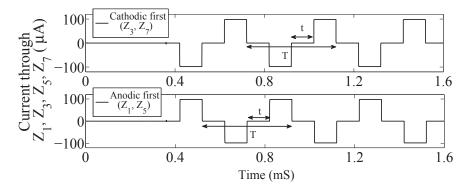

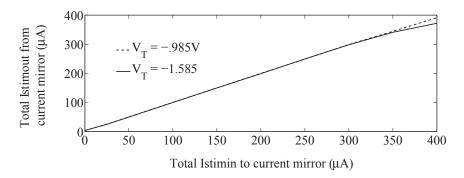

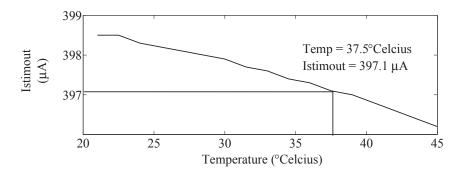

La deuxième puce (pilote de microélectrodes (MED)), une interface entre le SG et de l'arrangement de microélectrodes (MEA), fournit quatre niveaux différents de courant avec la valeur maximale de  $400\mu$ A par entrée et  $100\mu$ A par canal de sortie simultanément pour 8 à 16 sites de stimulation à travers les microélectrodes, connectés soit en configuration bipolaire ou monopolaire. Cette étage de sortie est hautement configurable et capable de délivrer une tension élevée pour satisfaire les conditions de l'interface à travers l'impédance de IET par rapport aux systèmes précédemment rapportés. Les valeurs nominales de plus grandes tensions d'alimentation sont de  $\pm 10$ V. La sortie de tension mesurée est conformément 10V/phase (anodique ou cathodique) pour les tensions d'alimentation spécifiées. L'incrémentation de tensions d'alimentation à  $\pm 13$ V permet de produire un courant de stimulation de  $220\mu$ A par canal de sortie permettant d'élever la tension de sortie jusqu'au 20V par phase. Cet étage de sortie regroupe un commutateur haute tension pour interfacer une matrice des miroirs de courant (3.3V /20V), un registre à décalage de 32-bits à entrée sérielle, sortie parallèle, et un circuit dédié pour bloquer des états interdits.

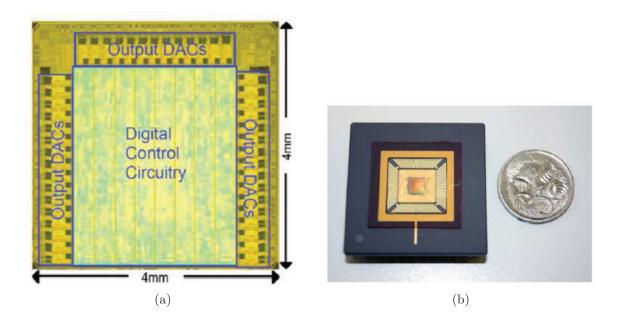

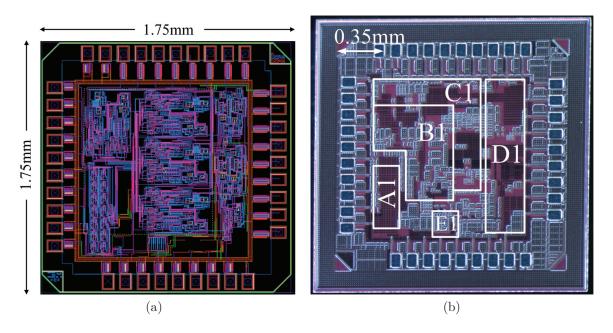

Les deux puces ont été conçues et fabriquées avec les technologies IBM CMOS  $0.13\mu m$  et Teledyne DALSA  $0.8\mu m$  5V/20V CMOS/DMOS avec des surfaces de silicium de  $1.75 \times 1.75 mm^2$  et  $4 \times 4 mm^2$  respectivement. Les budgets d'alimentation consommés par les puces basse et moyenne tensions ont été mesurées à 2.56 et 2.1 mW consécutivement.

Ajoutons qu'un nouveau protocole de transfert bidirectionnel sans fil de données par le biais d'une liaison capacitive, qui est basée sur le principe de position spatiale de modulation par impulsion (SPPM). Cette liaison a été proposée par Polystim team pour transmettre des données à 10Mbps au microstimulateur à travers la peau. Le microstimulateur récupère l'énergie sans fil via une autre liaison inductive, accordée sur une porteuse à une fréquence de 13.56MHz. Le module de microstimulation (MS), combinant le SG et le pilote de microélectrodes, à une architecture modulaire et a été interfacé avec un arrangement de microélectrodes en format pyramidal développé par Polystim team pour atteindre différents niveaux de neurones dans le cortex visuel primaire. L'ensemble du système proposé a été validé par des tests in vitro dans une solution saline (NaCl 0.15M) et les résultats expérimentaux démontrent l'efficacité du prototype complété.

#### **ABSTRACT**

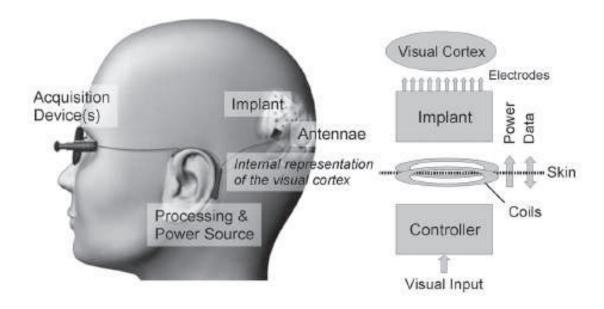

The general objective of this research project is the design, implementation and validation of an implantable wireless intracortical interface in advanced CMOS technology to aid the visually impaired people. The major challenges in this research are to meet the required high-voltage compliance across electrode-tissue interface (ETI), increase flexibility in multichannel microstimulation and monitoring, minimize power budget for an implantable biomedical device, reduce the implant size, and enhance the data rate in wireless transmission. Therefore, we present in this thesis a multi-chip intracortical microstimulation system based on a novel architecture for wireless data and power transmission comprising inductive and capacitive couplings.

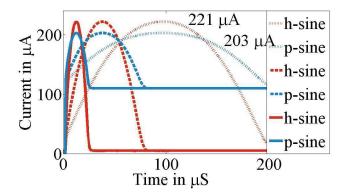

The first chip is an energy-efficient stimuli generator (SG) and the second one is a high-impedance microelectrode array driver output-stage. The 4-channel stimuli-generator produces rectangular, half-sine (HS), plateau-sine (PS), and other types of energy-efficient current pulse. The SG is featured with low-power controller, current mode source- and sink-digital-to-analog converters (DACs), multi-waveform generators, and 1.2V/3.3V interface current mirrors. The stimulation current per channel of the SG ranges from 2.32 to  $220\mu$ A per channel.

The second chip (microelectrode driver (MED)), an interface between the SG and the microelectrode array (MEA), supplies four different current levels with the maximum value of  $400\mu$ A per input and  $100\mu$ A per output channel. These currents can be delivered simultaneously to 8 to 16 stimulation sites through microelectrodes, connected either in bipolar or monopolar configuration. This output stage is highly-configurable and able to deliver higher compliance voltage across ETI impedance compared to previously reported designs. The nominal values of largest supply voltages are  $\pm 10$ V. The measured output compliance voltage is 10V/phase (anodic or cathodic) for the specified supply voltages. Increment of supply voltages to  $\pm 13$ V allows  $220\mu$ A stimulation current per output channel enhancing the output compliance voltage up to 20V per phase. This output-stage is featured with a high-voltage switch-matrix, 3.3V/20V current mirrors, an on-chip 32-bit serial-in parallel-out shift register, and the forbidden state logic building blocks.

The SG and MED chips have been designed and fabricated in IBM  $0.13\mu m$  CMOS and Teledyne DALSA  $0.8\mu m$  5V/20V CMOS/DMOS technologies with silicon areas occupied by them  $1.75 \times 1.75mm^2$  and  $4 \times 4mm^2$  respectively. The measured DC power budgets consumed by low-and mid-voltage microchips are 2.56 and 2.1mW consecutively.

On the other hand, a new capacitive link-based bi-directional wireless data transfer protocol,

which works on spatial pulse position modulation (SPPM) principle, has been implemented to transmit data at 3Mbps to the microstimulator through skin. Power is recovered wirelessly through an inductive-link, which is tuned at 13.56MHz carrier frequency. The microstimultion module (MS), combining the SG and MED, is modular in architecture and has been interfaced with a newly developed, by Polystim team, platinum coated pyramidal shaped microelectrode array (MEA), which can reach the different levels of neurons in the primary visual cortex. The multichip system has been successfully validated through in-vitro tests in 0.15M NaCl saline and the experimental results confirm the efficacy of the completed prototype.

# TABLE OF CONTENTS

| DEDICA | ATION                                                  |

|--------|--------------------------------------------------------|

| ACKNO  | WLEDGMENTS iv                                          |

| RÉSUM  | É                                                      |

| ABSTR  | ACT vi                                                 |

| LIST O | F TABLES xii                                           |

| LIST O | F FIGURES xiv                                          |

| LIST O | F APPENDICES                                           |

| LIST O | F ABREVIATIONS AND NOTATIONS                           |

| СНАРТ  | ER 1 INTRODUCTION                                      |

| 1.1    | Organisation of the thesis                             |

| СНАРТ  | ER 2 MICROSTIMULATION BASICS                           |

| 2.1    | Introduction                                           |

| 2.2    | Functional electrical stimulation                      |

|        | 2.2.1 Category of FES                                  |

|        | 2.2.2 Parameters of FES                                |

|        | 2.2.3 Stimulation waveforms                            |

| 2.3    | Microelectrodes                                        |

|        | 2.3.1 Working principle of stimulation microelectrodes |

|        | 2.3.2 Equivalent circuit of electrode                  |

| 2.4    | Visual system                                          |

| 2.5    | Primary visual cortex                                  |

| 2.6    | Neuron                                                 |

| 2.7    | The cytoplasmic membrane                               |

| 2.8    | Action potential                                       |

| 2.9    | Propagation of an action potential                     |

| 2.10   | Conclusion                                             |

| CHAPT | TER 3  | LITERATURE REVIEW AND THE PROPOSED SYSTEM                       |

|-------|--------|-----------------------------------------------------------------|

| 3.1   | Introd | $\operatorname{uction}$                                         |

| 3.2   | FES b  | ased prosthetic approaches to restore sight                     |

| 3.3   | Retina | l implant                                                       |

|       | 3.3.1  | Epi-retinal implant                                             |

|       | 3.3.2  | Sub-retinal implant                                             |

| 3.4   | Optic  | nerve microstimulation                                          |

| 3.5   | Visual | prosthesis using cortical microstimulation                      |

|       | 3.5.1  | Early works on visual cortex and intracortical microstimulation |

|       | 3.5.2  | Progress in physiological experiments                           |

| 3.6   | Genera | al architecture of the visual intracortical implant             |

|       | 3.6.1  | Implant developed at the Illinois Institute of Technology       |

|       | 3.6.2  | First system designed at the University of Michigan             |

|       | 3.6.3  | Second system developed at the University of Michigan           |

|       | 3.6.4  | Cortivision project at the Polytechnique Montreal               |

|       | 3.6.5  | Monash Vision Group                                             |

|       | 3.6.6  | Research Group at the University of Duke                        |

| 3.7   | Archit | ectures' comparison of visual prosthetic implants               |

| 3.8   | Hypot  | hesis and research contributions                                |

|       | 3.8.1  | Research questions                                              |

|       | 3.8.2  | Objectives                                                      |

|       | 3.8.3  | Scientific hypothesis of contributions                          |

| 3.9   | An ove | erview of the proposed system                                   |

| 3.10  | Conclu | nsion                                                           |

| СНАРТ | ER 4   | THE PROPOSED SYSTEM AND THE STIMULI-GENERATOR                   |

| 4.1   | Introd | uction                                                          |

| 4.2   | The pr | roposed system                                                  |

|       | 4.2.1  | Microstimulation module (MSM)                                   |

| 4.3   | The er | nergy-efficient and multi-waveform stimuli-generator            |

|       | 4.3.1  | Introduction                                                    |

|       | 4.3.2  | Exploration of energy-efficient waveforms                       |

|       | 4.3.3  | The proposed stimuli generator (SG)                             |

|       | 4.3.4  | Post-layout simulation and measurement results                  |

| 4.4   | Conclu | asion                                                           |

| СНАРТ | ER 5   | HIGH-VOLTAGE COMPLIANT MICROELECTRODE DRIVERS                   |

| 5.1   | Introduction                                                        | 80              |

|-------|---------------------------------------------------------------------|-----------------|

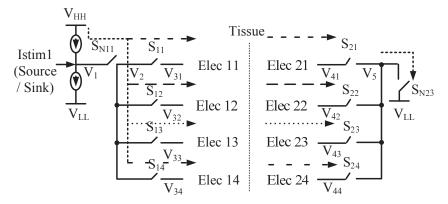

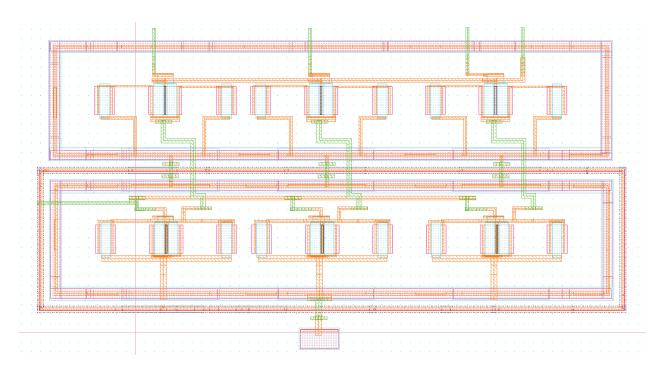

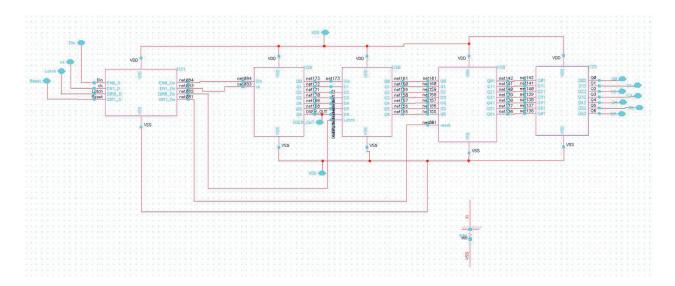

| 5.2   | Proposed microelectrode drivers                                     | 81              |

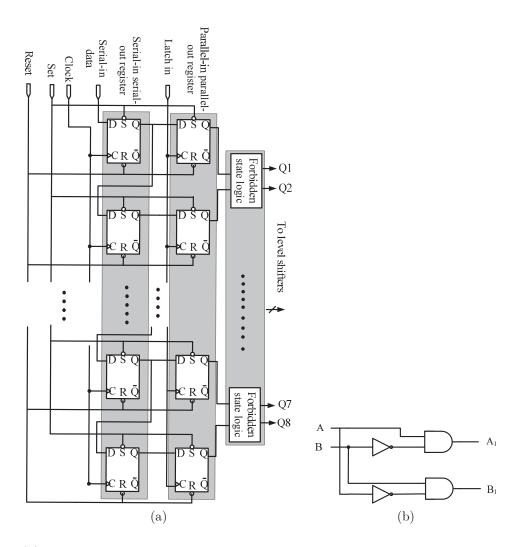

|       | 5.2.1 32-bit serial-in parallel-out shift register                  | 83              |

|       | 5.2.2 Forbidden state logic circuit                                 | 84              |

|       | 5.2.3 High-voltage level shifter                                    | 87              |

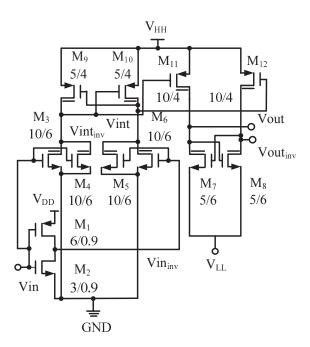

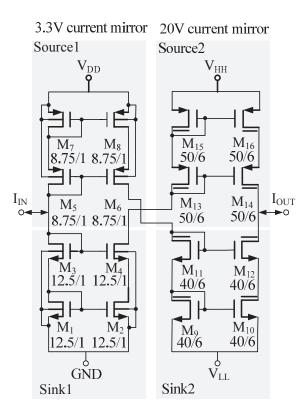

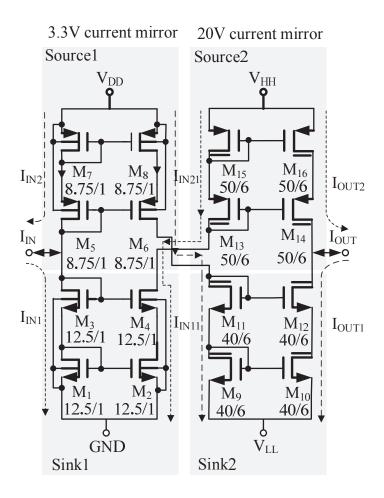

|       | 5.2.4 3.3V/20V current mirror                                       | 89              |

|       | 5.2.5 High-voltage switching                                        | 91              |

| 5.3   | Microelectrode model                                                | 93              |

| 5.4   | Results                                                             | 94              |

|       | 5.4.1 Post-layout simulation results                                | 95              |

|       | 5.4.2 Measurement results                                           | 99              |

| 5.5   | Conclusion                                                          | 06              |

| СНАРТ | TER 6 THE POWER AND DATA RECOVERY UNITS                             | 07              |

| 6.1   | Introduction                                                        | 07              |

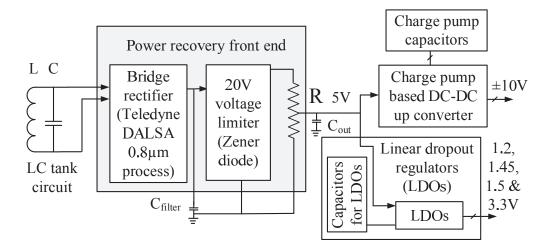

| 6.2   | Power recovery unit                                                 | 07              |

|       | 6.2.1 Proposed power recovery unit                                  | 08              |

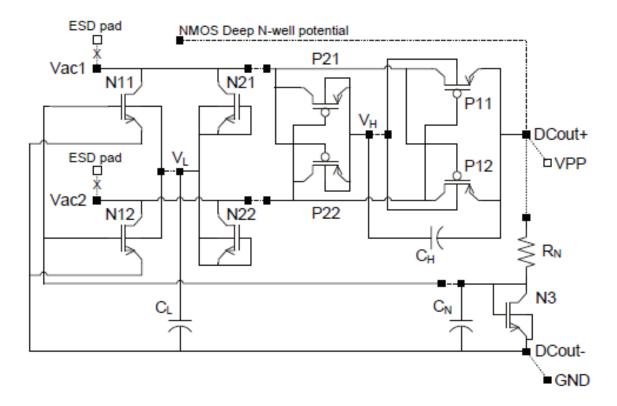

|       | 6.2.2 Full-wave bridge rectifier                                    | 09              |

|       |                                                                     | 10              |

| 6.3   |                                                                     | 13              |

|       | 6.3.1 Modeling of capacitive skin                                   | 15              |

|       |                                                                     | 17              |

|       | 6.3.3 System implementation, experimental results, and comparison 1 | 22              |

| 6.4   | Conclusion                                                          | 24              |

| CHAPT | ΓER 7 MONITORING UNIT, ASSEMBLY, AND VALIDATION 1                   | 26              |

| 7.1   | ,                                                                   | 26<br>26        |

| 7.1   |                                                                     | 26<br>26        |

| 1.2   |                                                                     | $\frac{20}{27}$ |

| 7.3   | •                                                                   | 21<br>28        |

|       |                                                                     | 20<br>29        |

| 7.4   | J                                                                   |                 |

| 7.5   | •                                                                   | 31              |

|       | J.                                                                  | 32              |

|       |                                                                     | 34              |

| 7.0   | •                                                                   | 35              |

| 7.6   | Conclusion                                                          | 37              |

| CHAP   | TER 8 CONCLUSION | 139 |

|--------|------------------|-----|

| 8.1    | Summary of work  | 139 |

| 8.2    | Contributions    | 141 |

| 8.3    | Achievements     | 142 |

| 8.4    | Recommendations  | 143 |

| 8.5    | Publications     | 146 |

| BIBLIC | OGRAPHY          | 148 |

| APPEN  | NDICES           | 164 |

# LIST OF TABLES

| Table 3.1 | Comparison of main visual intracortical implants                        | 51  |

|-----------|-------------------------------------------------------------------------|-----|

| Table 4.1 | Charge quantity (nC) delivered by the waveforms                         | 75  |

| Table 4.2 | Specifications and performance results summary                          | 78  |

| Table 5.1 | Truth table for forbidden state logic circuit                           | 86  |

| Table 5.2 | Specifications for ICJPM011 (MED1) and ICJPMSMX (MED2)                  | 97  |

| Table 5.3 | Comparison with other works                                             | 105 |

| Table 6.1 | Received signals for different sizes of capacitor plates [163]. © IEEE. | 120 |

| Table 6.2 | Results comparison with recently published data transceivers            | 124 |

| Table 7.1 | Performance comparison of the microstimulators                          | 136 |

| Table 7.2 | Performance comparison of the data and power recovery units             | 137 |

# LIST OF FIGURES

| Figure 2.1  | Stimulation parameters                                           | 8  |

|-------------|------------------------------------------------------------------|----|

| Figure 2.2  | Various types of constant current pulses                         | 10 |

| Figure 2.3  | Modes of electrode configuration for stimulation                 | 11 |

| Figure 2.4  | Strength–duration curve for activation of an action potential    | 12 |

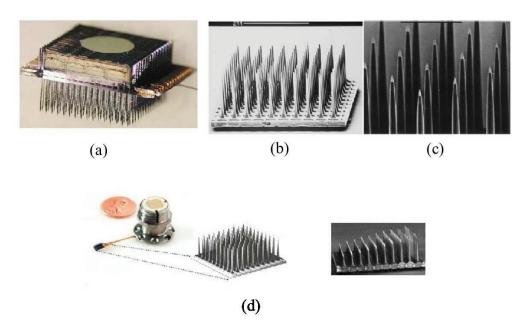

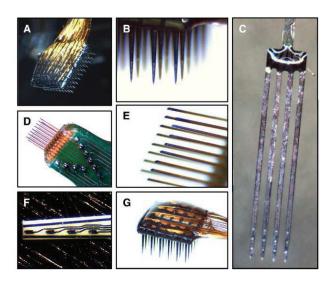

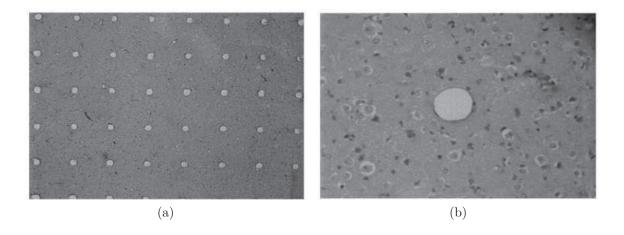

| Figure 2.5  | Silicon based microelectrode arrays                              | 14 |

| Figure 2.6  | Silicon based microelectrodes from Cyberkinetics                 | 15 |

| Figure 2.7  | Silicon on insulator, Polymar based, and Micralyne MEAs          | 15 |

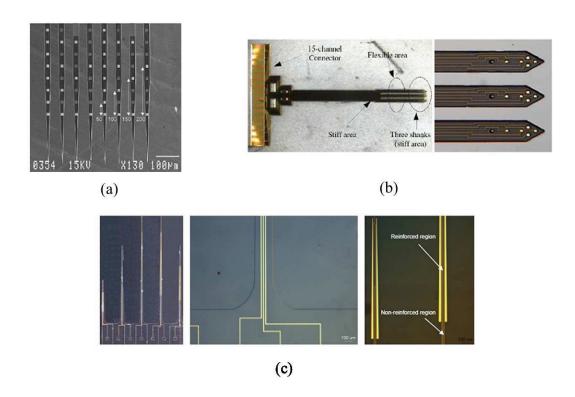

| Figure 2.8  | Equivalent circuit models for electrode-tissues interface (ETI)  | 16 |

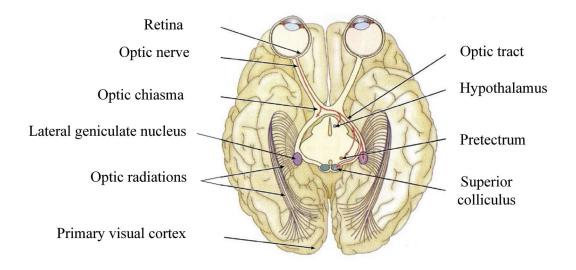

| Figure 2.9  | Modified version of the anatomy of the human visual system [22]  | 18 |

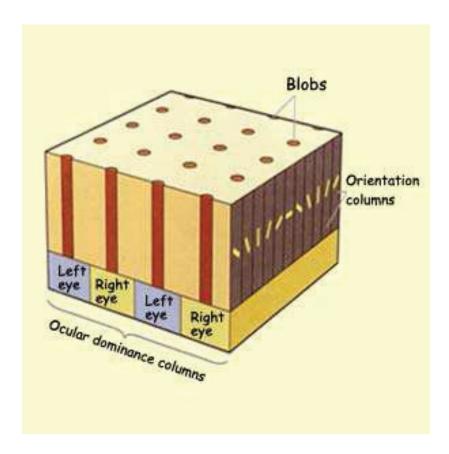

| Figure 2.10 | Organization of the columns in the primary visual cortex         | 19 |

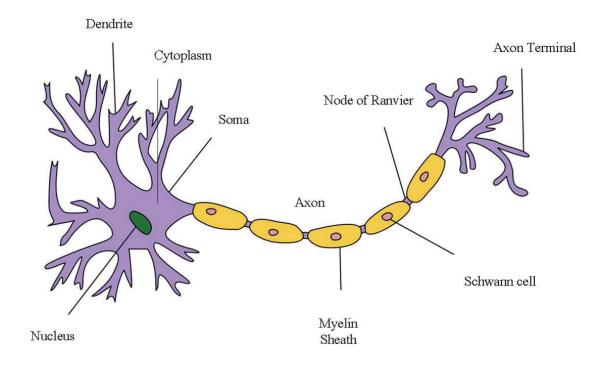

| Figure 2.11 | The anatomy of a neuron (modified version). © [44])              | 20 |

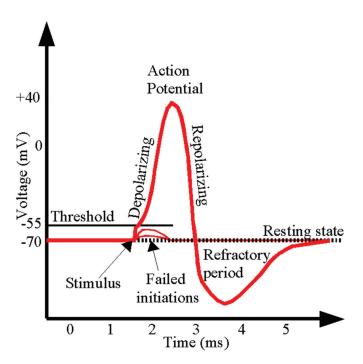

| Figure 2.12 | Action potential generation                                      | 21 |

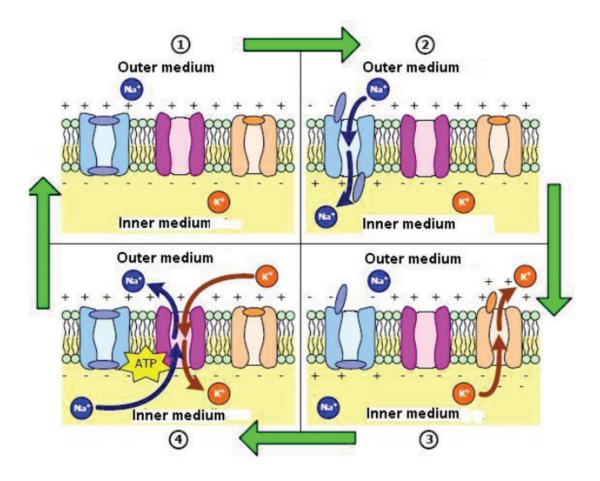

| Figure 2.13 | Mechanism of ion channels in a membrane cell                     | 23 |

| Figure 2.14 | Action potential propagation                                     | 24 |

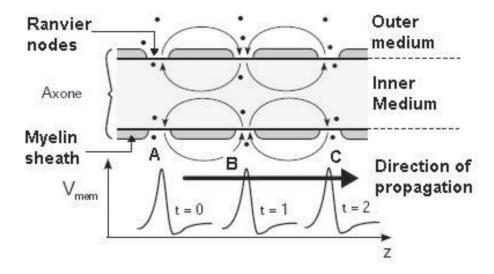

| Figure 3.1  | Types of retinal visual prosthesis                               | 26 |

| Figure 3.2  | Epi-retinal implant developed by Dr. Weiland and his group       | 27 |

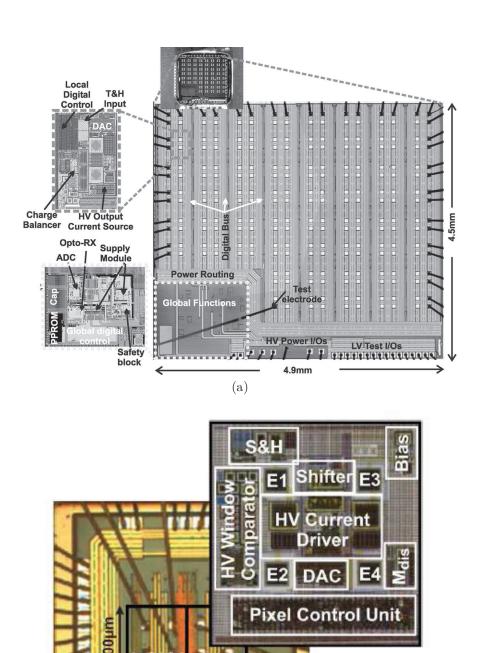

| Figure 3.3  | Retinal stimulator chip designed by M. Ortmanns et al            | 29 |

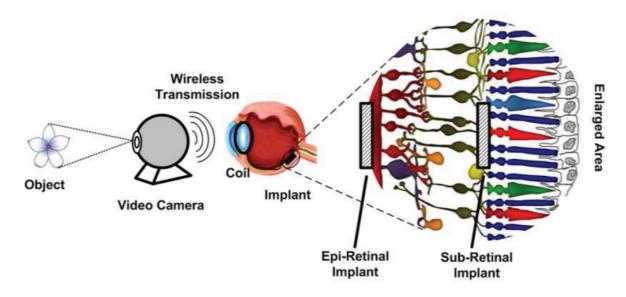

| Figure 3.4  | Retinal stimulator developed by Shawn K. Kelly et al             | 30 |

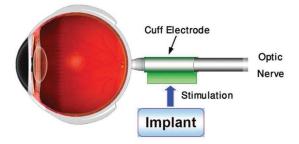

| Figure 3.5  | Optic nerve stimulation                                          | 31 |

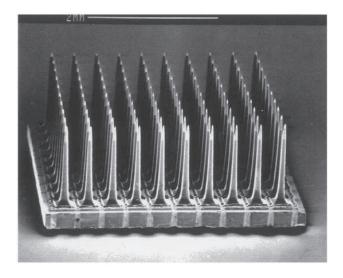

| Figure 3.6  | Silicon-based Utah electrode array                               | 33 |

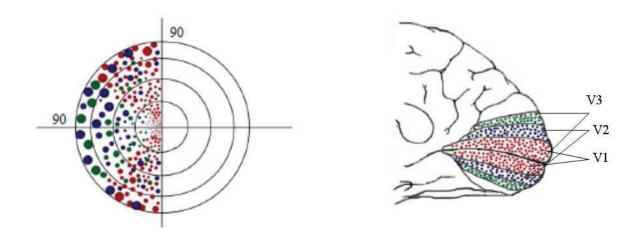

| Figure 3.7  | Physiological experiments with visual cortex                     | 34 |

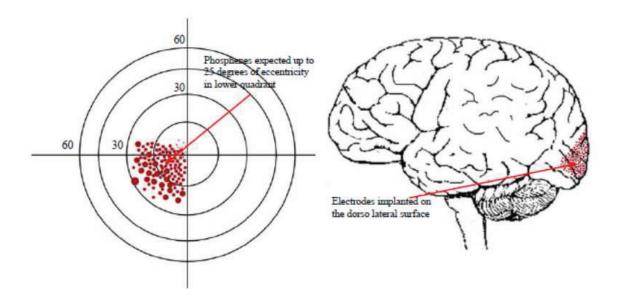

| Figure 3.8  | Visiotopic mapping of visual cortex                              | 34 |

| Figure 3.9  | Expected visiotopic mapping of visual cortex                     | 35 |

| Figure 3.10 | General architecture of a visual intracortical prosthetic device | 36 |

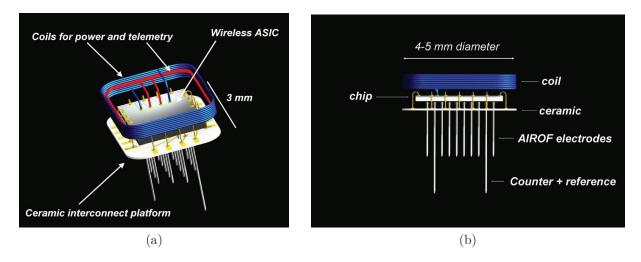

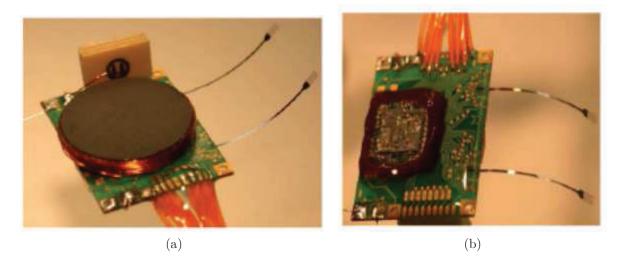

| Figure 3.11 | Implant developed by Troyk's team (a)                            | 37 |

| Figure 3.12 | Implant developed by Troyk's team (b)                            | 38 |

| Figure 3.13 | Implant developed by Troyk's team (c)                            | 38 |

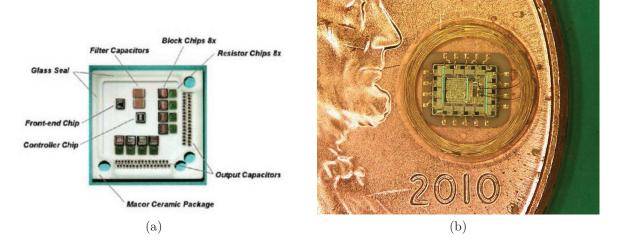

| Figure 3.14 | Implant developed by Ghovanloo et al. (a)                        | 39 |

| Figure 3.15 | Implant developed by Ghovanloo et al. (b)                        | 40 |

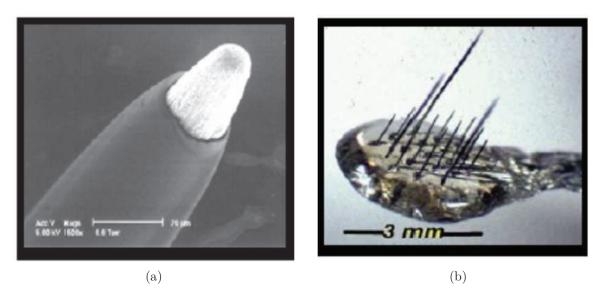

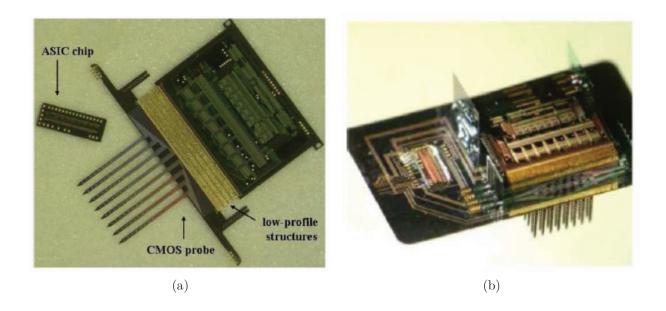

| Figure 3.16 | 64-site eight-channel low-profile stimulating probe              | 41 |

| Figure 3.17 | Photograph of a low-profile 3-D array                            | 41 |

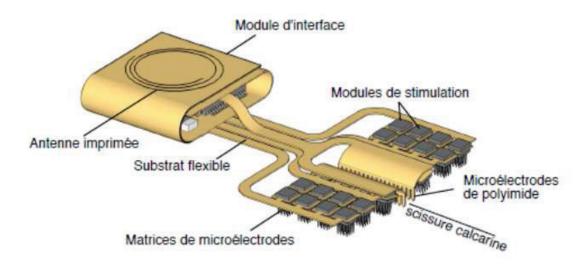

| Figure 3.18 | Sawan's team system: conceptual diagram                          | 42 |

| Figure 3.19 | Sawan's team system: schematic diagram                           | 43 |

|             |                                                                  |    |

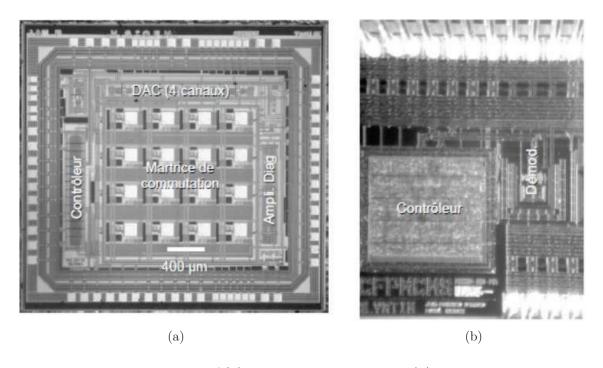

| Figure 3.20 | Chips fabricated for the Cortivision project                      | 43 |

|-------------|-------------------------------------------------------------------|----|

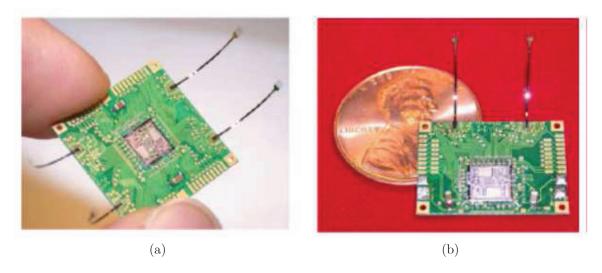

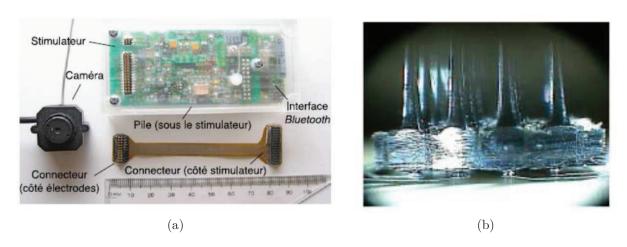

| Figure 3.21 | Portable stimulator developed by J. Coulombe et al                | 44 |

| Figure 3.22 | Portable stimulator developed by J. Coulombe et al                | 44 |

| Figure 3.23 | Chips fabricated by S. Ethier et al                               | 46 |

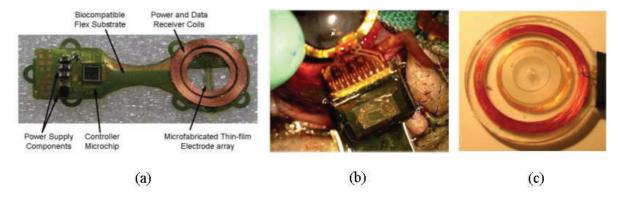

| Figure 3.24 | Various parts of the implant designed in MVG (a)                  | 47 |

| Figure 3.25 | Various parts of the implant designed in MVG (b)                  | 48 |

| Figure 3.26 | The stimulator chip designed in MVG                               | 49 |

| Figure 3.27 | Stimulator developed at the University of Duke                    | 50 |

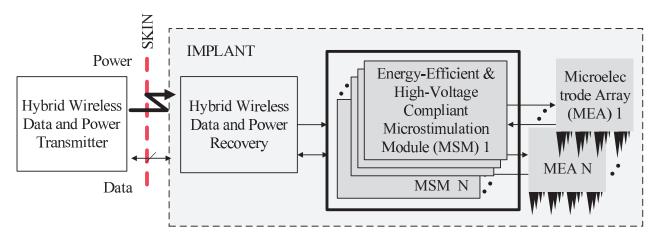

| Figure 3.28 | Overview of the proposed visual intracortical microstimulator     | 55 |

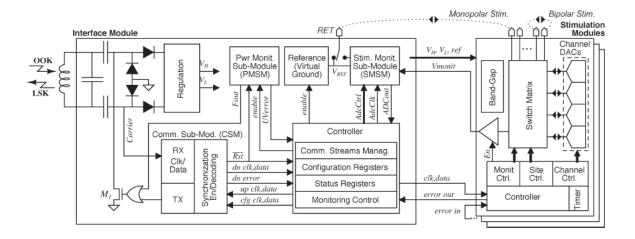

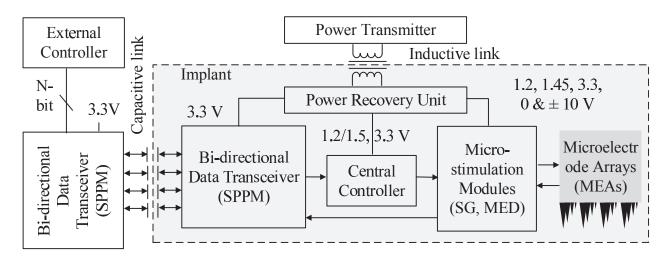

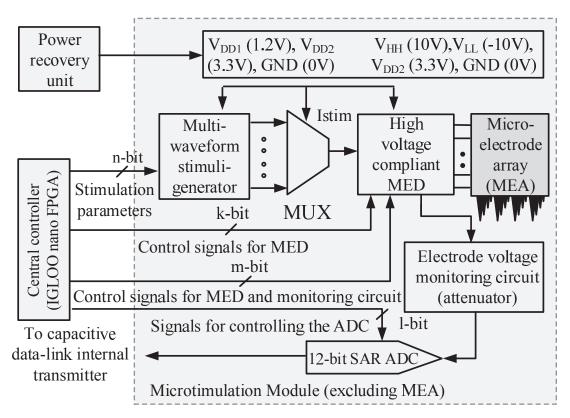

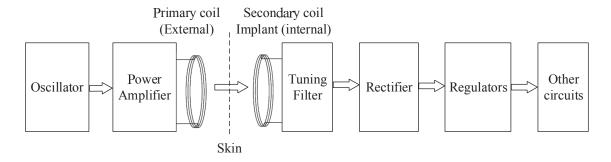

| Figure 4.1  | Architecture of the proposed visual intracortical microstimulator | 57 |

| Figure 4.2  | Architecture of the proposed microstimulation module              | 57 |

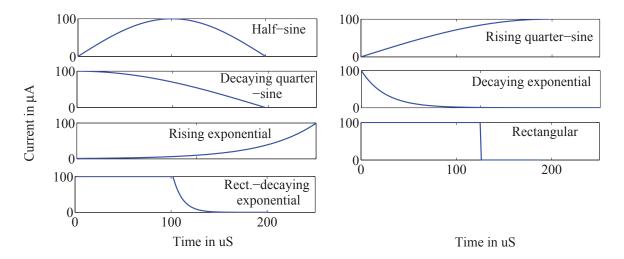

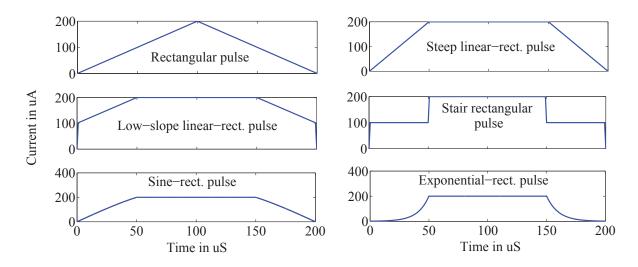

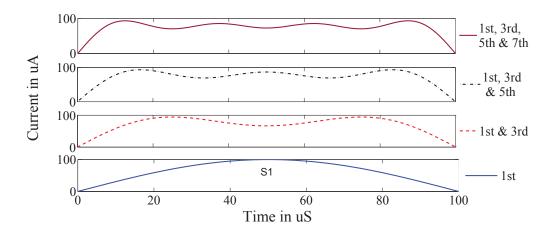

| Figure 4.3  | Waveforms used for efficiency analysis: first group               | 61 |

| Figure 4.4  | Waveforms used for efficiency analysis: second group              | 61 |

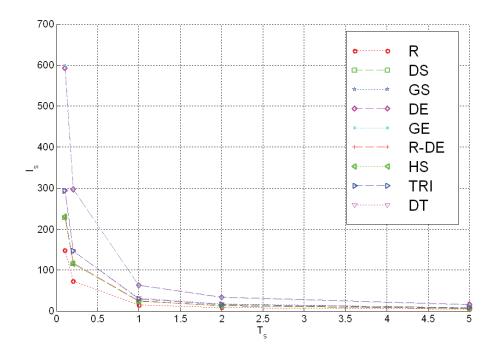

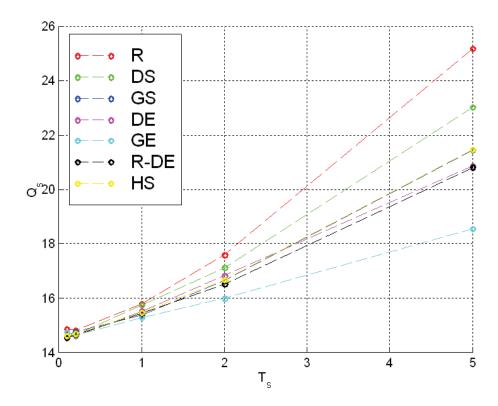

| Figure 4.5  | Strength-duration curves for first group of waveforms             | 62 |

| Figure 4.6  | Total charge delivered Vs pulse width                             | 63 |

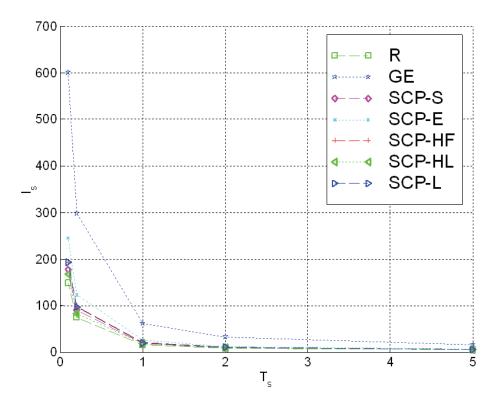

| Figure 4.7  | Strength-duration curves for second group of waveforms            | 64 |

| Figure 4.8  | Waveforms to be used for efficiency analysis: third group         | 64 |

| Figure 4.9  | Architecture of the stimuli generator                             | 65 |

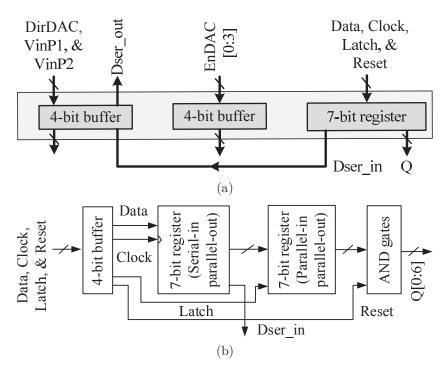

| Figure 4.10 | Digital controller and 7-bit SIPO shift register                  | 66 |

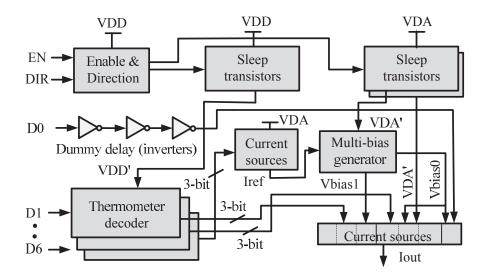

| Figure 4.11 | Block diagram representation of the source DAC                    | 67 |

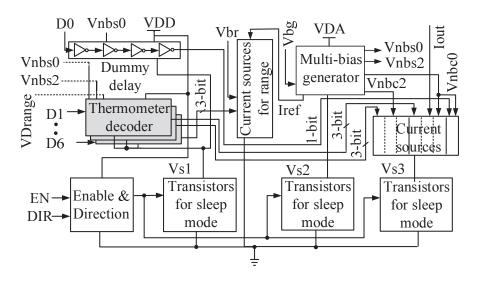

| Figure 4.12 | Architecture of the sink DAC                                      | 67 |

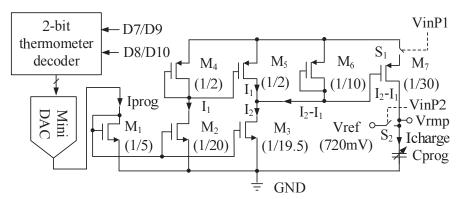

| Figure 4.13 | Block diagram of the thermometer decoder                          | 68 |

| Figure 4.14 | The 2-bit source DAC to set 3 ranges of Iref                      | 68 |

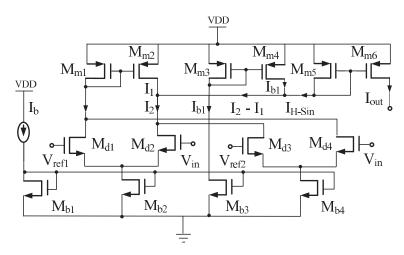

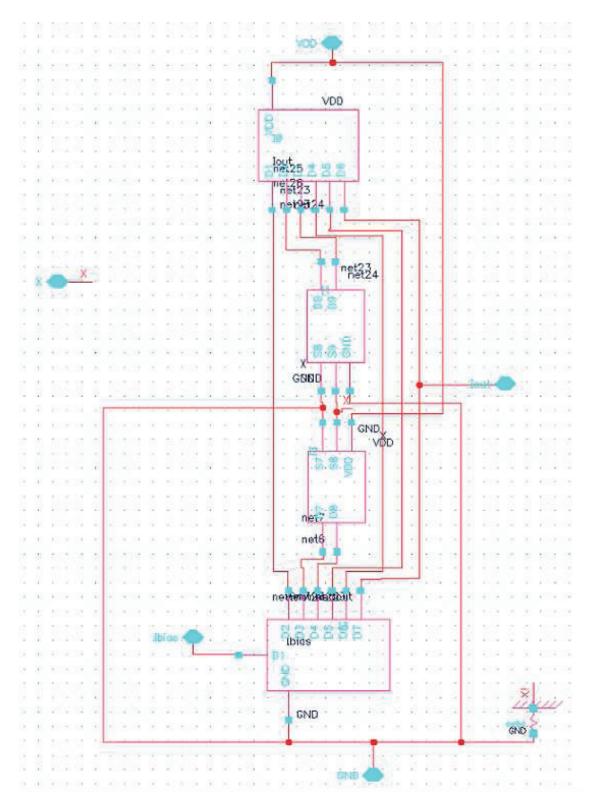

| Figure 4.15 | Circuit diagram of the multibias generator                        | 69 |

| Figure 4.16 | Circuit diagram of current sources used for sink DAC              | 69 |

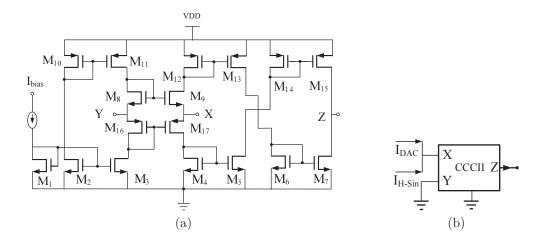

| Figure 4.17 | The schematic representation of the half-sine generator           | 70 |

| Figure 4.18 | Schematic of the programmable ramp voltage generator              | 71 |

| Figure 4.19 | Circuit diagram for the plateau-sine pulse generator              | 72 |

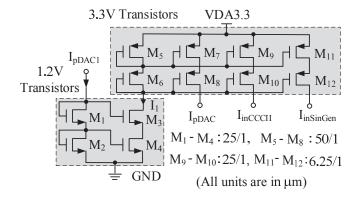

| Figure 4.20 | 1.2V/3.3V source current mirror circuit                           | 73 |

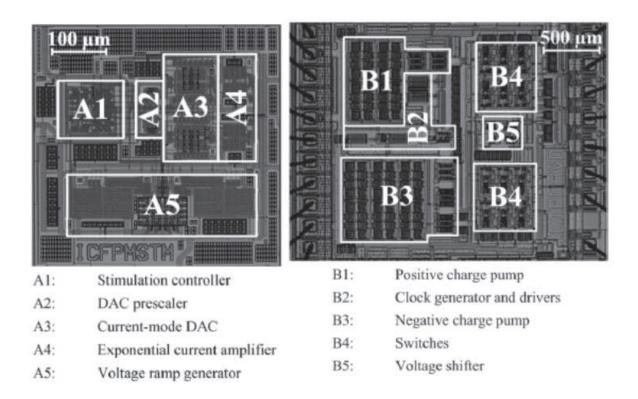

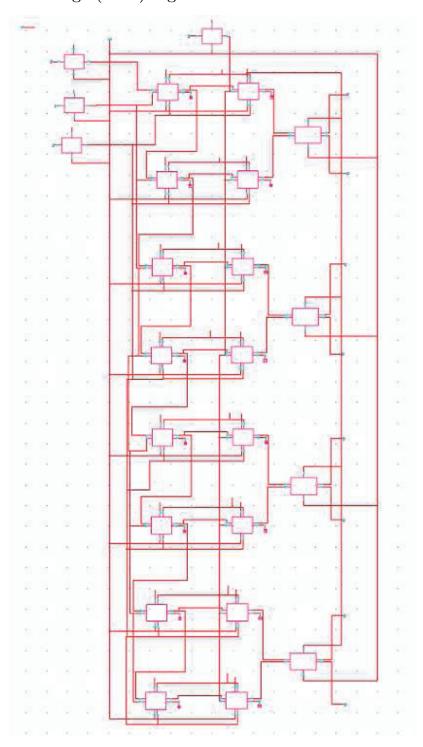

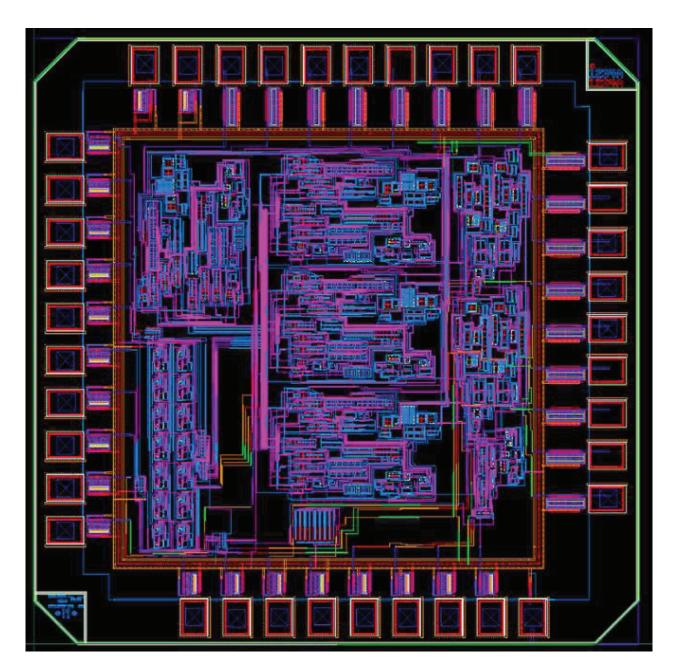

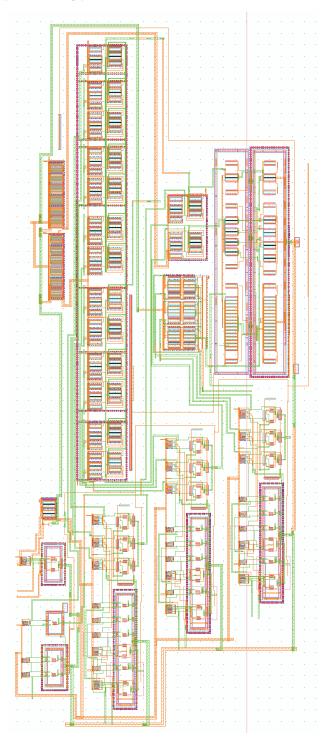

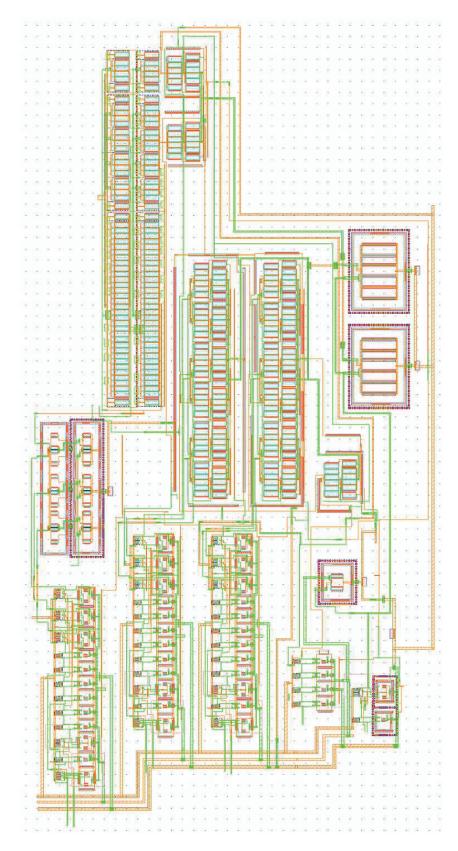

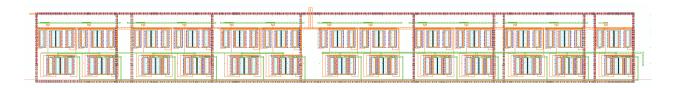

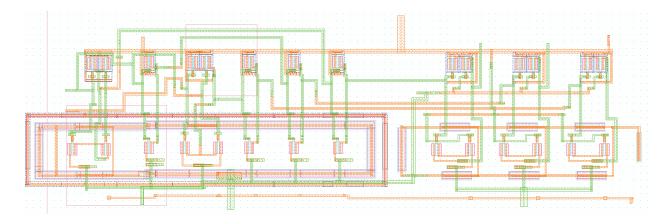

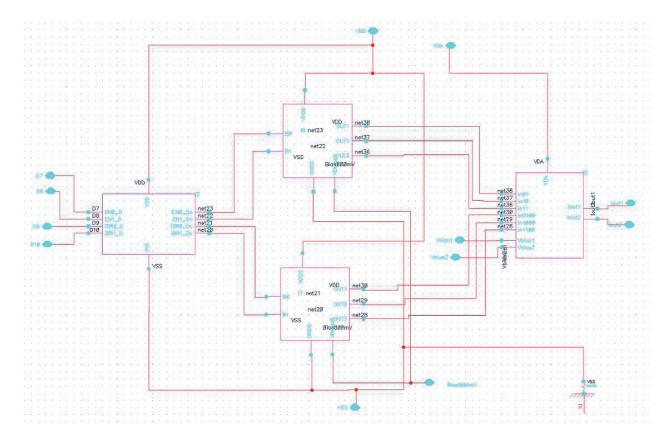

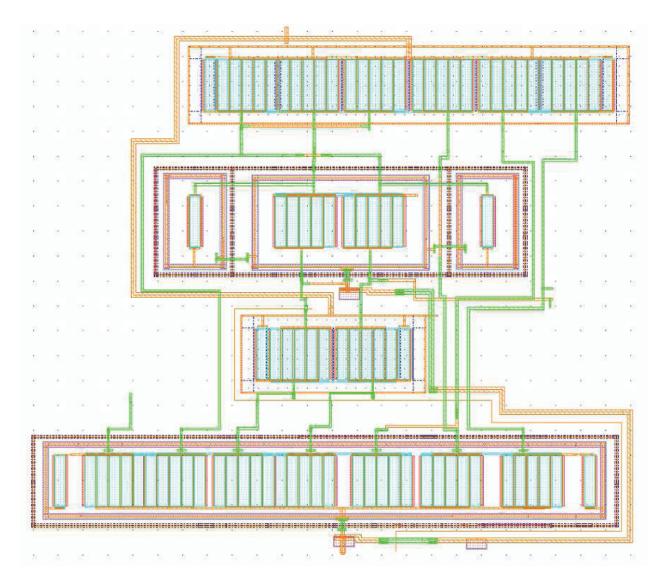

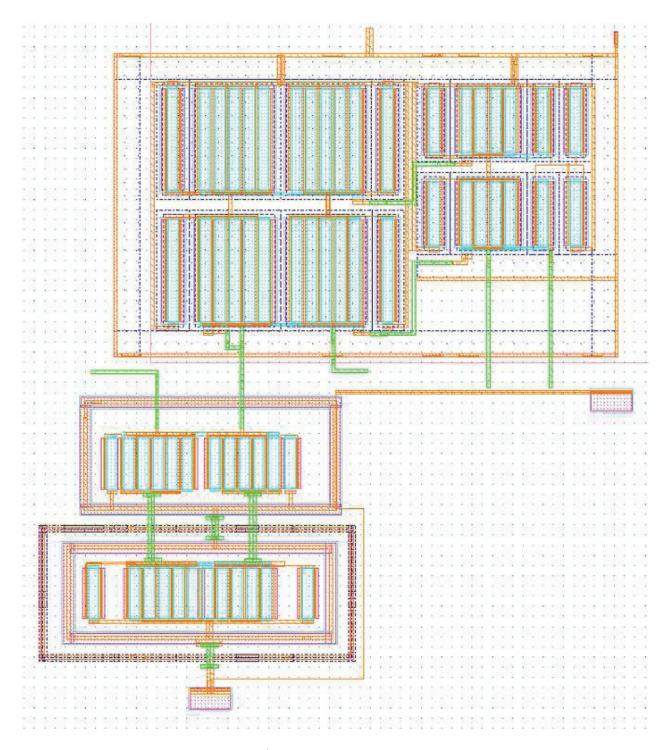

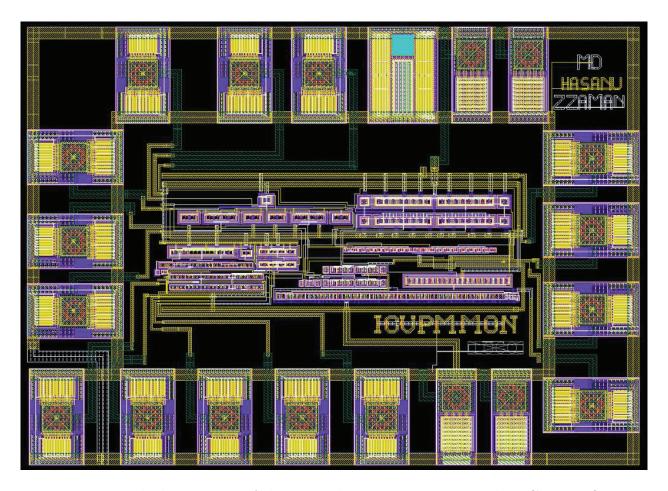

| Figure 4.21 | The stimuli-generator chip: ICGPMSTG                              | 74 |

| Figure 4.22 | Post-layout simulation: generated half- and plateau sine pulses   | 75 |

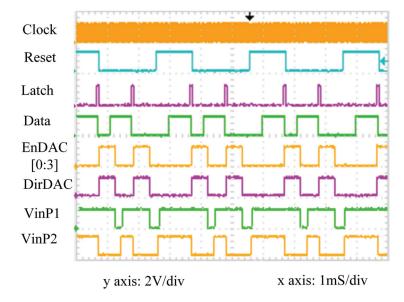

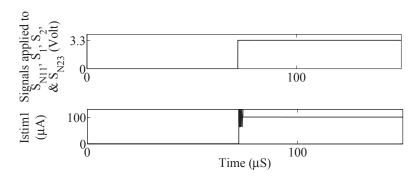

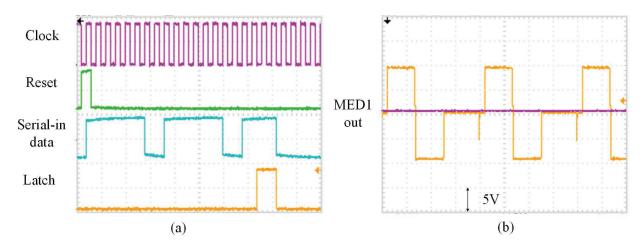

| Figure 4.23 | Control signals applied to the stimuli-generator chip             | 76 |

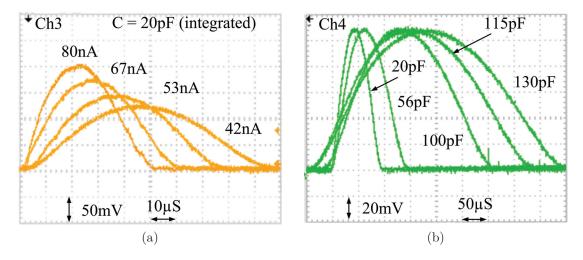

| Figure 4.24 | Experimental results: pulse-width variation of half-sine pulse    | 76 |

| Figure 4.25 | Pulse-width variations of the measured PS pulses                  | 77 |

| Figure 4.26 | Oscilloscope traces of the various forms of current pulses        | 77 |

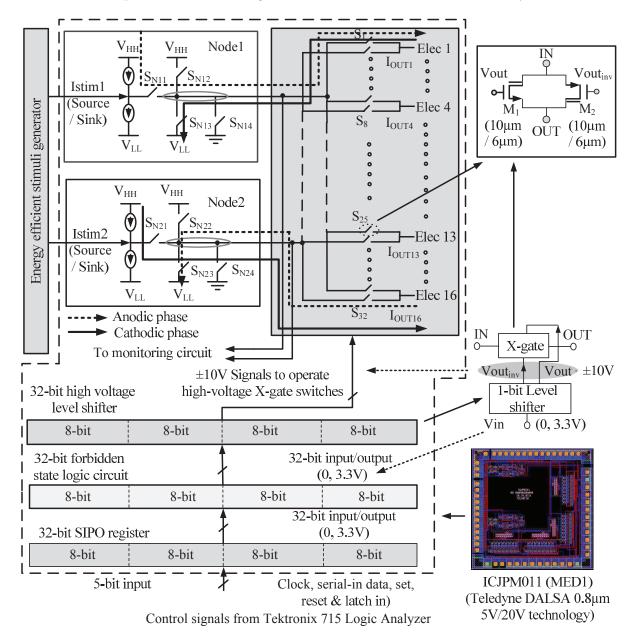

| Figure 5.1  | Architecture of the first high-impedance microelectrode driver    | 82 |

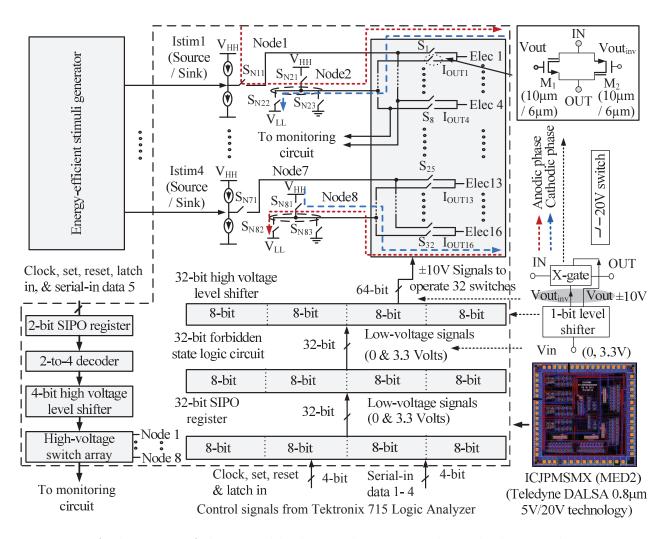

| Figure 5.2  | Architecture of the second high-impedance microelectrode driver                  | 84  |

|-------------|----------------------------------------------------------------------------------|-----|

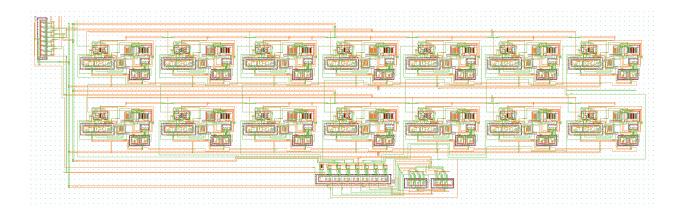

| Figure 5.3  | Block diagram of the 8-bit SIPO shift register and FSLC                          | 85  |

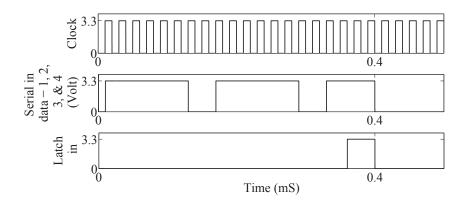

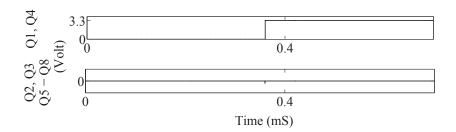

| Figure 5.4  | Control signals for the 32-bit SIPO shift register                               | 86  |

| Figure 5.5  | Signals for controlling 32 high-voltage switches in the switch matrix            | 86  |

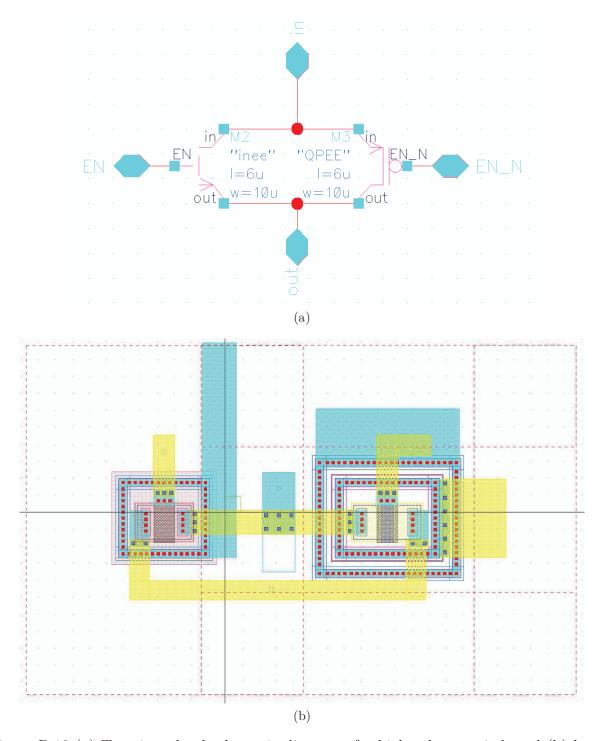

| Figure 5.6  | Circuit diagram of the high-voltage level shifter (LS)                           | 87  |

| Figure 5.7  | Post-layout transient simulation results of the high-voltage LS                  | 88  |

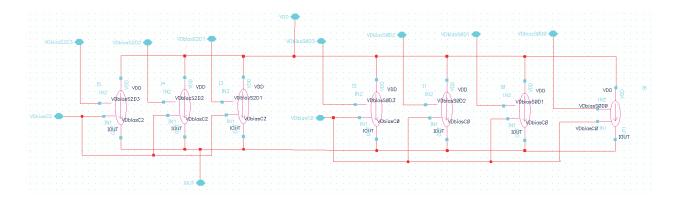

| Figure 5.8  | 3.3V/20V current mirror circuit                                                  | 89  |

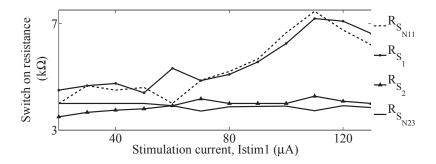

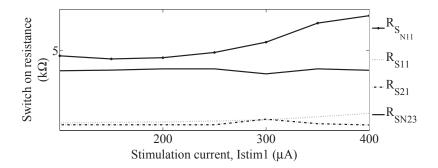

| Figure 5.9  | Schematic for switch ON-resistance calculation in the first scenario             | 92  |

| Figure 5.10 | Diagram for switch ON-resistance calculation in the second scenario.             | 92  |

| Figure 5.11 | Control signals for switch ON-resistance calculation                             | 93  |

| Figure 5.12 | Switch ON-resistance variation in the first scenario                             | 94  |

| Figure 5.13 | Switch ON-resistance variation in the first scenario                             | 94  |

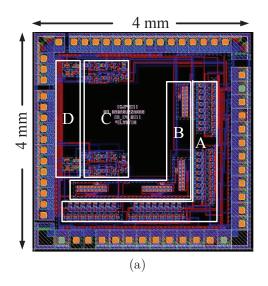

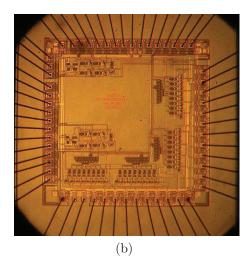

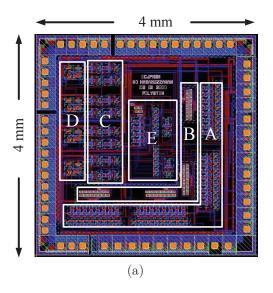

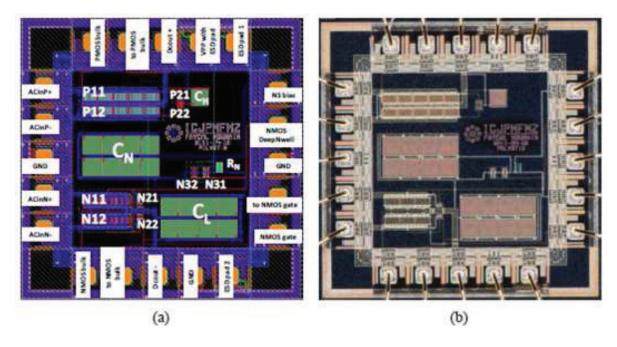

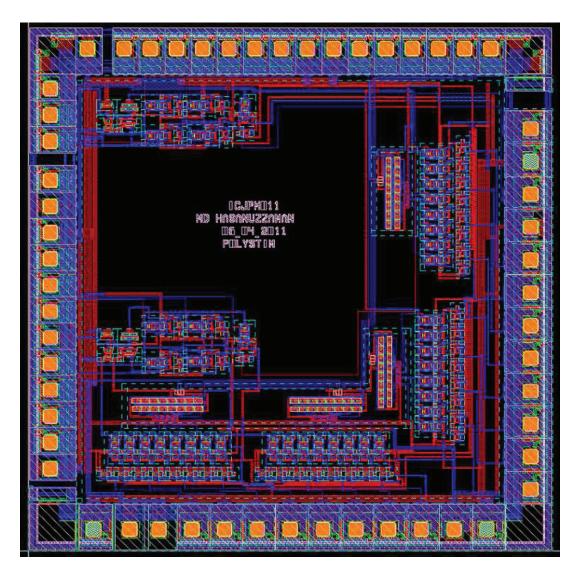

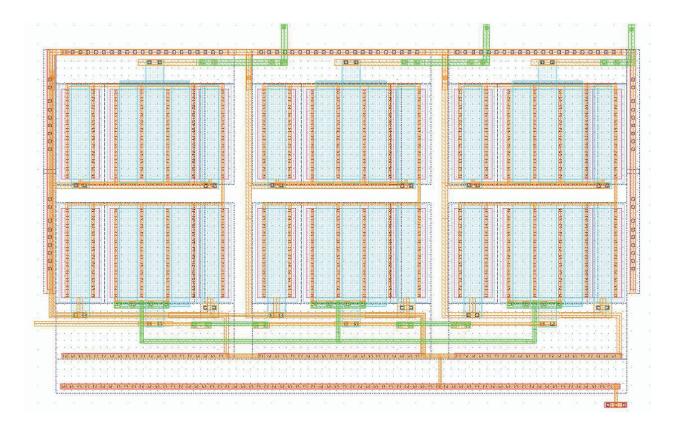

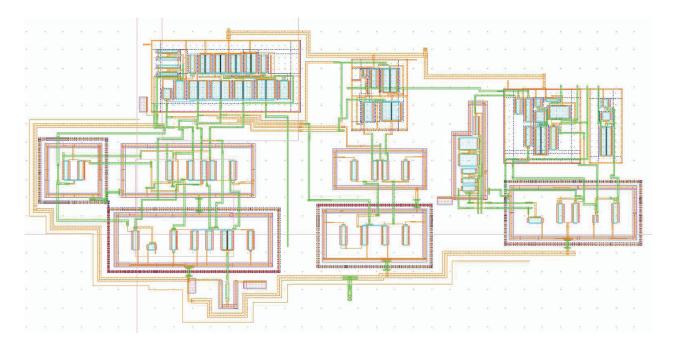

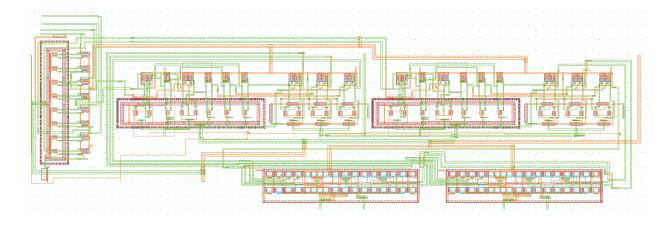

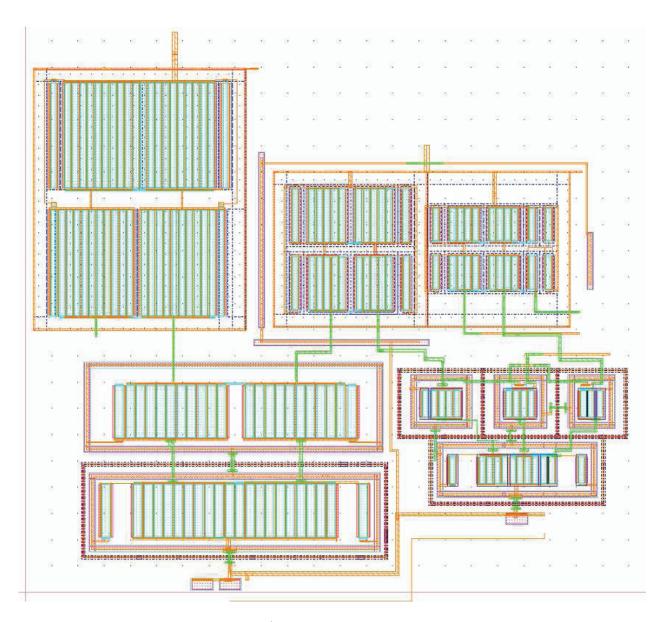

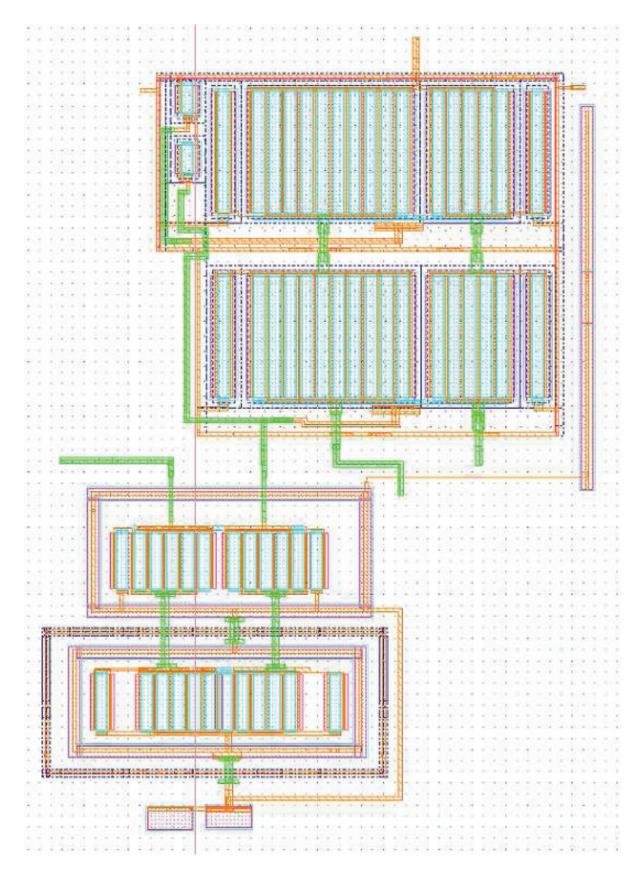

| Figure 5.14 | The layout view and microphotograph of the first MED                             | 95  |

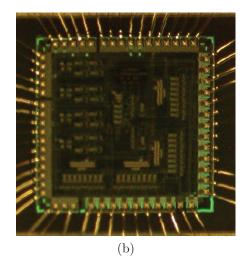

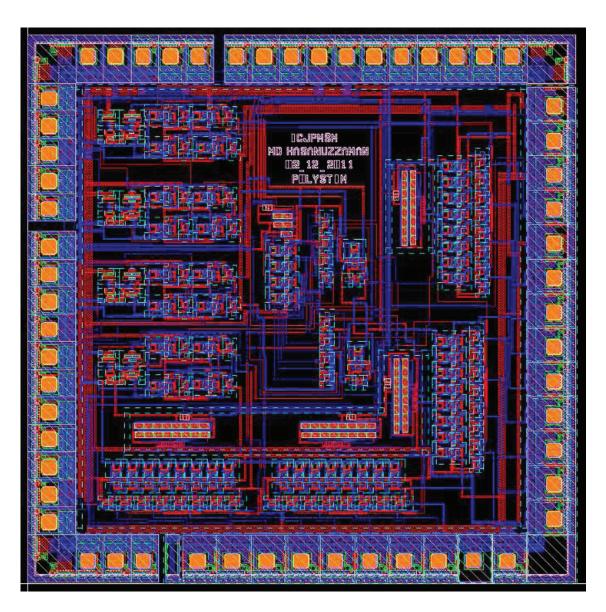

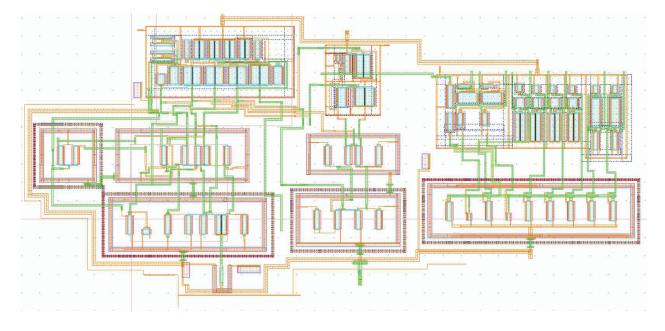

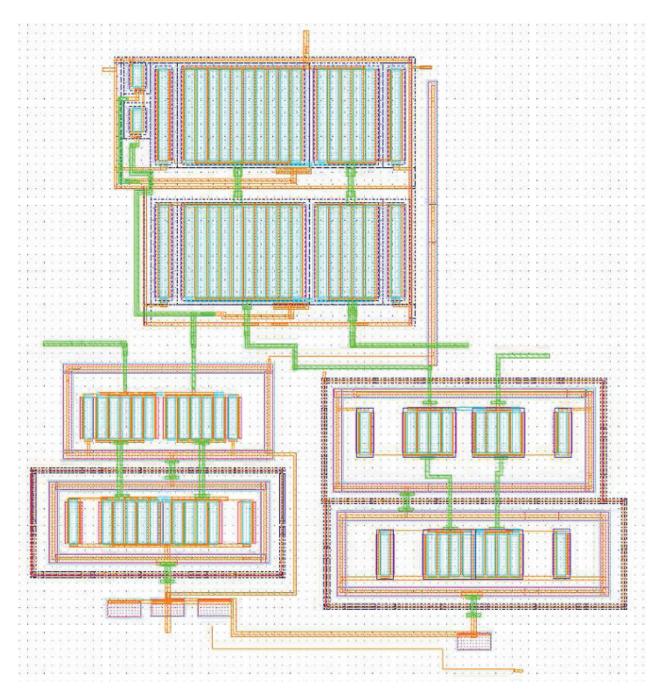

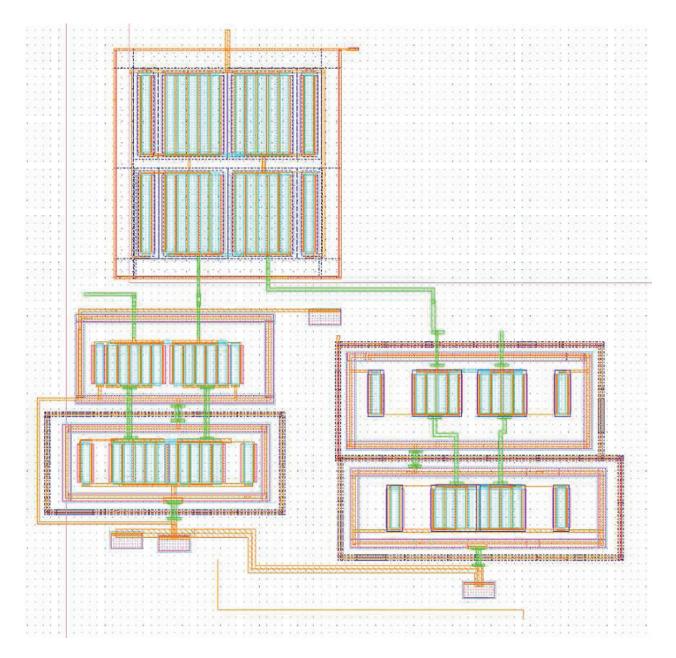

| Figure 5.15 | The layout view and microphotograph of the second MED                            | 96  |

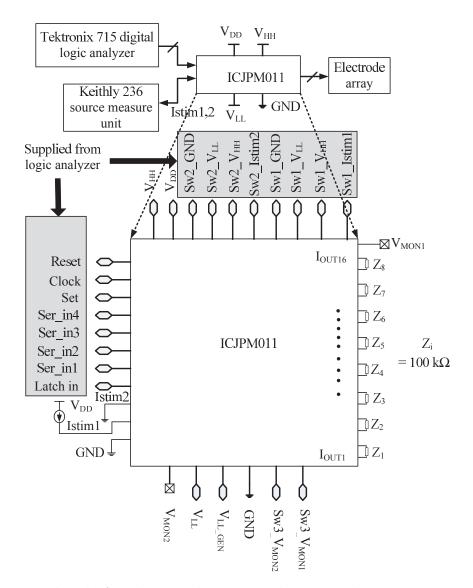

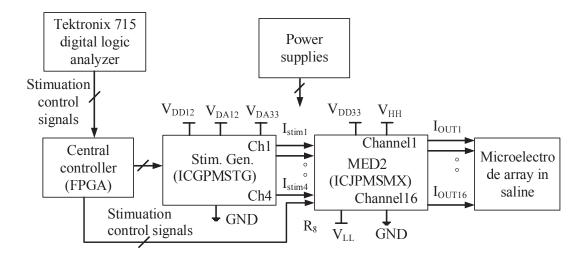

| Figure 5.16 | Test bench for the chips ICJPM011 and ICJPMSMX                                   | 98  |

| Figure 5.17 | Result showing the range of the linearity of two MEDs                            | 99  |

| Figure 5.18 | Trains of biphasic current pulses generated from the first MED                   | 99  |

| Figure 5.19 | Plot of the incremental effect of $V_{\rm T0}$ on the total stimulation current. | 99  |

| Figure 5.20 | The effect of temperature on output stimulation current                          | 100 |

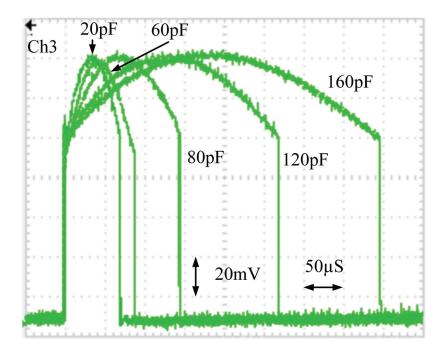

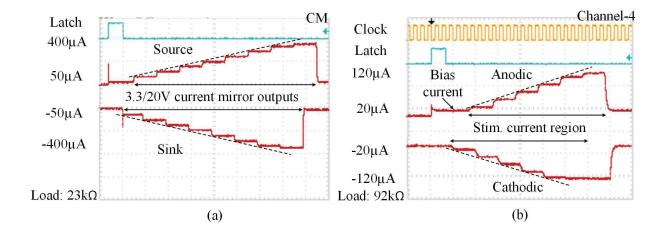

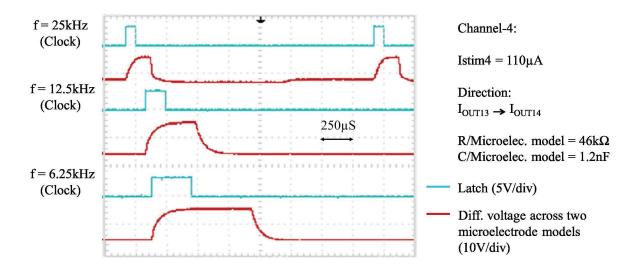

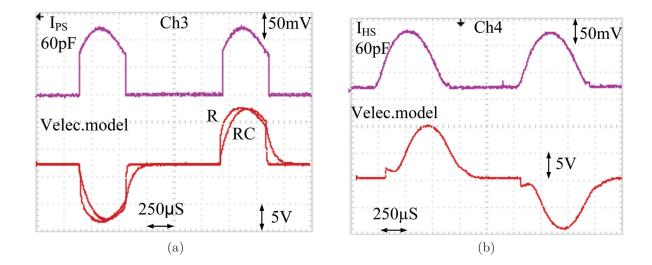

| Figure 5.21 | Experimental results of MED1                                                     | 100 |

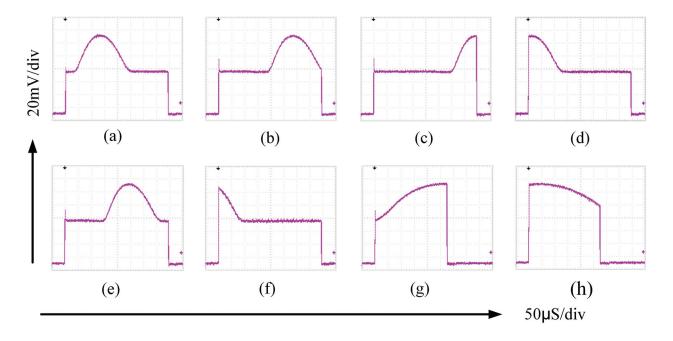

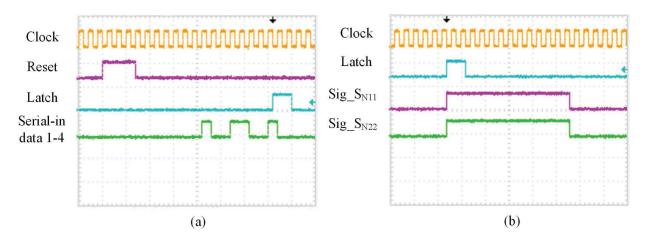

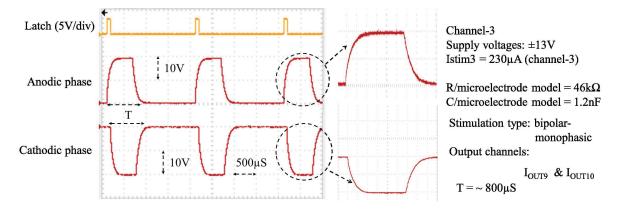

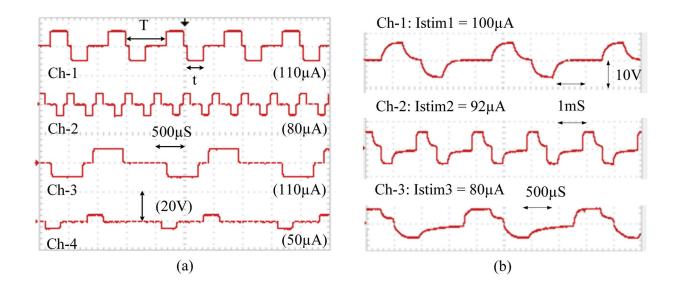

| Figure 5.22 | Experimental results of MED2                                                     | 101 |

| Figure 5.23 | Measurement results of MED2                                                      | 102 |

| Figure 5.24 | Experimental results of MED2                                                     | 103 |

| Figure 5.25 | Measurement results of MED2                                                      | 103 |

| Figure 5.26 | Experimental results of MED2                                                     | 104 |

| Figure 6.1  | Schematics of the power recovery unit                                            | 109 |

| Figure 6.2  | Circuit diagram of the rectifier chip © [146]                                    | 110 |

| Figure 6.3  | Power recovery front end rectifier chip                                          | 111 |

| Figure 6.4  | The power recovery unit assembled on a miniature PCB                             | 111 |

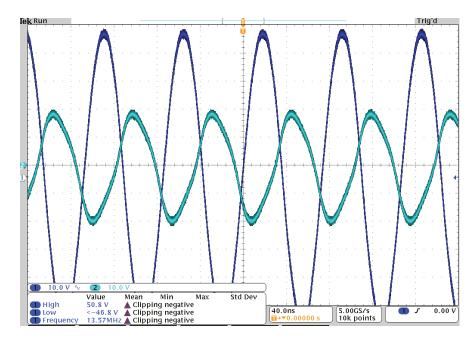

| Figure 6.5  | The transmitted and received RF signals                                          | 112 |

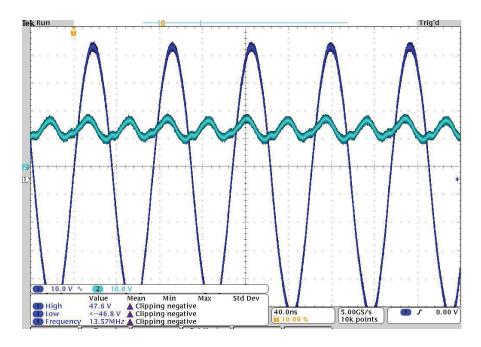

| Figure 6.6  | Measurement results from the rectifier                                           | 112 |

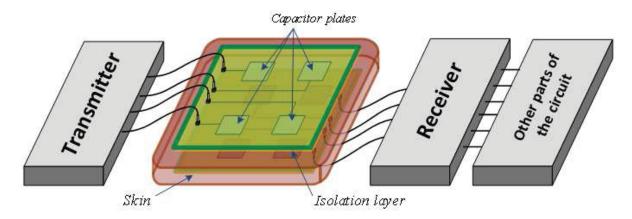

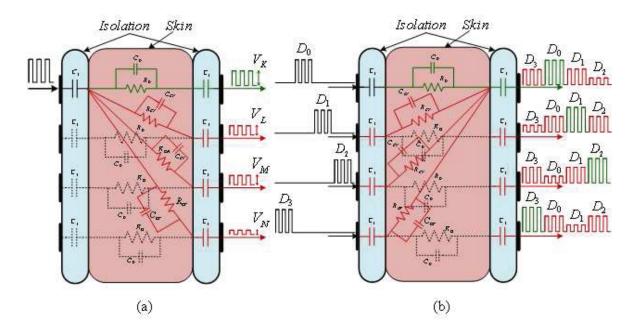

| Figure 6.7  | Conceptual representation of the proposed data transceiver                       | 114 |

| Figure 6.8  | COMSOL modeling of the capacitive-link                                           | 116 |

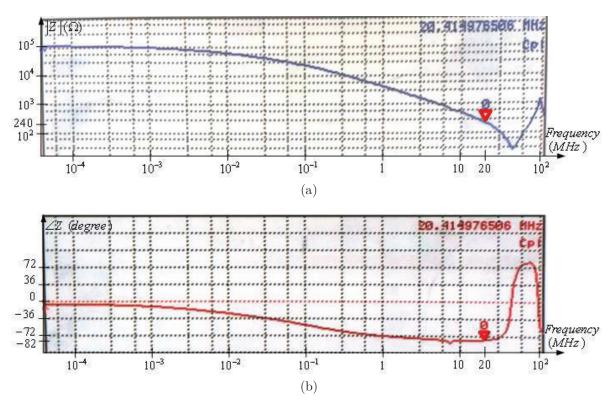

| Figure 6.9  | Characterization of sheep skin at 20MHz                                          | 117 |

| Figure 6.10 | SPPM transmitter and receiver                                                    | 118 |

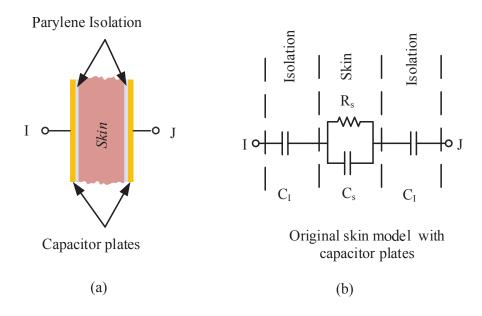

| Figure 6.11 | The equivalent circuit of skin model                                             | 118 |

| Figure 6.12 | Effect of crosstalk between non-overlapping plates                   | 119 |

|-------------|----------------------------------------------------------------------|-----|

| Figure 6.13 | Effect of crosstalk among all capacitive-channels                    | 119 |

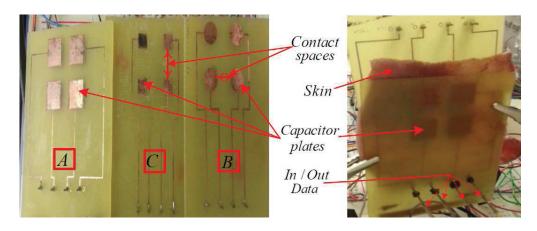

| Figure 6.14 | Fabricated capacitor plates                                          | 120 |

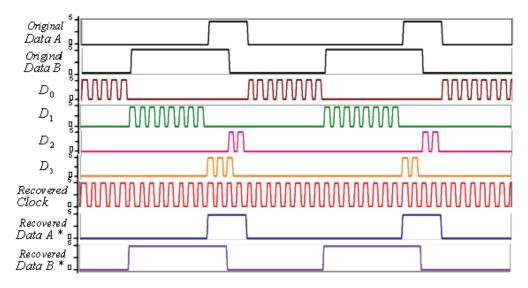

| Figure 6.15 | Recovered data and clock from simulation results [163]. $\odot$ IEEE | 121 |

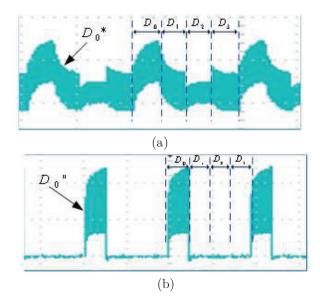

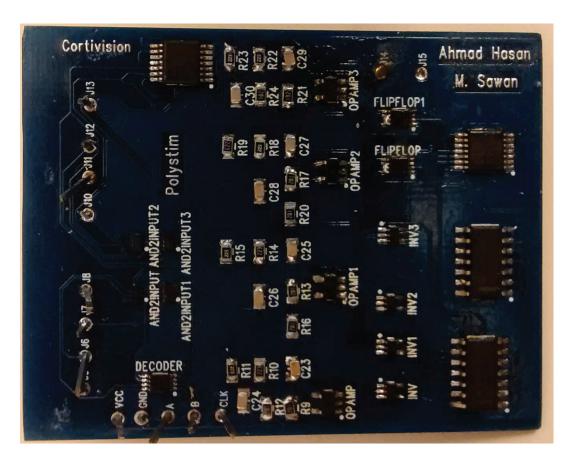

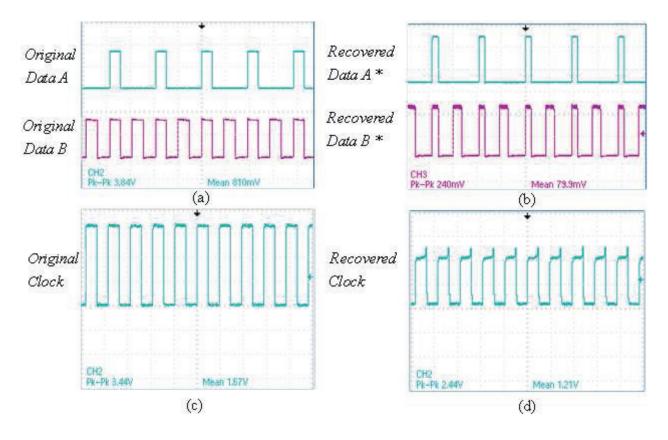

| Figure 6.16 | Experimental results(a)                                              | 122 |

| Figure 6.17 | Experimental results(b)                                              | 123 |

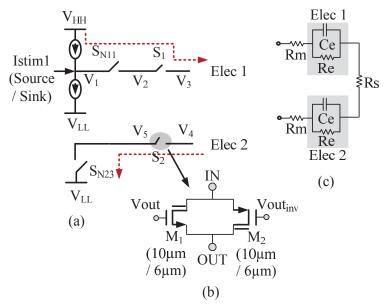

| Figure 7.1  | The ETI-voltage monitoring unit                                      | 126 |

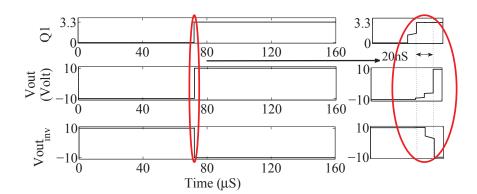

| Figure 7.2  | Experimental results: The ETI-voltage monitoring unit                | 127 |

| Figure 7.3  | The central controller                                               | 128 |

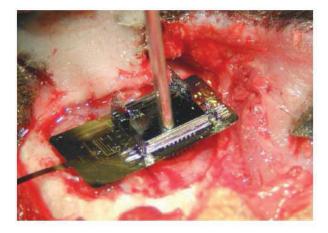

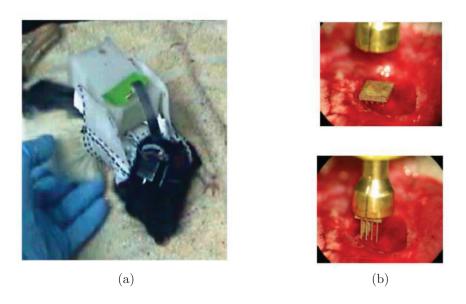

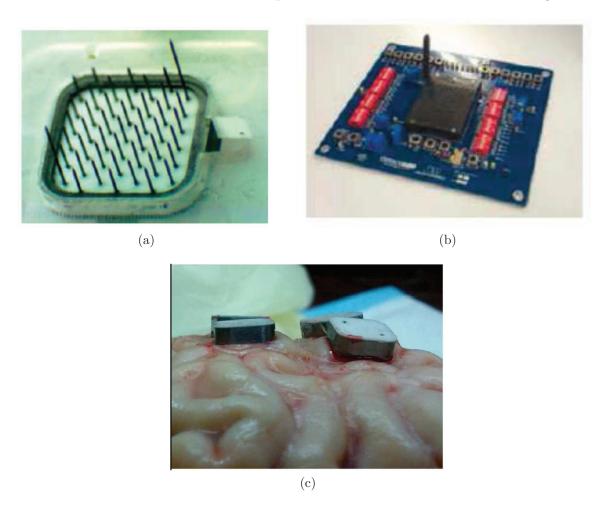

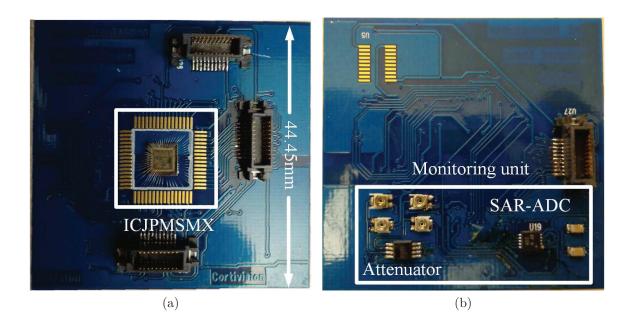

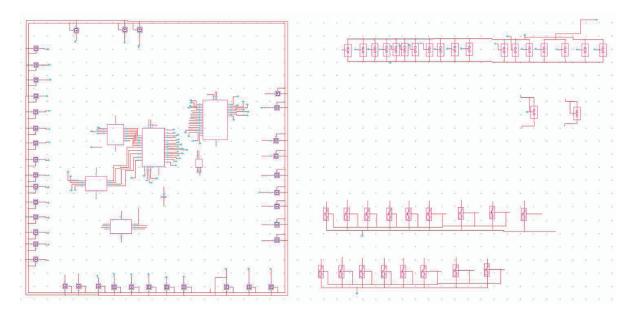

| Figure 7.4  | The assembled microstimulator prototype (a)                          | 130 |

| Figure 7.5  | The assembled microstimulator prototype (b)                          | 130 |

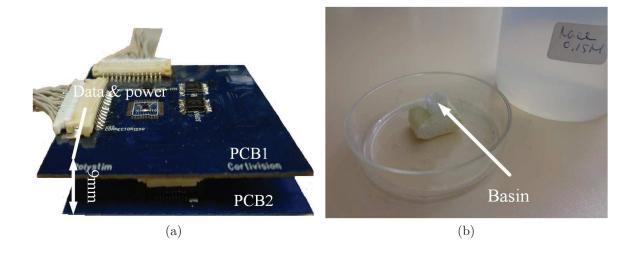

| Figure 7.6  | The assembled microstimulator prototype (c)                          | 131 |

| Figure 7.7  | The assembled microstimulator prototype (d)                          | 131 |

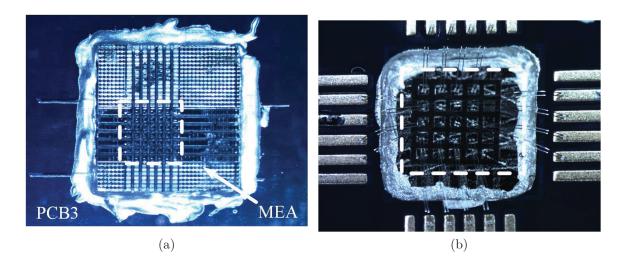

| Figure 7.8  | Experimental setup                                                   | 132 |

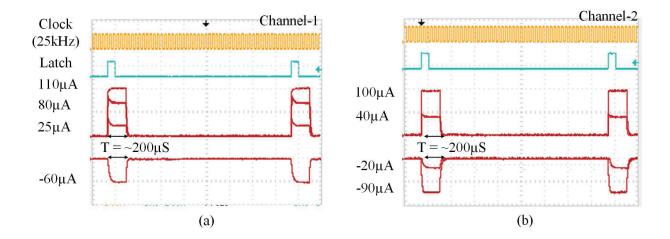

| Figure 7.9  | Experimental results from the microstimulator                        | 133 |

| Figure 7.10 | Biphasic stimulation signals                                         | 134 |

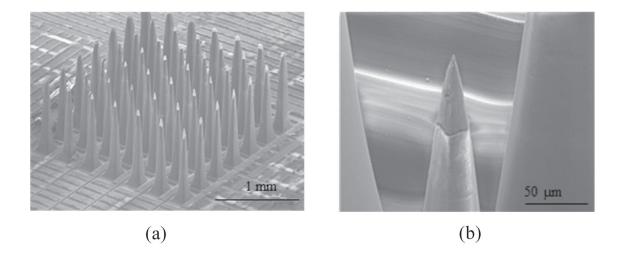

| Figure 7.11 | SEM images of the MEA                                                | 134 |

| Figure A.1  | 3.3V/20V current mirror circuit                                      | 164 |

| Figure A.2  | The basic elements of an inductive link                              | 167 |

| Figure A.3  | The generic model of a transcutaneous inductive link                 | 167 |

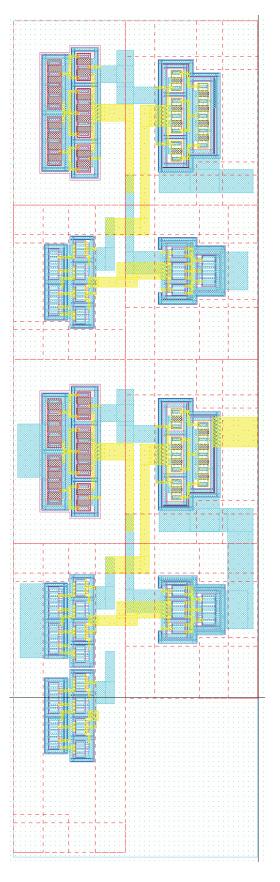

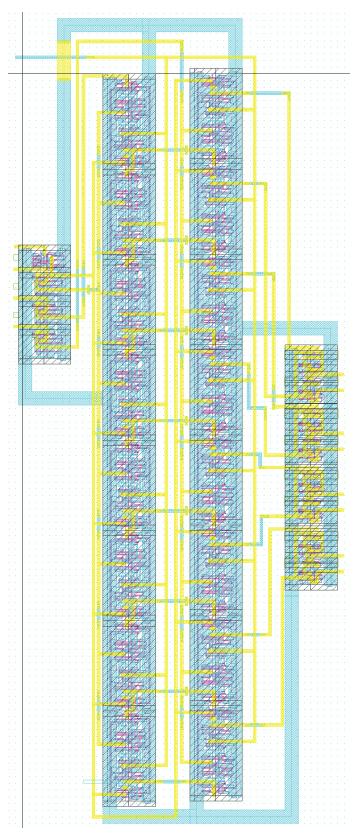

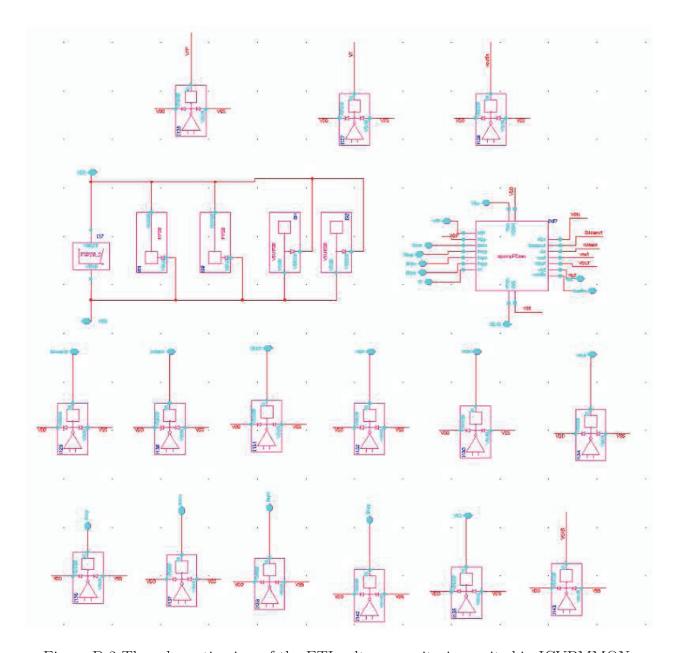

| Figure B.1  | The layout view of the first MED                                     | 169 |

| Figure B.2  | The layout view of the second MED                                    | 170 |

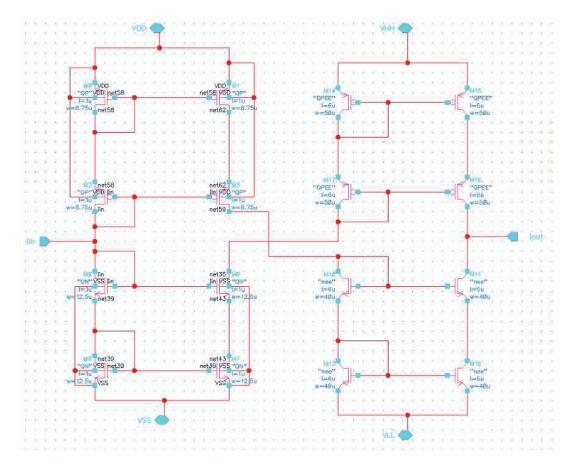

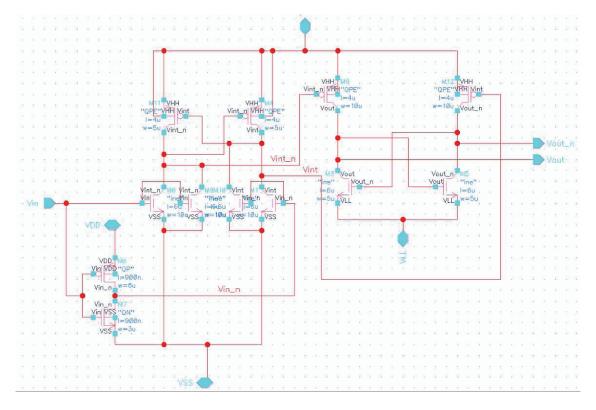

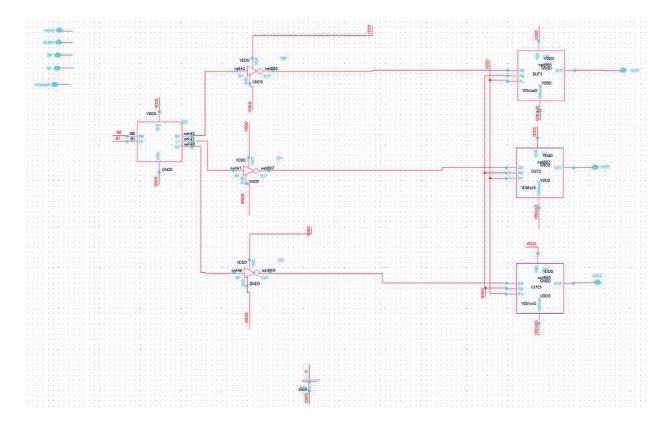

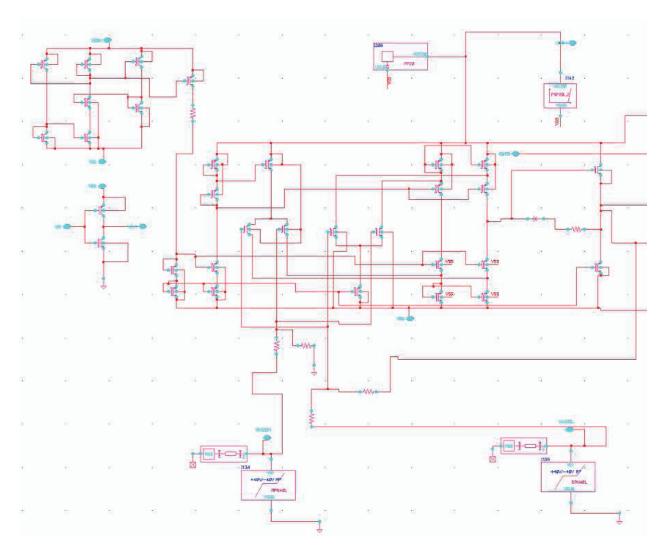

| Figure B.3  | The schematic diagram of the $3.3V/20V$ current mirror               | 171 |

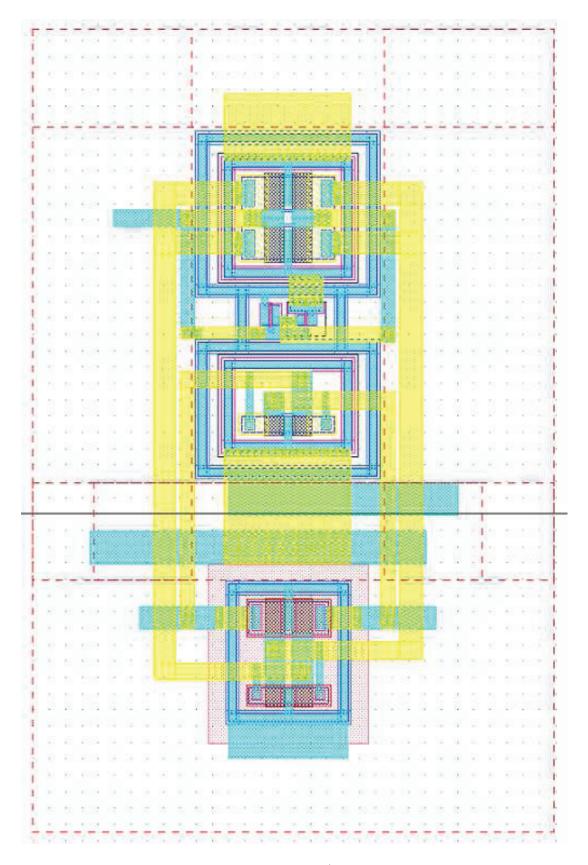

| Figure B.4  | The layout view of the $3.3V/20V$ current mirror                     | 172 |

| Figure B.5  | The $3.3V/20V$ high-voltage level-shifter                            | 173 |

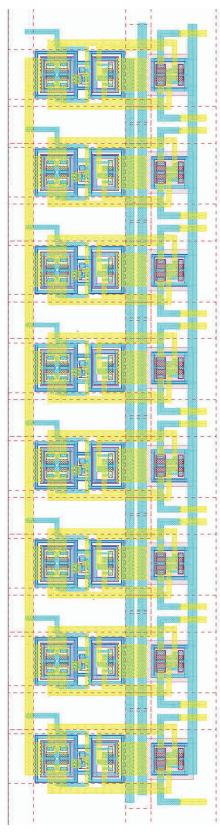

| Figure B.6  | The layout view of the $3.3V/20V$ high-voltage level-shifter         | 174 |

| Figure B.7  | 3.3V/20V high-voltage level-shifters                                 | 175 |

| Figure B.8  | The schematic diagram of the 8-bit register                          | 176 |

| Figure B.9  | The layout view of the 8-bit register                                | 177 |

| Figure B.10 | High-voltage switch.                                                 | 178 |

| Figure C.1  | The schematic view of the stimuli-generator chip                     | 179 |

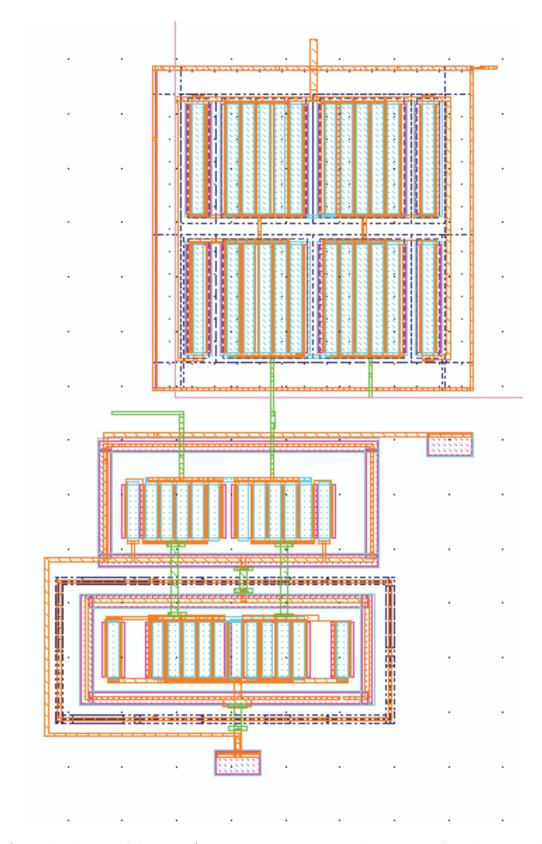

| Figure C.2  | The layout view of the stimuli-generator chip                        | 180 |

| Figure C.3  | The layout view of the source DAC                                    | 181 |

| Figure C.4  | The layout view of the sink DAC                                      | 182 |

| Figure C.5  | The schematic view of current sources in the source DAC              | 183 |

| Figure C.6  | The layout view of current sources in the source DAC                 | 183 |

| Figure C.7  | The layout view of current sources defining the range of source DAC. | 183 |

|-------------|----------------------------------------------------------------------|-----|

| Figure C.8  | The layout view of current sources defining the range of sink DAC    | 184 |

| Figure C.9  | The schematic diagram of the thermometer decoder                     | 185 |

| Figure C.10 | The layout view of the thermometer decoder                           | 185 |

| Figure C.11 | The layout view of the reference circuit for the DAC                 | 186 |

| Figure C.12 | The layout view of the reference circuit for different pulses        | 186 |

| Figure C.13 | The layout view of ramp voltage and HS pulse generators              | 187 |

| Figure C.14 | The schematic diagram of Iprog current sources                       | 188 |

| Figure C.15 | The layout view of Iprog current sources                             | 188 |

| Figure C.16 | The schematic diagram of the on-chip controller                      | 189 |

| Figure C.17 | The layout view of the on-chip controller                            | 189 |

| Figure C.18 | The schematic diagram of HS and other pulse types                    | 190 |

| Figure C.19 | The layout view of HS and other pulse types                          | 191 |

| Figure C.20 | The layout of the $1.2V/3.3V$ source current mirror $1$              | 192 |

| Figure C.21 | The layout of the $1.2V/3.3V$ sink current mirror 1                  | 193 |

| Figure C.22 | The layout of the $1.2V/3.3V$ source current mirror $2$              | 194 |

| Figure C.23 | The layout of the $1.2V/3.3V$ sink current mirror 2                  | 195 |

| Figure C.24 | The layout of the $1.2V/3.3V$ source current mirror $3$              | 196 |

| Figure C.25 | The layout of the $1.2V/3.3V$ sink current mirror 3                  | 197 |

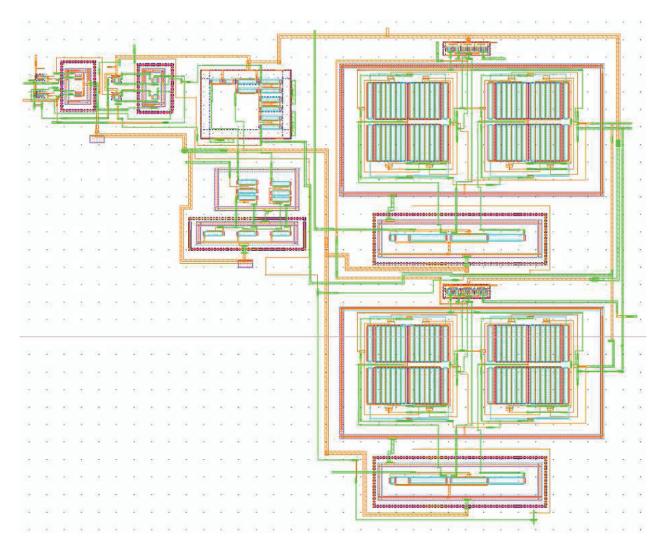

| Figure D.1  | The layout view of the chip ICVPMMON                                 | 198 |

| Figure D.2  | The schematic view of the chip ICVPMMON                              | 199 |

| Figure D.3  | The schematic view of the rail-to-rail opamp                         | 200 |

# LIST OF APPENDICES

| APPENDIX A | THEORIES AND ANALYTICAL EQUATIONS FOR THE DESIGNED |     |

|------------|----------------------------------------------------|-----|

|            | CIRCUITS                                           | 164 |

| APPENDIX B | ICJPM011 AND ICJPMSMX: THE MED CHIPS               | 169 |

| APPENDIX C | ICGPMSTG: THE STIMULI-GENERATOR CHIP               | 179 |

| APPENDIX D | ICVPMMON: THE ETI VOLTAGE MONITORING UNIT CHIP     | 198 |

#### LIST OF ABREVIATIONS AND NOTATIONS

#### LIST OF ABREVIATIONS

GRM Groupe de Recherche en Microélectronique LASEM Electronic Microsystems Assembly and

Encapsulation Laboratory

GR2M Microelectronics and Microsystems

Research Group

NSERC National Science and Engineering

Research Council

FRQNT Fonds de la recherche québécois sur

la nature et les technologies

CMC Canadian Microelectronics Corporation

CMOS Complimentary metal-oxide-semiconductor

DMOS Double diffused metal-oxide-semiconductor

SG Stimuli generator

ETI Electrode-tissue interface

MED Microelectrode driver

MEA Microelectrode array

HS Half-sine PS Plateau-sine

DAC Digital-to-analog converter

ADC Analog-to-digital converter

SAR Successive approximation

SPPM Spatial pulse position modulation

MS Microstimultion module WHO World Health Organization

FES Functional electrical stimulation

DBS Deep brain stimulation

CNS Central nervous system

CIC Charge injection capacity

GSA Geometric surface area

AIROF Activated iridium-oxide film SIROF Sputtered iridium-oxide film UIEA Utah intracortical electrode array

PPy Poly(pyrrole)

PEDOT Poly(3,4-ethylenedioxythiophene)

SOI Silicon on insulator

LGN Lateral geniculate nucleus

AMD Age related macular degeneration

RP Retinitis pigmentisa

ASIC Application specific integrated circuit

LSU Local stimulation unit

IEEE Institute of Electrical and Electronics

Engineers

PDMS Polydimethylsiloxane

RF Radio frequency

FSK Frequency shift keyed

LC Inductive-capacitive

IM Interface module

SM Stimulation module

MVG Monash Vision Group

OSHC Original scientific hypothesis of

contributions to research

SIPO Serial-in parallel-out SISO Serial-in serial-out

FF Flip-flop

FPGA Field programmable gate array

FSLC Forbidden state logic circuit

LS Level shifter

DMOS Double diffuse MOSFET

LDMOS Lateral double diffuse MOSFET

TG Transmission gate

ISM Industrial-scientific-medical LDO Low-drop out regulator ASK Amplitude Shift Keying

SPPM Spatial pulse position modulation

MIMO Multiple-Input and Multiple-Output

SNR Signal-to-noise ratio

SPPM Spatial pulse position modulation

AEM Amplitude-engraving modulation

CSP Chip scale package

BGA Ball grid array

PCB Printed circuit board

HDI High density interconnect

MUX Multiplexer

SEM Scanning electron microscope

#### LIST OF NOTATIONS

I<sub>th</sub> The current required to reach threshold

$\begin{array}{ccc} I_{th} & & Rheobase \ current \\ t_c & & Chronaxie \ time \end{array}$

$au_{\mathrm{m}}$  Membrane time constant  $Z_{\mathrm{w}}$  Warburg impedance

$R_{CT}$  Charge transfer resistance

Z<sub>CPA</sub> Non faradic pseudo capacitance

$\begin{array}{ccc} R & & & Resistance \\ V & & Voltage \\ t & & Time \end{array}$

T Pulse-width

E(t) Instantaneous energy P(t) Instantaneous power V(t) Instantaneous voltage I(t) Instantaneous current

$T_s$  Pulse-width Z(t) ETI impedance

$M_n$  Transistor

$V_{\mathrm{T}}$  Thermal voltage C Capacitance

IhsineHalf-sine current pulse $S_n$ TG based CMOS switch $Rs_{ON}$ Switch-on resistance

$g_{ds_{ON}}$  Switch-on transconductance

D<sub>i</sub> Digital data

#### CHAPTER 1

#### INTRODUCTION

In recent past, the field of biomedical engineering has proved to be a very promising to restore physiological functions. A substantial growth of research in biomedical engineering has been experienced in recent decades. Implantable medical devices have been found to be one of the major applications where scientists, engineers, and physicians have shown great enthusiasm. The pacemaker and cochlear implant have become commonly used prosthetic devices to restore vital functions. However, power and area miniaturization of implantable microelectronics circuits are still considered to be major challenges, that the researchers, nowadays, are trying to solve.

Scientific community has shown great interest for a long time to blindness, a serious physiological dysfunction, in which approximately 39 million blind people around the world are likely to be affected (World Health Organization [WHO], 2014). According to the study carried by WHO, in case of a significant number of patients such blindness cannot be treated following normal surgical procedure. To deal these cases, considered to be irreversible, a group of researchers have been studying functional electrical stimulation (FES) technique and employing it in microelectronic based prosthetic devices with an aim to enable visually impaired patients to recover functional vision. The performance of such systems are affected by the technical specifications related to the physical constraints, such as the energy efficiency of needed stimulation system and the required data rate to run an implant dedicated to such stimulation.

Authors presented different solutions addressing difficulties of the visual implants. However, these solutions are generally contemplated with a specific goal and have a limited perspective. Consequently, fundamental and technical considerations are omitted, and the results are not representative of solutions to complete systems in all respects.

The relevant recent publications of the most respected and advanced teams in this field have developed implants that allow sufficient stimulation and parallel data transfer rate capabilities, but present several drawbacks such as power consumption well beyond the authorized budget [1], [2], [3]. Owing to the limited power budget for the implantable biomedical devices, and in order to ensure the safety of biological tissues and for a long battery life, a transcutaneous inductive-link can not assuredly provide such amount of energy continuously to the implant [4]. Some solutions to optimize the energy transfer are also proposed, but can

not guarantee that the power of the implant is unduly affected by the activity of the latter [5], [6]. The high-voltage compliance, needed at the output stage of the device, is a major issue and it requires the use of high-voltage CMOS/DMOS process. On the other hand, minimizing power consumptions is also necessary. Therefore, a compromise between the use of low-power and high-voltage technologies, and complexity can be made to satisfy these two divergent requirements.

Therefore, the research team at the Polystim neurotech laboratory at the Polytechnique Montreal has launched the Cortivision project in this context. The purpose is to build a visual prosthetic implant to stimulate the visual cortex area. To achieve this goal, a functional prototype was built and successfully validated through in-vivo experiments on rats [7]. The power needed for the implant was derived from an external battery and was transmitted through a wireless inductive-link. It is essential to limit power dissipation of the implant for long battery life, as the microstimulator in daily application is used several hours per day. Therefore, for any implantable device, power consumption is a primary concern and an important constraint. The high impedance of the electrode between the electrode and the physiological tissue is the second design constraint for an intracortical microstimulator. This high-impedance necessitates the use of high voltages in the output-stage of a microstimulator for typical stimulation current of about  $100\mu A$ . Implementing the output-stage in low voltage CMOS process to satisfy the need of high-voltage is quite unreliable, as the generated high-voltage would stress the low-voltage transistors and make the system unreliable. Enhanced flexibility in the output-stage is also required for maximum channel count and delivering stimulation currents to neural sites using charge-balanced monopolar and bipolar stimulation. The third constraint is the multichannel monitoring of stimulation sites prior to, during, and after injecting excitation current to prevent the damage of the device and release of toxic ions in the tissues. Research teams have estimated that 625 to 1000 phosphenes in the visual field are needed to create useful vision [8]-[12]. For a wirelessly controlled microstimulator, data-rate of about 10Mbps is required to stimulate such large number of sites and the detailed calculation is provided in Chapter 6.

The primary goal of this research project is to build an intracortical microstimulator keeping energy savings, required data-rate and voltage-compliance across the electrode-tissue interface (ETI), enhanced flexibility in multichannel stimulation and monitoring in mind, when compared to the previously designed prototypes ([7], [13]). To accomplish our objective, new category of potential energy-efficient stimulation pulse types have been generated and delivered through a highly-configurable high-voltage compliant output-stage, named as microlectrode driver (MED). The new stimulation pulse patterns are introduced to minimize power consumption by some fraction both in the device as well as across ETI, when a large

number of neural sites are excited. The other objective of this thesis is to design and implement a wireless high data-rate (at least 10Mbps) communication module to maximize the stimulation channel count and capability in the device and therefore, neural sites through high density microelectrode array (MEA). Assuredly, characterization and validation of the newly developed prototype through in-vitro or in-vivo experiments are also within our objectives. However, such successful experiments do not endorse entirely the efficacy and safety of the device unless tested on human subjects. Therefore, the long term goal is to design the prototype, with an objective to implant and verify on human subjects.

## 1.1 Organisation of the thesis

This Ph.D. thesis includes eight chapters. The first chapter (this chapter) discusses the motivation behind this research and organization of this thesis. The second one discusses the basic principle and parameters of electrical stimulation, physiological concepts needed to understand the specifications of and build an intracortical microstimulation system, and essential elements required to create an interface between the former and neural tissues. In the beginning we discuss how different stimulation parameters affect the process of stimulation. Secondly, we proceed to different types of waveforms which can be employed in FES. Thirdly, an essential interface, the MEA, its working principle and types are addressed. Next, we proceed to discuss the different physiological aspects, such as visual system, different regions of visual cortex, neuron basics and its working principle, and generation of action potential and its propagation.

The third chapter deals with a review of the literature. We have categorized the visual prosthetic implants based on the location along the visual pathways. At first, we have presented an overview of architectures of different retinal implants designed by prominent research groups. Secondly, works and systems for optic nerve stimulation have been presented. Thirdly, we have discussed various visual intracortical implants, designed by renowned research groups. We have investigated the specifications and performances of the built prototypes. Their technical limitations, which have not been addressed and need to be solved, have been identified from global perspective. We have formulated the research questions to resolve the technical limitations or challenges in the existing intracortical architectures presented in the second chapter. Based on this, we have set up our general and specific objectives, and developed our hypotheses (original scientific hypothesis). Finally, we have proposed the new architecture of visual intracortical microstimulator satisfying the specifications derived from the research questions and objectives. The novel items related to the original contributions are presented in chapters 4 to 7.

The fourth chapter presents the proposed system and microstimulation module (MSM), and deals with the design and implementation of the energy-efficient stimuli-generator (SG). We begin with investigation on various types of excitation efficient pulse patterns and selecting those concluded to be the most energy-optimum for implementation. Next, the architecture of the SG, working and design principles of different functional blocks, and the experimental results of the fabricated chip are presented.

In the fifth chapter, we include the architectures of the microelectrode driver, discuss their configurability issues, design specifications and working principles of the building blocks. The experimental results are presented in the end.

The sixth chapter discusses the data and power recovery units. At first, we summarize the main published architectures of energy and power recovery units for biomedical devices. Next, we presented the configuration of the proposed subsystems, design and working principles of different circuits, and achieved results.

The ETI voltage monitoring unit; the central controller; and the assembly techniques of all the chips fabricated for this project, including MEA, and the additional discrete components are presented in chapter seven. At first, we have illustrated the ETI voltage monitoring unit and the associated experimental results, and next, discussed the configuration of the central controller. The in-vitro experimental results are also presented supporting the performance and validation of the complete prototype.

Finally, in chapter eight, we summarize all the work done, our contributions, and achievements in this thesis. Necessary steps to be taken for further improvements on the present design are also recommended here. This conclusion also presents the future direction as an extension to the current research.

## CHAPTER 2

#### MICROSTIMULATION BASICS

#### 2.1 Introduction

The origin of electric therapy dates back to the ancient time when a freed slave, Anthero, of the Roman Emperror Tiberius Claudius Nero Caesar (ruler of the ancient Rome from AD 14 to AD 37), stepped on a torpedo fish accidentally while walking by a seashore. Anthero was suffering from gout and the electric shock from the torpedo fish, which can reach sometimes about 100-150 volts (DC), worked as the electric therapy for him [14]. The ancients also used amber and magnetic rings for electric treatments. These properties of amber and magnetic rings were further studied in the medieval Europe by Italian mathematician and physician, Gerolamo Cardano (1501-1576). The first electric therapy was performed in 1744 by Christian Gottlieb Kratzenstein, a physician and Professor of Medicine at Halle, on a female patient to free her contracted little finger. The increase in the heart rate was also first observed by him while performing electrification on another patient. In the eighteenth and nineteenth centuries, further development was achieved due to Volta's battery, Galvanism, electrostatic machine, introduction of Newton's theories of matter. It was not until twentieth century, electric therapy has been termed as functional electrical stimulation and modernized with the development of miniaturized microelectronic devices. Generally, stimulation can be defined as the action of different stimuli on muscles, nerves, or sensory end organ. The impulse signals are produced in the nerve tissues in response to the applied stimulation signals, which can be chemical, electrical, or optical in nature, and activities are evoked in those biological body parts. The scope of this chapter is to focus on functional electrical stimulation and its applications to rehabilitation.

#### 2.2 Functional electrical stimulation

The principle, Functional Electrical Stimulation (FES), was first applied by W.T. Liberson and named it as Functional Electrotherapy [15]. The term FES was first introduced by Moe and Post, who defined it as the process of "pairing the stimulation simultaneously or intermittently with a functional task" [16]. As mentioned earlier, history says that this procedure, used for rehabilitation purpose is not new, and dates back in 1790 when Italian anatomist and physician Luigi Galvani observed motion in the leg muscles of a frog after applying elec-

trical currents. In 1831, Michael Faraday claimed that nerves can be stimulated by injecting electrical currents to them to create active movement [17]. Applications of FES are numerous, such as, pacemaker, deep brain stimulation (DBS) for Perkinson diseases, epilepsy [18], cochlear implant [19], motor nerves stimulator [20], bladder implant [21], retinal and visual intracortical implants [22] and so on.

During microstimulation, irrespective of applications, the net quantity of charge delivered to muscle or nerve tissue should be zero at the end of microstimulation period to prevent the electro-chemical reactions in the of biological tissue and for the safety of the patient. This can be achieved by providing charge-balanced biphasic waveforms. The associated parameters, which are amplitude and width of applied pulse, stimulation frequency and period, inter-pulse duration, type of waveforms etc. should be carefully chosen to receive optimum microstimulation effects. Electrical stimulation can be performed using voltage or current signals or in the form of delivered charge quantity. An integral part of the microstimulation system, microelectrode array, delivers the microstimulation signals to the stimulation sites. The microelectrode-tissue interface impedance, which can reach up to few Mega Ohms depending on the coating material used to coat the electrode tip, plays a vital role to define the compliance voltage needed for the microstimulation system.

## 2.2.1 Category of FES

Functional electrical stimulation can be categorized as voltage-mode and current-mode [23].

#### Voltage-mode stimulation

The stimulation signal in the voltage-mode stimulation is voltage, which is converted into current when the stimulation signal is applied to the electrode. The magnitude of the converted current or the quantity of delivered charge which is directly proportional to the applied current is not constant and affected by electrode-tissue interface, nerve and inter-electrode impedances. This method is applicable only when the information on the range of the change of electrode-impedance over time is available. Therefore, this method of microstimulation does not allow the precise control of the exact amount of charge to be passed to the microstimulations sites. An excessive amount of charge will cause irreversible Faradic electro-chemical reactions in the tissues and damage them. A number of voltage controlled microstimulator has been discussed in [24] – [26].

#### **Current-mode stimulation**

On the contrary, current-mode stimulation has the feature of controlling the charge quantity meticulously. This advantage of current-controlled stimulator over the voltage-mode has made it preferable for implementation in most of the stimulators. The output current is usually controlled by current-mode source or sink digital-to-analog converters (DACs). This method is appropriate when there is a possibility of wide variations of electrode-tissue interface impedance. The stimulator provides constant level of current, as long as the stimulation parameters are kept constant and provided that wave-forms other than the rectangular pulse are not applied. In this regard, it is worth to mention that there are other types of wave-forms which can be used for microstimulation for energy saving purpose and it will be discussed shortly. A wide variety of current mode stimulators have been developed so far, and two of such systems are reported in [22] and [27].

#### 2.2.2 Parameters of FES

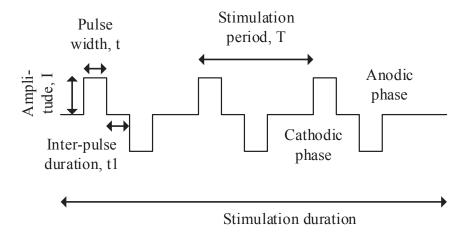

The efficiency of electrical stimulation can be optimized by customizing the associated stimulation parameters, illustrated in Figure 2.1. It is also necessary to ensure the safety and comfort of patient. The stimulation parameters are pulse width, amplitude and shape; interpulse duration; stimulation frequency and duration; duty cycle; type of stimulation waveform; phase of the pulse; number of pulse trains within stimulation duration etc.

## Amplitude/Intensity

The strength of the stimulation current, I, is determined by its magnitude (also the total quantity of charge delivered) in  $\mu$ A or mA. The type of the electrode also plays a significant role on the requirement of the intensity level of the current. Implantable penetrating electrodes require less current (up to few hundred microamperes) due to the proximity of the target area. On the contrary, surface mode stimulation which is a non-invasive technique, requires larger current, generally in the order of milliampere. The current with higher amplitude has the stronger depolarizing effect on the nerves. But, the intensity of the current is also restricted by the maximum tolerable heat dissipation limit in the tissue, and to prevent the damage to the nerve or muscle fibres and corrosion of electrode surface.

## Pulse-duration/width

The pulse-duration or width, t is defined as the time span of a single pulse. The width of a single pulse for both monophasic and biphasic waveforms vary depending on the amplitude

Figure 2.1 Typical constant current stimulation waveforms showing various stimulation parameters.

of the current and the net quantity of charge to be applied to the stimulation site. In [28], Cameron C.M. et al. applied monophasic and biphasic waveforms with pulse durations of  $10\mu\text{S} - 1\text{mS}$  to excite central nervous system (CNS) neuron populations. The objective was to identify the optimum stimulus and electrode geometry. In [29], Thomas J. F. et al. performed an investigation on different waveforms in order to identify their advantages over conventionally used rectangular waveforms for deep brain stimulation. Pulse width, in this case, was varied from  $50\mu\text{S}$  to 2mS. However, they also have mentioned the rectangular pulse of width  $100\mu\text{S}$  as the "gold standard" for neurostimulators. It is better to use narrow pulse width to minimize electrochemical reactions that may occur on the surface of the electrode.

#### Inter-pulse duration

Inter-pulse duration is defined by the distance between anodic and cathodic pulses within one complete stimulation period. Usually, a charge-balanced biphasic waveform is preferred to prevent the tissue damage. While performing stimulation, in some cases, irreversible reactions occur, leading to the development of positive potential (with respect to the pre-pulse potential) at the end of anodic phase. This electrochemical process causes electrode corrosion, may suppress an action potential and increase the stimulation threshold for a biphasic stimulation compared to monophasic case. These undesirable effects can be minimized by introducing an interphase delay between cathodic (stimulating) and anodic (reversal) phases. In [30], it has been suggested that an interphase (or inter-pulse) delay of about  $100\mu S$  is effective enough to prevent the action potential suppression while keeping the products of electrochemical reactions in the acceptable range.

## Stimulation frequency

Stimulation frequency is the inverse of the stimulation period, T as shown in Figure 2.1. T is the distance between two successive anodic or cathodic pulses for monophasic and biphasic stimulation. Stimulation frequency is application dependent and can range from 50 to 4000Hz.

#### Stimulation pulses

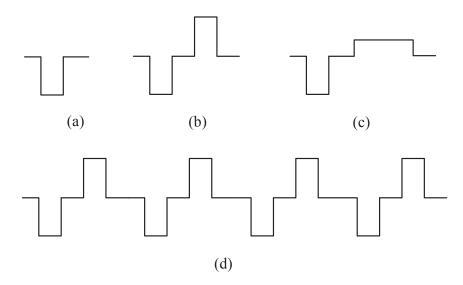

Stimulation waveforms are usually two types, monophasic and biphasic as shown in Figure 2.2.

Monophasic waveforms are unidirectional and consist of either positive or negative pulses. In practical cases, a number of repetitive cathodic (negative) pulses are applied to construct this unidirectional waveform. This kind of stimulus pattern is used generally in surface electrode stimulation. The one directional current causes electrode deterioration (corrosion, electrode tissue-interface impedance change) and polarization, and changes the ionic distribution in the biological medium, which in turn causes tissue damage. These undesirable effects can be minimized using biphasic waveforms, provided that those are charge-balanced. Biphasic waveforms consist of repeating pulse pattern, composed of cathodic (negative) pulse followed by anodic (positive) pulse. Cathodic pulse generates action potentials in the neural tissue by depolarizing the axons. The charge accumulated during this phase can damage the tissues due to the Faradic electro-chemical reaction. The succeeding anodic pulse of equal quantity of positive charge is applied to negate the residual negative charge accumulated in the preceding phase. The biphasic waveforms can be either symmetric or asymmetric as shown in Figure 2.2, where in both cases they should be charge-balanced. In most of the stimulators, charge-balanced waveforms are rectangular in shape, but waveforms with other pulse shapes can also be applied as long as they have the similar effect as of the former one on the nerve or muscle tissue. Usually, the primary pulse has rectangular-shape, and the secondary pulse can have either rectangular or exponentially decaying shape, known as active- and passive-discharging phase respectively. The quantity of charge delivered during any phase, Q(t), is the total area under that pulse. Q(t) is equal in both phases for charge-balanced waveforms irrespective of the symmetry in two phases.

## Electrode-configuration/Microstimuation-strategy

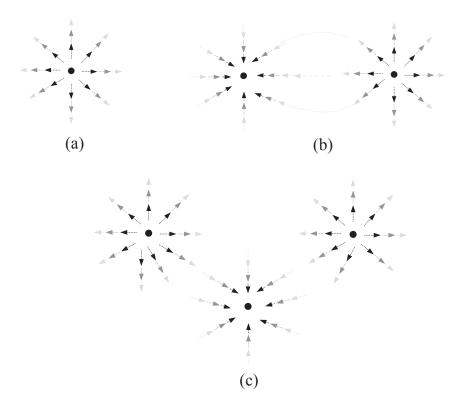

Electrodes can be configured either in monolpar, or bipolar, or tripolar or hexagonal arrangement. In monopolar case, as shown in Figure 2.3(a), stimulation current is passed through

Figure 2.2 Various types of constant current pulses: (a) monophasic, (b) biphasic (symmetric), (c) biphasic (assymmetric), and (d) pulse train (charge-balanced).

the active electrode which is also known as working electrode and a return (or counter) electrode, located near or far, is provided for the outgoing (return) current. The return electrode also works as a reference electrode in this case. Charge is balanced with the aid of a capacitor discharge circuit, resulting in a cathode leading monophasic and capacitive coupled waveform. In bipolar configuration, presented in Figure 2.3(b), two working electrodes are used for stimulation and current direction is altered to provide biphasic stimulation currents, conventionally beginning with the cathodic phase for physiological purpose. Potentials of both working and counter electrodes may fluctuate, which is measured with respect to the third electrode potential, kept at the reference point (usually ground) [30]. A various patterns of biphasic current waveforms can be applied and have been illustrated with their effects on stimulation efficacy, tissue damage and electrode corrosion in [30]. In tripolar mode, current, applied to two working electrodes, is evenly distributed among them and returns through the counter electrode.

#### 2.2.3 Stimulation waveforms

The rectangular pulse waveform has been used for microstimulation for long time because of its superior charge injection capacity over other types of pulse waveforms. The charge quantity per pulse, as mentioned earlier, is defined by the amplitude and duration of the pulse, and defines the strength of that pulse.

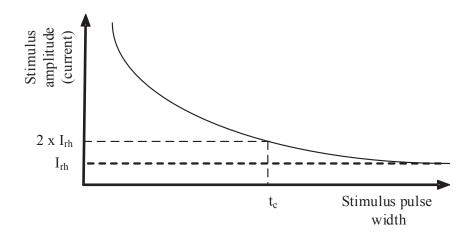

The relation between the amplitude of the current needed to generate an action potential and

Figure 2.3 Modes of electrode configuration for stimulation: (a) monopolar, (b) bipolar, and (c) tripolar.

the pulse duration was first described by the strength-duration curve formulated by Lapicque [31], [32]. The strength-duration curve is presented in Figure 2.4. The required stimulation current decreases with the increase in the pulse-width and is minimum for infinitely wide pulse. Two important parameters of this curve are the Chronaxie time ( $t_c$ ) and Rheobase current ( $I_{rh}$ ). Rheobase current, ( $I_{rh}$ ) corresponds to the current magnitude required for a pulse of infinite duration. The pulse width corresponding to twice of the rheobase current is the Chronaxie time tc. The strength-duration curve, shown in Figure 2.4, represents generally for a typical excitable tissue. However, the Rheobase current is empirical and its value is affected by the factors, such as the distance between the target neuron tissue and electrode and electrode geometry. The relation between the current required to reach threshold, ( $I_{th}$ ) and ( $I_{rh}$ ) can be well understood from the following equation

$$I_{\rm th} = \frac{I_{\rm rh}}{1 - e^{\frac{-W}{\tau_m}}} \tag{2.1}$$

Where,  $\tau_{\rm m}$  is the membrane time constant and W is the pulse width. In the literature, most of the strength-duration curves are defined for rectangular pulse.

Figure 2.4 Strength–duration curve for activation of an action potential.  $(I_{rh})$  is the Rheobase current and  $(t_c)$  is the Chronaxie time.

#### 2.3 Microelectrodes

An integral part of a neural stimulator is microelectrodes which are used to deliver the stimulation signals to the neural sites. Applications can be bladder prostheses, brain-stem and cochlear prostheses, deep brain stimulation (DBS) for treating Parkinson's diseases, epilepsy and vagus nerve stimulation for epilepsy. Microelectrodes for neural stimulation can be classified into two types based on their functional properties, surface electrodes and penetrating electrodes [33]. The first type of electrodes have the geometric surface area (GSA) of about  $100,000 \ \mu\text{m}^2$  and are placed on the surface of the stimulation sites [34]. They have low-charge density thresholds and high-charge/phase thresholds. Therefore, high current in the range of mA is required for stimulation using the surface electrodes. On the other hand, penetrating electrodes have high-charge density and low-charge/phase thresholds, and GSA of about  $10,000 \ \mu\text{m}^2$ . A large number of electrodes can be implanted in a smaller area providing better selectivity and spatial resolution. Another advantage is the needed smaller magnitude of current in the order of approximately  $100\mu\text{A}$  which reduces power consumption and increases the life span of the microstimualtor.

#### 2.3.1 Working principle of stimulation microelectrodes

Electro-chemical reaction occurs at the microelectrode-tissue interface due to the charge injection during microstimulation [34]. This reaction can be either capacitive or Faradic. Charging and discharging occur across the electrode-electrolyte double layer capacitors and reactions can be electrostatic or electrolytic in nature. Electrostatic capacitive charging

involves purely double-layer ion-electron charge separation and electrolyte dipole orientation. On the other hand, electrolytic reaction involves storing charge across a thin, high-dielectric-constant oxide at the electrode-electrolyte interface. Faradaic reactions involve the transfer of an electron across the electrode-electrolyte interface and require that some species, on the surface of the electrode or in solution, undergo a change in valence, i.e., are oxidized or reduced (oxidation-reduction process).

#### Surface electrodes

This type of electrode is non-invasive and attached to the skin [33]. Stimulation with surface electrodes has some disadvantages. Due to the high resistance of skin, stimulus voltage needs to be high enough for generating required tissue current. The necessity for large current is met also by making the electrode surface area large. Skin can be damaged at the high conductive areas due to the local current density. Surface electrodes are not a good choice for stimulation if nerves are located in the deep.

#### Percutaneous electrodes

Percutaneous electrodes are fine wire electrodes, placed close the nerves percutaneously, to provide stimulation current pulses in smaller magnitude in comparison to that for surface electrodes [33]. Monopolar stimulation currents are passed through the working electrodes and currents are returned through a common surface electrode, called return electrode.

#### Implantable electrodes

Implantation of these types of electrodes to the locations requires surgery [33]. However, this invasive technique has several advantages over non-invasive techniques. Electrodes can be placed almost precisely to the desired stimulation sites, spreading of current through surrounding tissues can be minimized, and required stimulation current is considerably reduced due to the proximity of electrodes to the nerves or muscle tissues. Examples can be peripheral nerve cuff electrode, wraparound electrode, monopolar epimysial electrode, intrathecal nerve root electrode, spinal stimulation electrodes, deep brain electrode, Michigan array, 3D Utah array and so on. With the advances in micromachining and microfabrication techniques a wide range of microelectrodes have been designed, fabricated and tested for various clinical applications such as cochlear-, visual intracortical-, bladder- and retinal implants, epilepsy, and Alzheimer diseases. Silicon based microelectrodes will be discussed in brief in the next section.

## Silicon based microelectrode array

These types of microelectrodes are made on silicon substrate and materials such as platinum, iridium, iridium-oxide, activated iridium-oxide (AIROF), sputtered iridium-oxide (SIROF)

Figure 2.5 Slicon based microelectrode arrays: (a) A 3-D 128 channel 1024 site michigan array, (b)-(c) Utah MEA [36], and (d) MEA from Blacrock Microsystems [37].

[34] or carbon nanotube are used to coat the tips of electrodes. Silicon substrate is doped with boron in case of Michigan array and electrodes are made of 4 mm long on average. Utah intracortical electrode array (UIEA) are made from a single silicon wafer of 0.2mm thickness. 1.2mm long electrodes are of needle shaped and the chemically etched sharp tips are layered with platinum, titanium-tungsten and platinum. This coating works as an electrical interface between the electrode surface and the surrounding biological tissues and provides impedance in the range of 80 - 150k $\Omega$  [35]. Access to the electrodes are provided through the gold contact pads in the back of each electrode. Figure 2.5 - Figure 2.6 show different types of silicon-based microelectrode array (MEA) fabricated by various research groups and companies [36], [37], [38].

There are also some other types of electrodes made of silicon substrate and thin film conductor based probes. Recent studies show that materials such as poly(pyrrole) (PPy) and poly(3,4-ethylenedioxythiophene) (PEDOT) have better biocompatibility than the conventionally used noble metals. Through the use of electrochemical polymerization process, PPy and PEDOT are deposited on the microelectrode sites [36], [39]. Figure 2.7 presents silicon

Figure 2.6 Silicon based microelectrodes from Cyberkinetics [38].

Figure 2.7 (a) Silicon on insulator (SOI), (b) Polymar based and (c) Micralyne MEAs [36].

on insulator (SOI), polymar based and Micralyne MEAs.

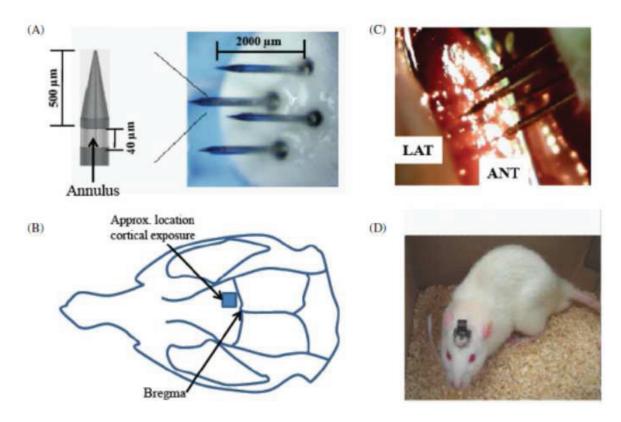

For our system, we have used a novel high-density silicon based platinum-coated microelectrode array designed by one of the Polystim Laboratory team members [40].

Figure 2.8 Equivalent circuit models for electrode-tissues interface (ETI) and ETI contacts: (a) ETI model, and (b) model of two ETIs and tissue contact. [41] © J. Biomedical Materials.

#### 2.3.2 Equivalent circuit of electrode

The typical ETI model consists of the Warburg impedance  $(Z_w)$ , a charge transfer resistance  $(R_{CT})$ , and a non faradic pseudo capacitance  $(Z_{CPA})$ , connected in parallel as presented in Figure 2.8(a) [41]. The Warburg impedance  $(Z_w)$  represents the diffusion of ionic components at the ETI interface and is expressed as follows:

$$Z_{w} = \frac{\sigma}{\sqrt{\omega}} (1 - j) \tag{2.2}$$

where  $\sigma$  is the diffusion coefficient, which is determined by the ion specie concentrations resulting from oxidation-reduction reactions close to ETI interface and the effective contact area.

The second component, R<sub>CT</sub>, in the ETI model represents the exchanged current near the ETI. It is a function of the injected stimulation current magnitude through the electrode and the developed voltage across the ETI interface. This component has been included in order to take the DC current through the interface into account.

Also, Z<sub>CPA</sub> indicates the inhomogeneous area of contact:

$$Z_{CPA} = \frac{1}{(j\omega C_{dl})^{\beta}} \tag{2.3}$$

where  $\omega$  is the angular frequency,  $\beta$  is the deviation index from a pure capacitance, and  $C_{dl}$  is the double layer capacitance.

Figure 2.8(b) shows the case, when two ETI models are in contact with tissue. Here, in between two ETI models, an electrolytic resistance,  $R_{\rm el}$  is connected in series with an electrode potential  $E_{\rm i}$ . Where,  $R_{\rm el}$  is the electrolyte resistance of the tissue.  $E_{\rm i}$  is 0 due to same area for the two contacts and the same materials used for them.

While performing in-vitro test, usually 0.9 % NaCl solution is used to represent the tissues and  $R_{el}$  is substituted by ohmic resistance  $R_{\Omega}$ .

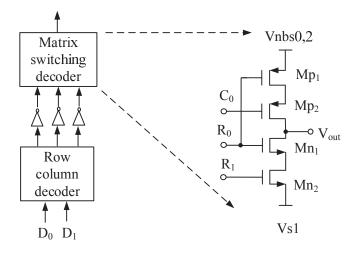

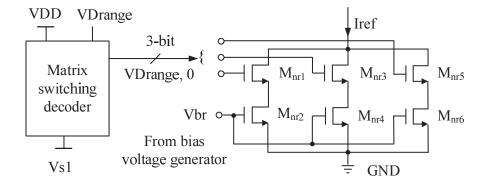

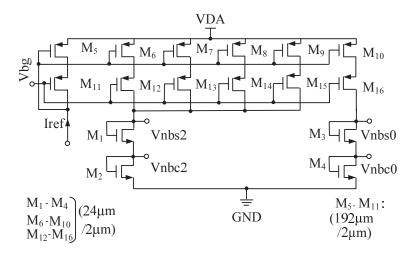

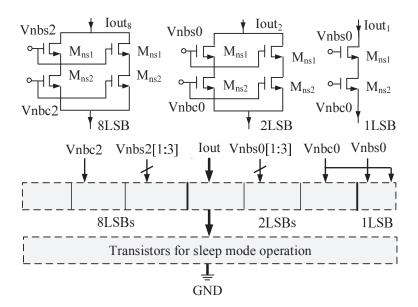

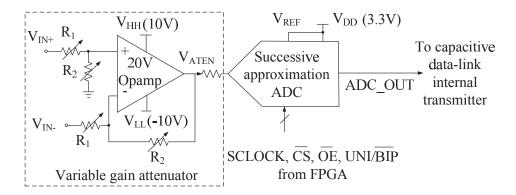

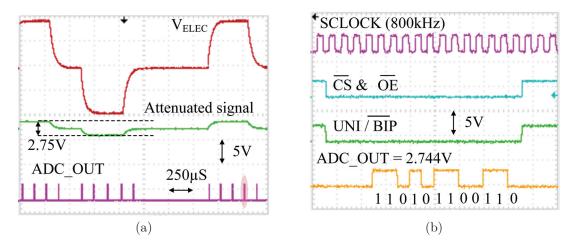

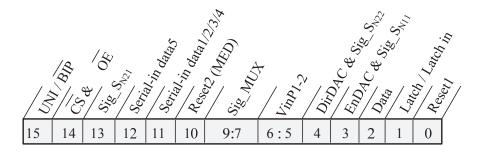

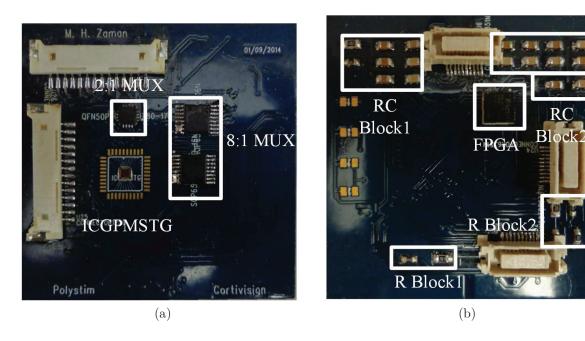

#### 2.4 Visual system