**Titre:** Analyse de performance multi-niveau et partionnement

Title: d'application radio sur une plateforme multiprocesseur

**Auteur:** José-Philippe Tremblay

Author:

**Date:** 2009

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Tremblay, J.-P. (2009). Analyse de performance multi-niveau et partionnement d'application radio sur une plateforme multiprocesseur [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/222/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/222/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Claude Thibeault

Advisors:

**Programme:** Génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

ANALYSE DE PERFORMANCE MULTI-NIVEAU ET PARTITIONNEMENT

D'APPLICATION RADIO SUR UNE PLATEFORME MULTIPROCESSEUR

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU

DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2009

© JOSÉ-PHILIPPE TREMBLAY, 2009.

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

ANALYSE DE PERFORMANCE MULTI-NIVEAU ET

PARTITIONNEMENT D'APPLICATION RADIO SUR UNE

PLATEFORME MULTIPROCESSEUR

Présenté par : TREMBLAY José-Philippe

En vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

A été dûment accepté par le jury d'examen constitué de :

M. DAVID Jean-Pierre, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. THIBEAULT Claude, Ph.D., membre et codirecteur de recherche

M. LANGLOIS Pierre, Ph.D., membre

## REMERCIEMENTS

Je te tiens d'abord à remercier M. Savaria et M. Thibeault, respectivement directeur et co-directeur de maîtrise, pour leur disponibilité, leur support et divers conseils menant à terme avec succès mes travaux de recherche. Je tiens également à souligner le soutien financier d'Octasic, principal partenaire du projet OPERA. Je remercie également mes coéquipiers du GRM et du Lacime pour leur support et encadrement lors de la réalisation du projet. Je souligne plus particulièrement l'appui de Mme Mbaye pour ses précieux conseils. Je termine par remercier ma famille et mes amis qui m'ont soutenu tout au long de mes études.

## RÉSUMÉ

Depuis déjà un bon nombre d'années, une demande importante est apparue dans le domaine des télécommunications en ce qui a trait aux systèmes portables. En plus des fonctions téléphoniques déjà existantes, plusieurs applications connexes viennent maintenant se greffer à ces appareils. Afin de pouvoir surmonter les défis imposés par ces nouvelles classes d'applications, de nouvelles méthodologies et topologies de circuit ont vu le jour. Ce mémoire s'inscrit dans le projet global OPERA qui a pour but d'explorer différentes classes d'applications par rapport à une implémentation matérielle existante de manière à guider les phases de configuration, de vérification et possiblement de modification du design actuel.

De manière plus spécifique à ce projet, un des buts était de faire ressortir rapidement et automatiquement si une application sélectionnée dans le domaine des télécommunications pouvait être exécutée selon les limites imposées par les différentes normes sur la puce Vocallo fournie par les concepteurs d'Octasic, le partenaire industriel qui supporte ce projet. Pour arriver à cet objectif, la méthodologie dite de conception basée sur les plateformes (Platform based design) a été sélectionnée. Cette technique repose sur la modélisation des différentes couches du système global, soit la couche physique représentant la puce Vocallo et la couche applicative servant à abstraire les algorithmes choisis. Une fois la modélisation des couches effectuées, il suffit de les relier en propageant les contraintes du niveau applicatif vers la couche matérielle de manière à obtenir une estimation de performance selon les caractéristiques abstraites dans chacun des modèles.

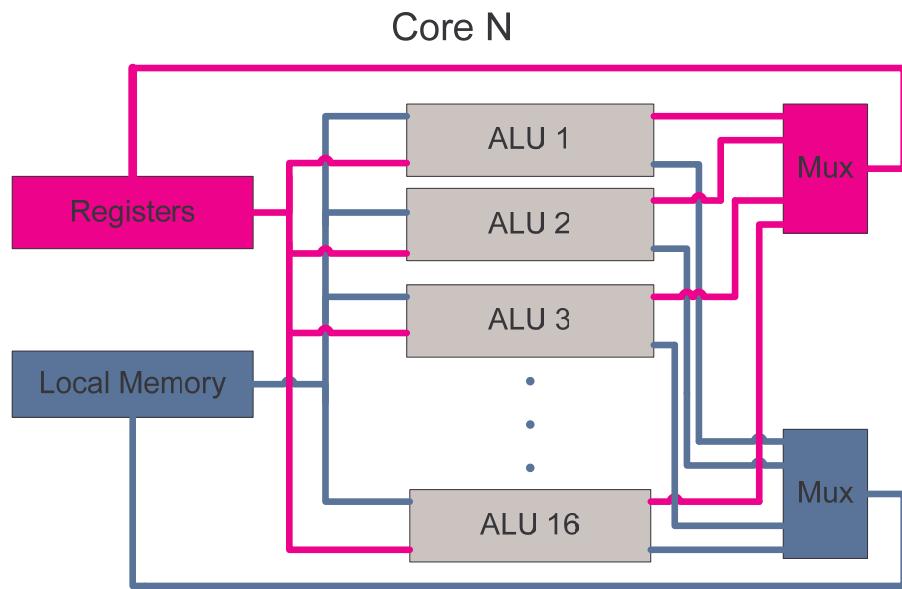

La puce Vocallo comporte plusieurs caractéristiques peu communes. En effet, le Vocallo est composé d'une matrice de 15 cœurs reliés à une mémoire externe par un seul et unique bus de communication. Chacun des ces cœurs est lui-même constitué de 16 unités opératives asynchrones (ALUs) fonctionnant en parallèle.

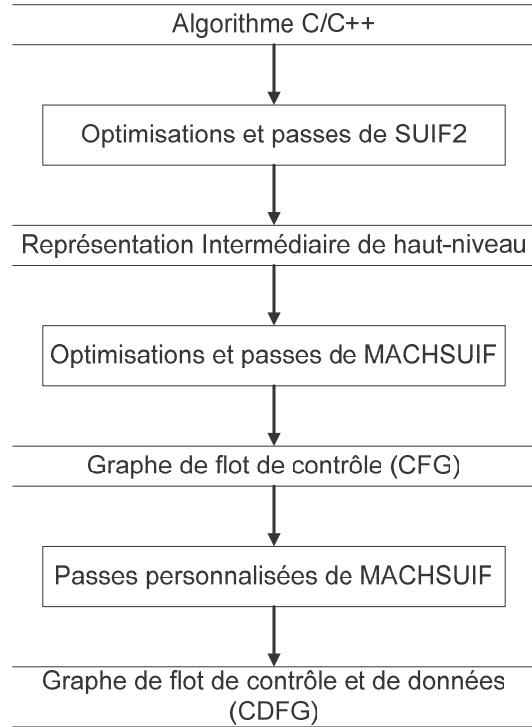

De manière à suivre la méthodologie choisie, il était nécessaire de sélectionner une représentation de l'application ainsi que d'effectuer une modélisation de la plateforme matérielle. Un graphe de flots de contrôle et de données (Control and Data Flow Graph) a été sélectionné afin de représenter les applications décrites en C ou C++. Afin de mieux visualiser le processus de développement d'une application, un processus de hiérarchisation et de caractérisation des nœuds a été instauré par rapport au graphique CDFG de base. Par la suite, à l'aide de notre infrastructure de travail basée sur SUIF2, plusieurs modélisations d'un cœur de la plateforme Vocallo ont été développées. La principale difficulté de ce procédé repose sur l'abstraction de l'asynchronisme présent dans les unités de calcul à l'intérieur d'un modèle synchrone.

La principale contribution de ce mémoire est la conception d'un outil automatique permettant d'obtenir des estimations de performance de l'exécution d'un algorithme exprimé en C ou C++ sur un des cœurs de la plateforme Vocallo. Les performances sont obtenues en termes de quantité requise de mémoire et de temps d'exécution. De nombreuses autres caractéristiques sont également annotées dans le graphique afin de pouvoir aisément comprendre les goulots d'étranglement dans les cas problématiques. Plusieurs exemples présentés dans le mémoire viennent montrer comment utiliser les estimations produites comme bases pour l'ordonnancement d'applications sur la matrice de processeurs. Notre outil rassemble finalement toutes les estimations effectuées sous une représentation graphique exprimée sous forme XML afin de servir pour la deuxième phase dynamique du projet OPERA.

## ABSTRACT

Over the last few years, an important increase in demand has appeared in the telecommunication world in terms of portable system. New classes of applications, like video capability, are now supported by these devices. In order to satisfy the challenges of these new types of software, new circuit topology and emerging methodology became a hot topic of research. This thesis is a small part of the OPERA project that tries to explore several classes of applications in regards to a specific hardware implementation in order to guide efficiently the phases of configuration and verification and possibly could lead to modifications of the design itself.

A main goal of this project was to quickly and automatically know if a selected application within the world of telecommunication could be executed on the Vocallo chipset, developed by Octasic, the industrial partner sponsoring this project, while satisfying the requirements imposed by the different standards. In order to achieve this goal, the Platform Based Design approach was chosen. This technique rests on the modeling of the different layers of the overall system. The physical layer serves to represent the Vocallo chip, while the application layer is used to capture the algorithm's requirements. Upon the completion of the modeling of these layers, the constraints of the application are propagated towards the physical layer to obtain an estimation of performances based on the selected models.

The Vocallo chip is characterised by several uncommon particularities. It is composed of a matrix of 15 cores linked to an external memory by a single communication bus. It is also important to specify that each of the cores is composed of 16 asynchronous ALUs working in parallel. By following the selected methodology, an intermediate representation of the application is selected. The control and data flow graph representation was chosen to represent applications described in C or C++. In order to better visualise possible tradeoffs when mapping applications, a hierarchical structure embedding detailed node models was created. Several versions of the Vocallo model

were then developed within the SUIF2 infrastructure. A major issue in this process was the abstraction of the asynchronous behaviour of the processing units.

The main contribution of this thesis is the implementation of an automated tool producing performance estimates of how Vocallo would behave when executing on one of the chip's core some key algorithms expressed in C or C++. These performances are reported in terms of memory requirements and overall execution time. Several other characteristics are also annotated on the graph to easily identify bottlenecks in the application. Several examples presented in the thesis show how to use these estimates as a basis for mapping target algorithms on the Vocallo core processors. Lastly, our tool also summarizes all of the estimates under a graphical form expressed with a XML format.

## TABLE DES MATIÈRES

|                              |      |

|------------------------------|------|

| Remerciements.....           | III  |

| Résumé.....                  | IV   |

| Abstract.....                | VI   |

| Table des matières.....      | VIII |

| Listes des figures.....      | XII  |

| Liste des Tableaux .....     | XIV  |

| Sigles et abréviations ..... | XV   |

| Liste des annexes .....      | XVI  |

|                                     |          |

|-------------------------------------|----------|

| <b>CHAPITRE 1 INTRODUCTION.....</b> | <b>1</b> |

|-------------------------------------|----------|

|                                                               |   |

|---------------------------------------------------------------|---|

| 1.1 Conception basée plateforme (Platform Based Design) ..... | 3 |

| 1.2 Contexte du projet.....                                   | 6 |

| 1.3 Architecture Vocallo.....                                 | 6 |

| 1.4 Applications visées .....                                 | 7 |

| 1.5 Contributions du mémoire .....                            | 8 |

| 1.6 Plan du mémoire .....                                     | 9 |

|                                         |           |

|-----------------------------------------|-----------|

| <b>CHAPITRE 2 MISE EN CONTEXTE.....</b> | <b>11</b> |

|-----------------------------------------|-----------|

|                                                     |    |

|-----------------------------------------------------|----|

| 2.1 Architecture MPSoC.....                         | 12 |

| 2.1.1 Historique des MPSoC.....                     | 12 |

| 2.1.2 Défis des MPSoC.....                          | 16 |

| 2.2 Graphe de flots de contrôle et de données ..... | 18 |

| 2.2.1 Principes de base.....                        | 18 |

| 2.2.2 Variantes du CDFG.....                        | 21 |

| 2.3 Partitionnement et ordonnancement .....         | 24 |

|                                                                        |           |

|------------------------------------------------------------------------|-----------|

| 2.4 Applications .....                                                 | 27        |

| <b>CHAPITRE 3 L'ARCHITECTURE DU VOCALLO .....</b>                      | <b>30</b> |

| 3.1 Spécification générale du Vocallo .....                            | 31        |

| 3.2 Architecture Inter-Noyaux .....                                    | 31        |

| 3.2.1 Matrice de processeurs.....                                      | 32        |

| 3.2.2 Communication inter-noyau .....                                  | 33        |

| 3.2.3 Circuits périphériques .....                                     | 34        |

| 3.3 Spécification d'un noyau .....                                     | 34        |

| 3.3.1 Mémoire Locale .....                                             | 35        |

| 3.3.2 Registres.....                                                   | 36        |

| 3.3.3 Architecture des ALU .....                                       | 37        |

| 3.4 Conclusion .....                                                   | 38        |

| <b>CHAPITRE 4 LES GRAPHES DE FLOTS DE CONTRÔLE ET DE DONNÉES .....</b> | <b>39</b> |

| 4.1 Cadre de travail .....                                             | 40        |

| 4.1.1 SUIF2.....                                                       | 40        |

| 4.1.2 MACHSUIF .....                                                   | 41        |

| 4.1.3 Flot de conception du CDFG .....                                 | 41        |

| 4.2 Processus de création du CDFG .....                                | 44        |

| 4.2.1 Algorithme de conversion du CFG vers le CDFG.....                | 45        |

| 4.2.2 Extraction des dépendances de données .....                      | 47        |

| 4.3 Hiérarchisation .....                                              | 50        |

| 4.3.1 Algorithme de hiérarchisation du CDFG.....                       | 51        |

| 4.3.2 Structures de contrôle .....                                     | 53        |

| 4.3.2.1 Structure séquentielle.....                                    | 53        |

| 4.3.2.2 Boucle .....                                                   | 54        |

| 4.3.2.3 Branchement .....                                              | 56        |

| 4.4 Caractérisations des nœuds .....                                   | 57        |

|                                                          |           |

|----------------------------------------------------------|-----------|

| 4.4.1 Nœuds de base .....                                | 57        |

| 4.4.2 Nœuds hiérarchiques.....                           | 58        |

| 4.5 Visualisation .....                                  | 59        |

| <b>CHAPITRE 5 ESTIMATION DES BESOINS EN MÉMOIRE.....</b> | <b>61</b> |

| 5.1 Estimation des besoins en mémoire .....              | 62        |

| 5.1.1 Caractérisation de la mémoire .....                | 62        |

| 5.1.2 Extraction des besoins en mémoire.....             | 64        |

| 5.1.3 Validation.....                                    | 65        |

| 5.2 Partitionnement .....                                | 68        |

| 5.2.1 Principes de partitionnement.....                  | 68        |

| 5.2.2 Exemple de partitionnement .....                   | 71        |

| 5.3 Conclusion .....                                     | 73        |

| <b>CHAPITRE 6 MODÉLISATION ET ORDONNANCEMENT .....</b>   | <b>75</b> |

| 6.1 Modélisation .....                                   | 75        |

| 6.1.1 Premier modèle .....                               | 75        |

| 6.1.2 Deuxième modèle .....                              | 77        |

| 6.1.3 Validation des modèles .....                       | 80        |

| 6.2 Ordonnancement d'application.....                    | 83        |

| 6.2.1 Taux d'utilisation.....                            | 83        |

| 6.2.2 Limite dues aux unités de contrôle .....           | 85        |

| 6.2.3 Exemple .....                                      | 87        |

| 6.3 Variabilité de la vitesse .....                      | 89        |

| 6.3.1 Cause architecturale.....                          | 89        |

| 6.3.2 Effet du parallélisme .....                        | 90        |

| 6.4 Conclusion .....                                     | 93        |

| <b>CHAPITRE 7 CONCLUSION .....</b>                       | <b>95</b> |

| 7.1 Synthèse des travaux.....                            | 95        |

|                                          |            |

|------------------------------------------|------------|

| 7.2 Limitations des travaux.....         | 97         |

| 7.3 Possibilités de travaux futurs ..... | 98         |

| <b>RÉFÉRENCES.....</b>                   | <b>99</b>  |

| <b>ANNEXES.....</b>                      | <b>104</b> |

## LISTES DES FIGURES

|                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-1. Évolution des modèles d'entrée de design utilisés dans le domaine de la conception de circuits intégrés.....  | 2  |

| Figure 1-2. Interaction entre les différentes couches d'abstraction .....                                                 | 5  |

| Figure 2-1. MPSoC Daytona de Lucent.....                                                                                  | 13 |

| Figure 2-2. Réseau de processeurs C-5.....                                                                                | 14 |

| Figure 2-3. Le Viper Nexperia de Philips.....                                                                             | 15 |

| Figure 2-4. Le OMAP 5912 de Texas Instrument .....                                                                        | 16 |

| Figure 2-5. Exemple de CFG et de DFG .....                                                                                | 19 |

| Figure 2-6. Exemple de code et de son CDFG équivalent.....                                                                | 20 |

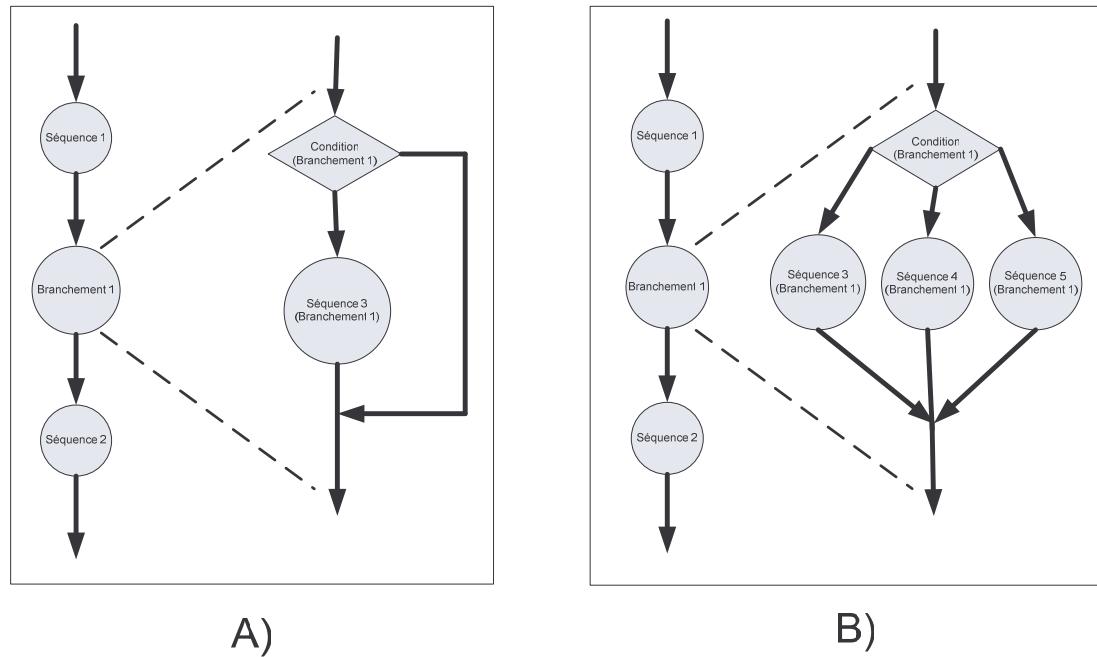

| Figure 2-7. Transformations de branchement : A) Branchement complet B) Branchement étendu.....                            | 22 |

| Figure 2-8. Transformations de boucle : A) Boucle complète B) Boucle étendue.....                                         | 23 |

| Figure 2-9. Exemples de partitionnement : A) Architecture MPSoC à 8 processeurs B-C-D) Stratégies de partitionnement..... | 25 |

| Figure 3-1. Schéma bloc de l'architecture complète du Vocallo [25] .....                                                  | 32 |

| Figure 3-2. Schéma bloc de l'architecture d'un noyau du Vocallo .....                                                     | 35 |

| Figure 4-1. Flot de conception d'un CDFG .....                                                                            | 42 |

| Figure 4-2. Algorithme de conversion du CFG vers le CDFG .....                                                            | 45 |

| Figure 4-3. Exemples de dépendances de données .....                                                                      | 50 |

| Figure 4-4. Algorithme de hiérarchisation du CDFG .....                                                                   | 52 |

| Figure 4-5. Exemples de représentations de boucles .....                                                                  | 55 |

| Figure 4-6. Exemples de représentations de branchements .....                                                             | 56 |

| Figure 5-1. Première étape de partitionnement.....                                                                        | 69 |

| Figure 5-2. Deuxième étape de partitionnement.....                                                                        | 70 |

| Figure 6-1. Algorithme d'ordonnancement du premier modèle .....                                                           | 76 |

| Figure 6-2. Deuxième algorithme d'ordonnancement .....                                                                    | 79 |

|                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| Figure 6-3. Exemple du deuxième modèle d'ordonnancement .....                                                   | 80 |

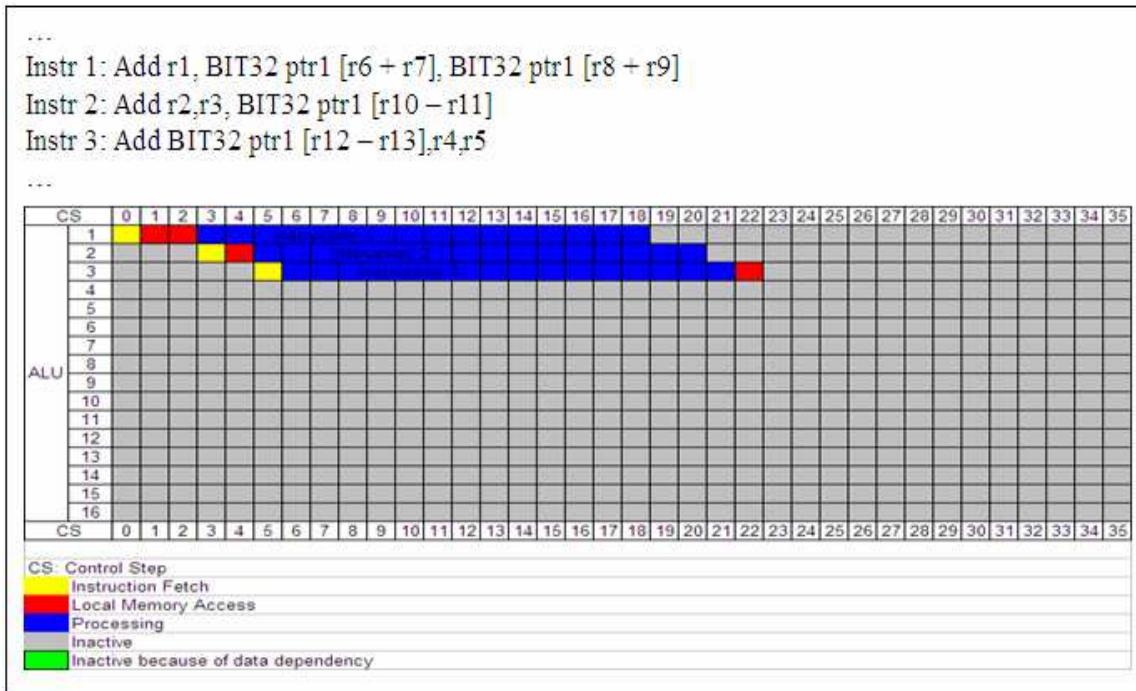

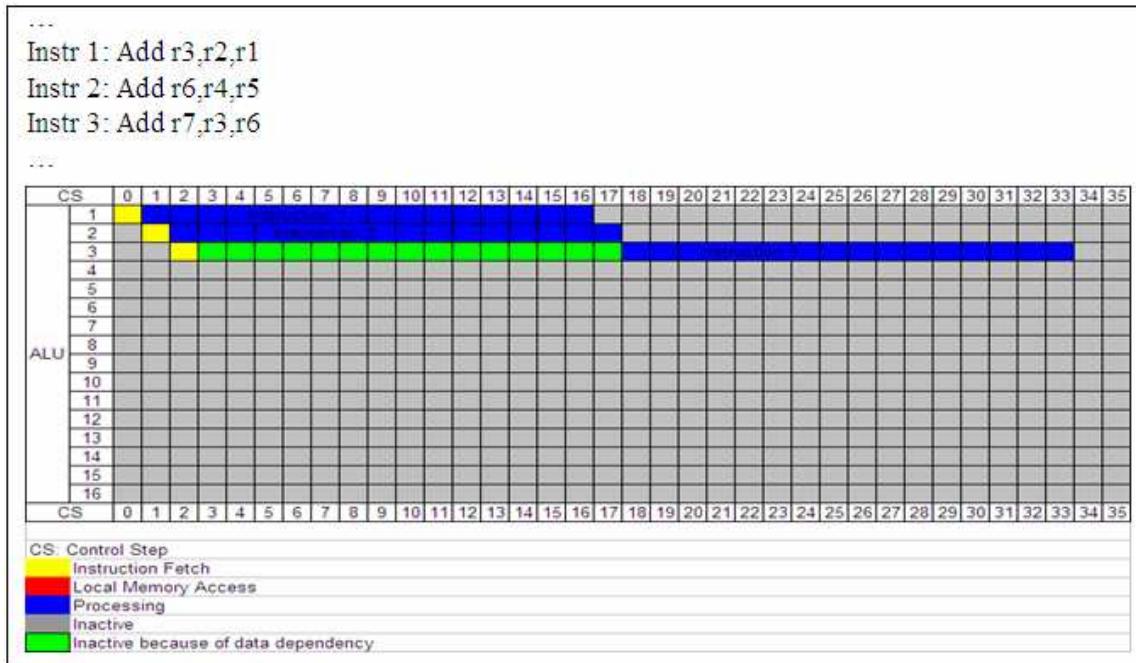

| Figure 6-4. Effet des dépendances de données .....                                                              | 85 |

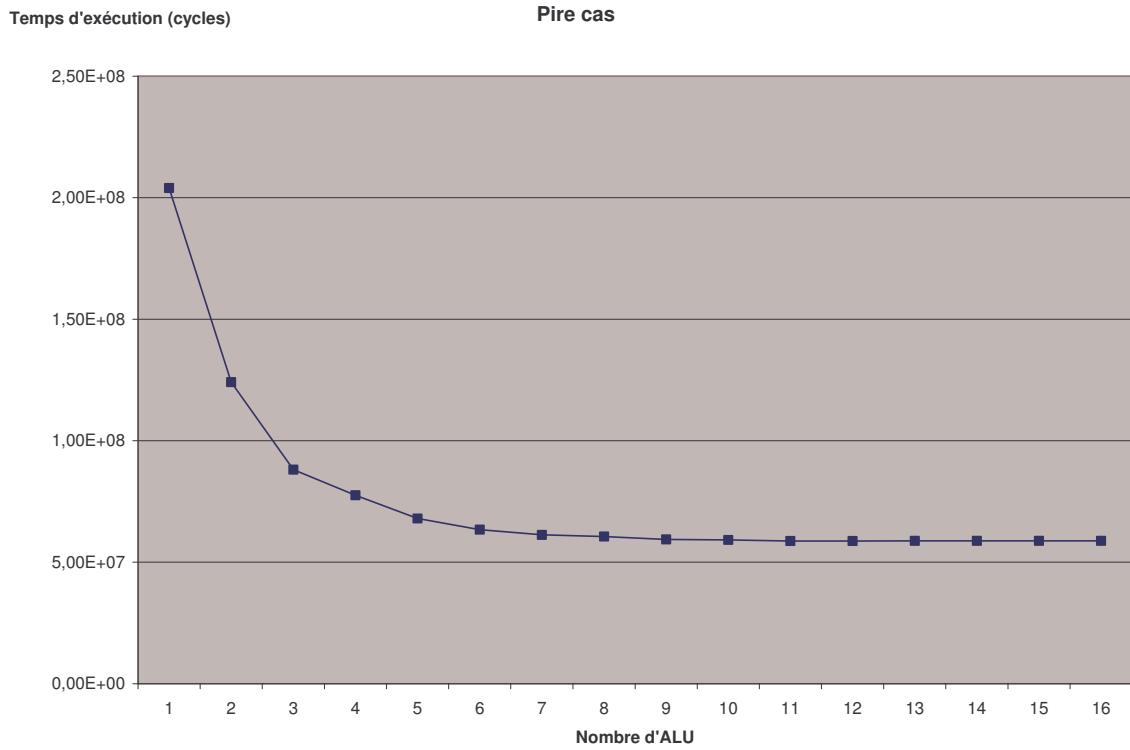

| Figure 6-5. Temps d'exécution du décodage Turbo en fonction du nombre d'Alu utilisés .....                      | 86 |

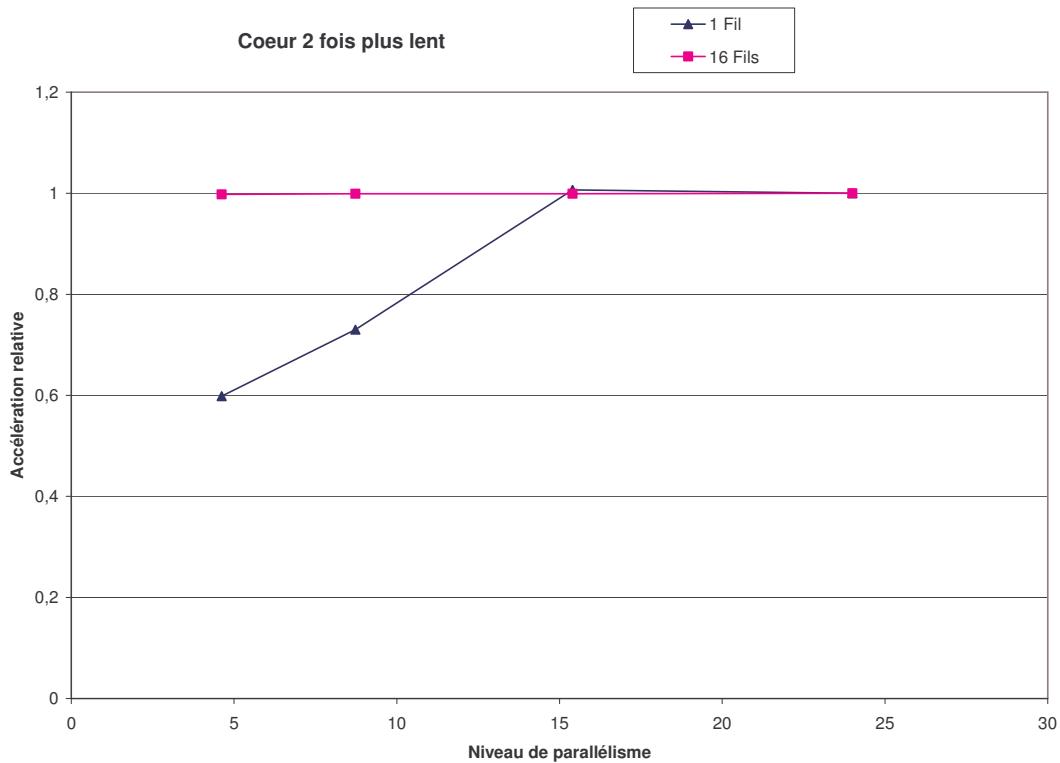

| Figure 6-6. Variation de l'accélération relative en fonction du niveau de parallélisme pour un cœur lent.....   | 91 |

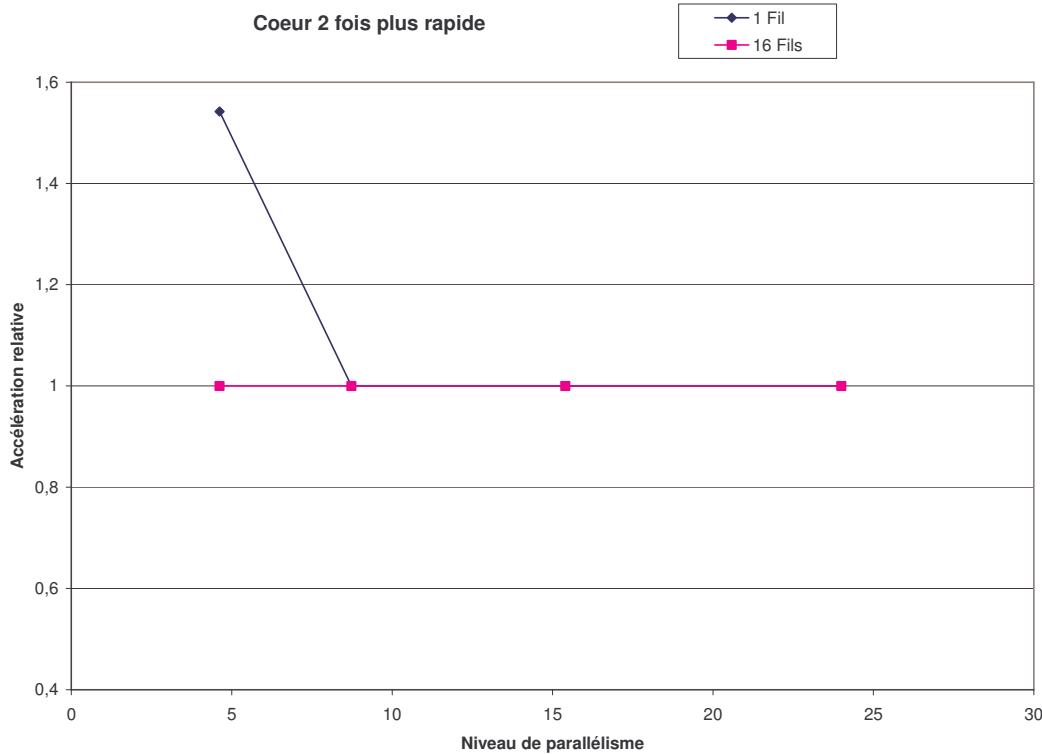

| Figure 6-7. Variation de l'accélération relative en fonction du niveau de parallélisme pour un cœur rapide..... | 92 |

## LISTE DES TABLEAUX

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

| Tableau 1-1. Ressources matérielles typiques et exemple de caractéristiques .....        | 4  |

| Tableau 3-1. Type et quantité des registres d'un noyau .....                             | 36 |

| Tableau 3-2. Étape d'exécution d'une instruction .....                                   | 37 |

| Tableau 4-1. Caractéristiques des nœuds de base .....                                    | 57 |

| Tableau 4-2. Caractéristiques des nœuds hiérarchiques .....                              | 58 |

| Tableau 5-1. Catégories de mémoire .....                                                 | 63 |

| Tableau 5-2. Estimation de la quantité de mémoire requise pour l'addition vectorielle .. | 66 |

| Tableau 5-3. Estimation mémoire pour le Maximum vectoriel .....                          | 66 |

| Tableau 5-4. Estimation mémoire pour le FIR Complexé .....                               | 66 |

| Tableau 5-5. Estimation mémoire pour le Filtre LMS .....                                 | 67 |

| Tableau 5-6. Partitionnement final avec une mémoire locale de 10 Ko .....                | 72 |

| Tableau 5-7. Partitionnement final avec une mémoire locale de 5 Ko .....                 | 72 |

| Tableau 5-8. Partitionnement final avec une mémoire locale de 3 Ko .....                 | 73 |

| Tableau 6-1. Durée moyenne des instructions selon leur classe .....                      | 78 |

| Tableau 6-2. Validation pour l'addition vectorielle .....                                | 81 |

| Tableau 6-3. Validation pour le maximum vectoriel .....                                  | 81 |

| Tableau 6-4. Validation pour le filtre complexe .....                                    | 81 |

| Tableau 6-5. Validation pour le filtre LMS .....                                         | 82 |

| Tableau 6-6. Validation pour le codage .....                                             | 82 |

| Tableau 6-7. Temps d'exécution en fonction du nombre de paquets traités .....            | 88 |

## SIGLES ET ABRÉVIATIONS

|       |                                               |

|-------|-----------------------------------------------|

| ALAP  | : As Late As Possible                         |

| ALU   | : Arithmetic and Logical Unit                 |

| ASAP  | : As Soon As Possible                         |

| CDFG  | : Control and Data Flow Graph                 |

| CDMA  | : Code Division Multiple Access               |

| CFG   | : Control Flow Graph                          |

| DDR   | : Double Data Rate                            |

| DFG   | : Data Flow Graph                             |

| DMA   | : Direct Memory Access                        |

| DSP   | : Digital Signal Processor                    |

| GDL   | : Graphical Description Language              |

| IP    | : Intellectual Property                       |

| MIMD  | : Multiple Instruction Multiple Data          |

| MPSoC | : Multi-Processor System on Chip              |

| NoC   | : Network on Chip                             |

| OFDM  | : Orthogonal Frequency Division Multiplexing  |

| OPERA | : Octasic Polytechnique ÉTS Radio Application |

| PBD   | : Platform Based Design                       |

| RISC  | : Reduced Instruction Set Computer            |

| RTW   | : Real-Time Workshop                          |

| SoC   | : System on Chip                              |

| SUIF  | : Stanford University Intermediate Format     |

| VCG   | : Visualization of Compiler Graphs            |

| WCDMA | : Wideband Code Division Multiple Access      |

| XML   | : eXtensible Markup Language                  |

## LISTE DES ANNEXES

**Annexe A.** Code de l'application synthétique servant de démonstration pour l'outil de partitionnement

**Annexe B.** Représentation XML du partitionnement final avec une mémoire locale de 10K

**Annexe C.** Représentation XML du partitionnement final avec une mémoire locale de 5K

**Annexe D.** Représentation XML du partitionnement final avec une mémoire locale de 3K

**Annexe E.** Algorithme synthétique servant l'effet du parallélisme par rapport à la vitesse d'un cœur

**Annexe F.** Représentation graphique de l'addition vectorielle

## CHAPITRE 1

### INTRODUCTION

La complexité toujours croissante des designs électroniques combinée à un nombre important de technologies devant être maîtrisées afin d'obtenir un produit de qualité répondant aux demandes du marché, poussent les sociétés à se concentrer sur leurs compétences primaires. Nous pouvons assister en effet à une restructuration de l'industrie d'un mode vertical au sein d'une même entreprise vers un modèle plus horizontal combinant le savoir-faire propre de plusieurs sociétés travaillant collectivement dans l'accomplissement d'un même design. Ce dernier facteur, ainsi que la pression exercée par un temps de mise en marché, toujours plus difficile à satisfaire, associé aux coûts importants liés à la réalisation de projets de grande envergure, entraîne le besoin de développer des méthodes de conception plus structurées axées sur le principe de réutilisabilité et d'implémentation correcte sans besoin d'itérations subséquentes. Cette quête de flexibilité dans le domaine des circuits embarqués force l'industrie à migrer vers des solutions programmables pour un nombre grandissant de classes d'applications, rendant urgent le besoin de nouvelles méthodologies palliant à toutes ces nouvelles exigences. Afin de toujours pouvoir compter sur un flot de design économiquement satisfaisant, celui-ci doit entre autre permettre de restreindre l'exploration de l'espace de design afin d'obtenir des résultats supérieurs dans les contraintes de temps fixées. Cette tendance est déjà observable dans les domaines de la programmation conventionnelle et de la conception de circuits intégrés. En informatique, de nouveaux langages utilisant un niveau d'abstraction plus élevé sont venus remplacer les langages traditionnels tels l'assembleur, tandis que l'utilisation de modules encapsulant de la propriété intellectuelle, couramment appelés blocs IP (Intellectual Property), est présentement en train de graduellement déplacer les cellules standardisées comme le module de base servant à exprimer le design d'un circuit intégré. Notons que les modules IP sont des structures plus complexes que les cellules normalisées et qu'en fait, un module IP peut

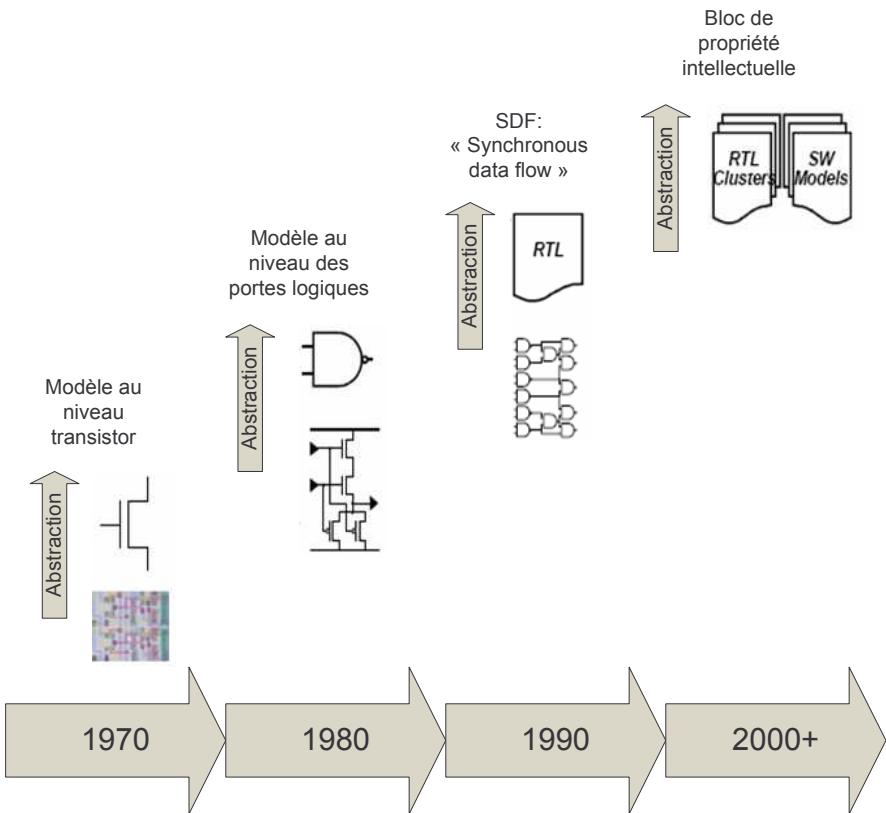

être composé d'un assemblage de cellules normalisées. La figure 1.1 [28] présente cette réalité en montrant l'évolution des modèles utilisés pour exprimer les designs. La méthodologie servant de base pour ce projet peut donc être vue comme la progression naturelle vers un niveau plus élevé d'abstraction dans la conception de systèmes embarqués complexes. La méthodologie adoptée est communément appelée design basé sur des plateformes ou plus communément appelé « platform-based design » (PBD). Cette méthodologie émergente peut aussi être considérée comme une excroissance de l'évolution des SoC dans laquelle les facteurs économiques engendrés par la fabrication et le design de circuits intégrés ont été longuement étudiés.

Figure 1-1. Évolution des modèles d'entrée de design utilisés dans le domaine de la conception de circuits intégrés

## 1.1 Conception basée plateforme (Platform Based Design)

L'objectif global du PBD est de proposer une méthodologie permettant d'évaluer plus rapidement et de manière efficace différentes combinaisons d'éléments de calcul (processeur à usage général, DSP, ...), de mémoire et d'interconnexions (bus, NOC, ...) en sacrifiant le moins possible une performance potentielle atteignable. Celle-ci s'applique à tous les niveaux d'abstraction du design procurant ainsi une structure de travail où des pratiques connues de design qui peuvent être tirées de recherches académiques peuvent être évaluées afin de permettre d'en justifier l'utilisation. Globalement, le PBD peut être décrit comme une approche du type rendez-vous au milieu (*meet-in the middle*) où plusieurs raffinements descendant successifs d'une même spécification rejoignent les abstractions d'implémentations possibles.

Pour ce faire, il est important de bien identifier les couches sur lesquelles reposeront les procédés de raffinement et d'abstraction. Ces couches prennent également le nom de plateforme. On peut aussi définir une plateforme comme un niveau d'abstraction facilitant un certain nombre de raffinements de manière à être elle-même raccordée à un autre niveau d'abstraction (plateforme) dans le flot de conception. Ces couches cachent les détails de plusieurs raffinements possibles des couches inférieures. Celles-ci servent entre autres à isoler les détails des niveaux subséquents tout en laissant transparaître assez d'informations à propos de ces niveaux inférieurs pour explorer l'espace de design afin d'obtenir une prédiction la plus précise possible d'une implémentation finale. Une plateforme peut prendre la forme d'une librairie d'éléments souvent caractérisés par un modèle de fonctionnement précis qui offre une estimation plus ou moins précise dépendant du modèle choisi. Les choix des caractéristiques abstraites des plateformes à chacun des niveaux sont primordiaux et ils sont toujours régis par un compromis entre la complexité et le degré de précision de la modélisation. Les éléments abstraits sont souvent sélectionnés selon un niveau d'importance pour le concepteur. Ces différentes ressources peuvent même être implémentées à l'aide de différents types de technologies

et fournir des performances très variables en fonction des choix effectués. Le tableau 1-1 décrit les ressources matérielles typiques ainsi que les caractéristiques à modéliser.

Tableau 1-1. Ressources matérielles typiques et exemple de caractéristiques

| Type de ressource   | Exemple                        | Caractéristiques     |              |

|---------------------|--------------------------------|----------------------|--------------|

| Unité de traitement | Processeurs                    | Fréquence d'Horloge  | MIPS         |

|                     | - Usage général                | Taille de la mémoire | Puissance    |

|                     | - Spécifique à une application | Jeu d'instructions   | Pipeline     |

|                     | - DSP                          |                      |              |

|                     | Dédiés                         | Latence              | Débit        |

|                     | - Co-processeurs               | Adressage            | Mode "Burst" |

|                     | - Hard-Soft IP                 | Taille               |              |

| Interconnexions     | Personnalisé                   | Taille               | Largeur      |

|                     | Bus                            | Latence              | Puissance    |

|                     | "Network-on-Chip"              | Vitesse d'accès      |              |

| Mémoires            | DRAM                           | Taille               | Latence      |

|                     | SRAM                           | Fréquence            | Puissance    |

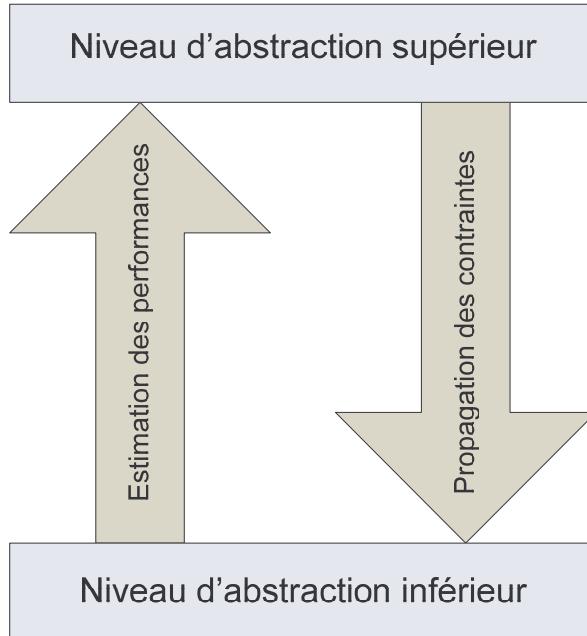

Dans le cas de plateformes représentant une architecture, il est à noter que la flexibilité se doit d'être une propriété primordiale. Ceci aura sûrement comme effet, dans les prochaines années, de satisfaire l'effort de calcul requis à l'aide d'éléments programmables, rendant ainsi le design électronique de plus en plus dépendant de sa partie logicielle et de la qualité de ce logiciel. Lorsque la composition des plateformes supérieure et inférieure est bien définie, il suffit de relier les deux pour former une pile de plateformes, communément appelée « *platform stack* ». Pour ce faire, puisque la PBD est de type rendez-vous au milieu, il faut propager les contraintes obtenues de la plateforme supérieure vers le bas et propager les performances estimées à l'aide de la plateforme inférieure vers le haut. Ce processus est illustré à la figure 1-2. Une pile de plateformes est donc composée d'au moins deux plateformes, ou de plusieurs séries de sous-plateformes, ainsi que de tous les outils et méthodes utilisés pour relier deux niveaux adjacents.

**Figure 1-2. Interaction entre les différentes couches d'abstraction**

L'utilisation de cette méthodologie émergente procure de nombreux bénéfices face aux problématiques actuelles du milieu en mettant en évidence le besoin accru de réutilisabilité et de régularité, pour en arriver à des circuits électroniques économiquement réalisables. En effet, les couches supérieures permettent le développement d'applications sans avoir à tenir compte des caractéristiques précises de leur implémentation matérielle. Les couches inférieures, quant à elles, servent à spécifier certains éléments comme partie d'une plateforme, de manière à pouvoir obtenir une estimation précise et rapide de plusieurs choix architecturaux aussi variés que complexes. Cette méthode semble en effet avoir été adoptée par plusieurs compagnies, dont Philips avec la Nexpria développée pour le multimédia et TI avec OMAP pour la téléphonie cellulaire [9]. Ces plateformes sont toutes deux basées sur des composants programmables. Il est à parier que de nombreuses autres leur emboîteront le pas dans les années à suivre.

## 1.2 Contexte du projet

Ce projet de maîtrise s'inscrit dans le cadre du projet OPÉRA qui signifie « Octasic Polytechnique ÉTS Radio Application ». L'objectif global du projet OPÉRA est d'explorer différentes classes d'applications par rapport à une implémentation matérielle existante, de manière à guider les phases de configuration, de vérification et possiblement de modification du design actuel. De manière plus spécifique, le projet de recherche OPÉRA vise à déterminer si la classe d'algorithmes choisie peut en effet être implémentée de manière efficace et correcte sur l'architecture étudiée. Il vise aussi à permettre d'identifier les goulots d'étranglement empêchant son bon fonctionnement dans le cas d'une réponse négative. La mise en lumière de ces goulots pourra entre autres servir de base dans le cas d'éventuels changements apportés à la plateforme étudiée. L'approche retenue pour effectuer cette tâche est celle de la conception basée sur les plateformes. Pour ce faire, deux types de modèles seront employés pour caractériser et relier les parties applicatives et matérielles de manière à définir un ensemble de plateformes selon les principes énoncés précédemment. Le premier, de nature statique, prendra la forme d'une bibliothèque contenant les caractéristiques retenues des deux niveaux, tandis que le deuxième sera dynamique, à l'aide de la modélisation effectuée dans le langage SystemC. Donc, dans le cadre de ce projet, la plateforme supérieure sera constituée d'une abstraction d'applications sélectionnées dans le domaine des télécommunications, alors que la couche inférieure représentera le processeur Vocallo, développé et fourni par la compagnie Octasic.

## 1.3 Architecture Vocallo

On peut décrire rapidement l'architecture Vocallo comme une matrice de processeurs homogènes de type DSP. Cette architecture s'inscrit dans la tendance des MPSoC. Malgré sa capacité à traiter des applications complexes sur une seule et même puce, à l'aide de ses multiples processeurs indépendants, l'objectif principal de sa conception était d'atteindre une consommation de puissance très faible. Cette dernière particularité,

qui constitue présentement un secteur de recherche complet en lui-même, est obtenue entre autres grâce à l'utilisation de plusieurs unités opératives asynchrones, dans chacun des coeurs de celle-ci. Plus de détails sur la complexité apparente et le fonctionnement de la puce seront donnés au chapitre 3. Comme la plateforme matérielle est fournie, les particularités suivantes devront être prises en compte, venant ainsi spécialiser la définition du PBD présentée ci-haut. En effet, la composition de la bibliothèque de caractérisation du processeur se fera principalement de manière à pouvoir identifier les goulots d'étranglement. Dans ce cas-ci, la plateforme inférieure servira spécialement à imposer les limites physiques de l'implémentation actuelle, plutôt qu'à restreindre l'exploration de l'espace de design pour respecter les exigences imposées par l'application retenue. Étant donnée la complexité du processeur au cœur de l'architecture Vocallo, un effort particulier devra aussi être accordé à une modélisation précise de ses caractéristiques, afin de pouvoir tirer les estimations les plus justes possibles. Vers la fin du projet, la mise à notre disposition d'une suite d'outils développés par Octasic en parallèle avec le déroulement du projet OPÉRA nous a offert la possibilité de pouvoir valider la justesse de nos approximations par rapport à celles prédites par les concepteurs de la puce. Dans une deuxième phase, cette validation pourra également être accomplie face à une exécution réelle de l'application sélectionnée sur les premiers prototypes physiques.

## 1.4 Applications visées

Ce projet de recherche vise principalement des applications de radio logicielle. Contrairement aux radios classiques, le principe de radio logicielle repose sur l'implémentation des différentes étapes de traitement de signal (filtrage, décimation, démodulation, décodage, ...) de manière purement logicielle ou à l'aide de matériel physique flexible. Cette méthode émergente en télécommunications permet d'atteindre des performances accrues tout en conférant une grande adaptabilité comparativement aux traditionnels composants matériels spécifiques (filtres, oscillateurs, ...). Cette flexibilité

s'obtient beaucoup plus facilement en ne changeant que des paramètres, au niveau logiciel dans le code, correspondants aux nouveaux objectifs de communication visés. Ces changements conduisent à reprogrammer une ou plusieurs unités de traitement sélectionnées (DSP, ASIC, FPGA, PC). Ce projet tend par contre à viser principalement trois grandes classes d'applications soient : les communications sans fils 3G, le WiFi et le WiMax. Toutes ces applications s'appuient elles-mêmes sur des technologies de transmission, telles les CDMA, WCDMA et OFDM. On peut rapidement caractériser les algorithmes de ces technologies comme étant très intenses en calcul sur une grande quantité de données. Ces dernières particularités semblent a priori faire de la plateforme Vocallo un bon choix permettant une grande flexibilité, parce qu'elle offre une importante puissance de calcul, particulièrement grâce à sa matrice de processeurs. Il est également à noter que la plupart des algorithmes de ce domaine sont codés en C ou en Matlab. De ce fait, l'analyse globale devra prendre en compte les différentes particularités de ces deux langages.

## 1.5 Contributions du mémoire

De manière plus spécifique, ce mémoire s'inscrit dans la première phase du projet global, soit l'analyse statique. Le but de cette recherche est de caractériser de manière automatique les applications sélectionnées en langage C afin d'en faire ressortir les différentes contraintes imposées et de pouvoir, à l'aide d'une modélisation de la plateforme Vocallo, prédire les performances de ces algorithmes dans le but éventuel de guider les décisions quant au partitionnement et au « mapping » des algorithmes afin de respecter les limites imposées par les différents standards de télécommunications. Pour ce faire, la technique du PBD est utilisée. L'extraction des contraintes des applications joue le rôle de niveau supérieur, tandis que la modélisation de la matrice de processeurs tiendra celui du niveau d'abstraction inférieur. La propagation des contraintes d'un niveau vers l'autre nous permettra de faire ressortir les forces et les faiblesses de la

plateforme matérielle face aux algorithmes choisis. De manière plus concrète, la contribution peut être divisée en trois étapes distinctes :

- Le développement d'un outil automatique d'extraction des contraintes d'un algorithme en C. L'expression des ces contraintes se fera sous la forme d'un graphe de type CDFG.

- L'analyse de la plateforme Vocallo et la conception d'un modèle en C qui corresponde le plus précisément possible à l'implémentation physique actuelle.

- Le regroupement des deux niveaux d'abstraction et en faisant ressortir, en analysant les résultats obtenus à l'aide de métriques de performances, les bonnes pratiques de programmation et d'ordonnancement, menant à la meilleure utilisation possible du processeur au cœur de l'architecture Vocallo vis-à-vis les classes d'applications mentionnées ci-haut.

## 1.6 Plan du mémoire

Ce mémoire commence par une introduction des différents concepts liés à l'utilisation de la méthode « Platform Based-Design ». Une brève description des nombreux aspects de ce projet sera aussi incluse dans ce premier chapitre. Le chapitre 2 fera office de revue de littérature et aura pour but de présenter et justifier l'utilisation de techniques ayant déjà prouvé leur efficacité dans un passé rapproché. Les principales caractéristiques d'un graphe de type CDFG, ainsi que différentes techniques d'ordonnancement seront en effet discutées dans cette section, qui se terminera par une description sommaire des algorithmes utilisés dans l'obtention des résultats présentés dans ce mémoire. Puisqu'une bonne compréhension de l'architecture Vocallo est nécessaire afin de comprendre la modélisation résultante, le chapitre 3 présentera en détails une description de tous les composants que l'on retrouve sur la plateforme matérielle ainsi que leurs interactions. Le chapitre 4 se concentrera sur la production automatique de notre version d'un CDFG typique, en expliquant toutes les nouvelles modifications, par rapport aux normes

introduites dans la littérature. Le chapitre 5 présentera les premiers résultats quant au partitionnement des applications, tandis que le chapitre 6 exposera le modèle du Vocallo et les différentes stratégies d'ordonnancement à l'aide des derniers résultats obtenus. La conclusion présentera un sommaire des méthodes présentées ainsi que leurs limites pour finir avec quelques indications sur les travaux futurs, notamment la phase dynamique du projet OPÉRA.

## CHAPITRE 2

### MISE EN CONTEXTE

Un des fondements de base du projet OPERA repose sur l'utilisation du PBD, afin d'obtenir une nouvelle méthodologie permettant de déterminer les performances d'une application sur le processeur Vocallo. Le présent mémoire couvre plus particulièrement l'analyse statique d'algorithmes codés en C. Donc, de par l'emploi du PBD, il est requis de choisir de manière précise les modèles et méthodes qui serviront à représenter et à relier les deux niveaux impliqués, soient l'extraction des contraintes imposées par les applications et la modélisation de la plateforme matérielle. Suite à l'abstraction complète des deux niveaux précédemment identifiés, une phase d'ordonnancement au niveau des opérations élémentaires devra être effectuée, afin de pouvoir estimer les performances. La grande majorité des étapes nécessaires à l'accomplissement de cette phase du projet ont déjà fait séparément l'objet de recherches au cours des années passées. Le fruit de ces expérimentations nous propose ainsi une multitude de techniques dont nous pouvons nous inspirer et que nous pouvons modifier selon nos besoins plus spécifiques. Le présent chapitre, servant de mise en contexte des différents éléments retrouvés dans le cadre de ce projet, commencera donc par présenter un bref historique de différentes plateformes matérielles représentant des défis similaires à ceux proposés par la puce Vocallo. Comme le choix de la représentation intermédiaire d'une application d'un niveau suffisamment bas a finalement abouti sur le graphique de type CDFG, plusieurs variantes et améliorations possibles par rapport à CDFG classique seront par la suite exposées. La section subséquente apportera quelques explications de base et exemples de méthodologies de recherche dans le domaine du partitionnement d'algorithmes et d'ordonnancement d'applications dans de multiples contextes. Le chapitre 2 sera complété en dernier lieu par une description sommaire des différents algorithmes utilisés dans l'obtention des résultats présentés dans le cadre de ce mémoire.

## 2.1 Architecture MPSoC

Il est facilement possible d'affirmer que les systèmes sur puce à processeurs multiples (MPSoC; Multiprocessors System-On-Chip) constituent une classe à part entière de l'évolution des systèmes VLSI. Cette classe est justifiée par des besoins communs précis comme le respect de contraintes de temps réel, la faible consommation de puissance et la nécessité de traiter des applications toujours plus complexes qui s'inscrivent souvent dans un contexte multi-usagers. Ceci est en effet très facile à observer dans les principaux domaines d'utilisation des MPSoC, soient le réseautage, les communications, le traitement de signal et le multimédia. Depuis l'avènement du premier MPSoC, de nombreuses architectures aux particularités souvent bien différentes ont été développées afin de répondre à ces classes d'applications spécifiques. La puce Vocallo représente en 2008 une des évolutions possibles de ce type d'architecture dans le domaine du traitement de signal. La section 2.1 servira entre autres à dresser un bref historique de quelques architectures représentant les générations précédentes de MPSoC ainsi qu'à identifier les principaux défis communs à leur réalisation.

### 2.1.1 Historique des MPSoC

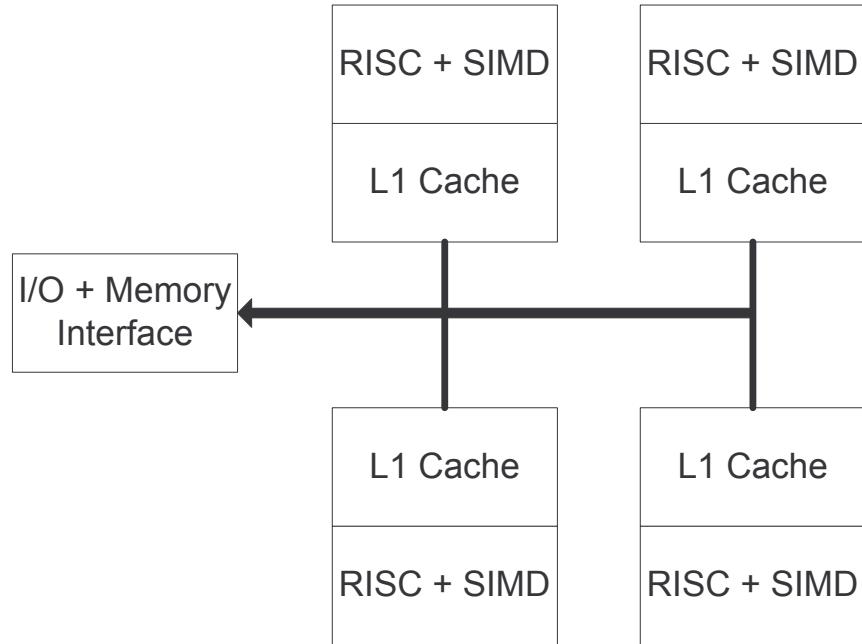

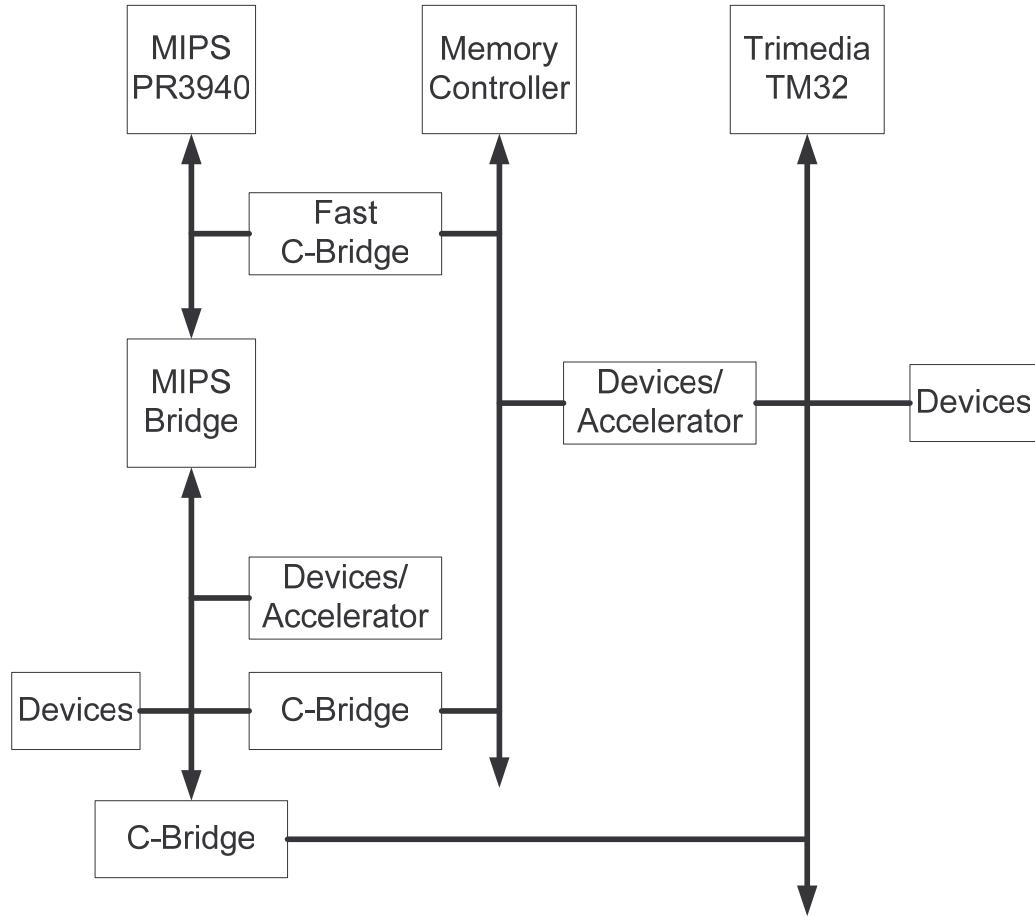

Parmi les premières architectures de MPSoC, on peut citer l'architecture Daytona développée par Lucent [1]. La topologie du Daytona est présentée à la figure 2-1. Le Daytona a été conçu pour être intégré dans une station de base sans fils. Chacun des cœurs effectue de manière identique le traitement de signaux provenant d'un certain nombre de canaux. Le Daytona est une architecture symétrique composé de 4 cœurs connectés par un bus rapide. Bien que technologiquement désuet, il est très facile d'en faire ressortir les grandes similarités avec la puce Vocallo, qui sera extensivement présentée dans le chapitre suivant. Suite à la sortie du Daytona, plusieurs autres MPSoC sont apparus sur le marché. Ils répondent à une plus grande variété d'applications et montrent des styles architecturaux plus divers et complexes.

Figure 2-1. MPSoC Daytona de Lucent

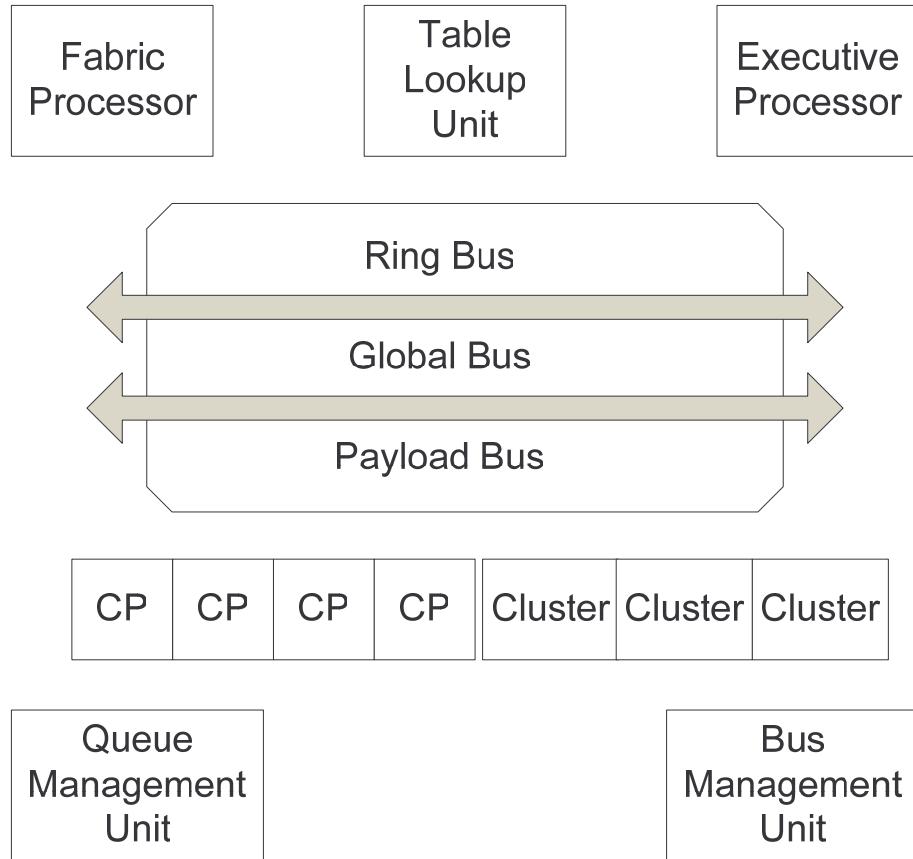

Le *C-5 Network processor* [7], représenté à la figure 2-2, a été quant à lui réalisé pour le traitement de paquets dans différents types de réseaux. Les paquets sont traités par les 4 processeurs de canal qui sont eux-mêmes constitués de 4 unités opératives chacun. L'implémentation de 3 bus différents permet entre autres le traitement de plusieurs types de trafics. Le C-5 doit par contre utiliser quelques processeurs extérieurs additionnels afin d'effectuer un travail plus spécialisé alors que le processeur exécutif (voir Fig. 2-2) possède un jeu d'instructions réduit de type RISC.

Figure 2-2. Réseau de processeurs C-5

Tel que mentionné précédemment, les MPSoC sont également en utilisation dans le domaine du multimédia. Le Philips Viper Nexperia [9], tel qu'illustré à la figure 2-3, se situe parmi les premiers exemples notables de processeur MPSoC en multimédia. Le Viper est principalement composé d'un MIPS servant de maître en étant responsable de prendre en charge le système d'exploitation et d'un processeur Trimedia VLIW répondant comme esclave aux commandes envoyées par le MIPS. Le système est régi par 3 bus, un pour chacun des processeurs tandis que le dernier est associé à l'interface d'accès à la mémoire externe. La partie de traitement multiprocesseur est par contre assurée par la présence de nombreux accélérateurs matériels attachés aux différents bus. Ces accélérateurs sont entre autres responsables d'effectuer les opérations plus complexes tels la conversion de couleurs, la mise à l'échelle, etc.

Figure 2-3. Le Viper Nexperia de Philips

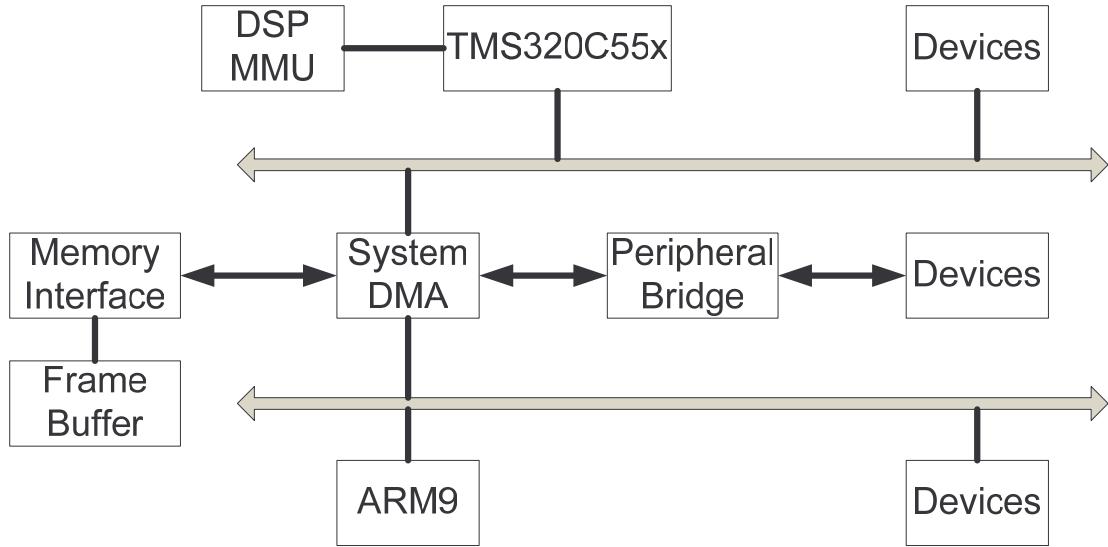

Les processeurs de téléphones cellulaires constituent une quatrième classe importante d'applications maintenant desservies principalement par les MPSoC. En effet, depuis déjà plusieurs années, ces appareils mobiles ont souvent la possibilité d'effectuer des opérations de communications ainsi que du multimédia. Plusieurs déclinaisons disponibles de l'architecture OMAP de Texas Instrument [31] permettent le support de toutes ces nouvelles fonctionnalités. La figure 2-4 présente la version 5912 du OMAP. Cette version est composée de deux processeurs. Le ARM9 sert de maître au TMS320C55x, DSP traditionnel, qui est quant à lui responsable des opérations de traitement de signal.

Figure 2-4. Le OMAP 5912 de Texas Instrument

### 2.1.2 Défis des MPSoC

Bien que tous les MPSoC présentés ci-dessus présentent des caractéristiques distinctes, ils se rejoignent quand même dans les défis reliés à leur implémentation et leur utilisation. Comme le design de MPSoC est de par sa nature basé sur les processeurs, donc sur une partie logicielle, une des difficultés majeures est de répartir adéquatement l'application sur la configuration optimale de l'implémentation matérielle. Depuis les débuts de l'informatique, les concepteurs de logiciels ont en effet appris à écrire du code séquentiel avec des machines de plus en plus rapides pour effectuer son exécution. On peut ainsi voir apparaître un contraste flagrant entre ce mode de pensée et le niveau de parallélisme offert par les nouveaux circuits de type MPSoC. On peut à présent distinguer deux classes majeures de système [22]. Le traitement symétrique (*Symmetric Multiprocessing* ou *SMP*) est caractérisé par un regroupement de processeurs ou de coeurs, partageant souvent le même accès à une mémoire globale et traitant des tâches similaires dans un contexte global commun. Le traitement asymétrique (*Asymmetric*

*multiprocessing* ou AMP) est défini par une structure de processeurs habituellement connectés de manière beaucoup moins serrée, qui peuvent souvent avoir des fonctionnalités totalement différentes et qui possèdent en général des ressources locales plus importantes comme des mémoires dédiées. Mais peu importe le modèle suivi, plusieurs tâches sont exécutées de manière concurrente. Elles doivent même souvent s'échanger des données ou avoir accès à des ressources partagées ou externes à la puce elle-même. Ceci a pour effet de pouvoir causer des combats de priorités, de l'interblocage (*deadlocking*), ou un manque de données à traiter (*data starving*) et peut aller jusqu'à engendrer la production de données incorrectes [22]. De cette instabilité imprédictible, due aux raisons précédemment énoncées, découle la grande difficulté, même malgré des années de recherche, de décomposer adéquatement une application codée de façon séquentielle en une série de tâches parallèles pouvant coopérer de manière ordonnée et prédictible. Dans le modèle symétrique, les tâches peuvent être assignées aux différents processeurs, puisqu'ils partagent généralement le même jeu d'instruction, selon les niveaux de trafics et la consommation de puissance désirée. Les communications inter-tâches sont souvent plus aisées à réaliser à partir d'une structure de mémoire commune mais un souci particulier doit être accordé afin de s'assurer de respecter toutes les dépendances présentes dans l'application et de bien équilibrer les charges que représentent ces tâches, afin d'obtenir un taux d'utilisation suffisant. Du côté asymétrique, la fonctionnalité et la granularité variable des unités de calcul requiert des mécanismes de communication plus complexes, mais qui doivent chercher à rester dans l'ensemble le plus efficace possible. Donc, peu importe le type d'architecture sélectionnée, un des défis majeurs reste le découpage de l'application. Ce processus demeure encore à ce jour une tâche ardue et hautement manuelle, habituellement basée sur l'expérience du concepteur.

Le débogage devient également problématique lors de l'utilisation des MPSoC. En effet, cette opération nécessite une connaissance approfondie du fonctionnement individuel de chaque partie tout en gardant une vision globale cohérente. Les outils permettant

l'instrumentation et l'analyse au niveau de l'interaction multiprocesseur restent encore à développer.

## 2.2 Graphe de flots de contrôle et de données

En suivant le PBD, une représentation à bas niveau devait être choisie afin de refléter et de pouvoir propager les caractéristiques des applications étudiées. Il existe plusieurs représentations possibles, mais comme tous les types de dépendance présents dans une application doivent absolument être pris en compte pour modéliser le plus justement possible les particularités d'algorithmes codés en C, notre choix s'est porté sur le graphe de flots de contrôle et de données (CDFG). Ce type de graphe est couramment utilisé comme représentation intermédiaire dans de nombreux compilateurs sur lesquels sont effectuées la plupart des optimisations et autres choix de design de manière à augmenter les performances globales de l'algorithme. Plus de détails en rapport à notre outil qui permet d'extraire des CDFG seront offerts dans le chapitre 4. Pour l'instant, la présente section se concentre sur une définition plus formelle de la composition de ce type de graphe, ainsi que quelques variantes notables tirées de recherches antérieures.

### 2.2.1 Principes de base

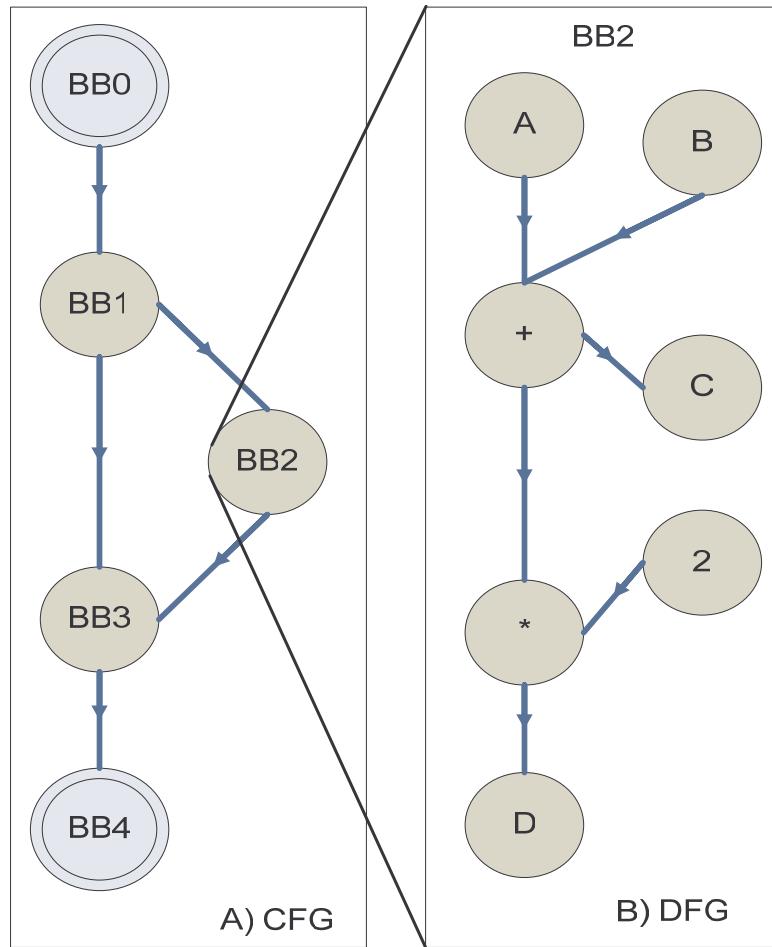

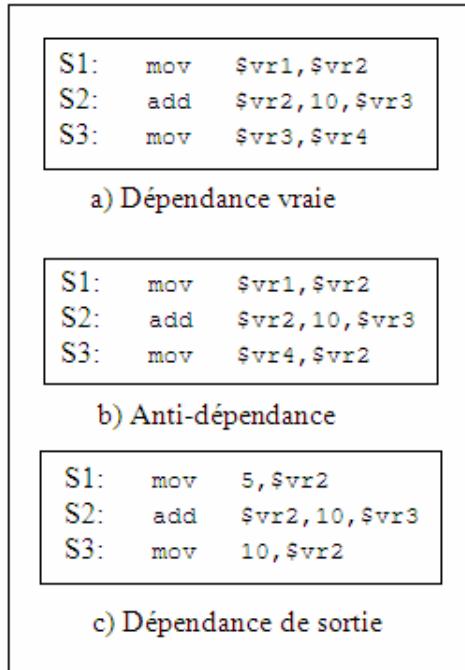

Un graphe de flots de contrôle et de données est traditionnellement composé de deux parties, soit le graphe de flots de contrôle (CFG) représentant les dépendances de contrôle et un ou plusieurs graphes de flots de données (DFG). Dans un CFG, un nœud, également appelé bloc de base, correspond à une séquence d'instructions consécutives dans laquelle le flot de contrôle est activé au début de celle-ci et inhibé à la fin de celle-ci, sans possibilité d'arrêt ou de branchement autre qu'à la fin de la séquence. Chacun de ces nœuds peut par la suite être représenté par un DFG où seront représentées les dépendances de données présentes entre chacune des opérations. Ce principe est présenté à la figure 2-5 [16]. Le graphe de gauche correspond aux dépendances de contrôle présentes entre les différents blocs de base. Celui de droite montre le DFG correspondant

au bloc de base BB2. La réunion de ces deux graphes constitue la base de la création d'un CDFG.

Figure 2-5. Exemple de CFG et de DFG

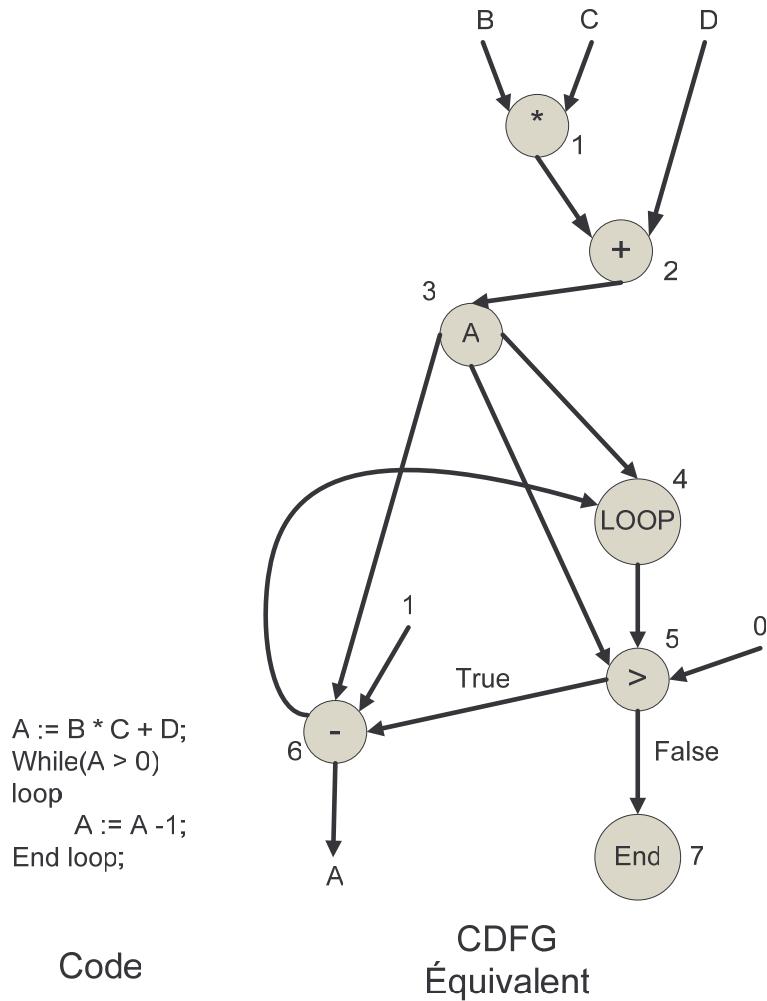

Donc un CDFG est un graphe orienté et acyclique, où les nœuds peuvent être de deux types : nœud opératif, représentant une opération arithmétique ou logique, ou nœud de contrôle servant à rendre compte des structures de contrôle telles les conditions IF/CASE ou les boucles. Tous les liens entre les nœuds sont orientés et impliquent une dépendance de données quand ils rejoignent deux nœuds opératifs et un changement de structure de contrôle lorsqu'ils servent à relier deux nœuds de contrôle. Ces liens peuvent également être traversés de manière conditionnelle en fonction de certaines conditions, comme les

différents cas d'une structure IF ou des bornes d'itérations de certaines boucles. Un exemple complet d'un CDFG représentant un court bout de code est présenté à la figure 2-6. On peut noter que les nœuds 1, 2, 5 et 6 sont des nœuds opératifs, tandis que les nœuds restants correspondent à des nœuds de contrôle. Le lien entre les nœuds 5 et 6 illustre le principe de lien conditionnel, car il n'est emprunté que lorsque la condition  $A > 0$  s'avère être exacte. Ceci résume la base nécessaire à la bonne compréhension de ce type de graphe. Par contre, de nombreux autres types de graphes dérivés du CDFG ont été développés au cours des années, afin de répondre de manière plus adéquate à certains problèmes spécifiques. La section suivante présentera quelques-uns de ces dérivés.

Figure 2-6. Exemple de code et de son CDFG équivalent

### 2.2.2 Variantes du CDFG

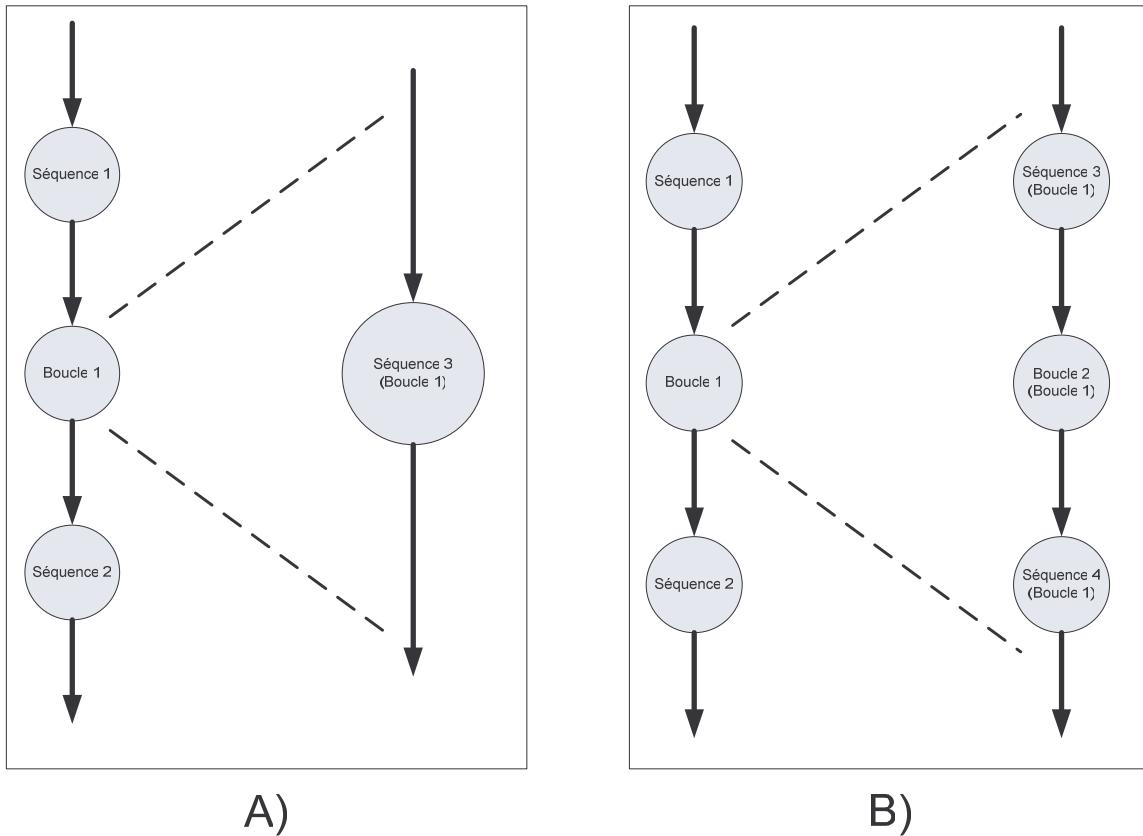

Depuis le début de l'utilisation des CDFG, ceux-ci ont majoritairement été employés comme représentation intermédiaire par certains compilateurs dans un but d'optimisation. Par contre, de nombreuses recherches académiques se servent maintenant des CDFG à d'autres fins en modifiant souvent l'aspect du graphe. Ce genre de graphe est particulièrement utile dans la synthèse de circuits à haut niveau. R. Namballa, dans le cadre d'une thèse intitulée *CHESS: A tool for CDFG extraction and high-level synthesis of VLSI* [24], se sert d'un CDFG afin de représenter une application codée en langage de description de matériel, soit le VHDL. L'outil développé procède selon les trois étapes suivantes : l'extraction d'un CDFG à partir de modules VHDL, l'ordonnancement et l'allocation du graphe obtenu et finalement l'association du résultat à un ensemble de composants physiques de manière à obtenir de manière automatique une architecture aux performances optimales. Ce principe est également repris par un bon nombre de groupes de recherche dont Smit et al. [29] qui ont la particularité de se baser sur des algorithmes en C. Un autre domaine d'application où le CDFG est bien visible est la synthèse mixte entre le matériel et le logiciel (*Hardware/Software Co-Design*). En effet, on peut voir dans [6] et [19] deux méthodologies différentes afin de partitionner une application afin de l'implanter en matériel ou en logiciel selon des critères bien précis pour chacun des auteurs. Dans le premier cas, la performance en termes de temps d'exécution est primordiale, tandis que la réduction des coûts de communication entre les parties matérielles et logicielles dicte les choix de design pour le second. Knudsen et al. [19] vont même jusqu'à développer leur propre variante du CDFG traditionnel afin de simplifier leur méthode. Leur graphique final découle de plusieurs transformations effectuées avant le partitionnement dans le but d'obtenir une structure permettant une meilleure estimation des communications entre certains nœuds implémentés sur des processeurs différents. Le but des transformations, qui sont surtout opérées au niveau des structures de contrôle, est d'atteindre une granularité assez fine pour une estimation correcte des communications, tout en restant suffisamment grossière afin de ne pas faire augmenter inutilement le temps requis pour le partitionnement et l'analyse du graphe. Les

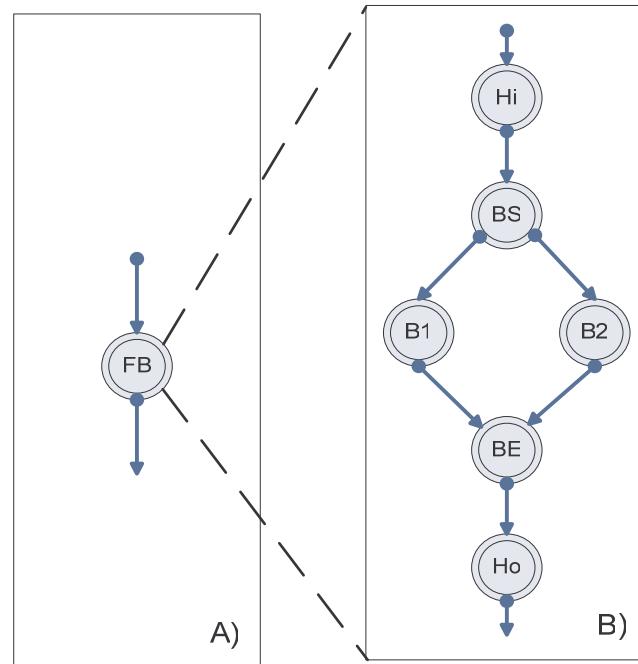

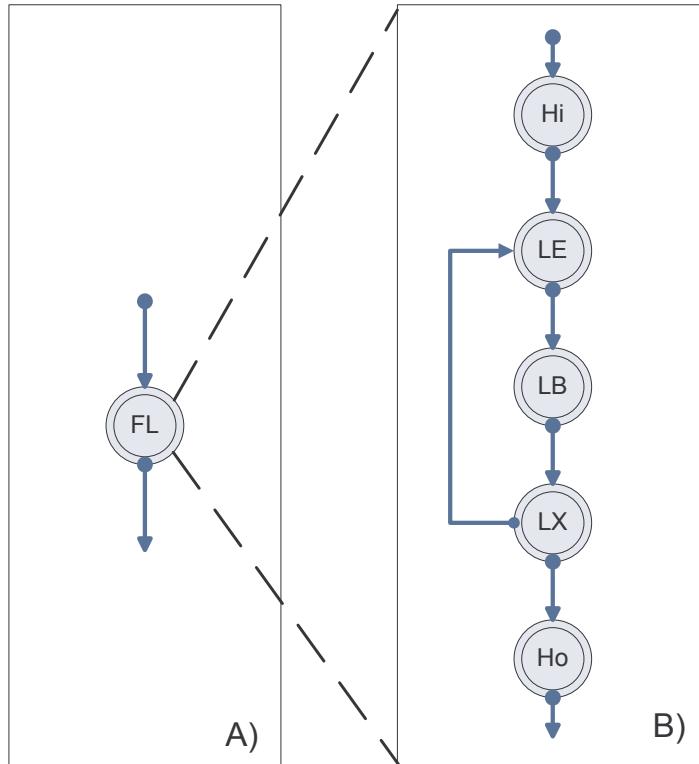

figures 2-7 [19] et 2-8 [19] montrent deux raffinements possibles pour les structures de branchements et de boucles. La liberté est par la suite donnée au concepteur de pouvoir intégrer le contenu de chacun des nouveaux nœuds ainsi créés ou de les laisser tels quels. Ces nouveaux nœuds correspondent à des étapes plus spécifiques des structures de contrôle présentées. En prenant l'exemple du branchement étendu à la figure 2-7, les nœuds *Hi* et *Ho* correspondent respectivement à l'entrée et la sortie du nœud hiérarchique, *BS* (Branch Start) contient un traitement commun préalable aux deux branches *B1* et *B2* de la structure conditionnelle tandis que *BE* (Branch End) implique une série d'opérations devant être effectuée après l'exécution de l'une ou l'autre des deux branches. Tous ces nouveaux nœuds servent à représenter de manière plus explicite la structure de branchement complète contenue dans le nœud *FB* (Full Branch). Le même principe est utilisé pour la représentation de la structure de boucle dans la figure 2-8.

Figure 2-7. Transformations de branchement : A) Branchement complet B) Branchement étendu

**Figure 2-8. Transformations de boucle : A) Boucle complète B) Boucle étendue**

Toujours dans le cadre du partitionnement logiciel/matériel, Wu et al. [33] introduisent le concept de hiérarchisation du CDFG en permettant à un nœud de contenir un sous graphe du même type et ce de manière récursive. Cette hiérarchisation peut être appliquée à toutes les structures de contrôle présentes dans une application conventionnelle. Leur article présente également la définition d'un nouveau type de nœud, soit le nœud de transport. Celui-ci est responsable de représenter les ressources de communications du système à implémenter. Le développement et l'inclusion de ce type de nœud dans le CDFG leur procure une flexibilité accrue dans la caractérisation de différents modes de transmission de données.

On peut brièvement conclure que le CDFG est en utilisation dans plusieurs domaines connexes au monde des compilateurs et que ceux-ci poussent souvent les concepteurs à redéfinir les bases mêmes du graphe classique afin d'arriver à un résultat final plus adapté à leurs champs d'intérêt.

## 2.3 Partitionnement et ordonnancement

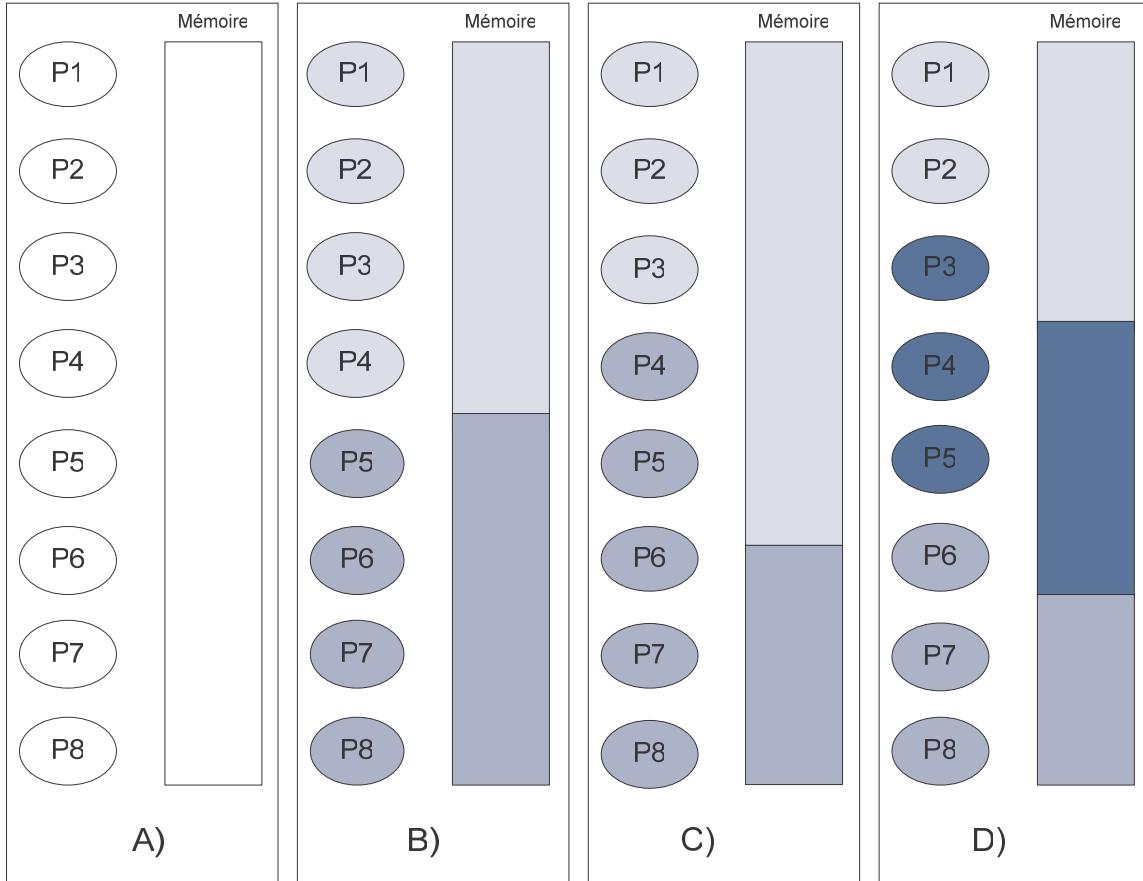

Un autre aspect contenu dans ce mémoire et ayant déjà été couvert extensivement par la littérature académique concerne le partitionnement d’application et son ordonnancement. La présente section portera sur l’explication sommaire de quelques principes et exemples, établis dans la littérature, portant sur l’application de ces deux disciplines dans le domaine des MPSoC. Comme mentionné précédemment dans la section sur les particularités des MPSoC, la difficulté dans le partitionnement d’une application découle du parallélisme offert par ces circuits émergents face à des algorithmes codés de manière séquentielle. Pour solutionner ce problème, Xue et al. [34] proposent une méthode d’ordonnancement dynamique basée sur un partitionnement effectué au préalable et qui prend en compte les différentes ressources, surtout en termes de consommation de mémoire et d’effort de calcul, requises par l’application. La première phase de leur technique consiste à prévoir les caractéristiques des différentes applications à traiter. La deuxième étape est effectuée par un outil de partitionnement dynamique assignant un nombre de processeurs, ainsi qu’une quantité de mémoire aux différentes tâches concurrentes. La figure 2-9 présente quelques stratégies de partitionnement sur un MPSoC contenant 8 processeurs distincts. Le premier cas correspond à toutes les unités de traitement disponible (P1 à P8) ainsi que la quantité de mémoire commune disponible. L’assignation d’une tâche à un regroupement de processeurs ainsi qu’à une quantité de mémoire est représentée par les différents sous-groupes délimités dans la figure 2-9 par différents codes de couleur dans les trois cas subséquents.

**Figure 2-9. Exemples de partitionnement : A) Architecture MPSoC à 8 processeurs B-C-D) Stratégies de partitionnement**

La méthode présentée permet entre autres de pouvoir évaluer adéquatement différentes stratégies de partitionnement. Les résultats obtenus tendent à démontrer encore une fois l'importance d'une bonne stratégie de partitionnement en termes de processeurs et de mémoire. Il existe également de nombreuses études se penchant sur l'optimisation de la mémoire dans un contexte multiprocesseurs [18, 21, 23]. Par contre, les techniques développées dans chacun de ces articles ne prennent pas en compte les besoins relatifs à l'effort de calcul, contrairement à notre approche et à celle, très similaire, proposée par Xue et al. [34]. Par exemple, Li et al. [21] essaient de démontrer qu'en augmentant la localité des données requises par une application dans un processeur donné, les

performances globales d'un MPSoC, de type matrice de processeurs, s'en trouvent améliorées. Leur méthode se base sur les concepts suivants. En augmentant la réutilisation des variables et données locales à un processeur, il est possible de diminuer la fréquence et la quantité de données devant être transférées à l'aide de communications entre les processeurs. Également, afin d'amortir les coûts de synchronisation entre les processeurs, il devrait y avoir une quantité suffisante de calculs à effectuer entre deux étapes de synchronisation. Finalement, une bonne répartition de l'effort de calcul sur chaque processeur tend généralement à augmenter le taux d'utilisation des processeurs de manière à passer le moins de temps possible en mode inactif. Toutes ces considérations ont été prises en compte lors de la transformation de leurs algorithmes vers une forme plus adaptée aux MPSoC. La transformation principale de leur méthode est le déroulement de boucles afin d'obtenir une application encore plus parallèle, tout en essayant de regrouper l'utilisation des données similaires sur un même processeur.

On retrouve également dans la littérature certaines méthodologies très similaires à celle du PBD utilisées dans le même but que le projet décrit dans ce mémoire, soit l'estimation de performances d'algorithmes sur une implémentation matérielle sélectionnée. En effet, ces méthodes sont principalement caractérisées par une représentation de l'application sous une forme donnée et une caractérisation de la partie matérielle. En effet, Russel et al. [26], décrivent une méthode d'analyse statique pour explorer l'implémentation de différentes architectures. Chacune des composantes de l'architecture est d'abord définie par rapport aux délais associés à chaque étape de traitement (calcul, transfert de données, ...). Par la suite, les différentes parties de l'application sont réparties parmi les composantes matérielles, afin d'en tirer les performances globales. Cette technique, contrairement à celle proposé dans ce mémoire, ne tient compte que des dépendances de contrôle et n'est pas effectuée de manière totalement automatique. Hwang et al. [17] ont quant à eux avancé une méthode dynamique d'estimation des performances pour des MPSoC hétérogènes. Comme dans le présent cas, l'application est représentée sous la forme d'un graphe de type CDFG. Par contre, seul le délai engendré par l'exécution des

blocs de base est comptabilisé pour être transmis à la modélisation de la plateforme matérielle formalisée à l'aide de SystemC. Bien que leur analyse soit dynamique, les résultats obtenus sont du même ordre de grandeur que ceux produits et présentés dans le cadre de ce mémoire, mais sans tenir compte des besoins en mémoire de l'algorithme et de la capacité de la plateforme. Finalement, dans le but de pouvoir sélectionner le processeur approprié ou d'estimer les changements à effectuer avec l'utilisation de processeur configurable, Gupta et al. [12] propose une méthode basée également sur l'utilisation de SUIF pour extraire les caractéristiques de l'application. Une série de paramètres similaires à ceux extraits par l'outil produit dans le cadre du projet OPERA viennent caractériser la représentation de l'application. Ces paramètres ne viennent cependant pas montrer le détail des nœuds représentant les instructions individuelles. En se basant sur ces derniers paramètres, un ordonnanceur calcule le nombre de cycles requis pour l'exécution de l'algorithme. Bien que la technique employée par les précédents auteurs soit proche de celle mise de l'avant dans ce mémoire, on peut voir que l'erreur relative des estimations est beaucoup plus importante que celle présentée dans la suite du mémoire. Il est à noter que la visualisation de la représentation intermédiaire de l'application étudiée et que le calcul de la consommation de mémoire, ainsi que le partitionnement automatique selon la quantité de mémoire disponible, sont des fonctionnalités qui ne sont présentes que dans la méthode proposée par ce mémoire.

Toutes ces techniques en viennent à démontrer la grande complexité de la programmation des MPSoC, puisque l'on peut tenter de résoudre ce problème en considérant ou non un certain nombre de facteurs différents (effort de calcul, quantité de mémoire requise, localité des données, parallélisme, ...), et en obtenant des améliorations très variables entre chacune des méthodes proposées.

## 2.4 Applications

Cette dernière section du chapitre de mise en contexte passe brièvement en revue les différentes applications qui ont été utilisées comme banc d'essai dans notre projet. Seul

un aperçu des algorithmes sera présenté dans ce mémoire. En effet le mémoire de Fredéric Plourde [25], un autre étudiant du projet Opéra, détaille explicitement le fonctionnement de nombreuses applications dans le domaine des télécommunications, dont toutes celles utilisées dans la réalisation de ce mémoire. Les bancs d'essai employés dans le développement et le test de l'outil final, ainsi que pour la production des résultats présentés au chapitre 6 ont été produits par différents membres du projet OPERA dans le cadre de leurs travaux de recherches respectifs ou de demandes particulières provenant d'Octasic. Ces algorithmes sont les suivants :

- Maximum Vectoriel

- Addition Vectorielle

- FIR Complexé

- Filtre égaliseur adaptatif LMS complexe

- Décodeur de Viterbi

- Décodeur Turbo

On peut classer les algorithmes étudiés en trois groupes sur la base de leur fonctionnalité et de leur niveau de complexité. Le premier est constitué d'opérations vectorielles, soit le maximum et l'addition. La sélection de ces opérations est due à leur grande utilisation dans le secteur des télécommunications. Elles sont utilisées pour implémenter de nombreuses fonctions plus complexes. Elles ont une relativement faible complexité algorithmique. En effet, ce faible niveau de complexité permet une première vérification rapide du fonctionnement de l'outil global, car le nombre restreint d'opérations tend à produire des CDFG aux tailles réduites, donc plus faciles à analyser de manière compréhensible par un individu. La vérification des estimations des ressources mémoires est aussi plus aisée sur du code aux demandes plus minimes en mémoires. Le deuxième groupe formé des deux types de filtres permet d'atteindre des niveaux de complexité intermédiaire, tout en considérant une fonctionnalité complète. Les filtres demeurent encore une des applications les plus couramment implémentés sur des DSP, ce qui augmente la pertinence de leur utilisation pour fins de validation. Brièvement, ces deux

configurations de filtres peuvent être employées pour produire un vaste éventail de filtres plus particuliers comme filtre passe-bas, égaliseur ou bien de mise en forme [25]. Les deux dernières applications sont deux différents types de décodeur en usage dans les classes d'applications ciblées par le projet Opéra. Ces différentes formes de codage servent à lutter contre les perturbations apportées par le support d'une transmission en remplaçant le message par un autre moins vulnérable à ces mêmes perturbations. L'emploi de celles-ci fournit comme avantage de procurer un haut niveau de complexité tout en fournissant des estimations d'algorithmes qui seront éventuellement implémentés sur la plateforme matérielle. Il est également à noter que plusieurs applications synthétiques ont été développées lors de la phase de développement de l'outil. Celles-ci avaient pour but de tester plus adéquatement certaines hypothèses ainsi que de pouvoir vérifier les limites de l'outil. Ces applications seront introduites dans le reste de ce mémoire lorsque les résultats relatifs à leur emploi seront présentés.

## CHAPITRE 3

### L'ARCHITECTURE DU VOCALLO

Le processeur Vocallo, qui est l'objet d'étude central du projet Opéra dans le cadre duquel ce projet de maîtrise a été réalisé, s'inscrit dans les courants observables dans le domaine des DSP au cours des dernières années, autant dans les sphères académique qu'industrielle. La constante réduction de la taille des transistors permet une augmentation de la complexité, pouvant se traduire en gain de performance, lorsque celle-ci est utilisée de manière efficace. Plusieurs techniques de pointe sont en usage présentement dans le domaine des DSP et ont entre autres deux objectifs principaux, soient la réduction de la puissance consommée et l'accélération de traitement des données. Grâce à l'augmentation du nombre de transistors par circuit, il est maintenant possible de concevoir des MPSoC qui sont composés de plusieurs unités de traitement permettant d'augmenter le parallélisme inhérent d'une plateforme donnée. Ce parallélisme permet d'augmenter le nombre d'opérations possibles par cycle d'horloge donc d'effectuer un nombre de calculs effectifs plus grand pour une même période de temps. Quant à la réduction de la consommation de puissance, une méthode en émergence est l'utilisation de circuits asynchrones. Cette dernière est particulièrement utile lorsqu'appliquée aux unités de calculs, responsables pour la grande majorité de la consommation de puissance. En effet, ce type de circuit, étant donné son absence de signal d'horloge, peut ne consommer virtuellement aucune énergie en mode d'attente, quand les circuits sont réalisés avec une technologie CMOS statique de longueur de grille suffisamment élevée. Les circuits de cette classe sont généralement capables de revenir en mode actif de manière quasi instantanée. Lorsque cette dernière technique est combinée avec l'utilisation de design de type MPSoC, comme dans le cas de la présente architecture, la possibilité de pouvoir désactiver un ou plusieurs cœurs selon le niveau d'activité rend cette dernière option très avantageuse. Cette variabilité du niveau d'activité est explicable en invoquant que l'effort de calcul des algorithmes de

télécommunications est fonction des conditions du canal de transmission, ainsi que le nombre d'usagers à traiter dans un contexte de temps réel. Ce chapitre présente les caractéristiques principales du processeur Vocallo.

### 3.1 Spécification générale du Vocallo

La puce Vocallo est un circuit multi-cœurs développé par Octasic pour le traitement vidéo, de la voix et de données sur IP. Comme une partie importante de ce projet consiste à évaluer les performances d'applications choisies dans le domaine des télécommunications, ce chapitre sert à dresser un portrait complet de l'architecture du Vocallo, afin de permettre une bonne compréhension de la modélisation du processeur dans les chapitres subséquents. De par la structure du processeur, nous utiliserons une approche descendante pour sa description en commençant par les caractéristiques globales de la plateforme, pour finir avec les détails fins de l'implémentation de chacun des cœurs.

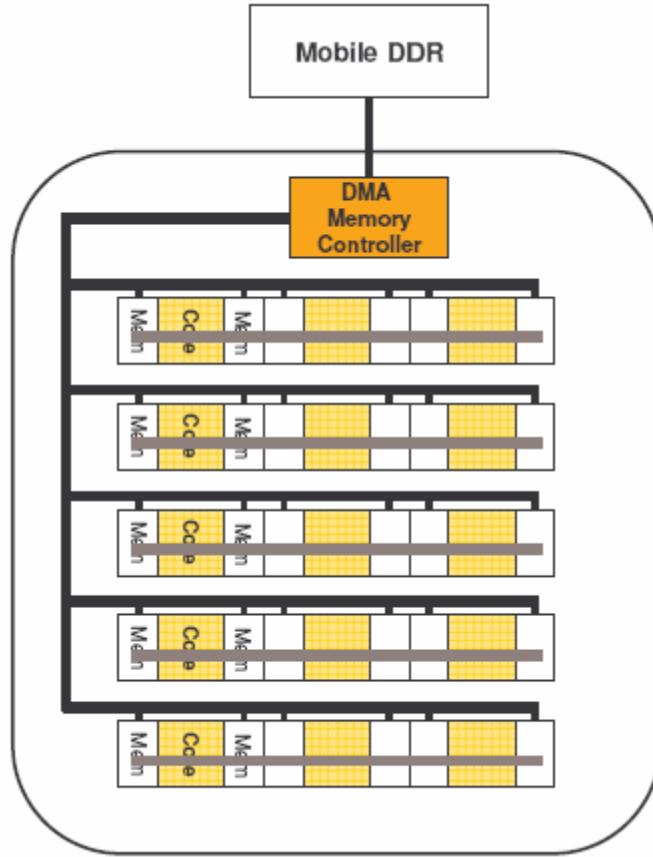

### 3.2 Architecture Inter-Noyaux

Au plus haut niveau d'abstraction, on peut définir le Vocallo comme un tableau homogène de processeurs reliés entre eux par un bus de communication. La figure 3-1 montre l'architecture à haut-niveau du Vocallo, ainsi que des autres composants externes nécessaires à son bon fonctionnement. Une courte section sera consacrée à chacun des éléments identifiés dans la figure 3-1, afin de bien saisir les différentes interactions et rôle de chacun des modules.

Figure 3-1. Schéma bloc de l'architecture complète du Vocallo [25]

### 3.2.1 Matrice de processeurs

La puce Vocallo est composée d'un ensemble de 15 noyaux identiques. Ces noyaux sont organisés selon un tableau composé de 5 rangées de 3 noyaux. Chaque noyau, contenant ses propres unités de calcul, effectue de manière autonome le traitement de données qui lui a été assigné. La description complète d'un noyau se retrouvera dans une des sections subséquentes.

Grâce à un ajout de circuiterie et au positionnement des noyaux, il est possible de désactiver les unités de traitement d'un noyau central et de répartir sa mémoire locale de manière égale entre ses voisins immédiats. Seuls les noyaux sur la même rangée peuvent être en droit d'utiliser cette mémoire supplémentaire. Cette dernière fonctionnalité peut être utile dans le cas où un partitionnement logiciel implique un besoin en mémoire

supérieur à celui disponible de manière normale dans un noyau. Selon Octasic, aucune dégradation de performance ne résulte de ce type de transfert pour le noyau bénéficiant du surplus de mémoire.

### 3.2.2 Communication inter-noyau

La figure 3-1 montre que chaque noyau est connecté au seul bus responsable de tous les transferts de données entre les noyaux et l'extérieur de la puce, ainsi que des communications entre deux ou plusieurs noyaux. Les données sont transmises sur un bus d'une largeur de 32 bits à une fréquence de 1.5 GHz, qui est lui-même supporté par quelques signaux de contrôle. Ces signaux de contrôle permettent à chaque noyau de signaler, au contrôleur DMA (Direct Memory Access), le besoin de recevoir ou de transmettre des données. Ces transferts d'informations sont amorcés sur une base premier arrivé premier servi. Le contrôleur DMA est en charge de recevoir toutes les requêtes de transmission et de contrôler le bus selon les demandes à traiter. Un système de priorités est également disponible pour aider dans l'ordonnancement des communications, mais aucune documentation décrivant son utilisation précise n'est encore disponible à ce jour. Tout transfert interne doit passer par le contrôleur de mémoire qui est aussi responsable des communications vers la mémoire externe et des entrées et sorties de la puce. Il est à noter qu'un seul transfert d'information peut avoir lieu à un moment donné, puisque nous sommes en présence d'un seul bus, mais le Vocallo permet par contre de pouvoir envoyer les mêmes données à tous les noyaux ou à n'importe quel regroupement de ceux-ci de manière simultanée. Cette dernière forme de communication est dite de type universelle (broadcast). Il faut également mentionner que lorsqu'un noyau est impliqué dans une communication, peu importe qu'il soit en transmission ou en réception, ce noyau cesse complètement ses activités. Donc une communication universelle à tous les noyaux aura pour effet d'arrêter complètement l'effort de calcul de toute la puce durant toute la durée du transfert.

### 3.2.3 Circuits périphériques