**Titre:** Validation matérielle d'une architecture générique de réseaux avioniques basée sur une gestion modulaire de la redondance

Title: Validation matérielle d'une architecture générique de réseaux avioniques basée sur une gestion modulaire de la redondance

**Auteur:** José-Philippe Tremblay

Author:

**Date:** 2016

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Tremblay, J.-P. (2016). Validation matérielle d'une architecture générique de réseaux avioniques basée sur une gestion modulaire de la redondance [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/2143/>

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/2143/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Claude Thibeault

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

VALIDATION MATÉRIELLE D'UNE ARCHITECTURE GÉNÉRIQUE DE RÉSEAUX

AVIONIQUES BASÉE SUR UNE GESTION MODULAIRE DE LA REDONDANCE

JOSÉ-PHILIPPE TREMBLAY

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR

(GÉNIE ÉLECTRIQUE)

AVRIL 2016

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée :

VALIDATION MATÉRIELLE D'UNE ARCHITECTURE GÉNÉRIQUE DE RÉSEAUX

AVIONIQUES BASÉE SUR UNE GESTION MODULAIRE DE LA REDONDANCE

présentée par : TREMBLAY José-Philippe

en vue de l'obtention du diplôme de : Philosophiae Doctor

a été dûment accepté par le jury d'examen constitué de :

M. SAWAN Mohamad, Ph. D., président

M. SAVARIA Yvon, Ph. D., membre et directeur de recherche

M. THIBEAULT Claude, Ph. D., membre et codirecteur de recherche

M. BELTRAME Giovanni, Ph. D., membre

M. AUDET Daniel, Ph. D., membre externe

## DÉDICACE

*À Claudia, Chloé et Camille avec tout mon amour ...*

## **REMERCIEMENTS**

Je te tiens d'abord à remercier M. Savaria et M. Thibeault, respectivement directeur et codirecteur de doctorat, pour leur disponibilité, leur support et divers conseils menant à terme avec succès mes travaux de recherche. Je tiens également à souligner le soutien financier de Bombardier, principal partenaire du projet AVIO402. Je remercie également mes coéquipiers du GRM et partenaires du projet AVIO402 pour leur support et encadrement lors de la réalisation du projet. Je souligne plus particulièrement l'appui de Safwen Bouanen et de Davide Trentin pour leur précieuse collaboration. Je termine par remercier ma famille et mes amis qui m'ont soutenu tout au long de mes études.

## RÉSUMÉ

Les systèmes avioniques ne cessent d"évoluer depuis l"apparition des technologies numériques au tournant des années 60. Après le passage par plusieurs paradigmes de développement, ces systèmes suivent maintenant l"approche « Integrated Modular Avionics » (IMA) depuis le début des années 2000. Contrairement aux méthodes antérieures, cette approche est basée sur une conception modulaire, un partage de ressources génériques entre plusieurs systèmes et l"utilisation plus poussée de bus multiplexés. La plupart des concepts utilisés par l"architecture IMA, bien que déjà connus dans le domaine de l"informatique distribuée, constituent un changement marqué par rapport aux modèles antérieurs dans le monde avionique. Ceux-ci viennent s"ajouter aux contraintes importantes de l'avionique classique telles que le déterminisme, le temps réel, la certification et les cibles élevées de fiabilité. L"adoption de l"approche IMA a déclenché une révision de plusieurs aspects de la conception, de la certification et de l"implémentation d'un système IMA afin d'en tirer profit. Cette révision, ralentie par les contraintes avioniques, est toujours en cours, et offre encore l"opportunité de développement de nouveaux outils, méthodes et modèles à tous les niveaux du processus d"implémentation d'un système IMA. Dans un contexte de proposition et de validation d'une nouvelle architecture IMA pour un réseau générique de capteurs à bord d'un avion, nous avons identifié quelques aspects des différentes approches traditionnelles pour la réalisation de ce type d"architecture pouvant être améliorés. Afin de remédier à certaines des différentes lacunes identifiées, nous avons proposé une approche de validation basée sur une plateforme matérielle reconfigurable ainsi qu'une nouvelle approche de gestion de la redondance pour l"atteinte des cibles de fiabilité. Contrairement aux outils statiques plus limités satisfaisant les besoins pour la conception d'une architecture fédérée, notre approche de validation est spécifiquement développée de manière à faciliter la conception d'une architecture IMA.

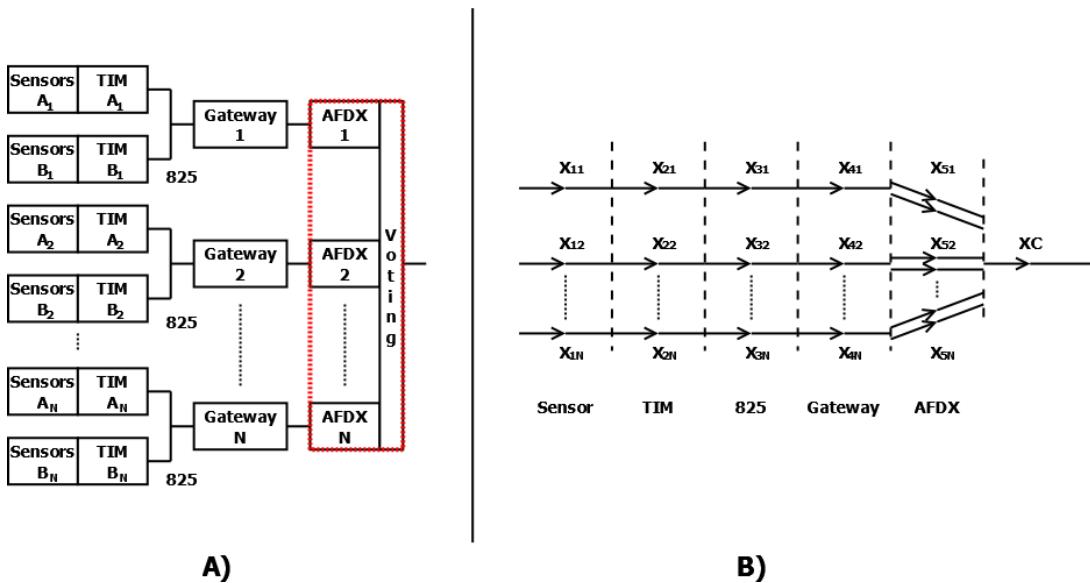

Dans le cadre de cette thèse, trois axes principaux de contributions originales se sont dégagés des travaux exécutés suivant les différents objectifs de recherche énoncés précédemment. Le premier axe se situe au niveau de la proposition d'une architecture hiérarchique de réseau de capteurs s'appuyant sur le modèle de base de la norme IEEE 1451. Cette norme facilite l'intégration de capteurs et actuateurs intelligents à tout système de commande par des interfaces normalisées et génériques. Afin d"être applicable dans le domaine avionique pour le traitement d'applications

critiques, nous avons introduit dans notre architecture de réseau de capteurs génériques notre propre gestion de la redondance permettant entre autres d'atteindre des niveaux plus élevés de fiabilité ainsi que de modifier le niveau de fiabilité selon les exigences. De manière à respecter les différentes contraintes liées au développement de systèmes avioniques, l'architecture proposée permet la personnalisation de la bande passante offerte, du niveau de fiabilité recherché, de la quantité de ressources consommées et du type de capteurs ou actuateurs utilisés. La modélisation de plusieurs configurations est présentée dans la thèse afin de pouvoir comparer les différentes architectures et en faire ressortir les avantages et inconvénients. Au niveau de la fiabilité, nos analyses montrent la polyvalence de notre architecture en permettant la modulation de la fiabilité totale du réseau grâce à la variation intégrée du nombre de composants et de bus, contrairement aux approches traditionnelles qui ne possèdent aucun mécanisme intrinsèque pour augmenter la fiabilité du réseau rendant leur application inefficace dans un contexte d'applications critiques. Au niveau de la consommation de ressources, notre architecture permet des gains raisonnables face aux architectures classiques.

Le second axe porte sur la proposition d'une plateforme matérielle de design et de validation de systèmes avioniques spécifiquement adaptée aux besoins de l'approche IMA. La constante migration vers les prochaines générations de systèmes avioniques requiert toujours l'adoption de nouvelles technologies de communication de données, comme ce fut le cas pour les protocoles ARINC 825 et ARINC 664 introduits il y a déjà quelques années. Les caractéristiques et performances peuvent varier énormément d'une norme à l'autre. L'intégration de ces protocoles peut donc demander un effort considérable afin de respecter les différentes contraintes du domaine avionique. Bien que des composants commerciaux soient disponibles, l'utilisation d'une implémentation matérielle personnalisée et générique peut s'avérer extrêmement utile dans la validation d'architectures ou d'analyses théoriques et l'identification des cas problématiques. À travers le cas de figure étudié, nous montrons les différents avantages de l'utilisation d'une plateforme matérielle, bien que certaines analyses du processus de design et de validation requièrent toujours l'emploi de modélisation logicielle ou mathématique. Le caractère réutilisable de la plateforme FPGA ainsi que l'architecture générique sélectionnée permet ultimement de réduire significativement l'effort de design et de validation de ce type de système. La possibilité offerte de validation en temps réel peut également s'avérer particulièrement utile dans le domaine. Dans le cas où une approche propriétaire est privilégiée comme dans le cadre de notre

projet, une compréhension plus complète des différentes normes peut permettre de détecter des modes d'erreur difficile à cerner à l'aide de modèles mathématiques ou de tester de nouvelles fonctionnalités tel le regroupement de trames dans un contrôleur ARINC 825. L'exemple final du système de monitorage montre par contre que l'approche matérielle peut être moins adaptée pour faire face à certaines problématiques ou analyses requises motivant toujours l'emploi de la modélisation.

Au niveau de l'atteinte des cibles de fiabilité, les systèmes avioniques ont toujours majoritairement recours à la redondance pour en assurer le respect. Le troisième et dernier axe de contribution de cette thèse repose sur la présentation de notre approche de gestion de la redondance spécifique au domaine avionique permettant entre autres la sélection du niveau approprié de redondance de manière spécifique pour chacune des couches traversées. Notre approche est illustrée à travers le design et la validation d'un réseau de capteurs basé sur un réseau AFDX principal, supporté par plusieurs bus secondaires suivant la norme ARINC 825. Afin de capturer fidèlement les contraintes du domaine avionique, les points communs de défaillance ou couplages ont été inclus dans la modélisation de notre architecture et dans celle des approches de gestion de redondance classiques. Une première analyse vient démontrer un gain de fiabilité substantiel face à l'approche de type « composant » ainsi qu'une fiabilité similaire à l'approche de type « système ». Une deuxième phase vient par contre démontrer la meilleure efficacité au niveau des ressources face à l'approche « système ». À l'aide de diverses analyses, la sensibilité du réseau face à un composant ou aux points de couplage vient faciliter la phase de design en permettant la sélection d'une configuration plus efficace par rapport aux contraintes spécifiées. L'architecture proposée prend le meilleur de chacune des méthodes classiques et élimine le plus de points communs de défaillance possible.

## ABSTRACT

Since the emergence of digital technologies in the 1960s, avionics has evolved very rapidly. To reflect the technological evolution, several design approaches have been followed up to the Integrated Modular Avionics (IMA) introduced in the late 1990s. Unlike previous approaches, IMA is based on modular conception, generic resources sharing between several previously independent systems and further use of multiplexed busses. While the major aspects used in the IMA architecture is already known in other fields such as distributed computing, they represent a fundamental change in regards to traditional approaches for avionics. These new concepts are added to the existing constraints of classic avionic such as determinism, real time application, certification and stringent reliability targets. Several aspects of the design, certification and implementation of an IMA system must be revised in order to maximize its benefit. The adoption of the IMA thus requires the development of new approaches, models and tools at each level of the implementation process of an IMA system. In a context of proposition and validation of a new IMA architecture for a generic sensor network, we have identified several key aspects of the traditional approaches that could be enhanced for a better compatibility with the IMA approach. In order to overcome these identified deficiencies, we have proposed a global validation approach based on a reconfigurable material platform combined with a new approach to redundancy management required to reach the reliability targets. Unlike the static tools devised for the previous federated design approach, our approach was specifically devised to ease the design process under the IMA architecture.

Within the context of this thesis, three primary areas of original contributions have been identified from our work done within the objectives of project AVIO 402. The first contribution resides in the proposition of a hierarchical architecture for a sensor network base on the reference model of the IEEE 1451 standard. This standard facilitates the integration and control of any type of intelligent transducer to any control system through normalized generic interfaces. In order to be compliant with the avionics constraints for critical applications, we have introduced within our architecture our own redundancy management scheme allowing the required levels of reliability as well as the possibility to tailor the system's reliability depending on the requirements. To reach these different requirements, the architecture can be personalized in terms of available bandwidth, reliability, quantity of consumed resources and of the type of transducers used. The

modeling of several configurations is presented in this thesis in order to compare the different architectures and highlight the benefits and limitations of each. Our reliability analyses show the versatility of our architecture by allowing the reliability modulation of the network by varying the number of components and/or busses unlike previous implementation of the IEEE 1451 standard. The IEEE 1451 standard would be applicable to the avionics field without this last feature. In terms of resource consumption, our architecture offers significant gains compared to traditional approaches.

The second contribution lies in the proposition of a hardware platform specifically devised for the design and validation of avionics system following the IMA approach. The steady evolution towards next generation avionics systems requires the adoption of new communications technologies, such as the ARINC 825 and AFDX protocols introduced several years ago and currently widely used. The characteristics and performances of these emerging technologies can greatly vary from one another and their integration can necessitate a considerable effort while complying with avionics constraints. Even if commercials components are available, a custom material generic implementation can be extremely useful for the validation of architectures or theoretical analyses and to identify problematic cases. Through a case study, we show the different advantages and limitations of the use of our hardware platform. As a first benefit, the reusable nature of the platform in combination with the selected generic architecture can greatly reduce the design and validation effort for this type of system. The direct inclusion of the certification process can also provide the same benefit by using final implementation for testing and validation. The possibility of real time validation is also extremely useful in the avionics domain. In the case where a proprietary approach is preferred, a better comprehension of the different standards can help detect error source difficult to identify with mathematic model or to test new features such as our testing of frame packing strategies directly included within our ARINC 825 controller. Our final example based on our innovative monitoring system shows that the hardware platform is not always the best suited for certain types of analysis. We then conclude that even though software and mathematical analysis are still needed, a mixed approach would still bring a lot of benefits to the design and validation of avionics systems.

In order to reach the high reliability targets, avionics systems have mostly relied on redundancy. The third and last contribution presented in this thesis resides in the presentation of our redundancy management approach. Globally, our approach allows the individual customization

of each stage of the network and is demonstrated through the validation of a sensor network devised within the AVIO 402 project. In order to correctly capture the constraints of the avionics field, single points of failures or coupling have been introduced into the model of our architecture as well as traditional approach to redundancy management. A first analysis shows a substantial gain in reliability compared to the typical component approach and a similar level of reliability than the system redundancy management scheme. In a second step, a better efficiency of consumed resources is measured in respect to the system architecture. The analyses also enable the selection of a more efficient configuration by underlining the sensitivity of the network to those single points of failures. The proposed redundancy management scheme takes the best advantages from each classical approach and eliminates as many single points of failures as possible.

## TABLE DES MATIÈRES

|                                                   |      |

|---------------------------------------------------|------|

| DÉDICACE .....                                    | iii  |

| REMERCIEMENTS .....                               | iv   |

| RÉSUMÉ .....                                      | v    |

| ABSTRACT .....                                    | viii |

| TABLE DES MATIÈRES .....                          | xi   |

| LISTE DES TABLEAUX .....                          | xiv  |

| LISTE DES FIGURES .....                           | xv   |

| LISTE DES SIGLES ET ABRÉVIATIONS .....            | xvii |

| CHAPITRE 1 INTRODUCTION .....                     | 1    |

| 1.1 Mise en contexte .....                        | 1    |

| 1.2 Problématique .....                           | 5    |

| 1.3 Cadre de projet .....                         | 6    |

| 1.4 Objectifs de recherche et contributions ..... | 9    |

| 1.5 Organisation de la thèse .....                | 11   |

| CHAPITRE 2 RÉSEAUX AVIONIQUES DE CAPTEURS .....   | 13   |

| 2.1 IEEE 1451 .....                               | 14   |

| 2.1.1 Principes de base .....                     | 14   |

| 2.1.2 Applications .....                          | 16   |

| 2.2 Design et validation de systèmes IMA .....    | 20   |

| 2.2.1 Approche classique .....                    | 20   |

| 2.2.2 Approches originales .....                  | 23   |

| 2.2.3 Monitorage .....                            | 27   |

| 2.3 ARINC 825 .....                               | 29   |

|                                                                                                           |                                                      |    |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------|----|

| 2.3.1                                                                                                     | Principes de base .....                              | 29 |

| 2.3.2                                                                                                     | Usages .....                                         | 30 |

| 2.3.3                                                                                                     | Regroupement de trames .....                         | 31 |

| 2.4                                                                                                       | Gestion de la redondance .....                       | 34 |

| 2.4.1                                                                                                     | Approche classique .....                             | 34 |

| 2.4.2                                                                                                     | Approche originale .....                             | 36 |

| 2.4.3                                                                                                     | Approches alternatives .....                         | 36 |

| CHAPITRE 3 ARTICLE 1 : A SYSTEM ARCHITECTURE FOR SMART SENSORS INTEGRATION IN AVIONICS APPLICATIONS ..... |                                                      | 39 |

| 3.1                                                                                                       | Introduction .....                                   | 40 |

| 3.2                                                                                                       | Related Works .....                                  | 41 |

| 3.3                                                                                                       | System Architecture .....                            | 44 |

| 3.4                                                                                                       | Reliability Evaluation .....                         | 46 |

| 3.5                                                                                                       | Results .....                                        | 47 |

| 3.6                                                                                                       | Conclusion .....                                     | 51 |

| CHAPITRE 4 ARTICLE 2 : HIERARCHICAL REDUNDANCY MANAGEMENT FOR AVIONIC NETWORKS .....                      |                                                      | 52 |

| 4.1                                                                                                       | Abstract .....                                       | 52 |

| 4.2                                                                                                       | Introduction .....                                   | 52 |

| 4.3                                                                                                       | Avionics Networks Redundancy .....                   | 54 |

| 4.3.1                                                                                                     | Redundancy Management .....                          | 54 |

| 4.3.2                                                                                                     | Federated and Integrated Modular Architectures ..... | 57 |

| 4.4                                                                                                       | Redundancy Management .....                          | 59 |

| 4.5                                                                                                       | Hierarchical Architecture Analysis .....             | 67 |

| 4.5.1                                                                                                     | Reliability estimations .....                        | 67 |

|                                                                                  |            |

|----------------------------------------------------------------------------------|------------|

| 4.5.2 Complexity analysis .....                                                  | 70         |

| 4.5.3 Coupling's impact on reliability.....                                      | 72         |

| 4.6 Conclusion.....                                                              | 77         |

| <b>CHAPITRE 5 DISCUSSION GÉNÉRALE .....</b>                                      | <b>79</b>  |

| 5.1 Architecture générique de réseau avionique .....                             | 79         |

| 5.1.1 Sommaire .....                                                             | 79         |

| 5.1.2 Discussion .....                                                           | 80         |

| 5.2 Validation de l'approche mixte pour l'intégration de réseaux avioniques..... | 81         |

| 5.2.1 Sommaire .....                                                             | 81         |

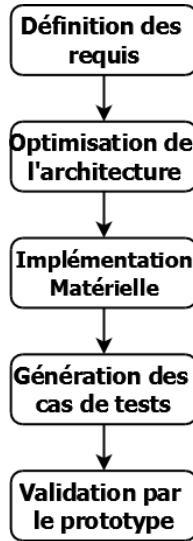

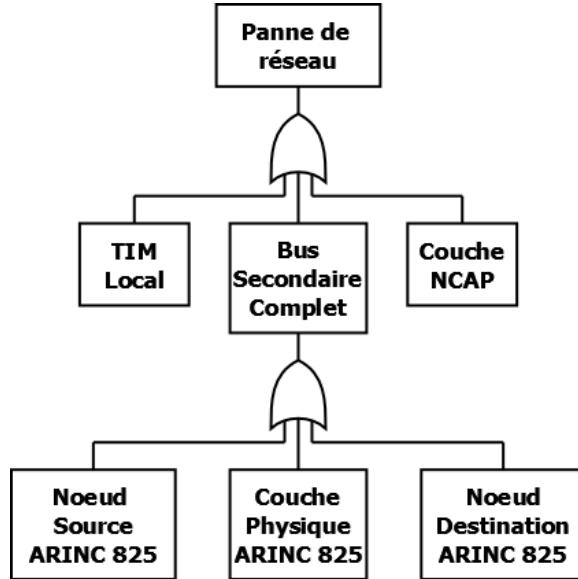

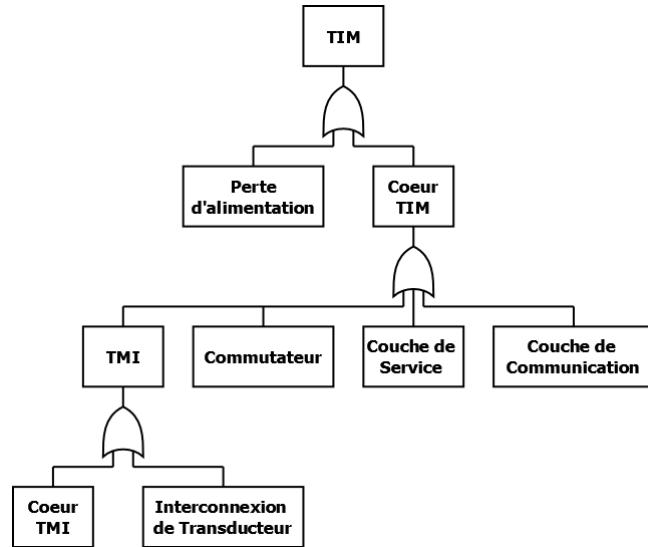

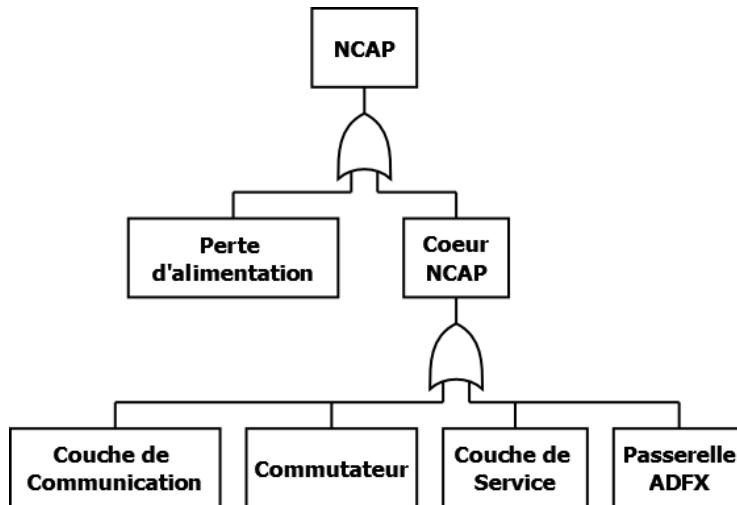

| 5.2.2 Méthodologie .....                                                         | 82         |

| 5.2.3 Implémentation.....                                                        | 86         |

| 5.2.4 Discussion .....                                                           | 95         |

| 5.3 Gestion modulaire de la redondance .....                                     | 100        |

| 5.3.1 Sommaire .....                                                             | 100        |

| 5.3.2 Discussion .....                                                           | 101        |

| <b>CHAPITRE 6 CONCLUSION .....</b>                                               | <b>103</b> |

| 6.1 Synthèse .....                                                               | 103        |

| 6.2 Limitations et travaux futurs .....                                          | 105        |

| <b>RÉFÉRENCES .....</b>                                                          | <b>107</b> |

## LISTE DES TABLEAUX

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| Tableau 2.1: Domaines d'application de la norme IEEE 1451 .....                     | 19 |

| Tableau 2.2: Niveau de redondance et cibles de fiabilité [1] .....                  | 34 |

| Tableau 3.1: Modules complexity and failure rate.....                               | 48 |

| Tableau 4.1: Architecture's failure rates .....                                     | 69 |

| Tableau 4.2: Number of components for the traditional architectures.....            | 70 |

| Tableau 4.3: Number of components for the hierarchical architecture.....            | 71 |

| Tableau 5.1: Requis .....                                                           | 85 |

| Tableau 5.2: Notation adoptée pour décrire les composants.....                      | 88 |

| Tableau 5.3: Complexité des composants .....                                        | 91 |

| Tableau 5.4: Latence moyenne de trames .....                                        | 94 |

| Tableau 5.5: Validation de réseau .....                                             | 95 |

| Tableau 5.6: Trafic sous la stratégie de regroupement de trames <i>M-to-1</i> ..... | 99 |

## LISTE DES FIGURES

|                                                                                                 |    |

|-------------------------------------------------------------------------------------------------|----|

| Figure 1-1: Évolution des architectures avioniques [1] .....                                    | 1  |

| Figure 1-2: Architectures distribuées A) analogique B) numérique .....                          | 2  |

| Figure 1-3: Exemple d'architecture fédérée .....                                                | 3  |

| Figure 1-4: Exemple d'architecture IMA [1] .....                                                | 4  |

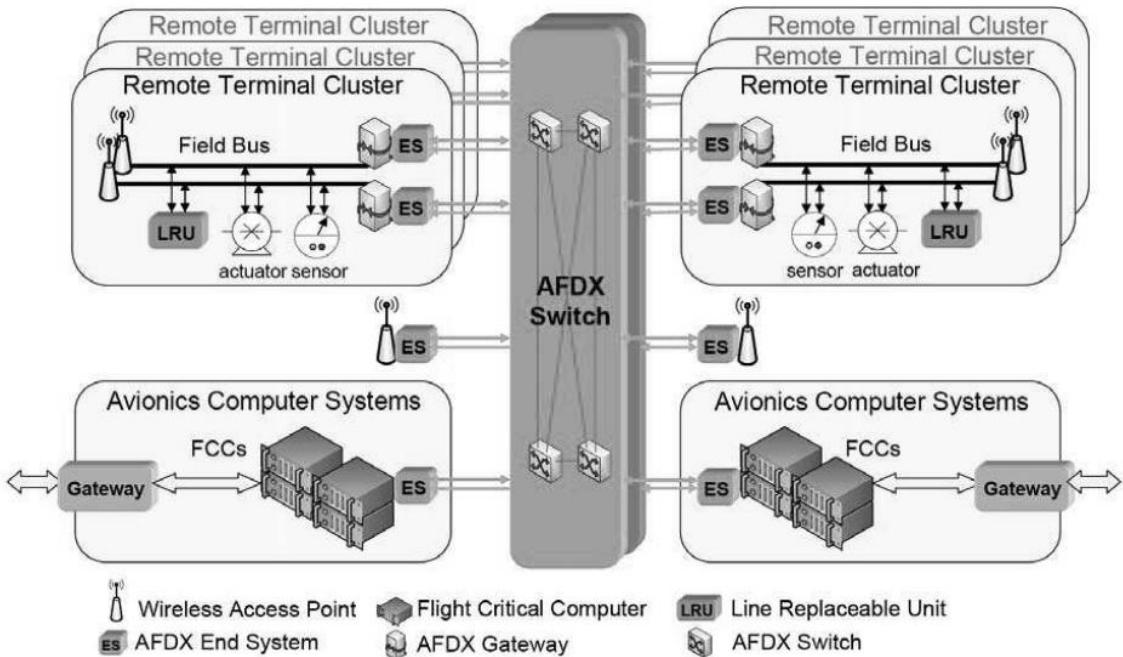

| Figure 1-5: Architecture proposée [6].....                                                      | 8  |

| Figure 2-1: Modèle de référence du IEEE 1451 [7].....                                           | 15 |

| Figure 2-2: Architecture réseau [12] .....                                                      | 17 |

| Figure 2-3: Architecture réseau [14] .....                                                      | 18 |

| Figure 2-4: Relation entre les principales normes avioniques [1].....                           | 22 |

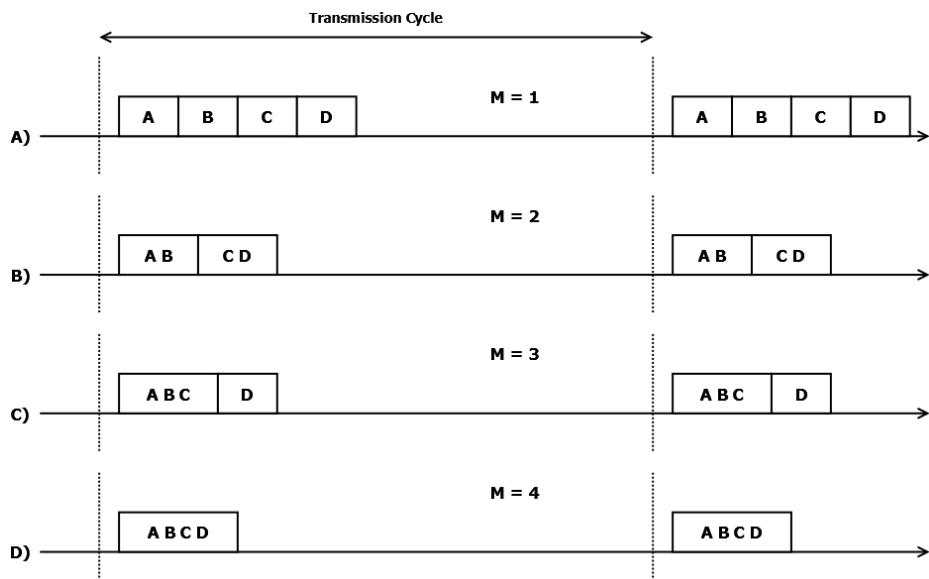

| Figure 2-5: Stratégie <i>M-to-1</i> .....                                                       | 33 |

| Figure 2-6: Architecture Com-Mon .....                                                          | 35 |

| Figure 3-1: IEEE 1451 Reference Model, adapted from [7].....                                    | 42 |

| Figure 3-2: IEEE 1451 Distributed Architecture .....                                            | 43 |

| Figure 3-3: Custom global architecture.....                                                     | 45 |

| Figure 3-4: Custom TIM's architecture .....                                                     | 45 |

| Figure 3-5: Custom NCAP's architecture .....                                                    | 46 |

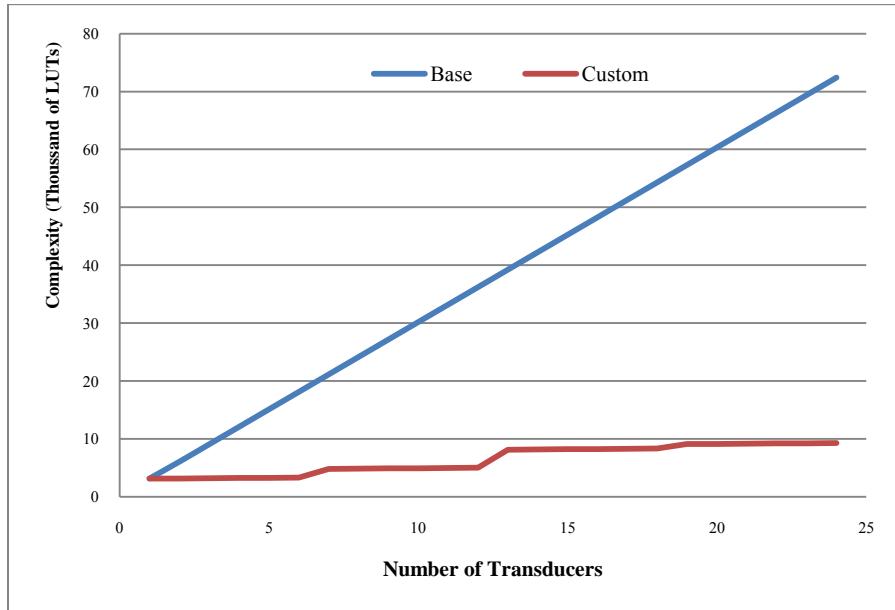

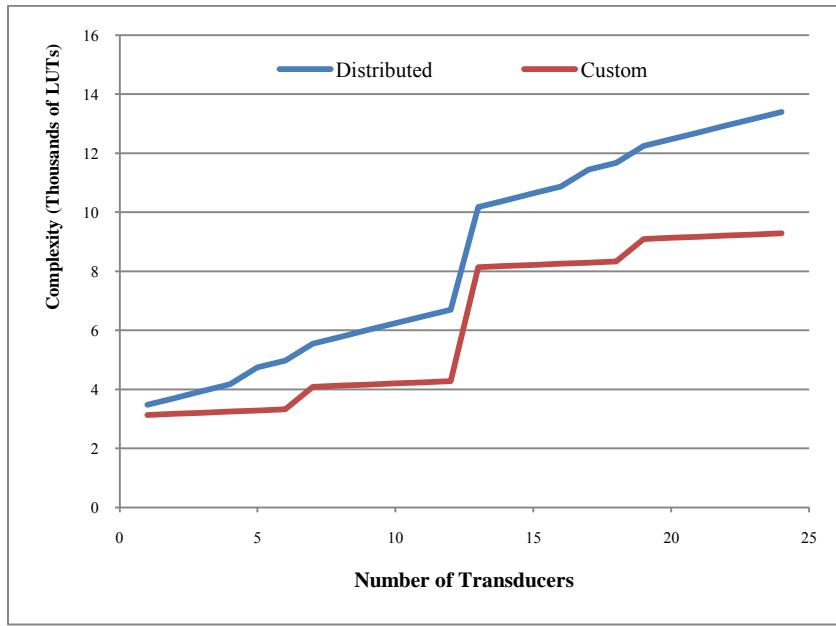

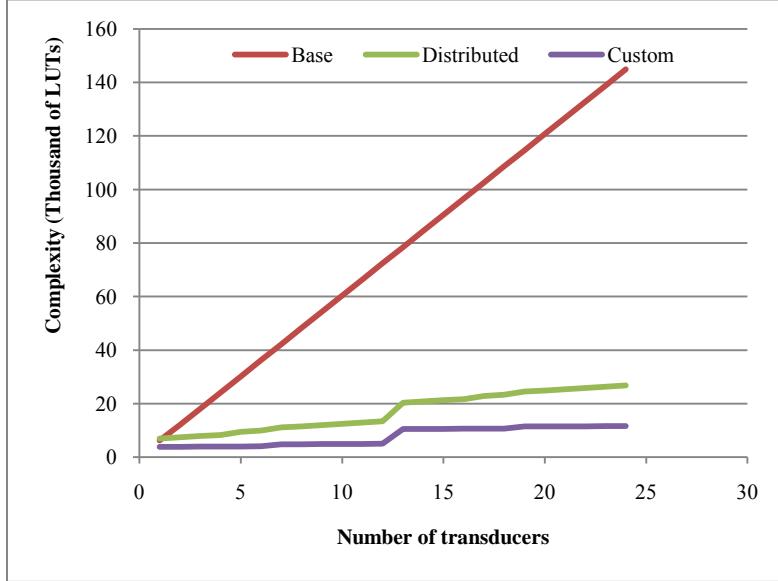

| Figure 3-6: Network Complexity Vs. Number of Transducers.....                                   | 49 |

| Figure 3-7: Network Complexity Vs. Number of Transducers.....                                   | 50 |

| Figure 3-8: Network Complexity Vs Number of Transducers.....                                    | 51 |

| Figure 4-1: Federated Architecture .....                                                        | 57 |

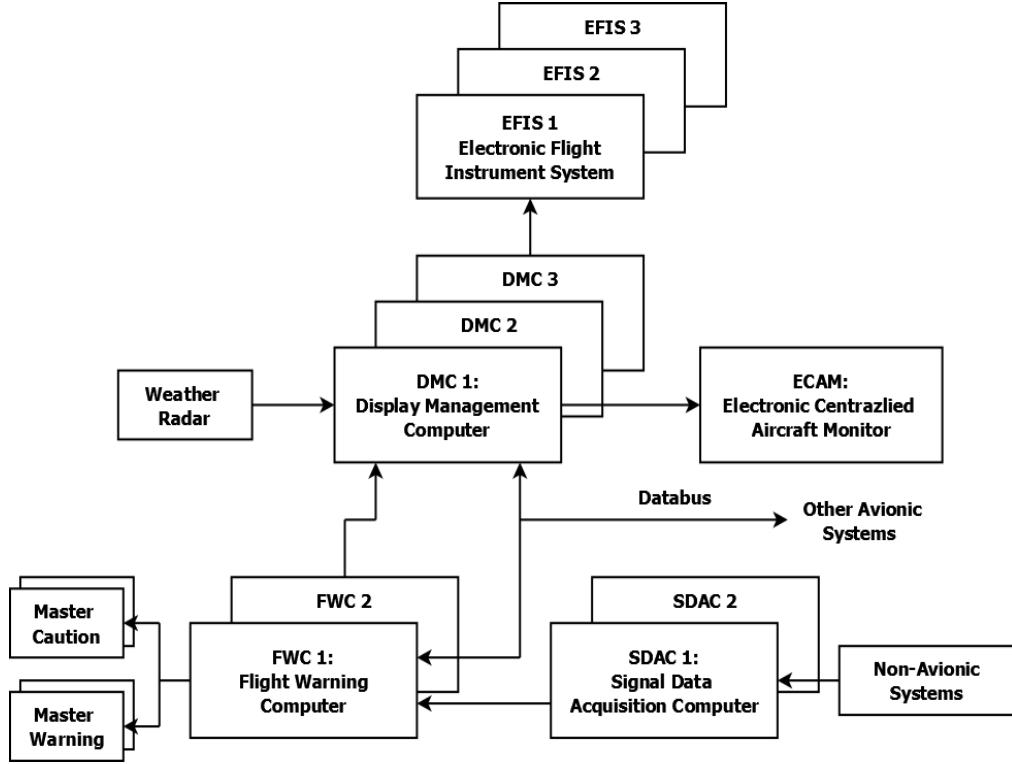

| Figure 4-2: Airbus A320 flight deck display system [1].....                                     | 58 |

| Figure 4-3: IMA Architecture .....                                                              | 59 |

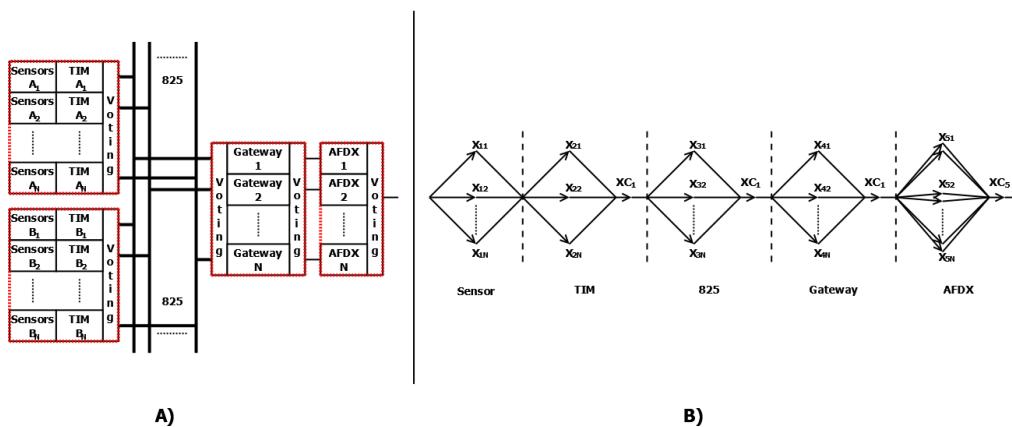

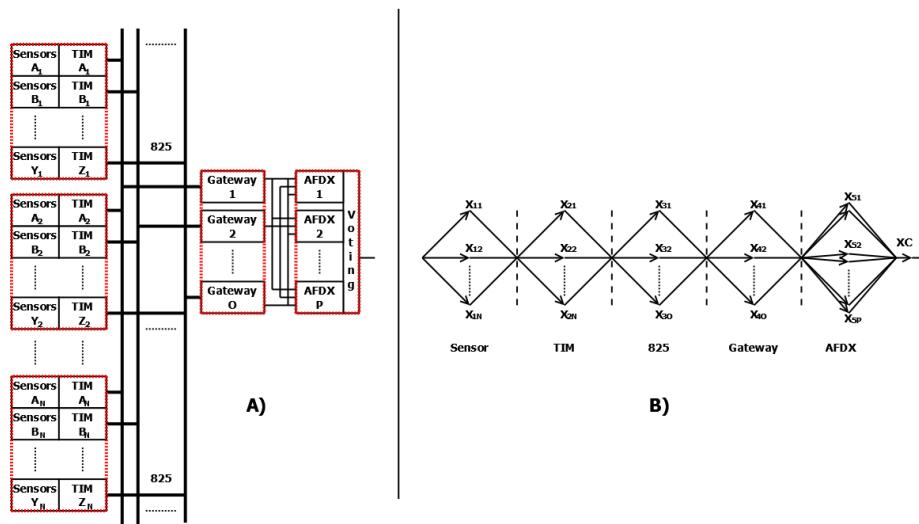

| Figure 4-4: A) Functional architecture, non-redundant version B) Associated reliability model.. | 60 |

|                                                                                                                |    |

|----------------------------------------------------------------------------------------------------------------|----|

| Figure 4-5: A) System redundant architecture, B) Associated reliability model .....                            | 62 |

| Figure 4-6: A) Component redundant architecture B) Associated reliability model .....                          | 63 |

| Figure 4-7: A) Hierarchically redundant architecture, B) Associated reliability model .....                    | 64 |

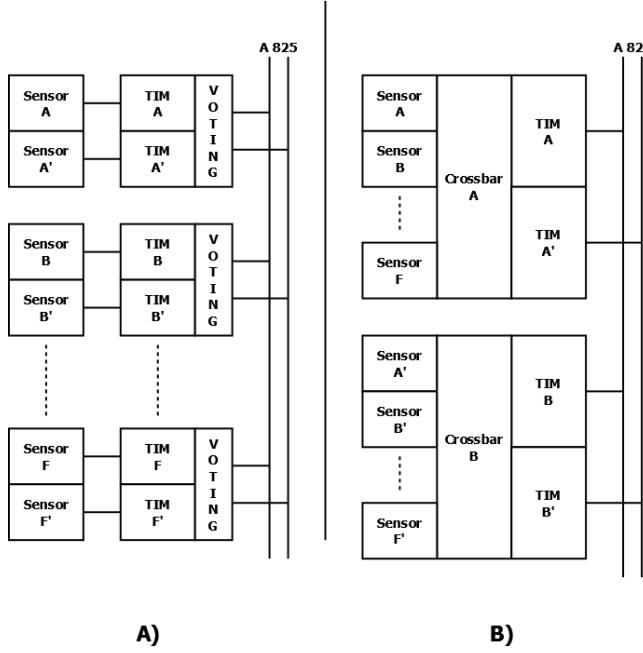

| Figure 4-8: TIM Structure A) Component Architecture B) Hierarchical Architecture .....                         | 65 |

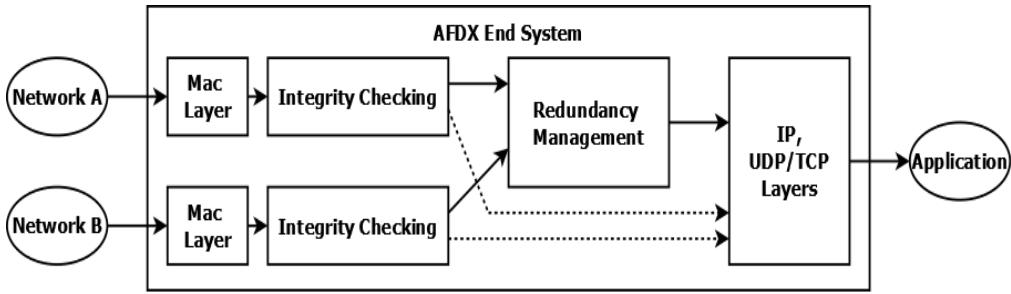

| Figure 4-9: AFDX End System Specification.....                                                                 | 66 |

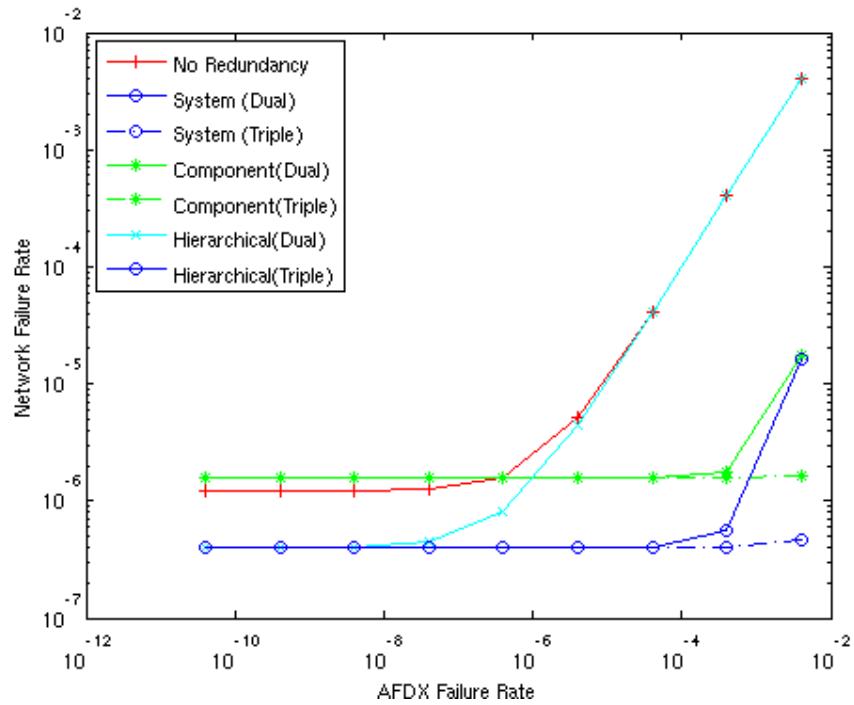

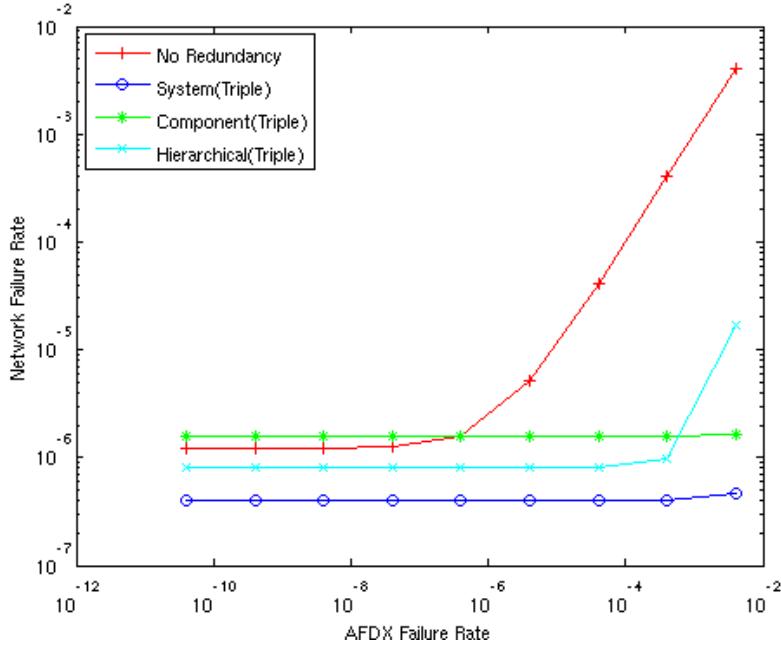

| Figure 4-10: Architecture“s unreliability as a function of the AFDX“s unreliability for error detection .....  | 73 |

| Figure 4-11: Architecture“s unreliability as a function of the AFDX“s unreliability for data correction.....   | 74 |

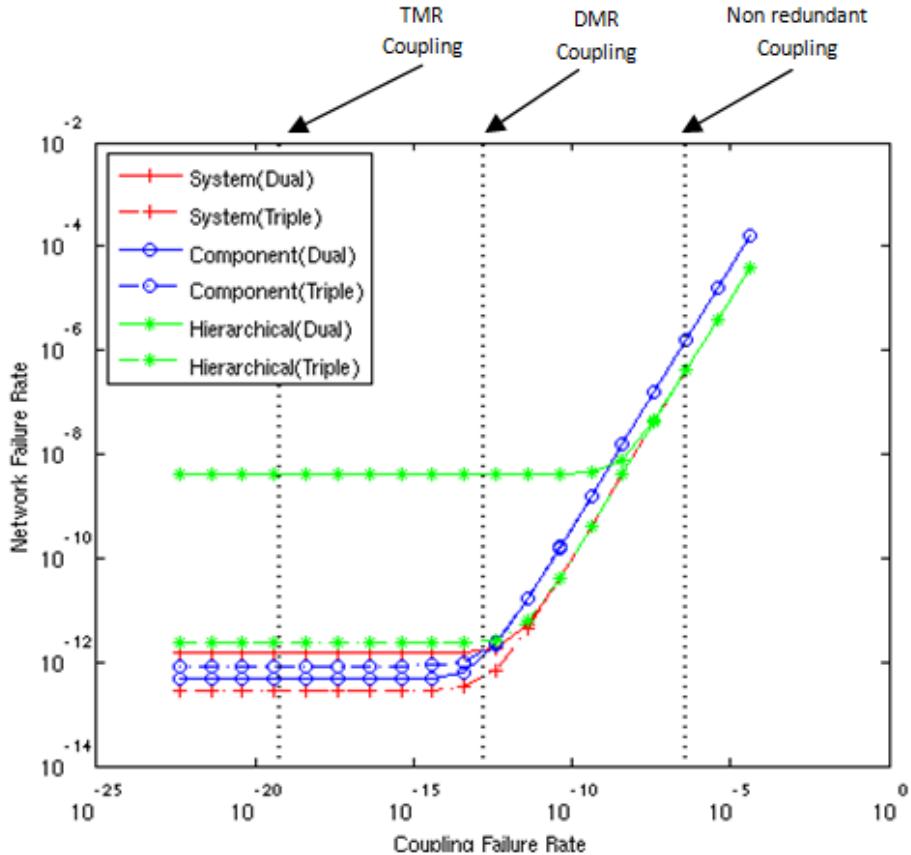

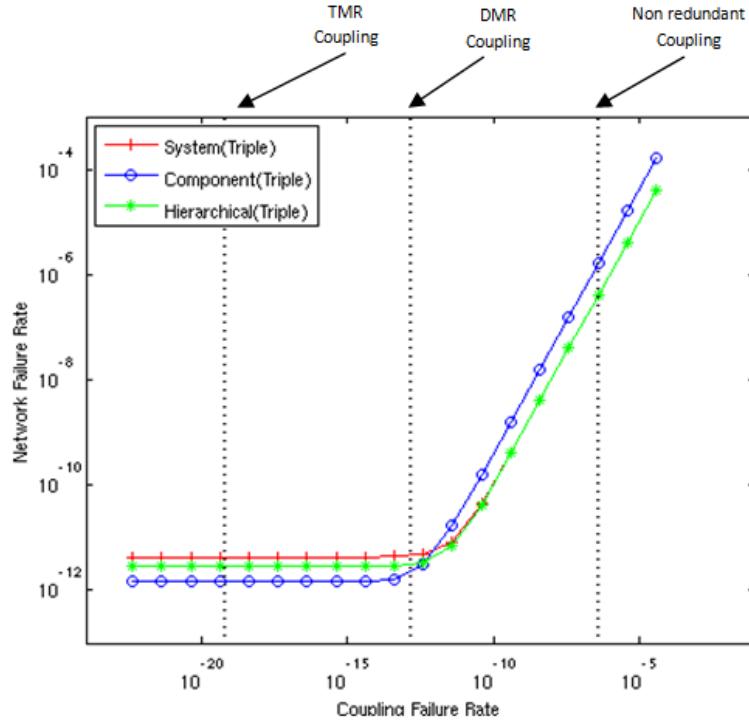

| Figure 4-12: Architecture“s unreliability as a function the coupling“s unreliability for error detection ..... | 75 |

| Figure 4-13: Architecture“s unreliability against the coupling“s unreliability for data correction             | 76 |

| Figure 5-1: Méthodologie proposée .....                                                                        | 83 |

| Figure 5-2: Arbre de panne du réseau complet .....                                                             | 88 |

| Figure 5-3: Arbre de panne d“un TIM .....                                                                      | 89 |

| Figure 5-4: Arbre de panne d“un NCAP .....                                                                     | 89 |

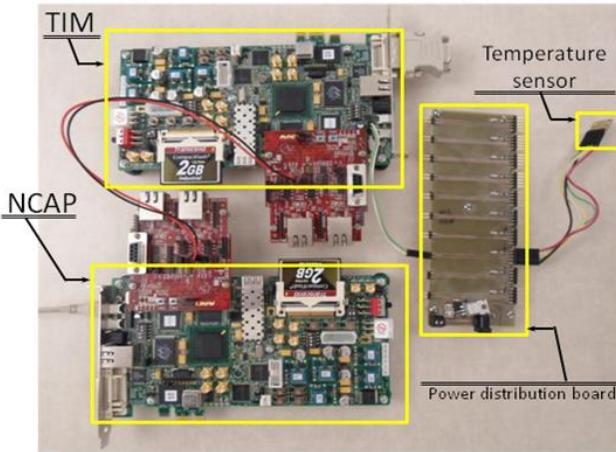

| Figure 5-5: Prototype matériel .....                                                                           | 92 |

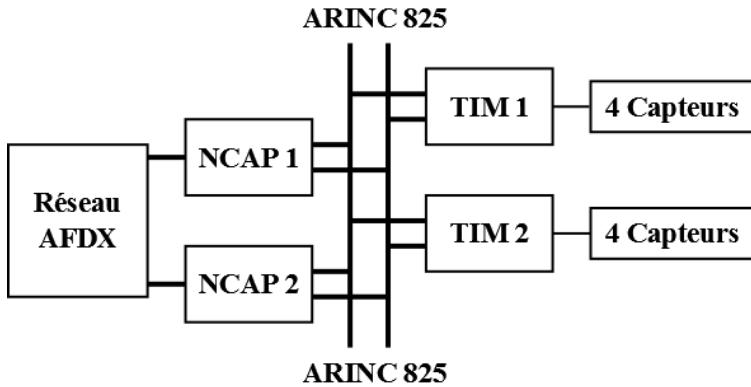

| Figure 5-6: Exemple de réseau .....                                                                            | 94 |

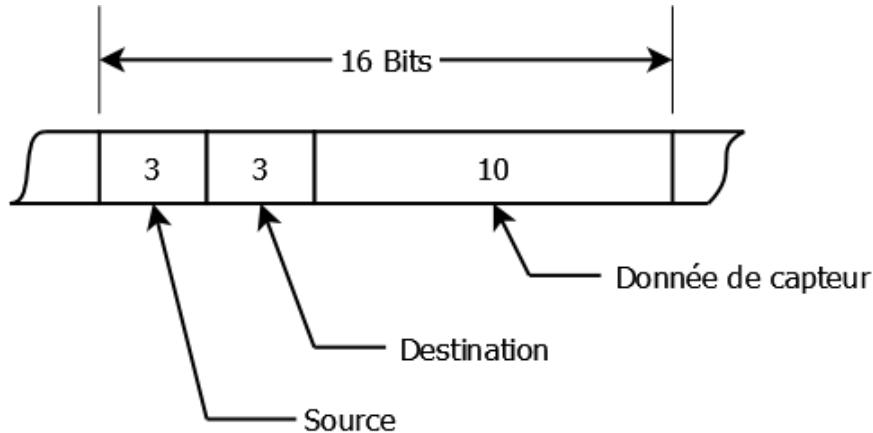

| Figure 5-7: Composition de la trame.....                                                                       | 98 |

## **LISTE DES SIGLES ET ABRÉVIATIONS**

|      |                                       |

|------|---------------------------------------|

| ARP  | Avionics Recommended Practices        |

| CAN  | Controller Area Network               |

| DASC | Digital Avionics System Conference    |

| FCC  | Flight Control Computer               |

| FMEA | Failures Modes and Effects Analysis   |

| FPGA | Field Programmable Gate Array         |

| FTA  | Fault Tree Analysis                   |

| IMA  | Integrated Modular Avionics           |

| LRU  | Line Replaceable Unit                 |

| LUT  | Look Up Table                         |

| NCAP | Network Capable Application Processor |

| SEU  | Single Event Upset                    |

| TEDS | Transducer Electronic Datasheet       |

| TIM  | Transducer Interface Module           |

| TRL  | Technological Readiness Level         |

## CHAPITRE 1 INTRODUCTION

### 1.1 Mise en contexte

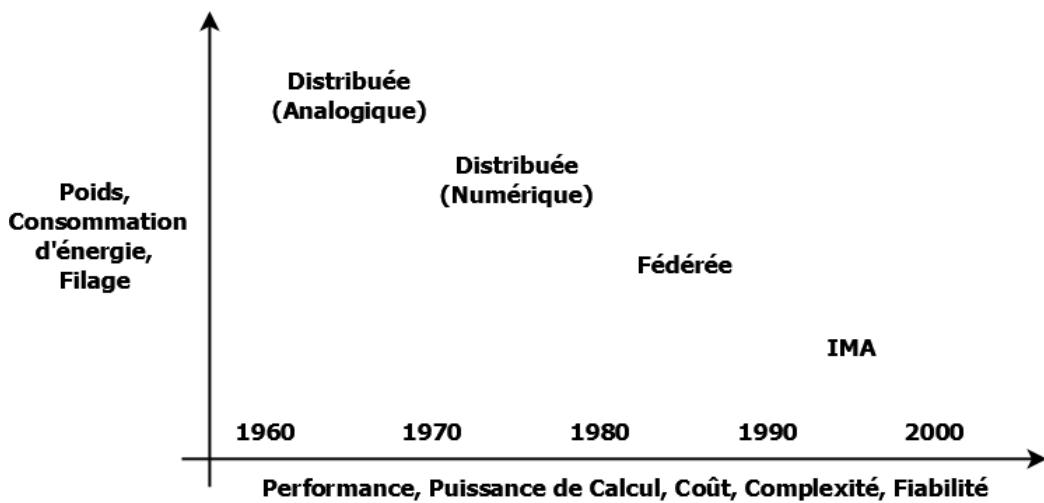

Dans le domaine aéronautique, l'application des technologies numériques a été introduite rapidement suite à l'amélioration marquée des performances et de la complexité des différents aéronefs civils. La Figure 1-1 représente l'évolution des architectures avioniques depuis l'introduction des composants électroniques au début des années 60. Auparavant, la quasi-totalité des systèmes aéronautiques dans l'industrie civile était implantée de manière électromécanique. Plusieurs des appareils développés à l'aide des approches distribuées analogique et numérique sont toujours en service, tels le Boeing 707 et les premiers modèles de Boeing 737, bien que leur nombre diminue rapidement en raison du coût de maintenance exorbitant de ces systèmes vieillissants [1].

Figure 1-1: Évolution des architectures avioniques [1]

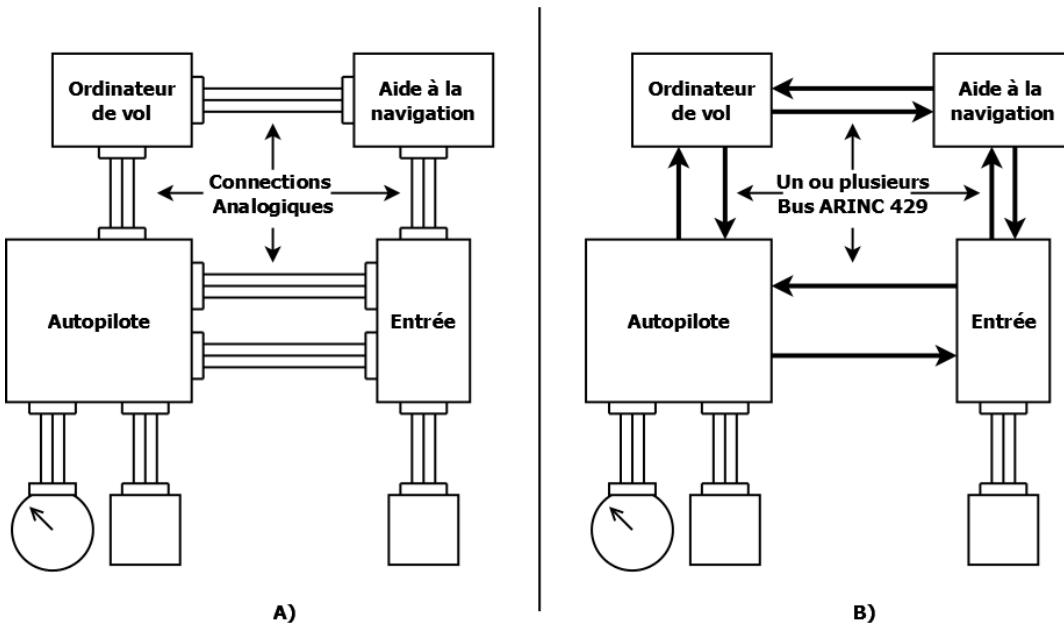

Les deux premiers paradigmes de développement de systèmes avioniques, basés sur l'isolation complète de chaque sous-système, n'ont comme distinction que la technologie utilisée pour leur implémentation. L'évolution technologique des années 70, incluant l'apparition de bus de données numériques, permit entre autres d'augmenter la performance de ces systèmes en maintenant la même approche de développement d'architecture. À ce moment, les connexions analogiques directes ont été remplacées par des bus de données unidirectionnels, tel le ARINC 429 [2], le protocole le plus populaire à l'époque. Malgré un faible débit de 100 kbps, cette

norme est toujours importante pour l'interfaçage de composants plus simples et comme manière d'introduire de la dissimilitude dans les systèmes critiques. Malgré l'introduction de bus pour l'architecture numérique, le raccordement des instruments à ce stade ne pouvait toujours se faire que de manière analogique. La grande popularité de l'ARINC 429 a mené à un premier effort de standardisation des équipements permettant éventuellement une évolution vers l'approche fédérée. Bien que l'augmentation des performances des transferts numériques à l'intérieur d'un même système ait mené à une utilisation grandissante de processeurs numériques dans de nouveaux systèmes, le développement de chaque système est demeuré orienté vers la réalisation d'une seule fonction indépendante. La figure suivante fournit plus de détails sur un exemple d'architecture distribuée réalisée selon les approches analogiques et numériques. À la Figure 1-2, la distinction majeure entre les deux modèles repose sur le remplacement de nombreux fils indépendants par des bus unidirectionnels de données numériques.

Figure 1-2: Architectures distribuées A) analogique B) numérique

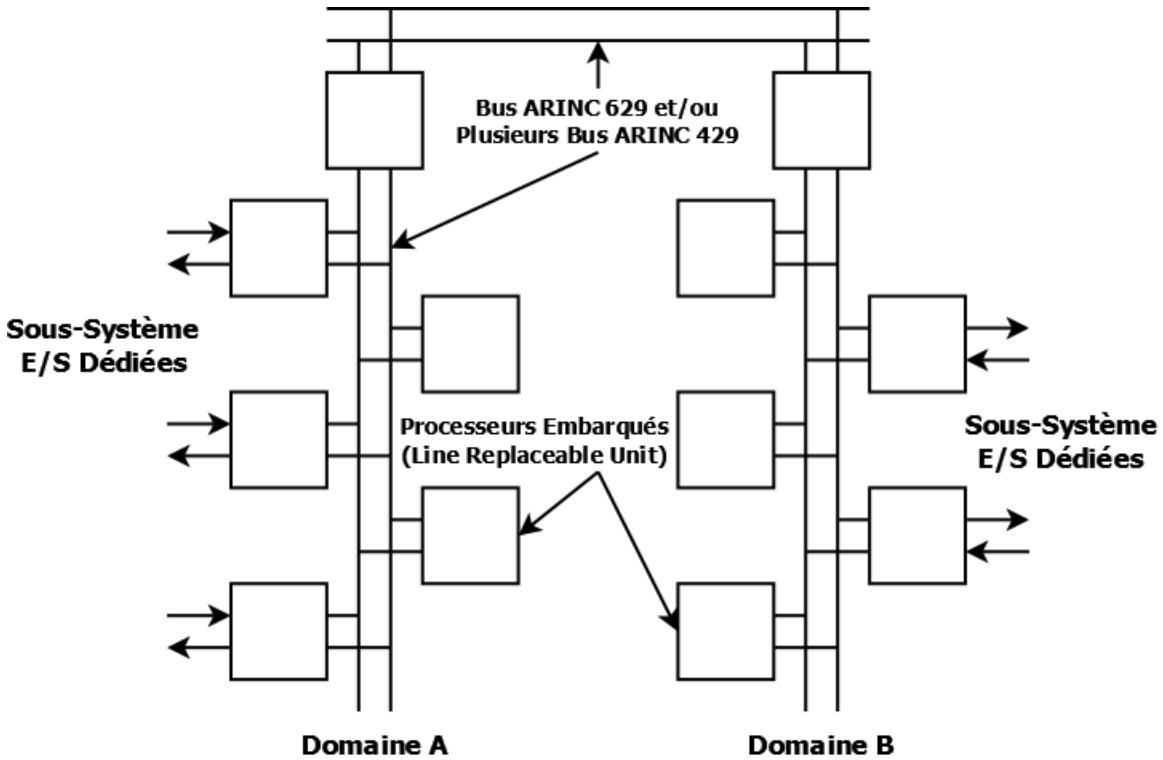

L'approche de conception introduite après l'approche distribuée, communément appelée l'architecture fédérée, est basée sur la séparation des fonctions et du matériel et permet un processus simple de validation et d'intégration avec de simples assurances de respect des contraintes de bande passante et de synchronisation. Avec l'approche fédérée, les systèmes avioniques ont graduellement été intégrés et groupés selon les différents domaines d'application (commande de vol, carburant, train d'atterrissage ...). La Figure 1-3 montre un exemple

d'architecture fédérée typique tel que l'on peut retrouver à bord du Boeing 777. Cette architecture a été adoptée massivement par l'industrie à partir des années 80.

Figure 1-3: Exemple d'architecture fédérée

L'approche fédérée traditionnelle repose donc sur le développement de composants fonctionnels indépendants connectés par des bus unidirectionnels et par d'autres signaux de contrôle dédiés. À ce stade de développement, l'équipement avionique se décline principalement sous la forme de designs propriétaires offrant une solution dédiée à une fonctionnalité précise limitant l'utilisation de ces composants dans d'autres champs d'activité. Les limitations de cette architecture ont commencé à apparaître avec l'avènement des nouvelles technologies de communication et la multiplication des composants de toutes sortes. En effet, les avancées technologiques en électronique permettant une intégration toujours plus efficace des différents composants ont permis de grandement augmenter les différentes fonctionnalités requises à bord d'un aéronef. L'utilisation croissante de ces technologies numériques a donc entraîné une augmentation marquée de la complexité des systèmes. En suivant l'approche fédérée, ces nouvelles fonctionnalités ont entraîné une augmentation significative du nombre d'équipements de toutes sortes (Bus, CPU, LRU, FCC). Cette complexité croissante des systèmes avioniques a entraîné

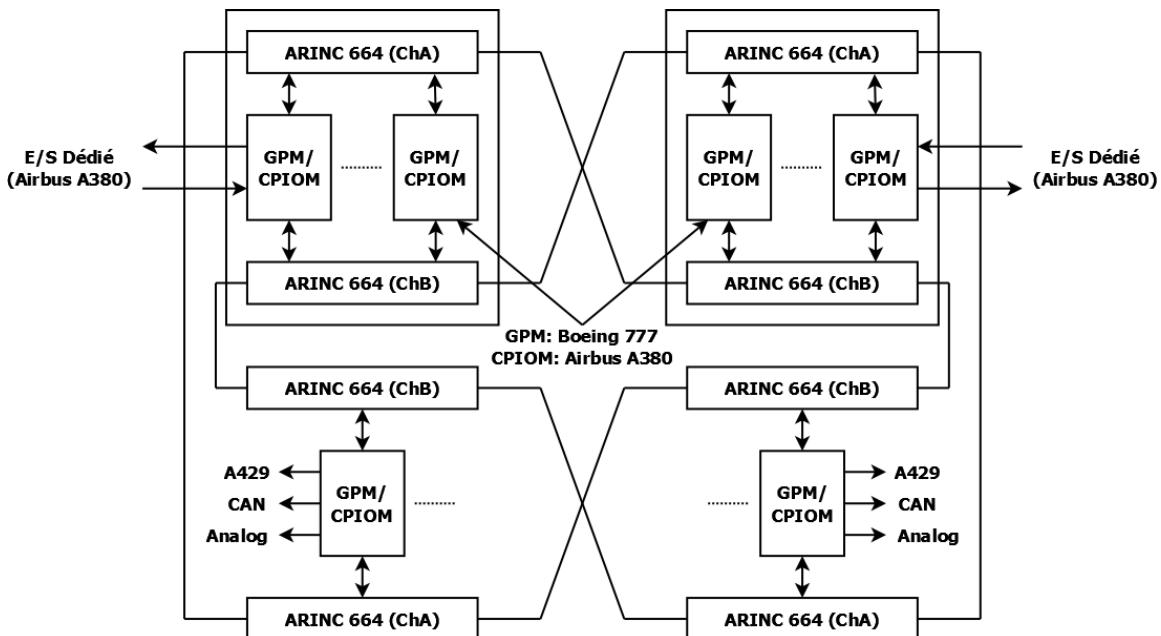

une augmentation substantielle des coûts de développement et d'exploitation. La réduction et la maîtrise de cette complexité permettent donc un meilleur contrôle des coûts de réalisation, de maintenance et de mise à niveau. Pour faire face à ces nouveaux défis, un nouveau paradigme de développement a donc été nécessaire. À l'aide des nouvelles technologies aux capacités toujours grandissantes, il est maintenant possible de pallier aux limites de l'architecture fédérée à l'aide d'une nouvelle architecture intégrée communément appelée l'« architecture intégrée modulaire ou « Integrated Modular Avionics » (IMA). Un exemple typique de l'architecture IMA est présenté à la Figure 1-4.

Figure 1-4: Exemple d'architecture IMA [1]

Ce nouveau type d'architecture est quant à lui basé sur une conception modulaire et un partage de ressources génériques entre plusieurs systèmes. Les bus mono-émetteur de l'approche fédérée sont entre autres remplacés par des bus multiplexés. Une normalisation plus poussée de l'architecture matérielle est donc requise pour une connexion harmonieuse à plusieurs systèmes. Au niveau applicatif, le développement peut s'effectuer de manière indépendante de la structure d'implémentation et doit également être en mesure de supporter plusieurs périphériques simultanément. Comme exemple d'application d'une architecture IMA dans la conception d'un avion moderne, nous pouvons citer le cas du A380 chez Airbus. L'approche IMA retenue par Airbus consiste à développer une série de composants de base pouvant être assemblés de manière modulaire pour répondre aux besoins de tout système. Dans le cas du A380, ces composants sont

utilisés pour construire les 30 modules du système incluant les modules requis pour l'atteinte des cibles de fiabilité grâce à la redondance. Par la suite, le fournisseur de chaque système développe le côté applicatif en respectant les interfaces des différents modules de base. Grâce à ce système, plusieurs applications (freinage, contrôle de vol, carburant, etc.) peuvent même se retrouver sur le même module tout en provenant de fournisseurs différents et complètement indépendants. La stratégie adoptée permet à Airbus dans ce cas d'améliorer l'efficacité de l'utilisation des ressources. L'avantage principal de l'utilisation de l'architecture IMA est donc de pouvoir optimiser les ressources utilisées contrairement aux modèles précédents.

## 1.2 Problématique

La plupart des concepts utilisés par l'architecture IMA, bien que déjà connus dans le domaine de l'informatique distribuée, constituent un changement marqué par rapport aux modèles antérieurs dans le monde avionique. Ceux-ci viennent s'ajouter aux contraintes importantes de l'avionique classique telles que le déterminisme, le temps réel, la certification et les cibles élevées de fiabilité. L'adoption de l'approche IMA a déclenché une révision de plusieurs aspects de la conception, de la certification et de l'implémentation d'un système IMA afin d'en tirer profit. Cette révision, ralentie par les contraintes avioniques, est toujours en cours, et offre encore l'opportunité de développement de nouveaux outils, méthodes et modèles à tous les niveaux du processus d'implémentation d'un système IMA.

Plusieurs aspects du design et de la validation des architectures IMA doivent être abordés de manière différente. Par exemple, l'utilisation d'un support matériel commun demande toujours une spécification propre, mais doit également être considérée dans les analyses de performance et de sûreté de chacun des sous-systèmes impliqués. L'interaction entre les différents systèmes doit être prise en compte afin de valider le comportement du système entier. Le développement d'applications évoluant sur le même support physique requiert également l'introduction d'une certaine forme de parallélisme pour l'intégration et la validation des différentes fonctions implémentées. Au niveau de la gestion des ressources, un partage global demande une gestion des ressources inexploitées au niveau système plutôt qu'au niveau local. Dans les architectures antérieures, la présence de ressources supplémentaires n'était nullement utile, puisque celles-ci ne peuvent être employées à accroître ou modifier les fonctionnalités des différents systèmes connexes. Dans une architecture IMA, la capacité de croissance est implicitement requise lors des

phases de conception et d'implémentation pour apporter une flexibilité au système et minimiser les efforts de modification.

Bien qu'au moins une vingtaine d'années se soient écoulées depuis l'introduction des principes de base des architectures IMA, il semble évident que les outils et méthodes permettant l'évaluation et la réalisation des phases de conception et d'implémentation n'ont pas évolué suffisamment pour permettre une utilisation optimale de ce type d'architectures. Les techniques et approches traditionnelles couramment utilisées seront présentées tout au long de cette thèse. Cette lente évolution des pratiques avioniques traditionnelles s'explique en partie du fait que les avancées technologiques aient été suffisantes du début des années 60 au tournant des années 2000 pour améliorer substantiellement les performances des systèmes avioniques. Les changements apportés par l'architecture IMA impliquent également une évolution des méthodes et outils de conception, d'implémentation et de validation pour continuer l'amélioration des performances de ces systèmes. Cette distinction peut, entre autres, expliquer le retard au niveau de l'évolution des outils et des approches, puisque l'architecture IMA demande une révision des méthodes.

Dans un contexte de proposition et de validation d'une nouvelle architecture IMA pour un réseau générique de capteurs à bord d'un avion, nous avons identifié quelques aspects des différentes approches traditionnelles pour la réalisation de ce type d'architectures pouvant être améliorés. Afin de pallier à certaines des différentes lacunes identifiées, nous avons proposé une approche de validation basée sur une plateforme matérielle reconfigurable ainsi qu'une nouvelle approche de gestion de la redondance pour l'atteinte des cibles de fiabilité. Contrairement aux outils statiques plus limités satisfaisant les besoins pour la conception d'une architecture fédérée, notre approche de validation est spécifiquement développée de manière à faciliter la conception d'une architecture IMA. De même, une application traditionnelle de la gestion de la redondance ne permettait pas de tirer profit de la flexibilité offerte par une architecture IMA. Les détails des différentes contributions de cette thèse seront présentés à la section 1.4.

### 1.3 Cadre de projet

Dans l'industrie avionique, de nombreux systèmes de capteurs et d'actuateurs sont requis afin d'assurer un nombre grandissant de fonctions à bord des avions. Avec les approches et outils conventionnels, la connexion de ces instruments demanderait un câblage réseau lourd et

encombrant. Les différentes cibles de fiabilité en avionique pour les systèmes critiques en complexifient le design de par l'installation redondante d'une grande partie des composants à bord d'un aéronef. De plus, la communication entre différents modules appartenant à divers domaines d'application est maintenant requise dans les nouvelles plateformes avioniques. Ceci entraîne une augmentation marquée de la demande en bande passante à l'intérieur des aéronefs, tout en devant s'assurer de respecter l'intégrité des données critiques lors de leur transmission.

Les travaux et propositions présentés dans cette thèse de doctorat ont été largement réalisés dans le cadre du projet AVIO402, qui tentait de répondre aux nouvelles demandes du domaine avionique énoncées précédemment. Le but de ce projet était donc de proposer de nouvelles architectures pour assurer des communications fiables de données critiques dans un avion en réduisant la complexité des systèmes câblés à l'aide de trois parties complémentaires :

- l'adoption de nouveaux bus de données multifonctionnels hautement fiables;

- le développement de nouvelles interfaces analogiques pour de nouveaux types de capteurs et actuateurs;

- l'exploration des effets des communications sans fil à bord d'un avion.

Une architecture appropriée a donc été développée en respectant chacun de ces aspects de manière à faciliter leur interopérabilité. Ces sujets sont des points d'intérêt reliés au développement technologique des systèmes avioniques de prochaine génération pour les partenaires industriels impliqués, soit Thales Canada inc. (Thales) et Bombardier Aerospace inc. (Bombardier). Ce domaine de recherche est également une des priorités principales du Consortium de Recherche et d'Innovation en Aérospatiale du Québec, le CRIAQ, qui a contribué financièrement à la réalisation de ce projet.

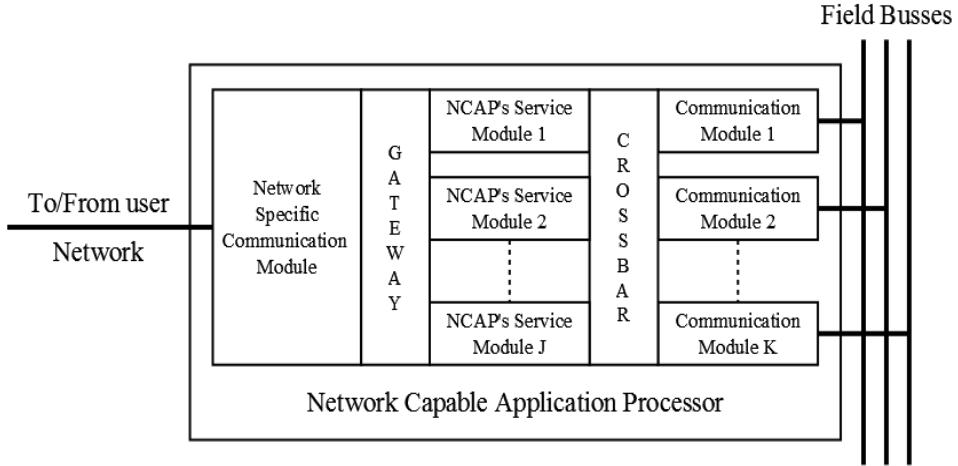

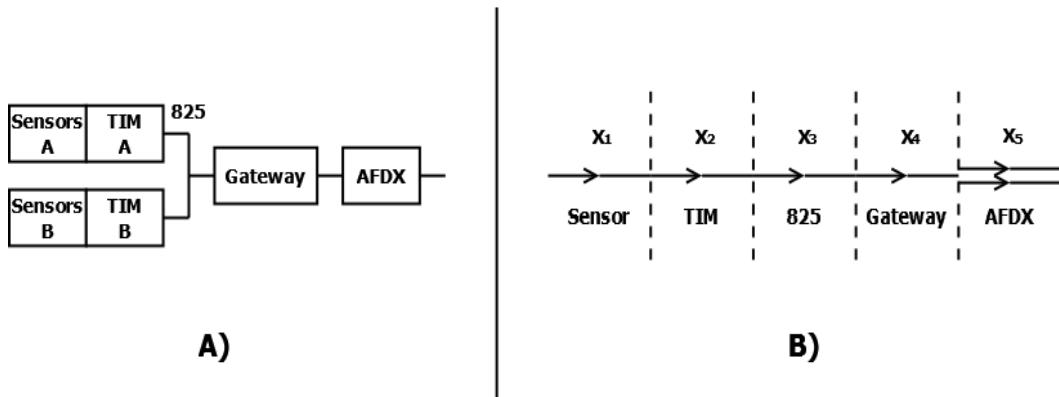

La nouvelle topologie qui a été développée dans le cadre du projet repose sur l'utilisation du protocole de transmission de données AFDX/ARINC664 [3] comme architecture de base du réseau. Cette norme permet une bande passante amplement suffisante pour les besoins en communication à bord d'un avion. Par contre, le coût élevé associé à chacune des interfaces de connexion à un réseau AFDX rend la connexion individuelle des capteurs/actuateurs relativement dispendieuse. Un réseau secondaire est donc nécessaire pour compléter le réseau AFDX en regroupant une série de capteurs/actuateurs et éventuellement de plusieurs autres types de périphériques à un seul port d'accès AFDX. Le diagramme du système proposé est présenté à la

Figure 1-5. Afin de se conformer aux exigences en matière de fiabilité, le bus secondaire suit la norme ARINC 825 [4], une version modifiée du protocole CAN [5] qui répond spécifiquement aux besoins du domaine avionique.

Les diverses parties de ce réseau de capteurs ont été implémentées et validées sur une plateforme matérielle reconfigurable basée sur des FPGA afin de se rendre à un niveau de maturité technologique (Technology Readiness Level) TRL4, correspondant à une validation en laboratoire à l'aide d'un prototype. Cette plateforme matérielle servant de prototype a été utilisée pour l'évaluation des performances réelles de cette architecture en matière de bande passante et d'intégrité des données. Ce prototype comprend entre autres des mécanismes d'injection de pannes de manière à simuler différents types de défaillances et des modules matériels additionnels améliorant l'intégrité et la fiabilité du réseau.

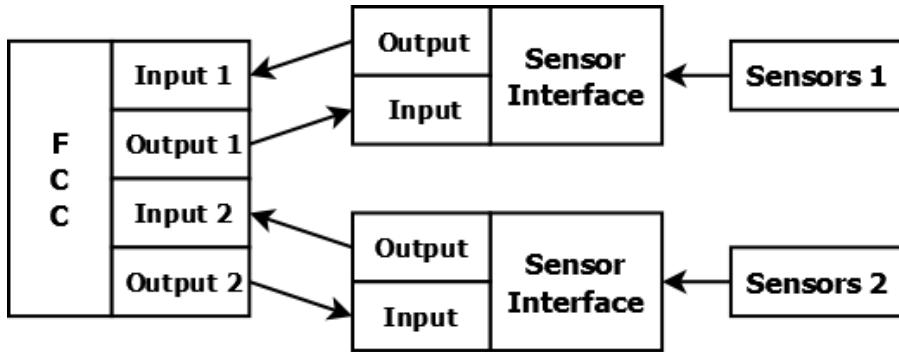

Figure 1-5: Architecture proposée [6]

Les travaux de cette thèse, qui s'inscrivent à l'intérieur du projet AVIO402, ont porté principalement sur l'élaboration d'une architecture de réseau de données plus efficace pour le réseau secondaire reliant les capteurs/actuateurs au réseau principal. Cette architecture se devait d'être la plus générique possible afin de desservir une quantité variable de capteurs/actuateurs de toutes sortes. Pour ce faire, l'architecture proposée s'est inspirée de la norme IEEE 1451 [7], qui suggère un modèle de référence standard permettant l'accès et le contrôle de transducteurs, d'une

manière la plus générique possible, à travers des interfaces communes vers tout système de contrôle ou d'Instrumentation. La topologie proposée peut ultimement être implémentée avec une grande liberté quant au choix du protocole de transmission et des couches physiques du réseau, pouvant même supporter une éventuelle implémentation sans fil.

La fiabilité du réseau devait également être validée afin de satisfaire les niveaux requis imposés par le domaine avionique. Le réseau de transmission se devait d'avoir un taux de pannes inférieur à celui des composants qu'il connecte, soit les capteurs/transducteurs et les ordinateurs de vol. En raison de la nature critique des données recueillies par les capteurs et des commandes envoyées aux actuateurs pour le calcul et le maintien de la bonne trajectoire de vol, le niveau de tolérance aux pannes se devait d'être très élevé, soit de l'ordre d'une erreur non détectée ou d'une panne pour  $10^9$  heures de vol. Puisqu'un des buts de cette partie du projet AVIO402 était de proposer un réseau étant le plus générique possible, le degré de fiabilité devait également être ajusté en fonction du niveau requis pour l'application. Par contre, il est à noter que les hausses de fiabilité sont généralement accompagnées par une augmentation de la consommation de ressources matérielles de la plateforme matérielle, puisque cette hausse de fiabilité est traditionnellement acquise grâce à l'ajout de redondance dans le système. Une stratégie a été mise de l'avant pour ajuster la fiabilité tout en essayant de minimiser la consommation de ressources. Globalement, l'approche présentée cherche à mieux intégrer ces techniques de fiabilité afin de minimiser la consommation de ressources et l'effort de validation.

## 1.4 Objectifs de recherche et contributions

Dans le cadre de cette thèse, trois axes principaux de contributions originales se sont dégagés des travaux exécutés suivant les différents objectifs de recherche. Le premier objectif de recherche était de proposer une nouvelle architecture de réseaux avioniques pour la connexion de capteurs ou actuateurs. En effet, l'examen des architectures utilisées traditionnellement dans l'industrie ne permettait pas l'atteinte des requis fixés en matière de flexibilité, reconfigurabilité et tolérance aux pannes. Afin de pouvoir répondre aux besoins imposés par le cadre du projet AVIO 402, la proposition d'une nouvelle architecture a donc été nécessaire. Cette architecture fait l'objet d'un premier article [8] intitulé « A System Architecture for Smart Sensors Integration in Avionics Applications » et publié dans la revue « SAE International Journal of Aerospace » en 2012. La

version intégrale de cet article se trouve au chapitre 3. Les contributions de cette architecture de systèmes avioniques sont :

- Afin de conférer un caractère générique et configurable aux architectures avionique existantes, une nouvelle architecture hiérarchique est proposée. En se basant entre autres sur la norme IEEE 1451, l'architecture proposée permet la connexion des capteurs et actuateurs intelligents à tout système numérique.

- L'architecture hiérarchique innove en permettant une optimisation des ressources consommées et de la fiabilité selon les contraintes à considérer. Un système critique peut donc être implanté de manière à assurer un niveau élevé de fiabilité tandis que l'on peut minimiser la consommation de ressources d'un système non critique grâce à la même architecture hiérarchique.

- En comparaison avec des architectures similaires suivant la norme 1451, nous avons pu établir que pour un même niveau de fiabilité, l'architecture hiérarchique proposée entraîne une réduction de la consommation de ressources quand on la compare avec des architectures existantes.

Le second objectif de recherche visait la proposition d'une nouvelle approche de conception et de validation adaptée pour l'implémentation de réseaux avioniques suivant les principes de l'IMA. Pour faire suite à la problématique exposée à la section 1.2, nous avons en effet établi que les outils de conception et de validation utilisés pour les architectures précédant l'introduction de l'IMA n'étaient toujours pas adaptés à nos objectifs de travail. La nouvelle approche basée sur une plateforme matérielle a fait l'objet de la section 5.2. Les contributions de cette approche matérielle sont :

- Une approche basée sur l'exploitation d'une plateforme matérielle servant à la phase initiale de conception qui prend en considération les principes IMA et permet la validation de l'architecture sélectionnée au niveau approprié. Les approches traditionnelles logicielles se concentrent sur la validation d'un simple aspect de l'architecture plutôt que de la considérer dans son ensemble.

- Afin de pouvoir faire une validation matérielle multiplateforme de notre architecture, le développement d'un nouveau mécanisme hybride de mesure de latence des trames du

réseau a été nécessaire. En effet, les moniteurs existants ne permettaient pas une mesure de latence du réseau dans son entier en ne supportant l'examen que de sous-sections.

Dans le cadre du processus de validation de notre architecture hiérarchique à travers la nouvelle approche matérielle, un troisième objectif de recherche, exposé au chapitre 5.2, prenait la forme d'une évaluation de possibles améliorations pouvant être apportées au protocole ARINC 825. Les contributions au niveau des améliorations proposées sont :

- L'inclusion dans les contrôleurs ARINC 825 de stratégies d'agrégation de trames qui permettent la réduction de la bande passante consommée et la connexion d'un nombre supérieur de capteurs ou actuateurs pour la même configuration d'architecture hiérarchique.

- La modification au protocole de gestion d'erreur des contrôleurs ARINC 825 qui a été nécessaire afin d'assurer le fonctionnement correct des mécanismes de tolérance aux pannes.

Le dernier objectif de recherche cherchait à déterminer la méthode appropriée d'introduction de la redondance dans un réseau avionique afin d'atteindre des cibles de fiabilité. Notre approche à la gestion de la redondance pour les systèmes avioniques est présentée dans un article [9] intitulé « Hierarchical Redundancy Management for Avionic Networks » soumis à la revue « Transactions on Aerospace and Electronic Systems ». Cet article se trouve au chapitre 5. Les contributions au niveau des améliorations proposées sont que:

- L'analyse de l'architecture hiérarchique révèle qu'elle permet de réduire les effets de couplages indésirables en avionique en réduisant le nombre de points communs de défaillance, contrairement aux approches traditionnelles d'introduction de redondance.

- Dans le cadre d'introduction de redondance dans un réseau avionique, l'approche hiérarchique permet également de réaliser un gain au niveau de la consommation de ressources comparativement aux techniques usuelles de gestion de la redondance.

## 1.5 Organisation de la thèse

L'introduction de cette thèse a présenté l'évolution du domaine avionique au niveau des architectures de réseau ainsi que les différentes problématiques qui s'y rattachent. À partir du cadre de travail des réalisations effectuées, les différentes contributions réclamées dans cette

thèse ont été énoncées. Le reste de la thèse continue selon la structure suivante. Le chapitre 2 explore la littérature pertinente et aura pour but de présenter et justifier les techniques et approches ayant déjà prouvé leur efficacité dans un passé rapproché, ainsi qu'à établir les principes de base dans les domaines pertinents. Ce chapitre est divisé en 3 sections rattachées à chacun des 3 axes de contribution afin de les mettre plus spécifiquement en contexte.

Deux articles pertinents à ces contributions constituent la suite de cette thèse. Le premier article, composant le chapitre 3, présente l'architecture générique ainsi que ses différentes distinctions et avantages d'utilisation. Le chapitre 4 contient le dernier article portant sur la gestion de la redondance de l'architecture hiérarchique ainsi que sur l'analyse des points communs de défaillance pour les différentes méthodes étudiées. Le chapitre 5 contient des détails additionnels de nos travaux de recherche en faisant un retour sur les articles exposés sous la forme d'une discussion générale. Les différents choix menant aux résultats sont également discutés. Finalement, le chapitre 6 vient conclure cette thèse en résumant brièvement son contenu et en donnant quelques indications sur les possibles améliorations futures.

## CHAPITRE 2 RÉSEAUX AVIONIQUES DE CAPTEURS

Quand on analyse les premières générations de systèmes avioniques antérieurs à l'avènement du concept IMA au tournant des années 2000, on constate que l'évolution des architectures se résumait principalement à une simple évolution des composants rendus désuets par l'avancement des technologies numériques. Avec l'arrivée de l'IMA, plusieurs aspects des méthodes de design et validation ont dû être adaptés pour faire face aux nouvelles possibilités. Pour ce faire, les connaissances de plusieurs autres domaines (temps réel, fiabilité, capteurs intelligents, etc.) ont été intégrées aux techniques traditionnelles afin de faire face à ces nouvelles problématiques, tel le partage de systèmes génériques, les interactions entre différentes applications et la reconfiguration dynamique, spécialement dans le cadre d'applications critiques. Les principales contraintes au niveau d'applications critiques seront présentées dans la section portant sur les méthodes de design et validation de systèmes avioniques.

Le présent chapitre met en contexte chacun des articles composants cette thèse en présentant de manière plus spécifique les principaux champs d'intérêt et technologies abordés. Le champ d'intérêt de la première contribution évoquée dans [8] couvre l'intégration du protocole IEEE 1451 [7] au processus de design de systèmes avioniques. Pour débuter, les principes de base de la norme IEEE 1451 seront donc exposés afin de mettre en contexte les contributions contenues dans l'article [8]. Les différentes applications de la norme IEEE 1451 ainsi que les architectures résultantes de son intégration feront par la suite ressortir les avantages et limites de la transposition de ces différentes architectures dans le domaine avionique. Les différentes tendances et derniers avancements significatifs seront finalement exposés pour mettre en lumière l'intérêt de proposer une nouvelle architecture intégrant le protocole IEEE 1451 tout en respectant les spécificités du domaine avionique.

Les contributions énoncées de cette thèse se situent au niveau des différentes approches de design et validation de réseaux avioniques. L'approche classique de design sera d'abord présentée en complétant avec les différentes variantes les plus pertinentes. Les différentes stratégies décrites et classées par type d'approche logicielle ou matérielle viendront donc s'ajouter à celle de ce dernier article. La dernière partie de cette section présentera les derniers travaux dans le domaine des moniteurs de surveillance pour situer une partie des contributions évoqué au chapitre 5.2. Le protocole ARINC 825, incluant l'implémentation d'un nœud de contrôle, sert de base aux

prochaines contributions énoncées dans cette thèse. Les principes de base du protocole ARINC 825 seront donc exposés ainsi que l'état de la recherche récente sur cette norme. Cette section se conclura par la présentation des stratégies de regroupement de trames en faisant ressortir les avantages et inconvénients de l'utilisation de ces techniques. Les derniers avancements dans le domaine seront également présentés.

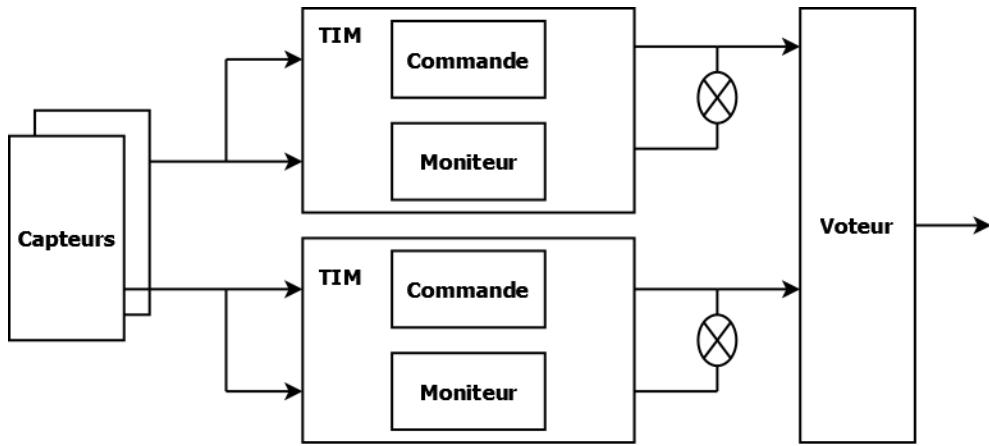

Le dernier thème abordé dans cette revue de littérature portera sur la gestion de la redondance pour mieux mettre en lumière les contributions du dernier article [9] composant cette thèse. L'approche classique d'intégration de redondance dans un système avionique sera d'abord présentée. L'architecture Com-Mon sera exposée à ce niveau afin de venir compléter les architectures de comparaison déjà incluses dans le second article [9]. Les derniers travaux pertinents présentés depuis la publication de [9] seront par la suite présentés en focalisant sur l'importance du système de votation lors de l'utilisation de la redondance. Pour compléter, une courte liste des approches alternatives à la redondance sera également exposée.

## 2.1 IEEE 1451

Pour commencer, une courte explication présentera les principes de base de la norme IEEE 1451 suivie par les principales applications et architectures découlant de la recherche dans le domaine de ce protocole. De plus amples détails sont inclus dans l'article du chapitre 3. Les références contenues dans cette thèse reflèteront donc les avancements réalisés et les tendances observées depuis 2012, soit la date de parution du premier article. Toutes les références pertinentes publiées antérieurement peuvent être trouvées directement dans l'article du chapitre 3.

### 2.1.1 Principes de base

Les différents types de capteurs et d'actuateurs sont une partie importante de plusieurs systèmes dans les domaines de la production en chaîne, du contrôle industriel, des transports, de l'aéronautique, etc. Puisque ceux-ci sont utilisés dans de nombreuses applications, leurs implémentations sont généralement spécifiques à une classe précise d'applications. Le support de plusieurs protocoles de communication et de réseaux ou le développement de plusieurs versions du même transducteur demanderait des efforts significatifs qui s'avèrent peu avantageux pour le manufacturier. La norme intitulée « *IEEE 1451 : Standard for a Smart Transducer Interface for Sensors and Actuators* » [7] a été proposée afin de régler ces problèmes. Son objectif principal est

de proposer un cadre d'implémentation pour le contrôle de transducteurs à travers des interfaces normalisées. En suivant la norme, les transducteurs peuvent donc être connectés directement à un ordinateur, un système d'instrumentation ou tout autre type de réseau de contrôle. Le modèle de référence mis de l'avant est complètement indépendant du protocole de communication et même du choix d'une implémentation logicielle ou matérielle.

Le respect de cette norme permet de diminuer l'effort de design, en particulier lors d'utilisations dans de multiples applications aux caractéristiques différentes. Le système devient également plus facile à installer, mettre à jour, remplacer et déplacer. Ces derniers avantages sont particulièrement recherchés lors de la sélection de tout système inclus à bord d'un aéronef.

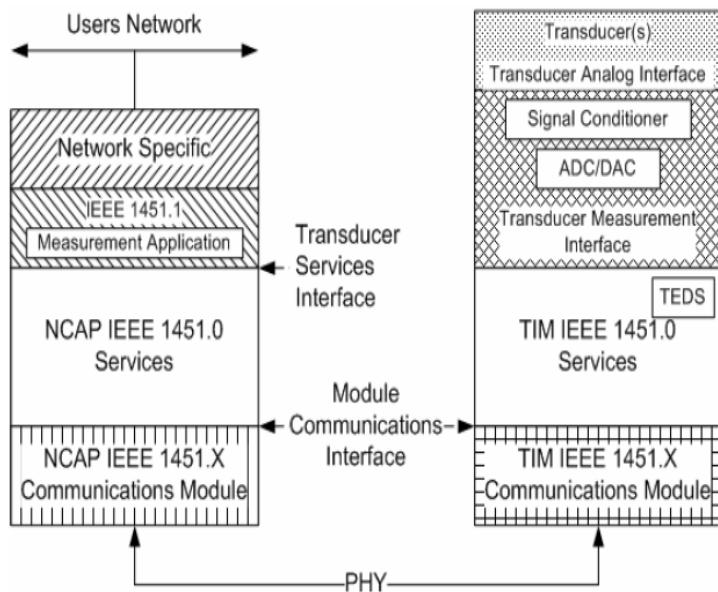

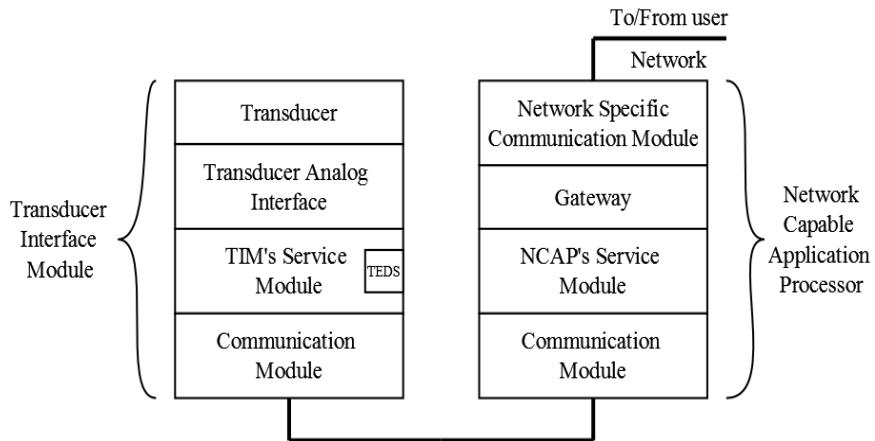

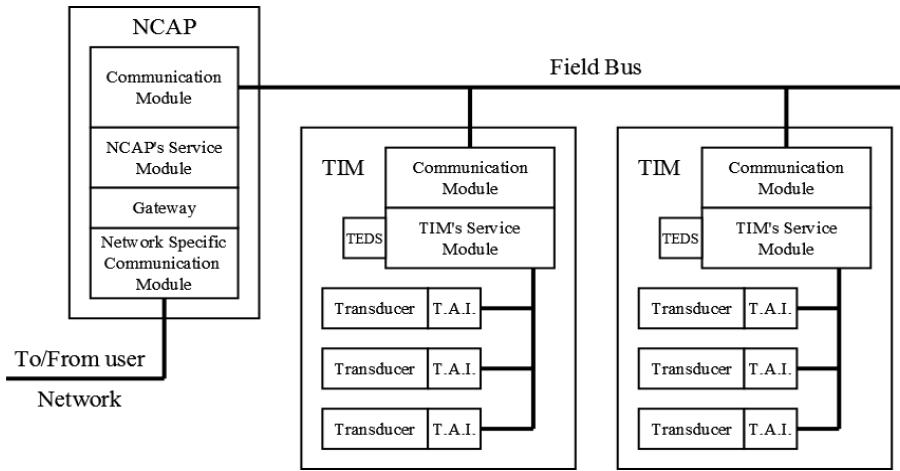

Figure 2-1: Modèle de référence du IEEE 1451 [7]

Le modèle de référence de la norme IEEE 1451 est présenté à la Figure 2-1. La section centrale de la spécification propose une série d'opérations et de commandes séparées en deux modules principaux. Le « Transducer Interface Module (TIM) » est responsable du conditionnement du signal analogique, de la conversion numérique, du traitement des commandes, du transfert des données et du stockage des informations relatives aux transducteurs dans un module appelé « Transducers Electronic Data Sheet (TEDS) ». Chaque TIM contient également au moins un transducteur tandis que les TEDS doivent être contenus dans une mémoire non volatile. La deuxième partie, le « Network Capable Application Processor (NCAP) », est responsable de lier

les modules TIM au réseau principal. Les NCAP sont responsables du contrôle des interfaces, de la correction des données et de l'interprétation et encodage des messages. Plus de détails sur l'IEEE 1451 sont inclus dans les deux premiers articles [8, 10] de cette thèse.

## 2.1.2 Applications

Une première revue de littérature sur les usages possibles du IEEE 1451 [11], publiée en 2015, montre bien l'état présent de la recherche dans ce domaine. De manière globale, aucune application n'a nécessité de modifications majeures de la norme depuis son introduction en 1997. Les travaux réalisés ont en majorité eu comme objectif principal de s'assurer l'applicabilité de la norme dans des domaines précis, afin d'ajouter au domaine un caractère générique et flexible. Pour en arriver à une intégration réussie, de nombreuses interprétations mineures se conformant toujours à la norme de base ont été proposées. Notre approche hiérarchique constitue à nos yeux la première proposition architecturale apportant une contribution substantielle à la norme en y conférant un caractère fiable. En effet, l'introduction de mesure architecturale de gestion de la redondance globale, afin d'assurer un niveau adéquat de fiabilité, est requise pour une utilisation en avionique dans le cadre d'applications critiques. Par pallier à ce manque de la norme originale, nous proposons donc dans [8] notre architecture hiérarchique permettant un niveau modulable de fiabilité. Malgré l'ajout de la fiabilité à la norme, notre architecture hiérarchique s'y conforme toujours grâce aux différentes libertés d'implémentation permises. Plus de détails et d'analyses à ce sujet suivront la présentation des 3 articles à la section discussion. Afin d'illustrer ces derniers propos, le reste de la section présentera les exemples les plus pertinents afin de faire ressortir la diversité des champs d'application et des technologies de communication utilisées pour mieux situer nos travaux.

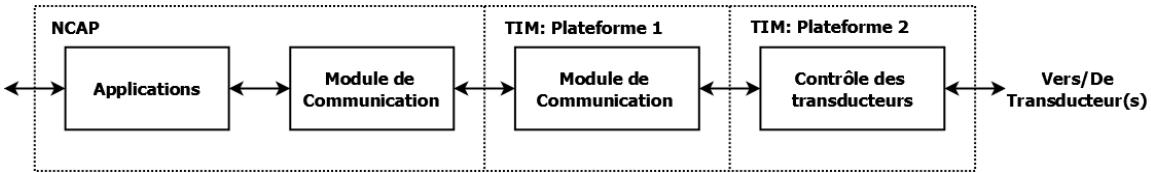

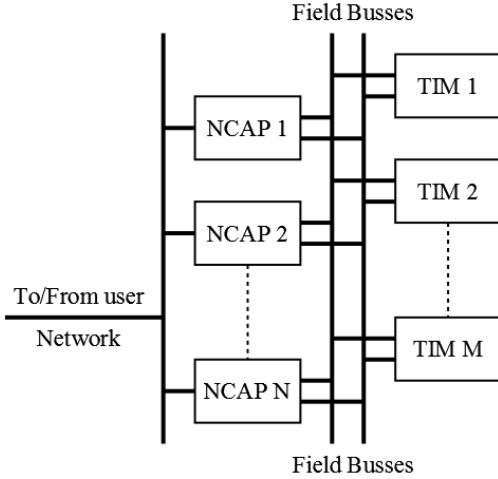

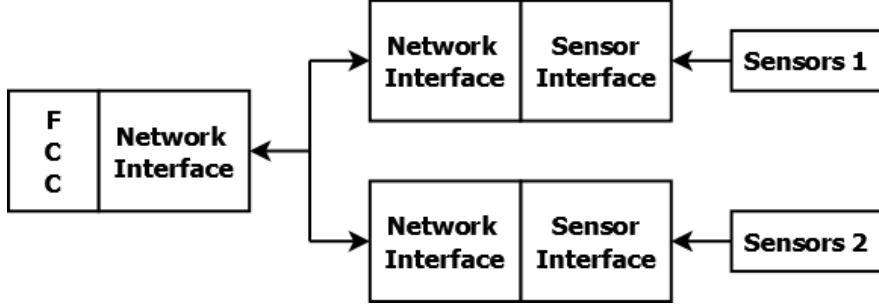

Un premier cas typique de modifications apportées au protocole IEEE 1451 pour répondre aux besoins de nouveaux domaines d'application est proposé par Grisotomi et al. [12]. Leur intégration du IEEE 1451 dans un contexte de surveillance de procédé industriel permet la diversification de l'approvisionnement et une facilité accrue d'entretien, causant une augmentation de la fiabilité et de l'efficience globale. Au niveau de la connexion entre TIM et NCAP, l'implémentation à l'aide de microcontrôleurs repose sur le protocole sans fil IEEE 802.15.4 [13] issu de la famille des « Low Rate Wireless Personal Area Network » (LR WPAN). Leur approche modulaire, scindant le TIM en deux, leur permet d'accroître la polyvalence de

l'implémentation en fonction de requis spécifiques au domaine d'exploitation. Malgré leur architecture, présentée à la Figure 2-2, l'implémentation respecte toujours la norme IEEE 1451.

Figure 2-2: Architecture réseau [12]

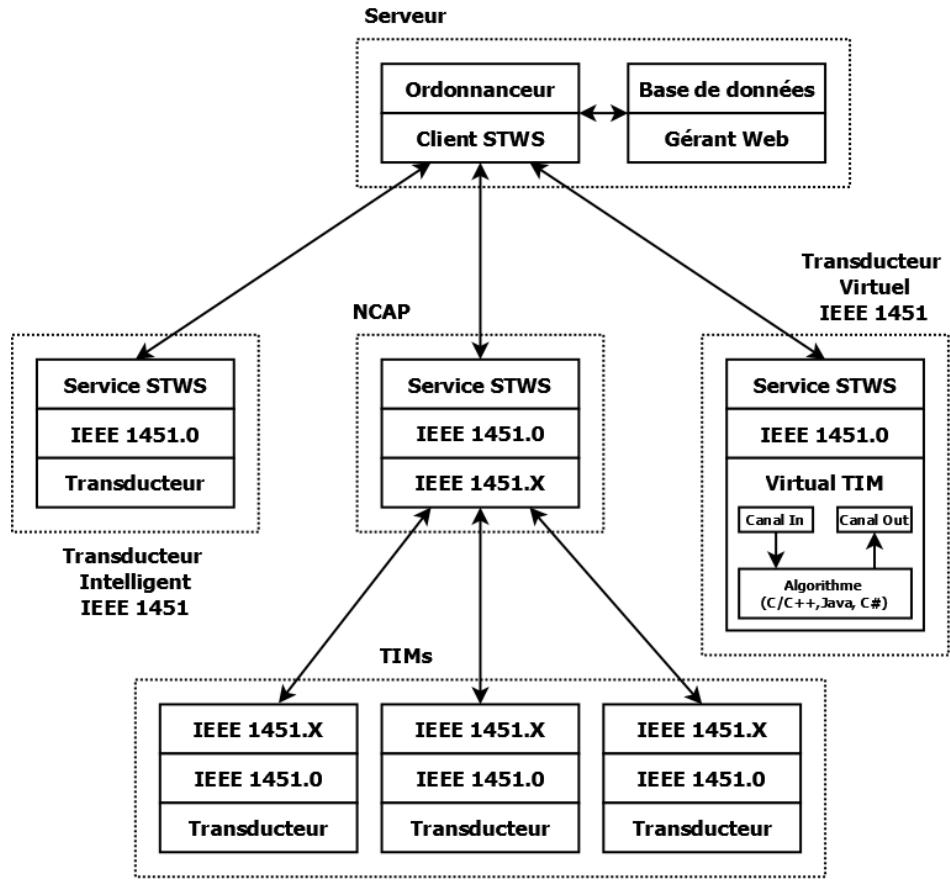

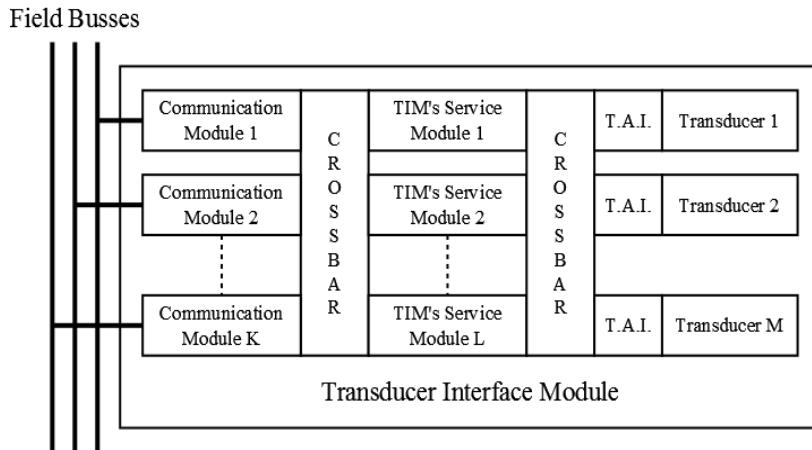

Cette séparation du TIM, n'étant pas spécifiée par la norme, leur donne la liberté de séparer physiquement en deux modules distincts le contrôle du réseau sans fil et du transducteur. Cette division du TIM a également entraîné la répartition de l'information des TEDS sur les deux plateformes, un premier pour l'adressage et la connexion au réseau et le second pour le contrôle des transducteurs. Aucune nouvelle fonctionnalité, comme de nouvelles informations à ajouter aux TEDS ou un style d'adressage différent, n'a par contre été requise. On peut noter que malgré l'introduction de cette séparation, le type d'architecture se classe parmi le style de base selon la classification introduite dans notre article. Une deuxième proposition distincte ressort du travail de Bezanic et als. [14] sur leur approche pour faciliter l'intégration de nouvelles fonctionnalités dans une architecture respectant la norme IEEE 1451. Ces nouvelles fonctionnalités sont intégrées à des transducteurs virtuels qui sont considérés pareillement aux transducteurs physiques au niveau réseau. Parallèlement à l'intégration de services web à leur implémentation IEEE 1451, Bezanic et als. [14] se servent de ce nouveau concept de transducteur virtuel pour améliorer leur design d'un système de dégivrage. L'utilisation de services web connaît présentement une croissance importante dans les domaines de surveillance, de l'environnement et des transports intelligents. L'architecture proposée par [14], présentée à la Figure 2-3, constitue donc le premier effort d'intégration du IEEE 1451 dans un système implanté à l'aide du « Web Service Description Langage » (WSDL). Le code source WSDL est compilé et programmé sur des plateformes matérielles développées autour d'un processeur embarqué ARM.

Figure 2-3: Architecture réseau [14]

Bien que le TIM virtuel possède les canaux d'entrée et de sortie, telle sa version réelle, un algorithme contenu dans le TIM virtuel traite les données entrantes et produit les données à transmettre. Dans le cas exposé par [14], un algorithme de prédiction de la formation de glace apporte des données supplémentaires au serveur de contrôle gérant l'activation des dégivreurs. Par l'entremise du réseau sans fil, le transducteur virtuel achemine des informations supplémentaires au serveur de contrôle à l'aide des données brut des capteurs. Le transducteur virtuel permet donc dans ce cas d'implémenter un algorithme au niveau des transducteurs plutôt que dans le serveur. Bien que les architectures générées respectent toujours la norme IEEE 1451, le design et l'emploi du transducteur virtuel ne sont pas balisés par la norme. Au niveau architectural, la structure obtenue peut supporter les deux types de topologies, soit celle de base et la distribuée. Le tableau suivant vient compléter l'analyse des travaux pertinents dans le domaine du IEEE 1451 à l'aide d'un résumé de leurs principales caractéristiques. Chacune des références couvre donc une intégration du IEEE 1451 dans le domaine d'application indiqué.

Tableau 2.1: Domaines d'application de la norme IEEE 1451

| Référence | Année de publication | Domaine d'application            | Méthode d'implémentation | Architecture | Protocole de communication |

|-----------|----------------------|----------------------------------|--------------------------|--------------|----------------------------|

| 12        | 2014                 | Procédé industriel               | Microcontrôleur          | Base         | IEEE 802.15.4              |

| 14        | 2015                 | Dégivrage                        | Services Web             | Distribué    | Ethernet                   |

| 15        | 2013                 | Protection de l'environnement    | SoC                      | Base         | Dédié                      |

| 16        | 2014                 | "Internet of Things" (IOT)       | Simulation Logicielle    | Distribué    | Non Applicable             |

| 17        | 2015                 | Qualité de l'eau                 | C/C++                    | Distribué    | Nordic Multic peaceiver    |

| 18        | 2014                 | Système de transport intelligent | Visioway (IP)            | Distribué    | Wi-Fi                      |

| 19        | 2014                 | Aerospace                        | Non Disponible           | Distribué    | Zigbee                     |

| 20        | 2013                 | Validation électronique          | FGPA                     | Base         | UART                       |

On peut voir qu'au cours des dernières années, le protocole IEEE 1451 a été sélectionné et implémenté avec succès dans de nombreuses nouvelles sphères d'activités. Au niveau avionique, il est important de noter que bien que les travaux de Alena et al. [15] aient été effectués pour le compte de la NASA, leur utilisation du IEEE 1451 n'était limitée qu'à la reconfiguration des modules et aux tests au sol. L'architecture développée n'était donc pas assujettie aux règles de l'avionique, mais plutôt à celle du domaine de l'instrumentation et de la programmation. Suite à cette revue extensive des travaux dans le domaine du IEEE 1451, nous pensons être en mesure d'affirmer que nous sommes les premiers chercheurs à introduire le IEEE 1451 dans le cadre d'applications critiques en avioniques grâce à notre proposition d'architecture pouvant entre autres conférer le niveau requis de fiabilité.

Au niveau de la méthode d'implémentation, on peut conclure que les approches logicielles et matérielles ont été également privilégiées. Certains [16] ont même choisi d'implémenter le réseau de contrôle des autobus d'une ville entière à l'aide d'un système de capteurs propriétaire (Visioway). Malgré toutes les applications recensées, aucun processeur spécialisé n'a été proposé jusqu'à maintenant. Bien que le type d'architecture dépende beaucoup du domaine d'application,

les architectures distribuées tendent à être plus fortement favorisées, puisqu'elles permettent la connexion d'un plus grand nombre de transducteurs afin de maximiser les capacités des ressources matérielle et logicielle. Les augmentations de bande passante dues aux protocoles supportés viennent accentuer cette situation en permettant le regroupement d'un plus grand nombre de transducteurs sous un même réseau. Les nombreux protocoles de communication en usage dans les travaux du tableau 1 montrent bien la polyvalence de la norme IEEE 1451, un de ses fondements de base. Les choix varient de protocole dédié [17] conçu pour une application unique jusqu'aux réseaux sans fils [12, 15, 16] en utilisation grandissante. Au niveau des protocoles de communication avioniques, aucune référence formelle n'a été trouvée parmi la littérature examinée. De nombreux articles font par contre référence au protocole de transmission CAN pour application non critique, mais aucune mention de l'ARINC 825 en combinaison avec le IEEE 1451 n'a été trouvée, jusqu'à la parution de notre article [8].

Globalement, nous pouvons donc conclure qu'au niveau de la recherche sur le IEEE 1451, les dernières avancées se résument principalement à de simples ajustements afin d'accommoder les particularités spécifiques de chacun des nouveaux domaines d'application considérés. Notre approche présentée dans [8] implique une évolution majeure du IEEE 1451 afin de satisfaire la fiabilité requise dans les applications critiques.

## 2.2 Design et validation de systèmes IMA

Pour commencer, une courte explication présentera l'approche classique guidant le design et la validation de systèmes avioniques depuis l'introduction des IMA. Les références composant cette section reflète donc les derniers avancements réalisés et les tendances du domaine.

### 2.2.1 Approche classique

De nos jours, la méthodologie classique de design de systèmes IMA reprend les techniques utilisées pour les paradigmes de développement antérieurs applicables aux systèmes avioniques en incorporant les nouvelles particularités des architectures IMA. En raison de la nature configurable des architectures IMA, les différentes ressources doivent être assignées aux multiples fonctionnalités selon le temps alloué, la quantité de mémoire requise, les entrées/sorties des réseaux de communication et de l'interfaçage avec les périphériques externes. L'allocation des ressources s'effectue habituellement à l'aide de tables de configuration précisant les

différentes propriétés à respecter pour chacune des fonctions à implémenter. Ces propriétés permettent la modification individuelle d'une fonction sans affecter le système dans son entier. La définition de ces propriétés sert également de base pour les nombreux processus de certification. Globalement, la méthode de design IMA suit les étapes suivantes :

1. Définition des fonctionnalités desservies par le système;

- Identification des besoins en entrées/sorties et des périphériques externes tels que capteurs et actuateurs;

2. Définition des éléments de traitement requis pour l'implémentation de chacune des fonctions;

- Proposition d'une architecture satisfaisant les requis de fiabilité et de performances;

3. Définition des besoins en ressources pour chacune des fonctionnalités;

4. Définition des échanges entre les éléments de traitement et les fonctionnalités;

5. Allocation des éléments de traitement à la plateforme physique.

L'allocation prédéterminée des ressources est finalement communiquée à la plateforme physique à l'aide d'un fichier de configuration. Les configurations obtenues devraient donc s'assurer du respect des différentes propriétés énoncées lors de la première étape. Le processus de design de systèmes avioniques est également sujet à de nombreux requis émanant de réglementations en vigueur et des spécifications. Afin de bien montrer la quantité imposante requise d'analyses de toutes sortes, la Figure 2-4 indique les relations entre les principales normes à respecter. Les guides « Avionics Recommended Practices » (ARP) sont publiés par la Society of Automotive Engineers (SAE) depuis 1989 et leur respect est toujours obligatoire à ce jour.

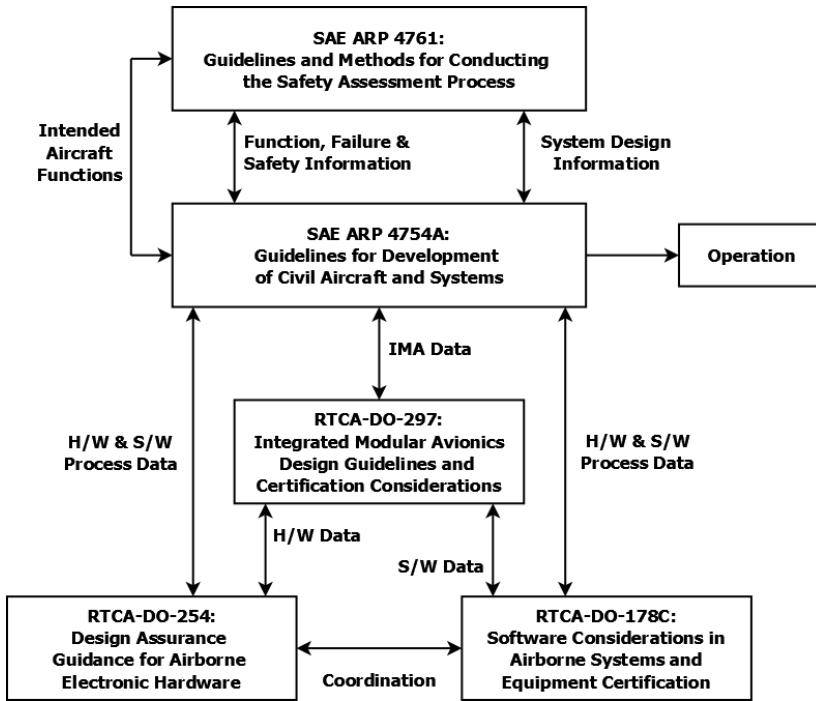

Figure 2-4: Relation entre les principales normes avioniques [1]

Le guide ARP 4754A contient les détails globaux du processus de design d'un système avionique en faisant, entre autres, le lien entre les différents processus et la documentation, tel qu'ilustré à la Figure 2-4. Le document ARP 4761 détaille, quant à lui, toutes les cibles et analyses de fiabilité, incluant les « Fault Tree Analysis » (FTA), les Failure Modes and Effect Analysis » (FMEA) et les analyses de Markov. Ces derniers outils ont tous été utilisés par les membres de l'équipe AVIO 402 afin d'assurer le respect des normes avioniques dans le design et la validation de notre prototype. Ces analyses font également l'objet de recherches tentant entre autres de faciliter leur application sur des réseaux [18].

De manière plus spécifique aux systèmes IMA, la norme DO-297 en présente les fondements en précisant les lignes directrices permettant son développement et son intégration. Pour terminer, les deux derniers guides décrivent en détail les processus de certification requis. Le document DO-178 cible la programmation d'applications logicielles, tandis que le développement matériel est visé par le guide DO 254. Plusieurs autres normes peuvent venir s'ajouter à celle présente dans la figure 9, telles les normes ARINC qui varient en fonction des choix de protocoles et d'implémentations. Les contraintes utilisées dans le cadre de ce projet proviennent donc de ces

documents. Leur conformité a également été vérifiée par différents intervenants du domaine avionique pour un respect des conditions réelles d'exécution.

## 2.2.2 Approches originales

Afin de satisfaire tous les concepts et règles contenues dans les derniers documents présentés, de nombreux travaux ont cherché à proposer des variantes ou des améliorations des processus établis. Les sections suivantes viennent brosser un portrait global des travaux les plus récents. Chaque section est consacrée à une des deux classes d'approches de design et validation, soit l'approche basée sur la modélisation logicielle et les méthodes reposant sur l'utilisation directe de plateforme matérielle. Les particularités des deux approches principales recensées seront brièvement décrites afin de mieux situer les travaux pertinents dans le même champ d'activités depuis la parution de notre deuxième article. [10] Les travaux présentés dans cette thèse viendront donc appuyer les références incluses dans cette seconde publication.

### 2.2.2.1 Modélisation logicielle