**Titre:** Synthèse et description de circuits numériques au niveau des transferts synchronisés par les données

Title: Transfers synchronized by data

**Auteur:** Marc-André Daigneault

Author:

**Date:** 2015

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Daigneault, M.-A. (2015). Synthèse et description de circuits numériques au niveau des transferts synchronisés par les données [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/2031/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/2031/>

PolyPublie URL:

**Directeurs de recherche:** Jean Pierre David, & Jean Mahseredjian

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

SYNTHÈSE ET DESCRIPTION DE CIRCUITS NUMÉRIQUES AU NIVEAU DES

TRANSFERTS SYNCHRONISÉS PAR LES DONNÉES

MARC-ANDRÉ DAIGNEAULT

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIÆ DOCTOR

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2015

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée :

SYNTHÈSE ET DESCRIPTION DE CIRCUITS NUMÉRIQUES AU NIVEAU DES

TRANSFERTS SYNCHRONISÉS PAR LES DONNÉES

présentée par : DAIGNEAULT Marc-André

en vue de l'obtention du diplôme de : Philosophiæ Doctor

a été dûment acceptée par le jury d'examen constitué de :

M. SAVARIA Yvon, Ph. D., président

M. DAVID Jean Pierre, Ph. D., membre et directeur de recherche

M. MAHSEREDJIAN Jean, Ph. D., membre et codirecteur de recherche

M. BOIS Guy, Ph. D., membre

M. BLAQUIÈRE Yves, Ph. D., membre externe

## DÉDICACE

*"Tout le monde tient le beau pour le beau,

c'est en cela que réside sa laideur.*

*Tout le monde tient le bien pour le bien,

c'est en cela que réside son mal."*

*- Lao-tseu, Tao Tö King*

*"Where ignorance is our master,

there is no possibility of real peace."*

*- Dalaï Lama XIV*

## REMERCIEMENTS

Cette thèse de Doctorat représente pour moi l'accomplissement et l'aboutissement d'un long parcours académique, qui m'a parfois semblé n'avoir de fin! Un long parcours qui hélas je dois l'admettre n'a commencé à me stimuler qu'à partir de la maîtrise. Néanmoins je ne saurais manquer de reconnaître que l'accomplissement de cette présente étape de ma vie, que je suis sur le point de compléter, est sans contredit le fruit de l'accomplissement de toutes les étapes passées, différentes étapes qui m'ont permis d'arriver à celle-ci. Cet accomplissement n'est pas que le miens, il est également celui de tous ceux et celles qui m'ont accompagné, supporté, inspiré, et permis de grandir tout au long de ma vie. Sans eux, il m'est difficile de croire que je serais devenu la personne que je suis aujourd'hui, que j'aurais pu me rendre aussi loin dans mon parcours, et de mener à terme cette longue aventure qu'aura été pour moi les études supérieures à l'École Polytechnique de Montréal. C'est donc avec grand plaisir et humilité que je tiens ici à remercier tous ceux et celles qui ont contribué à cette grande réalisation personnelle.

J'aimerais tout d'abord remercier ma proche famille, René, Sylvie, Véronique, ainsi que Michel, Jean-Philippe, Marc-André, et Jean-François, auprès de qui j'ai eu la chance inouïe de grandir tout au long de ma vie. Vous avez sans contredit constitué un point d'ancrage, et un phare, d'une valeur inestimable pour un petit navire qui est souvent parti à la dérive. Les mots me manqueraient ici pour exprimer toute la reconnaissance que je vous dois. Je tiens également à remercier la grande famille, mes grands-parents, oncles et tantes, ainsi que mes cousins et cousines qui ont laissé en moi une empreinte indélébile de par leur chaleur, leurs valeurs, leur humour, et leur simplicité. Je ne saurais tous les mentionner tant la liste est longue. Je garderai toujours un souvenir intarissable de combien j'ai ri lors des nombreux soupers et parties de cartes les dimanches chez les Daigneault tout au long de ma jeunesse. Roger, André, et Claire, merci. Une attention toute spéciale aussi à ma marraine et mon parrain, Claudette et Fernand, pour tous les moments passés alors que vous nous gardiez de jour ma soeur et moi pendant notre petite enfance.

J'aimerais également remercier les peu nombreuses, mais combien tant exceptionnelles compagnes amoureuses avec qui j'ai eu la chance de partager des moments privilégiés de ma vie. Tout particulièrement Isabelle, une femme au coeur d'une générosité rarement égalée, qui est sans aucun doute à ce jour celle qui m'a le plus fait grandir en tant qu'homme.

Je ne saurais manquer de remercier tous mes amis, de la petite école à aujourd'hui, avec qui j'ai passé une grande partie des plus beaux moments de ma vie. J'ai tant ri auprès de vous,

et je me compte si chanceux d'avoir pu grandir auprès et avec vous. En quelque sorte vous n'avez été pour moi rien de moins qu'une deuxième famille.

Je tiens également à remercier tous les collègues de laboratoire avec qui j'ai partagé l'espace unique du local M-5028 pendant toutes mes études supérieures : David, Etienne B., Patrick, Mathieu, Tarek, Jonas, Walid, Adrien, Nasreddine, Matthieu, Hémin, et Federico, même si je n'y ai sans doute pas été présent autant que je l'aurais dû. Merci pour tous les échanges, partages, et débats que nous avons eu, et pour m'avoir fait beaucoup rire bien sur, en plus d'avoir contribué à m'offrir une ouverture toute particulière sur le monde et des réalités d'ailleurs. Il m'est difficile d'espérer retrouver un jour dans un si petit espace autant de personnes si exceptionnelles. Je tiens également à remercier les nombreux collègues et coéquipiers avec qui j'ai eu la chance de travailler tout au long de mes études, tout spécialement Yan et Etienne L. de l'équipe *Dreamwafer*, que j'ai eu la chance de rencontrer avant de débuter ma maîtrise.

Je tiens aussi à remercier tous les étudiants, de l'École Polytechnique de Montréal et de l'UQAM, à qui j'ai eu le privilège d'enseigner pour les cours et laboratoires de circuits logiques, de prototypage rapide de systèmes numériques, ainsi que de microcontrôleurs et applications, pendant toute la durée de mes études supérieures. De ceux qui m'ont donné le plus de troubles à ceux qui ont su me surprendre fois après fois alors que je mettais souvent la barre de mes évaluations assez haute. J'espère que vous ne m'en voulez pas trop, mais en face d'un tel potentiel et d'un tel talent, je ne me serais jamais pardonné de faire une évaluation trop facile. J'ai toujours cru que l'université devait offrir un milieu propice à la découverte de nos forces et faiblesses, et nous permettant de nous dépasser et de trouver nos limites. Car nos limites sont souvent beaucoup plus loin que nous le pensons, et il m'a toujours été d'une grande importance de contribuer à vous offrir un contexte vous permettant de les découvrir. Et de mémoire, il y en avait généralement toujours au moins un dans le groupe qui arrivait à me démontrer que je n'avais pas trop exagéré ! Dans tous les cas, j'espère avoir su vous faire grandir, je peux vous dire en retour que vous m'avez permis de grandir et que vous avez su, de par votre curiosité, votre détermination, et vos efforts, à m'inspirer. Une attention toute spéciale à l'intention des étudiants du dernier groupe de cours de circuits logiques à qui j'ai eu l'honneur d'enseigner pour les applaudissements à la fin des derniers cours et l'ovation de fin de trimestre, j'en suis toujours tout ému encore aujourd'hui quand je me remémore ces moments. Merci à tous.

Je tiens également à remercier mon directeur de recherche, le professeur David, pour avoir encadré et supervisé mes travaux aux études supérieures à l'École Polytechnique de Montréal. Jean Pierre a su m'inspirer, et me faire grandir non seulement sur le plan professionnel mais également personnel. Je lui serai toujours reconnaissant pour le support et son écoute des

plus précieuse dans certains des moments les plus difficiles de ma vie. Il a su m'amener plus loin, et me faire découvrir une passion pour la recherche en science appliquée dans les domaines de la conception des circuits numériques et de la science informatique, ainsi que pour l'enseignement. C'eut été un honneur pour moi de passer une des périodes les plus stimulantes de ma vie sous sa supervision.

Je tiens également à remercier nombre de professeurs qui m'ont enseigné ou avec qui j'ai eu la chance de travailler durant mon long parcours. De part leur rigueur intellectuelle, leur passion, leur professionnalisme, et leur niveau d'expertise, ils ont été pour moi de grandes sources d'inspiration. J'en oublie sans doute quelques-uns, mais je pense notamment aux professeurs Yves Audet, Yves Blaquier, Guy Bois, Jean-Jules Brault, Jean Pierre David, Robert Guardo, Pierre Langlois, Jean-Jacques Laurin, Mario Lefebvre, Jean Mahseredjian, Christian Morin, Yvon Savaria, et Mohamad Sawan. J'en profite également pour remercier l'administration de l'École Polytechnique de Montréal et son personnel pour avoir su réunir des professeurs de si grande qualité, et de m'avoir permis d'étudier dans un environnement aussi stimulant. C'eut été pour moi un honneur de pouvoir réaliser mon parcours dans cet établissement de premier plan au niveau de la recherche scientifique en ingénierie au Canada, et de calibre international.

Je tiens également à remercier le Conseil de Recherche en Science Naturelle et de Génie (CRSNG) du gouvernement du Canada pour m'avoir octroyé une bourse d'études de 3 ans, qui a été pour moi un signal clair que je me devais de tenter cette grande aventure, et de pousser mes études plus loin.

Je tiens en tout dernier lieu à témoigner de ma gratitude envers mon employeur actuel, Synopsys Inc., pour m'avoir invité à leurs bureaux pour une entrevue cet été alors je terminais le premier jet de la rédaction de cette thèse, ainsi qu'à toute l'équipe pour l'accueil chaleureux auquel j'ai eu droit à mon arrivée suivant l'acceptation de l'offre d'emploi qui m'avait été faite. Mon directeur de recherche s'était fait rassurant vers la fin de cette thèse comme quoi j'étais attendu à la fin de mes études, mais je n'en étais pas moins des plus heureux lorsque cette affirmation eut été démontrée par un exemple réel. La réalisation de cette thèse de doctorat a été pour moi une des aventures les plus éprouvante à laquelle je me suis prêté dans ma vie, et a certes mis ma détermination à rude épreuve. Dans ce long périple où les limites sont infinies et la destination inconnue, je me suis souvent remis en question, et pendant une longue période l'horizon lointain me paraissait bien sombre. Cette aventure me fit souvent penser au récit de la traversée de l'Atlantique en kayak, seul, sans assistance et sans escale, par Mathieu Morverand, que nous avions lu une fois à l'école secondaire. C'est aujourd'hui avec grande humilité mais non sans fierté que je porte un regard derrière moi

sur ce que j'ai réalisé pendant cette étape déterminante de ma vie. Et c'est avec le plus grand enthousiasme que j'en entreprends une nouvelle, en joignant l'équipe du groupe de vérification chez Synopsys, un leader mondial dans le domaine des outils de conception et de vérification de circuits intégrés. Une nouvelle étape, rendue possible par toutes celles qui lui ont précédée.

## RÉSUMÉ

Au-delà des processeurs d'instructions multi-coeurs, le monde du traitement numérique haute performance moderne est également caractérisé par l'utilisation de circuits spécifiques à un domaine d'application implémentés au moyen de circuits programmables FPGA (réseau de portes programmables *in situ*). Les FPGA représentent des candidats intéressants à la réalisation de calculs haute-performances pour différentes raisons. D'une part, le nombre importants de blocs de propriétés intellectuelles gravés en dur sur ces puces (processeurs, mémoires, unités de traitement de signal numérique) réduit l'écart qui les sépare des circuits intégrés dédiés en termes de ressources disponibles. Un écart qui s'explique par le haut niveau de configurabilité offert par le circuit programmable, une capacité pour laquelle un grand nombre de ressources doit être dédié sans être utilisé par le circuit programmé. Néanmoins dans un contexte où souvent plus de transistors sont disponibles qu'on puisse en utiliser, le coût associé à la configurabilité s'en trouve d'autant réduit.

De par leur capacité à être reconfigurés complètement ou partiellement, les FPGAs modernes, tout comme les processeurs d'instructions, offrent la flexibilité requise pour supporter un grand nombre d'applications. Néanmoins, contrairement aux processeurs d'instructions qui peuvent être programmés avec différents langages de programmation haut-niveau (Java, C#, C/C++, MPI, OpenMP, OpenCL), la programmation d'un FPGA requiert la spécification d'un circuit numérique, ce qui représente un obstacle majeur à leur plus grande adoption. La description de circuits numériques est généralement exprimée au moyen d'un langage concurrent pour lequel le niveau d'abstraction se situe au niveau des transferts entre registres (RTL), tels les langages VHDL et Verilog. Pour une application donnée, la réalisation d'un circuit numérique spécialisé requiert typiquement un effort de conception significativement plus grand qu'une réalisation logicielle. Il existe aujourd'hui différents outils académiques et commerciaux permettant la synthèse haut-niveau de circuits numériques en partant de descriptions C/C++/SystemC, et plus récemment OpenCL. Cependant, selon l'application considérée, ces outils ne permettent pas toujours d'obtenir des performances comparables à celles qui peuvent être obtenues avec une description RTL produite manuellement.

On s'intéresse dans ce travail à un outil de synthèse de niveau intermédiaire offrant un compromis entre les performances atteignables au moyen d'une méthode de conception RTL, ainsi que les temps de conception que permet la synthèse à haut-niveau. On considère ainsi la synthèse de circuits numériques partant d'un langage supportant la description de machines à états algorithmiques (ASM) contrôlant des connexions entre des sources et des puits avec

des interfaces de synchronisation prédéfinies. Ces interfaces sont similaires aux interfaces à flot de données *AXI4-Stream* et *Avalon-Streaming*, disposant de signaux de synchronisation de type prêt-à-envoyer/prêt-à-recevoir pour supporter la synchronisation des transferts à la source et à la destination.

Le langage d'entrée considéré est basé sur le langage de description de circuits CASM (*Channel-based Algorithmic State Machine*) existant. Le langage CASM permet la description de connexions *bloquantes*, qui bloquent le flot de contrôle d'une ASM (*Algorithmic State Machine*) tant qu'un transfert de donnée n'a pas eu lieu entre la source et le puits correspondants. Ce langage permet ainsi la description de circuits numériques comme un ensemble de processus concurrents activant dynamiquement des transferts synchronisés par les données, et ce en faisant abstraction du détail de la logique de contrôle requise pour supporter cette synchronisation. Néanmoins, l'interconnexion de sources et de puits dans différentes topologies peut induire des boucles combinatoires en termes des signaux de synchronisation des interfaces à flot de données. De telles relations cycliques sont problématiques d'une part parce qu'elles sont associées à des comportements indéterminés, et d'autre part parce qu'elles mènent à des circuits qui ne sont pas synthétisables ou qui n'ont pas le comportement désiré. La présence de telles boucles combinatoires peut s'expliquer par la présence de relations combinatoires entre les entrées et sorties de synchronisation des différents composants interconnectés. Nous proposons une approche automatisée au niveau fonctionnel (logique) capable de transformer les boucles combinatoires en circuits acycliques synthétisables. Ceci est essentiellement réalisé en ne permettant que les états stables de la boucle correspondants à un plus grand nombre de transferts de données complétés à chaque cycle. Nous proposons également d'augmenter la syntaxe de base du langage CASM avec une syntaxe supportant la description de règles d'autorisation des transferts de données, ainsi que de nouveaux opérateurs de connexions avancés.

La méthodologie de synthèse de circuits numériques présentée dans ce travail a été automatisée au moyen d'un compilateur décrit en langage Java. Pour évaluer la viabilité de la méthode de synthèse à niveau intermédiaire proposée, celle-ci a été appliquée à un certain nombre d'applications, notamment dans le domaine du traitement numérique avec des opérateur pipelinés utilisant une représentation des nombres en virgule-flottante. La description de circuits avec le langage de description au niveau des transferts synchronisés par les données présenté offre au développeur un niveau de contrôle sur l'architecture qui se rapproche du niveau RTL, tout en permettant d'abstraire différentes difficultés inhérentes à l'interconnexion d'interfaces synchronisées par les données dans différentes topologies. La méthodologie proposée permet une description plus concise des comportements désirés, et l'automatisation de différentes tâches liées à l'implémentation de la logique de contrôle vient également réduire

les sources d'erreurs possibles.

## ABSTRACT

Beyond modern multi/many-cores processors, the world of computing is also characterized by the use of dedicated circuits implemented on Field-Programmable Gate-Arrays (FPGAs). For many reasons, modern FPGAs have become interesting targets for high-performance computing applications. On one hand, their integration of considerable amounts of IP blocks (processors, memories, DSPs) has contributed to reduce the resource/performance gap that exist with Application Specific Integrated Devices (ASICs). A gap that is easily explained by the high-level of reconfigurability that these devices provide, a feature for which a considerable amount of resources (transistors) must be dedicated. Nevertheless, in a context where often more transistors are often available than it is needed or required, the impact of such a cost is less important.

The ability to reconfigure completely or partially modern FPGAs further offer the flexibility required to support multiple different applications over time, similarly to instruction processors. However, while instruction processors can be programmed with different high abstraction level software programming languages (Java, C#, C/C++, MPI, OpenMP, OpenCL), FPGA programming typically requires the specification of a hardware design, which is a major obstacle to their widespread use. The description of a hardware design is generally done at the register-transfer level (RTL), using hardware description languages (HDLs) such as VHDL and Verilog. For a given application, the design and verification of a dedicated circuit requires a significantly more important effort than a software implementation. Nowadays, numerous commercial and academic tools allow the high-level synthesis of hardware designs starting from a software description using programming languages such as C/C++/SystemC, and more recently OpenCL. Nevertheless, depending on the application considered, at current state of the art, these tools do not allow performances that matches those which can be obtained through hand-made RTL designs.

In this work, we consider an intermediate-level synthesis methodology offering a compromise between the performances and design times that can be obtained with RTL and high-level synthesis methodologies. We consider an input hardware description language that allows the description of algorithmic state machines (ASMs) handling connections between sources and sinks with predefined streaming interfaces. These interfaces are similar AXI4-Streaming and Avalon-Streaming interfaces, featuring ready-to-send/ready-to-receive synchronisation signals.

The intermediate-level hardware description language considered is based on the existing

CASM language. CASM allows the description of blocking connections, which can implicitly stall the control flow of an ASM as long as a data transfer hasn't occurred over the specified blocking connection. The CASM language allows the description of a hardware design as a collection of ASMs handling dynamic data-synchronized connections, in a way that abstracts the details of the low-level control logic required to support the adequate synchronization of data transfers. However, the interconnection of different sources and sinks in various topologies can induce combinational loops (cyclic relations) in terms of the synchronization signals of the streaming interfaces. Such combinational loops are problematic because they are associated to indeterminate behaviors, and lead to circuits that are not synthesizable, or that do not have the desired behavior. The presence of such combinational loops can be explained by the presence of combinational relations between the synchronization inputs and outputs of the interconnected devices. In this work, we propose an automated approach at the functional (logic) level that is able to transform such combinational loops into acyclic combinational functions, which can then be synthesized into digital designs. This is achieved by allowing only the stable states that correspond to the largest amount of completed data transfers, for any given clock cycle. We also propose to augment the syntax of the CASM language such as to allow the specification of data transfer authorization rules, as well as the addition of advanced connection operators.

The automated synthesis methodology proposed in this thesis has been implemented as part of a compiler developed using the Java programming language. In order to evaluate the applicability of the proposed intermediate-level synthesis methodology, the compiler has been applied to the synthesis of various applications in the field of floating-point computing. The description of hardware designs with our intermediate-level hardware description language provides the design with a level of control that is close to that of RTL, while abstracting the complexities inherent to the interconnection of streaming interfaces in different topologies. The proposed design method allows for a more concise description of the desired behavior, while automating the various tasks associated to the implementation of the low-level synchronisation logic, reducing design and verification times.

## TABLE DES MATIÈRES

|                                                                                    |      |

|------------------------------------------------------------------------------------|------|

| DÉDICACE . . . . .                                                                 | iii  |

| REMERCIEMENTS . . . . .                                                            | iv   |

| RÉSUMÉ . . . . .                                                                   | viii |

| ABSTRACT . . . . .                                                                 | xi   |

| TABLE DES MATIÈRES . . . . .                                                       | xiii |

| LISTE DES TABLEAUX . . . . .                                                       | xvi  |

| LISTE DES FIGURES . . . . .                                                        | xvii |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                                         | xix  |

| <br>CHAPITRE 1 INTRODUCTION . . . . .                                              | 1    |

| 1.1 Problématique . . . . .                                                        | 2    |

| 1.2 Concepts fondamentaux . . . . .                                                | 2    |

| 1.3 Objectifs de recherche . . . . .                                               | 4    |

| 1.4 Contributions . . . . .                                                        | 6    |

| 1.5 Plan de la thèse . . . . .                                                     | 8    |

| <br>CHAPITRE 2 REVUE DE LITTÉRATURE . . . . .                                      | 9    |

| 2.1 Introduction . . . . .                                                         | 9    |

| 2.2 Description comportementale et synthèse haut-niveau . . . . .                  | 12   |

| 2.2.1 Outils de synthèse haut-niveau C/C++/SystemC . . . . .                       | 15   |

| 2.2.2 Synthèse haut-niveau OpenCL . . . . .                                        | 17   |

| 2.3 Description et synthèse de circuits numériques au-delà du niveau RTL . . . . . | 18   |

| 2.3.1 Bluespec SystemVerilog . . . . .                                             | 18   |

| 2.3.2 Maxeler Compiler . . . . .                                                   | 19   |

| 2.3.3 Langages synchrones . . . . .                                                | 19   |

| 2.3.4 Machines séquentielles algorithmiques . . . . .                              | 20   |

| 2.3.5 Langage de niveau intermédiaire CASM . . . . .                               | 21   |

| 2.4 Conclusion . . . . .                                                           | 22   |

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| CHAPITRE 3 DESCRIPTION DE CIRCUITS AVEC LE LANGAGE CASM+ . . . . .          | 24 |

| 3.1 Introduction . . . . .                                                  | 24 |

| 3.2 Règles d'autorisation de transferts de données . . . . .                | 24 |

| 3.3 Opérateurs de connexion différée . . . . .                              | 25 |

| 3.3.1 Motivation . . . . .                                                  | 26 |

| 3.3.2 Sémantique . . . . .                                                  | 26 |

| 3.3.3 Ordonnancement . . . . .                                              | 30 |

| 3.3.4 Transformation . . . . .                                              | 30 |

| 3.4 Opérateurs de connexion sur réseau d'interconnexions pipeliné . . . . . | 33 |

| 3.4.1 Motivation . . . . .                                                  | 34 |

| 3.4.2 Sémantique . . . . .                                                  | 34 |

| 3.4.3 Ordonnancement . . . . .                                              | 34 |

| 3.4.4 Transformation . . . . .                                              | 35 |

| 3.5 Conclusion . . . . .                                                    | 36 |

| CHAPITRE 4 SYNTHÈSE AUTOMATISÉE DES DESCRIPTIONS CASM+ . . . . .            | 38 |

| 4.1 Introduction . . . . .                                                  | 38 |

| 4.2 Problématique . . . . .                                                 | 40 |

| 4.2.1 Dépendances combinatoires structurelles . . . . .                     | 40 |

| 4.2.2 Relations combinatoires cycliques . . . . .                           | 42 |

| 4.3 Logique de synchronisation des transferts . . . . .                     | 43 |

| 4.4 Analyse de stabilité . . . . .                                          | 45 |

| 4.4.1 Recherche d'un ensemble de points de rétroaction . . . . .            | 45 |

| 4.4.2 Contrainte de stabilité . . . . .                                     | 46 |

| 4.4.3 Mono- et Multi-stabilité . . . . .                                    | 47 |

| 4.5 Stabilisation des relations combinatoires cycliques . . . . .           | 48 |

| 4.5.1 Méthode I . . . . .                                                   | 50 |

| 4.5.2 Méthode II . . . . .                                                  | 50 |

| 4.6 Génération de fonctions combinatoires acycliques . . . . .              | 51 |

| 4.7 Conclusion . . . . .                                                    | 52 |

| CHAPITRE 5 APPLICATION À LA CONCEPTION DE CIRCUITS . . . . .                | 54 |

| 5.1 Introduction . . . . .                                                  | 54 |

| 5.2 Tri de données rapide . . . . .                                         | 54 |

| 5.2.1 Algorithme . . . . .                                                  | 54 |

| 5.2.2 Conception . . . . .                                                  | 55 |

| 5.2.3 Résultats de synthèse et d'implémentation . . . . .                   | 55 |

|                                    |                                                                        |    |

|------------------------------------|------------------------------------------------------------------------|----|

| 5.2.4                              | Discussion . . . . .                                                   | 56 |

| 5.3                                | Accumulateur pipeliné . . . . .                                        | 57 |

| 5.3.1                              | Conception . . . . .                                                   | 57 |

| 5.3.2                              | Description sans opérateur de connexion différée . . . . .             | 58 |

| 5.3.3                              | Description avec opérateurs de connexions différée . . . . .           | 59 |

| 5.3.4                              | Résultats de synthèse et d'implémentation . . . . .                    | 59 |

| 5.3.5                              | Discussion . . . . .                                                   | 62 |

| 5.4                                | Produit matriciel . . . . .                                            | 63 |

| 5.4.1                              | Algorithme . . . . .                                                   | 63 |

| 5.4.2                              | Conception . . . . .                                                   | 63 |

| 5.4.3                              | Résultats de synthèse et d'implémentation . . . . .                    | 67 |

| 5.4.4                              | Discussion . . . . .                                                   | 68 |

| 5.5                                | Élimination Gaussienne . . . . .                                       | 71 |

| 5.5.1                              | Algorithme . . . . .                                                   | 71 |

| 5.5.2                              | Conception . . . . .                                                   | 72 |

| 5.5.3                              | Résultats de synthèse et d'implémentation . . . . .                    | 75 |

| 5.5.4                              | Discussion . . . . .                                                   | 78 |

| 5.6                                | Inversion de matrices . . . . .                                        | 80 |

| 5.6.1                              | Algorithme . . . . .                                                   | 80 |

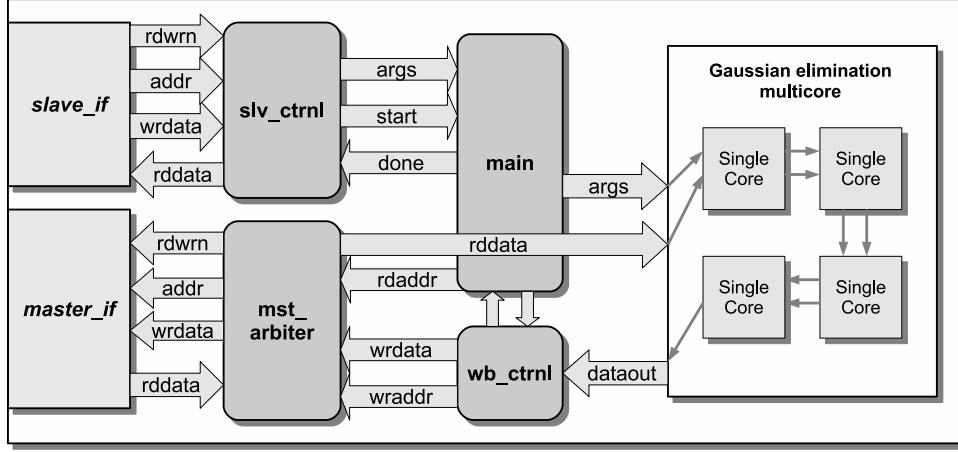

| 5.6.2                              | Conception . . . . .                                                   | 81 |

| 5.6.3                              | Résultats de synthèse et d'implémentation . . . . .                    | 82 |

| 5.6.4                              | Temps d'exécutions . . . . .                                           | 83 |

| 5.6.5                              | Discussion . . . . .                                                   | 83 |

| 5.7                                | Conclusion . . . . .                                                   | 86 |

| CHAPITRE 6 CONCLUSION . . . . .    |                                                                        | 87 |

| 6.1                                | Synthèse des travaux . . . . .                                         | 87 |

| 6.2                                | Comparaison avec l'état de l'art . . . . .                             | 89 |

| 6.3                                | Limitations de la solution proposée et améliorations futures . . . . . | 92 |

| PUBLICATIONS DE L'AUTEUR . . . . . |                                                                        | 94 |

| RÉFÉRENCES . . . . .               |                                                                        | 96 |

## LISTE DES TABLEAUX

|              |                                                                              |    |

|--------------|------------------------------------------------------------------------------|----|

| Tableau 3.1  | Attributs de connexions . . . . .                                            | 25 |

| Tableau 4.1  | Table de vérité de la contrainte de stabilité de la Figure 4.9 . . . . .     | 49 |

| Tableau 4.2  | Table de vérité de la contrainte de stabilité après stabilisation . . . . .  | 51 |

| Tableau 4.3  | Table de vérité de la fonction <i>add0.out.rtr</i> résolue . . . . .         | 52 |

| Tableau 5.1  | Exécution des implémentations simple et à pipeline fonctionnel. . . . .      | 56 |

| Tableau 5.2  | Utilisation des ressources pour les deux implémentations. . . . .            | 57 |

| Tableau 5.3  | Résultats de synthèse de l'accumulateur sur un FPGA Virtex-5 . . . . .       | 62 |

| Tableau 5.4  | Utilisation des ressources pour le produit matriciel (Stratix-III) . . . . . | 69 |

| Tableau 5.5  | Utilisation des ressources pour le produit matriciel (Virtex-5) . . . . .    | 69 |

| Tableau 5.6  | Performances pour le produit matriciel sur FPGA. . . . .                     | 69 |

| Tableau 5.7  | Comparaison d'implémentations dédiées au produit matriciel. . . . .          | 70 |

| Tableau 5.8  | Utilisation des ressources pour un unité de type-I (Stratix-V) . . . . .     | 76 |

| Tableau 5.9  | Utilisation des ressources pour l'accélérateur type-I (Stratix-V) . . . . .  | 76 |

| Tableau 5.10 | Utilisation des ressources pour l'accélérateur type-I (Virtex-5) . . . . .   | 76 |

| Tableau 5.11 | Efficacité des calculs d'un unité de traitement(type-I) . . . . .            | 77 |

| Tableau 5.12 | Utilisation des ressources pour un unité de type-II (Stratix-V) . . . . .    | 77 |

| Tableau 5.13 | Utilisation des ressources pour l'accélérateur de type-II (Stratix-V) .      | 78 |

| Tableau 5.14 | Utilisation des ressources pour l'accélérateur de type-II (Virtex-5) .       | 78 |

| Tableau 5.15 | Efficacité des calculs d'un unité de traitement (type-II) . . . . .          | 78 |

| Tableau 5.16 | Comparaison des unités de traitement (Virtex-5) . . . . .                    | 79 |

| Tableau 5.17 | Comparaison avec un outil de synthèse C . . . . .                            | 80 |

| Tableau 5.18 | Résultats d'implémentation en simple précision (Virtex-5) . . . . .          | 83 |

| Tableau 5.19 | Temps d'exécution (4 coeurs de traitement) . . . . .                         | 83 |

| Tableau 5.20 | Comparaison des designs dédiés pour l'inversion de matrices . . . . .        | 84 |

| Tableau 5.21 | Comparaison contrôle vs. chemin de données . . . . .                         | 85 |

## LISTE DES FIGURES

|             |                                                                             |    |

|-------------|-----------------------------------------------------------------------------|----|

| Figure 1.1  | Interconnexion de sources et de puits synchronisés par les données. . . . . | 4  |

| Figure 1.2  | Interconnexion produisant une relation combinatoire cyclique. . . . .       | 6  |

| Figure 2.1  | Niveaux d'abstractions pour la conception de circuits numériques. . . . .   | 10 |

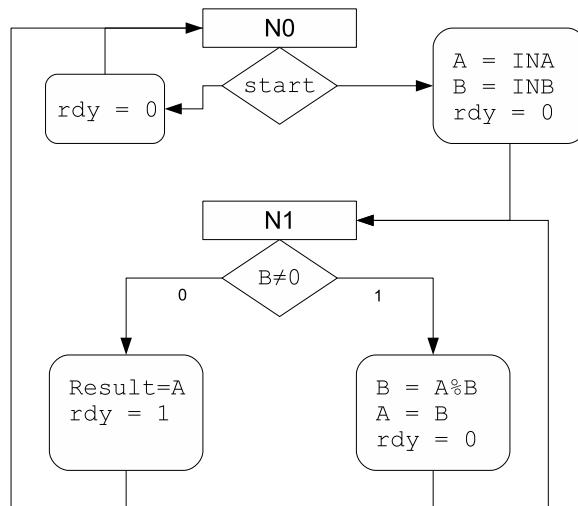

| Figure 2.2  | ASM pour l'algorithme de recherche du PGDC. . . . .                         | 20 |

| Figure 2.3  | Protocole de synchronisation complète. . . . .                              | 21 |

| Figure 2.4  | Description CASM pour l'algorithme de recherche du PGDC. . . . .            | 22 |

| Figure 3.1  | Exemple d'utilisation de règles d'autorisation. . . . .                     | 26 |

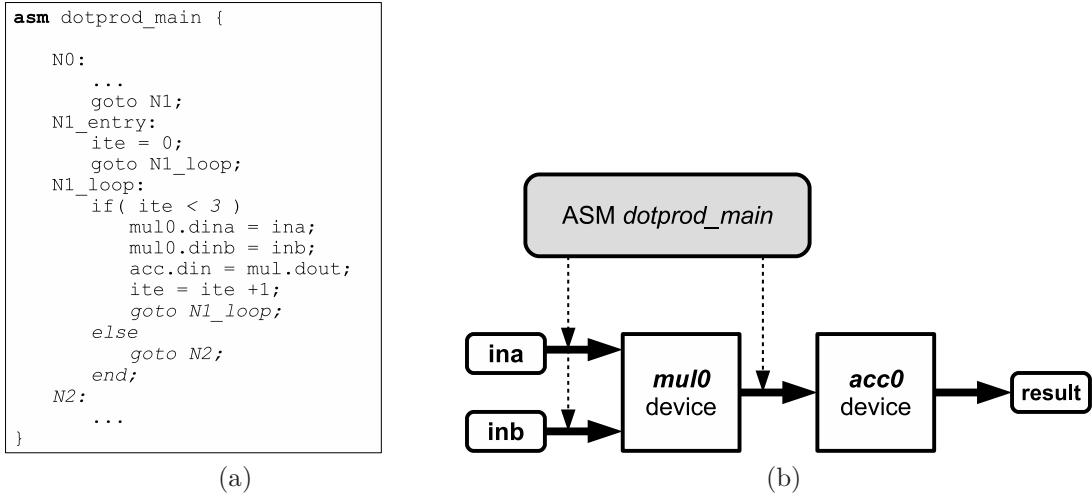

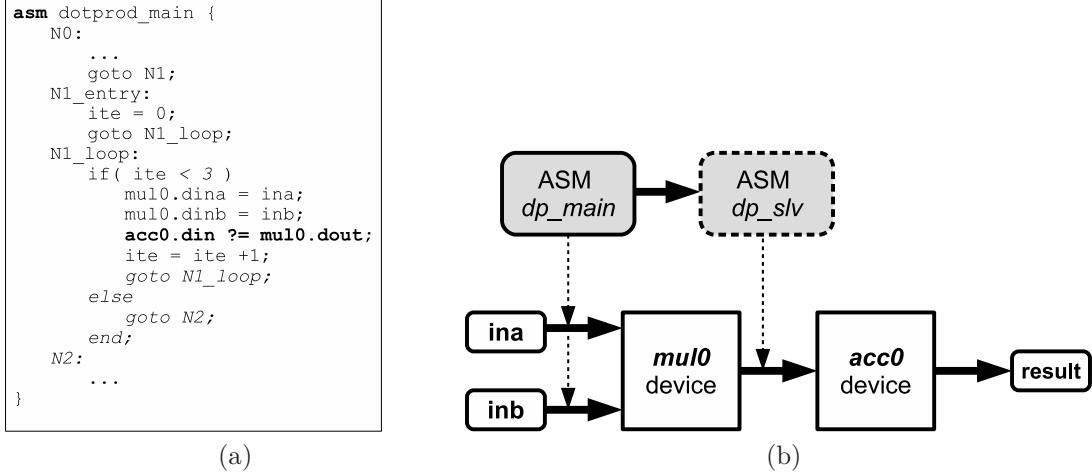

| Figure 3.2  | Description CASM d'un produit scalaire. . . . .                             | 27 |

| Figure 3.3  | Description CASM d'un produit scalaire avec connexion différée . . . . .    | 28 |

| Figure 3.4  | Simple utilisation de l'opérateur de connexion différée. . . . .            | 29 |

| Figure 3.5  | Description de boucle avec opérateur de connexion différée. . . . .         | 30 |

| Figure 3.6  | Description de boucles avec opérateur de connexion différée. . . . .        | 31 |

| Figure 3.7  | Sémantique pour les opérateurs de connexion différée I. . . . .             | 32 |

| Figure 3.8  | Sémantique pour les opérateurs de connexion différée II. . . . .            | 33 |

| Figure 3.9  | Sémantiques pour les opérateurs de connexions réseaux. . . . .              | 36 |

| Figure 4.1  | Flot de compilation CASM. . . . .                                           | 39 |

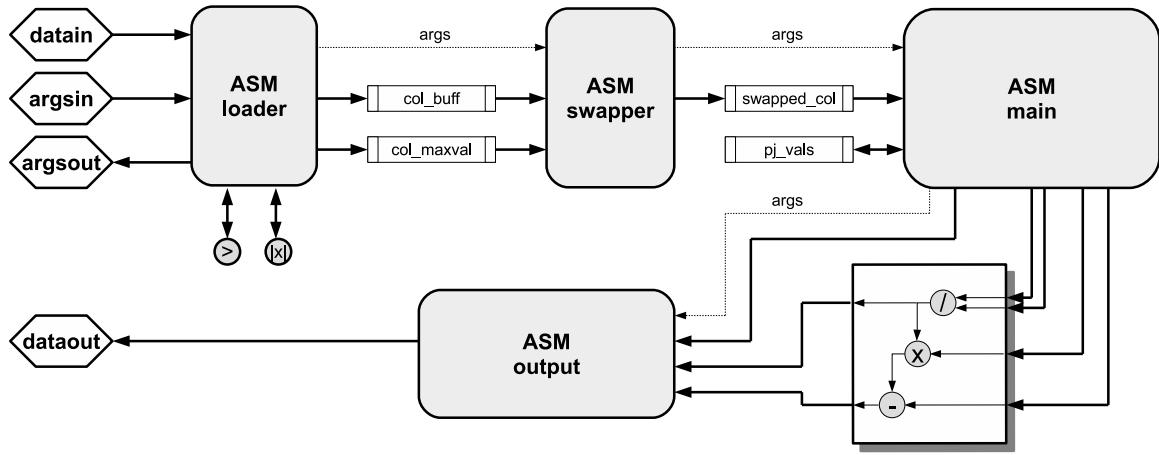

| Figure 4.2  | Architecture associée à une description CASM+. . . . .                      | 40 |

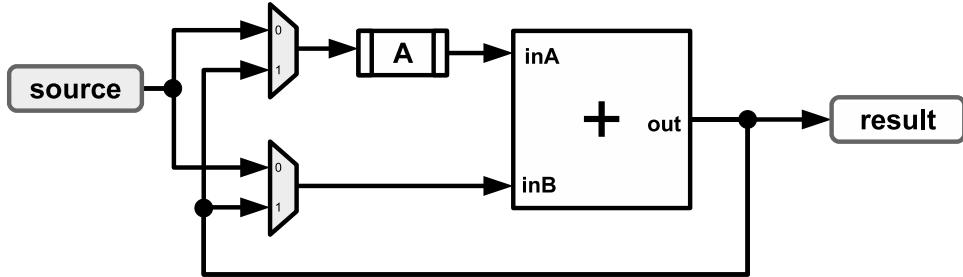

| Figure 4.3  | Deux opérateurs complètement synchronisés. . . . .                          | 41 |

| Figure 4.4  | FIFO complètement synchronisée, avec chemin de contournement. . . . .       | 42 |

| Figure 4.5  | Accumulateur basé sur un additionneur pipeliné. . . . .                     | 43 |

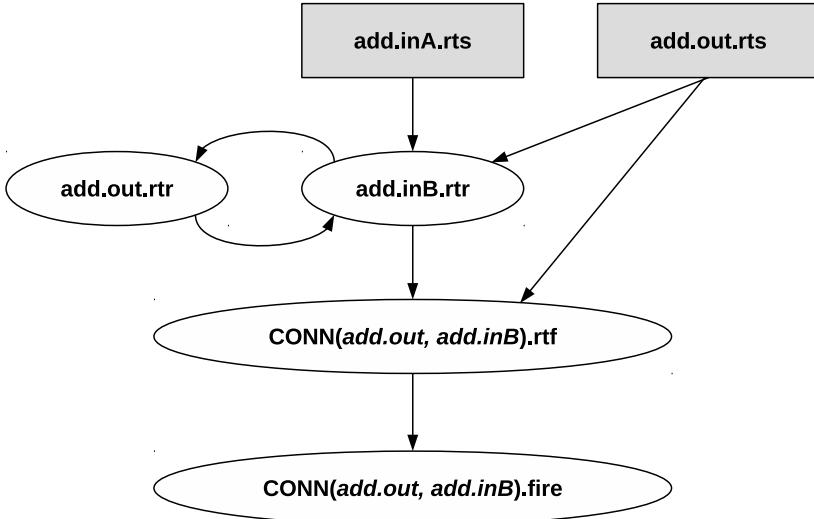

| Figure 4.6  | Exemple de réseau combinatoire cyclique. . . . .                            | 45 |

| Figure 4.7  | Transformation d'un réseau cyclique . . . . .                               | 46 |

| Figure 4.8  | Table de vérité pour une contrainte de stabilité C . . . . .                | 48 |

| Figure 4.9  | Exemple de réseau combinatoire acyclique boucle-ouverte. . . . .            | 49 |

| Figure 4.10 | Exemple de réseau combinatoire acyclique résolu. . . . .                    | 52 |

| Figure 5.1  | Algorithme <i>quicksort</i> . . . . .                                       | 55 |

| Figure 5.2  | Algorithme <i>partition</i> . . . . .                                       | 55 |

| Figure 5.3  | Représentation STL de l'architecture avec mémoire partagée. . . . .         | 56 |

| Figure 5.4  | Représentation STL de l'architecture proposée. . . . .                      | 58 |

| Figure 5.5  | Comparaison des chemins de données pour l'accumulateur . . . . .            | 58 |

| Figure 5.6  | Description CASM+ d'un accumulateur pipeliné. . . . .                       | 60 |

| Figure 5.7  | Description d'un accumulateur pipeliné avec connexions différées. . . . .   | 61 |

| Figure 5.8  | Algorithme de produit matriciel $A \times B = C$ . . . . .                  | 63 |

|             |                                                                             |    |

|-------------|-----------------------------------------------------------------------------|----|

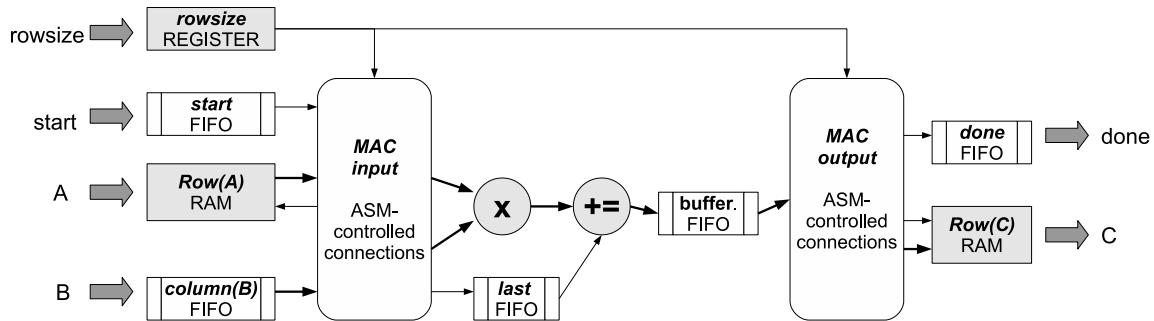

| Figure 5.9  | Représentation STL de l'architecture d'un élément de traitement. . . . .    | 64 |

| Figure 5.10 | Description CASM+ de l'ASM <i>MACinput</i> . . . . .                        | 65 |

| Figure 5.11 | Description CASM+ de l'ASM <i>MACoutput</i> . . . . .                       | 66 |

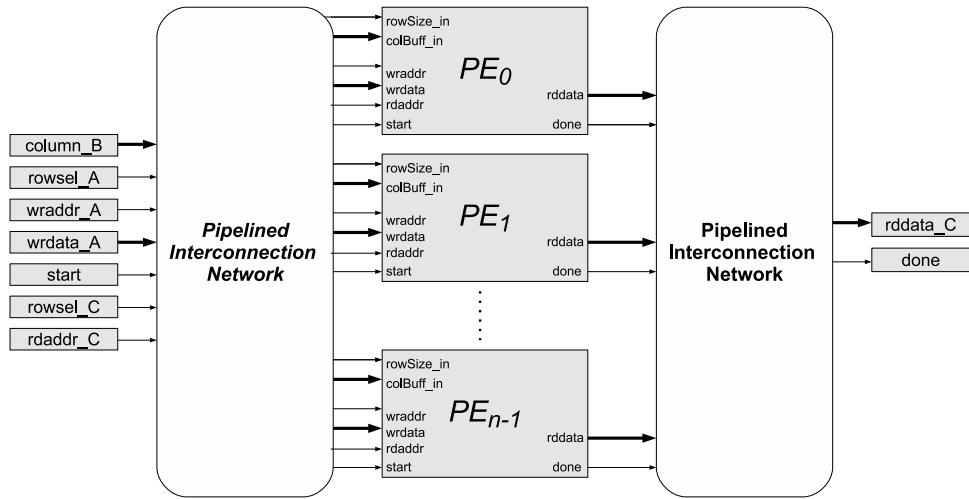

| Figure 5.12 | Architecture intégrant de multiples unités de traitements. . . . .          | 67 |

| Figure 5.13 | Représentation STL d'un réseau d'interconnexions pipeliné. . . . .          | 67 |

| Figure 5.14 | Description CASM+ d'un réseau d'interconnexions pipeliné. . . . .           | 68 |

| Figure 5.15 | Algorithme d'élimination Gaussienne. . . . .                                | 71 |

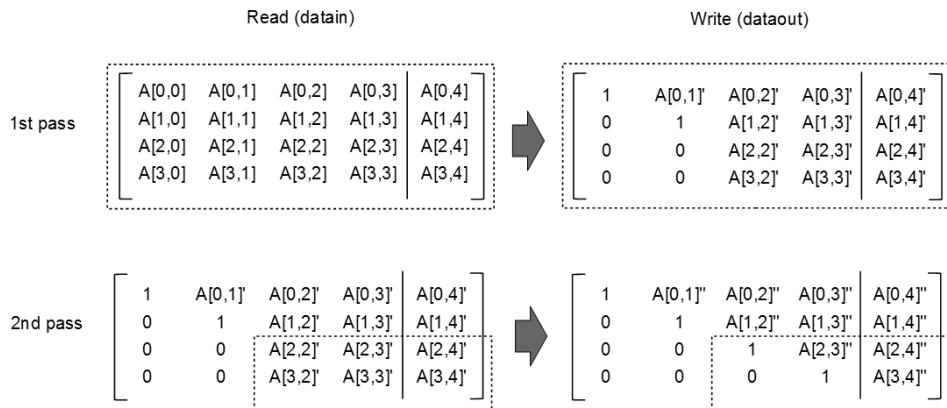

| Figure 5.16 | Illustration des accès mémoire sur deux passes consécutives. . . . .        | 72 |

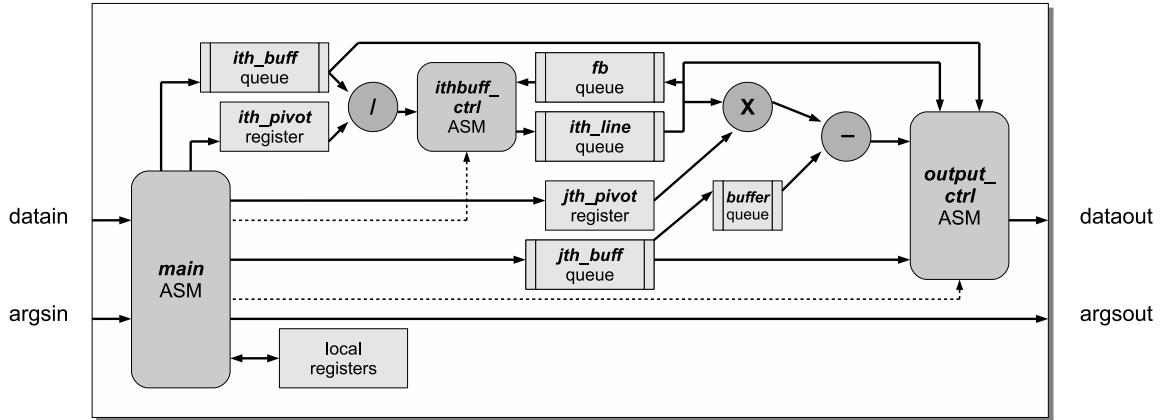

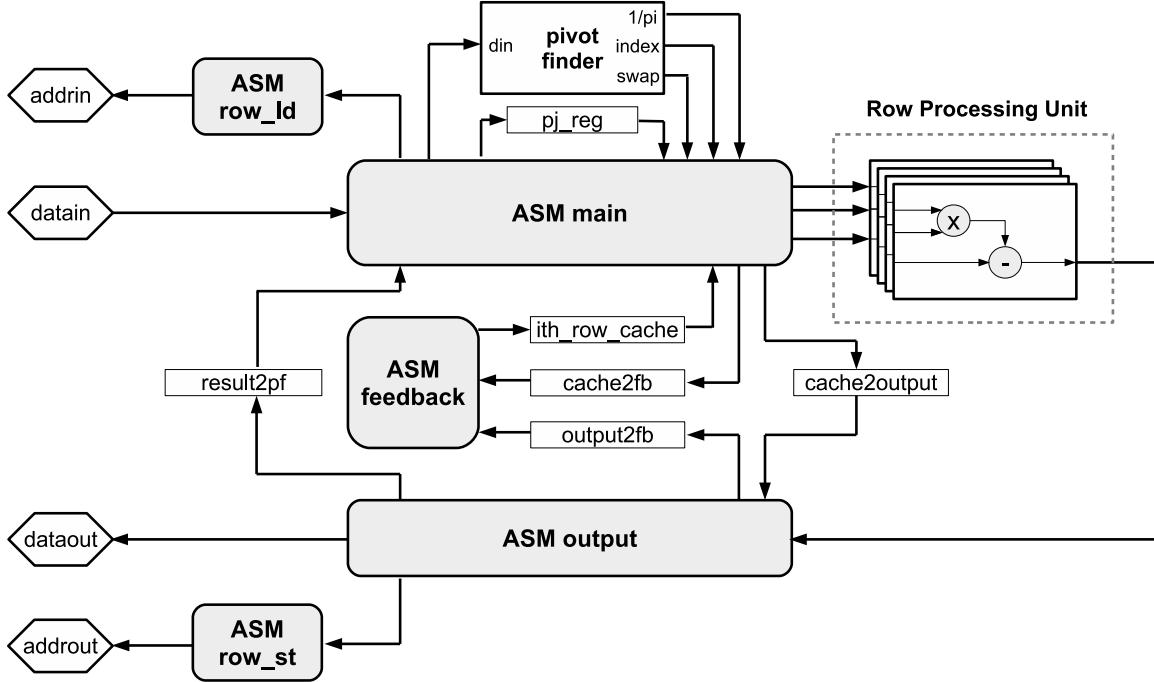

| Figure 5.17 | Architecture d'une unité de traitement (type-I). . . . .                    | 73 |

| Figure 5.18 | Architecture intégrant de multiples unités de traitements en série. . . . . | 74 |

| Figure 5.19 | Architecture d'une unité de traitement (type-II). . . . .                   | 75 |

| Figure 5.20 | Algorithme d'inversion de matrice Gauss-Jordan. . . . .                     | 81 |

| Figure 5.21 | Optimisation des accès mémoire. . . . .                                     | 81 |

| Figure 5.22 | Architecture dédiée pour l'inversion de matrices Gauss-Jordan. . . . .      | 82 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|        |                                                     |

|--------|-----------------------------------------------------|

| FPGA   | Field-Programmable Gate Array                       |

| CPU    | Central Processing Unit                             |

| GPU    | Graphical Processing Unit                           |

| DSP    | Digital Signal Processor                            |

| EDA    | Electronic Design Automation                        |

| HLS    | High-Level Synthesis                                |

| RTL    | Register-Transfer Level                             |

| ITRS   | International Technology Roadmap for Semiconductors |

| CFG    | Control-Flow Graph                                  |

| DFG    | Data-Flow Graph                                     |

| CDFG   | Control/Data-Flow Graph                             |

| HTG    | Hierarchical Task Graph                             |

| KPN    | Kahn Process Network                                |

| LLVM   | Low Level Virtual Machine                           |

| OpenCL | Open Computing Language                             |

| OpenMP | Open Multi-Processing                               |

| MPI    | Message Passing Interface                           |

| SCC    | Strongly Connected Component                        |

| FVS    | Feedback Vertex Set                                 |

| PE     | Processing Element                                  |

| AXI    | Advanced eXtensible Interface                       |

| CIM    | Computation In Memory                               |

| TLM    | Transaction-Level Modeling                          |

| ANSI   | American National Standards Institute               |

| ESL    | Electronic System Level                             |

| VHSIC  | Very High Speed Integrated Circuit                  |

| VHDL   | VHSIC Hardware Description Language                 |

| SoC    | System-on-Chip                                      |

| ASM    | Algorithmic State Machine                           |

| RAM    | Random Access Memory                                |

| FIFO   | First-In First-Out                                  |

| BDD    | Binary Decision Diagram                             |

| LPM    | Library of Parameterized Modules                    |

FLOPS Floating-Point Operations Per Second

LUT Look Up Table

## CHAPITRE 1 INTRODUCTION

Il y a de cela une décennie (en 2005), Intel prenait un virage important en lançant la production de puces de processeurs dont les hautes-performances allaient désormais reposer sur plusieurs coeurs (*cores*). De nos jours, les puces multiprocesseurs sont omniprésentes dans nos vie, de l'unité de traitement centrale au processeur graphique d'un ordinateur de bureau, jusqu'à l'intérieur de nos téléphones cellulaires. Elles composent également le cœur des noeuds des superordinateurs les plus puissants de la planète. Cette tendance à voir augmenter le nombre de coeurs par puces s'observe toujours alors que l'on passe graduellement de puces à multiples-coeurs (*multi-cores*) vers des puces à beaucoup-de-coeurs (*many-cores*), et elle ne semble pas sur le point de s'arrêter. Au cœur de ce changement fondamental se trouve la rupture de la mise-à-l'échelle de Dennard (Robert H. Dennard) qui stipule essentiellement que la densité de puissance des transistors demeure constante avec chaque nouvelle génération de transistors [1]. Dans ce contexte, la performance des processeurs mono-coeur a cessé de croître au rythme de la loi de Moore. De plus, les puces de processeurs modernes sont confrontées au problème du silicium obscur (*dark silicon*), qui fait référence au fait que les procédés de microfabrication peuvent désormais intégrer plus de transistors qu'il est possible d'en utiliser, de sorte à ce que toute la surface d'une puce ne puisse être utilisée simultanément [2].

Au-delà des processeurs d'instructions multi-coeurs, le monde du traitement numérique haute-performance moderne est également caractérisé par l'utilisation de circuits spécifiques à un domaine d'application implémentés au moyen de circuits programmables FPGA (réseau de portes programmables *in situ*). Intel faisait d'ailleurs récemment l'acquisition du fabricant de FPGA Altera. Les FPGA représentent des candidats intéressants à la réalisation de calculs haute-performances pour différentes raisons. D'une part, le nombre importants de blocs de propriété intellectuelle gravés en dur sur ces puces (processeurs, mémoires, unités de traitement de signal numérique) réduit l'écart qui les sépare des circuits intégrés dédiés en termes de ressources disponibles [3]. Un écart qui s'explique justement par le haut niveau de configurabilité offert par le circuit programmable, une capacité pour laquelle un grand nombre de ressources doit être dédié sans être utilisé par le circuit programmé. Néanmoins dans un contexte où plus de transistors sont disponibles qu'on puisse en utiliser, le coût associé à la configurabilité s'en trouve d'autant réduit. On note également que le problème du silicium obscur ne se pose pas dans la même mesure puisqu'une grande proportion des transistors est *de facto* inactive après la programmation d'un FPGA. L'utilisation de blocs de propriété intellectuelle dédiés permet également de réduire l'écart de performance séparant les circuits intégrés dédiés des FPGAs. Récemment, des FPGA ont été utilisés par Microsoft dans

ses centres de données pour accélérer l'engin de recherche *Bing* [4]. Les différentes analyses effectuées rapportent des améliorations significatives en termes de débits et de latence.

## 1.1 Problématique

De par leur capacité à être reconfigurés complètement ou partiellement, les FPGA modernes, tout comme les processeurs d'instructions, offrent la flexibilité requise pour supporter un grand nombre d'applications. Néanmoins, contrairement aux processeurs d'instructions qui sont programmés avec différents langages de programmation haut-niveau (Java, C/C++, MPI, OpenMP, OpenCL), la programmation d'un FPGA requiert la spécification d'un circuit numérique, ce qui représente un obstacle majeur à leur plus grande adoption. La description de circuits numériques est généralement exprimée au moyen d'un langage concurrent pour lequel le niveau d'abstraction se situe au niveau des transferts entre registres (RTL), tels les langages VHDL et Verilog. Pour une application donnée, la réalisation d'un circuit numérique spécialisé requiert typiquement un effort significativement plus grand qu'une réalisation logicielle. Dans [5], une comparaison entre un FPGA et une unité de traitement graphique (GPU) pour l'implémentation de noyaux de calculs d'applications scientifiques rapporte un temps de développement  $10\times$  plus important pour la solution FPGA. De plus, la description de circuits au niveau RTL est une tâche souvent réservée aux experts en conception de circuits FPGA, et est difficilement accessible aux spécialistes provenant de différents domaines d'applications scientifiques. Il existe aujourd'hui différents outils académiques et commerciaux permettant la synthèse haut-niveau de circuits numériques en partant de descriptions C/C++/SystemC [6], et plus récemment OpenCL [7]. Cependant, selon l'application considérée, ces outils ne permettent pas toujours d'obtenir des performances comparables à celles qui peuvent être obtenues avec une description RTL produite manuellement.

## 1.2 Concepts fondamentaux

On s'intéresse dans ce travail à un outil de synthèse de niveau intermédiaire offrant un compromis entre les performances atteignables aux moyens d'une méthode de conception RTL et les temps de conception que permet la synthèse à haut-niveau. On considère ainsi la synthèse de circuits numériques partant d'un langage supportant la description de machines à états algorithmiques contrôlant des connexions entre des sources et des puits avec des interfaces de synchronisation prédéfinies. Ces interfaces sont similaires aux interfaces à flot de données *AXI4-Stream* et *Avalon-Streaming*, disposant de signaux de synchronisation de type prêt-à-envoyer/prêt-à-recevoir pour supporter la synchronisation des transferts à la source

et à la destination. Un transfert de données survient lorsque la source et le puits associés à une connexion sont tous deux prêts. Un tel niveau d'abstraction est offert par le langage de description de circuits de niveau intermédiaire CASM, proposé dans [8]. CASM permet aussi la description de connexions *bloquantes*, qui bloquent le flot de contrôle d'une ASM tant qu'un transfert de donnée n'a pas eu lieu entre la source et le puits correspondants. Conjointement, ces deux caractéristiques fondamentales du langage CASM permettent la description de circuits numériques comme un ensemble de processus concurrents activant dynamiquement des transferts synchronisés par les données, et ce en faisant abstraction du détail de la logique de contrôle requise pour supporter cette synchronisation. Le déplacement d'une donnée entre une source et un puits synchronisés par les données devient aussi simple que la spécification d'une instruction (en langage machine) de déplacement de donnée entre registres dans un processeur d'instructions.

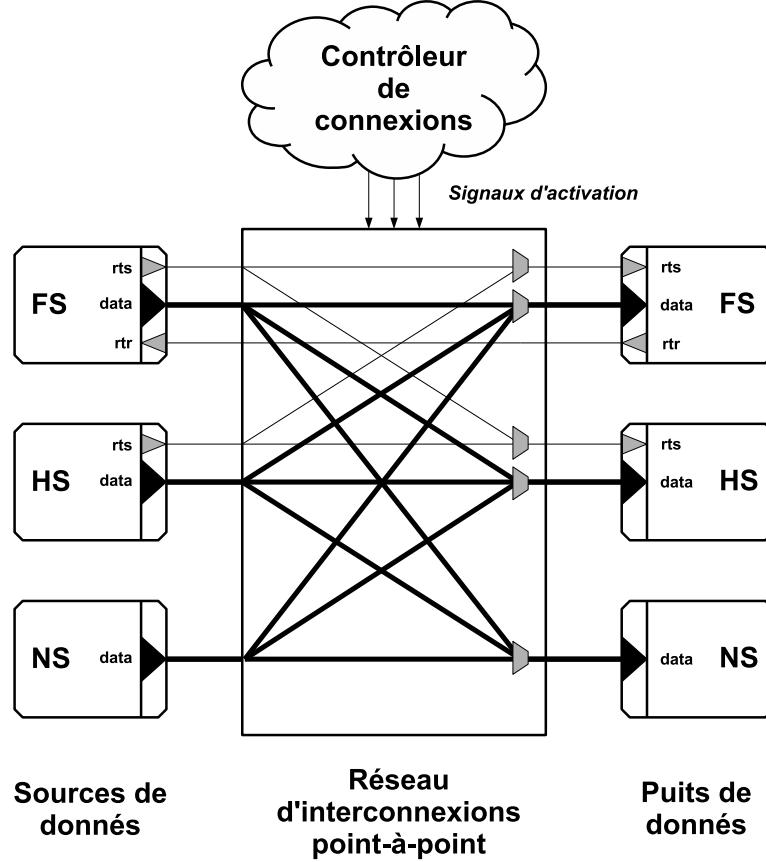

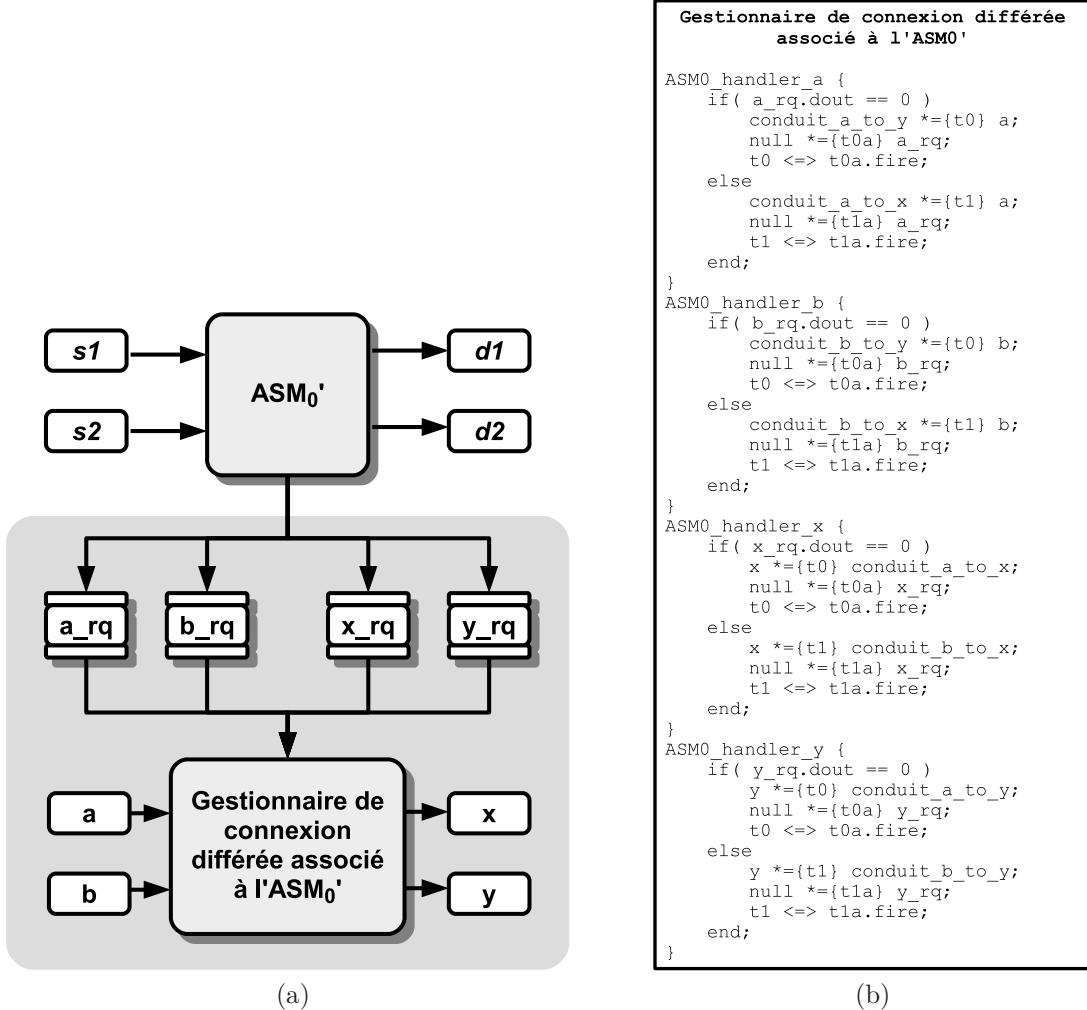

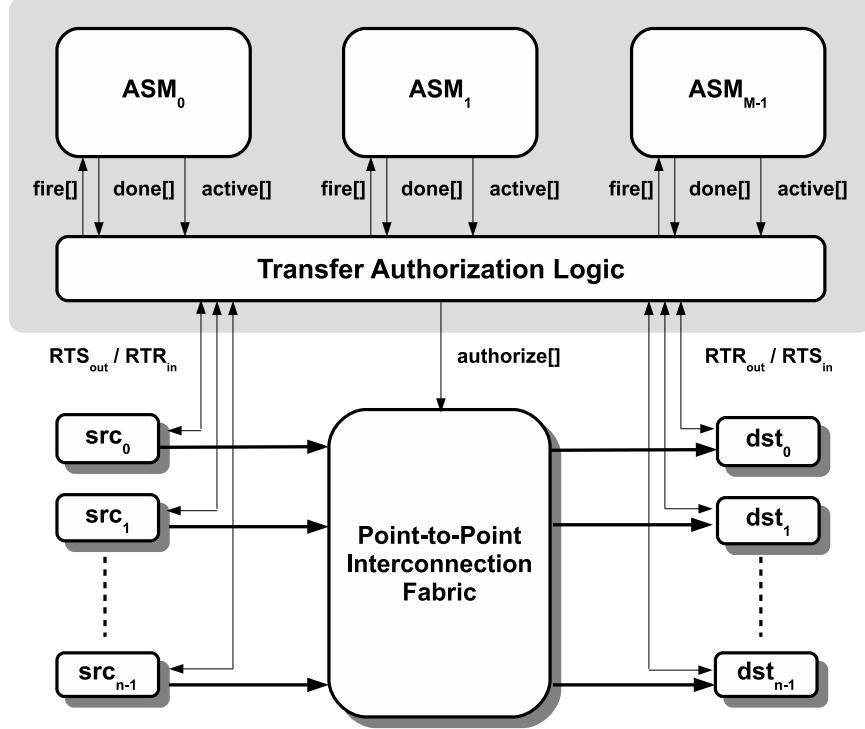

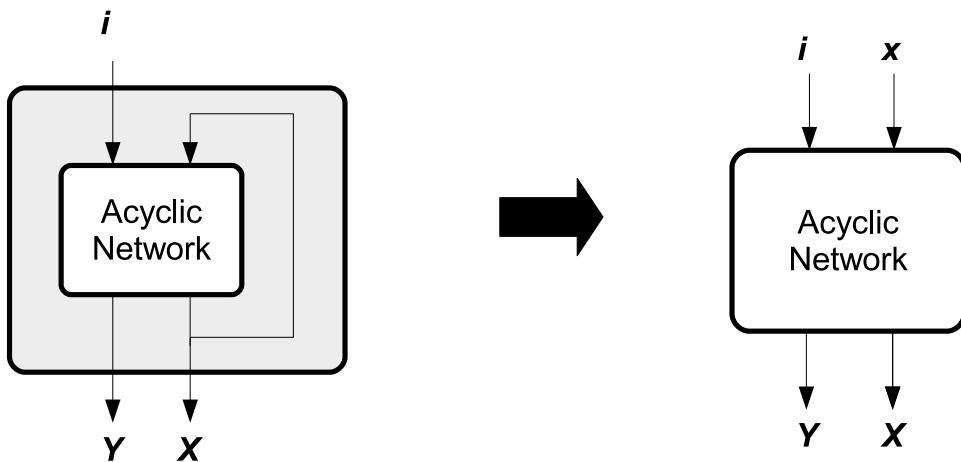

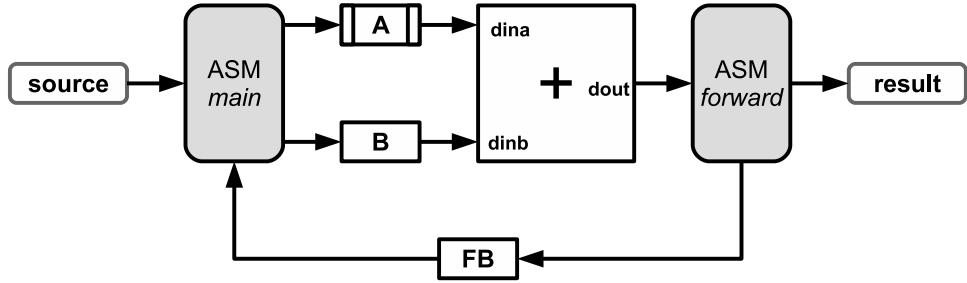

La Figure 1.1 illustre de manière abstraite le niveau d'abstraction considéré, comprenant un contrôleur de connexions (une machine à états), ainsi qu'un ensemble de sources et de puits synchronisés par les données interconnectés par un réseau d'interconnexion point-à-point. Le contrôleur est responsable d'activer dynamiquement des connexions entre les sources et puits présents. Lorsqu'une connexion non-bloquante est activée, un canal synchronisé par les données est établi entre la source et le puits associés à cette dernière. Lorsqu'un canal est établi, les données peuvent circuler librement de la source à la destination, à raison d'une donnée par cycle d'horloge pour lequel la source et le puits sont tous deux prêts à envoyer et recevoir, respectivement. Dans le cas d'une connexion bloquante, le canal est établi jusqu'à ce que le transfert d'une donnée ait lieu, après quoi le canal disparaît (i.e. : la connexion est automatiquement désactivée).

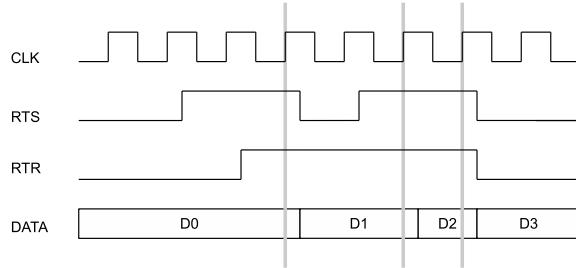

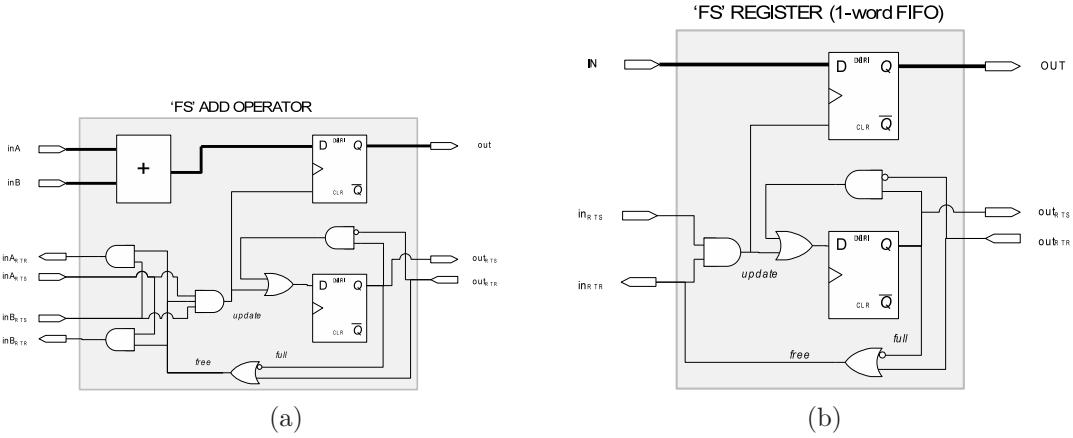

Les sources et les puits supportent différents protocoles de synchronisation (*FS*, *HS*, et *NS*). Le protocole *FS* (*Full-Synchronized*) est associé à une interface disposant de deux signaux de synchronisation, *rts* (*ready-to-send*) et *rtr* (*ready-to-receive*). Le signal *rts* indique si la source est prête à envoyer une donnée, tandis que le signal *rtr* indique si le puits est prêt à recevoir une donnée. Le protocole *HS* (*Half-Synchronized*) est associé à une interface ne disposant que d'un signal *rts*. Pour ce protocole, la synchronisation se fait à la source uniquement. La source ne se soucie pas que la donnée soit reçue (i.e. : la contre-pression n'est pas prise en compte, on considère que le puits est toujours prêt à recevoir). Dans le cas du protocole *NS* (*Not-Synchronized*), une donnée est envoyée à chaque cycle d'horloge (i.e. : on considère que la source et le puits sont toujours prêts à envoyer et recevoir des données). Notons qu'il est possible d'interconnecter des sources et des puits qui ont des protocoles de synchronisation différents. Dans de tels cas, si une sortie de synchronisation (*rts/rtr*) ne peut pas être pairée à une entrée de synchronisation (*rts/rtr*) correspondante, cette dernière est considérée/laissée

flottante. De même, si une entrée de synchronisation (*rts/rtr*) ne peut pas être paire à une sortie de synchronisation (*rts/rtr*) correspondante, cette dernière est assignée à la valeur 1 (vrai).

Figure 1.1 Interconnexion de sources et de puits avec des interfaces synchronisées par les données supportant différents protocoles (FS,HS,NS). Les triangles représentent les entrées et sorties, et les trapèzes des multiplexeurs.

### 1.3 Objectifs de recherche

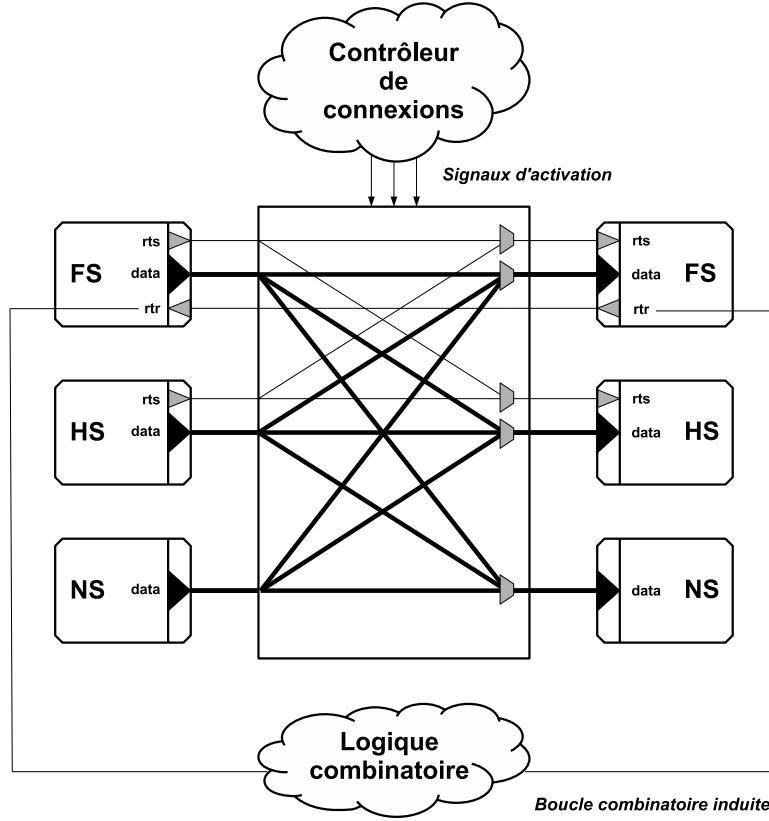

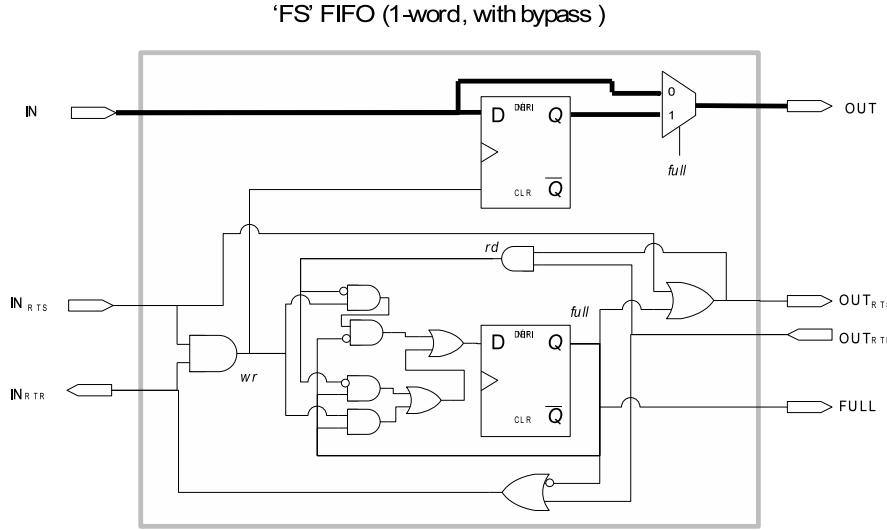

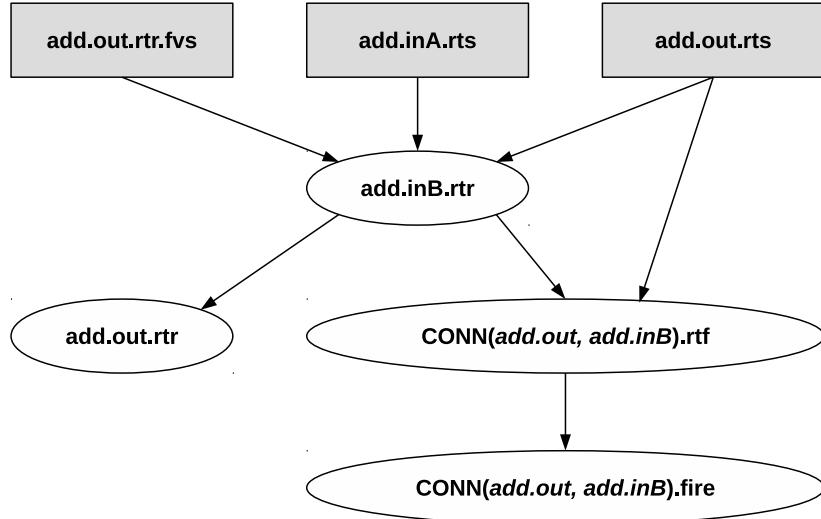

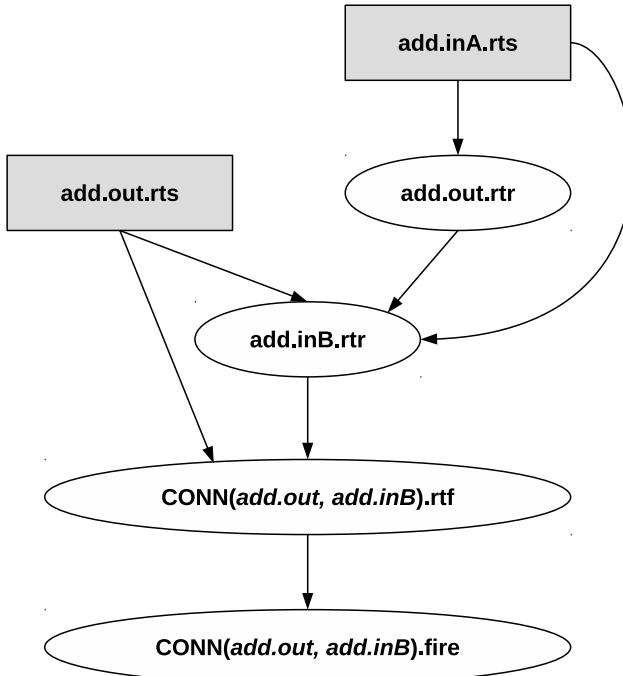

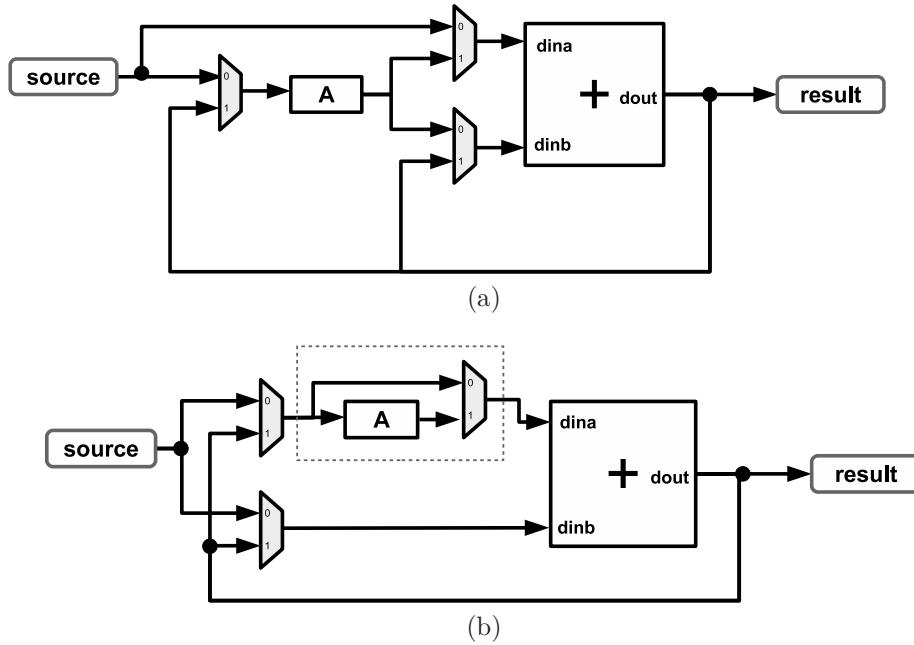

Bien que le language de niveau intermédiaire CASM contribue à simplifier la description de circuits numériques, l'interconnexion de sources et de puits dans différentes topologies peut induire des boucles combinatoires en termes des signaux de synchronisation des interfaces à flot de données. De plus, ces boucles combinatoires ne sont pas nécessairement équivalentes à des réseaux acycliques de fonctions combinatoires. De telles relations cycliques sont problématiques, d'une part parce qu'elles sont associées à des comportements indéterminés, et d'autre part, parce qu'elles mènent à des circuits qui ne sont pas synthétisables ou qui n'ont

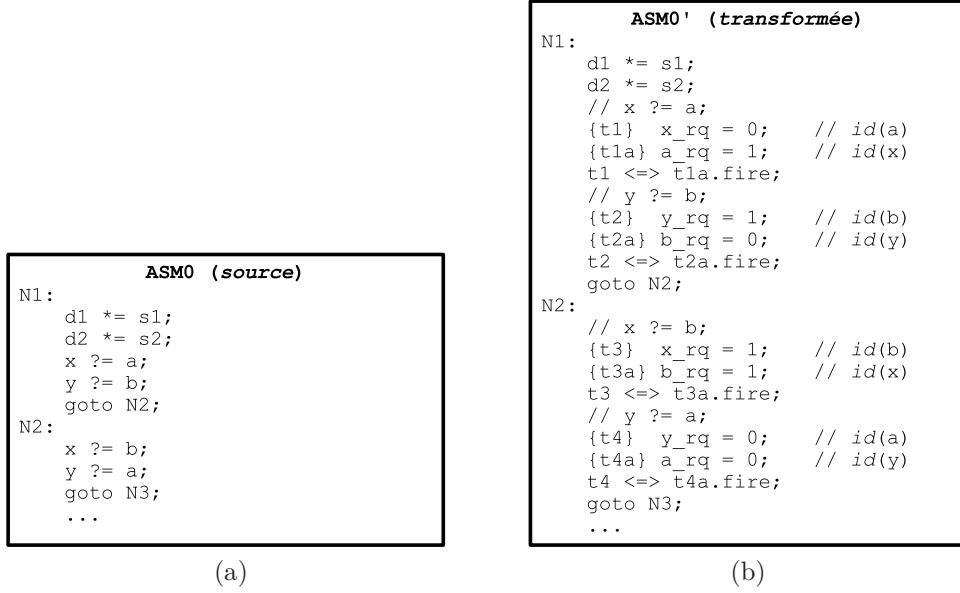

pas le comportement désiré. La présence de telles boucles combinatoires peut s'expliquer par la présence de relations combinatoires entre les entrées et sorties de synchronisation des différents composants interconnectés. Par exemple, une FIFO *complètement synchronisée* est prête à recevoir une nouvelle entrée si elle n'est pas pleine (dépendance à un état interne), ou si elle est lue au même cycle (dépendance avec une entrée de synchronisation). La Figure 1.2 donne une illustration simple de cette problématique, en considérant le modèle illustré à la Figure 1.1. Dans cette illustration, d'une part l'entrée *rtr* de la source *FS* peut dépendre de la sortie *rtr* du puit *FS*, et d'autre part la présence d'une dépendance combinatoire entre la sortie *rtr* du puit *FS* et l'entrée *rtr* de la source *FS* vient produire une relation combinatoire cyclique. Afin de résoudre le problème, nous proposons une approche automatisée au niveau fonctionnel (logique) capable de transformer les boucles combinatoires en circuits acycliques synthétisables. Ceci est essentiellement réalisé en ne permettant que les états stables de la boucle correspondants à un plus grand nombre de transferts de données complétés à chaque cycle. Cette approche fonctionnelle vient s'inscrire dans l'objectif de faciliter l'accès et de simplifier la description de circuits numériques. De même, elle permet d'abstraire un problème important associé à l'implémentation bas-niveau de la logique de contrôle pour la synchronisation des transferts de données. Nous proposons également une syntaxe permettant de spécifier des règles pour la synchronisation et l'ordonnancement des transferts de données sur un groupe de connexions activées. Cette nouvelle syntaxe offre une séparation au niveau de la description du contrôle en termes des connexions à activer vis-à-vis de comment les transferts doivent s'exécuter au sein des connexions activées. Lorsque des règles d'autorisation forment des relations cycliques, celles-ci sont automatiquement traduites en un réseau acyclique de fonctions logiques de contrôle qui maximise le nombre de transferts de données.

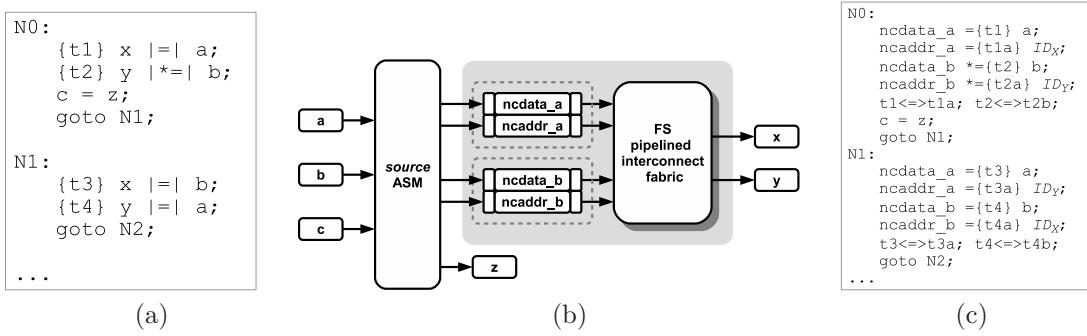

Nous proposons également de nouveaux opérateurs de connexions avancés développés dans l'objectif de simplifier la description de circuits qui interconnectent des opérateurs pipelinés. Une des difficultés inhérentes à l'utilisation d'opérateurs pipelinés est la présence d'un décalage temporel entre le moment auquel les opérandes sont acceptées par l'opérateur et celui pour lequel l'opérateur produit un résultat à sa sortie. Il s'ensuit que la spécification algorithmique d'architectures intégrant des opérateurs pipelinés est significativement plus complexe qu'il en est pour la spécification d'architectures intégrant des opérateurs non-pipelinés. L'opérateur de connexion différée présenté dans cette thèse contribue à abstraire cette complexité, la ramenant à un niveau qui s'apparente à celle de la spécification algorithmique d'architectures intégrant des opérateurs non-pipelinés. D'autre part, l'interconnexion d'un grand nombre de sources et puits au moyen d'un réseau combinatoire d'interconnexions point-à-point peut contribuer à augmenter significativement le chemin critique de l'architecture (au niveau de la logique d'aiguillage du chemin de données), ce qui peut affecter négativement

Figure 1.2 Interconnexion de sources et de puits induisant une relation combinatoire cyclique.

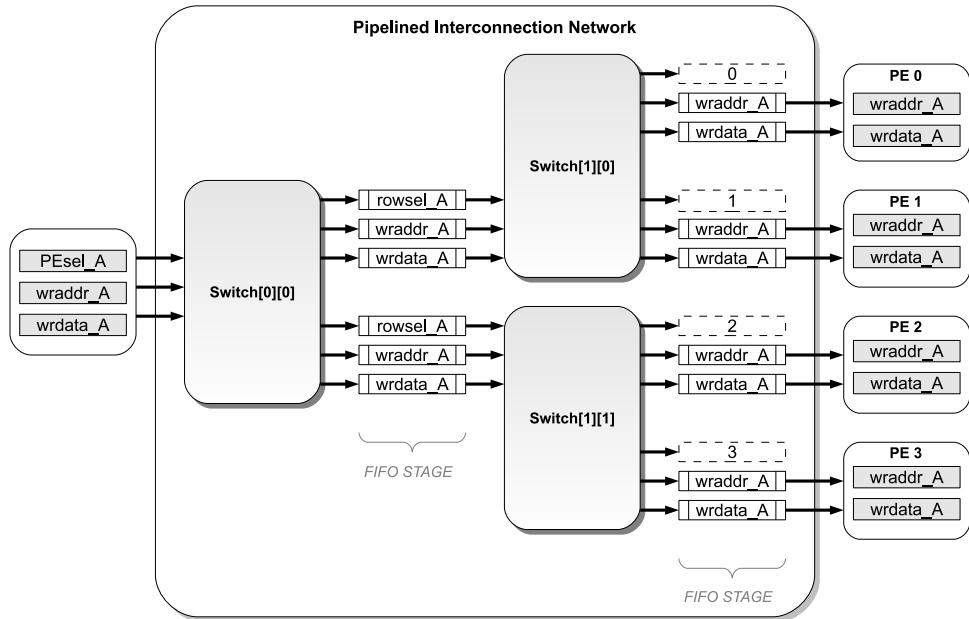

les performances du circuit spécifié. Pour contrecarrer ce problème, il est typiquement requis de faire appel à un ou plusieurs réseaux d'interconnexions pipelinés. Or le passage d'un réseau d'interconnexion combinatoire point-à-point vers un réseau d'interconnexion pipeliné entraîne une modification non-négligeable de la description algorithmique. Il faut notamment gérer l'adressage adéquat des destinations accessibles via le réseau d'interconnexions. Les opérateurs de connexions sur un réseau pipeliné que nous proposons dans ce travail permettent d'abstraire la gestion d'un tel adressage en inférant automatiquement un réseau d'interconnexion pipeliné synchronisé par les données. La syntaxe est telle que la description de connexions sur un réseau d'interconnexion pipeliné est similaire à la description de connexions point-à-point non-pipelinées.

## 1.4 Contributions

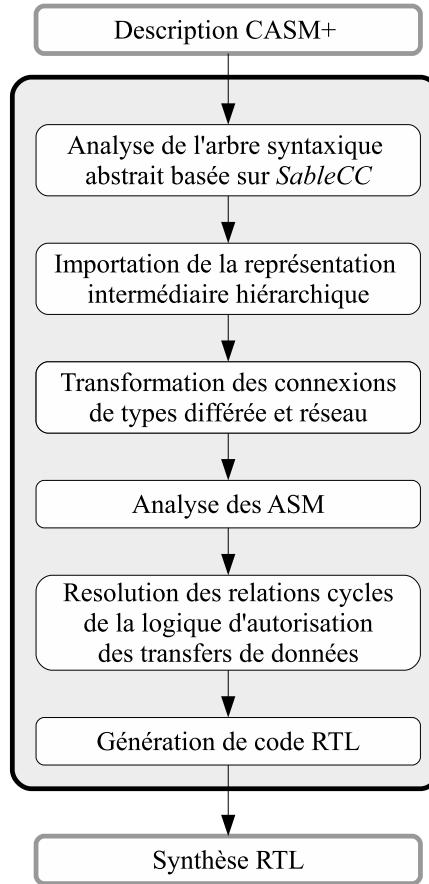

La méthodologie de synthèse de circuits numériques présentée dans ce travail a été automatisée au moyen d'un compilateur décrit en langage Java. Pour évaluer la viabilité de la méthode de synthèse à niveau intermédiaire proposée, celle-ci a été appliquée à un certain

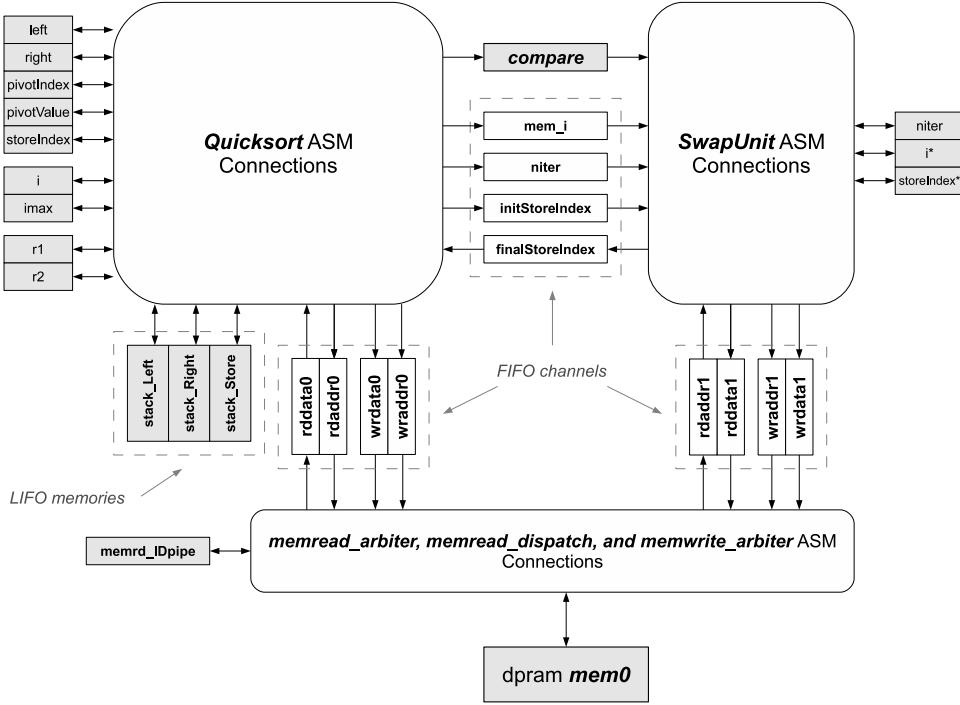

nombre d'applications, notamment dans le domaine du traitement numérique avec des opérateurs pipelinés utilisant une représentation des nombres en virgule-flottante. On considère des circuits réalisant des algorithmes avec différents niveaux de complexité au niveau du flot de contrôle. Les applications considérées incluent le tri de données *Quicksort*, l'accumulation pipelinée en représentation virgule-flottante, le produit matriciel dense, l'élimination Gaussienne, et l'inversion de matrices. Une comparaison de certains circuits numériques produits avec notre approche de synthèse de niveau intermédiaire avec d'autres implémentations similaires décrites au niveau RTL et/ou au niveau C montrent que l'approche proposée permet un compromis intéressant entre les 2 approches, en termes de qualité d'implémentation et de temps de développement. La description de circuits avec le langage de description au niveau des transferts synchronisés par les données présenté offre au développeur un niveau de contrôle sur l'architecture qui se rapproche du niveau RTL, tout en permettant d'abstraire différentes difficultés inhérentes à l'interconnexion d'interfaces synchronisées par les données dans différentes topologies. La méthodologie proposée permet une description plus concise des comportements désirés, et l'automatisation de différentes tâches liées à l'implémentation de la logique de contrôle vient également réduire les sources d'erreurs possibles.

De manière sommaire, cette thèse présente les contributions suivantes au niveau de la description et de la synthèse automatisée de circuits au niveau des transferts synchronisés par les données :

1. Une méthode de résolution automatisée des boucles combinatoires en termes des signaux de synchronisation des interfaces synchronisées par les données. Cette résolution est exécutée de manière à produire un réseau acyclique de fonctions maximisant le nombre de transferts de données.

2. Le langage permet la description de règles contrôlant l'autorisation des transferts de données au sein des connexions activées. Les règles formant des relations cycliques en termes des signaux de synchronisation des sources et puits sont résolues de manière automatisée.

3. Un opérateur de connexion avancé de type *diffréé*, mis au point pour abstraire un niveau de complexité associé à la spécification de circuits intégrants des opérateurs pipelinés, et un mécanisme de traduction associé vers des transferts de base (bloquants/non-bloquants).

4. Un opérateur de connexion avancé de type *réseau d'interconnexion pipeliné*, mis au point pour abstraire la complexité liée à l'utilisation d'un réseau d'interconnexion pipeliné pour interconnecter de grands nombres de sources et de puits de données.

5. Un compilateur permettant d'automatiser la synthèse de niveau intermédiaire des

descriptions de circuits décrits au niveau des transferts synchronisés par les données. Le compilateur produit une description au niveau RTL décrite en langage VHDL synthétisable qui peut être traitée avec les outils existants.

6. L'application de la méthode de synthèse de niveau intermédiaire à différentes applications au niveau du traitement numérique avec des opérateurs pipelinés utilisant une représentation des nombres de type virgule-flottante, telles la sommation pipelinée, le produit matriciel dense, l'élimination Gaussienne, et l'inversion de matrice. Ces applications sont comparées avec des implémentations produites avec des approches RTL et de synthèse haut-niveau en langage C, de manière à évaluer le compromis offert par l'approche de niveau intermédiaire en termes de performances et de temps de conception.

## 1.5 Plan de la thèse

La suite de cet ouvrage est organisée comme suit : Le chapitre 2 présente un survol de l'état de l'art en matière de description et synthèse à un niveau d'abstraction allant au-delà de celui offert par les langages de descriptions au niveau des transferts entre les registres (RTL). Le chapitre 3 présente les ajouts apportés au langage CASM existant, ce qui inclut la descriptions de règles d'autorisation des transferts de données, et des opérateurs de connexions avancés. Le chapitre 4 présente la méthode au niveau fonctionnel permettant la résolution automatique des boucles combinatoires en termes des signaux de synchronisation des interfaces synchronisées par les données. Le chapitre 5 vient ensuite présenter l'application de la méthode de synthèse de niveau intermédiaire à la conception de divers circuits numériques de différentes complexités. Le chapitre 6 vient conclure cette thèse.

## CHAPITRE 2 REVUE DE LITTÉRATURE

### 2.1 Introduction

Le domaine de l'automatisation de la conception des circuit numériques (EDA) a vu le jour dans les années suivant l'arrivée des circuits intégrés (1958). L'évolution des outils de conceptions assistée par ordinateurs est étroitement liée à l'évolution des circuits intégrés : les nouvelles générations d'outils de conception rendent possibles le développement de circuits plus complexes, qui permettent à leur tour de supporter de nouvelles générations d'outils de conception pour des circuits de plus grandes complexités. Après tout la conjecture de Moore, qui s'applique encore aujourd'hui, stipule que la densité de transistors double tous les deux ans, si bien que les circuits intégrés modernes peuvent intégrer plus d'un milliard de transistors. Il va sans dire que ce taux de croissance exponentiel demeure une source de pression inouïe et sans repos sur l'évolution des outils de conception responsables d'assister et d'automatiser le développement des circuits intégrés. Afin de composer avec cette augmentation incessante de la complexité, différents niveaux d'abstractions (plus élevés) ont été graduellement ajoutés/superposés au flot de conception des circuits numériques intégrés. Une description à un niveau d'abstraction plus élevé contient moins de détails par rapport à l'implémentation finale, mais est plus efficace pour exprimer la fonctionnalité désirée. Le flot de conception assistée par ordinateurs permet d'automatiser le raffinement d'une spécification à un niveau d'abstraction donné jusqu'à une implémentation physique finale.

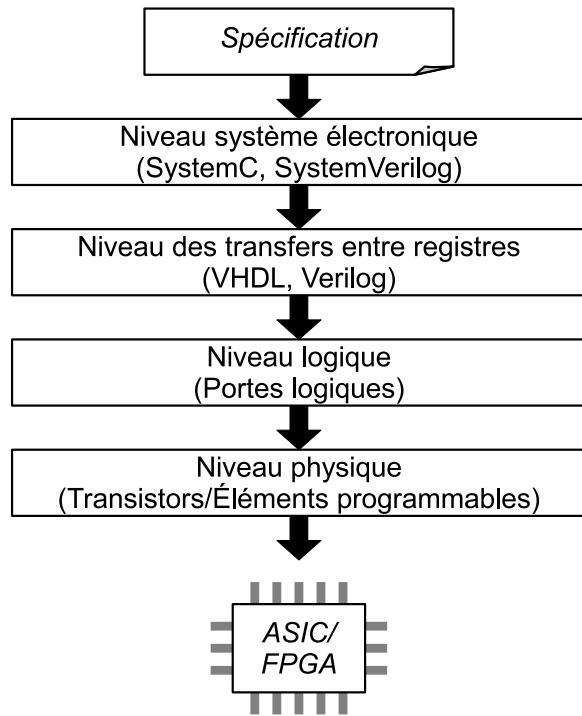

La Figure 2.1 illustre les 4 principaux niveaux de conceptions du processus de synthèse automatisé des circuits numériques intégrés. À l'état de l'art, le *niveau système* représente le plus haut-niveau d'abstraction. À ce niveau d'abstraction, un système complexe est décrit en termes de processus communicants au moyen de langages tels SystemC et SystemVerilog, qui permettent de supporter différents degrés de raffinements au niveau de la spécification des communications et du traitement (*untimed*, *partially-timed*, *cycle accurate*). Il est ainsi possible de raffiner successivement la spécification exécutable du système à concevoir en partant d'un programme C/C++ dépourvu de toute notion de concurrence, jusqu'à une spécification pour laquelle les transferts et les opérations sont spécifiées avec un modèle d'exécution concurrente, exprimé au niveau du cycle d'horloge. Un tel niveau de raffinement se rapproche à peu de choses près du niveau de conception suivant, le *niveau des transferts entre registres* (RTL). Au niveau RTL, un circuit est entièrement spécifié au niveau du cycle d'horloge en termes de transferts de données entre des registres, et en termes d'opérations arithmétiques et logiques (combinatoires) à réaliser sur ces données. Au *niveau logique*, l'implémentation se précise

alors que le circuit intégré est représenté par un réseau de portes logiques (ET/NON-ET, OU/NON-OU, et inverseurs). Au niveau des portes, le comportement observé se rapproche davantage de l'implémentation physique finale du circuit. Ce niveau permet également différentes optimisations indépendantes de la technologie du réseau de portes logiques (optimisations 2-niveaux, multi-niveaux, etc...). Le plus bas niveau d'abstraction, le *niveau physique*, offre une représentation du circuit au niveau des ressources physiques qui composent le circuit. Dans un flot de conception dédié, ces ressources sont essentiellement des transistors interconnectés au moyen de traces métalliques, tandis que dans un flot de conception FPGA il s'agit plutôt d'éléments configurables du circuit programmable (blocs de logiques configurables et matrices de routage).

Figure 2.1 Niveaux d'abstractions pour la conception de circuits numériques.

L'automatisation du processus de raffinement d'une spécification produite à un plus haut niveau d'abstraction vers une implémentation physique bas-niveau est très avantageuse sur le plan de la productivité associée au développement de circuits numériques intégrés. De manière analogue au monde de la conception logicielle, la spécification d'une application à un niveau d'abstraction plus élevé permet une plus grande portabilité, et rend possible une optimisation automatisée de la spécification en ciblant différents objectifs de conception (surface, vitesse, et consommation de puissance). En masquant les détails d'implémentation des couches d'abstractions inférieures, un niveau d'abstraction supérieur rend également possible

un développement plus agile, et plus tolérant aux changements de spécifications tardifs. En effet, il est plus simple d'apporter un changement à un algorithme lorsque la spécification du circuit correspondant est produite à un niveau algorithmique plutôt qu'à un niveau physique. De plus, en déléguant la prise en charge des détails d'implémentation bas-niveaux à des outils de conception automatisée, on réduit significativement les sources d'erreurs possibles en plus de faciliter leur identification et leur correction, ce qui contribue également à réduire l'effort de développement d'un circuit intégré.

À l'état de l'art, bien qu'il soit possible de produire un circuit numérique depuis une spécification algorithmique au moyen des outils de synthèse haut-niveau, le développement de circuit numériques spécialisés est typiquement réalisé au niveau RTL. Les outils de synthèse haut-niveau permettent de produire rapidement un circuit spécialisé pour un algorithme donnée, mais de manière générale les implémentations résultantes ne sont pas comparables aux implémentations produites manuellement au niveau RTL. Dans le rapport sur la feuille de route des semi-conducteurs (ITRS) [9], cette incapacité des outils de synthèse haut-niveau à remplacer l'approche RTL comme niveau de description de circuit est formulée ainsi :

*For instance, although behavioral synthesis is essential to system-level design, efficient behavioral synthesis is not yet realized today, despite having been a research topic for more than a decade, and despite recent advances driven by C- and SystemC-based synthesis and transaction level modeling (TLM) technologies.*

Cette situation représente un obstacle majeur à l'automatisation de la synthèse d'une spécification au niveau système ou algorithmique en une spécification au niveau RTL. La description de circuits spécialisés au niveau RTL requiert l'expertise des concepteurs de circuits dédiés, et n'est généralement pas accessible aux développeurs d'applications scientifiques ne disposant pas d'une telle expertise. De plus, le niveau d'abstraction RTL introduit dans les années 90 n'est plus adéquat pour composer avec les niveaux de complexité rendus possibles par les procédés de fabrications modernes, ce qui a une impact négatif sur la productivité associée au développement des circuits intégrés.

Ce chapitre présente une revue de l'état de l'art en matière de description et de synthèse de circuits numériques au-delà du niveau RTL. La section 2.2 porte un regard sur les plus récents avancements dans le vaste domaine de la synthèse comportementale haut-niveau. La section 2.3 fait un survol de différentes méthodes de description et de synthèse de circuits dédiés au-delà du niveau RTL.

## 2.2 Description comportementale et synthèse haut-niveau

Les premiers travaux de recherches dans de domaine de la synthèse comportementale datent des années 70, et ont réellement pris de l'importance à partir des années 80. Une analyse présentée dans [10] propose un survol historiques des différentes générations d'outils de synthèse à haut-niveau. On y rapporte notamment les principales raisons derrière les échecs des générations précédentes et les succès de la dernière génération. La synthèse comportementale haut-niveau fait généralement référence à la synthèse de programmes décrits en langage C ou un de ces dérivés (C++/SystemC/OpenCL). Cela s'explique notamment par le fait que les langages C/C++ ont longtemps été et demeurent encore aujourd'hui parmi les langages de programmations les plus connus et utilisés au sein de la communauté.

Le flot de conception de synthèse haut-niveau est caractérisé par 4 étapes importantes permettant la transformation d'un programme en description d'un circuit numérique :

1. *Capture du programme* : Le programme est capturé en une représentation interne. Les représentations internes courantes sont les graphes de flot de contrôle et de données (CFG, DFG, CDFG) et les graphes hiérarchiques de tâches (HTG). Différentes optimisations sont réalisées sur la représentation interne (propagation de constantes, élimination de code inutile, ...).

2. *Allocation* : Allocation de ressources (opérateurs et éléments de mémoire) permettant de supporter l'exécution des différentes opérations du programme. Différentes ressources peuvent supporter des opérations identiques.

3. *Ordonnancement* : Ordonnancement des opérations du programme de manière à optimiser le temps d'exécution ou la quantité de ressources utilisées. Optimisation des boucles itératives. Analyse des dépendances de données qui existent entre les différentes opérations du programme.

4. *Association des ressources et synthèse du contrôle* : Association des opérations à des ressources du circuit. La synthèse du contrôle implique la génération des circuits d'ajouillage (mux) de données et de séquenceurs supportant l'exécution des cédules associées aux différentes opérations.

Conjointement, les étapes d'allocation, d'ordonnancement, d'association des ressources, et de synthèse du contrôle réalisent la synthèse d'un circuit automatiquement optimisé afin de satisfaire différents objectifs en termes d'utilisation de ressources et de temps d'exécution. Pour une couverture plus exhaustive, [11] présente une introduction au flot de synthèse haut-niveau, tandis que [12] offre une couverture plus en profondeur de la théorie et des algorithmes supportant les optimisations architecturales des étapes 2 à 4.

À l'état de l'art, un effort de recherche important est toujours investi vers l'amélioration des résultats de synthèse haut-niveau des circuits numériques. Dans [13, 14, 15, 16], un riche ensemble de transformations visant la parallélisation des opérations est proposé. Les travaux dans [13, 17] explorent des transformations de code spéculatives. Dans [14], une technique de décalage de boucle (*loop shifting*) est présentée, permettant de décaler les opérations au-delà des frontières de chaque itération. Les travaux dans [18, 19] traitent de la synthèse comportementale de descriptions contenant des opérations sur des nombres utilisant une représentation à virgule flottante. Le travail dans [20, 21] s'intéresse à la synthèse de descriptions C contenant des pointeurs et des structures de données complexes. Le travail dans [22] s'intéresse à la synthèse comportementale ciblant des systèmes reconfigurables dynamiquement. Dans [23], une approche visant la génération d'architectures multi modes, intégré à l'outil de synthèse comportementale *GAUT*, est proposée.

L'analyse des accès mémoire par des pointeurs peut être utilisée afin de paralléliser davantage les opérations, et de générer des hiérarchies mémoires distribuées supportant une meilleure réutilisation des données. Dans [24], une approche permettant de partitionner les calculs et les tableaux vers différentes mémoires est présentée. Par analyse des empreintes des accès mémoires au travers des boucles, il est possible de réaliser des regroupements de partitions de tableaux dans différentes mémoires et de générer plusieurs unités de calculs de type contrôleur et chemin de données. L'approche proposée pour la génération de systèmes à mémoires distribuées, en plus de permettre des améliorations des temps d'exécution, permet également une réduction intéressante dans les tests comparatifs effectués avec un outil commercial partant de code C non transformé. Dans [25], une autre approche exposant au compilateur l'interaction entre le système mémoire et les unités de calculs est présentée. La méthodologie s'intéresse particulièrement aux accès à des tableaux dans des boucles imbriquées. Ainsi, en présence de réutilisation de données, le compilateur peut prévoir des mémoires tampons (embarqués) pour contenir des partitions de tableaux ce qui permet de réduire considérablement les temps d'accès. Le compilateur est également en mesure d'explorer la possibilité d'utiliser plusieurs mémoires parallèles afin de permettre une plus grande bande passante vers les unités de calcul. Dans [26], une approche consistant à utiliser des mémoires avec unités de calculs intégrés (CIM) dans la synthèse comportementale est proposée. L'idée derrière l'utilisation de telles mémoires est qu'elles offrent une meilleure bande passante que le système d'interconnexions (bus) à l'unité de calcul intégré et qu'elles permettent de réduire les communications au travers de ce même système d'interconnexions. Les résultats obtenus font état d'amélioration d'un facteur 2x en termes de performances et de réduction de la mesure énergie-délais pour des applications intenses en accès mémoires. Dans [27], une méthode (évalué dans le cadre de travail offert par l'outil *Cyber*) permettant de générer des architectures à mémoires

distribuées hétérogènes, ciblant les applications intensives en accès mémoires est proposée.

A l'ère de l'électronique mobile, les techniques d'optimisations pour la synthèse à haut-niveau de circuits numériques à faibles consommations de puissance font également l'objet de recherches actives. Dans [28], une approche basée sur l'utilisation de verrous (*latch*) est présentée. Les verrous possèdent plusieurs avantages en termes de surface, de puissance et de vitesse, mais ne peuvent pas être lus et écrits simultanément. La méthodologie proposée montre que l'utilisation d'une seule horloge est possible en modifiant légèrement le temps de vie des variables. Cette méthode est ensuite comparée à une approche basée sur l'utilisation d'horloge activable (*clock gating*), et des réductions de puissances allant de 39% à 65% sont obtenues avec des surfaces similaires. D'autres travaux [29] considèrent également le verrou comme élément mémoire de base pour la synthèse à haut niveau. En plus de réduire la puissance, les verrous sont ici également utilisés afin de réduire (potentiellement) la latence. Les algorithmes ont été intégrés au cadre de travail HLS-1, et les résultats de comparaison avec un outil de synthèse haut-niveau "conventionnel" rapportent des réductions de latence en moyenne de 18,2% en plus de réductions de surface et de puissance de 9,2% et 18,2% respectivement. Dans [30], le problème d'effets thermiques dans les circuits intégrés est considéré. La méthodologie consiste en un recuit simulé en 2 étapes combinant la minimisation de puissance et de la température du circuit. La méthodologie réussit systématiquement à trouver des implémentations avec des températures de pointe réduites. Les résultats, obtenus par comparaison avec un compilateur haut-niveau minimisant la puissance, font état d'une diminution de la température de pointe de l'ordre de 12% à 16% pour un surcoût de surface moyen de 15%. Les travaux présentés dans [31], poursuivant un objectif similaire, les étapes d'ordonnancement et de liaison (*scheduling* et *binding*) utilisent le retour de simulations thermiques afin de produire des circuits pour lesquels la température moyenne est réduite. Les résultats font état d'une réduction moyenne d'environ 7° C.