|                         | Providing Bi-Directional, Analog, and Differential Signal Transmission<br>Capability to an Electronic Prototyping Platform                                                                                                                                                                              |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Wasim Hussain                                                                                                                                                                                                                                                                                           |

| Date:                   | 2015                                                                                                                                                                                                                                                                                                    |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                                               |

| Référence:<br>Citation: | Hussain, W. (2015). Providing Bi-Directional, Analog, and Differential Signal Transmission Capability to an Electronic Prototyping Platform [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/2002/">https://publications.polymtl.ca/2002/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| <b>URL de PolyPublie:</b> PolyPublie URL: | https://publications.polymtl.ca/2002/ |

|-------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors:  | Yvon Savaria, & Yves Blaquière        |

| <b>Programme:</b> Program:                | génie électrique                      |

## UNIVERSITÉ DE MONTRÉAL

# PROVIDING BI-DIRECTIONAL, ANALOG, AND DIFFERENTIAL SIGNAL TRANSMISSION CAPABILITY TO AN ELECTRONIC PROTOTYPING PLATFORM

# WASIM HUSSAIN DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE PHILOSOPHIAE DOCTOR (GÉNIE ÉLECTRIQUE) DÉCEMBRE 2015

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée:

# PROVIDING BI-DIRECTIONAL, ANALOG, AND DIFFERENTIAL SIGNAL TRANSMISSION CAPABILITY TO AN ELECTRONIC PROTOTYPING PLATFORM

présentée par : HUSSAIN Wasim

en vue de l'obtention du diplôme de : <u>Philosophiae Doctor</u> a été dûment acceptée par le jury d'examen constitué de :

- M. SAWAN Mohamad, Ph. D., président

- M. SAVARIA Yvon, Ph. D., membre et directeur de recherche

- M. BLAQUIÈRE Yves, Ph. D., membre et codirecteur de recherche

- M. AUDET Yves, Ph. D., membre

- M. NABKI Frédéric, Ph. D., membre externe

# **DEDICATION**

To my beloved parents...

#### ACKNOWLEDGEMENTS

I would like to express my deepest gratitude to my supervisor Professor Yvon Savaria and Professor Yves Blaquière for their insightful guidance and constant support throughout this research. I feel extremely privileged to have been able to work under their supervision. They provided me with a healthy research environment with full freedom to develop my work as well as adequate supervision to lead me in the right direction. I am indebted to them.

I would like to express my deep gratitude to Gestion Technocap, the Natural Sciences and Engineering Research Council of Canada and the Mitacs program for supporting my research. I am grateful to CMC Microsystems for the products and services that facilitated this research (CAD tools by Cadence, fabrication services using 0.13 μm CMOS technology from IBM, and packaging services).

I am grateful to Omar Al Terkawi for his help in CAD tools and laying out the test chip. I thank Bryan Tremblant for helping me with the PCB. I thank Rejean Lepage for keeping the lab computers up and running all times, particularly before tape-out deadlines. Special thanks to Marie Yannick Laplante of the Electrical Engineering Department for being so friendly and supportive, even with last minute requests. It has been a great pleasure for me to be a part of the Groupe de Recherche en Microèlectronique et Microsystèmes (GRM).

Last but surely not least, I am grateful to my family for their endless care and support throughout the long path of my academic endeavour.

#### RÉSUMÉ

Les réseaux d'interconnexions programmables (FPIN) se retrouvent largement utilisés dans plusieurs structures bien connues telles que les FPGA, les plateformes de prototypages ainsi que dans plusieurs architectures de réseaux intégrés. Le but de la présente thèse est d'améliorer la structure actuelle des FPIN ainsi que les plateformes de prototypages se basant sur cette technologie afin d'y intégrer d'autres fonctionnalités telles que des interfaces pour les signaux bidirectionnels de type drain-ouvert, les signaux analogiques ou bien les signaux différentiels. Cette thèse présente trois différents circuits qui ont été implémentés dans cette optique. Les interconnexions de ces trois circuits peuvent être reconfigurées pour supporter une interface de type bidirectionnelle drain-ouvert, de type analogique ou différentielle, le tout au travers un réseau d'interconnexions configurable numérique unidirectionnel, ou FPIN. Le besoin d'une telle interface fut tout d'abord envisagé dans le contexte du WaferBoard, qui consiste en une plateforme reconfigurable de prototypage pour les systèmes électroniques. Le cœur de ce WaferBoard consiste en un circuit intégré à l'échelle d'une tranche entière de silicium, qui est constitué d'une matrice bidimensionnelle de cellules. Une large partie de la surface disponible s'en retrouve déjà utilisée par des plots configurables (CIO), l'aiguillage des multiplexeurs du FPIN, des registres dédiés à la chaine JTAG et d'autres circuiteries de contrôle. De ce fait, il en devient primordial que les interfaces bidirectionnelle drain-ouvert, analogique et différentielle soit les plus compactes possibles. Puisque ces circuits d'interfaces seront dédiés pour une plateforme utilisant une tranche de silicium (wafer-scale), l'architecture de ces derniers doit être robuste en regard des variations de procédé, de la température ainsi que de l'alimentation.

La première contribution de cette thèse est l'élaboration et la conception d'une interface de type drain-ouvert ainsi que de son support d'interconnexion bidirectionnel utilisant un réseau numérique unidirectionnel à signalisation asymétrique (à l'opposé de la signalisation différentielle) FPIN. L'interface proposée peut interconnecter plusieurs nœuds d'un FPIN. À l'aide de cette interface, le réseau d'interconnexions peut imiter le comportement et le fonctionnement d'un bus de type drain-ouvert (ou collecteur-ouvert) (tel qu'utilisé par le protocole  $I^2C$ ). De ce fait, plusieurs plots de type drain-ouvert provenant d'une multitude de circuits-intégrés (ICs) différents peuvent y être connectés au travers le FPIN à l'aide de l'interface proposée. Cette interface a été fabriquée en technologie CMOS 0.13 µm et occupe une surface de 65 µm × 22 µm par plot. Les résultats expérimentaux démontrent que plusieurs instances de cette interface peuvent être interconnectées entre eux en utilisant l'architecture d'interconnexions proposée. Cette architecture combinant six plots de type drain-ouvert a été

testée. Les délais de propagation sur cette interconnexion sont approximés par  $0.26 \cdot n + 51$  ns et  $0.26 \cdot n + 94$  ns pour les fronts montants et descendants lorsque chaque plot a une charge capacitive de 15 pF à sa sortie, où n est le nombre d'interfaces connectées. Ces délais, combinés au délai de propagation du FPIN, sont les facteurs limitant le nombre maximal d'interfaces pouvant y être connectées simultanément pour une vitesse de communication donnée. À titre d'exemple, le prototype d'interface peut supporter plus de 20 unités de type I<sup>2</sup>C Mode Rapide Plus  $(3.4 \, \text{Mbit/s})$ .

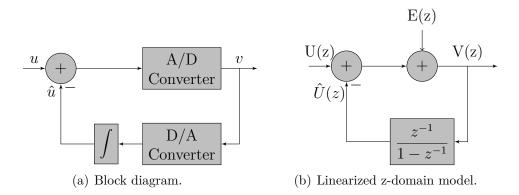

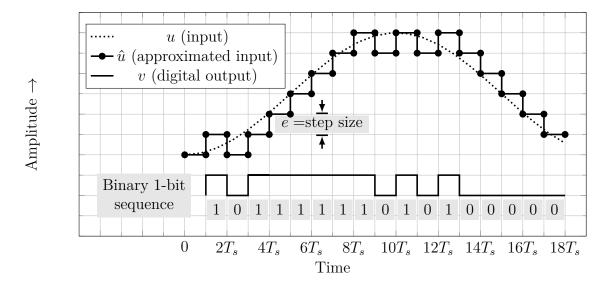

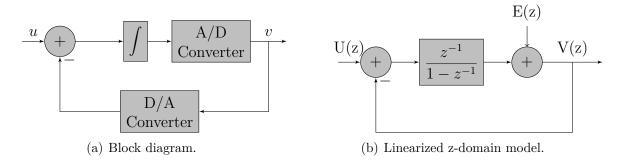

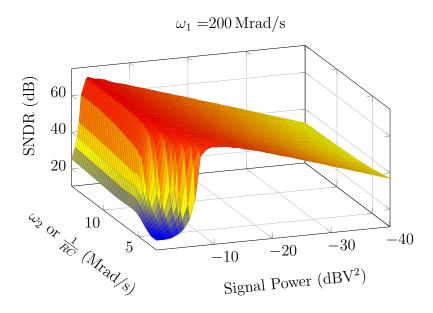

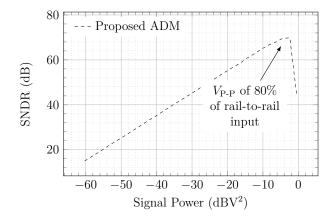

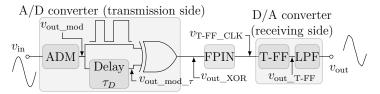

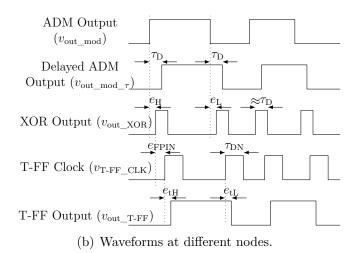

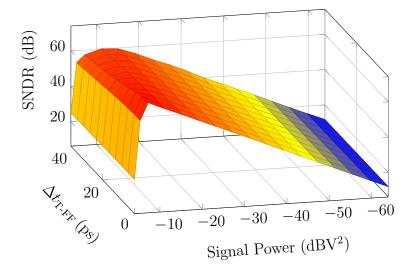

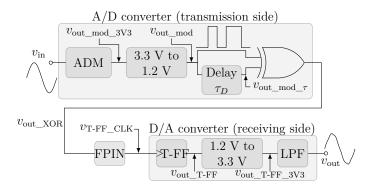

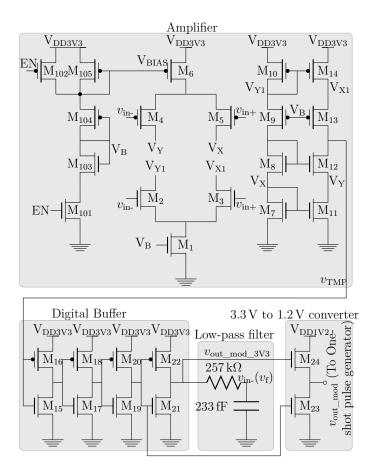

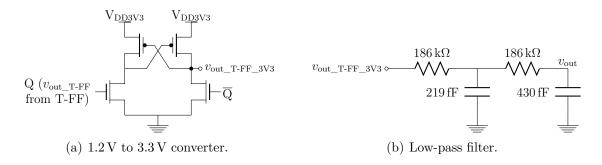

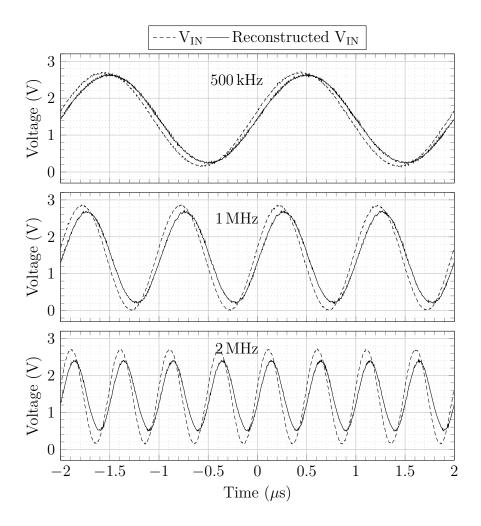

La deuxième contribution de cette thèse de doctorat décrit une interface analogique qui comprend un convertisseur analogique/numérique (A/N) (transmetteur) et un convertisseur numérique/analogique (NA) (récepteur) afin de permettre la propagation d'un signal analogique au travers une plateforme de prototypage de type FPIN. Le circuit intégré (uIC) transmetteur fournit le signal au convertisseur A/N. Ce dernier convertit le dit signal dans le domaine numérique pouvant se propager dans la plateforme FPIN jusqu'au récepteur. Un convertisseur N/A se situant du côté de la réception effectue la conversion afin de reproduire le signal analogique original pour le transmettre à l'uIC de destination. Cependant, les contraintes de surface de silicium de la plateforme de prototypage visée étant extrêmes, une conception très compacte fut requise pour les deux types de convertisseurs. Les convertisseurs de type sur-échantillonnage ne peuvent être utilisés dû aux performances exigées par ce type de convertisseurs pour les composantes analogiques (i.e. amplificateurs, comparateurs, résistances, sources de courant ou capacités) en plus du filtrage numérique requérant une surface de silicium relativement grande. La seconde contribution de cette thèse se situe donc dans l'élaboration et le développement d'un circuit très compact utilisant une version asynchrone d'un modulateur de type  $\Delta$  (asynchonous  $\Delta$  modulator - ADM) pour effectuer la conversion du domaine analogique vers le numérique. Ce convertisseur est proposé comme un moyen de transmettre un signal analogique à l'aide d'un réseau numérique d'interconnexions. Une analyse détaillée du mécanisme de conversion A/N du circuit ADM est également présentée dans cette thèse. Une méthode d'analyse graphique a été utilisée pour évaluer la fréquence d'oscillation de l'ADM afin de paramétrer le dit circuit. L'équivalence du spectre fréquentiel du signal d'entrée modulé ainsi que le spectre basse fréquence de la sortie de l'ADM, obtenu en utilisant un simple filtre de type passe-bas, peut être utilisé en guise de convertisseur N/A pour effectuer la reconstruction du signal analogique d'entrée. Le circuit ADM a été fabriqué dans une technologie CMOS 0.13 µm. Les mesures effectuées sur le circuit montrent des SNR et SNDR de 57 et 47 dB respectivement pour une bande passante de 2 MHz. L'ADM occupe une surface active de silicium de  $45 \,\mu\text{m} \times 22 \,\mu\text{m}$ . L'ensemble des convertisseurs A/N et N/A demande un courant total de 0.15 mA avec une alimentation de 3.3V pour une surface totale de  $45 \,\mu\text{m} \times 46 \,\mu\text{m}$ . Lorsque comparé avec des convertisseurs A/N similaires, le circuit ADM

peut supporter des signaux de bande passante modérée pour une résolution moyenne mais occupe une surface de silicium très réduite.

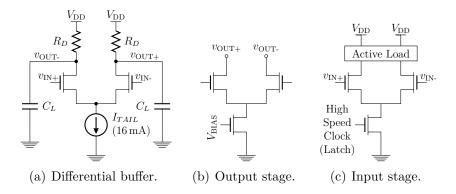

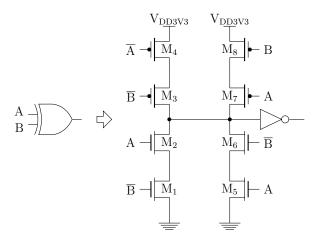

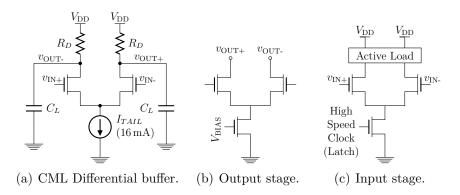

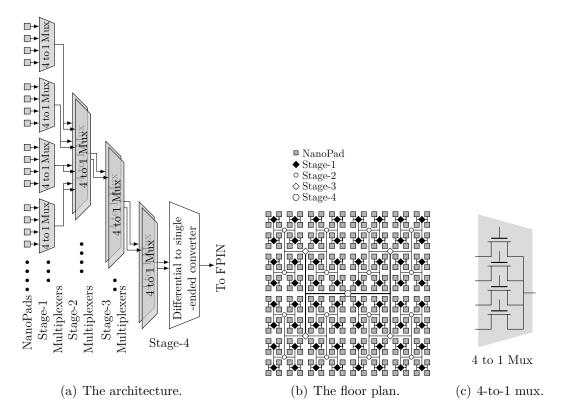

Une interface différentielle de reconfiguration spatiale a également été développée pour supporter la logique dite en mode courant (CML) pour la transmission de signaux au travers un réseau numérique unidirectionnel à signalisation asymétrique d'une plateforme de type FPIN (WaferBoard). Cette interface a été développée en collaboration avec Oliver Valorge, un stagiaire postdoctoral de l'École Polytechnique de Montréal. Deux types d'étages d'entrée pour l'interface différentielle ont été investiguées. Le premier type est basé sur un tampon de gain unitaire utilisant des multiplexeurs et a été entièrement développé et élaboré par Olivier Valorge. L'étage d'entrée de ce premier circuit occupe une surface de silicium relativement grande, c'est pourquoi une seconde alternative a été développée et élaborée par l'auteur de cette thèse afin de réduire le coût en surface de l'étage d'entrée. Cette thèse de doctorat comporte donc une troisième contribution en lien avec le développement d'un étage d'entrée différentiel basé sur des multiplexeurs à transistors passifs. Cet étage a été dessiné pour une technologie CMOS 0.13 µm et des validations après le dessin des masques ont été effectuées pour établir la faisabilité du concept. Des plots complémentaires différentiels peuvent être détectés sur une surface maximale de  $2 \,\mathrm{mm} \times 2 \,\mathrm{mm}$  ( $1 \,\mathrm{mm} \times 1 \,\mathrm{mm}$  dans le pire cas) sur la surface de la plateforme de prototypage. Les deux étages d'entrées proposés utilisent une structure d'arbre en H configurable afin d'équilibrer la propagation des signaux différentiels. L'étage d'entrée, basé sur un multiplexage de tampons de gain unitaire peut supporter un flot de données jusqu'à 2.5 Gbps avec 200 mV de dégagement sous des conditions typiques compatibles avec la spécification PCIe. Pour l'autre approche l'étage d'entrée utilise des multiplexeurs à transistors et peut opérer jusqu'à 2 Gbps. Cependant, le circuit occupe une surface plus faible (5%) en comparaison avec la première solution.

#### **ABSTRACT**

Field programmable interconnection networks (FPINs) are ubiquitously found embedded in field-programmable gate arrays (FPGAs), in prototyping platforms, and in many Network-on-Chip architectures. The aim of this research was to augment the application domains of current FPIN-based prototyping and emulation platforms by supporting open-drain bi-directional signals, analog signals or differential signals. Three interface circuits have been elaborated and developed to that end in this thesis. These three interface circuits can support reconfigurable routing of open-drain bi-directional, analog and differential signals through an uni-directional digital FPIN. The need for such interface circuits were originally conceived in the context of the WaferBoard, a system prototyping platform. The core of the WaferBoard is a wafer-scale IC that is composed of a two dimensional array of unit cells. Available area was already over-utilized by the configurable I/O (CIO) buffers, crossbar multiplexers of the FPIN, registers of the JTAG chain, and other control circuits. Thus, the interface circuits for open-drain bi-directional, analog and differential signalling had to be made very compact. As the implementation of these interface circuits target "wafer-scale" integration, these interface circuits had to be very robust to parametric variations (process, temperature, power supply).

The first contribution of this thesis is the elaboration and development of an open-drain interface circuit and a corresponding interconnect topology to support bi-directional communication through the uni-directional digital FPIN of prototyping platforms. The proposed interface can interconnect multiple nodes in a FPIN. With that interface, the interconnection network imitates the behaviour of open-drain (or open-collector) buses (e.g., those following the I<sup>2</sup>C protocol). Thus, multiple open-drain I/Os from external integrated circuits (ICs) can be connected together through the FPIN by the proposed interface circuit. The interface that has been fabricated in a  $0.13 \,\mu m$  CMOS technology takes  $65 \,\mu m \times 22 \,\mu m$  per pin. Test results show that several instances of this interface can be interconnected through the proposed interconnect topology. The interconnect topology combining six open-drain I/Os was implemented and tested. The interconnect has propagation delays of approximately  $0.26 \cdot n + 51 \text{ ns}$ and  $0.26 \cdot n + 94$  ns for rising and falling edge transitions respectively, when each pin has a capacitance of 15 pF, where n is the number of interconnected interfaces. These delays and the propagation delays of the FPIN limit the maximum number of interface circuits that can be interconnected for a given communication speed (i.e. I<sup>2</sup>C Fast-mode Plus with 3.4 Mbit/s). The prototype interface units can support more than 20 I<sup>2</sup>C Fast-mode Plus devices.

The second contribution relates to an analog interface circuit that comprises A/D (transmit-

ter) and D/A (receiver) converters to support analog signal propagation through the digital FPIN of the prototyping platform. Transmitting user integrated circuit (uIC) provides the analog signal to the A/D converter. The A/D converter converts it into a digital format that can be propagated through the digital FPIN to the receiving side. The receiving side comprises a D/A converter that can reproduce the original analog signal and provide it to the receiving user integrated circuit. However, due to the stringent constraints on the available silicon area, a very compact implementation of A/D and D/A converters were required for compatibility with the prototyping platform. Conventional Nyquist-rate and oversampled converters could not be utilized, because of their respective requirements of high-accuracy analog components (amplifiers, comparators, resistors, current sources or capacitors) and digital filtering that require comparatively large silicon area. Thus, the second contribution of this thesis is the elaboration and development of a compact circuit-implementation of an asynchronous  $\Delta$ -modulator (ADM) for A/D conversion. This data converter was proposed as a means to propagate analog signals into digital interconnection networks. A detailed analysis of the A/D conversion mechanism of the proposed ADM circuit is presented in this thesis. A graphical method is used to analyze and evaluate the inherent oscillation frequency of the proposed ADM circuit in terms of its circuit parameters. Due to the equivalence of the spectrum of the modulating input signal and the low-frequency spectrum of the ADM output, a simple low-pass filter can be used as D/A converter to reconstruct the input analog signal. The proposed ADM was fabricated in a 0.13 µm CMOS technology. Measurement results showed SNR and SNDR of 57 and 47dB respectively for an input bandwidth of  $2\,\mathrm{MHz}$ . The ADM occupies  $45\,\mu\mathrm{m} \times 22\,\mu\mathrm{m}$  active area. The entire A/D and D/A converterpair consumes  $0.15\,\mathrm{mA}$  from a  $3.3\,\mathrm{V}$  supply and occupies  $45\,\mu\mathrm{m} \times 46\,\mu\mathrm{m}$  area. Compared to other similar A/D converters, the proposed ADM supports moderate signal bandwidth and medium-resolution, while requiring very small area.

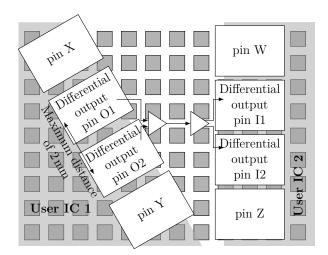

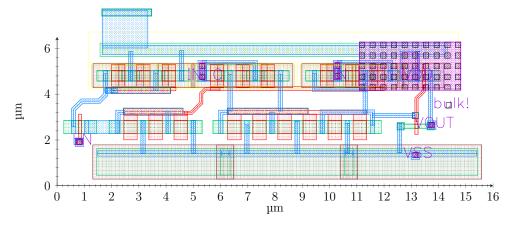

A spatially reconfigurable differential interface was also developed to support current mode logic (CML) signal transmission through the single-ended digital FPIN of the prototyping platform (WaferBoard). It was developed in collaboration with Olivier Valorge, a post-doctoral fellow at Polytechnique Montréal. Two types of input stage for the differential interface were investigated. The first input stage, based on unity-gain buffer based multiplexers, was developed and elaborated by Olivier Valorge. In that first circuit, the input stage occupied a relatively larger silicon area. Thus, an alternate input stage was developed and elaborated by the author to reduce the cost of the first input stage. Thus, the third contribution of this thesis is the elaboration and development of a differential input stage based on pass-transistor based multiplexers. This input stage was laid out in a 0.13 µm CMOS technology and post-layout simulation was used to validate the feasibility of the concept. Complementary pins

of differential pair spread over a maximum area of  $2\,\mathrm{mm}\times2\,\mathrm{mm}$  ( $1\,\mathrm{mm}\times1\,\mathrm{mm}$  in the worst case scenario) on the surface of the prototyping platform can be supported. Both versions of the proposed input stage utilized configurable H-tree structures for balanced differential signal propagation. The input stage, based on unity-gain buffer multiplexers, can support data rates of up to  $2.5\,\mathrm{Gbps}$ , with  $200\,\mathrm{mV}$  of voltage swing under typical conditions compatible with PCIe specifications. The input stage, based on pass-transistor multiplexers, can support data rates of up to  $2\,\mathrm{Gbps}$  while occupying significantly less area (5%) compared to the unity-gain buffer based input stage.

# TABLE OF CONTENT

| DEDIC  | ATION                                             |

|--------|---------------------------------------------------|

| ACKNO  | OWLEDGEMENTS iv                                   |

| RÉSUM  | ſÉ                                                |

| ABSTR  | ACT viii                                          |

| TABLE  | OF CONTENT xi                                     |

| LIST O | F TABLE xv                                        |

| LIST O | F FIGURES xvi                                     |

| LIST O | F ABBREVIATION                                    |

| LIST O | F APPENDICES                                      |

| CHAPT  | TER 1 INTRODUCTION                                |

| 1.1    | Active Reconfigurable Board Overview              |

| 1.2    | Enhanced Programmable Devices (EPDs)              |

| 1.3    | Motivation                                        |

|        | 1.3.1 Open-drain Bi-directional communication     |

|        | 1.3.2 Analog Signal Communication                 |

|        | 1.3.3 Differential Signal communication           |

| 1.4    | High Level Objectives of This Research            |

| 1.5    | Organization of Thesis                            |

| СНАРТ  | TER 2 BACKGROUND INFORMATION AND RELATED PREVIOUS |

| WO     | RKS                                               |

| 2.1    | Active Reconfigurable Platform [1]                |

|        | 2.1.1 WaferNet                                    |

|        | 2.1.2 Silicon Area Constraints of WaferIC         |

| 2.2    | Bi-Directional Interface                          |

|        | 2.2.1 $I^{2}C$ Bus                                |

| 2.3    | Analog Interface                                  |

|       | 2.3.1 A             | Analog to Digital Converter                                          | 14 |

|-------|---------------------|----------------------------------------------------------------------|----|

|       | $2.3.2$ $\triangle$ | <b>\</b> -Modulator                                                  | 15 |

|       | $2.3.3$ $\Sigma$    | $\Delta \Delta \operatorname{Modulator} \ldots \ldots \ldots \ldots$ | 17 |

|       | 2.3.4 A             | asynchronous $\Sigma\Delta$ Modulator                                | 22 |

| 2.4   | Different           | ial Interface                                                        | 24 |

|       | 2.4.1 C             | Compatibility with the WaferBoard                                    | 24 |

|       | 2.4.2 P             | Physical and Electrical Constraints of Differential Signaling        | 25 |

| CHAPT | TER 3 O             | RGANIZATION OF THESIS                                                | 26 |

| 3.1   | Organiza            | ation of Thesis                                                      | 26 |

| 3.2   | Article-1           | and Article-2                                                        | 26 |

|       | 3.2.1 A             | Article-1 (Chapter 4)                                                | 26 |

|       | 3.2.2 A             | Article-2 (Chapter 5)                                                | 27 |

| 3.3   | Article-3           | 6 (Chapter 6)                                                        | 27 |

| 3.4   | Article-4           | (Chapter 7) and Chapter 8                                            | 28 |

|       | 3.4.1 A             | Article-4 (Chapter 7)                                                | 28 |

|       | 3.4.2 C             | Chapter 8                                                            | 29 |

| CHAPT | TER 4 A             | ARTICLE 1: AN INTERFACE FOR I <sup>2</sup> C PROTOCOL IN WAFER-      |    |

| BOA   | $ARD^{TM}$          |                                                                      | 30 |

| 4.1   | Introduc            | tion                                                                 | 31 |

| 4.2   | Backgrou            | und                                                                  | 31 |

| 4.3   | Proposed            | d Interface for I <sup>2</sup> C Compatibility                       | 33 |

| 4.4   | Simulation          | on Results                                                           | 37 |

| 4.5   | Conclusi            | on                                                                   | 38 |

| CHAPT | ΓER 5 A             | RTICLE 2: AN INTERFACE FOR OPEN-DRAIN BI-DIRECTIONAL                 |    |

| COI   | MMUNIC.             | ATION IN FIELD PROGRAMMABLE INTERCONNECTION NET-                     |    |

| WO    | RKS                 |                                                                      | 39 |

| 5.1   | Introduc            | tion                                                                 | 40 |

| 5.2   | Backgrou            | und                                                                  | 42 |

|       | 5.2.1 A             | Active Reconfigurable Platform [1]                                   | 42 |

|       | 5.2.2 C             | Open-drain Connection Based Communication                            | 42 |

| 5.3   | Proposed            | d Architecture of the Bi-Directional Interface                       | 42 |

|       | 5.3.1 V             | Vorking Principle of the Bi-Directional Interface                    | 44 |

|       | 5.3.2 S             | tate-Latching Phenomenon                                             | 46 |

|       | 533 T               | The Ring-Interconnection Network of the Ri-Directional Interface     | 47 |

|            | 5.3.4  | Queue and Dual-Queue Interconnection Topologies                                          | 53  |

|------------|--------|------------------------------------------------------------------------------------------|-----|

|            | 5.3.5  | Proposed Bi-Directional Interface                                                        | 54  |

|            | 5.3.6  | Propagation Delay of Dual-Queue Interconnection Topology                                 | 54  |

|            | 5.3.7  | Maximun Number of Interface Units in a Dual-Queue Interconnection                        |     |

|            |        | Topology                                                                                 | 58  |

| 5.4        | Protot | type Test-Chip and Measurement Results                                                   | 59  |

|            | 5.4.1  | Design Specification of the Bi-directional Interface                                     | 60  |

|            | 5.4.2  | Delay Characterization of the Bi-directional Interface from Post-Layout                  |     |

|            |        | Simulation                                                                               | 61  |

|            | 5.4.3  | Test-chip and Test-bench Specifications                                                  | 63  |

|            | 5.4.4  | Measurement results from dual-queue topology with 8 interface units                      | 63  |

| 5.5        | Concl  | usion                                                                                    | 65  |

| СНАРТ      | ΓER 6  | ARTICLE 3: AN ASYNCHRONOUS DELTA-MODULATOR BASED                                         |     |

| $A/\Gamma$ | CON    | VERTER FOR AN ELECTRONIC SYSTEM PROTOTYPING PLAT-                                        |     |

| FOI        | RM     |                                                                                          | 67  |

| 6.1        | Introd | luction                                                                                  | 68  |

| 6.2        | Backg  | round                                                                                    | 69  |

|            | 6.2.1  | Field Programmable Interconnection Networks                                              | 69  |

|            | 6.2.2  | The Target Application: Prototyping Platform [1]                                         | 70  |

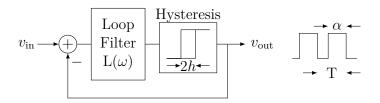

|            | 6.2.3  | Analog Interface Based on Asynchronous $\Sigma\Delta$ Modulation or $\Delta$ -Modulation | . 7 |

|            | 6.2.4  | Limitations of Existing Asynchronous $\Sigma\Delta$ Modulator Implementations            | 72  |

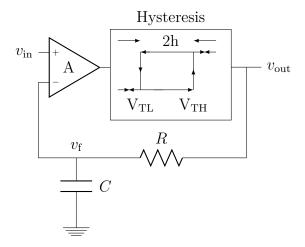

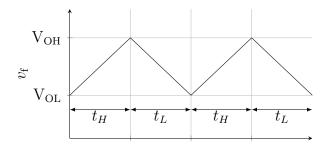

| 6.3        | Propo  | sed Asynchronous $\Delta$ -Modulator                                                     | 74  |

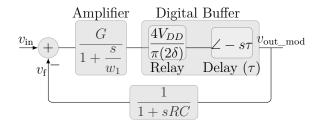

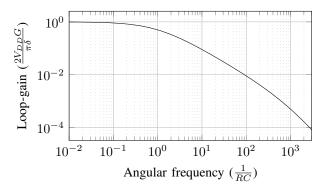

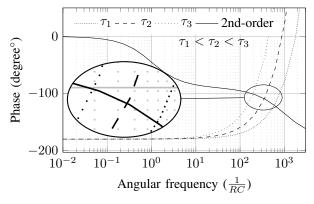

|            | 6.3.1  | Proposed Asynchronous $\Delta$ -Modulator                                                | 74  |

|            | 6.3.2  | Working Principle of the Proposed Asynchronous $\Delta$ -Modulator                       | 75  |

|            | 6.3.3  | Behavioral Simulation of the Asynchronous $\Delta$ -Modulator                            | 77  |

| 6.4        | Propo  | sed Analog Interface Circuit and Post-Layout Simulation Results                          | 79  |

|            | 6.4.1  | ADM-based Analog Interface                                                               | 79  |

|            | 6.4.2  | Implementation                                                                           | 82  |

|            | 6.4.3  | Behavioral and Post Layout Simulation of the Asynchronous $\Delta$ -Modulator            | 84  |

| 6.5        | Protot | type Test-Chip and Measurement Results                                                   | 86  |

|            | 6.5.1  | Measurement Results                                                                      | 86  |

|            | 6.5.2  | Comparison with Other Published A/D Converters                                           | 89  |

| 6.6        | Concl  | usion                                                                                    | 93  |

| СНАРТ      | ΓER 7  | ARTICLE 4: A NOVEL SPATIALLY CONFIGURABLE DIFFEREN-                                      |     |

TIAL INTERFACE FOR AN ELECTRONIC SYSTEM PROTOTYPING PLAT-

| FOI   | RM      |                                                                            | 96  |

|-------|---------|----------------------------------------------------------------------------|-----|

| 7.1   | Introd  | uction                                                                     | 97  |

| 7.2   | Backg   | round                                                                      | 99  |

|       | 7.2.1   | Compatibility with WaferBoard, a Prototyping Platform for Electronic       |     |

|       |         | Systems                                                                    | 99  |

|       | 7.2.2   | Physical and Electrical Constraints                                        | 99  |

| 7.3   | Propo   | sed Architecture and Circuit Implementation of the Differential Interface  | 101 |

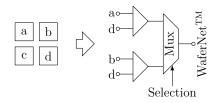

|       | 7.3.1   | Propagation Network : WaferNet $^{\text{\tiny TM}}$                        | 104 |

|       | 7.3.2   | Input Stage                                                                | 104 |

|       | 7.3.3   | H-Tree Input Differential Network                                          | 105 |

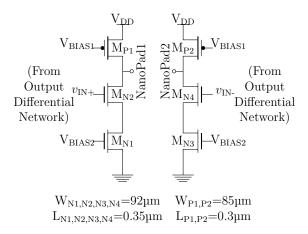

|       | 7.3.4   | Output Differential Network                                                | 107 |

| 7.4   | Measu   | red Results                                                                | 108 |

| 7.5   | Conclu  | usion                                                                      | 110 |

| CHAPT | ΓER 8   | PASS-TRANSISTOR MULTIPLEXER BASED DIFFERENTIAL IN                          | _   |

| PUT   | ΓSTAC   | E                                                                          | 112 |

| 8.1   | Differe | ential Interface Based on Unity-Gain Buffer Multiplexer                    | 112 |

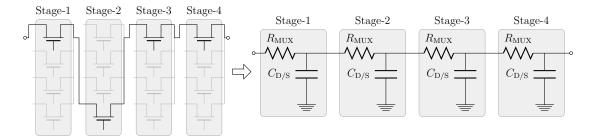

| 8.2   | Differe | ential Input Stage based on Pass-Transistor Multiplexer                    | 113 |

|       | 8.2.1   | H-Tree Input Differential Network                                          | 113 |

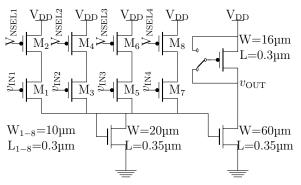

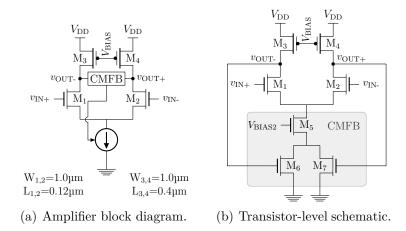

|       | 8.2.2   | Differential-to-Single Ended Converter                                     | 115 |

| 8.3   | Simula  | ation Results                                                              | 117 |

|       | 8.3.1   | Input stage with differential amplifier and differential output            | 117 |

|       | 8.3.2   | Input stage with current mode differential-to-single-ended converter $\ .$ | 121 |

|       | 8.3.3   | Comparison between the input stage based on unity-gain buffer multi-       |     |

|       |         | plexer and the input stage based on pass-transistor multiplexer            | 124 |

| 8.4   | Summ    | ary of Contribution                                                        | 126 |

| СНАРТ | ΓER 9   | GENERAL DISCUSSION                                                         | 129 |

| 9.1   | Bi-Dir  | rectional Interface                                                        | 129 |

| 9.2   | ADM-    | based Analog Interface                                                     | 129 |

| 9.3   | Differe | ential Signal Interface                                                    | 130 |

| CONCI | LUSION  | 1                                                                          | 131 |

| REFER | RENCE   | S                                                                          | 134 |

| APPEN | IDICES  |                                                                            | 142 |

# LIST OF TABLE

| Table 2.1 | Area of an unit cell in a test-chip that was previously fabricated in                |     |

|-----------|--------------------------------------------------------------------------------------|-----|

|           | TowerJazz's 0.18 µm CMOS technology                                                  | 11  |

| Table 4.1 | Corner Simulation                                                                    | 38  |

| Table 4.2 | Area of the interface                                                                | 38  |

| Table 5.1 | Pull-down current of open-drain buses                                                | 47  |

| Table 5.2 | Different states with respect to the voltage level of the BDIO node                  | 47  |

| Table 5.3 | Delays and rise/fall times of the interface circuit                                  | 55  |

| Table 5.4 | Design specification of the bi-directional interface in the test-chip ac-            |     |

|           | cording to $I^2C$ Fast-mode Plus protocol                                            | 61  |

| Table 5.5 | Characterization of the Interface Circuit Based on Post Layout Circuit               |     |

|           | Simulations                                                                          | 62  |

| Table 6.1 | The values of $e_{\rm tH}$ and $e_{\rm tL}$ from post-layout simulation              | 83  |

| Table 6.2 | Comparison with published compact over<br>sampling $\mathrm{A}/\mathrm{D}$ converter | 92  |

| Table 7.1 | Characteristics of the differential interface from post-layout simulation.           | 109 |

| Table 7.2 | Areas of the differential interface and their stages for one four-stages             |     |

|           | interface unit                                                                       | 110 |

| Table 8.1 | Silicon area of the pass transistor based input stage                                | 119 |

| Table 8.2 | Comparison between the input stage based on unity-gain buffer multi-                 |     |

|           | plexer and the input stage based on pass-transistor multiplexer                      | 128 |

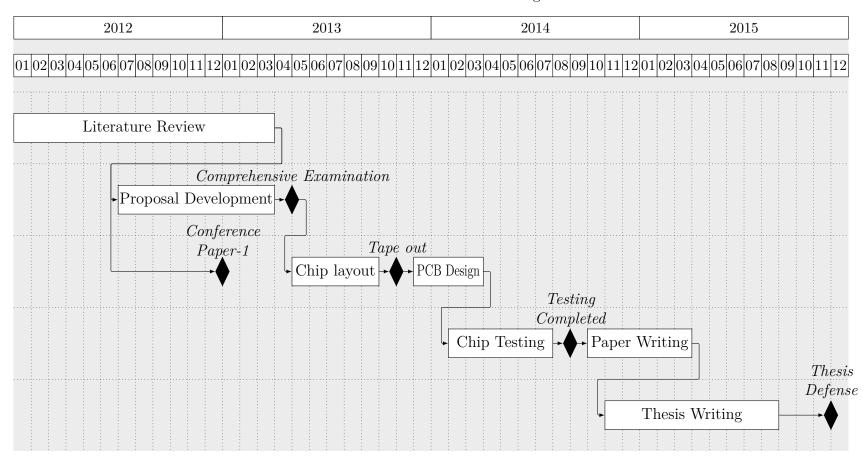

| Table B.1 | Timeline of the tasks leading to PhD                                                 | 146 |

# LIST OF FIGURES

| Figure 1.1  | Generic model of a field programmable interconnection network (FPIN) in a FPGA                                                                                                                                               | 6  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2  | Conceptual overview of the active reconfigurable board                                                                                                                                                                       | 3  |

| Figure 1.3  | Hierarchical description of the active reconfigurable board                                                                                                                                                                  | 3  |

| Figure 1.4  | Schematic diagram and propagation path of an electrical signal between two uICs pins in contact with the CIO/Nanopads on the WaferIC. The electrical signal propagates from a <i>source</i> uIC to a <i>destination</i> uIC. | 4  |

| Figure 1.5  | Possible uses of enhanced programmable devices (EPDs)                                                                                                                                                                        | 5  |

| Figure 2.1  | WaferNet showing the connections between neighboring 1, 2, 4, 8, 16 and 32 in all directions                                                                                                                                 | ę  |

| Figure 2.2  | Architecture of an unit cell [1] with configuration registers, CIOs and crossbar multiplexers                                                                                                                                | 10 |

| Figure 2.3  | $I^2C$ Bus                                                                                                                                                                                                                   | 12 |

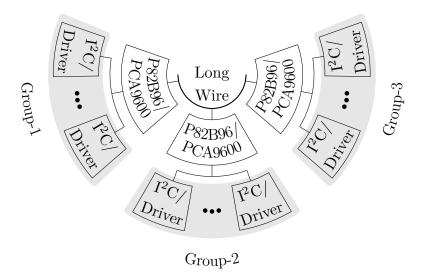

| Figure 2.4  | Connection of P82B96/PCA9600 $I^2C$ bus extension buffers                                                                                                                                                                    | 13 |

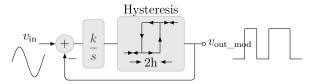

| Figure 2.5  | $\Delta$ -modulator                                                                                                                                                                                                          | 16 |

| Figure 2.6  | Waveform at various nodes of the $\Delta$ -modulation in Fig. 2.5(a)                                                                                                                                                         | 16 |

| Figure 2.7  | $\Sigma\Delta$ modulator                                                                                                                                                                                                     | 18 |

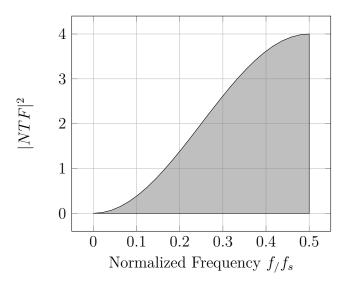

| Figure 2.8  | Noise-shaping function for the $\Sigma\Delta$ modulator shown in Fig. 2.7(a)                                                                                                                                                 | 19 |

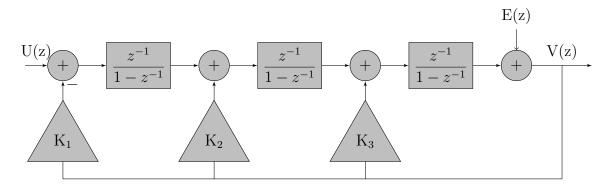

| Figure 2.9  | A third-order $\Sigma\Delta$ modulator                                                                                                                                                                                       | 20 |

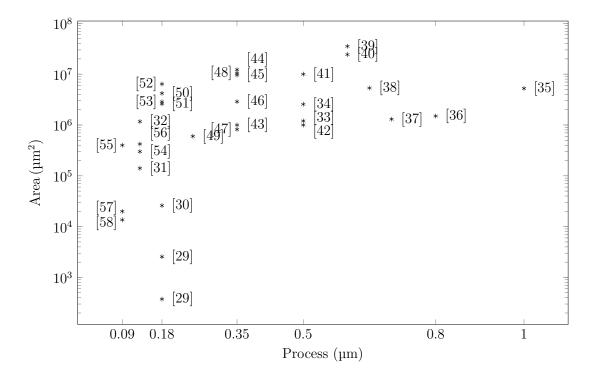

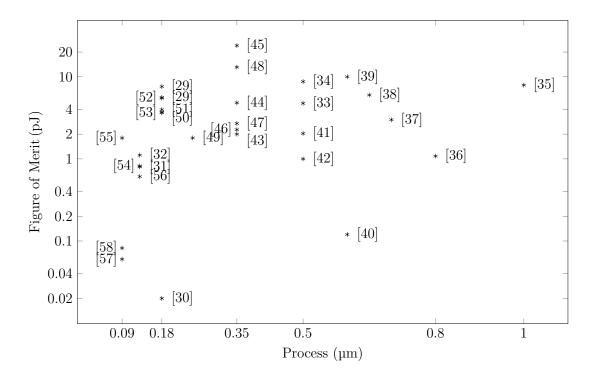

| Figure 2.10 | Comparison between $\Sigma\Delta$ modulators of given technology process node versus area ( $\mu m^2$ )                                                                                                                      | 21 |

| Figure 2.11 | Comparison between $\Sigma\Delta$ modulators of given technology process node versus FoM (pJ)                                                                                                                                | 21 |

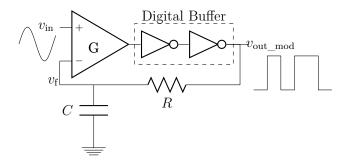

| Figure 2.12 | Asynchronous $\Sigma\Delta$ modulator                                                                                                                                                                                        | 23 |

| Figure 2.13 | Differential buffer structure                                                                                                                                                                                                | 25 |

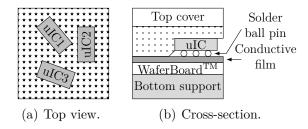

| Figure 4.1  | Wafer<br>IC $^{\rm TM}$ with ICs deposited: (a) top view, (b) cross section view                                                                                                                                             | 32 |

| Figure 4.2  | $I^2C$ Bus                                                                                                                                                                                                                   | 33 |

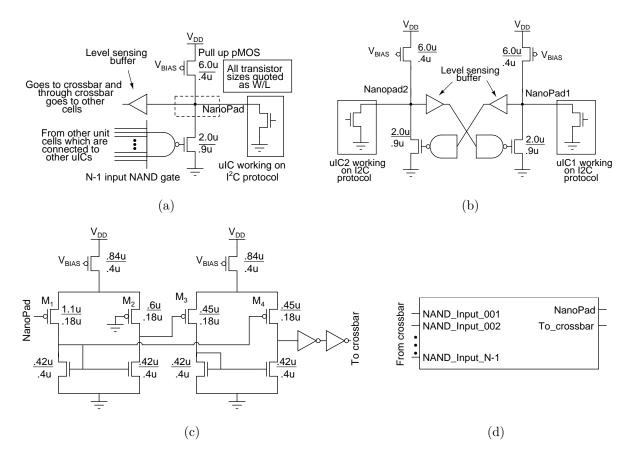

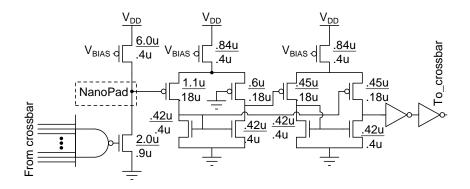

| Figure 4.3  | (a) Proposed interface. (b) Two instances of the interface interconnected together. (c) The level sensing buffer to remove the latching                                                                                      |    |

|             | problem. (d) Block diagram                                                                                                                                                                                                   | 35 |

| Figure 4.4  | Full schematic of the interface                                                                                                                                                                                              | 36 |

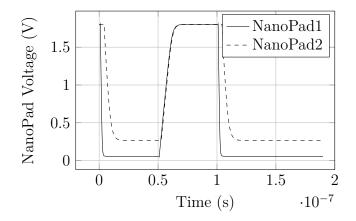

| Figure 4.5  | Simulation result                                                                                                                                                                                                            | 37 |

| Figure 5.1  | Generic model of an FPIN in an FPGA                                                                                                                                                                                          | 41 |

| Figure 5.2  | Hierarchical description of the active reconfigurable platform, from sys-            |    |

|-------------|--------------------------------------------------------------------------------------|----|

|             | tem level to configurable I/O (CIO)                                                  | 43 |

| Figure 5.3  | Example of an $I^2C$ -bus configuration                                              | 43 |

| Figure 5.4  | Each <i>circle</i> represents an interface unit circuit                              | 45 |

| Figure 5.5  | Development of the bi-directional interface unit circuit                             | 45 |

| Figure 5.6  | Development of pseudo-ring interconnection topology. Each circle re-                 |    |

|             | presents an interface unit circuit and is labelled $\mathrm{IU}\#.$                  | 48 |

| Figure 5.7  | Logical signal flow diagram. Low Detector module of each interface                   |    |

|             | unit (IU#) is labelled LD. Each BDIO node belongs to the respective                  |    |

|             | interface unit (IU) and represents distinct physical nodes                           | 50 |

| Figure 5.8  | Logical signal flow diagram of dual-queue interconnection topology.                  |    |

|             | Two individual queue network are joined together. Each queue net-                    |    |

|             | work have five interface units. Four interface units (labelled IU#) are              |    |

|             | connected to external ODD and one $Master\ unit$ (labelled MU). $Low$                |    |

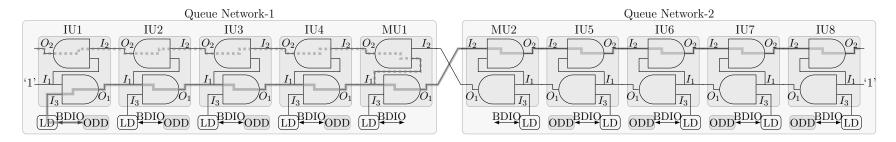

|             | Detector module of each interface unit (IU#) is labelled as LD. $$                   | 52 |

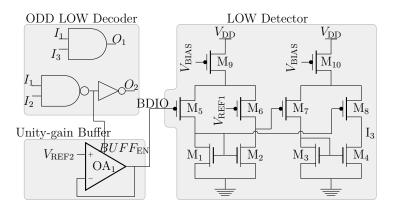

| Figure 5.9  | Schematic of the interface unit (IU)                                                 | 55 |

| Figure 5.10 | Detailed transistor-level schematic of the bi-directional interface unit             |    |

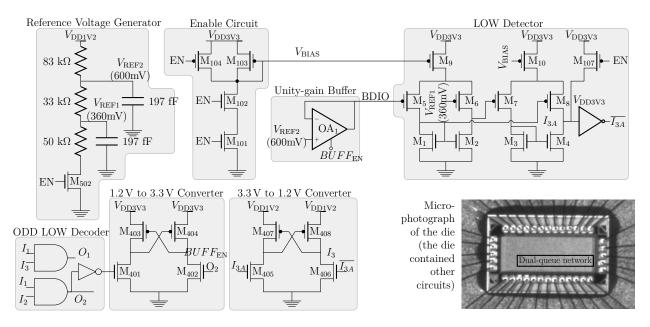

|             | and micro-photograph of the die                                                      | 59 |

| Figure 5.11 | Dual-queue interconnection topology with 8 interface units implemen-                 |    |

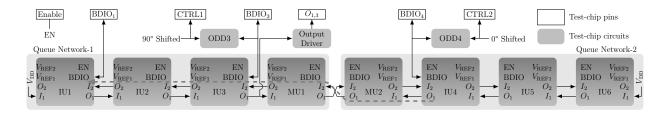

|             | ted in the test-chip                                                                 | 63 |

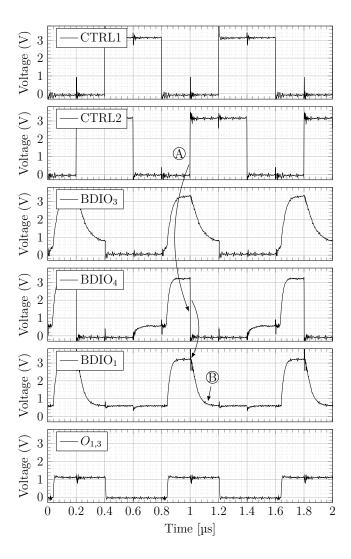

| Figure 5.12 | Measurement result of dual-queue interconnected network (shown in                    |    |

|             | Fig. 5.11) from the test-chip                                                        | 64 |

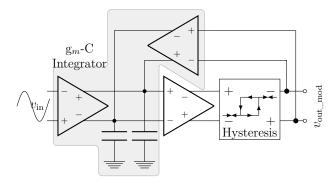

| Figure 6.1  | Asynchronous $\Sigma\Delta$ modulator                                                | 69 |

| Figure 6.2  | Generic FPIN model of a Field Programmable Interconnection Network.                  | 70 |

| Figure 6.3  | Hierarchical description of the reconfigurable board to CIO                          | 71 |

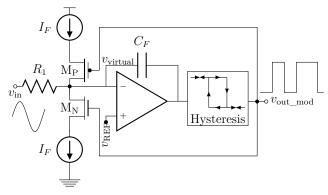

| Figure 6.4  | Different implementations of the generic asynchronous $\Sigma\Delta$ modulator.      | 73 |

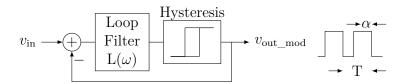

| Figure 6.5  | The proposed ADM                                                                     | 75 |

| Figure 6.6  | Proposed linear s-domain model of the ADM shown in Fig. 6.5                          | 76 |

| Figure 6.7  | Evaluation of the oscillation frequency of the asynchronous $\Sigma\Delta$ modulator |    |

|             | (ASDM)                                                                               | 77 |

| Figure 6.8  | Input signal frequency is 1 MHz                                                      | 78 |

| Figure 6.9  | High-level simulation with Simulink® of the proposed ADM architec-                   |    |

|             | ture model (Fig. 6.5). Input signal frequency is 1 MHz. Representative               |    |

|             | component noise sources are included but the RC-filter is ideal                      | 79 |

| Figure 6.10 | ADM-based analog interface                                                           | 80 |

| Figure 6.11 | Block diagram and waveform of the ADM-based analog interface                         | 81 |

| Figure 6.12 | Schematic of the X-OR gate                                                                          | 83  |

|-------------|-----------------------------------------------------------------------------------------------------|-----|

| Figure 6.13 | The effect of mismatch between $e_{\rm tH}$ and $e_{\rm tL}$ on the SNDR                            | 83  |

| Figure 6.14 | Detailed block diagram of the proposed ADM-based analog interface.                                  | 84  |

| Figure 6.15 | Schematic of the ADM & $3.3~\mathrm{V}$ to $1.2~\mathrm{V}$ converter (transmission side).          | 85  |

| Figure 6.16 | Schematic of the D/A converter (receiving side)                                                     | 85  |

| Figure 6.17 | Simulation of the proposed ADM based on s-model in Simulink® and                                    |     |

|             | post-layout simulations in Cadence ( $V_{\rm DD}=3.3~{\rm V}$ ) respectively. Simulink <sup>®</sup> |     |

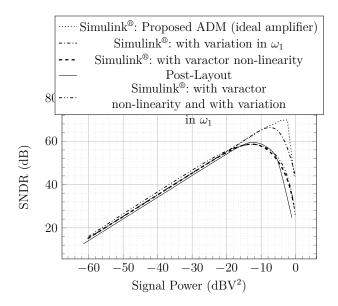

|             | model included the non-linearity of the filter                                                      | 86  |

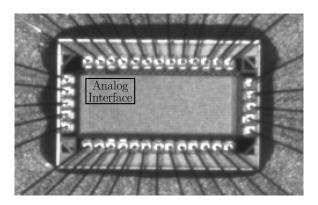

| Figure 6.18 | Micro-photograph of the die (the die contained other circuits)                                      | 87  |

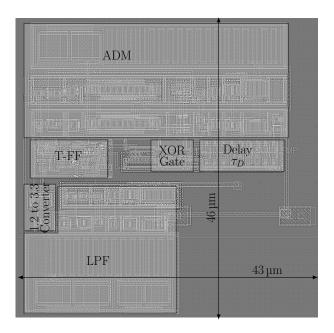

| Figure 6.19 | Layout of the ADM and LPF to reconstruct the input signal                                           | 88  |

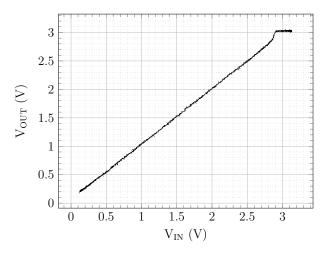

| Figure 6.20 | Measured DC transfer characteristics from the test-chip ( $V_{DD} = 3.3 \text{ V}$ )                |     |

|             | of the asynchronous $\Delta$ -modulator shown in Fig. 6.15                                          | 88  |

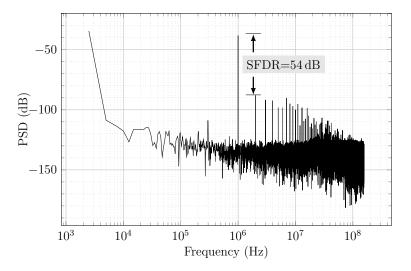

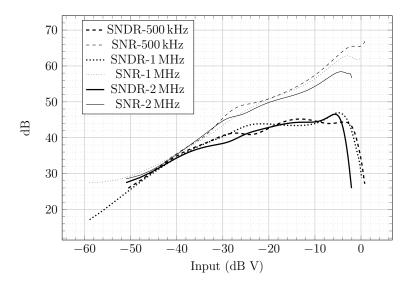

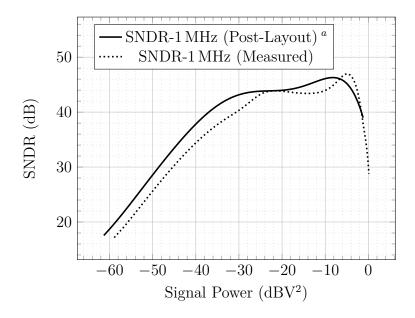

| Figure 6.21 | Measured noise performances from the test-chip                                                      | 89  |

| Figure 6.22 | Simulation of the proposed ADM in with noisy power supply to mimic                                  |     |

|             | the actual test-bench scenario                                                                      | 90  |

| Figure 6.23 | Comparison between $\Sigma\Delta$ modulators and the proposed $\Delta$ -modulator                   |     |

|             | on technology process node versus Area ( $\mu m^2$ ) and FoM (pJ)                                   | 91  |

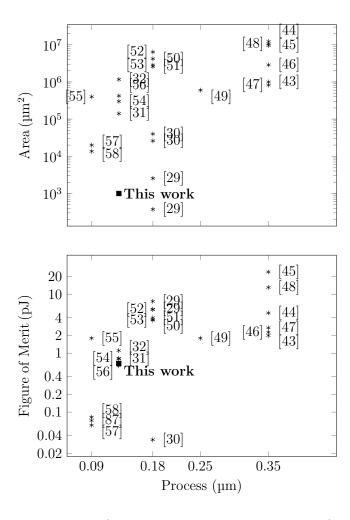

| Figure 6.24 | Measurement result for input frequency of $500\mathrm{kHz},1\mathrm{MHz},\mathrm{and}2\mathrm{MHz}$ |     |

|             | from the test-chip.                                                                                 | 95  |

| Figure 7.1  | CML structure                                                                                       | 98  |

| Figure 7.2  | Conceptual overview of the active reconfigurable platform                                           | 100 |

| Figure 7.3  | Differential pins of user's ICs interfacing with the NanoPad array of                               |     |

|             | the WaferIC (zoom of Fig. 7.2(a)) [3]                                                               | 100 |

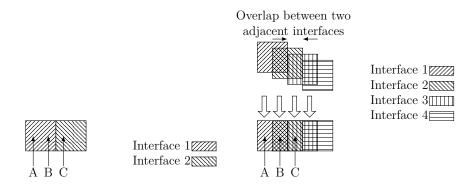

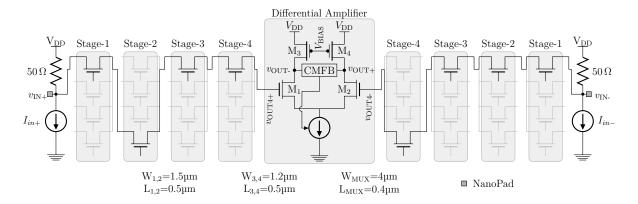

| Figure 7.4  | Architecture of the embedded differential propagation chain [3]                                     | 102 |

| Figure 7.5  | The input differential configurable network                                                         | 102 |

| Figure 7.6  | Tiling of differential interface unit                                                               | 103 |

| Figure 7.7  | Continuous floor plan of the architecture with overlap between adjacent                             |     |

|             | interface units. Each of the two shaded rectangles can be configured as                             |     |

|             | a differential interface unit                                                                       | 104 |

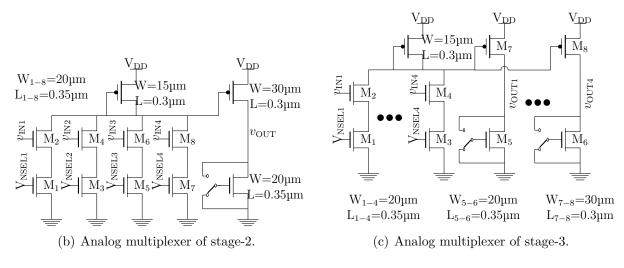

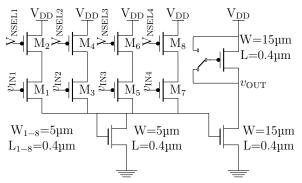

| Figure 7.8  | Schematic of the analog multiplexers                                                                | 106 |

| Figure 7.9  | Configurable differential-to-single-ended converter (the multiplexers in                            |     |

|             | these two figures are digital multiplexers)                                                         | 107 |

| Figure 7.10 | Schematic of the interface output circuit in each NanoPad                                           | 108 |

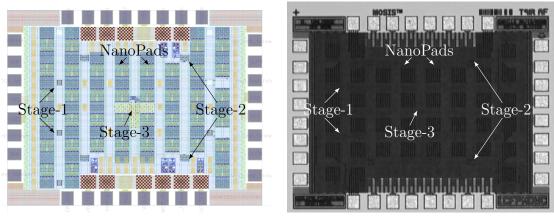

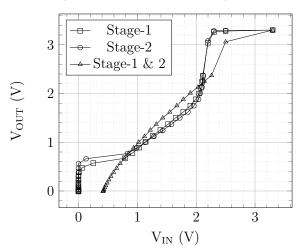

| Figure 7.11 | Test-chip                                                                                           | 109 |

| Figure 7.12 | Measured DC transfer characteristics ( $V_{DD}=3.3~V$ ) of the analog                               |     |

|             | multiplexers shown in Fig. 7.8                                                                      | 109 |

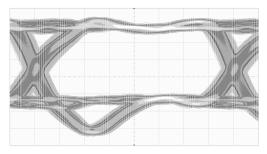

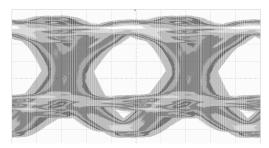

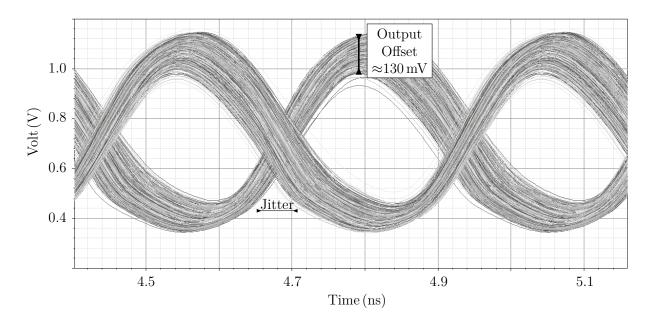

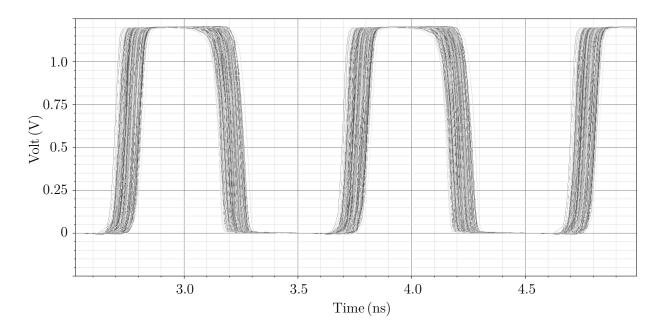

| Figure 7.13 | Measured eye diagrams at different data rates from test-chip 11                                                 | .1 |

|-------------|-----------------------------------------------------------------------------------------------------------------|----|

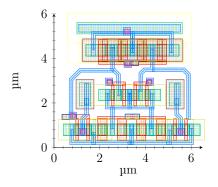

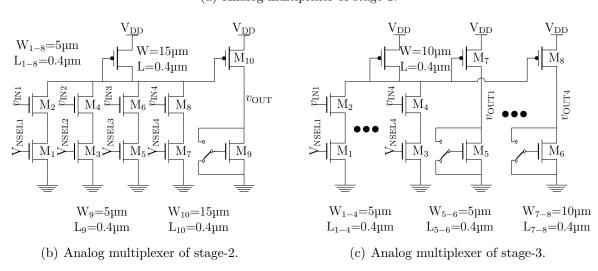

| Figure 8.1  | Architecture and floor plan of the pass transistor multiplexer based                                            |    |

|             | differential input stage                                                                                        | .4 |

| Figure 8.2  | Pass-transistor based model                                                                                     | .5 |

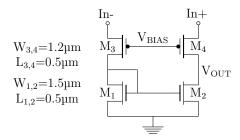

| Figure 8.3  | Differential amplifier with differential output                                                                 | .5 |

| Figure 8.4  | Schematic of the differential input stage and differential amplifier with                                       |    |

|             | differential output in stage-4                                                                                  | .6 |

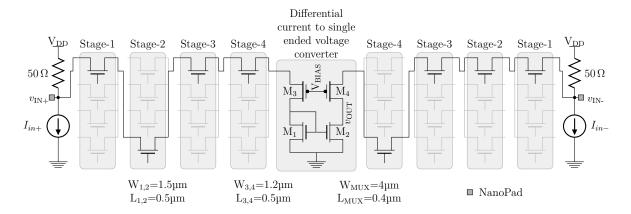

| Figure 8.5  | Proposed differential-to-single ended converter                                                                 | .6 |

| Figure 8.6  | Schematic of the differential input stage with the differential-to-single                                       |    |

|             | ended converter at Stage-4                                                                                      | .7 |

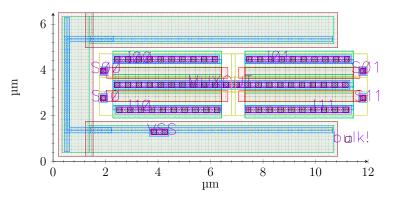

| Figure 8.7  | Layout                                                                                                          | .8 |

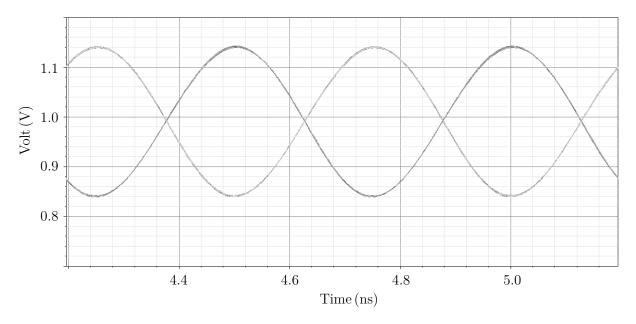

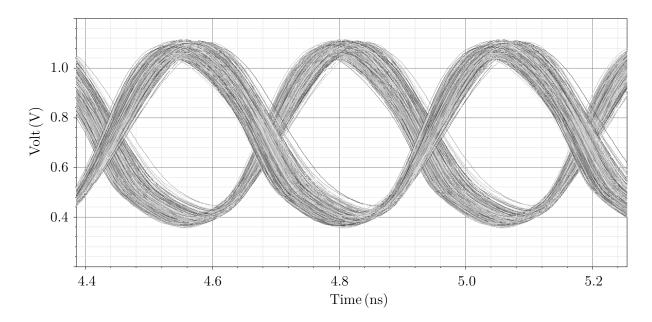

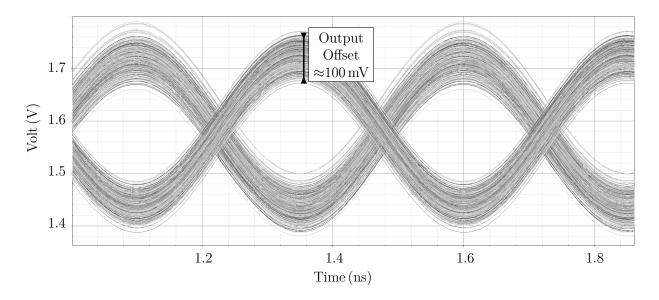

| Figure 8.8  | $2\mathrm{GHz}$ output ( $v_{\mathrm{OUT4+}}$ and $v_{\mathrm{OUT4-}}$ in Fig. 8.4) of stage-4 multiplexer      |    |

|             | from Monte Carlo <b>mismatch variation</b> (typical-typical) simulation.                                        |    |

|             | Input ( $v_{\text{IN-}}$ and $v_{\text{IN+}}$ in Fig. 8.4) common-mode voltage=1.0 V 11                         | .9 |

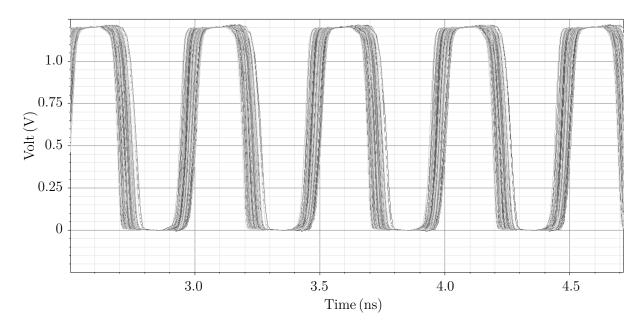

| Figure 8.9  | $2\mathrm{GHz}$ output ( $v_{\mathrm{OUT+}}$ and $v_{\mathrm{OUT-}}$ in Fig. 8.4) of stage-4 fully differential |    |

|             | amplifier from Monte Carlo mismatch variation (typical-typical) si-                                             |    |

|             | mulation. Input ( $v_{\text{IN-}}$ and $v_{\text{IN+}}$ in Fig. 8.4) common-mode voltage=1.0 V.12               | 20 |

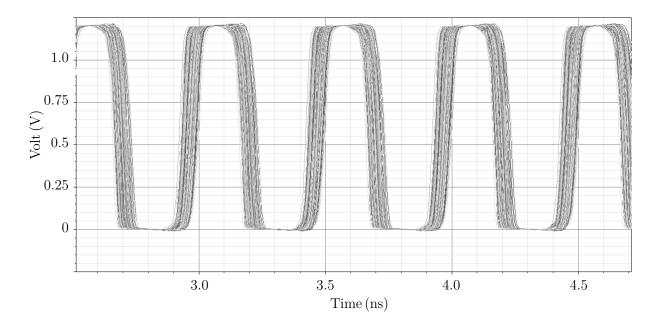

| Figure 8.10 | ${\bf 2GHz}$ output ( $v_{\rm OUT+}$ and $v_{\rm OUT-}$ in Fig. 8.4) of Stage-4 fully differential              |    |

|             | amplifier from Monte Carlo process variation (typical-typical) simu-                                            |    |

|             | lation. Input ( $v_{\text{IN-}}$ and $v_{\text{IN+}}$ in Fig. 8.4) common-mode voltage=1.0 V. 12                | 21 |

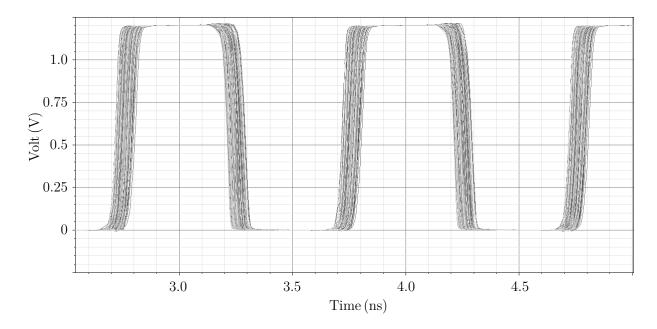

| Figure 8.11 | $2\mathrm{GHz}$ output ( $v_\mathrm{OUT}$ in Fig. 8.6) of the differential-to-single-ended                      |    |

|             | converter from Monte Carlo <b>mismatch variation</b> (typical-typical) si-                                      |    |

|             | mulation. Input ( $v_{\text{IN-}}$ and $v_{\text{IN+}}$ in Fig. 8.6) common-mode voltage=1.2 V.12               | 22 |

| Figure 8.12 | $2\mathrm{GHz}$ output ( $v_\mathrm{OUT}$ in Fig. 8.6) of the differential-to-single-ended                      |    |

|             | converter from Monte Carlo <b>mismatch variation</b> (typical-typical) si-                                      |    |

|             | mulation. Input ( $v_{\text{IN-}}$ and $v_{\text{IN+}}$ in Fig. 8.6) common-mode voltage=1.6 V.12               | 22 |

| Figure 8.13 | $1\mathrm{GHz}$ output ( $v_\mathrm{OUT}$ in Fig. 8.6) of the differential-to-single-ended                      |    |

|             | converter from Monte Carlo <b>mismatch variation</b> (typical-typical) si-                                      |    |

|             | mulation. Input ( $v_{\text{IN-}}$ and $v_{\text{IN+}}$ in Fig. 8.6) common-mode voltage=1.2 V.12               | 23 |

| Figure 8.14 | $1\mathrm{GHz}$ output ( $v_\mathrm{OUT}$ in Fig. 8.6) of the differential-to-single-ended                      |    |

|             | converter from Monte Carlo <b>mismatch variation</b> (typical-typical) si-                                      |    |

|             | mulation. Input ( $v_{\text{IN-}}$ and $v_{\text{IN+}}$ in Fig. 8.6) common-mode voltage=2.0 V.12               | 23 |

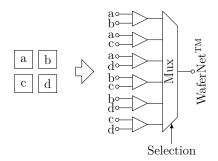

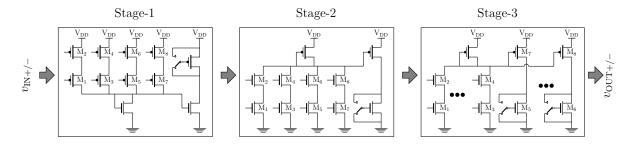

| Figure 8.15 | Schematic of the analog multiplexers simulated in IBM 0.13 $\mu m$ CMOS                                         |    |

|             | technology                                                                                                      | 25 |

| Figure 8.16 | The signal path consisting of 3 multiplexer stages that was simulated                                           |    |

|             | in IBM 0.13 µm CMOS technology                                                                                  | 25 |

| Figure 8.17 | <b>2 GHz</b> output ( $v_{\text{OUT}+/-}$ in Fig. 8.16) of the stage-3 multiplexer from |     |

|-------------|-----------------------------------------------------------------------------------------|-----|

|             | Monte Carlo <b>mismatch variation</b> (typical-typical) simulation. Input               |     |

|             | $(v_{\text{IN}+/-} \text{ in Fig. 8.16})$ common-mode voltage=1.6 V and voltage swing   |     |

|             | $V_{\text{P-P}}=800\text{mV}$ was used                                                  | 126 |

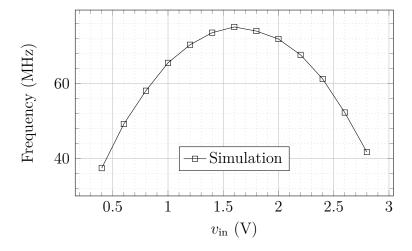

| Figure A.1  | The ASDM used in the proposed analog interface                                          | 144 |

| Figure A.2  | Waveform of the hysteresis input assuming $v_{\rm in}$ is a DC value and 0 <            |     |

|             | $v_{\rm in} < V_{\rm DD}$                                                               | 144 |

| Figure A.3  | Simulated frequency of oscilation ( $V_{DD} = 3.3 \text{ V}$ ) of the asynchronous      |     |

|             | $\Sigma\Delta$ modulator shown in Fig. 6.15 for different $v_{\rm in}$                  | 145 |

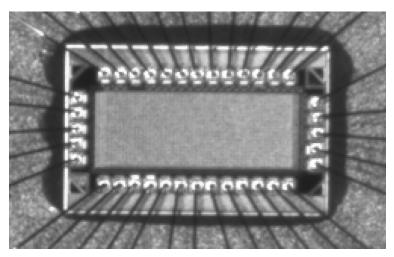

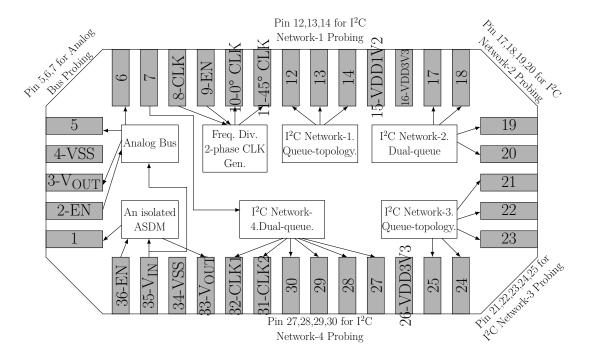

| Figure C.1  | Test chip                                                                               | 147 |

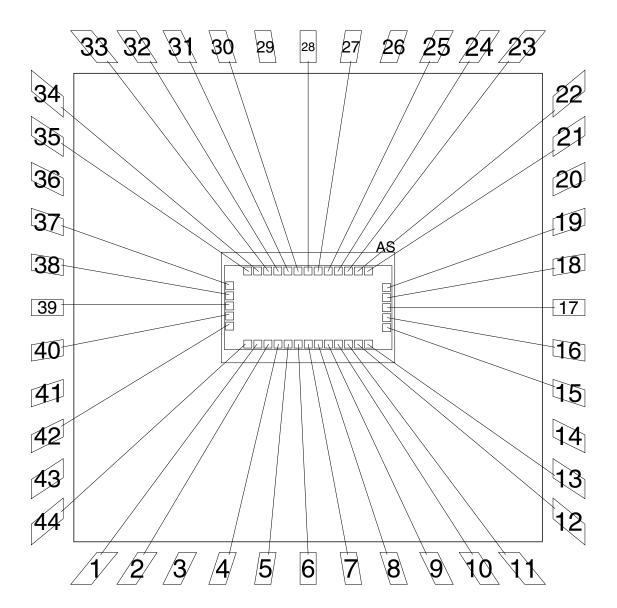

| Figure C.2  | Bonding diagram of test chip. Package type: CQFP44A                                     | 148 |

| Figure C.3  | Pin assignment of the test chip                                                         | 149 |

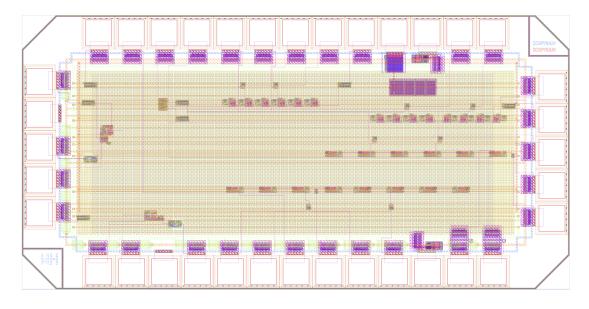

| Figure C.4  | Layout of test chip                                                                     | 149 |

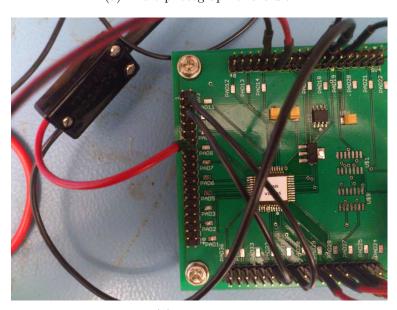

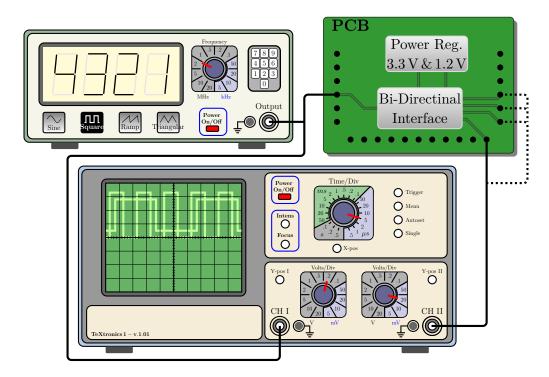

| Figure C.5  | Test setup of the bi-directional interface                                              | 150 |

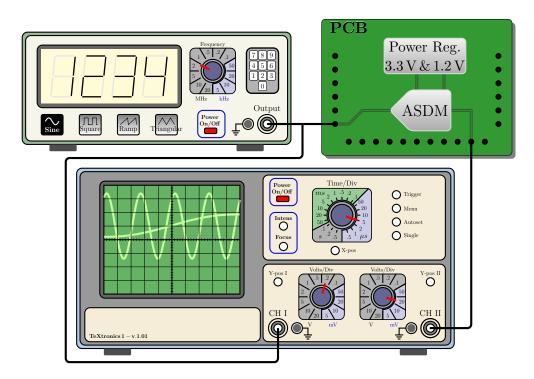

| Figure C.6  | Test setup of the ASDM                                                                  | 150 |

#### LIST OF ABBREVIATION

**ADC** analog-to-digital converter. 7

**ADM** asynchronous  $\Delta$ -modulator. ix, xiv, 22, 26–28, 67, 68, 129–133

**ASDM** asynchronous  $\Sigma\Delta$  modulator. xv, xviii, xxi, 20, 22, 23, 77, 132, 133, 143, 145, 150

ATCA advanced telecom computing architecture. 5

CIO configurable I/O. viii, 3-6, 11, 12, 24, 25, 28, 29, 112, 113, 116, 125, 126

CLB configurable logic block. 1

CML current mode logic. ix, 6, 28, 29, 112, 114, 118, 123, 126, 131

$\mathbf{CT}$ - $\mathbf{\Sigma}\Delta$  continuous-time  $\Sigma\Delta$  modulator. 22

**DAC** digital-to-analog converter. 7

**DDC** display data channel. 5

DLL delay-locked loop. 132, 133

**ENOB** effective number of bit. 19

**EPD** enhanced programmable device. 3, 4

FoM figure of merit. 20, 130

FPGA field-programmable gate array. viii, xvii, 1–4, 26, 40, 41, 66, 129

**FPIC** field programmable interconnection chip. 1

**FPIN** field programmable interconnection network. viii, ix, xvii, 1–8, 14, 22, 24–29, 39–47, 54, 56, 57, 59, 60, 66, 112–114, 129, 131

**GPIO** general purpose input output. 11

**HSTL** high-speed transceiver logic. 6

I<sup>2</sup>C Inter-Integrated Circuit. 11

IC integrated circuit. viii, 2

**IPMI** intelligent platform management interface. 5

LVDS low voltage differential signalling. 6

LVPECL low voltage positive-emitter-coupled logic. 6

**OSR** oversampling ratio. 19

PCB printed circuit board. 11, 150

PLL phase-locked loop. 14, 132, 133

PMBus power management bus. 5

SFDR spurious-free dynamic range. 130

SMBus system management bus. 5

SNDR signal-to-noise and distortion ratio. 20, 28, 130

SNR signal-to-noise ratio. 28, 130

**SQNR** signal-to-quantization noise ratio. 17

SSI stacked silicon interconnect. 1

**TSV** through-silicon via. 1–3

TTL transistor-transistor logic. 14

uIC user integrated circuit. ix, xvii, 2-4, 6, 8, 9, 11, 13, 25, 28, 29, 113, 114, 116, 118

VCO voltage controlled oscillator. 10, 14

## LIST OF APPENDICES

| APPENDIX A                       | 142 |

|----------------------------------|-----|

| APPENDIX B Time Line             | 146 |

| APPENDIX C Details of Test Chips | 147 |

#### CHAPTER 1 INTRODUCTION

Following Moore's law, semiconductor technology scaling has ushered the remarkable progress of microelectronic integration over the past four decades. Every technology generation, introduced every two to three years, has doubled the transistor count per chip, increased the operating frequency by 43%, and reduced the switching energy consumption by 65% on average [4]. Very complex systems with programmability at the user end have been made possible by leveraging such unprecedented logic density increase. A very successful class of configurable integrated circuits enabled by these trends is the field-programmable gate arrays (FPGAs).

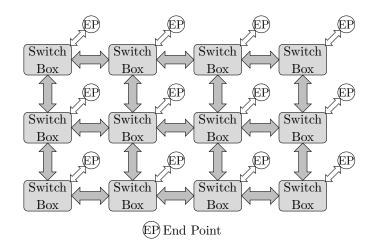

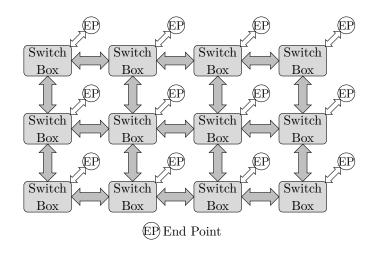

Field programmable interconnection networks (FPINs) are the backbone of emulation and prototyping platforms, i.e. FPGAs, ZeBu Server [5], Veloce verification system [6], Cadence® Palladium® series of accelerators/emulators [7], and many other Network-on-Chip architectures [8]. FPINs provide reconfigurable interconnections between various endpoints, i.e. the configurable logic blocks (CLBs) in FPGAs. Any digital hardware can be emulated in FP-GAs partly by reconfiguring their embedded FPINs. However, reconfigurability of the FPINs sometimes entails long interconnects between endpoints that result in excessive propagation delays. Buffers are typically inserted along these on-chip resistive interconnects to ensure fast signal propagation and linear signal delay increase with distance. Once configured, interconnects are therefore uni-directional. Systems used for digital hardware emulation can enhance their capability and performance by having programmable interconnection between FPGAs. Commercial logic emulation systems, such as the REALIZER SYSTEM [9], use programmable interconnection devices between FPGAs. These devices are called field programmable interconnection chips (FPICs). Fig. 1.1 illustrates an example where an FPIN provides programmable interconnections between endpoints (I/O or configurable logic blocks) in an FPGA.

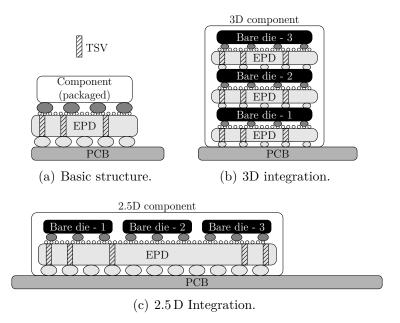

Modern FPGAs, such as those from the Xilinx's Virtex-7 family [10], can emulate circuits with up to 2000 000 logic gates and that maximum complexity keeps growing. Some of the large FPGA chips are internally implemented as several smaller connected FPGA dies. By combining through-silicon vias (TSVs) and microbump technology, Xilinx has developed a stacked silicon interconnect (SSI) technology that is the foundation of Virtex-7 FPGAs [11]. Xilinx notably uses a passive silicon interposer to combine multiple FPGA Super Logic Region (SLR). Instead of creating a 3D-stack, the FPGAs are put side-by-side on a passive interposer and hence this technology is called 2.5 D integration. The interposer is built using a

Figure 1.1 Generic model of a field programmable interconnection network (FPIN) in a FPGA.

low-risk, high-yield 65 nm process with four passive layers of metallization. It provides tens of thousands of die-to-die connections to enable ultra-high interconnect bandwidth, less power consumption and one fifth the latency of standard I/Os [11]. This passive interposer does not contain any transistor and hence, it is claimed to be a low risk and low cost device that does not introduce TSV related performance degradations [12].

#### 1.1 Active Reconfigurable Board Overview

In addition to FPGAs, an example of an FPIN-based circuit targeted in this thesis is the active reconfigurable platform named WaferBoard that was proposed in [1]. It was developed as a prototyping platform that provides interconnections among multiple user integrated circuits (uICs) to test and prototype electronic systems. This reconfigurable platform can be easily extended as an *active* silicon interposer, because unlike the aforementioned passive interposer of Xilinx, the interconnection network can be dynamically configured like an FPGA. It has an uni-directional switch box based FPIN that can be programmed by the user to interconnect the component uICs. The reconfigurable platform is primarily designed to provide digital interconnections between component uICs. However, as originally proposed, this FPIN-based prototyping platform was not supporting open-drain bi-directional signals (notably used in the I<sup>2</sup>C protocol and its derivatives [13–16]), analog signals, or differential signals.

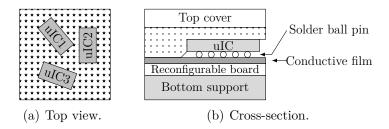

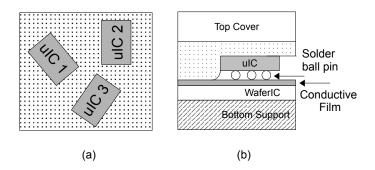

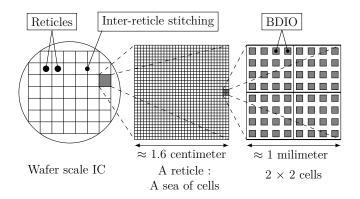

The core of the active reconfigurable board is a wafer scale IC (called WaferIC [1]) upon which user component ICs or uICs are to be deposited. The surface and cross-section of the active reconfigurable board is shown in Fig. 1.2(a) & 1.2(b) respectively. The surface of the

Figure 1.2 Conceptual overview of the active reconfigurable board.

Figure 1.3 Hierarchical description of the active reconfigurable board.

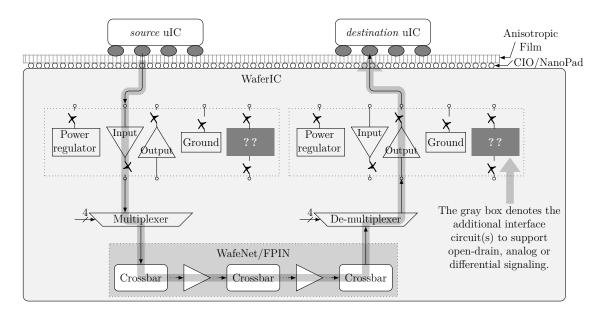

wafer scale IC has a dense array of very fine (tens of microns) conducting pads acting as configurable I/Os (CIOs), as shown in Fig. 1.3. These CIOs are called NanoPads in [1]. An FPIN is embedded in the wafer scale IC. The FPIN can be configured, similar to an FPGA, to connect any two CIOs. uIC pins are to have physical contacts with the CIO and communicate through the embedded FPIN as shown in Fig. 1.4. Each CIO has its own configurable I/O buffers. If a CIO is to operate as an input, then the respective CIO is configured as input and this buffer receives the signal from a *source* uIC and propagates it through the FPIN to other destination CIOs. The destination CIO's buffer is configured as an output buffer and it propagates the signal to the corresponding *destination* uIC.

### 1.2 Enhanced Programmable Devices (EPDs)

Demands for increased density, higher bandwidths, and lower power pushed IC designs toward 3D IC encapsulation. 3D ICs are manufactured by stacking multiple silicon wafers and/or dies and interconnecting them vertically. Passive silicon interposers with TSVs and several metallization layers are used to align the micro-beads of each silicon die. These dense interconnections between chip layers present a significant challenge to the alignment, testing and diagnosis. Enhanced programmable devices (EPDs) are conceived as active silicon inter-

Figure 1.4 Schematic diagram and propagation path of an electrical signal between two uICs pins in contact with the CIO/Nanopads on the WaferIC. The electrical signal propagates from a *source* uIC to a *destination* uIC.

posers that can provide, in addition to configurable interconnections, enhancements in terms of testability and diagnosis. A possible basic structure of an EPD is shown in Fig. 1.5. EPDs are intended to support as many types of signal interfaces as possible. As envisioned, similar to the aforementioned WaferBoard [1], an EPD surface has a dense array of CIOs and each CIO is connected to an internal FPIN that can be configured to connect a CIO to any others.

#### 1.3 Motivation

Configurability of FPINs is extensively utilized in FPGAs, in prototyping platforms, and in many network-on-chip architectures. This thesis work was motivated by the observation that the application domains of such FPIN-based prototyping and emulation platform could be significantly broadened by supporting open-drain bi-directional signals, analog signals, and differential signals. Three interface circuits were thus elaborated and developed to support reconfigurable routing of open-drain bi-directional, analog or differential signals through a uni-directional digital FPIN. Even though the need for such interface circuits were originally conceived in the context of the WaferBoard [1], the developed interface circuits can be integrated in or with FPGAs, active silicon interposers (*i.e.* EPDs) or any platform that embeds some digital FPINs.

Figure 1.5 Possible uses of enhanced programmable devices (EPDs).

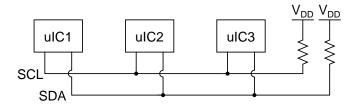

#### 1.3.1 Open-drain Bi-directional communication

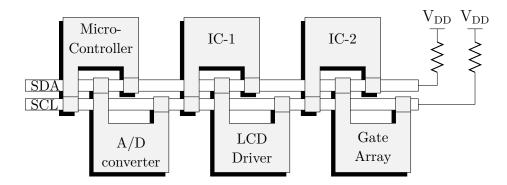

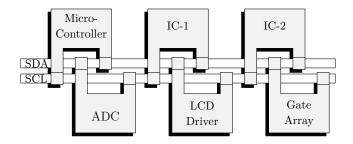

Multi-master bi-directional communication is widely used in electronic communication systems. It is used between low-speed peripherals and a motherboard, in embedded systems, in cellphones, and in many other electronic devices. The most widely used bi-directional bus is the I<sup>2</sup>C protocol. Several other communication standards are derived from the I<sup>2</sup>C protocol [15, 16]. Some of these I<sup>2</sup>C derived standards are the:

- 1. System management bus (SMBus) [16].

- 2. Power management bus (PMBus) [17].

- 3. Intelligent platform management interface (IPMI) [18].

- 4. Display data channel (DDC) [19].

- 5. Advanced telecom computing architecture (ATCA) [20].

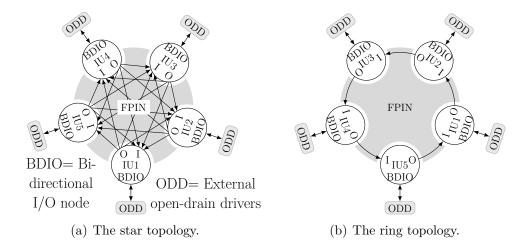

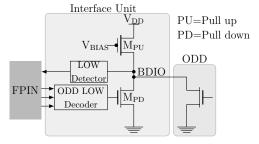

The main principle of the I<sup>2</sup>C protocol is that it is an open-drain (or open-collector) bus. All the derived protocols depend on the "wired AND" property of open-drain (or open-collector) connections. FPINs cannot *directly* support such "wired AND" connections, because each interconnection link is established by uni-directional binary digital signaling. Additional interface circuits are required at the CIOs or endpoints to support "wired AND" connections to outside world while the internal connections inside the FPIN is established by uni-directional digital buffers and switch boxes (multiplexers).

#### 1.3.2 Analog Signal Communication

The WaferBoard [1] was primarily developed to prototype digital electronic systems. However, nowadays many electronic systems are at least partly mixed-signal systems. Having the ability to reconfigurably route analog signals through the embedded FPIN can greatly improve the versatility of the WaferBoard or any electronic system prototyping platforms. In the context of the WaferBoard, A/D (transmitter) and D/A (receiver) converters are required to support analog signal propagation through the digital FPIN. The A/D converter receives the input analog signal from the transmitting user integrated circuit (uIC) and converts it into a digital format that can be propagated through the digital FPIN to the receiving side. This receiving side must comprise a D/A converter that can reproduce the original analog signal and provide it to the receiving uIC. However, due to the stringent limitations on the available silicon area, a very compact implementation of A/D and D/A converter is required for compatibility with the WaferBoard. Thus, the author was motivated to find a compact A/D and D/A converter solution that can support reconfigurable routing of analog signals within the existing constraints of the WaferBoard [1].

#### 1.3.3 Differential Signal communication

Differential signaling is widely used in high speed data transmission. It sends an electrical signal and its complement as a differential pair of signals through two conductors. External electromagnetic interferences tend to affect both conductors similarly and the receiving end only detects the difference between the conductors. Thus, differential signaling mitigates common mode electromagnetic coupling that affects single-ended signaling. Standards, currently in use for differential signaling, include for instance low voltage differential signalling (LVDS), low voltage positive-emitter-coupled logic (LVPECL), CML, and high-speed transceiver logic (HSTL) [21].

A differential interface must achieve spatial reconfigurability to support differential signaling in a FPIN-based prototyping platform such as the WaferBoard [1]. As uICs can be randomly placed on the active surface of the WaferBoard, the corresponding "contacted" CIOs/NanoPads can have random physical locations. The differential interface must have the ability to support such randomly located CIOs/NanoPads and still maintain the required symmetry and signal integrity of high-speed differential signaling. The operating speed of standard differential signaling is higher than the target operating speed of the prototyping platform. The primary target of the differential interface for the prototyping platform is for versatility purpose rather than supporting the highest possible speed.

#### 1.4 High Level Objectives of This Research

The aim of this research is:

- 1. To develop an interface that can support open-drain interconnection based bi-directional buses (such as I<sup>2</sup>C) in any digital FPIN-based prototyping platform.

- 2. To develop an interface that can support analog signal transmission in the WaferBoard [1] according to WaferBoard's constraints (see Sec.2.1.2).

- 3. To develop an interface that can support differential signal transmission through the single-ended digital FPIN of the WaferBoard.

#### 1.5 Organization of Thesis

This thesis is organized as follows. Chapter 2 presents background information and related previous works, with a brief overview of the prototyping platform [1], open-drain interconnection based bi-directional bus, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and differential signalling. Chapter 3 presents the detailed organization of the thesis while Chapters 4–8 constitute the core of the thesis. Chapter 9 presents a general discussion on the entire thesis. The contributions from this thesis are finally summarized and possible future works are discussed in Conclusion.

# CHAPTER 2 BACKGROUND INFORMATION AND RELATED PREVIOUS WORKS

A brief review of the FPIN-based prototyping platform [1] will facilitate the reader to properly understand the topic discussed in this thesis. Characteristics of open-drain, analog, and differential signalling are reviewed in the perspective of the prototyping platform to support explanation of the the proposed solutions. Sec. 2.1 describes the prototyping platform and its various constraints imposed to interface circuits. Sec. 2.2 presents an overview of open-drain interconnection based bi-directional buses. Sec. 2.3 presents different types of A/D and D/A converters, and considers their feasibility for the digital FPIN-based prototyping platform [1]. Sec. 2.4 presents various constraints of differential signaling in the target environment of the digital FPIN-based prototyping platform [1].

#### 2.1 Active Reconfigurable Platform [1]

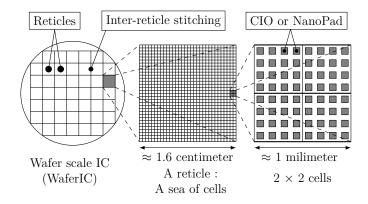

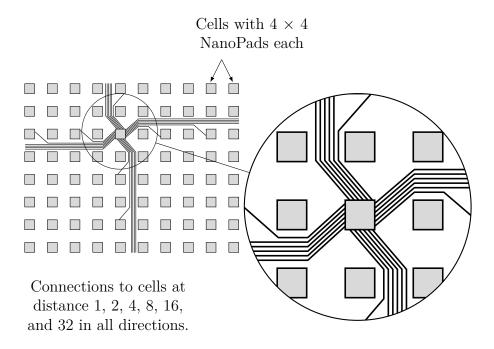

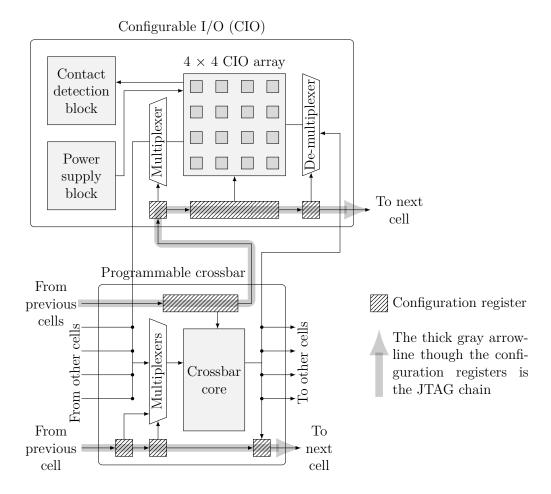

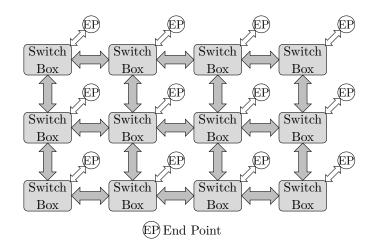

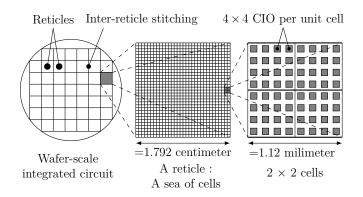

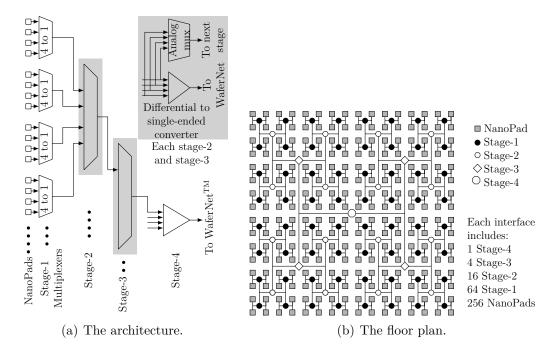

The WaferIC shown in Fig. 1.3 is the core of an active reconfigurable platform [1]. Component uICs are to be placed on the surface of the WaferIC. The building block of the WaferIC is called a *unit cell*. Each unit cell contains an array of  $4 \times 4$  CIO, I/O buffers, routing and control circuitries, and a multiplexer-based crossbar. This crossbar routes incoming signals to one of the CIOs, belonging to itself or to other unit cells. When a signal is propagated through the WaferIC, it is routed from unit cell to unit cell until it reaches the destination CIO and the corresponding uIC pin [1]. The dimension of each unit cell is  $560 \,\mu\text{m} \times 560 \,\mu\text{m}$  [1]. These cells are tiled within a reticle, and the WaferIC is built from repetition of this reticle across the entire wafer.

#### 2.1.1 WaferNet

Each unit cell is connected to an embedded digital FPIN, called WaferNet, as shown in Fig. 2.1, that can be configured to connect any two unit cells, whatever their position is. In other words, any two CIOs belonging to any two unit cells can be connected by the WaferNet. Each unit cell has connections with other unit cells which are 1,2,4,8,16, and 32<sup>nd</sup> unit cells away in all fours directions, as shown in Fig. 2.1. An uIC pin (or solder ball) can be contacted to several CIOs. The WaferIC detects and maps the contacted pins, and a netlist is generated according to the required connections. Then the WaferNet is configured to provide

Figure 2.1 WaferNet showing the connections between neighboring 1, 2, 4, 8, 16 and 32 in all directions.

all required connections between the uICs according to the netlist [1].

The routing of signals through the WaferNet, from a unit cell to another unit cell is accomplished by digital multiplexer-based crossbars. Each CIO has its own buffers. If a CIO is to operate as an input, then the respective I/O buffer is configured accordingly and this buffer receives the signal from a uIC and propagates it to the embedded crossbar of the local unit cell to which it belongs. The crossbar routes the signal to the link pointing toward the destination CIO's unit cell. Since the signal path can make a "jump" of only 1,2,4,8,16, and 32 unit cells at a time, it usually takes several jumps in all four directions for the signal to reach some arbitrary destination unit cell. At the destination cell, the CIO buffer is configured as an output buffer. All I/O buffers must be explicitly configured, either as an input or an output buffer. Normally this configuration is done before "testing" or "prototyping" with uICs. After CIOs are configured, the state remains unchanged during the entire period of testing or prototyping operation.

#### 2.1.2 Silicon Area Constraints of WaferIC

The functional architecture of the unit cell is depicted in Fig. 2.2. If any additional features are intended to be added, it must be fitted into the unit cell's dimension of  $560 \,\mu\text{m} \times 560 \,\mu\text{m}$  only that translates into an area of  $313600 \,\mu\text{m}^2$ . This area is already overstretched by the CIO

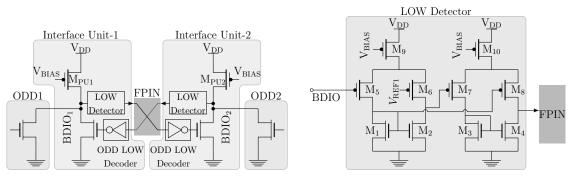

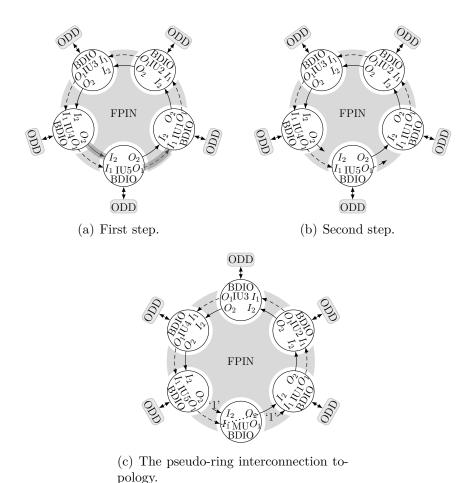

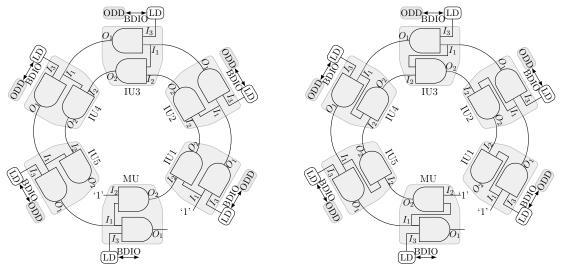

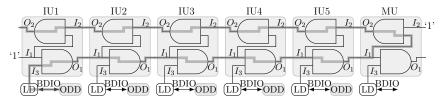

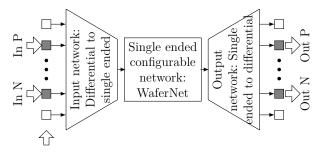

Figure 2.2 Architecture of an unit cell [1] with configuration registers, CIOs and crossbar multiplexers.