**Titre:** Circuits analogiques de lecture pour un capteur d'images couleur

Title: CMOS à photodéTECTeurs sans filtre

**Auteur:** Philippe Ménard Beaudoin

Author:

**Date:** 2009

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Ménard Beaudoin, P. (2009). Circuits analogiques de lecture pour un capteur d'images couleur CMOS à photodéTECTeurs sans filtre [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/180/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/180/>

PolyPublie URL:

**Directeurs de recherche:** Yves Audet

Advisors:

**Programme:** Génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

CIRCUITS ANALOGIQUES DE LECTURE POUR

UN CAPTEUR D'IMAGES COULEUR CMOS

À PHOTODÉTECTEURS SANS FILTRE

PHILIPPE MÉNARD BEAUDOIN

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2009

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

CIRCUITS ANALOGIQUES DE LECTURE POUR

UN CAPTEUR D'IMAGES COULEUR CMOS

À PHOTODÉTECTEURS SANS FILTRE

présenté par: MÉNARD BEAUDOIN Philippe

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. SAWAN Mohamad, Ph.D., président de jury

M. AUDET Yves, Ph.D., membre et directeur de recherche

M. FAYOMI Christian J.B., Ph.D., membre externe

## **REMERCIEMENTS**

Je tiens tout d'abord à remercier mon directeur de recherche, monsieur Yves Audet, professeur adjoint au département de génie électrique de l'École Polytechnique de Montréal, pour avoir dirigé mon projet de main de maître et m'avoir aidé à réaliser certains de mes objectifs professionnels. Ses qualités humaines ont grandement contribué à rendre mon parcours aux cycles supérieurs aussi plaisant que possible.

Je souhaite aussi adresser mes remerciements à messieurs Mohamad Sawan et Christian J. B. Fayomi, pour avoir accepté de participer au jury d'examen de ce mémoire en tant que président et membre externe, respectivement.

Mes plus sincères remerciements vont à monsieur Victor Hugo Ponce-Ponce, professeur invité, pour m'avoir aidé à la réalisation de plusieurs dessins des masques. Son attitude professionnelle et sa personnalité remarquable m'ont inspiré à devenir un meilleur étudiant et à grandir en tant qu'individu.

Je ne peux passer sous silence l'apport inestimable des techniciens Laurent Mouden et Jacques Girardin, qui ont collaboré de façon significative à la partie expérimentale de mon projet.

Merci à Sanyo Corporation, à Univalor et au Ministère du Développement Économique, de l'Innovation et de l'Exportation (MDEIE) pour leur appui financier qui fût, bien évidemment, une composante essentielle à la réalisation de ce projet.

Finalement, merci à monsieur Réjean Lepage, administrateur système au Groupe de Recherche en Microélectronique et Microsystèmes (GR2M), pour avoir fait en sorte que les systèmes informatiques soient des outils de travail efficaces et fonctionnels en tout temps.

## RÉSUMÉ

La résolution spatiale des capteurs d'images couleur actuels, qu'ils soient de type CCD (Charge-Coupled Device) ou à base de circuits CMOS (Complementary Metal-Oxide-Semiconductor), est limitée par leur méthode de discrimination des couleurs. En fait, comme la plupart des photodéTECTeurs ne sont sensibles qu'à l'intensité de la lumière et non pas à sa longueur d'onde, il faut déposer un filtre chromatique à la surface du capteur pour ne transmettre que la longueur d'onde désirée vers chaque photodéTECTeur. On extrapole par la suite la couleur équivalente d'un regroupement de pixels à l'aide d'algorithmes mathématiques, ce qui restreint l'atteinte d'une résolution spatiale comparable à celle d'une pellicule chimique photosensible de bonne qualité. De surcroît, la déposition du filtre chromatique réduit la sensibilité du capteur en absorbant une partie de l'énergie lumineuse, ce qui impose une restriction supplémentaire au niveau de la gamme dynamique. Dans le but de corriger ces lacunes, l'équipe de recherche du professeur Yves Audet a développé et breveté un photodéTECTeur innovateur permettant la discrimination des couleurs sans recourir à un filtre chromatique. Réalisable en technologie CMOS standard, ce photodéTECTeur est un candidat idéal pour l'intégration des circuits périphériques de traitement des signaux et la réalisation d'un circuit intégré de type COC (Camera On Chip). Le présent travail de recherche s'inscrit dans le processus de développement et de caractérisation de ce photodéTECTeur. Plus spécifiquement, il consiste à concevoir les circuits analogiques de traitement de signal en vue d'obtenir un capteur d'images intégré complet comportant trois sorties analogiques qui correspondent aux couleurs détectées par le photodéTECTeur. Pour ce faire, une nouvelle topologie de pixel actif APS (Active Pixel Sensor) a été développée à partir des caractéristiques expérimentales du photodéTECTeur. Par la suite, les circuits analogiques de traitement du signal périphériques ont été conçus afin de compléter le système d'acquisition d'images. Le prototype a été fabriqué en technologie  $0.25\mu\text{m}$  3.3V et les résultats obtenus témoignent du fonctionnement adéquat des circuits conçus.

## ABSTRACT

Many of today's CCD (Charge-Coupled Device) and CMOS (Complementary Metal-Oxide-Semiconductor) color image sensors exhibit a lower than desirable spatial resolution on behalf of their color detection and extrapolation mechanisms. Indeed, most photodetector units respond to light energies whose wavelengths are within their sensitive range, without actually distinguishing the actual wavelength. Hence, a method for separating colors must be implemented. The most popular of these methods consists in placing a CFA (Color Filter Array) atop the pixel array in order to define the wavelength received by every pixel. As it requires many pixels to determine a single element of color information in the image, the spatial resolution is limited to numbers well below those of a high-quality photo film. Furthermore, optical filtering reduces sensor sensitivity by absorbing part of the energy contained in the incoming light, thus limiting the available dynamic range. In order to alleviate these shortcomings, Professor Yves Audet's design team has developed and patented an innovative photodetector structure with integrated color detection that doesn't require the addition of a CFA. Since this photodetector can be fabricated using a standard CMOS technology, signal processing circuits can be implemented on the same chip to produce a COC (Camera On Chip). This work is part of the ongoing development and characterization process of the filterless photodetector. More specifically, it consists of the design of the analog circuits required to achieve a complete integrated image sensor having three analog signal outputs corresponding to the detected colors. Based on previously collected experimental data about the photodetector, an innovative APS (Active Pixel Sensor) architecture was created. Then, the peripheral analog signal processing circuits were designed to complete the analog image capture system. The prototype has been fabricated using  $0.25\mu\text{m}$  3.3V CMOS technology and experimental results demonstrate the functionality of the circuits.

## TABLE DES MATIÈRES

|                                                              |      |

|--------------------------------------------------------------|------|

| REMERCIEMENTS .....                                          | iii  |

| RÉSUMÉ .....                                                 | iv   |

| ABSTRACT .....                                               | v    |

| TABLES DES MATIÈRES .....                                    | vi   |

| LISTE DES TABLEAUX.....                                      | x    |

| LISTE DES FIGURES.....                                       | xi   |

| LISTE DES SIGLES ET ABBRÉVIATIONS.....                       | xv   |

| LISTE DES ANNEXES.....                                       | xvii |

| INTRODUCTION .....                                           | 1    |

| CHAPITRE 1 PRINCIPES DE BASE DES CAPTEURS D'IMAGES CMOS..... | 4    |

| 1.1 INTRODUCTION .....                                       | 4    |

| 1.2 STRUCTURE GÉNÉRALE DES CAPTEURS D'IMAGES CMOS .....      | 6    |

| 1.2.1 Modes d'accès aux pixels .....                         | 7    |

| 1.2.2 Traitement des signaux .....                           | 7    |

| 1.3 ARCHITECTURES DE PIXELS .....                            | 11   |

| 1.3.1 Pixels passifs (PPS) .....                             | 12   |

| 1.3.2 Pixels actifs (APS).....                               | 13   |

| 1.3.3 Pixels numériques (DPS).....                           | 17   |

| 1.3.4 Facteur de remplissage .....                           | 18   |

| 1.4 INDICATEURS DE PERFORMANCE.....                          | 19   |

|                                                                     |           |

|---------------------------------------------------------------------|-----------|

| 1.4.1 Résolution et résolution spatiale .....                       | 19        |

| 1.4.2 Courant de noirceur .....                                     | 20        |

| 1.4.3 Bruit .....                                                   | 20        |

| 1.4.4 Gamme dynamique .....                                         | 24        |

| 1.5 PROCÉDÉS DE DISCRIMINATION DES COULEURS .....                   | 26        |

| 1.5.1 Méthode par expositions successives .....                     | 26        |

| 1.5.2 Séparation des couleurs .....                                 | 26        |

| 1.5.3 Filtre chromatique .....                                      | 27        |

| 1.5.4 Discrimination spectrale verticale .....                      | 28        |

| 1.6 PHOTODÉTECTEUR SANS FILTRE INNOVATEUR .....                     | 29        |

| 1.7 CONCLUSION .....                                                | 32        |

| <b>CHAPITRE 2 CONCEPTION DU PROTOTYPE DE CAPTEUR D'IMAGES .....</b> | <b>33</b> |

| 2.1 INTRODUCTION ET CONTRAINTES DE CONCEPTION .....                 | 33        |

| 2.1.1 Architecture du capteur .....                                 | 33        |

| 2.1.2 Mode d'acquisition séquentiel .....                           | 34        |

| 2.1.3 Architecture du pixel .....                                   | 34        |

| 2.1.4 Interface avec les périphériques externes .....               | 35        |

| 2.1.5 Taille du pixel .....                                         | 35        |

| 2.1.6 Performances du capteur .....                                 | 35        |

| 2.1.7 Technologie CMOS .....                                        | 36        |

| 2.2 ARCHITECTURE DES CIRCUITS DE LECTURE .....                      | 36        |

| 2.2.1 Architecture générale des circuits de lecture .....           | 36        |

|                                                                        |     |

|------------------------------------------------------------------------|-----|

| 2.2.2 Portes de transmission .....                                     | 37  |

| 2.2.3 Bus de colonne et de sortie .....                                | 38  |

| 2.3 CIRCUITS DU PIXEL ACTIF .....                                      | 38  |

| 2.3.1 Intégrateur inverseur .....                                      | 38  |

| 2.3.2 Intégrateur inverseur à paire différentielle .....               | 42  |

| 2.3.3 Conception et réalisation physique du pixel actif.....           | 74  |

| 2.4 CIRCUITS DE COLONNE .....                                          | 84  |

| 2.4.1 Architecture générale des circuits de colonne .....              | 84  |

| 2.4.2 Tampon de colonne .....                                          | 85  |

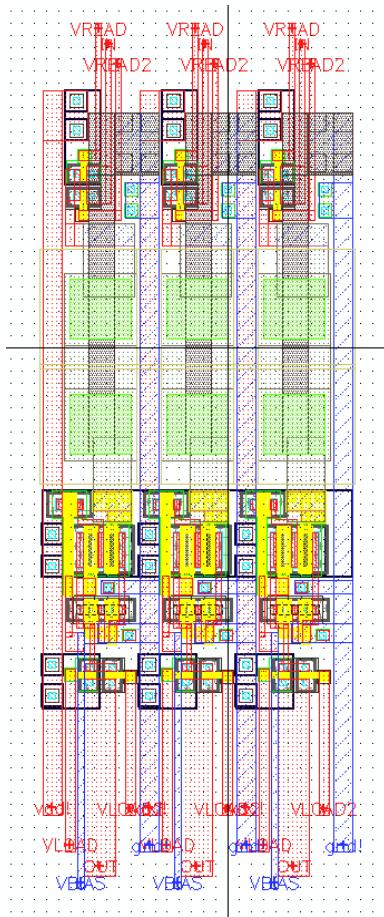

| 2.4.3 Conception et réalisation physique des circuits de colonne ..... | 89  |

| 2.5 TAMPONS DE SORTIE.....                                             | 92  |

| 2.5.1 Contraintes de conception des tampons de sortie .....            | 92  |

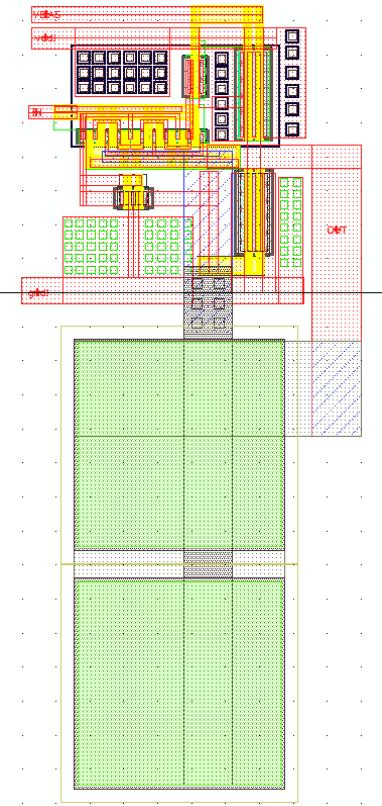

| 2.5.2 Architecture des tampons de sortie.....                          | 92  |

| 2.5.3 Processus de conception des tampons de sortie.....               | 94  |

| 2.6 CONCLUSION .....                                                   | 96  |

| CHAPITRE 3 MESURES ET RÉSULTATS .....                                  | 97  |

| 3.1 INTRODUCTION .....                                                 | 97  |

| 3.2 BLOCS DE TRAITEMENT ANALOGIQUE.....                                | 98  |

| 3.2.1 Pixel actif à intégrateur inverseur .....                        | 98  |

| 3.2.2 Tampons de colonne.....                                          | 119 |

| 3.2.3 Tampons de sortie.....                                           | 124 |

| 3.3 CAPTEUR D'IMAGES COMPLET .....                                     | 129 |

|                                           |     |

|-------------------------------------------|-----|

| 3.3.1 Description du banc d'essai .....   | 129 |

| 3.3.2 Vérification du fonctionnement..... | 131 |

| 3.3.3 Analyse du bruit.....               | 134 |

| 3.4 CONCLUSION .....                      | 142 |

| CONCLUSION .....                          | 143 |

| RÉFÉRENCES.....                           | 147 |

## LISTE DES TABLEAUX

|             |                                                                             |     |

|-------------|-----------------------------------------------------------------------------|-----|

| Tableau 2.1 | Paramètres de conception de l'intégrateur inverseur .....                   | 75  |

| Tableau 2.2 | Valeurs finales des paramètres de l'intégrateur inverseur .....             | 83  |

| Tableau 2.3 | Caractéristiques du dessin des masques du pixel actif.....                  | 83  |

| Tableau 2.4 | Paramètres de conception des tampons de colonne .....                       | 90  |

| Tableau 2.5 | Valeurs finales des paramètres des circuits de colonne .....                | 91  |

| Tableau 2.6 | Valeurs finales des paramètres des tampons de sortie .....                  | 94  |

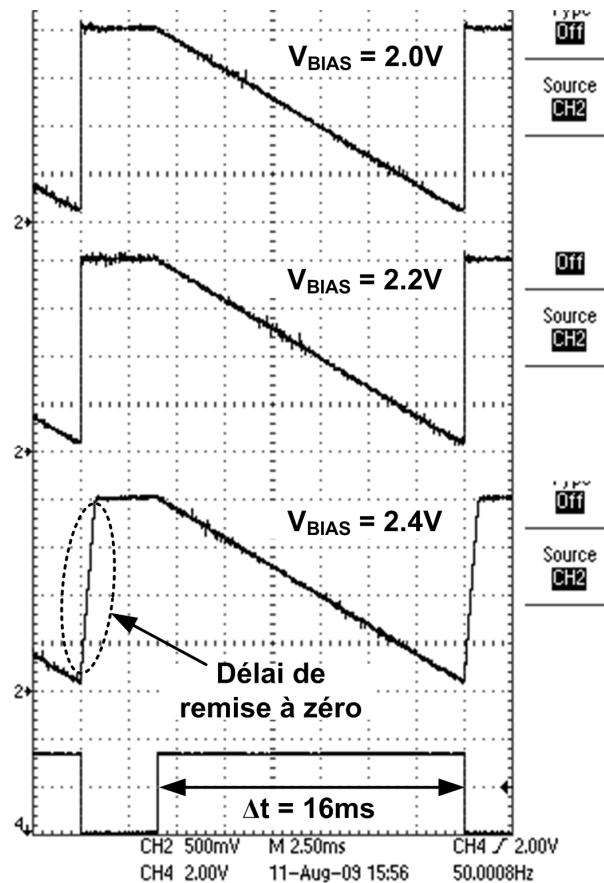

| Tableau 3.1 | Délai de remise à zéro et linéarité de l'intégration.....                   | 109 |

| Tableau 3.2 | Caractéristiques de l'analyse transitoire de la phase d'échantillonnage ... | 119 |

| Tableau 3.3 | Caractéristiques DC du tampon de colonne .....                              | 121 |

| Tableau 3.4 | Caractéristiques de la réponse transitoire du tampon de colonne .....       | 123 |

| Tableau 3.5 | Caractéristiques DC du tampon de sortie .....                               | 126 |

| Tableau 3.6 | Caractéristiques de la réponse transitoire du tampon de sortie .....        | 128 |

| Tableau 3.7 | Délais de lecture totaux estimés dans le pire cas .....                     | 129 |

| Tableau 3.8 | Tensions efficaces du bruit temporel au nœud de sortie .....                | 141 |

| Tableau 3.9 | Contribution individuelle des circuits au bruit temporel.....               | 141 |

| Tableau A.1 | Mesures de $C_{EQD}$ .....                                                  | 172 |

| Tableau A.2 | Mesures de $C_{EQ4}$ .....                                                  | 174 |

## LISTE DES FIGURES

|                                                                                       |    |

|---------------------------------------------------------------------------------------|----|

| Figure 1.1 Structure générale d'un capteur d'images CMOS .....                        | 6  |

| Figure 1.2 Méthode générale de traitement analogique .....                            | 8  |

| Figure 1.3 Conversion analogique à numérique globale .....                            | 9  |

| Figure 1.4 Conversion analogique à numérique par colonnes .....                       | 9  |

| Figure 1.5 Conversion analogique à numérique intégrée aux pixels .....                | 10 |

| Figure 1.6 Schéma-bloc généralisé d'un pixel CMOS.....                                | 11 |

| Figure 1.7 Pixel passif (PPS) .....                                                   | 12 |

| Figure 1.8 Pixel actif à trois transistors (3T-APS).....                              | 14 |

| Figure 1.9 Pixel actif à quatre transistors (4T-APS).....                             | 15 |

| Figure 1.10 Partage des pixels en regroupements de quatre (1.75T-APS) .....           | 19 |

| Figure 1.11 Double échantillonnage corrélé (CDS).....                                 | 23 |

| Figure 1.12 Échantillonnage différentiel de type remise à zéro (DRS) .....            | 24 |

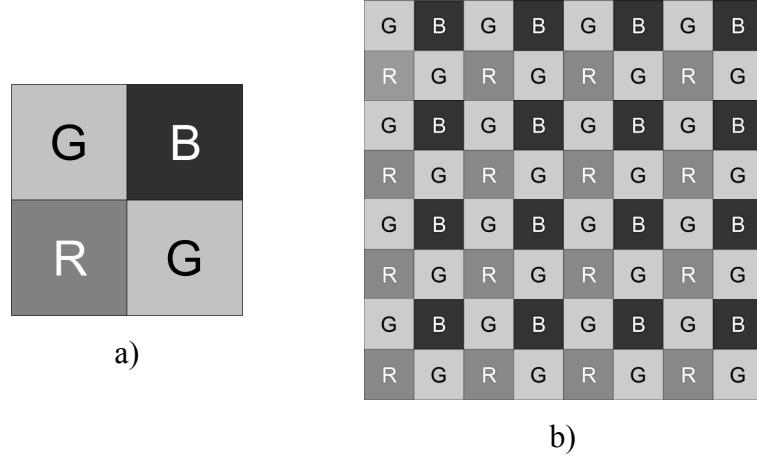

| Figure 1.13 Mosaïque à patron de Bayer .....                                          | 28 |

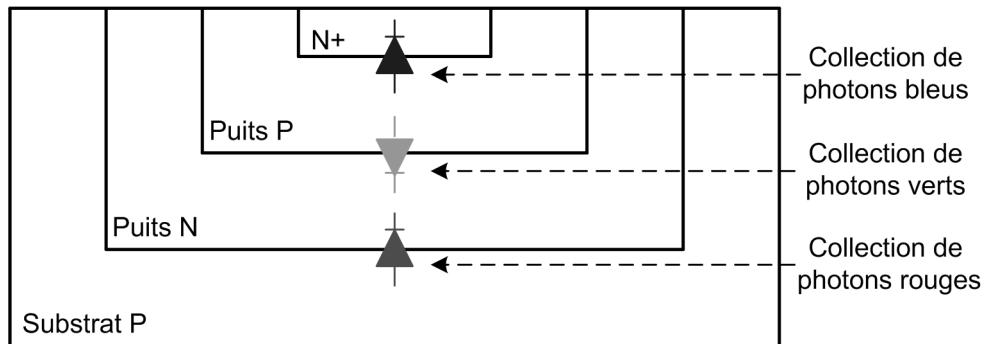

| Figure 1.14 Discrimination spectrale verticale .....                                  | 29 |

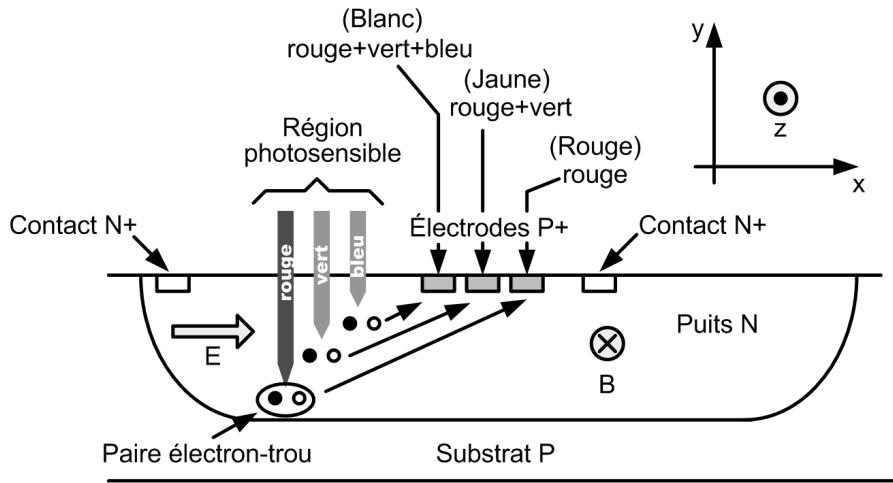

| Figure 1.15 Photodétecteur sans filtre.....                                           | 30 |

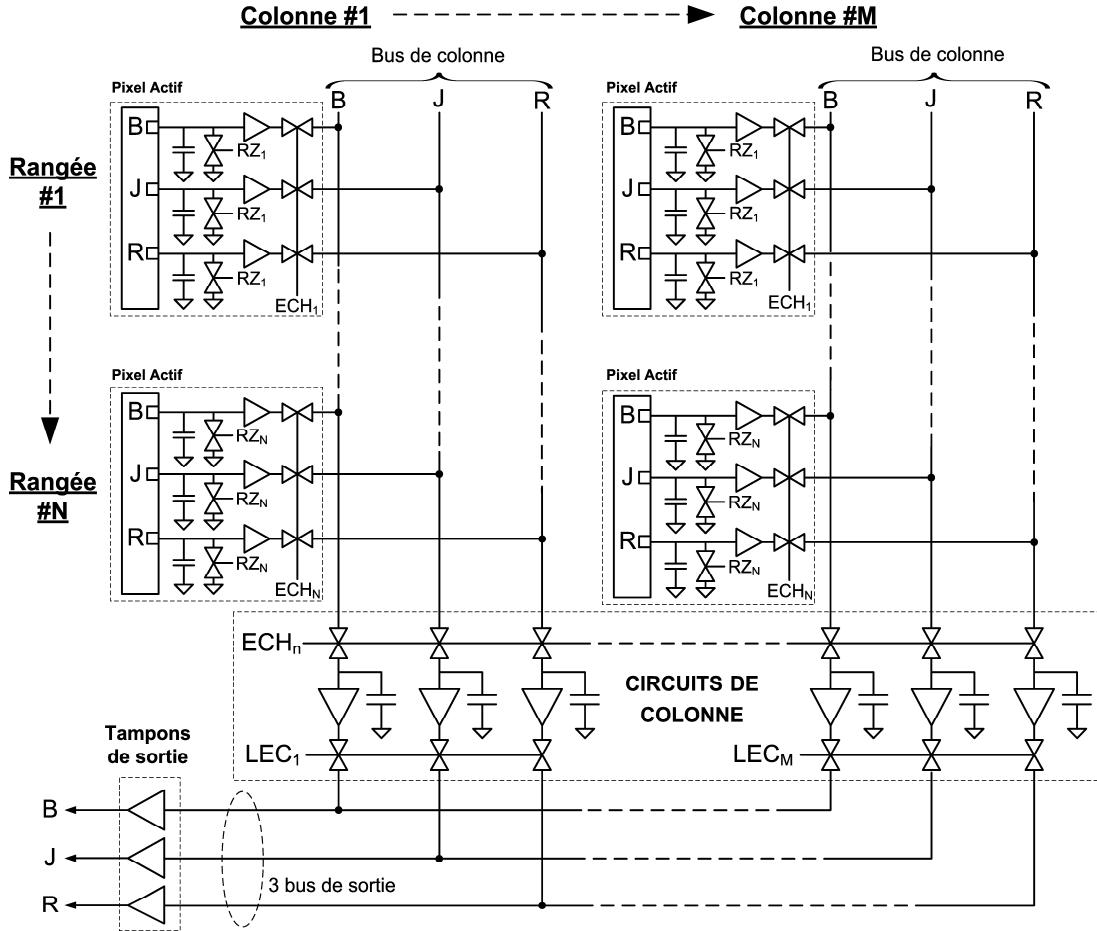

| Figure 2.1 Architecture des circuits de lecture.....                                  | 37 |

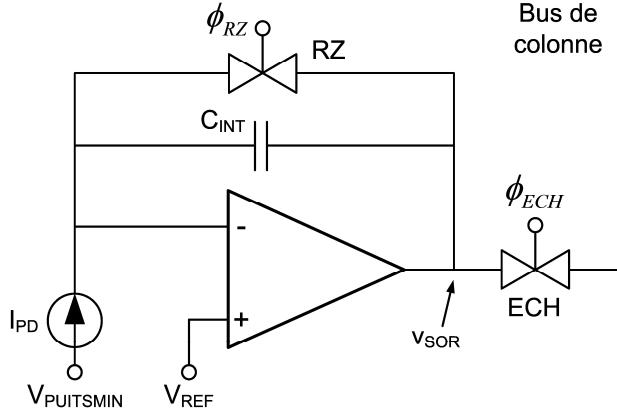

| Figure 2.2 Pixel actif à intégrateur inverseur .....                                  | 39 |

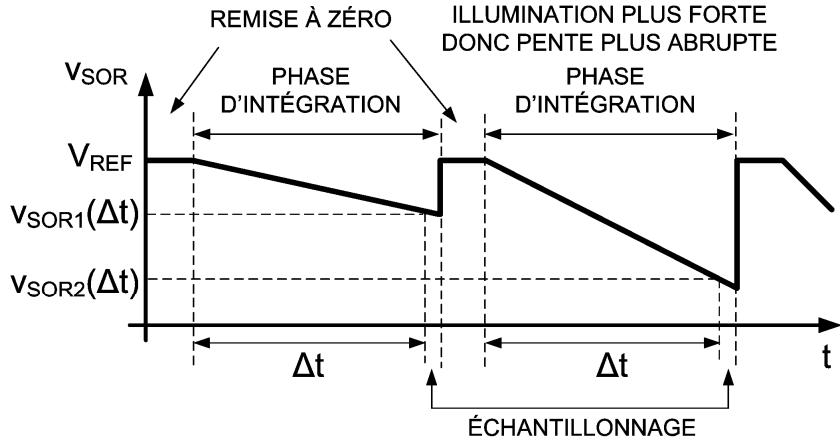

| Figure 2.3 Tension de sortie du pixel actif à intégrateur inverseur.....              | 42 |

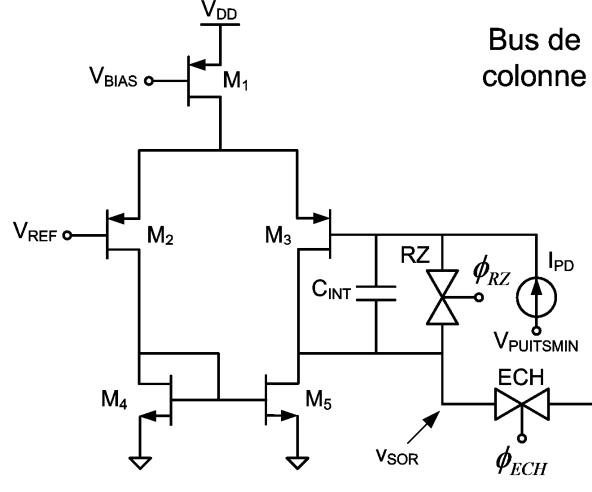

| Figure 2.4 Pixel actif à intégrateur inverseur avec paire différentielle .....        | 43 |

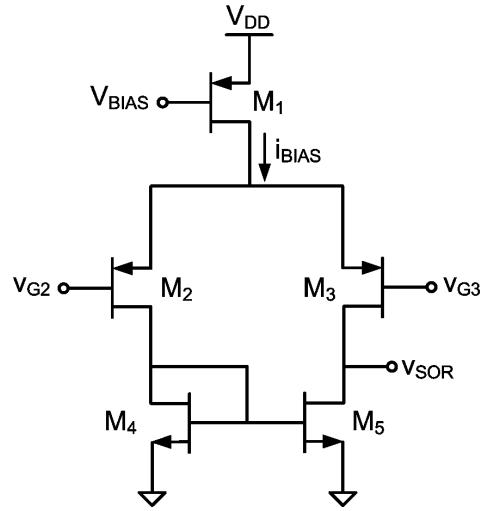

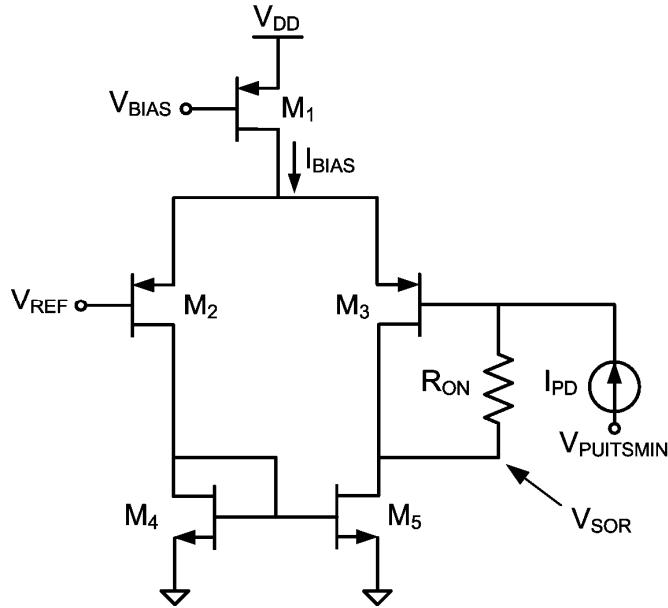

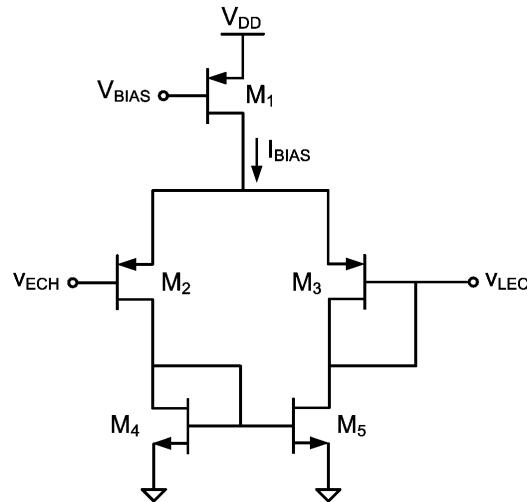

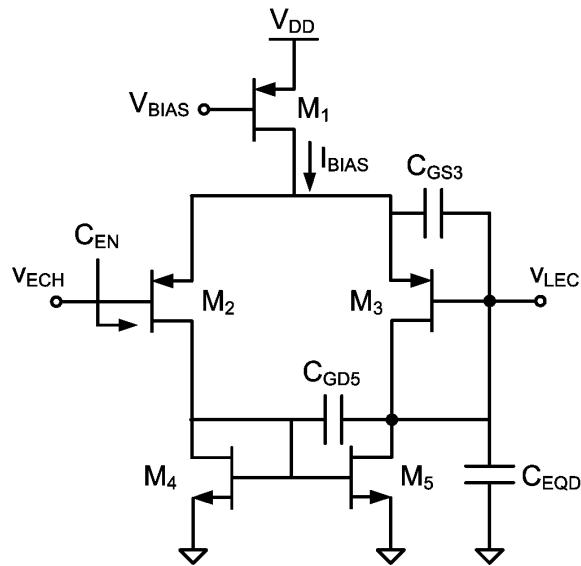

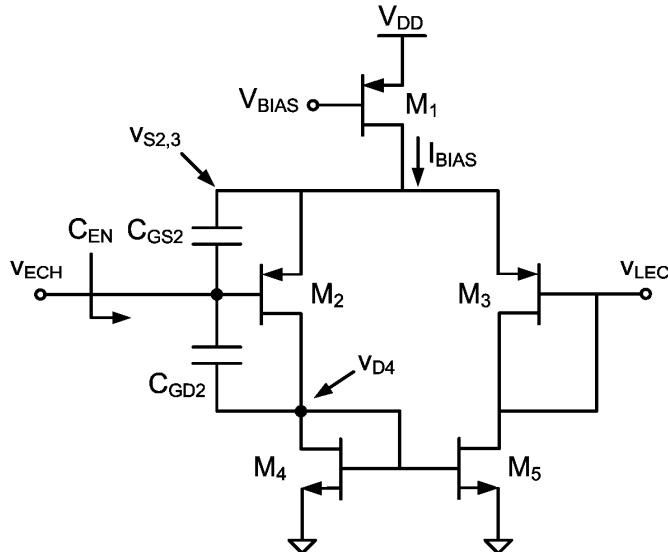

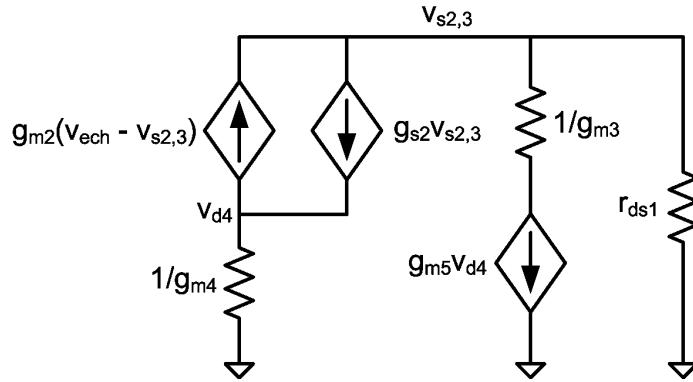

| Figure 2.5 Paire différentielle utilisée pour réaliser l'intégrateur inverseur .....  | 44 |

| Figure 2.6 Pixel actif lors de la phase de remise à zéro (régime permanent) .....     | 50 |

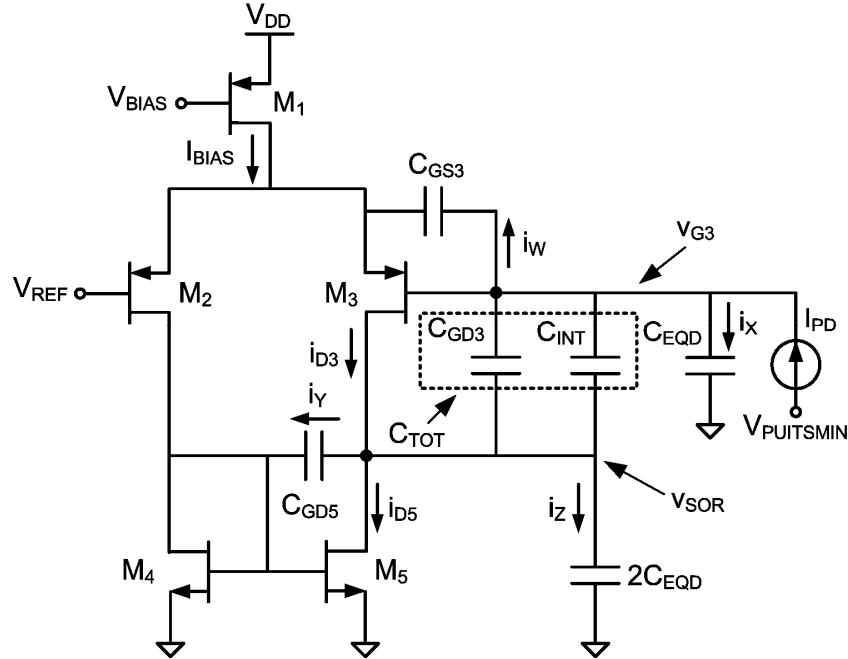

| Figure 2.7 Pixel actif lors de la phase d'intégration.....                            | 53 |

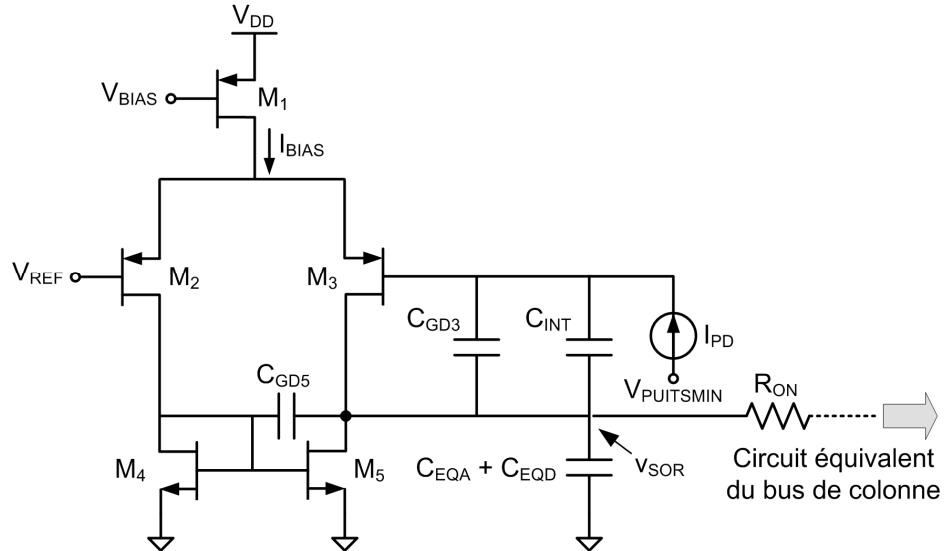

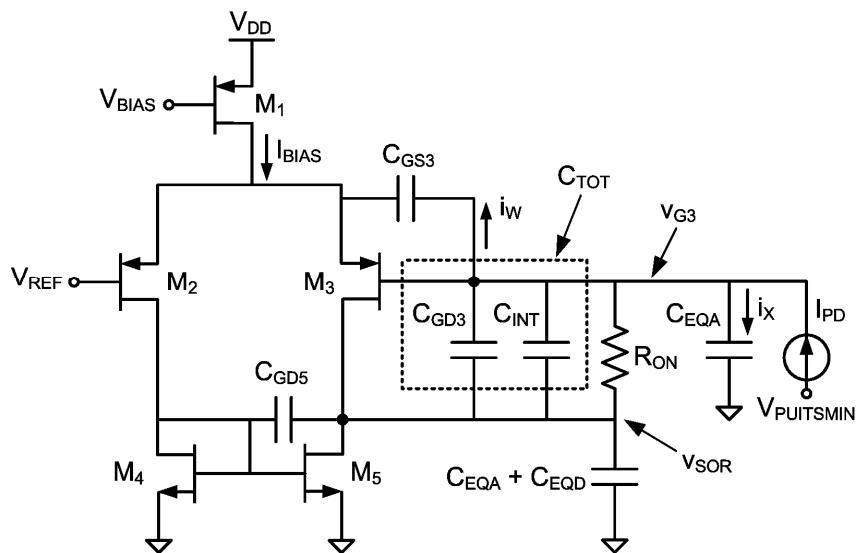

| Figure 2.8 Pixel actif lors de la phase d'échantillonnage.....                        | 60 |

| Figure 2.9 Pixel actif lors de la phase de remise à zéro (régime transitoire) .....   | 61 |

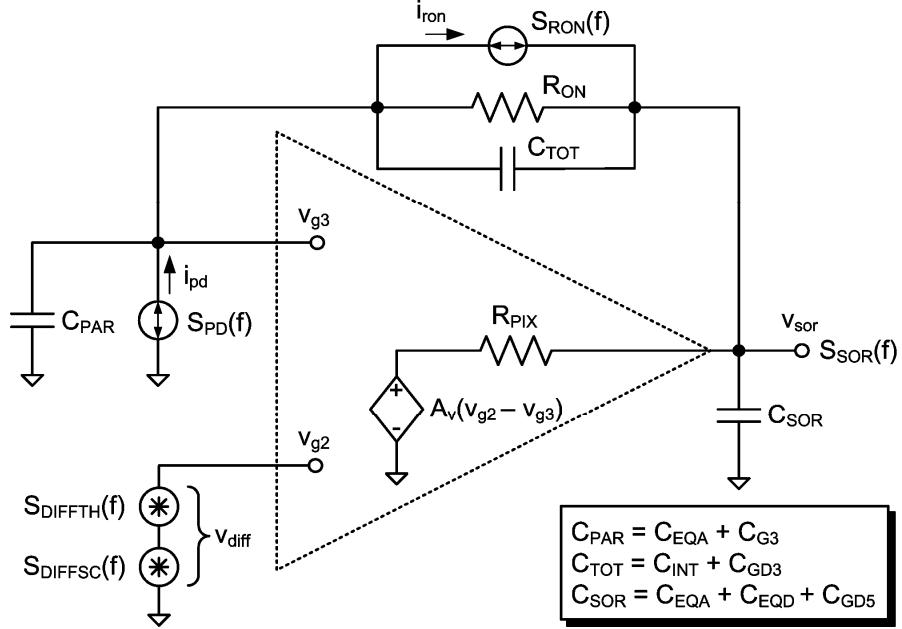

| Figure 2.10 Circuit équivalent du bruit du pixel actif lors de la remise à zéro ..... | 68 |

| Figure 2.11 Pixel actif à intégrateur inverseur à trois entrées.....                  | 74 |

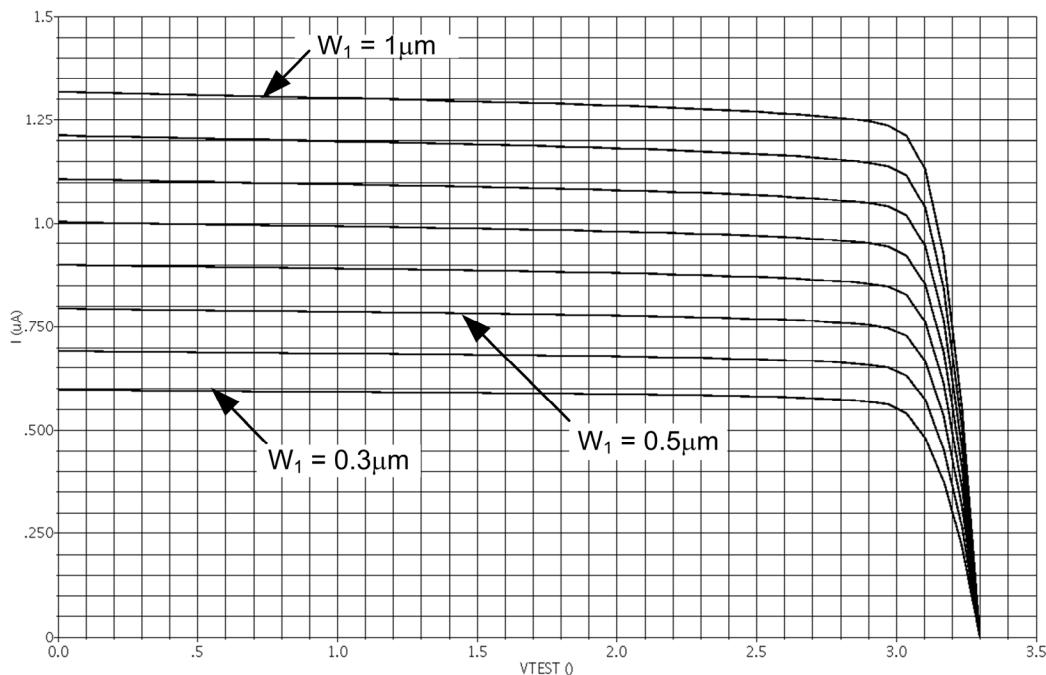

| Figure 2.12 Courant de polarisation $I_{BIAS}$ .....                                  | 79 |

|                                                                                                                        |     |

|------------------------------------------------------------------------------------------------------------------------|-----|

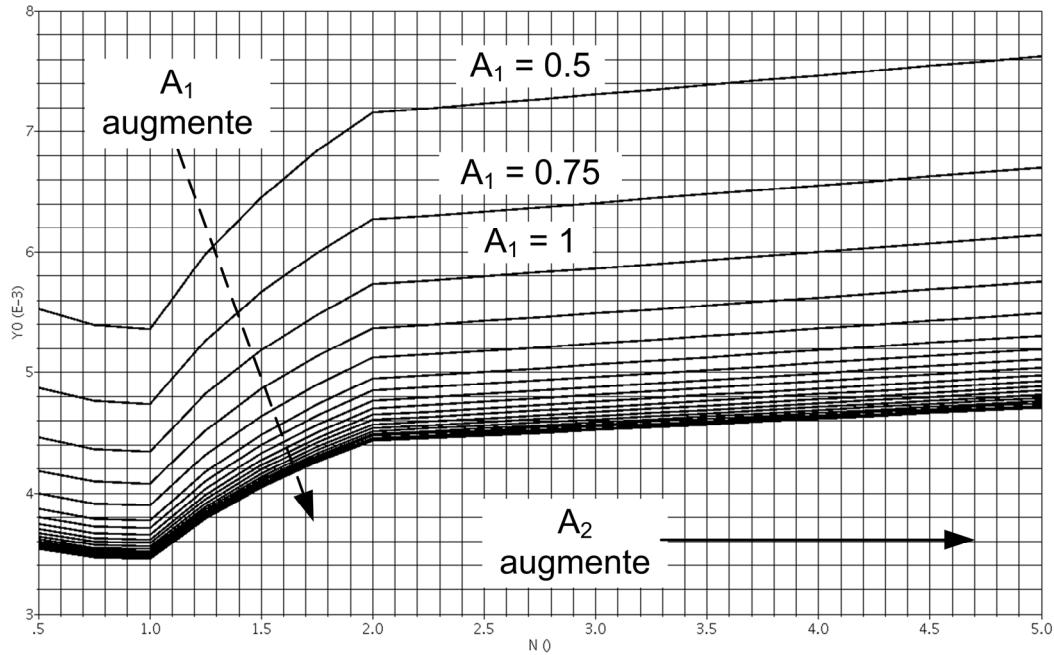

| Figure 2.13 Valeur moyenne de la tension de décalage pour différentes valeurs des multiplicateurs $A_1$ et $A_2$ ..... | 81  |

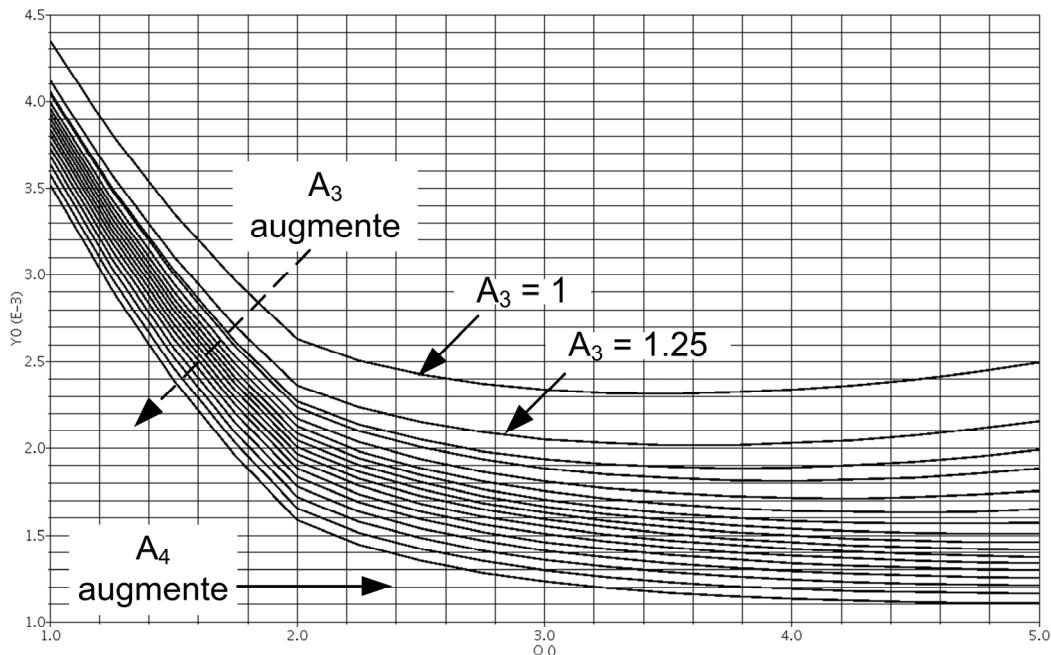

| Figure 2.14 Valeur moyenne de la tension de décalage pour différentes valeurs des multiplicateurs $A_3$ et $A_4$ ..... | 82  |

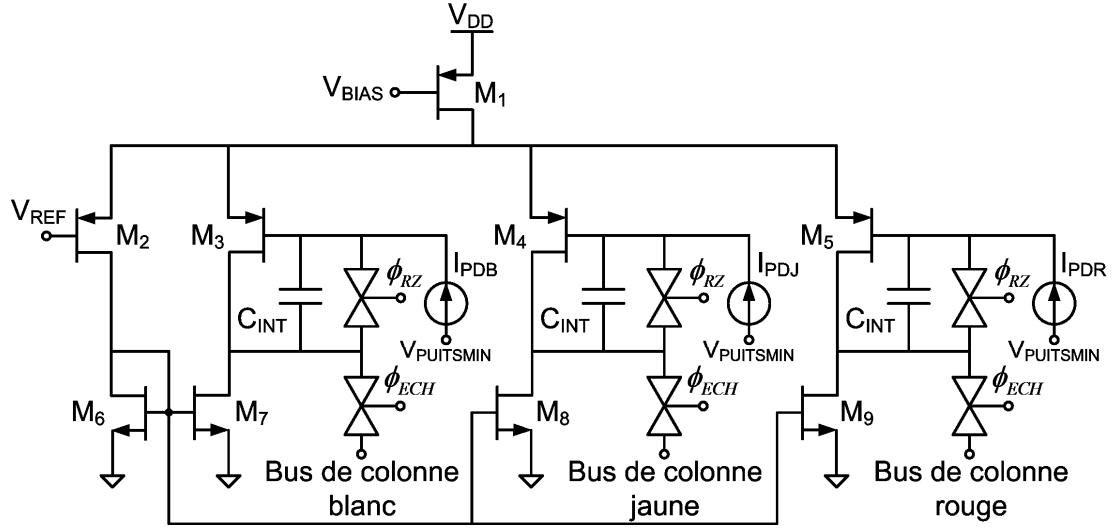

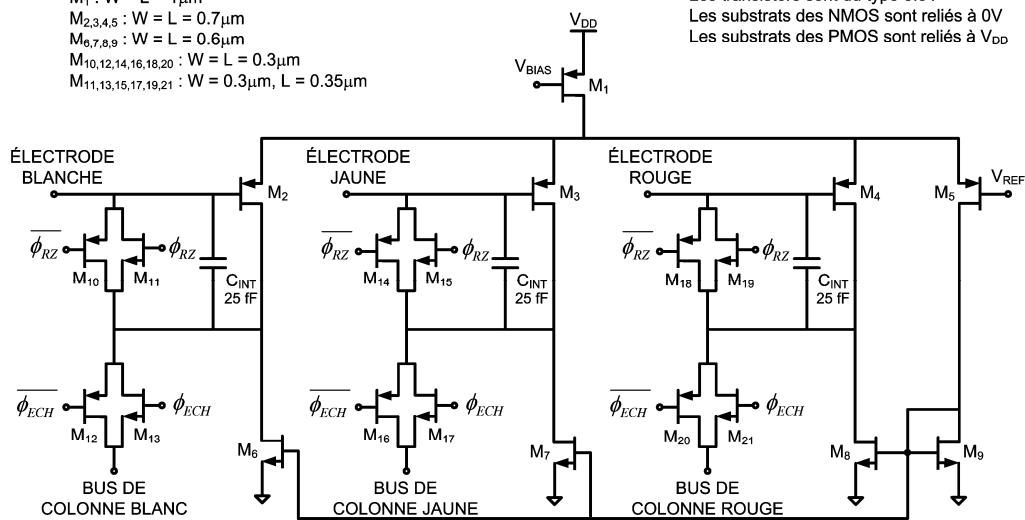

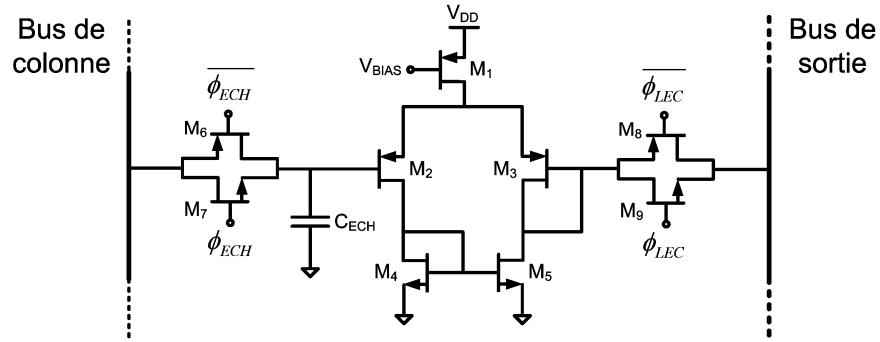

| Figure 2.15 Circuit de colonne (1/3).....                                                                              | 84  |

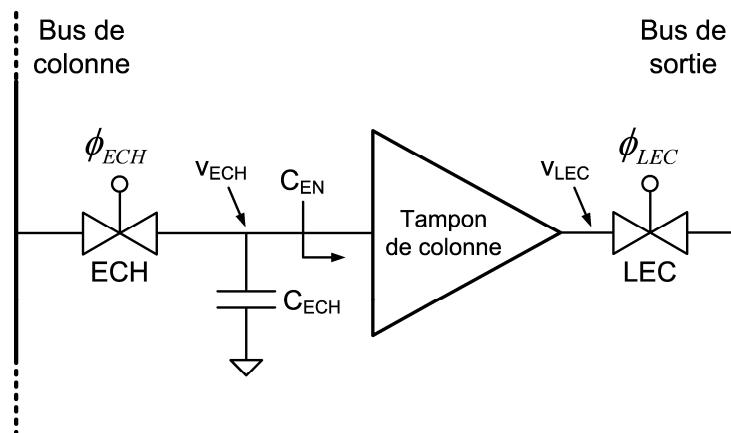

| Figure 2.16 Architecture d'un tampon de colonne.....                                                                   | 85  |

| Figure 2.17 Tampon de colonne durant la phase d'échantillonnage.....                                                   | 87  |

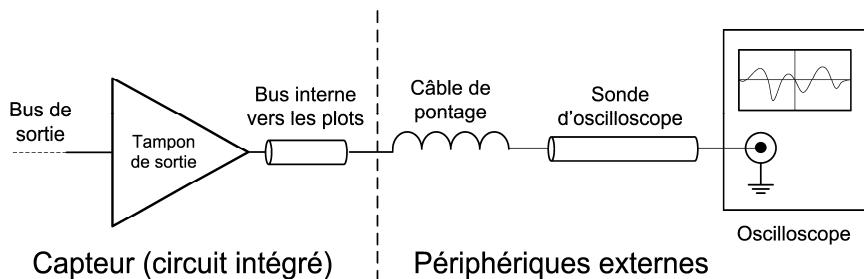

| Figure 2.18 Interface entre le capteur et les périphériques externes .....                                             | 92  |

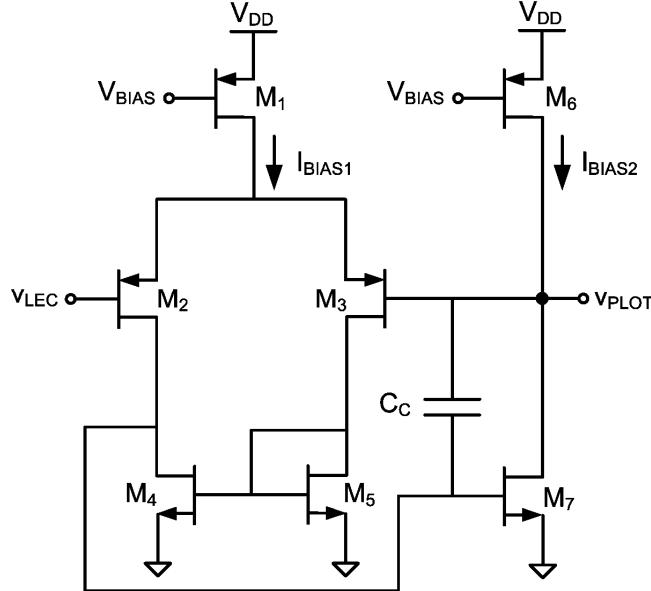

| Figure 2.19 Architecture d'un tampon de sortie .....                                                                   | 93  |

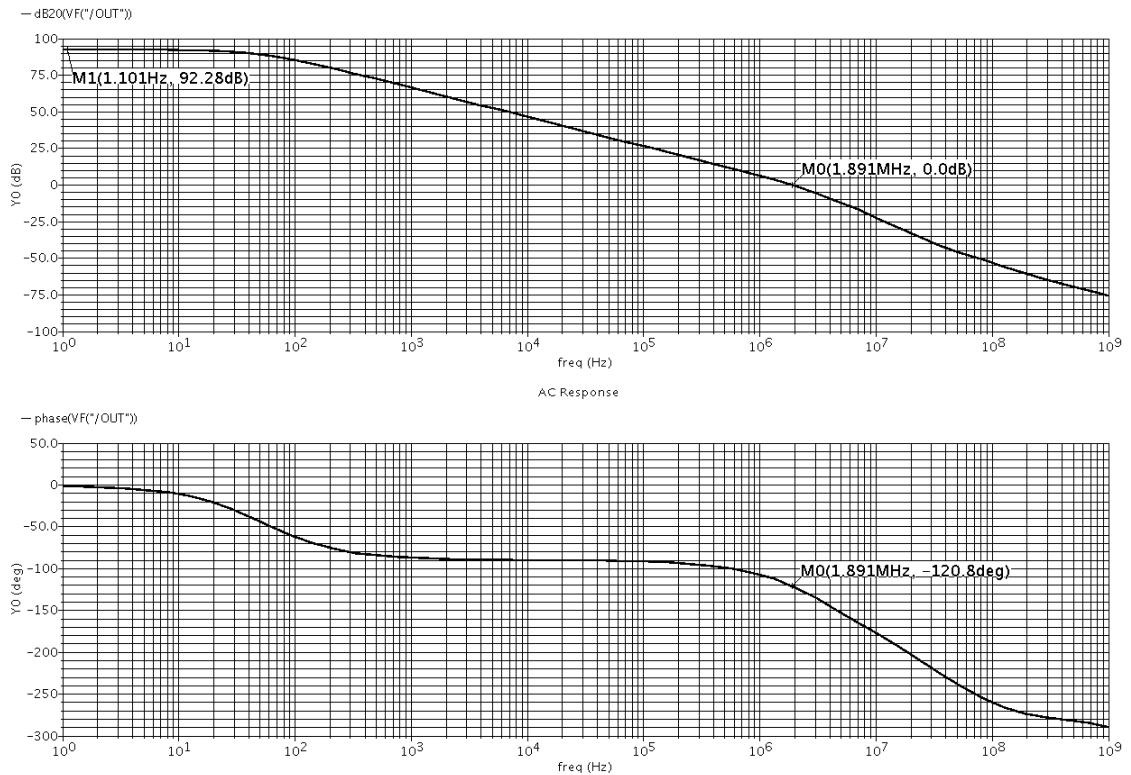

| Figure 2.20 Marge de phase d'un tampon de sortie .....                                                                 | 95  |

| Figure 2.21 Réponse à l'échelon d'un tampon de sortie.....                                                             | 96  |

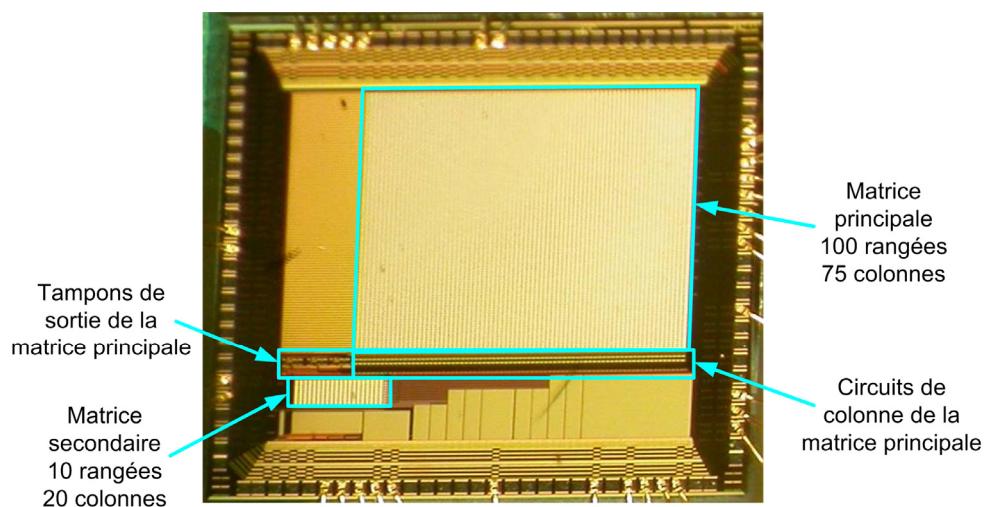

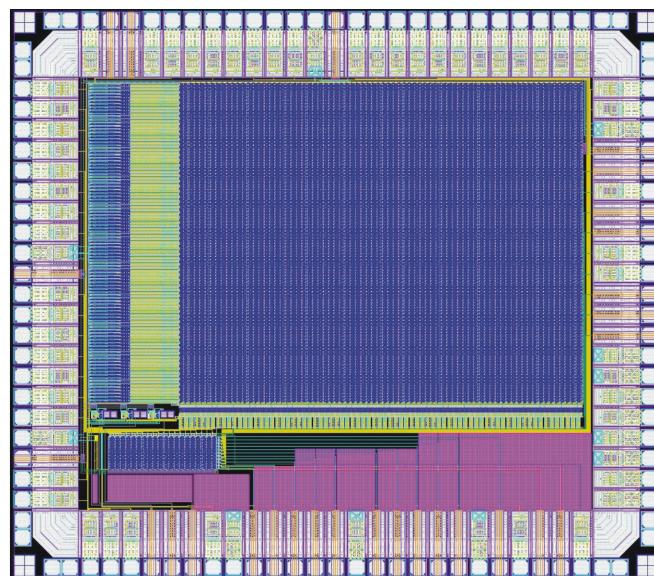

| Figure 3.1 Photographie du circuit intégré.....                                                                        | 97  |

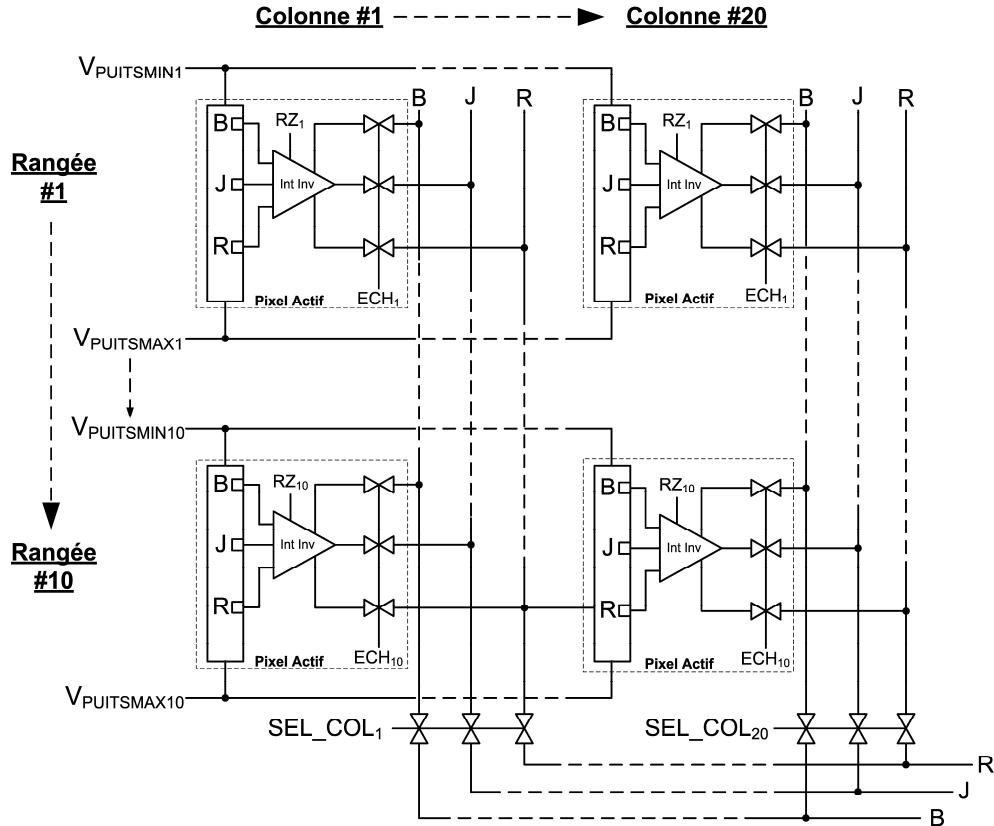

| Figure 3.2 Architecture de la matrice secondaire.....                                                                  | 99  |

| Figure 3.3 Banc d'essai utilisé pour caractériser le pixel actif .....                                                 | 101 |

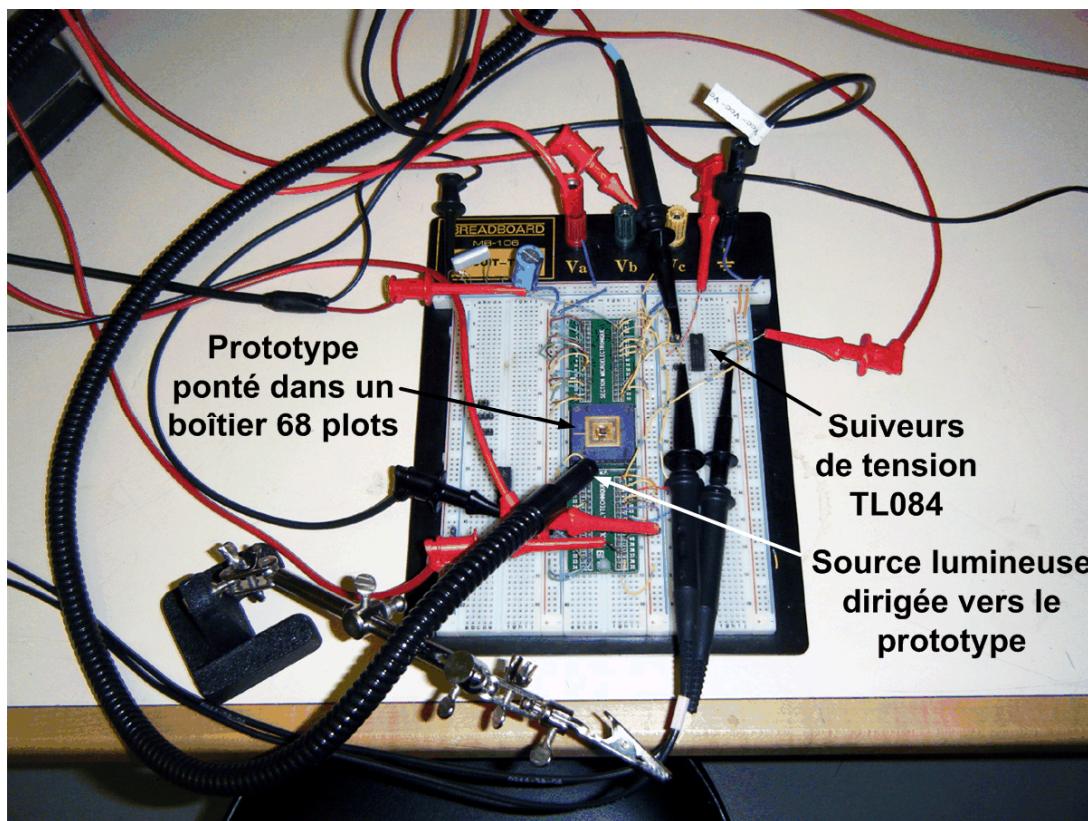

| Figure 3.4 Plan rapproché du montage sur proto-plaquette .....                                                         | 102 |

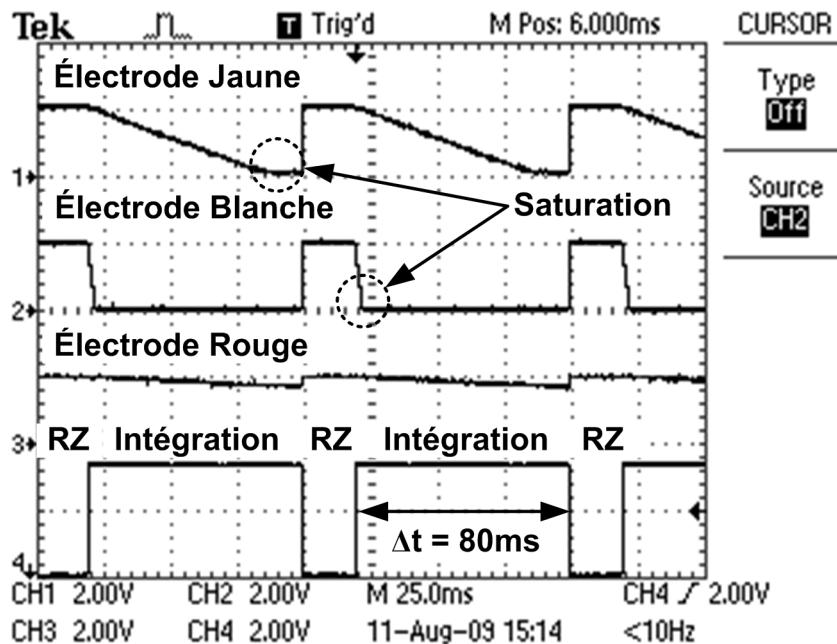

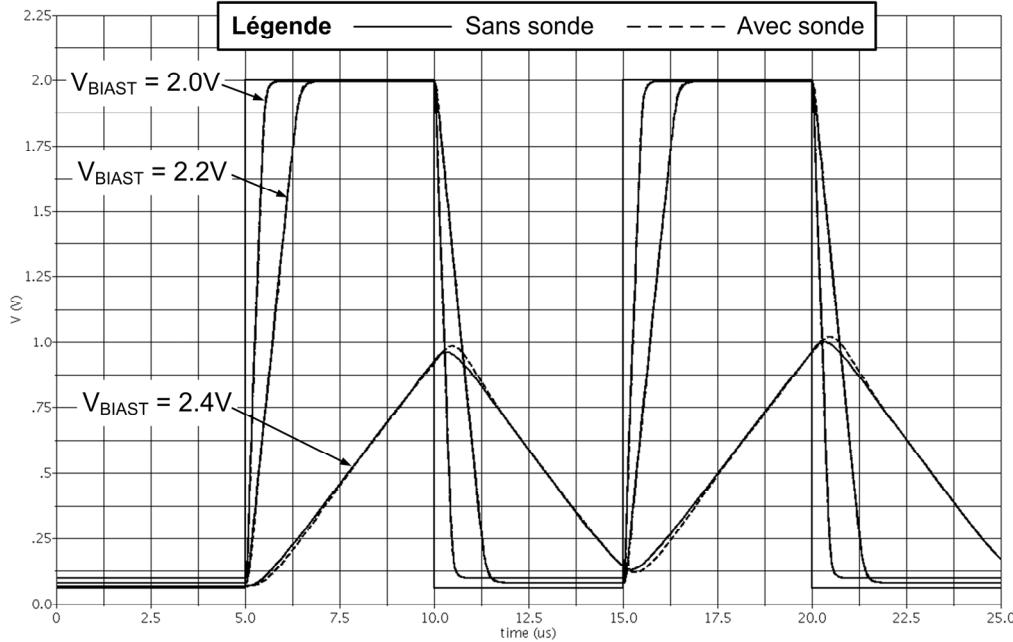

| Figure 3.5 Fonctionnement du pixel actif à intégrateur inverseur .....                                                 | 104 |

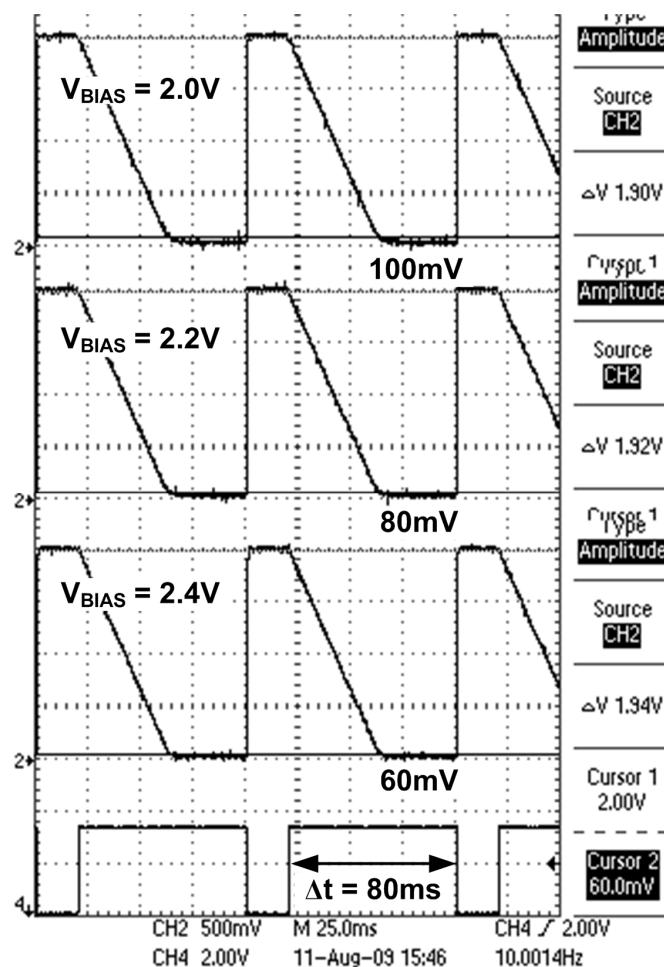

| Figure 3.6 Limites d'excursion inférieure de la tension de sortie.....                                                 | 105 |

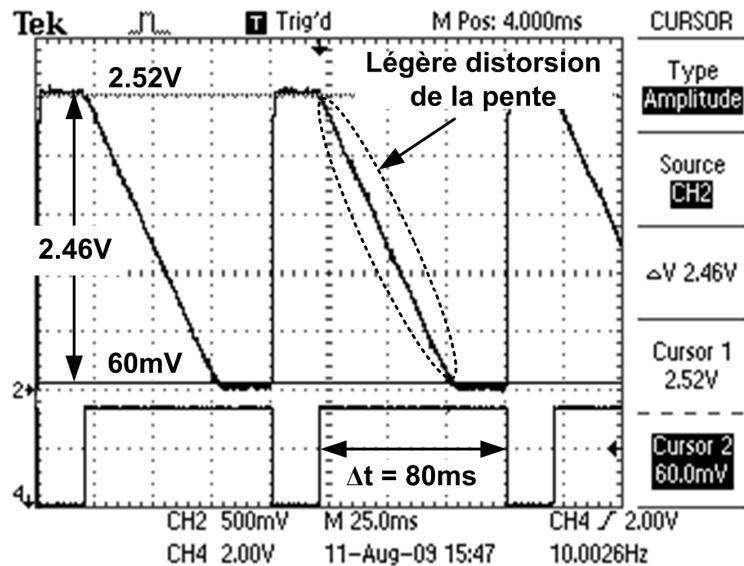

| Figure 3.7 Écart dynamique maximal absolu du pixel actif.....                                                          | 106 |

| Figure 3.8 Délais de remise à zéro et intégration.....                                                                 | 107 |

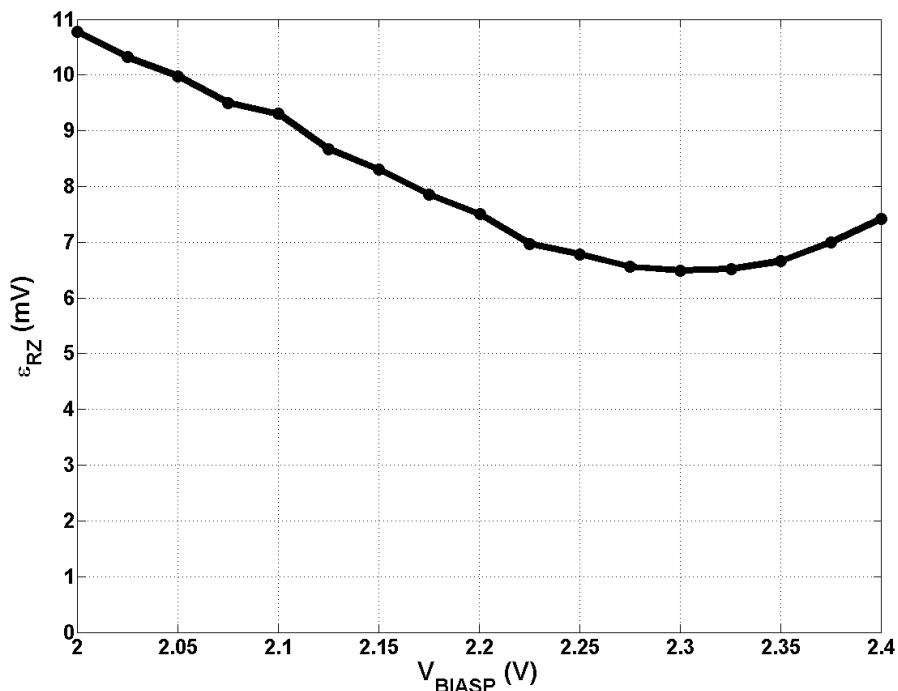

| Figure 3.9 Tension de décalage lors de la remise à zéro.....                                                           | 111 |

| Figure 3.10 Courants de noirceur du photodétecteur .....                                                               | 112 |

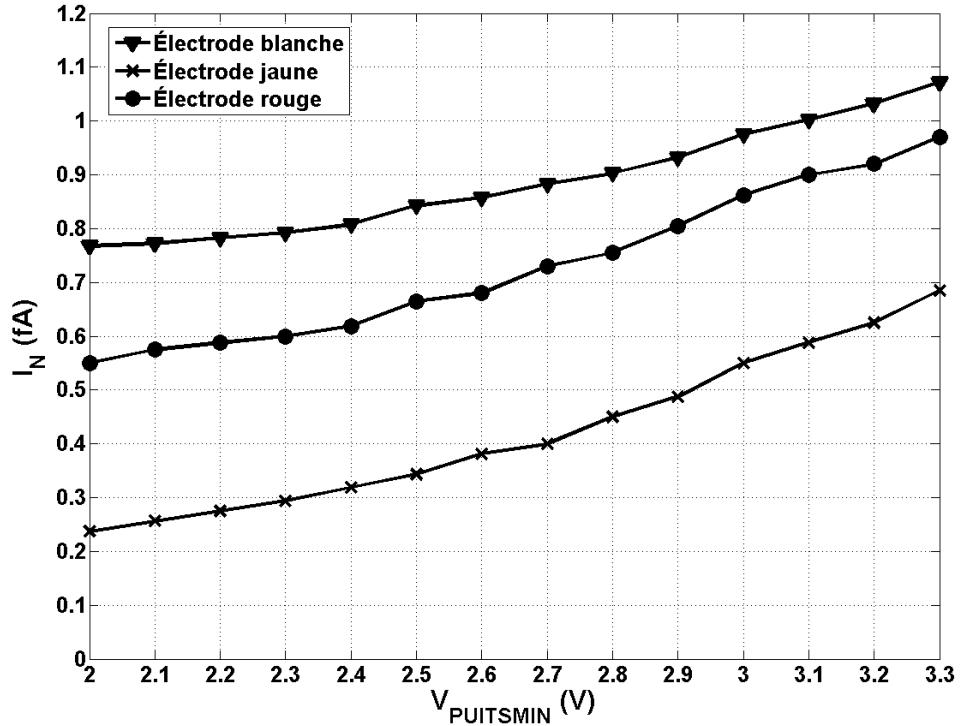

| Figure 3.11 Courants de noirceur en fonction de la tension $V_{PUITSMIN}$ .....                                        | 114 |

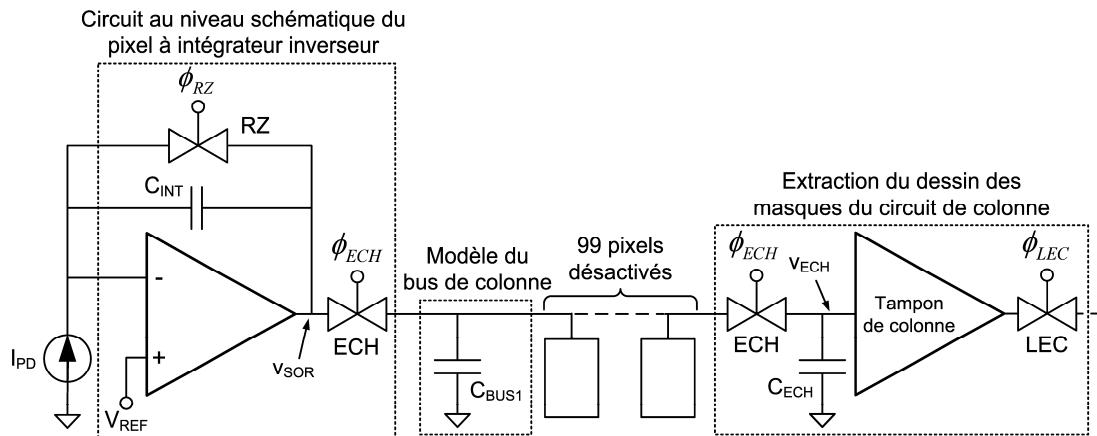

| Figure 3.12 Circuit de simulation utilisé pour évaluer le délai d'échantillonnage .....                                | 115 |

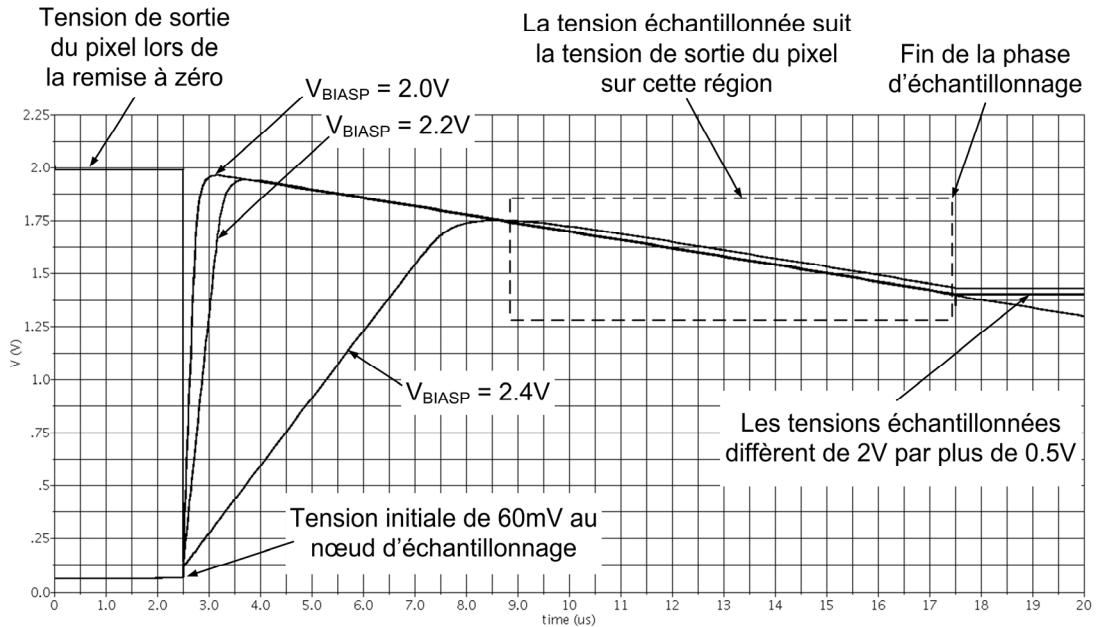

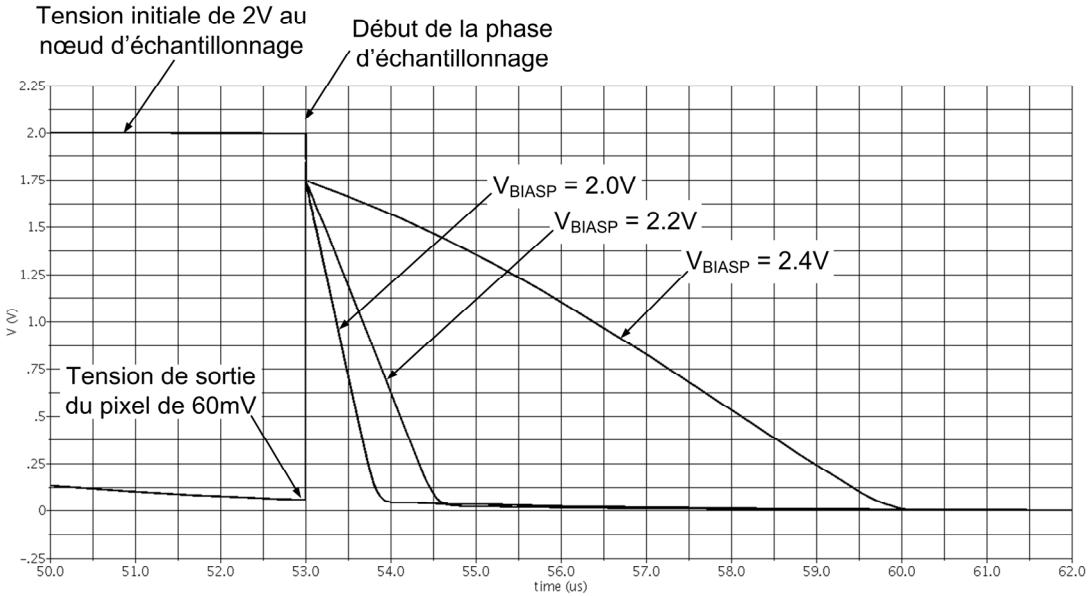

| Figure 3.13 Analyse transitoire de la phase d'échantillonnage (montée) .....                                           | 117 |

| Figure 3.14 Analyse transitoire de la phase d'échantillonnage (descente) .....                                         | 118 |

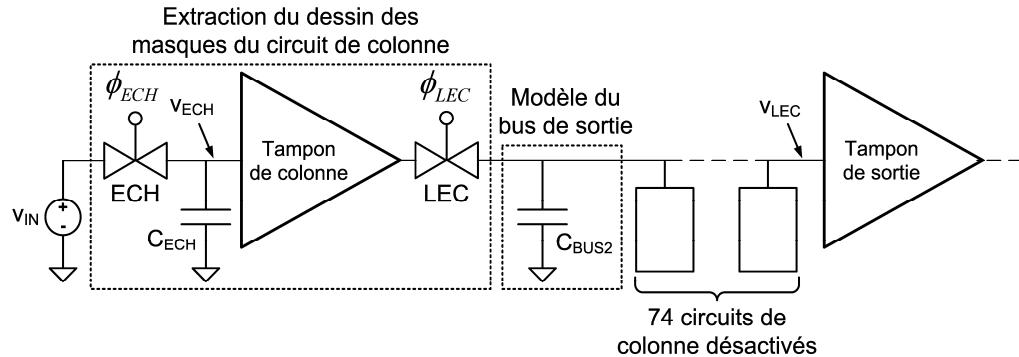

| Figure 3.15 Circuit de simulation utilisé pour caractériser les tampons de colonne.....                                | 119 |

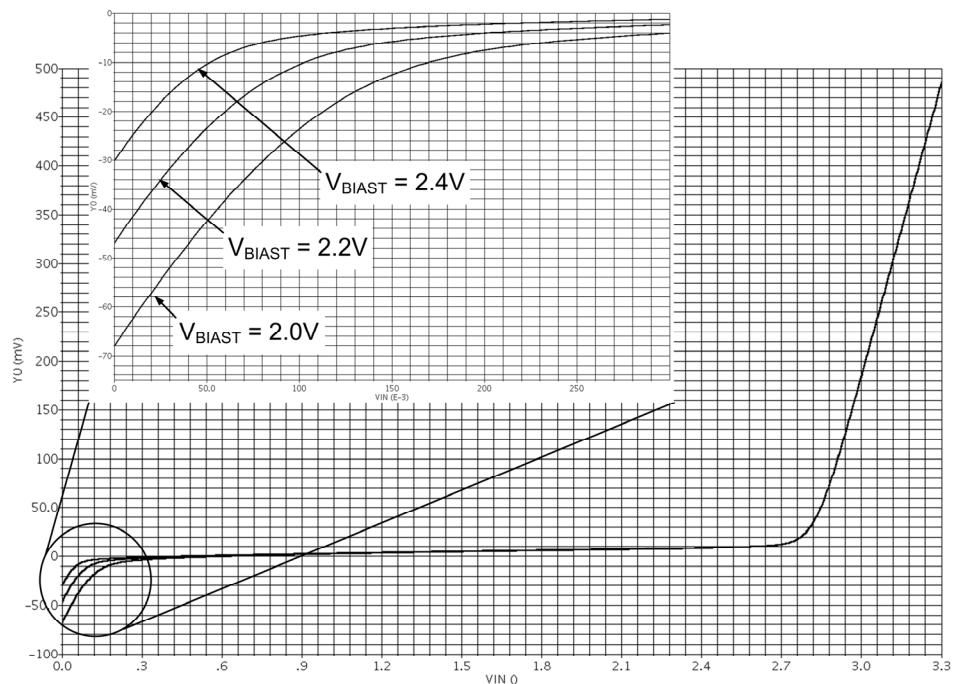

| Figure 3.16 Tension de décalage du tampon de colonne .....                                                             | 121 |

| Figure 3.17 Réponse transitoire du tampon de colonne.....                                                              | 122 |

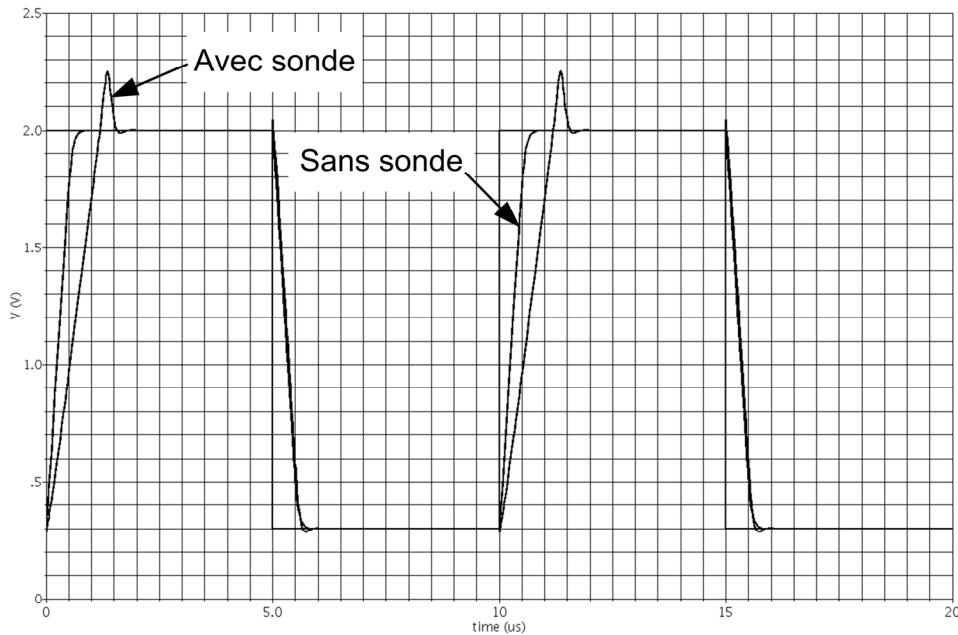

| Figure 3.18 Circuit de simulation utilisé pour caractériser les tampons de sortie .....                                | 124 |

|                                                                                                                      |     |

|----------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.19 Tension de décalage du tampon de sortie (sans sonde) .....                                               | 125 |

| Figure 3.20 Réponse transitoire du tampon de sortie.....                                                             | 127 |

| Figure 3.21 Réponse transitoire combinée des tampons de colonne et de sortie.....                                    | 129 |

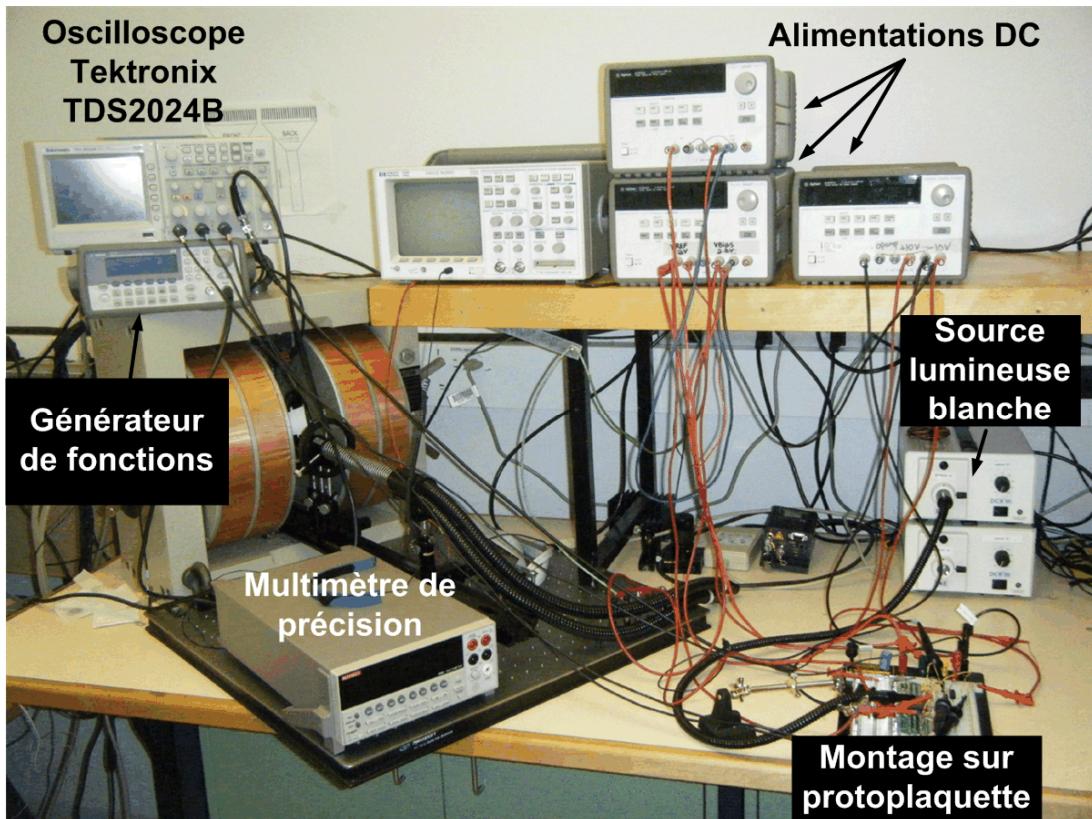

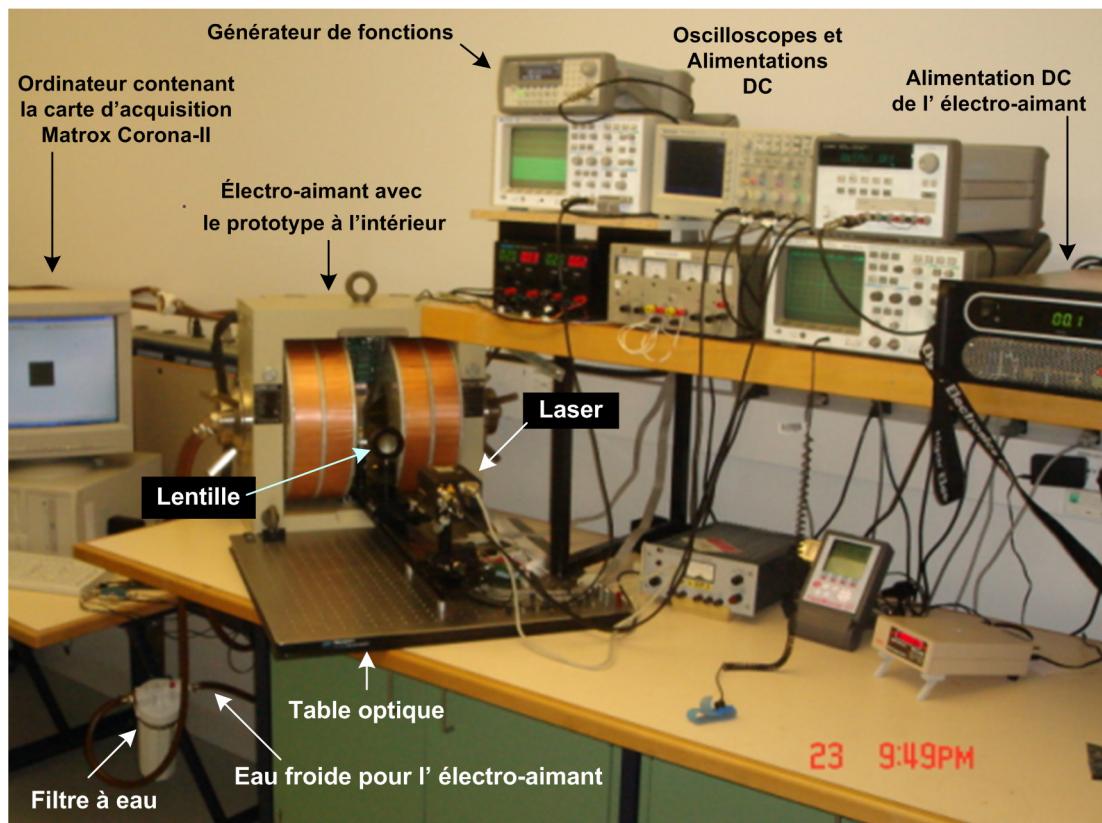

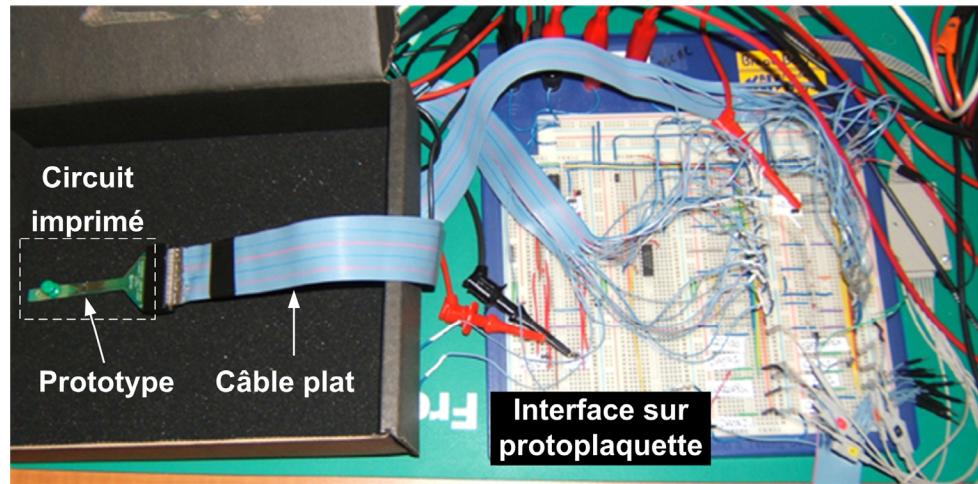

| Figure 3.22 Banc d'essai utilisé pour tester la matrice principale .....                                             | 130 |

| Figure 3.23 Circuit imprimé et interface électronique .....                                                          | 131 |

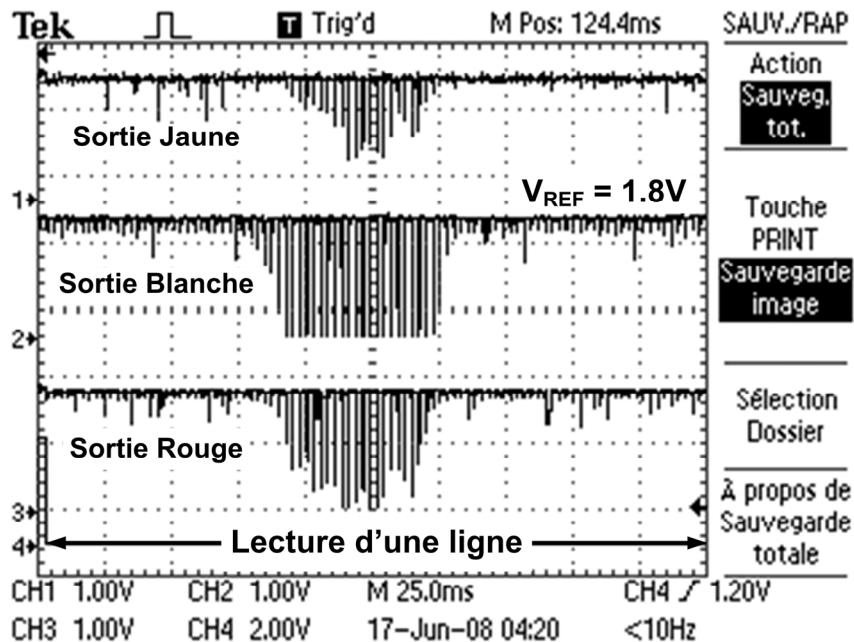

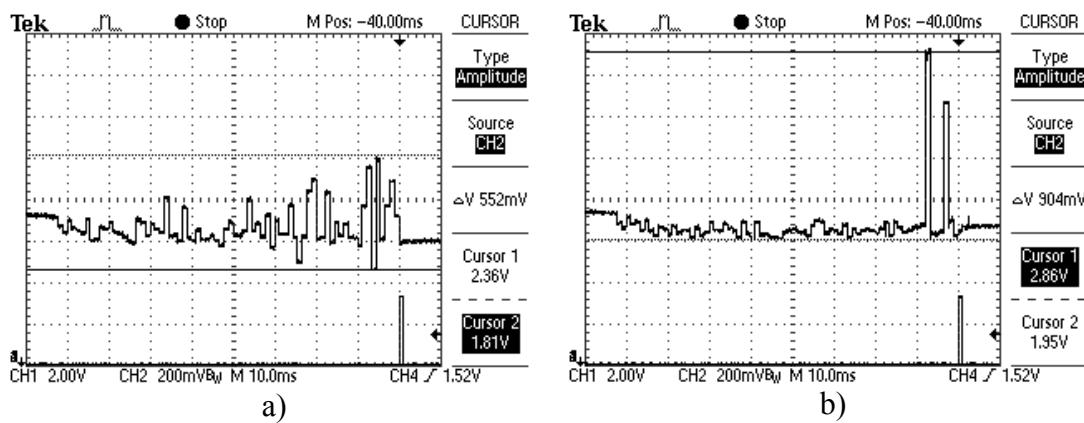

| Figure 3.24 Réponse d'une ligne à un faisceau laser rouge.....                                                       | 132 |

| Figure 3.25 Image monochromatique acquise avec la matrice principale.....                                            | 134 |

| Figure 3.26 Lecture d'une ligne remise à zéro.....                                                                   | 136 |

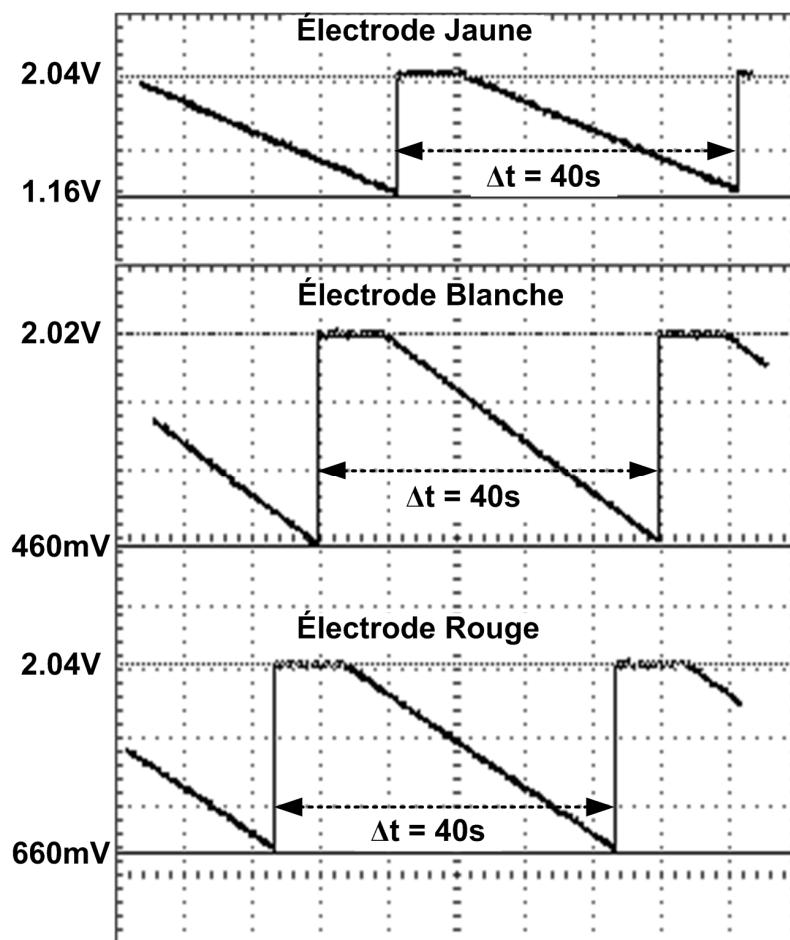

| Figure 3.27 Intégration du courant de noirceur des photodétecteurs .....                                             | 137 |

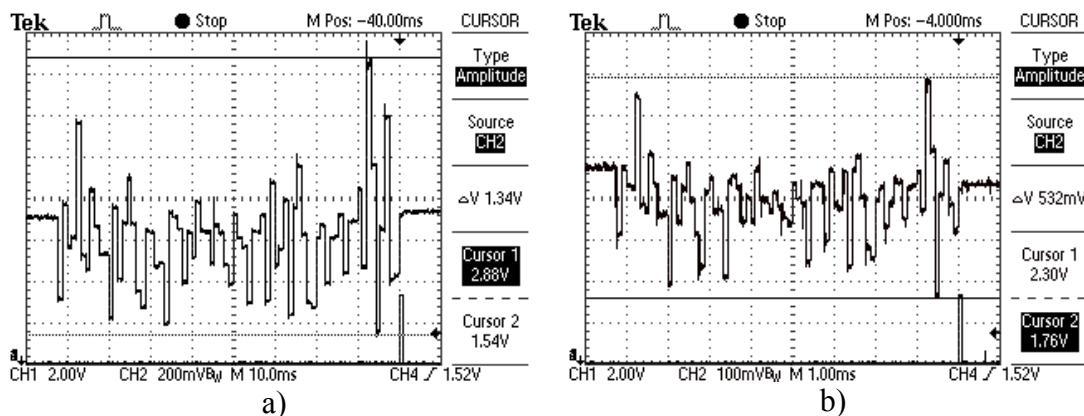

| Figure 3.28 Tension de décalage totale.....                                                                          | 138 |

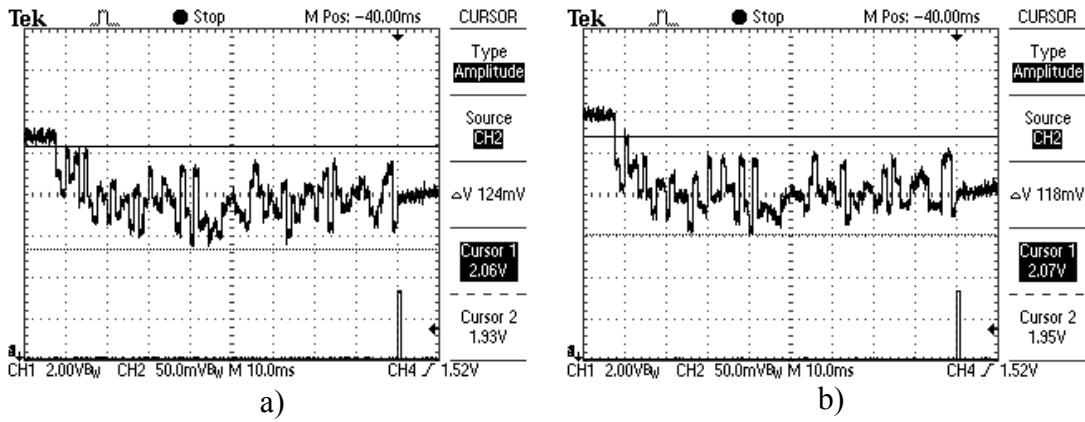

| Figure 3.29 Mesure expérimentale du bruit temporel.....                                                              | 139 |

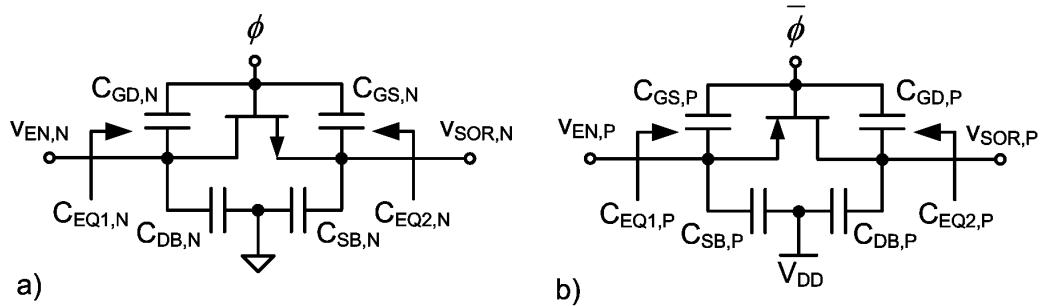

| Figure A.1 Portes de transmission NMOS et PMOS .....                                                                 | 153 |

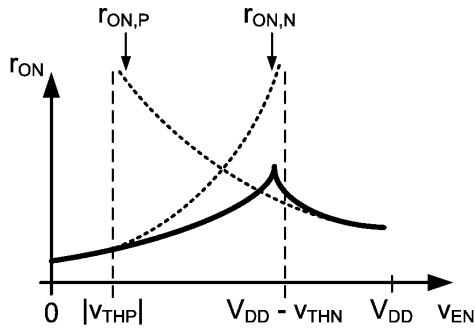

| Figure A.2 Plage de conduction.....                                                                                  | 154 |

| Figure A.3 Résistance d'une porte de transmission activée.....                                                       | 156 |

| Figure A.4 Capacités équivalentes des portes de transmission.....                                                    | 157 |

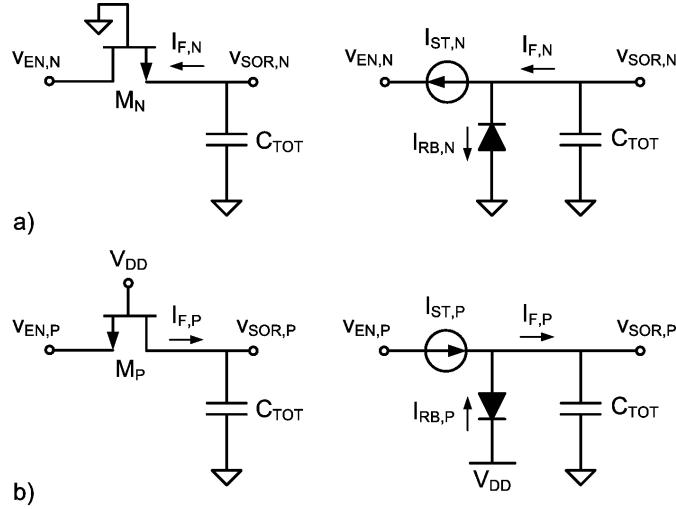

| Figure A.5 Courant de fuite d'une porte de transmission désactivée .....                                             | 159 |

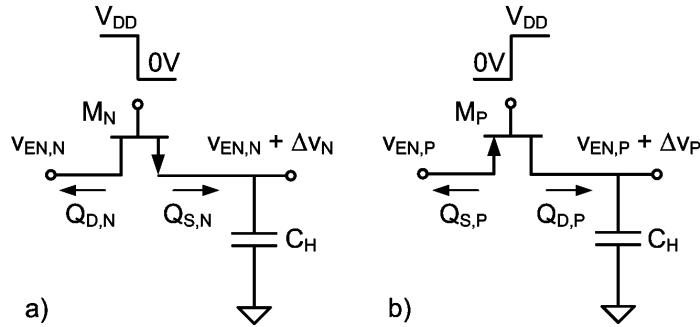

| Figure A.6 Injection de charge.....                                                                                  | 160 |

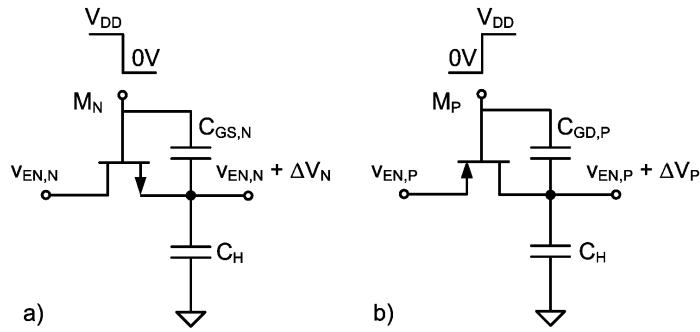

| Figure A.7 Transfert de charge dû au signal de commande.....                                                         | 162 |

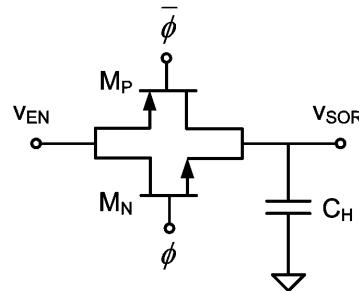

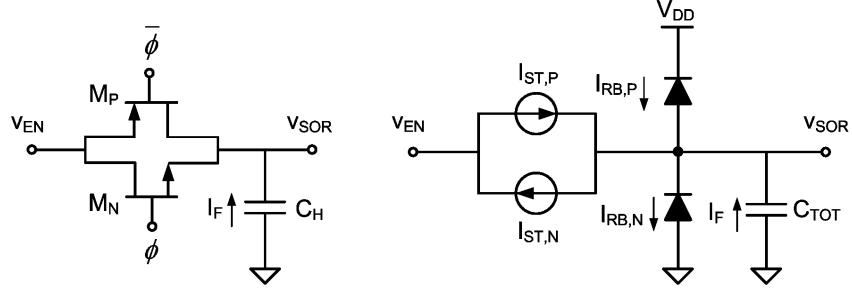

| Figure A.8 Porte de transmission CMOS.....                                                                           | 163 |

| Figure A.9 Résistance d'une porte CMOS activée .....                                                                 | 164 |

| Figure A.10 Courant de fuite de la porte CMOS désactivée .....                                                       | 165 |

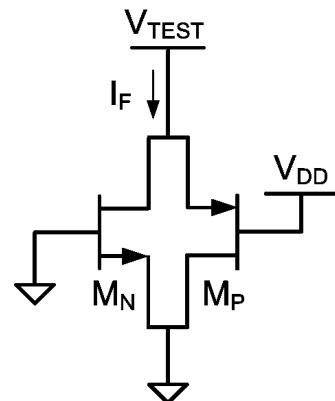

| Figure A.11 Évaluation du courant de fuite .....                                                                     | 167 |

| Figure A.12 Courant de fuite de la porte CMOS .....                                                                  | 168 |

| Figure A.13 Résistance de la porte CMOS désactivée .....                                                             | 168 |

| Figure A.14 Évaluation de la résistance d'une porte CMOS activée.....                                                | 169 |

| Figure A.15 Résistance de la porte CMOS activée.....                                                                 | 170 |

| Figure A.16 Circuit utilisé pour déterminer la capacité équivalente d'une porte de transmission CMOS désactivée..... | 171 |

|                                                                                                                   |     |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Figure A.17 Circuit utilisé pour déterminer la capacité équivalente d'une porte de transmission CMOS activée..... | 173 |

| Figure A.18 Modèles électriques simplifiés d'une porte de transmission .....                                      | 174 |

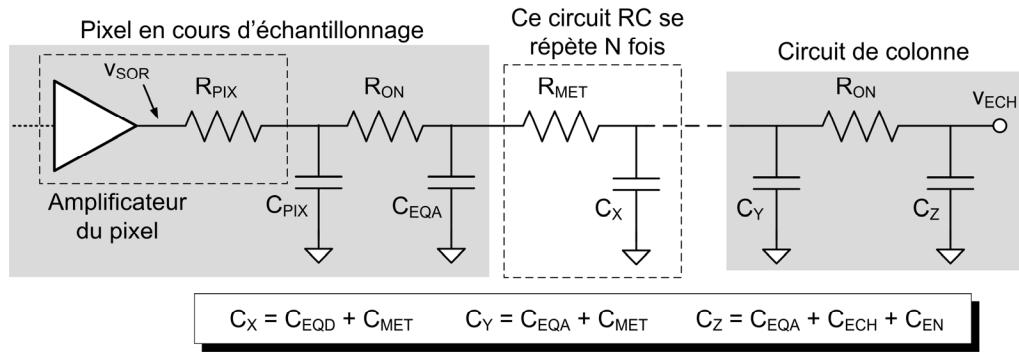

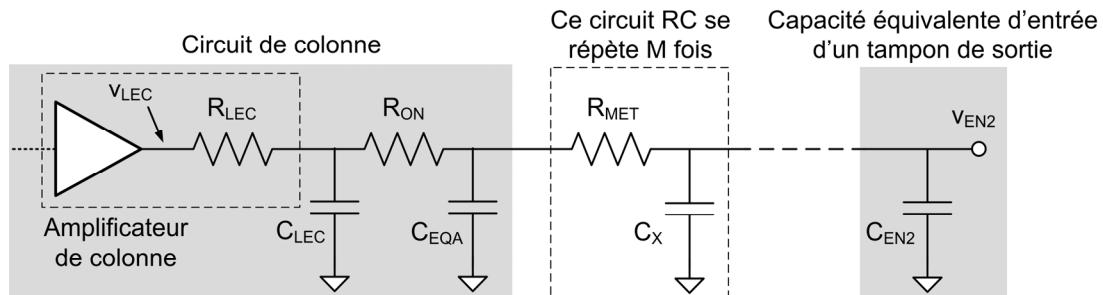

| Figure B.1 Bus de colonne durant l'échantillonnage d'un pixel.....                                                | 175 |

| Figure B.2 Circuit équivalent d'un bus de colonne durant l'échantillonnage .....                                  | 176 |

| Figure B.3 Circuit équivalent d'un bus de sortie durant la lecture .....                                          | 178 |

| Figure C.1 Schéma électrique d'un pixel actif.....                                                                | 180 |

| Figure C.2 Dessin des masques d'un pixel actif .....                                                              | 180 |

| Figure C.3 Schéma électrique d'un circuit de colonne (1/3) .....                                                  | 181 |

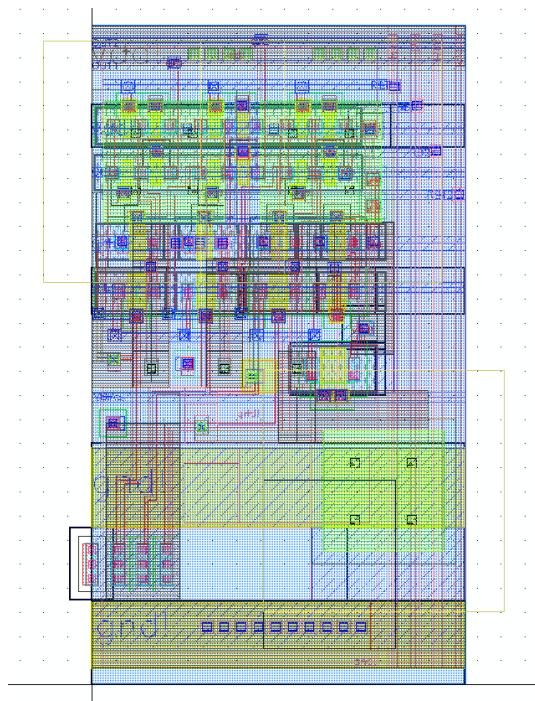

| Figure C.4 Dessin des masques d'un circuit de colonne.....                                                        | 181 |

| Figure C.5 Dessin des masques d'un tampon de sortie.....                                                          | 182 |

| Figure C.6 Dessin des masques du prototype .....                                                                  | 182 |

| Figure D.1 Capacité d'entrée du tampon de colonne.....                                                            | 183 |

| Figure D.2 Modèle petit signal simplifié du tampon de colonne.....                                                | 185 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|      |                                         |

|------|-----------------------------------------|

| °    | Degré                                   |

| aA   | Attoampère                              |

| APS  | Active Pixel Sensor                     |

| CAN  | Convertisseur analogique à numérique    |

| CCD  | Charge-Coupled Device                   |

| CDS  | Correlated Double Sampling              |

| CFA  | Color Filter Array                      |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| COC  | Camera On Chip                          |

| dB   | Décibel                                 |

| DSC  | Digital Still Camera                    |

| DPS  | Digital Pixel Sensor                    |

| DRS  | Delta Reset Sampling                    |

| fF   | Femtofarad                              |

| FPGA | Field-Programmable Gate Array           |

| FPN  | Fixed Pattern Noise                     |

| GΩ   | Giga-ohm                                |

| JFET | Junction Field-Effect Transistor        |

| kΩ   | Kilo-ohm                                |

| ms   | Milliseconde                            |

| mV   | Millivolt                               |

| mW   | Milliwatt                               |

| MHz  | Mégahertz                               |

| MΩ   | Méga-ohm                                |

| NMOS | N-type Metal-Oxide-Semiconductor        |

| nA   | Nanoampère                              |

| nF   | Nanofarad                               |

|                  |                                            |

|------------------|--------------------------------------------|

| nV               | Nanovolt                                   |

| pA               | Picoampère                                 |

| PC               | Personal Computer                          |

| pF               | Picofarad                                  |

| pHz              | Picoherz                                   |

| PIN              | P-Intrinsic-N                              |

| PMOS             | P-type Metal-Oxide-Semiconductor           |

| PPD              | Pinned Photodiode                          |

| PPS              | Passive Pixel Sensor                       |

| RVB              | Rouge Vert Bleu                            |

| s                | Seconde                                    |

| Si               | Silicium                                   |

| SiO <sub>2</sub> | Dioxyde de silicium                        |

| T                | Tesla                                      |

| THz              | Terahertz                                  |

| TSMC             | Taiwan Semiconductor Manufacturing Company |

| TΩ               | Téra-ohm                                   |

| μm               | Micromètre                                 |

| μs               | Microseconde                               |

| μV               | Microvolt                                  |

| V                | Volt                                       |

| VGA              | Video Graphics Array                       |

| W                | Watt                                       |

| 1.75T-APS        | 1.75 transistor Active Pixel Sensor        |

| 3T-APS           | Three transistor Active Pixel Sensor       |

| 4T-APS           | Four transistor Active Pixel Sensor        |

## LISTE DES ANNEXES

|                                                                         |     |

|-------------------------------------------------------------------------|-----|

| ANNEXE A CARACTÉRISATION DES PORTES DE TRANSMISSION.....                | 152 |

| A.1 THÉORIE DES PORTES DE TRANSMISSION.....                             | 152 |

| A.1.1 Portes de transmission NMOS et PMOS .....                         | 152 |

| A.1.2 Portes de transmission CMOS .....                                 | 163 |

| A.2 CARACTÉRISATION PAR SIMULATION.....                                 | 166 |

| A.2.1 Courant de fuite et résistance équivalente en mode désactivé..... | 167 |

| A.2.2 Résistance équivalente en mode activé.....                        | 169 |

| A.2.3 Capacité équivalente en mode désactivé .....                      | 170 |

| A.2.4 Capacité équivalente en mode activé.....                          | 171 |

| A.3 MODÈLES ÉLECTRIQUES SIMPLIFIÉS DES PORTES DE TRANSMISSION .....     | 174 |

| ANNEXE B CIRCUITS ÉQUIVALENTS DES BUS DE SIGNAUX.....                   | 175 |

| B.1 CIRCUIT ÉQUIVALENT D’UN BUS DE COLONNE .....                        | 175 |

| B.2 CIRCUIT ÉQUIVALENT D’UN BUS DE SORTIE .....                         | 178 |

| ANNEXE C SCHÉMAS ÉLECTRIQUES ET DESSINS DES MASQUES .....               | 180 |

| ANNEXE D CAPACITÉ D’ENTRÉE DU TAMPON DE COLONNE.....                    | 183 |

## INTRODUCTION

L’extinction des médias analogiques au profit des supports numériques est désormais une prémissse acquise qui, lorsque couplée à la miniaturisation des produits électroniques, engendre un besoin grandissant au niveau des interfaces de conversion entre l’univers analogique et le monde numérique. Cette observation est d’autant plus vérifique en ce qui concerne les capteurs d’image, auxquels est dévouée une importante partie de la recherche en microélectronique. Les travaux de recherche actuels visent plus spécifiquement à satisfaire la demande croissante pour les capteurs d’image miniatures, légers, peu énergivores et performants. Les champs d’application de tels capteurs sont vastes et s’étendent des appareils-photo numériques haute-performance jusqu’aux caméras destinées à améliorer la vision dans les véhicules automobiles, en passant par les capteurs dédiés aux téléphones cellulaires et les systèmes de vision robotique.

Les avancées technologiques majeures accomplies ces dernières années dans le domaine des procédés de fabrication CMOS (*Complementary Metal-Oxide-Semiconductor*) ont causé une réorientation de la recherche de pointe, qui a délaissé progressivement les capteurs CCD (*Charge-Coupled Device*) en faveur des capteurs CMOS. Ces derniers sont désormais en mesure d’offrir une qualité d’image s’approchant à plusieurs égards à celle des capteurs CCD, tout en permettant l’intégration simultanée, sur un même substrat, des pixels et des circuits de traitement du signal. En outre, la consommation de puissance des capteurs CMOS est généralement inférieure à celle des capteurs CCD, ce qui en fait un choix logique pour les applications mobiles alimentées par accumulateurs.

Malgré ces améliorations, les capteurs d’image actuels, qu’ils soient de type CMOS ou CCD, présentent une limitation importante en ce qui concerne la résolution spatiale. En effet, même les capteurs d’image les plus performants actuellement disponibles sur le marché offrent une résolution spatiale largement inférieure à celle obtenue avec une pellicule chimique photosensible. Cette lacune découle principalement du fait que la

taille d'un pixel électronique est plus grande que celle d'un pixel chimique et que les photodétecteurs électroniques conventionnels sont uniquement sensibles à l'intensité lumineuse et n'offrent pas la possibilité de distinguer la longueur d'onde de la lumière reçue.

Par conséquent, la discrimination des couleurs est habituellement assurée par un filtre chromatique superposé à la matrice de pixels. Ainsi, chaque pixel répond à l'intensité lumineuse correspondant à la longueur d'onde traversée par le filtre. Afin de déterminer correctement la couleur perçue, on doit combiner les lectures de plusieurs pixels qui répondent à des longueurs d'ondes différentes. On crée donc habituellement des regroupements de quatre pixels sensibles à différentes longueurs d'ondes et on utilise un algorithme d'interpolation pour en extraire la couleur globale. Bien qu'une augmentation du nombre de pixels qui composent le capteur favorise une meilleure résolution spatiale, même les capteurs les plus performants ne parviennent pas, à ce jour, à atteindre une résolution spatiale comparable à celle des pellicules chimiques photosensibles traditionnelles de bonne qualité. De plus, l'utilisation d'un filtre chromatique réduit la sensibilité des capteurs d'images en absorbant et réfléchissant une partie de l'énergie lumineuse et augmente les coûts de production en raison de l'étape supplémentaire de fabrication requise pour déposer le filtre chromatique sur la matrice de pixels.

Dans le but de pallier à ces inconvénients, l'équipe de recherche du professeur Yves Audet (équipe de travail Foryon) a développé un nouveau type de photodétecteur qui discrimine les couleurs et élimine la nécessité d'un filtre chromatique. Celui-ci comporte trois électrodes indépendantes qui réagissent à des couleurs distinctes, assurant ainsi la détection chromatique à même le pixel. D'autre part, ce photodétecteur peut être fabriqué à l'aide d'une technologie CMOS standard, ce qui en fait un candidat idéal pour l'intégration des circuits périphériques de traitement des signaux et la réalisation d'une caméra sur puce (COC, *Camera On Chip*).

Le présent travail de recherche consiste principalement en la conception d'une nouvelle topologie de pixel actif (APS, *Active Pixel Sensor*) basée sur le comportement électrique expérimental et simulé du photodétecteur sans filtre. Cette architecture de pixel actif innovatrice est actuellement en cours d'homologation pour un brevet [4]. Elle procure une excellente linéarité, un très bon écart dynamique et permet, par sa flexibilité, de poursuivre la caractérisation du photodétecteur sans filtre. En outre, sa structure différentielle permet d'effectuer la compensation du courant de noirceur des photodétecteurs à l'intérieur même du pixel, tel que détaillé dans un article de conférence publié [6].

La seconde partie du travail de recherche porte sur la conception des circuits d'échantillonnage et d'amplification périphériques qui permettent de véhiculer les signaux produits par le pixel actif innovateur vers l'extérieur du circuit intégré. Afin de valider le fonctionnement expérimental des circuits conçus, le prototype de capteur d'images a été fabriqué en technologie CMOS  $0.25\mu\text{m}$ .

L'organisation de ce mémoire se divise en trois chapitres. Tout d'abord, le premier chapitre décrit les principes de base des capteurs d'image CMOS, présente une revue de la littérature des différents circuits analogiques qui les composent et introduit le photodétecteur sans filtre innovateur. Ensuite, le second chapitre analyse les divers circuits employés dans le prototype de capteur d'images et détaille le processus de conception. Enfin, le troisième chapitre présente les résultats expérimentaux obtenus à l'aide du prototype de capteur d'images, ainsi que des résultats de simulation complémentaires.

# CHAPITRE 1

## PRINCIPES DE BASE DES CAPTEURS D'IMAGES CMOS

### 1.1 Introduction

Le capteur d'images est la pierre angulaire de tout système d'acquisition d'images, quelle que soit son application. En effet, les simulations et les études expérimentales ont démontré que le capteur d'images est l'élément qui établit la limite de performance d'un système d'acquisition d'images [9]. Cette raison justifie à elle seule la recherche extensive dévouée aux capteurs d'images depuis plusieurs années et, par le fait même, le présent projet de recherche.

Jusqu'à la fin des années 1990, les capteurs de type CCD ont dominé le marché de façon outrageuse en raison de leur qualité d'image exceptionnelle [9], [21], [22], [27]. Forts des innovations technologiques et des efforts de recherche soutenus des dernières années, les capteurs d'images CMOS ont gagné en termes de qualité d'image et la préférence pour les capteurs CCD s'est estompée pour laisser une plus grande place aux capteurs CMOS [9], [21], [22], [27]. À ce propos, mentionnons que certains capteurs CMOS haut de gamme actuels sont en mesure de procurer une qualité d'image rivalisant avec les capteurs CCD pour les applications telles les caméras numériques (DSC, *Digital Still Camera*) [21].

À l'opposé des capteurs CCD, les capteurs CMOS offrent l'intéressante possibilité d'intégrer les circuits de traitement de signal sur un même substrat en vue d'obtenir une caméra sur puce. De plus, puisque leur tension d'alimentation est plus faible que celle requise par les capteurs CCD, les capteurs CMOS possèdent une consommation de puissance largement inférieure [9], [21], [22], [27], [36]. En outre, mentionnons que les coûts associés à la fabrication des capteurs CMOS sont plus faibles que ceux engendrés par les capteurs CCD, puisque la technologie CMOS est plus répandue et que l'accès à cette dernière est plus aisé [21].

Ces caractéristiques font en sorte que les capteurs d'images CMOS se prêtent à un plus grand nombre d'applications que leurs équivalents à CCD [36]. Parmi celles-ci, on dénombre les produits grand public qui requièrent un coût minime, une faible consommation de puissance et une petite taille, telles les souris optiques, les caméras web, les caméscopes, les téléphones cellulaires et les caméras numériques [9]. De plus, les capteurs CMOS sont idéaux pour les applications qui nécessitent un procédé de traitement des signaux local, compact et efficient, telles les utilisations de surveillance, la vision robotique, les appareils médicaux et les caméras utilisées dans les automobiles [9], [22].

Il est pertinent de noter que la miniaturisation des capteurs CMOS présente un retard sur la réduction d'échelle des technologies CMOS. Ce décalage est principalement attribuable au fait que les procédés CMOS récents et de très petite taille ne se prêtent pas bien aux applications d'acquisition d'images, notamment en raison du bruit élevé, du grand courant de fuite, de la faible sensibilité et des difficultés optiques [27]. Puisque l'utilisation d'une technologie de plus petite taille réduit les dimensions d'un pixel et permet d'augmenter la résolution, des efforts considérables sont faits en vue d'améliorer la performance optique de la technologie CMOS  $0.18\mu\text{m}$  [9]. À cet effet, il est suggéré que la miniaturisation des pixels CMOS sera limitée par la quantité d'électrons qui peuvent être emmagasinés dans un pixel [27].

Ce chapitre vise à détailler les principes de base des capteurs d'images CMOS. Dans un premier temps, la structure générale et le fonctionnement de base des capteurs d'images CMOS seront expliqués. Par la suite, les architectures des pixels et les principaux indicateurs de performance des capteurs d'images seront détaillés. Finalement, une exploration des procédés de discrimination des couleurs couramment utilisés dans les capteurs CMOS commerciaux sera présentée.

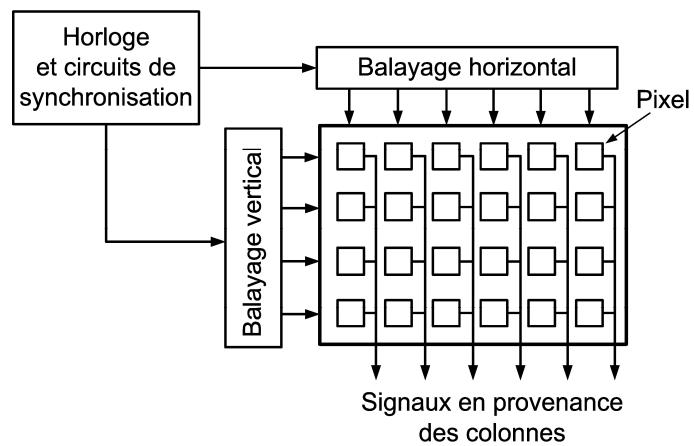

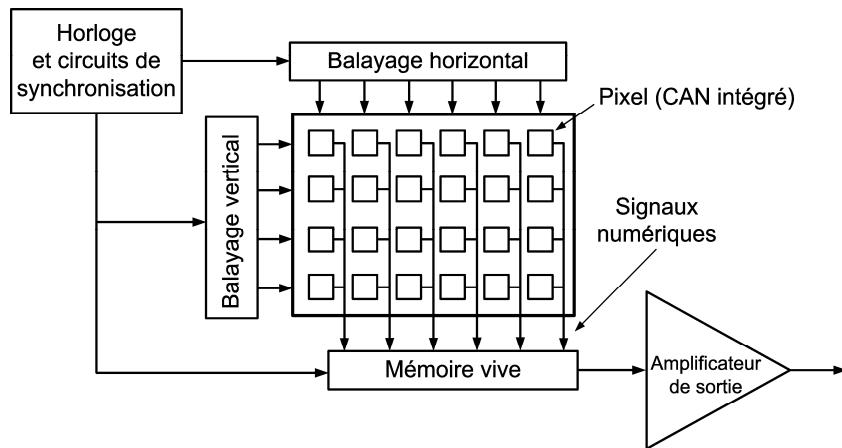

## 1.2 Structure générale des capteurs d'images CMOS

Par définition, un capteur d'images CMOS est un dispositif à semi-conducteurs ayant pour rôle de convertir des signaux lumineux en signaux électriques pouvant ensuite être traités de manière analogique ou numérique et sauvegardés dans une mémoire afin d'en assurer la conservation [21]. La conversion de l'image observée en signaux électriques est effectuée par un regroupement de pixels qui sont disposés en une structure de forme rectangulaire appelée matrice. Le nombre de pixels que comprend une matrice dépend, entre autres, de la complexité et la qualité du capteur et varie de quelques milliers à plusieurs millions. Afin de récupérer et traiter les signaux en provenance de ces pixels, on utilise un mécanisme de balayage qui permet de sélectionner un ou plusieurs pixels à la fois de façon séquentielle ou arbitraire. Cette tâche est confiée à deux blocs synchronisés par une horloge, le premier assurant le balayage horizontal (des colonnes) et le second assurant le balayage vertical (des rangées). La Figure 1.1 illustre la structure générale d'un capteur d'images CMOS. On y retrouve les principaux constituants, soient une matrice de pixels ainsi que des circuits de balayage horizontal et vertical commandés par un circuit de synchronisation [9], [27]. Il est à noter que les pixels d'une même colonne partagent un bus de sortie des données afin de limiter le nombre de connexions à l'intérieur de la matrice.

Figure 1.1 Structure générale d'un capteur d'images CMOS

### 1.2.1 Modes d'accès aux pixels

Contrairement aux capteurs d'images CCD, les capteurs CMOS allouent l'emploi d'un adressage de type X-Y. Celui-ci permet d'alimenter uniquement les pixels désirés à un instant donné, ce qui contribue grandement à réduire la consommation de puissance du capteur d'images [9], [21].

Il existe deux modes d'accès aux pixels qui composent la matrice, le mode séquentiel et le mode arbitraire [21], [22]. Dans le premier cas, on balaie séquentiellement la totalité de la matrice qui est considérée comme une trame continue. Ainsi, une impulsion de sélection est habituellement fournie à chaque ligne et les colonnes sont ensuite parcourues une à la fois [21]. Pour ce faire, on utilise des circuits de balayage à base de registres à décalage, ce qui en fait une technique simple à implémenter et qui procure un faible bruit de commutation [21]. Dans le cas où l'on désire accéder aux pixels arbitrairement, on emploie un circuit de balayage à base de décodeurs. Ces derniers assurent une grande flexibilité et permettent, si désiré, de lire uniquement une portion de la matrice. Cette particularité est d'ailleurs utilisée par certains capteurs multi-résolution puisqu'elle permet de varier les dimensions de la matrice de façon dynamique [22]. L'utilisation de décodeurs augmente cependant la complexité de la logique de commande et, par conséquent, le bruit de commutation.

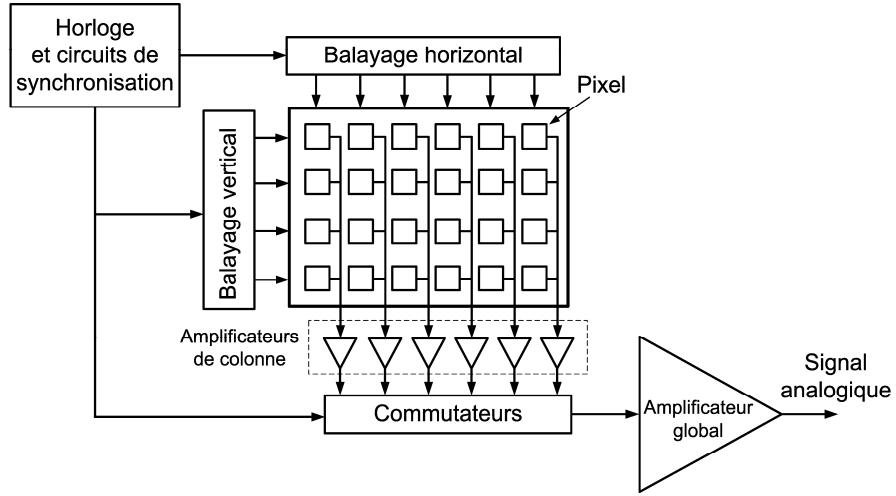

### 1.2.2 Traitement des signaux

Le traitement des signaux en provenance de la matrice de pixels peut s'effectuer de façon analogique ou numérique [21]. Dans le cas d'un traitement entièrement analogique, on utilise généralement un amplificateur global commun à toute la matrice de pixels, auquel on ajoute des amplificateurs partagés par les pixels d'une même colonne afin de réduire le bruit et l'effet de charge, tel qu'illustré à la Figure 1.2. Les commutateurs analogiques permettent quant à eux d'effectuer un multiplexage temporel en n'envoyant à l'amplificateur global que les signaux en provenance de la colonne désirée.

Figure 1.2 Méthode générale de traitement analogique

Une telle architecture était surtout utilisée à l'époque des premiers capteurs d'images CMOS. Toutefois, les capteurs à sortie numérique sont récemment devenus très populaires en raison de la simplicité apportée par l'élimination de l'interface analogique [21]. Par conséquent, les capteurs d'images CMOS modernes intègrent de facto une conversion analogique à numérique [27], ce qui permet, entre autres, d'effectuer le traitement des couleurs et les procédés de réduction du bruit de façon numérique [22].

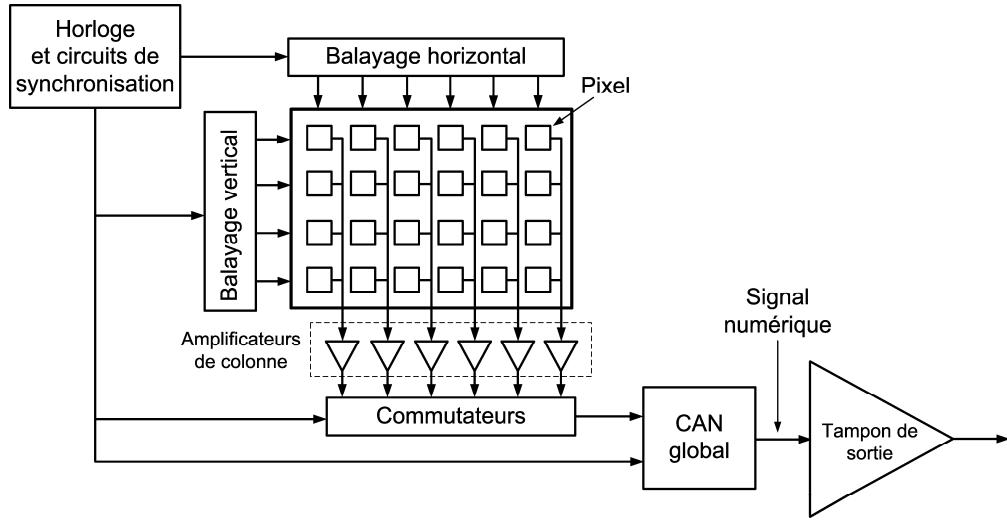

À ce propos, il existe trois méthodes distinctes pour numériser le signal analogique en provenance des pixels [12], [21], [22], [36]. La première méthode, illustrée à la Figure 1.3, consiste à remplacer l'amplificateur global vu précédemment par un convertisseur analogique à numérique (CAN) partagé par la totalité de la matrice. Cette façon de faire est pratique, réduit la dissipation de puissance et assure un traitement numérique identique pour chaque pixel, mais requiert un convertisseur de très haute qualité pour permettre une opération à grande vitesse et avec faible bruit [12], [22]. La présence d'un tampon en sortie aide à préserver l'intégrité des signaux numériques lorsque le capteur est relié à une charge externe.

Figure 1.3 Conversion analogique à numérique globale

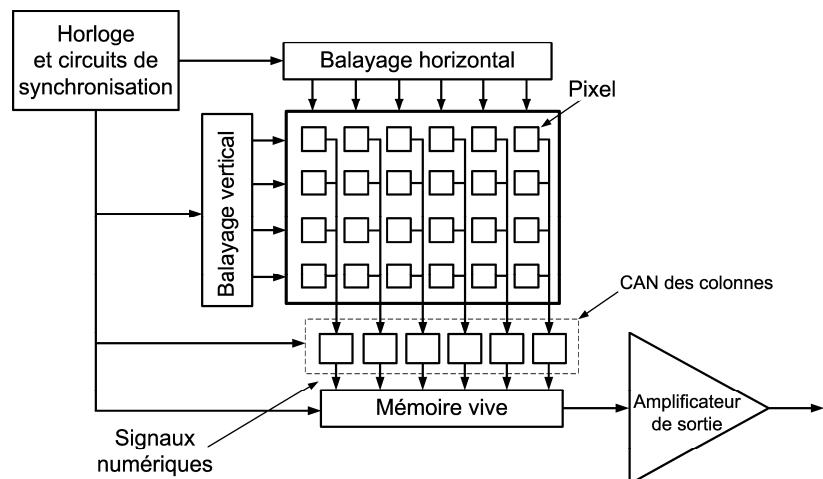

La seconde méthode de traitement, montrée à la Figure 1.4 consiste à effectuer une conversion analogique à numérique à chacune des colonnes [11], [20], [21], [22], [36], [37]. Puisque les données à envoyer en sortie sont désormais numériques, une mémoire vive remplace le commutateur afin de permettre le multiplexage temporel en mémorisant les données en provenance des colonnes.

Figure 1.4 Conversion analogique à numérique par colonnes

Cette technique est bien adaptée aux capteurs CMOS puisque les rangées de pixels sont électriquement indépendantes [22]. De plus, elle permet l'utilisation de convertisseurs fonctionnant à une vitesse moindre [22], [36]. Ses désavantages sont liés aux contraintes physiques concernant les dimensions des convertisseurs, ces derniers devant être plus étroits que les colonnes, de même que sur la nécessité d'apparier les convertisseurs dans le but de minimiser les variations [36]. Notons à nouveau la présence de l'amplificateur de sortie qui remplit les fonctions susmentionnées.

La Figure 1.5 illustre la troisième méthode qui consiste à effectuer la conversion analogique à numérique à l'intérieur des pixels [9], [12], [21], [22], [29], [36]. Cette architecture permet une plus grande flexibilité de traitement, réduit la charge de travail sur les circuits externes à la matrice, permet l'utilisation de convertisseurs plus lents [12], augmente le rapport signal sur bruit et réduit la consommation de puissance [9], [29], [36]. Ces améliorations se font toutefois aux dépens d'un plus grand nombre de transistors à l'intérieur du pixel, ce qui en augmente la taille [9], [21], [22], [36]. Il s'ensuit que cette méthode de conversion est généralement réservée aux applications où la rapidité de traitement et la faible consommation de puissance priment sur la qualité d'image [21].

Figure 1.5 Conversion analogique à numérique intégrée aux pixels

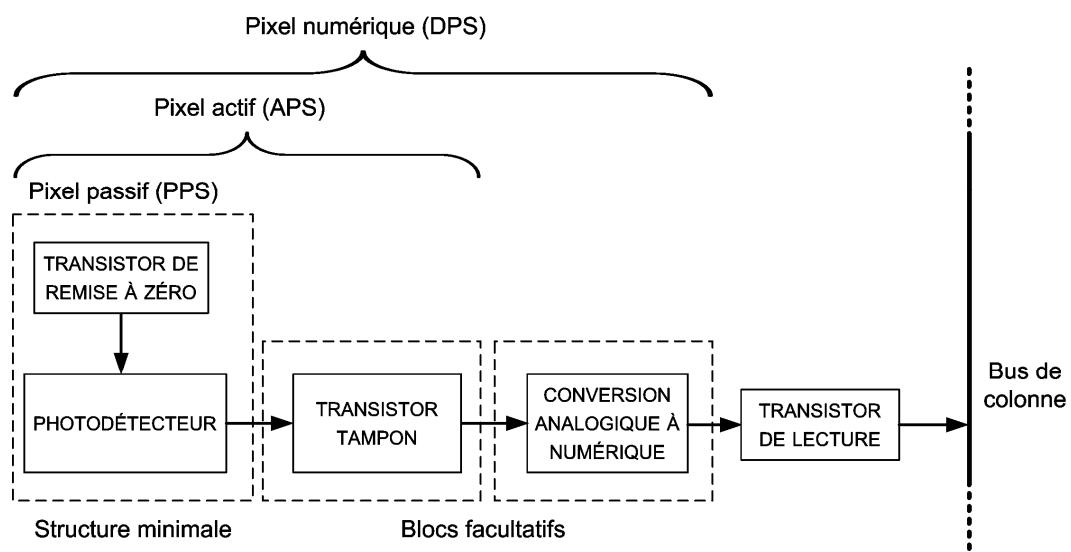

### 1.3 Architectures de pixels

Jusqu'à présent, nous avons considéré les pixels comme étant des blocs de traitement permettant la conversion de la lumière reçue en un signal électrique en sortie. Or, puisque la matrice de pixels détermine en grande partie la qualité d'image d'un capteur CMOS [22], il est important d'en détailler la structure interne. Il existe trois principaux types de pixels CMOS, les pixels passifs (PPS, *Passive Pixel Sensor*), les pixels actifs (APS, *Active Pixel Sensor*) et les pixels numériques (DPS, *Digital Pixel Sensor*). Le schéma-bloc généralisé d'un pixel donné à la Figure 1.6 illustre les différences entre ces trois types de pixels. Mentionnons d'abord que tout pixel CMOS comprend un photodétecteur qui permet la conversion de la lumière captée en charge électronique. Le type de photodétecteur le plus répandu de nos jours est la photodiode, notamment en raison de sa bonne sensibilité [22], [36]. Bien que la charge électronique fournie par le photodétecteur puisse être lue en régime continu, cette façon de faire est déconseillée, car le courant obtenu sous une illumination normale est souvent inférieur à quelques picoampères, ce qui rend difficile le traitement du signal et anéantit le rapport signal sur bruit [9]. De ce fait, les pixels CMOS actuels utilisent plutôt un mode d'opération qui implique l'intégration de la charge électronique à un nœud capacitif [9], [36].

Figure 1.6 Schéma-bloc généralisé d'un pixel CMOS

Le fonctionnement généralisé d'un pixel CMOS se décompose en trois phases distinctes, soient la remise à zéro, l'intégration et la lecture [36]. La remise à zéro consiste à transférer une quantité de charges préétablie aux bornes de la photodiode à l'aide d'un interrupteur à transistor. Ensuite, durant l'intégration, les photons captés par la photodiode causent une réduction du nombre de charges contenues approximativement proportionnelle au niveau d'illumination observé. Suite à la période d'intégration, les charges restantes sont envoyées sur le bus de colonne par l'entremise d'un interrupteur à transistor [36]. Finalement, un amplificateur de charges (amplificateur de transrésistance) convertit ces charges en tension.

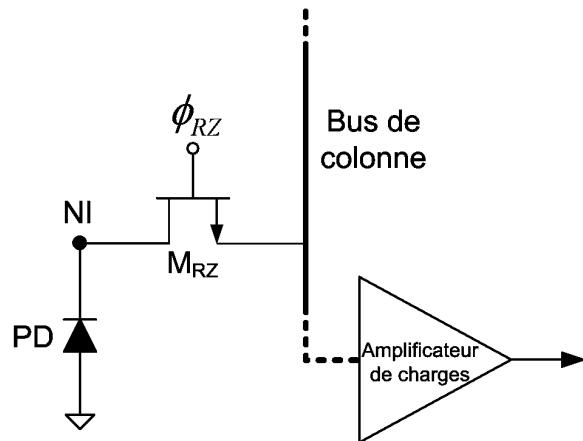

### 1.3.1 Pixel passif (PPS)

Les étapes d'opération énumérées précédemment décrivent le fonctionnement général du pixel passif. Il s'agit du premier type de pixel CMOS à avoir été développé et son schéma électrique est donné à la Figure 1.7 [9], [22], [27], [36]. On y retrouve la photodiode,  $PD$ , le nœud d'intégration,  $NI$ , le transistor  $M_{RZ}$  qui remplit à la fois les fonctions de remise à zéro et de transfert de charges sur le bus de colonne, ainsi que l'amplificateur de charges situé à l'extérieur de la matrice. Bien que cet amplificateur puisse être partagé par toute la matrice, les architectures modernes basées sur le pixel passif emploient un amplificateur par colonne [36].

Figure 1.7 Pixel passif (PPS)

L'utilisation d'un transistor unique est rendue possible en combinant les opérations de lecture et de remise à zéro. Pour ce faire, le bus de colonne est en tout temps soumis à la tension de référence utilisée pour la remise à zéro de la photodiode. Lors de l'opération combinée de lecture et remise à zéro, la différence de tension entre le nœud d'intégration et la tension du bus produit un courant détecté par l'amplificateur de charges, qui convertit ensuite ce courant en tension proportionnelle à l'illumination observée [21], [27], [36].

La performance des capteurs CMOS utilisant ces pixels passifs est largement inférieure à celle offerte par les capteurs CCD, ce qui limite leur utilisation aux applications qui ne demandent qu'une qualité d'image marginale [9]. Plus spécifiquement, la grande capacité parasite des bus de colonne entraîne l'étalement des charges détectées, ce qui rend les signaux de sortie excessivement vulnérables au bruit [9], [27], [29], [36] et augmente dramatiquement le temps de lecture [9], [21], [36]. Par ailleurs, mentionnons que ces inconvénients sont d'autant plus nuisibles que la taille de la matrice de pixels augmente [21]. Certaines innovations ont pour objectif de réduire la vulnérabilité au bruit des pixels passifs [33], mais le grand nombre de transistors qu'elles requièrent diminue les avantages d'une telle stratégie. Pour conclure, mentionnons que, malgré ses lacunes, l'architecture du pixel passif a perduré jusqu'au début des années 1990, car les dimensions des transistors CMOS de l'époque étaient telles que l'on ne pouvait se permettre d'avoir plus d'un transistor par pixel [9].

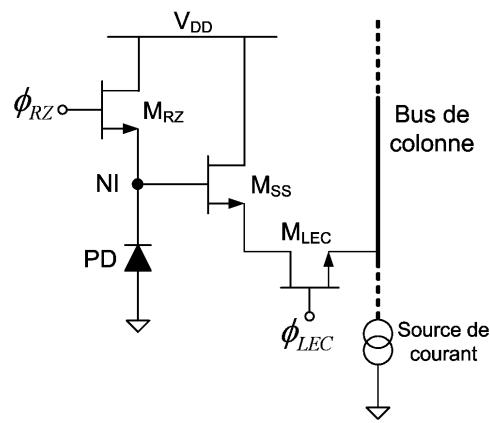

### 1.3.2 Pixels actifs (APS)

L'avènement des technologies CMOS plus compactes, la nécessité de produire des matrices de pixels de plus grande taille et la volonté de corriger les lacunes du pixel passif ont mené à l'invention de la structure du pixel actif. Comme l'illustre la Figure 1.6, un pixel actif reprend la structure de base d'un pixel passif auquel s'ajoute un transistor tampon ayant pour rôle de séparer électriquement le nœud d'intégration et le

bus de colonne [21], [22], [36]. L'ajout de ce transistor augmente la rapidité de lecture et le rapport signal sur bruit [9], [21].

La présence d'un étage tampon entre le nœud d'intégration et le bus de colonne fait en sorte que le transistor de remise à zéro ne peut plus être utilisé comme commutateur de lecture. Quelques astuces ont été présentées pour contrecarrer cet inconvénient [15], mais la solution la plus souvent rencontrée demeure l'architecture de pixel à trois transistors illustrée à la Figure 1.8. On y observe le transistor de remise à zéro,  $M_{RZ}$ , le transistor de lecture,  $M_{LEC}$ , et le transistor tampon configuré en source suiveur,  $M_{SS}$  [36]. Une telle architecture est nommée pixel actif à trois transistors (3T-APS). Son fonctionnement est similaire à celui du pixel passif, à la différence que le signal envoyé sur le bus de colonne n'est pas un courant, mais une tension correspondant à la différence de charge due à l'illumination. Il est à noter que, puisque la charge au nœud d'intégration diminue avec l'illumination, une tension de sortie élevée indique une illumination faible et vice-versa [36].

Figure 1.8 Pixel actif à trois transistors (3T-APS)

La source de courant qui polarise le transistor tampon est située à l'extérieur de la matrice de pixels et elle est partagée par tous les transistors d'une même colonne. Cela contribue à réduire la taille des pixels et les variations de réponse entre ces derniers [36].

Une particularité intéressante du pixel actif est son mode de lecture non-destructif [9], [22]. Ainsi, contrairement au pixel passif, un même signal de sortie peut être lu plusieurs fois sans perte d'information. Cette caractéristique facilite l'implémentation de circuits périphériques de réduction de bruit et ajoute une flexibilité au niveau des modes de lecture. Finalement, mentionnons que la structure à trois transistors peut être utilisée avec n'importe quel type de photodétecteur [36].

Bien que le pixel actif à trois transistors corrige la plupart des lacunes du pixel passif, il présente des inconvénients qui préviennent son application à grande échelle. Tout d'abord, puisque la photodiode agit à la fois comme photodétecteur et région de photoconversion, il est impossible de varier le gain de conversion photonique sans redimensionner la photodiode, ce qui pose problème si l'on souhaite optimiser la taille du pixel tout en minimisant le niveau de bruit [9]. Le second désavantage, hérité du pixel passif, est le bruit thermique engendré lors de la remise à zéro [22], [27]. Comme nous le verrons lors de l'étude du bruit, ce bruit thermique de remise à zéro ne peut pas être éliminé par les techniques conventionnelles d'échantillonnage différentiel.

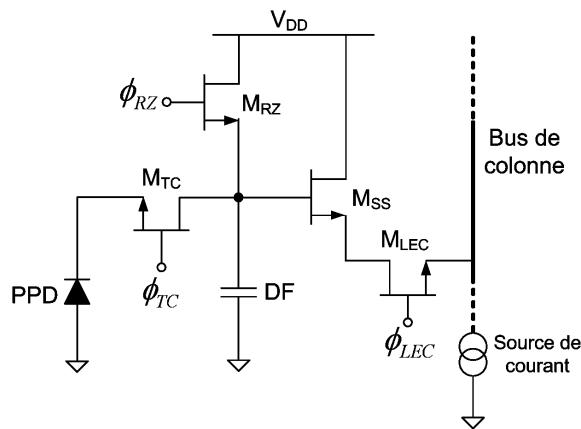

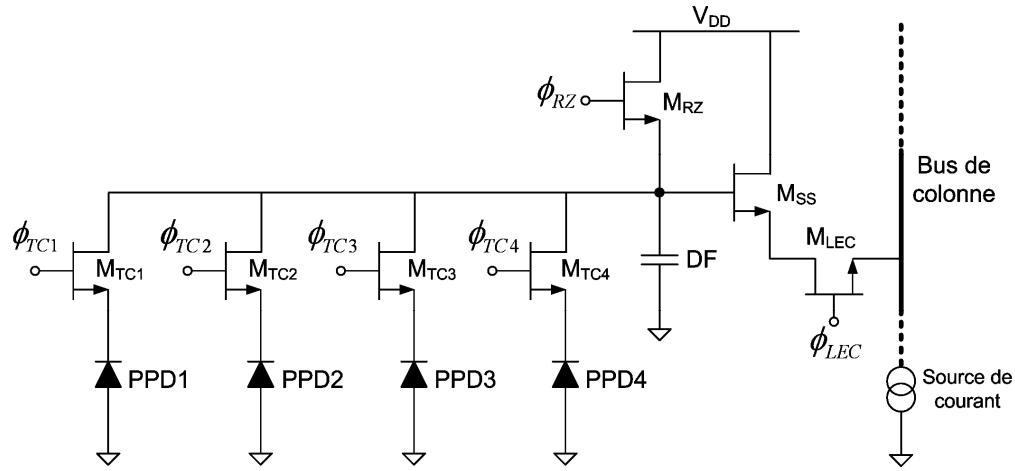

Figure 1.9 Pixel actif à quatre transistors (4T-APS)

La possibilité d'éliminer le bruit thermique de remise à zéro à l'aide d'un échantillonnage différentiel (p. ex. double échantillonnage corrélé) a motivé la naissance

d'une seconde structure de pixel actif, illustrée à la Figure 1.9. Son principe fondamental de fonctionnement consiste à isoler la photodiode lors des opérations de remise à zéro et de lecture en ajoutant un transistor de transfert de charges,  $M_{TC}$ , et une diffusion flottante,  $DF$ . On obtient ainsi un pixel actif à quatre transistors (4T-APS) [9], [22], [27], [36].

Notons que les transistors  $M_{RZ}$ ,  $M_{LEC}$  et  $M_{SS}$  réalisent des fonctions identiques à celles discutées pour le pixel actif à trois transistors, tandis que le transistor de transfert de charges,  $M_{TC}$ , permet d'isoler la photodiode de la diffusion flottante. Il en résulte que le pixel 4T-APS offre la possibilité de mémoriser la tension de remise à zéro à l'intérieur du pixel, en vue d'effectuer un échantillonnage différentiel.

Le cycle de lecture débute par l'activation des transistors  $M_{TC}$  et  $M_{RZ}$ , ce qui entraîne la remise à zéro de la photodiode et de la diffusion flottante. Par la suite, le transistor  $M_{TC}$  se désactive pour isoler la photodiode du reste du circuit et laisser place à l'intégration qui s'effectue durant un temps donné. Peu avant la fin de l'intégration, le transistor  $M_{RZ}$  se désactive et la diffusion flottante,  $DF$ , se prépare à recevoir les charges en provenance de la photodiode. C'est alors que les transistors  $M_{TC}$  et  $M_{LECT}$  s'activent simultanément pour transférer les charges vers la diffusion flottante et ainsi effectuer la lecture du pixel à l'instant de l'architecture à trois transistors.

Puisque la photodiode doit être débitée de la totalité de ses charges lors de la lecture, on a recours à une photodiode de type PPD (*pinned photodiode*), issue de l'ajout d'une couche de semi-conducteur  $P^+$  en surface [22]. Celle-ci possède deux avantages principaux par rapport à la photodiode conventionnelle de type PN, soient une meilleure sensibilité (surtout pour les courtes longueurs d'ondes) et un bruit thermique réduit [9], [27]. En revanche, sa zone de charge d'espace est plus longue que celle d'une photodiode traditionnelle, ce qui diminue sa capacité d'accumulation des charges et son efficacité quantique [36].

L'excellente performance du pixel 4T-APS a contribué à l'essor des capteurs d'images CMOS, au point où il s'agit actuellement de l'architecture de pixel la plus répandue [27]. Celle-ci comporte toutefois des inconvénients non-négligeables. En premier lieu, on note que la photodiode PPD requiert une technologie de fabrication CMOS particulière et dispendieuse, en comparaison avec la photodiode PN qui peut être réalisée à partir d'un procédé standard [21], [22]. Ensuite, un transfert de charge incomplet entre la photodiode et la diffusion flottante peut entraîner un décalage dans l'image [21], [22].

### **1.3.3 Pixels numériques (DPS)**

Comme l'indique la Figure 1.6, l'ajout d'un convertisseur analogique à numérique à la structure d'un pixel actif résulte en un pixel numérique [9], [12], [13], [21], [22], [29], [36]. Les avantages résultant de l'inclusion du convertisseur analogique à numérique à l'intérieur du pixel sont nombreux. Tout d'abord, puisque le parcours analogique du signal est confiné à l'intérieur du pixel, la détérioration causée par le bruit et les effets de charge sont minimisés [9], [13], [29], [36]. D'autre part, la vitesse des circuits analogiques est indépendante de la quantité totale de pixels, ce qui favorise les matrices ayant un grand nombre de pixels [29] et permet un processus de lecture très rapide [9], [21], [36]. Ensuite, en raison du fait que les convertisseurs analogiques à numériques traitent le signal en provenance d'un seul pixel, les contraintes associées à leur design sont amoindries [13], [29], [36] et la consommation de puissance globale du capteur est réduite [36]. Enfin, l'intégration du traitement numérique à même le pixel permet un ajustement flexible des paramètres d'exposition de l'image [29].

Toutefois, tel que mentionné à la sous-section 1.2.2, cette architecture possède plusieurs limitations en raison du nombre élevé de transistors que requiert son implémentation, ce qui résulte en des pixels de grande taille [9], [21], [22], [36]. Pour cette raison, les pixels numériques sont, encore à ce jour, réservés à des applications spécifiques qui privilégient la rapidité et la flexibilité de lecture plutôt qu'une qualité d'image exceptionnelle [21].

### 1.3.4 Facteur de remplissage

Afin de maximiser la quantité de lumière absorbée et réduire la distance entre les éléments photosensibles, le photodétecteur doit idéalement occuper la majorité de la surface du pixel. Cette observation est particulièrement pertinente en ce qui concerne les capteurs optimisés pour une grande qualité d'image, tels ceux utilisés dans les applications DSC [21], [22]. Il est donc utile de définir le facteur de remplissage d'un pixel comme étant le rapport de la surface occupée par le photodétecteur sur la surface totale du pixel [22], [36].

En raison du fait qu'ils ne comportent qu'un seul transistor, les pixels passifs ont un très grand facteur de remplissage [9], [22], [27], alors que le facteur de remplissage des pixels actifs varie de 50% à 70% [36]. Notons que les pixels actifs 4T ont un facteur de remplissage inférieur à celui des pixels 3T en raison de l'ajout de la diffusion flottante et de la grille de transfert [22], [27]. Néanmoins, puisque les photodiodes PPD qui composent la structure 4T sont isolées de leurs diffusions flottantes par leurs grilles de transfert, il est possible de faire en sorte que plusieurs photodiodes PPD partagent la même diffusion flottante, ce qui augmente le facteur de remplissage [9], [21], [22], [27]. La Figure 1.10 illustre le partage d'une diffusion flottante par un groupe de quatre photodiodes PPD. Puisque l'on retrouve sept transistors pour chaque groupe de quatre pixels de la matrice, on nomme cette structure 1.75T-APS. Le principal désavantage du partage de pixels résulte du fait qu'un seul pixel parmi le groupe incorpore les transistors  $M_{RZ}$ ,  $M_{SS}$  et  $M_{LEC}$ , ce qui engendre une asymétrie dans la disposition physique des pixels. Cette asymétrie cause une augmentation du bruit à patron fixe (cf. section 1.4.3) [27] et une attention particulière doit être portée lors du dessin des masques de manière à répartir les transistors le plus également possible [21].

Figure 1.10 Partage des pixels en regroupements de quatre (1.75T-APS)

Un autre inconvénient de cette technique est la complexité accrue du processus de lecture, car il faut tenir compte du partage dans le mécanisme de remise à zéro, d'intégration et de transfert des données au bus de colonne. Finalement, notons que les pixels numériques possèdent les plus faibles taux de remplissage en raison des transistors additionnels requis pour la conversion analogique à numérique [9], [21].

## 1.4 Indicateurs de performance

La fidélité de l'image captée par rapport à la scène originale est un pré-requis important dans la majorité des applications. Par conséquent, il existe plusieurs indicateurs de performance qui qualifient et quantifient les performances d'un capteur d'images CMOS. Les sous-sections suivantes visent à introduire les principaux indicateurs de performance qui sont reliés, de près ou de loin, aux circuits électroniques qui composent le capteur d'images.

### 1.4.1 Résolution et résolution spatiale

La résolution d'un capteur d'images est définie comme étant le nombre de pixels qui composent la matrice. Assumant une dimension fixe pour la matrice, la technique la plus populaire pour augmenter la résolution consiste à réduire la surface occupée par un pixel

en optimisant les dessins de masque. Pour ce faire, on peut diminuer le nombre de transistors compris dans un pixel actif, on encore réduire la taille des transistors utilisés. Pour sa part, la résolution spatiale d'un capteur d'images détermine le plus petit détail d'une image optique que le capteur est en mesure de discerner [9]. Bien que la résolution spatiale augmente en fonction du nombre de pixels compris dans la matrice, elle dépend également de la géométrie des pixels, ainsi que de la méthode de détection et d'extrapolation des couleurs. Les systèmes optiques et les lentilles utilisés en amont du capteur ont également une influence sur la résolution spatiale et leur contribution ne doit pas être négligée.

#### **1.4.2 Courant de noirceur**

Le courant de noirceur est le courant de sortie du photodétecteur en l'absence totale de lumière [9]. Les conséquences d'un courant de noirceur élevé sont, entre autres, l'impossibilité d'obtenir un niveau de noir satisfaisant et une réduction de la plage d'illumination que le capteur est en mesure de détecter. En outre, la variation des courants de noirceur des pixels entraîne une réduction de l'uniformité de l'image en situation de faible illumination. Cette non-uniformité ne peut pas être rectifiée par un mécanisme externe de correction [21]. Il est donc important de minimiser le courant de noirceur lors de la conception du pixel, tel qu'exemplifié par [31], où le transistor suiveur d'un pixel actif est enfoui dans le substrat. Enfin, en raison de l'isolation des défauts de surface procurée par la couche supplémentaire P<sup>+</sup>, les photodiodes PPD possèdent un courant de noirceur plus faible que les photodiodes traditionnelles [21]. [27], [36].

#### **1.4.3 Bruit**

La différence de fidélité entre les pellicules photosensibles traditionnelles et les capteurs d'images CMOS s'explique en grande partie par les différents types de bruits électroniques qui affligent ces derniers. Les sous-sections suivantes font état des deux catégories de bruit présentes dans un capteur d'images CMOS, soient le bruit spatial et

le bruit temporel [21], [27], ainsi que d'un survol des principaux mécanismes de suppression du bruit.

#### *1.4.3.1 Bruit spatial*

Le bruit spatial est invariable par rapport au temps et ses effets sont identiques d'une image à l'autre. Sa composante principale est le bruit à patron fixe (FPN, *Fixed Pattern Noise*) qui est généralement causé par les variations entre les différents circuits de traitement du signal. À ce titre, la variabilité entre les circuits de colonne, qu'ils soient analogiques ou numériques, est l'une des plus importantes sources de bruit à patron fixe et elle est considérablement nuisible puisqu'elle cause des stries verticales dans l'image [9]. Une portion du bruit à patron fixe est également attribuable aux différences inévitables entre les transistors qui composent les pixels actifs d'une matrice [21], [36]. Plus spécifiquement, on note que les variations des tensions de seuil des transistors suiveurs peuvent atteindre plusieurs dizaines de millivolts et sont à l'origine de la plupart du bruit à patron fixe en provenance des pixels [21]. Par ailleurs, les inégalités des parcours empruntés par les signaux analogiques causent également un bruit à patron fixe [9]. Pour leur part, les capteurs utilisant des pixels numériques présentent un bruit à patron fixe réduit, car les effets des variations analogiques sont confinés à l'intérieur des pixels [9]. Enfin, soulignons que l'on retrouve également un bruit à patron fixe dû aux différences entre les courants de noirceur des pixels [27].

#### *1.4.3.2 Bruit temporel*

Comme son nom l'indique, le bruit temporel est sujet à des fluctuations en fonction du temps. Il sévit de manière indépendante pour chaque pixel et il varie lors de l'acquisition de chaque image. De ce fait, il s'agit de la non-linéarité la plus fondamentale d'un capteur d'images [9]. Le bruit temporel peut être segmenté en quatre types de bruits ayant des origines différentes. Par ordre d'importance, on retrouve le bruit de grenaille entraîné par la variation statistique du nombre de photons excités durant le processus d'intégration [9], [27], le bruit thermique occasionné par la résistance équivalente du

transistor de remise à zéro d'un pixel [21], [22], les bruits thermique et de scintillation (1/f) dus aux différents circuits de lecture et, finalement, le bruit de quantification des convertisseurs analogique à numérique [9]. Dans le cas d'un pixel actif à trois transistors, il a été observé que les principales sources de bruit thermique sont le bruit de remise à zéro et le bruit de grenaille du photodétecteur [28]. Enfin, il est pertinent de mentionner que le bruit temporel affecte la qualité d'image de façon similaire au bruit spatial, car ils sont tous deux figés lors de la sauvegarde de l'image [21].

#### *1.4.3.3 Mécanismes de suppression du bruit*

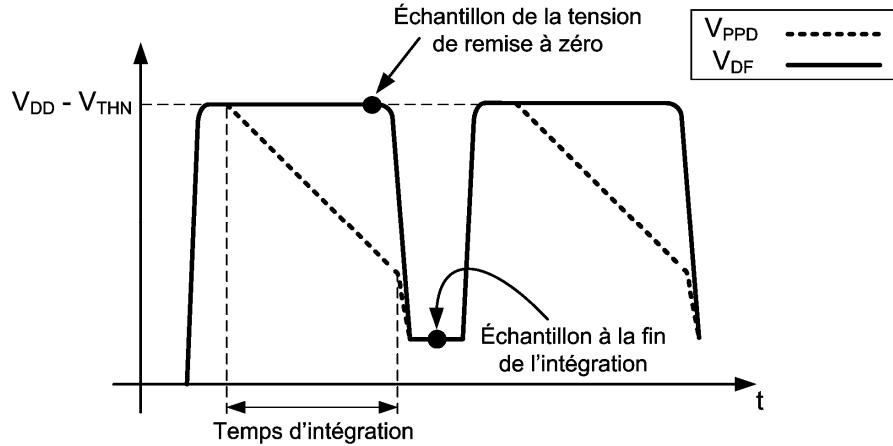

La technique de suppression du bruit la plus répandue dans les capteurs d'images est l'échantillonnage différentiel. Cette méthode consiste à comparer deux échantillons de la tension de sortie du pixel, le premier correspondant à la tension de remise à zéro et le second étant la tension de sortie après l'intégration. S'il y a corrélation entre les bruits contenus dans les deux échantillons, le signal résultant de leur différence sera exempt de bruit. Dans le cas d'une architecture de pixel actif à quatre transistors, l'échantillonnage différentiel compare la tension de remise à zéro, mémorisée dans la diffusion flottante, avec la tension aux bornes de la diffusion flottante après le transfert des charges en provenance de la photodiode. Ces deux échantillons contiennent à la fois le bruit thermique de remise à zéro, les variations des tensions de seuil des transistors et les fluctuations dues à la géométrie des photodétecteurs. Puisque ces bruits sont totalement corrélés, la différence entre les échantillons annule le bruit et procure le signal désiré [27], [36]. Dans ce cas précis, l'échantillonnage différentiel est nommé double échantillonnage corrélé (CDS, *Correlated Double Sampling*) [9], [21], [22], [27], [36]. Notons que si la fréquence d'échantillonnage est élevée, le bruit de scintillation (1/f) contenu dans deux échantillons successifs est fortement corrélé, donc considérablement réduit par le mécanisme CDS [9]. La Figure 1.11 illustre les tensions aux bornes de la photodiode PPD,  $V_{PPD}$ , et de la diffusion flottante,  $V_{DF}$ , ainsi que les échantillons requis par la technique CDS. Notons que la tension échantillonnée suite à l'intégration est inférieure à celle obtenue aux bornes de la photodiode au même instant en raison du

transfert de charges vers la diffusion flottante qui survient lorsque le transistor de transfert de charges,  $M_{TC}$ , est activé.

Figure 1.11 Double échantillonnage corrélé (CDS)

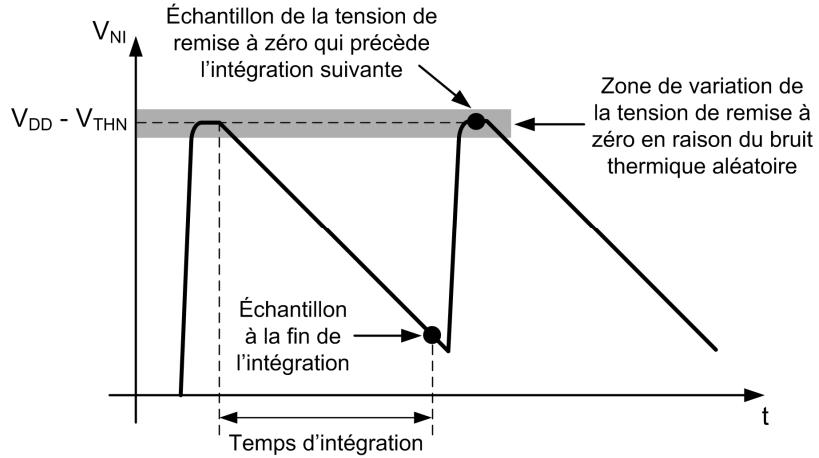

Lorsqu'on emploie une architecture à trois transistors (3T), le nœud de lecture n'est pas isolé par un transistor de transfert de charges, il n'y a donc pas d'élément de mémoire interne au pixel permettant de conserver la valeur de la tension de remise à zéro qui précède l'intégration [9], [22]. On doit alors avoir recours à un échantillonnage différentiel de type remise à zéro (DRS, *Delta Reset Sampling*) [9]. Cette méthode consiste à comparer la lecture obtenue à la fin d'un cycle d'intégration avec la lecture de la tension de remise à zéro du cycle suivant. La Figure 1.12 montre les instants auxquels la tension du nœud d'intégration,  $V_{NI}$ , est échantillonnée en supposant une illumination constante. Puisque les cycles d'intégration utilisés pour la comparaison sont différents, le bruit temporel (plus particulièrement le bruit thermique de remise à zéro) entre les deux lectures n'est pas corrélé. Il s'ensuit que l'échantillonnage DRS n'est pas aussi performant que le double échantillonnage corrélé. En fait, l'échantillonnage DRS double la puissance du bruit de remise à zéro [9]. Par contre, il élimine efficacement les composantes du bruit spatial.

Figure 1.12 Échantillonnage différentiel de type remise à zéro (DRS)

Ces deux mécanismes de comparaison requièrent au minimum deux échantillonneurs bloqueurs et un amplificateur différentiel [22] et sont habituellement implémentés dans les circuits de colonne [21], [36]. Par conséquent, le bruit à patron fixe causé par les circuits de colonne n'est pas supprimé par ce procédé [36]. Pour remédier à cet inconvénient, on peut avoir recours à une utilisation aléatoire des circuits de colonne visant à répartir les variabilités [25]. D'autre part, notons que certains capteurs destinés à des applications spécialisées ne peuvent utiliser un mécanisme de comparaison séquentiel et externe aux pixels. Le cas échéant, on peut effectuer le double échantillonnage corrélé à l'intérieur même du pixel [18], ou encore réduire le bruit à patron fixe du pixel en utilisant une grille flottante incorporée au pixel [34].

#### 1.4.4 Gamme dynamique

La gamme dynamique d'un capteur quantifie son habileté à acquérir des scènes ayant une grande plage de luminosités [9]. Plus précisément, on peut définir la gamme dynamique comme étant le rapport entre le niveau maximal de signal en sortie sur le seuil de bruit déterminé par le courant de noirceur [9], [22], [36]. Cette caractéristique revêt une grande importance puisque certaines scènes naturelles exhibent des écarts dynamiques de contraste excédant 100dB [9] et que la gamme dynamique de l'oeil humain est supérieure à 90dB [9], [36]. La pellicule photosensible parvient à atteindre

une gamme dynamique d'environ 80dB [36], tandis que celle des capteurs CMOS actuels s'étend de 40dB à 60dB [9].

Il existe deux astuces fondamentales pour améliorer la gamme dynamique, soit réduire le courant de noirceur, ou encore augmenter le niveau de saturation du signal en optimisant les circuits électroniques ou en haussant la tension d'alimentation [36]. En outre, la gamme dynamique est indirectement influencée par le bruit temporel et le bruit à patron fixe, qui influencent la plage d'illumination pouvant être détectée [9]. Il est à noter qu'il est impossible d'accroître la gamme dynamique en augmentant le temps d'intégration, car le courant de noirceur est intégré au même titre que le signal lumineux [9]. De plus, bien que l'utilisation d'une technologie CMOS plus petite augmente le facteur de remplissage, les tensions d'alimentation plus faibles réduisent la gamme dynamique [36]. Cette difficulté a été contournée par [19] en utilisant deux types de photodéTECTEURS (une photogrille et une photodiode) et un procédé de remise à zéro innovateur, ce qui permet une gamme dynamique de 86dB avec une tension d'alimentation inférieure à 1V.

Les besoins sans cesse croissants en termes de performance ont mené à l'élaboration de plusieurs techniques avancées d'optimisation de la gamme dynamique. L'utilisation de capacités de débordement permet d'atteindre une gamme dynamique de 100dB [14], alors qu'en [26], une technique consistant à évaluer le temps d'intégration requis pour atteindre la saturation résulte en une gamme dynamique de 120dB. Une autre astuce, démontrée dans [16], réside en l'implémentation d'une compression dynamique interne au capteur utilisant une boucle de rétroaction négative pour moduler la capacité d'intégration la photodiode en variant la tension à ses bornes. Il est également possible d'effectuer une conversion lumière-fréquence intégrée au pixel pour obtenir une gamme dynamique expérimentale de 130dB [32]. L'application d'une méthode similaire par les auteurs de [8] génère une gamme dynamique simulée de 150dB. L'application de cette méthode de conversion se fait toutefois au détriment du facteur de remplissage, principalement en raison de l'ajout de plusieurs transistors à l'architecture du pixel.

## 1.5 Procédés de discrimination des couleurs

Les photodétecteurs traditionnels sont sensibles à une pluralité de longueurs d'ondes comprises dans le spectre visible. Par conséquent, il est impossible de détecter les couleurs en l'absence d'un mécanisme externe [7], [21], [29]. Les sous-sections suivantes décrivent les quatre principaux procédés de discrimination des couleurs.

### 1.5.1 Méthode par expositions successives

Comme son nom l'indique, la méthode par expositions successives consiste à illuminer la scène plusieurs fois à l'aide de sources lumineuses de différentes couleurs, tout en faisant l'acquisition d'une image à chaque exposition. La combinaison subséquente des images acquises durant ce processus permet d'obtenir une reproduction couleur de la scène [22], [29]. Cette méthode doit toutefois être employée avec une scène statique dans un environnement contrôlé [29] et son utilisation est habituellement réservée à certaines applications médicales [22].

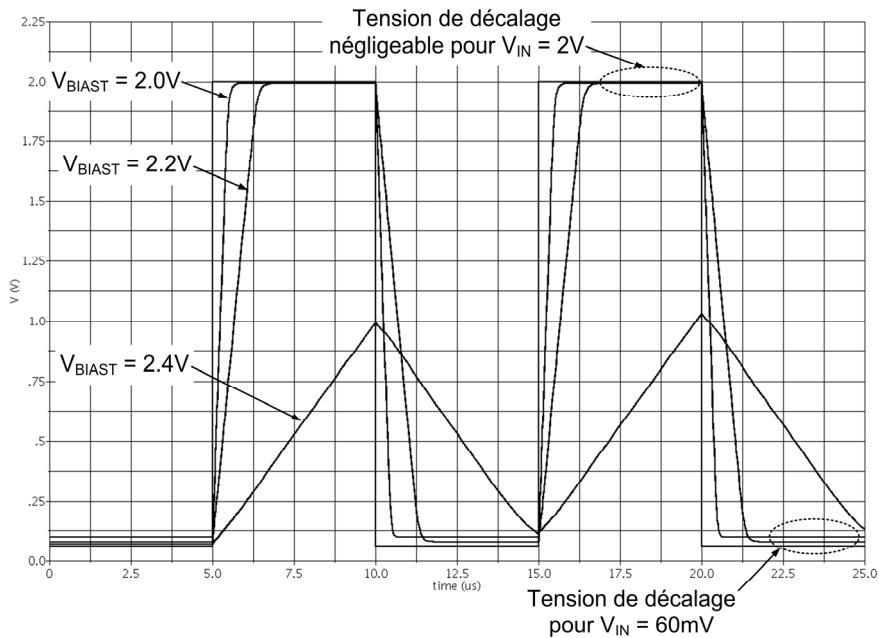

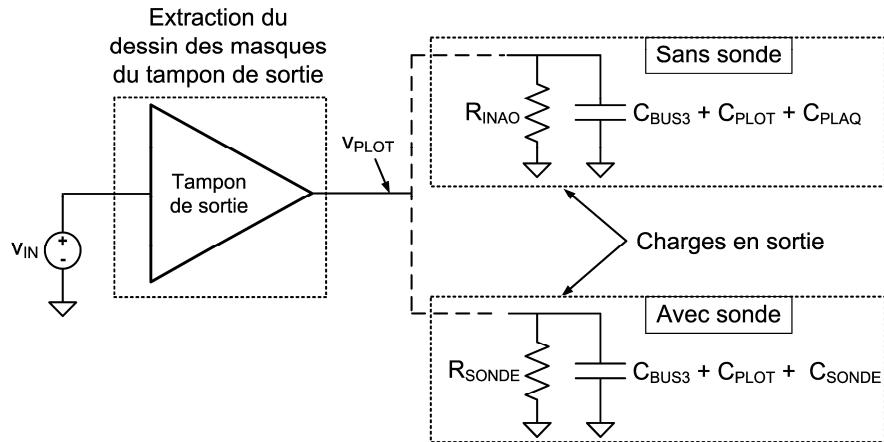

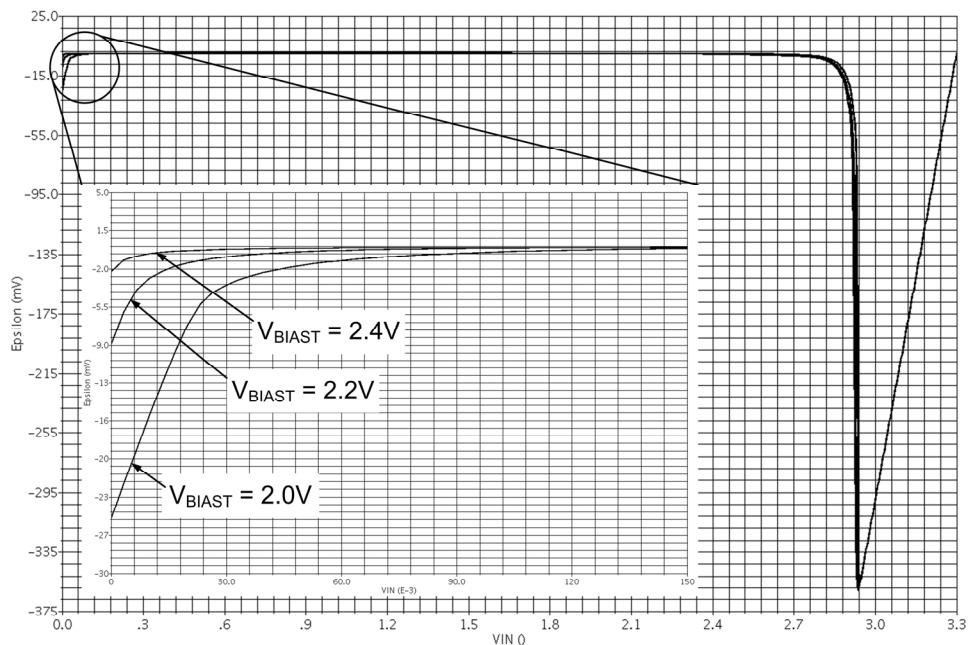

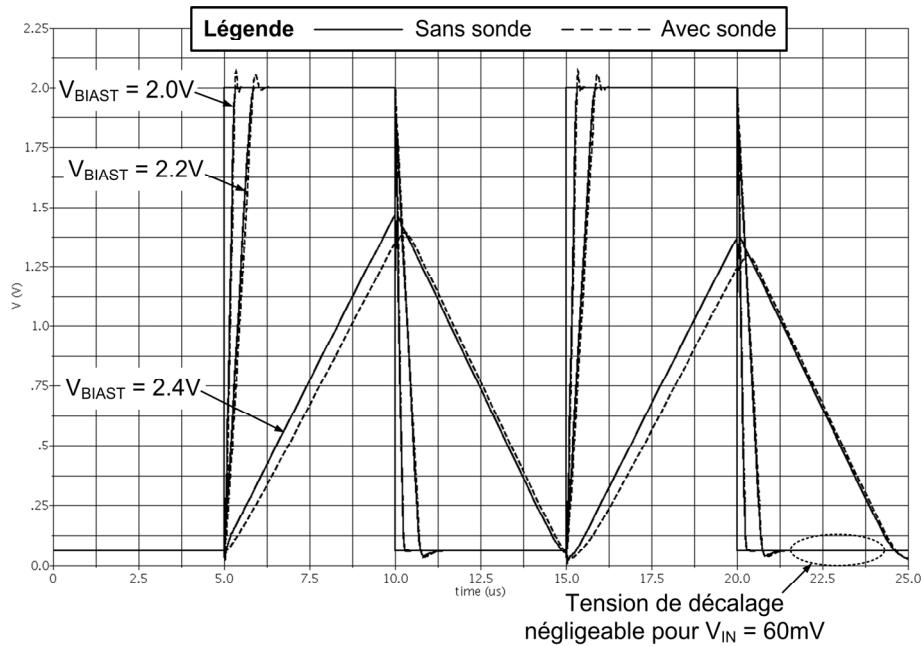

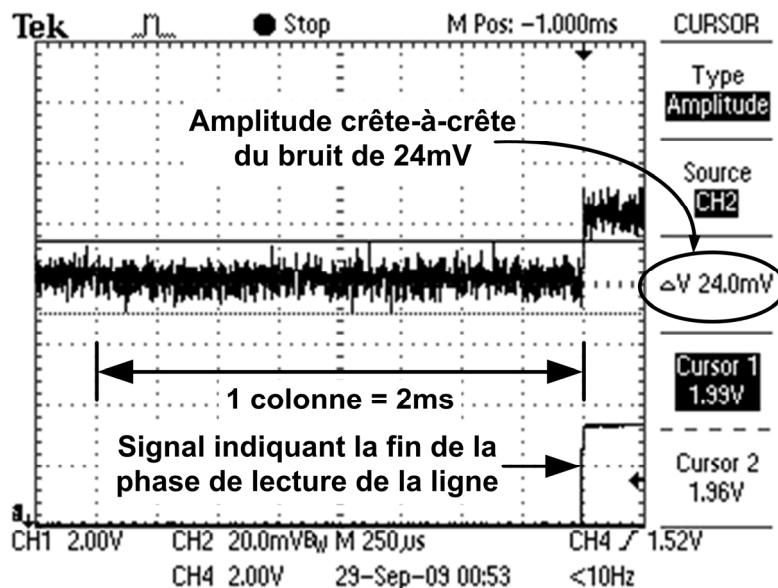

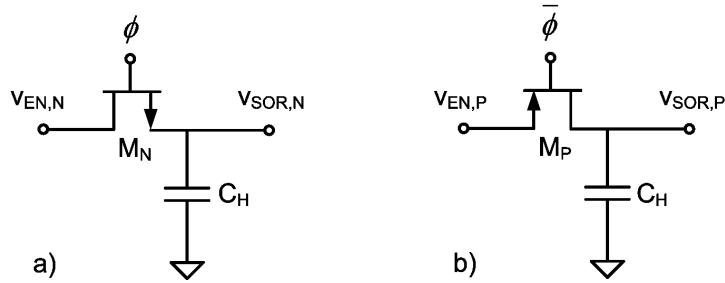

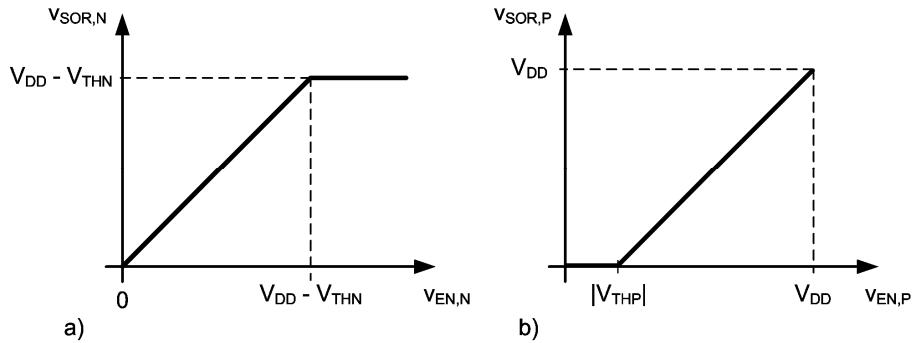

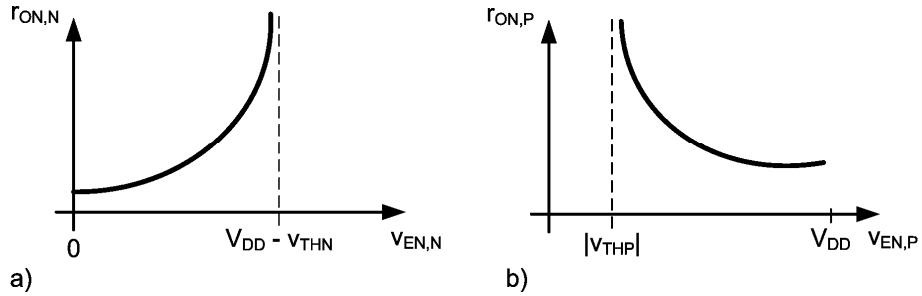

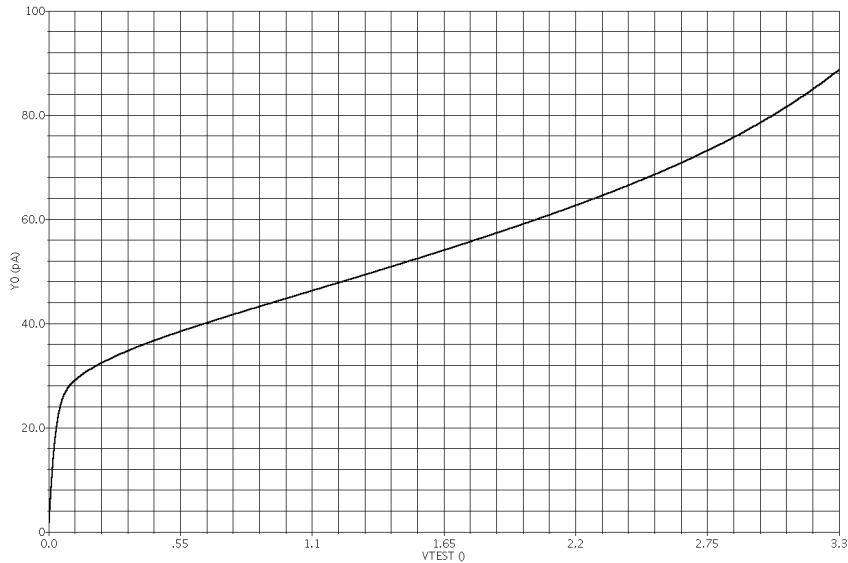

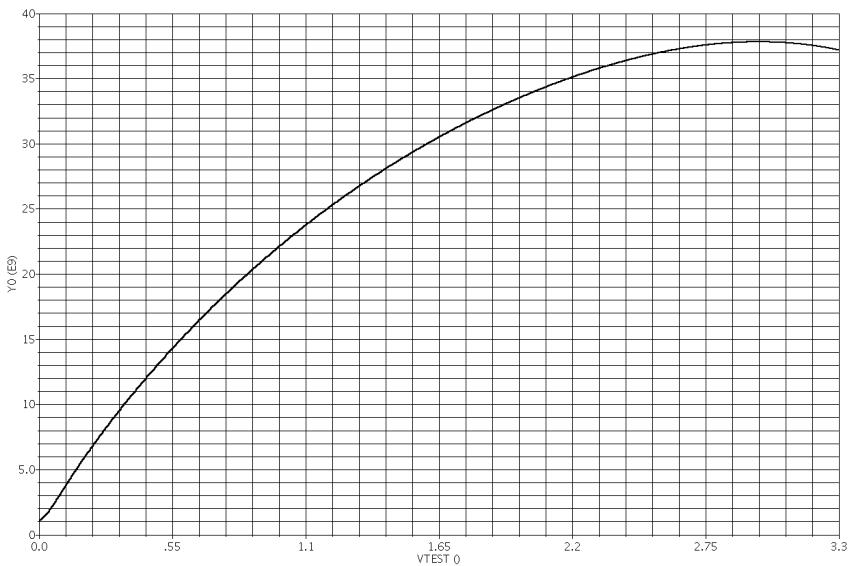

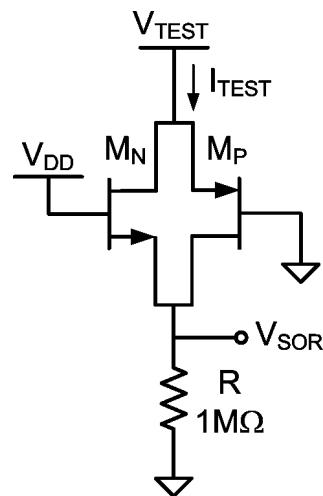

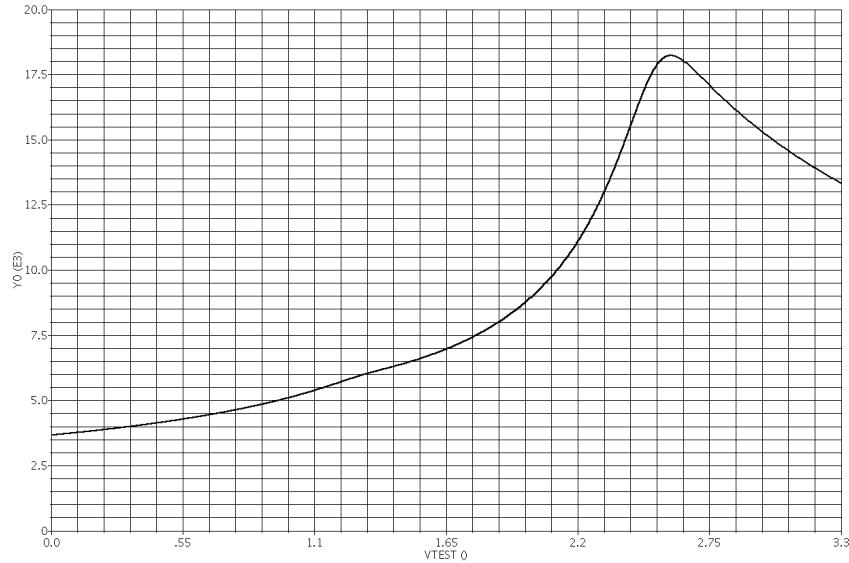

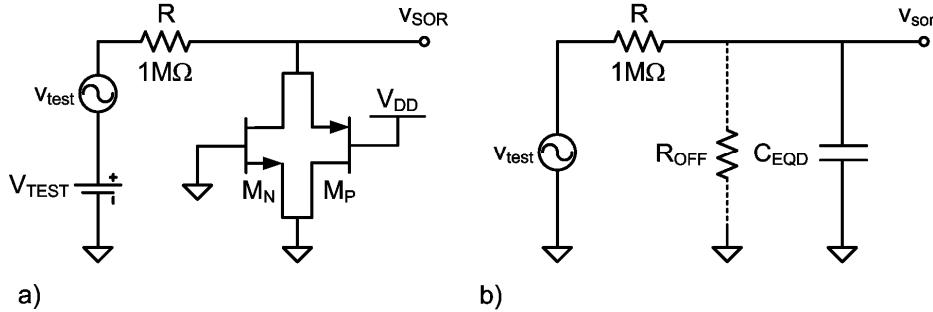

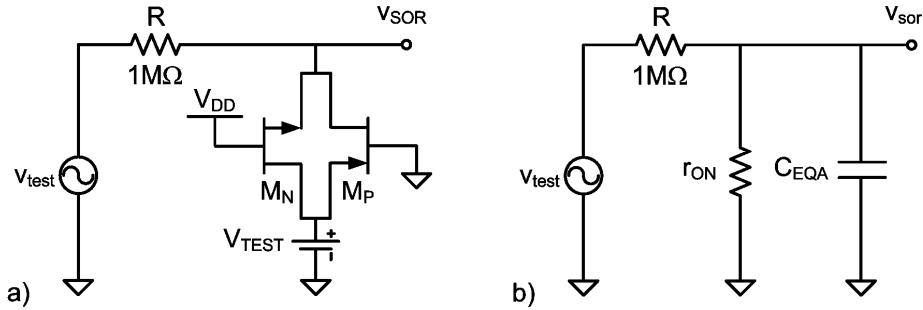

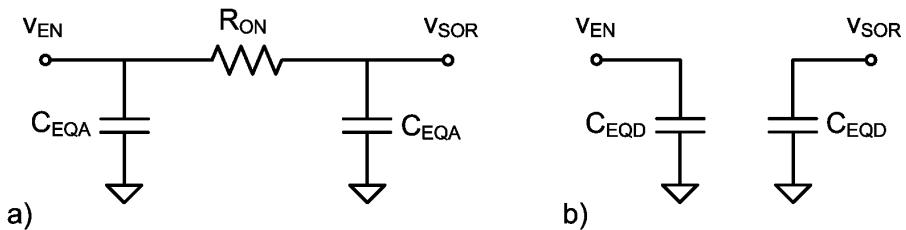

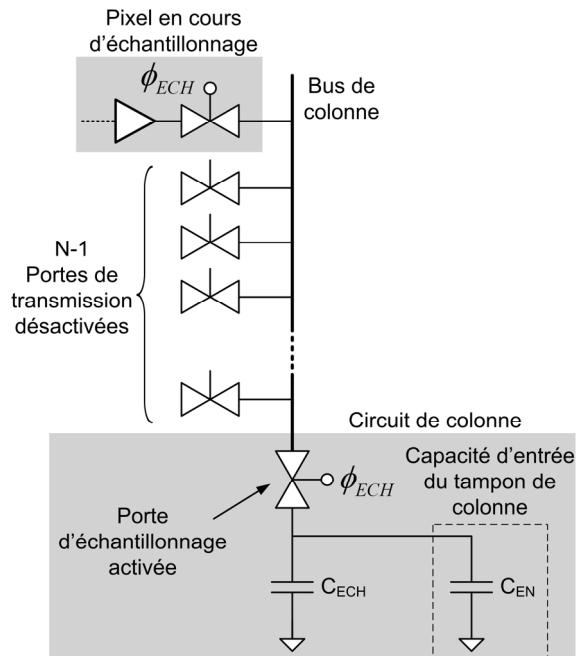

### 1.5.2 Séparation des couleurs