**Titre:** Algorithmes de diagnostic d'une chaîne JTAG reconfigurable et tolérante aux pannes au sein de la technologie WaferIC

Title: tolerant aux pannes au sein de la technologie WaferIC

**Auteur:** Safa Berrima

Author:

**Date:** 2014

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Berrima, S. (2014). Algorithmes de diagnostic d'une chaîne JTAG reconfigurable et tolérante aux pannes au sein de la technologie WaferIC [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/1636/>

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/1636/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Yves Blaquier

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

ALGORITHMES DE DIAGNOSTIC D'UNE CHAÎNE JTAG RECONFIGURABLE ET

TOLÉRANTE AUX PANNES AU SEIN DE LA TECHNOLOGIE WAFERIC

SAFA BERRIMA

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2014

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

ALGORITHMES DE DIAGNOSTIC D'UNE CHAÎNE JTAG RECONFIGURABLE ET

TOLÉRANTE AUX PANNES AU SEIN DE LA TECHNOLOGIE WAFERIC

présenté par : BERRIMA Safa

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. DAVID Jean-Pierre, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. BLAQUIÈRE Yves, Ph.D., membre et codirecteur de recherche

M. BOIS Guy, Ph.D., membre

## REMERCIEMENTS

Je tiens à remercier le professeur Yvon Savaria, mon directeur de recherche et directeur du département de génie électrique de l'École Polytechnique de Montréal jusqu'à Juin 2014. Je le remercie pour ses judicieux conseils, l'aide et le temps qu'il a bien voulu m'accorder ainsi qu'avoir cru en moi pour me faire rejoindre son équipe de recherche. Je tiens à remercier également le professeur Yves Blaqui  re, mon co-directeur pour son   coute, son encadrement, sa patience et sa disponibilit   malgr   un emploi du temps charg   autant que directeur des programmes en microélectronique de l'universit   du Qu  bec    Montr  al.

J'ai eu beaucoup de chance d'avoir deux excellents encadrants tout au long de mon projet de maîtrise. Sans messieurs Yves Blaqui  re et Yvon Savaria ce travail n'aurait pas pu voir le jour.

Je remercie tous mes co-  quipiers au laboratoire GRM de l'  cole Polytechnique de Montr  al sp  cialement Gontran Sion et Sylvain Charasse. Gr  ce    leurs efforts, ce travail a pu   tre test   au laboratoire. J'ai b  n  fici   de leurs connaissances techniques et de leur savoir-faire.

Je veux exprimer mes remerciements et ma gratitude aux employ  s du d  partement de g  nie   lectrique qui m'ont apport   l'aide et l'assistance n  cessaires    l'elaboration de ce travail. Je remercie en particulier R  jean Lepage, analyste syst  mes, pour son soutien informatique ainsi que Nathalie L  vesque, agente aux dossiers   tudiants, qui a toujours   t   pr  sente pour r  pondre efficacement    mes questions.

Je tiens finalement    exprimer ma gratitude envers ma famille pour tout l'amour et le soutien qu'ils m'apportent depuis toujours. J'esp  re qu'ils trouveront dans ce travail le fruit de leurs efforts et sacrifices.

## RÉSUMÉ

Dans ce mémoire, des algorithmes de diagnostic d'une chaîne JTAG reconfigurable et tolérante aux pannes dans un circuit intégré à l'échelle de la tranche (*Wafer Scale Integrated Circuit WSI*) sont présentés. Le circuit intégré en question, nommé WaferIC, est au cœur du projet de recherche DreamWafer™ qui implique plusieurs universités canadiennes. Ce projet vise à élaborer une plateforme de prototypage rapide pour les systèmes électroniques. C'est d'une certaine façon l'équivalent d'un circuit imprimé reprogrammable. Les circuits discrets, comme les FPGA et les mémoires par exemple seront déposés sur la surface du WaferIC. Ce dernier est un substrat programmable de la taille d'une tranche de Silicium et configurable qui réalise les interconnexions nécessaires entre les circuits et ce conformément à une spécification des interconnexions fournie par l'ingénieur en conception.

Le WaferIC est composé de milliers de cellules connectées entre elles par des liens intercellulaires formant ainsi un vaste réseau d'interconnexions reconfigurable. Une chaîne de balayage conforme au protocole JTAG est utilisée pour configurer les cellules du WaferIC.

Pour minimiser le temps de configuration, ce présent mémoire propose des algorithmes pour repérer le plus d'éléments (cellules et liens) fonctionnels possible au sein du WaferIC. La chaîne JTAG de configuration passera par ces éléments fonctionnels pour configurer toutes les cellules du WaferIC. Le premier objectif du diagnostic est d'établir un ensemble de chemins qui couvrent toutes les cellules et tous les liens intercellulaires du WaferIC. La taille des flux de bits JTAG qui créent ces chemins doit être minimale. Dans ce contexte, une étude théorique est faite dans ce mémoire pour prouver que la taille d'un flux de bits JTAG nécessaire pour établir un chemin de  $N$  cellules croît en  $O(N^2)$ .

Un algorithme de recherche basé sur le principe de la dichotomie a aussi été implémenté dans le cadre de ce projet de maîtrise. Cet algorithme est appliqué sur les chemins trouvés non fonctionnels pour localiser le plus précisément possible les liens défectueux dans ces chemins. L'état des cellules sera déduit à partir des liens. En effet, une cellule est défectueuse si tous ses liens entrants ou sortants sont défectueux. Des algorithmes heuristiques ont également été implémentés pour analyser les chemins non fonctionnels dans le cas où l'algorithme de

dichotomie n'arrive pas à localiser précisément le(s) lien(s) défectueux. Ces algorithmes heuristiques améliorent la résolution du diagnostic et tentent de localiser le plus étroitement possible la ou les défectuosité(s).

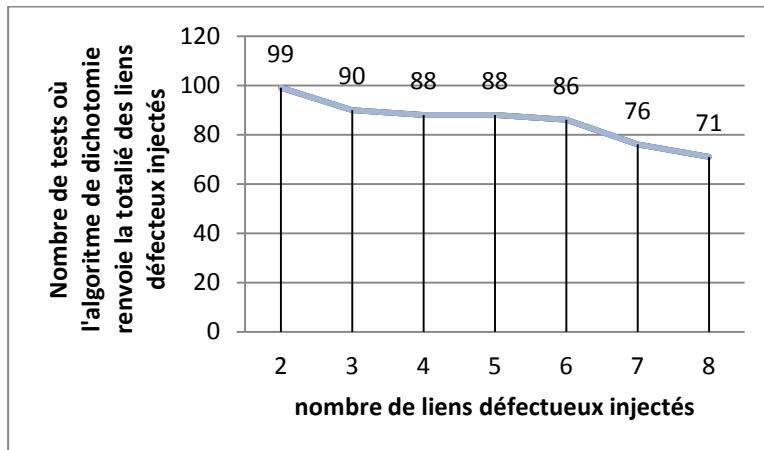

Les algorithmes développés ont été testés sur un prototype miniaturisé du WaferIC. Dans un réticule contenant 1024 cellules, une zone de 4 cellules a été trouvée potentiellement défectueuse, le reste du réticule a été caractérisé comme fonctionnel par les algorithmes de diagnostic. Des résultats de simulation ont également été dressés montrant le comportement des algorithmes en présence d'un ou de plusieurs liens défectueux. L'algorithme de dichotomie développé localise un seul lien défectueux dans le réticule avec une probabilité de plus de 99%. Il localise jusqu'à huit liens défectueux simultanés avec une probabilité de 71%.

## ABSTRACT

In this master project, algorithms to diagnose a reconfigurable and defect tolerant JTAG scan chain in a wafer scale integrated circuit are proposed. The integrated circuit, called WaferIC is at the core of the DreamWafer™ research project involving several Canadian universities. This project aims to develop a platform for rapid electronic system prototyping. That platform is analogous to a reconfigurable printed circuit board. Circuits are deposited on the surface of the WaferIC. This device is a configurable and programmable substrate that implements all the necessary interconnections between the circuits in accordance with the user specification.

The WaferIC is made of thousands of cells interconnected with intercellular links forming an extensive and reconfigurable network of interconnections.

A JTAG scan chain is used to configure the cells of the WaferIC. To minimize the configuration time, this master project proposes algorithms to identify functional elements (cells and links). This scan chain uses those functional elements to configure all the cells of the WaferIC. The first objective is to find a set of paths that cover all cells and links of the WaferIC. The length of the JTAG bit streams that create these paths must be reasonably short, and possibly optimal. In light of this, a theoretical study is done that proves that the size of a JTAG bit stream grows as  $O(N^2)$  for a path made of  $N$  cells. A set search dichotomic algorithm was also developed to be applied on defective paths to accurately locate defective links within these paths. The state of cells can be deduced from links. Indeed, if all incoming and outgoing links of a cell are defective, then the cell is defective. Heuristic algorithms have also been developed to analyze non-functional paths in the case where the dichotomic algorithm is unable to locate precisely the defective link(s).

The algorithms developed were tested on a miniaturized prototype of the WaferIC. In a reticle containing 1024 cells, an area of 4 cells has been found as potentially defective. The rest of the reticle has been characterized as functional by the diagnosis algorithms. Simulation results were also been reported showing the behavior of the algorithm in presence of one or several defects. It is shown that the dichotomic algorithm accurately pinpoints a single defect with a

probability of more than 99% and also accurately locates up to 8 defects with a probability of 71%.

## TABLE DES MATIÈRES

|                                                                     |      |

|---------------------------------------------------------------------|------|

| REMERCIEMENTS .....                                                 | III  |

| RÉSUMÉ.....                                                         | IV   |

| ABSTRACT .....                                                      | VI   |

| TABLE DES MATIÈRES .....                                            | VIII |

| LISTE DES TABLEAUX .....                                            | XI   |

| LISTE DES FIGURES .....                                             | XII  |

| LISTE DES SIGLES ET ABRÉVIATIONS .....                              | XVI  |

| LISTE DES ANNEXES .....                                             | XVII |

| INTRODUCTION.....                                                   | 1    |

| CHAPITRE 1. REVUE DE LITTÉRATURE.....                               | 6    |

| 1.1    Introduction .....                                           | 6    |

| 1.2    Les limitations des systèmes sur PCB .....                   | 6    |

| 1.3    Le WaferBoard <sup>TM</sup> .....                            | 9    |

| 1.3.1    WaferIC .....                                              | 10   |

| 1.3.2    WaferNet .....                                             | 11   |

| 1.3.3    PowerBlock .....                                           | 12   |

| 1.3.4    WaferConnect.....                                          | 13   |

| 1.4    Protocole de test avec les chaînes JTAG .....                | 15   |

| 1.4.1    Brève introduction à la norme JTAG .....                   | 15   |

| 1.4.2    Différentes architectures de chaînes JTAG existantes ..... | 16   |

| 1.4.3    Tolérance aux pannes des systèmes JTAG.....                | 18   |

| 1.5    Architecture de la chaîne JTAG adoptée pour le WaferIC ..... | 21   |

|                    |                                                                                                                                                   |           |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1.5.1              | Structure interne d'une cellule unitaire .....                                                                                                    | 21        |

| 1.5.2              | Une chaîne reconfigurable et tolérante aux pannes.....                                                                                            | 23        |

| 1.5.3              | Montage expérimental pour communiquer avec un réticule du WaferIC .....                                                                           | 26        |

| 1.6                | Problématique de ce mémoire .....                                                                                                                 | 28        |

| 1.7                | Contributions de ce mémoire.....                                                                                                                  | 31        |

| 1.8                | Sommaire .....                                                                                                                                    | 32        |

| <b>CHAPITRE 2.</b> | <b>OUTILS NÉCESSAIRES AU DIAGNOSTIC DE LA CHAÎNE DE BALAYAGE.....</b>                                                                             | <b>34</b> |

| 2.1                | Introduction .....                                                                                                                                | 34        |

| 2.2                | Quelques exemples de défectuosités .....                                                                                                          | 35        |

| 2.2.1              | Lien intercellulaire défectueux.....                                                                                                              | 35        |

| 2.2.2              | Défectuosité au niveau de la circuiterie interne de la cellule .....                                                                              | 36        |

| 2.3                | Définition des éléments du réticule .....                                                                                                         | 38        |

| 2.4                | Complexité temporelle de création d'un chemin.....                                                                                                | 40        |

| 2.5                | Complexité temporelle de deux couvertures possibles : Couverture par des chemins rectangulaires et couverture par des chemins en serpentins ..... | 43        |

| 2.6                | Couverture par des chemins rectangulaires (modélisation avec Matlab) .....                                                                        | 47        |

| 2.7                | Sommaire.....                                                                                                                                     | 54        |

| <b>CHAPITRE 3.</b> | <b>MÉTHODE ALGORITHMIQUE POUR LE DIAGNOSTIC DE LA CHAÎNE JTAG.....</b>                                                                            | <b>55</b> |

| 3.1                | Introduction .....                                                                                                                                | 55        |

| 3.2                | Recherche des éléments défectueux en se basant sur la théorie des ensembles .....                                                                 | 55        |

| 3.3                | L'algorithme de diagnostic par dichotomie.....                                                                                                    | 57        |

| 3.4                | Diagnostic par des algorithmes heuristiques .....                                                                                                 | 61        |

| 3.4.1              | Premier algorithme heuristique : HEURISTIC_1 .....                                                                                                | 61        |

|                                                                                                                    |     |

|--------------------------------------------------------------------------------------------------------------------|-----|

| 3.4.2 Deuxième algorithme heuristique : HEURISTIC_2 (cas d'un seul lien défectueux).....                           | 67  |

| 3.5 Routage basé sur l'algorithme de LEE .....                                                                     | 73  |

| 3.6 Sommaire.....                                                                                                  | 76  |

| CHAPITRE 4. RÉSULTATS .....                                                                                        | 78  |

| 4.1 Introduction .....                                                                                             | 78  |

| 4.2 Estimation du nombre de défectuosités dans un réticule par la loi de Poisson et la loi binomiale négative..... | 78  |

| 4.3 Résultats de simulation.....                                                                                   | 81  |

| 4.3.1 Comportement de l'algorithme en présence d'un seul lien défectueux .....                                     | 82  |

| 4.3.2 Comportement de l'algorithme en présence de plusieurs liens défectueux .....                                 | 88  |

| 4.4 Résultats expérimentaux.....                                                                                   | 90  |

| 4.5 Sommaire.....                                                                                                  | 95  |

| CONCLUSION .....                                                                                                   | 96  |

| REFERENCES .....                                                                                                   | 100 |

| ANNEXE A CAS DE FIGURE OU L'ALGORITHME HEURISTIC_1 EST APPELE....                                                  | 103 |

| ANNEXE B CAS DE FIGURE OU L'ALGORITHME DE DICHOTOMIE NE RETROUVE PAS LES DEFECTUOSITES .....                       | 106 |

## LISTE DES TABLEAUX

|                                                                                                                                                                |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Tableau 2.1 Flux de données JTAG nécessaire à la création du chemin donné dans la figure 2-4.b.                                                                | 41    |

| .....                                                                                                                                                          | ..... |

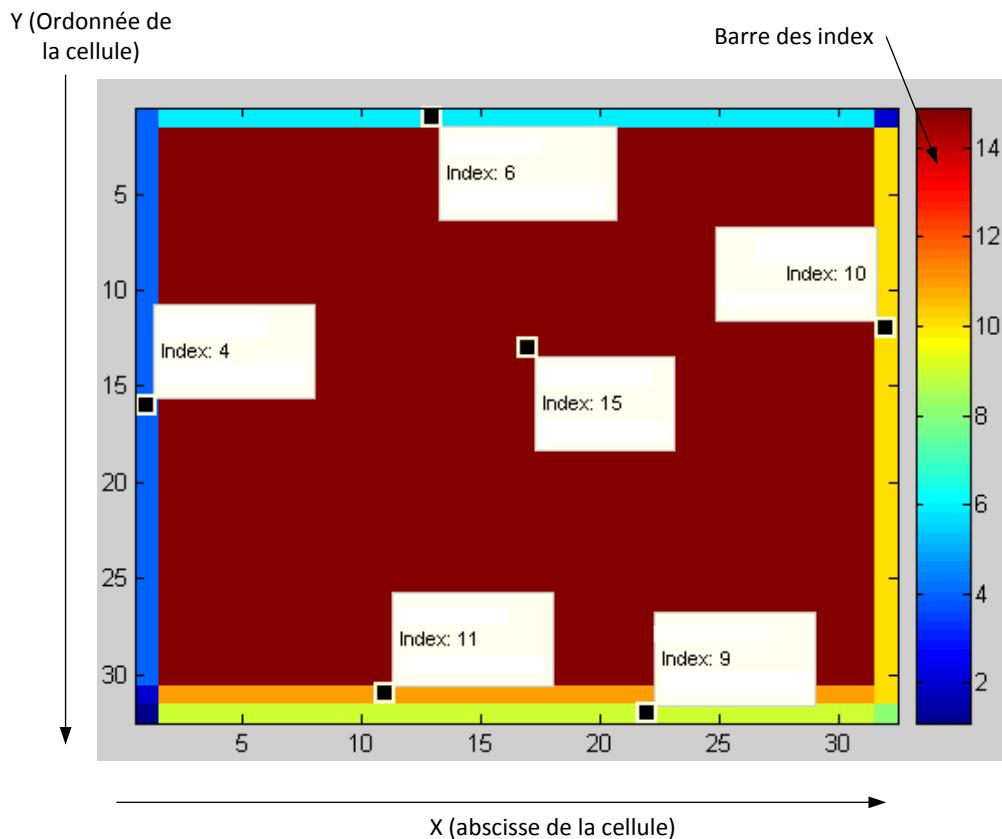

| Tableau 2.2 Signification des index des cellules.....                                                                                                          | 50    |

| Tableau 2.3 Nombre de cellules dans chacun des rectangles verticaux.....                                                                                       | 52    |

| Tableau 2.4 Nombre de bits de configuration de chacun des rectangles verticaux.....                                                                            | 52    |

| Tableau 2.5 Nombre de cellules dans chacun des rectangles horizontaux.....                                                                                     | 53    |

| Tableau 2.6 Nombre de bits de configuration de chacun des rectangles horizontaux. ....                                                                         | 53    |

|                                                                                                                                                                |       |

| Tableau 4.1 Résultats donnés par l'algorithme de dichotomie pour un seul lien défectueux injecté (nombre de liens total dans le réticule est égal à 3843)..... | 82    |

| .....                                                                                                                                                          | ..... |

| Tableau 4.2 Résultats correspondant aux liens de la figure 4-3 (nombre total des liens du réticule est égal à 3843).....                                       | 83    |

| .....                                                                                                                                                          | ..... |

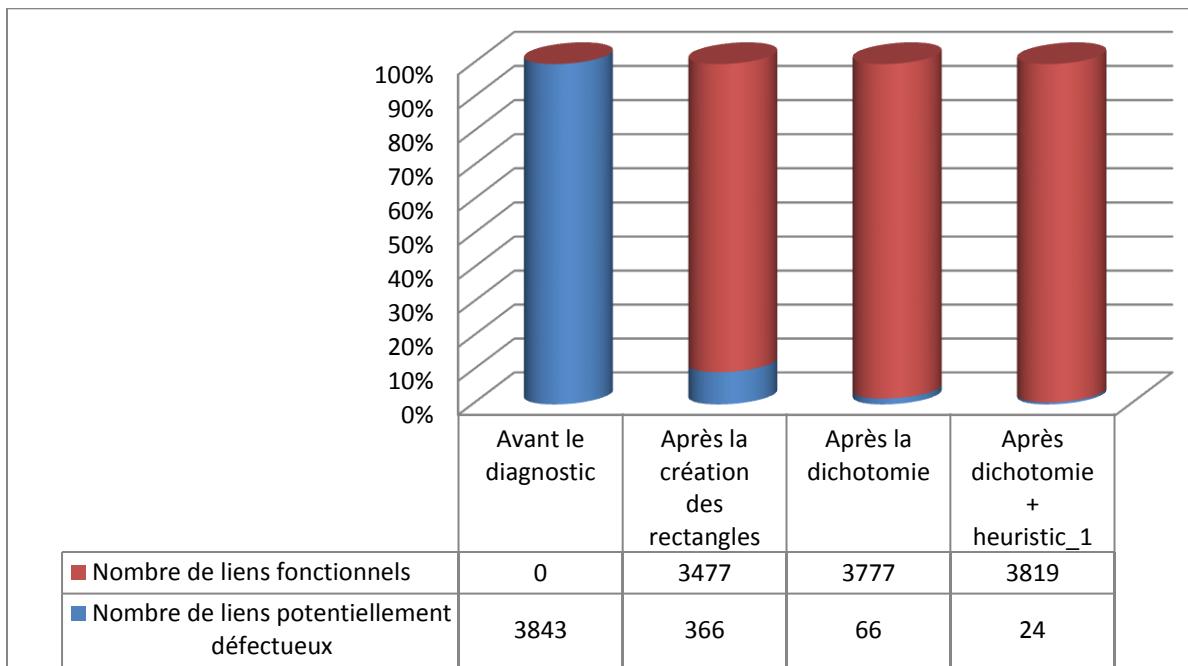

| Tableau 4.3 Évolution du nombre de liens potentiellement défectueux durant le diagnostic du réticule du mini-WaferIC. ....                                     | 94    |

| .....                                                                                                                                                          | ..... |

| Tableau 4.4 Évolution du nombre de liens fonctionnels durant le diagnostic du réticule du mini-WaferIC.....                                                    | 94    |

| .....                                                                                                                                                          | ..... |

## LISTE DES FIGURES

|                                                                                                                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-1: Modèle éclaté du WaferBoard <sup>TM</sup> (figure extraite de [9]). .....                                                                                                                           | 9  |

| Figure 1-2: Zoom au niveau d'un réticule et d'une cellule (figure extraite de [9]). .....                                                                                                                       | 11 |

| Figure 1-3: Interconnexions au sein du WaferNet (figure extraite de [9]). .....                                                                                                                                 | 12 |

| Figure 1-4: Alimentations requises au PowerBlock et au WaferIC. .....                                                                                                                                           | 13 |

| Figure 1-5: Chaîne ILLINOIS.....                                                                                                                                                                                | 18 |

| Figure 1-6 Architecture JTAG en anneau. ....                                                                                                                                                                    | 19 |

| Figure 1-7: Architecture JTAG en étoile.....                                                                                                                                                                    | 20 |

| Figure 1-8: Architecture JTAG Multi Drop. ....                                                                                                                                                                  | 20 |

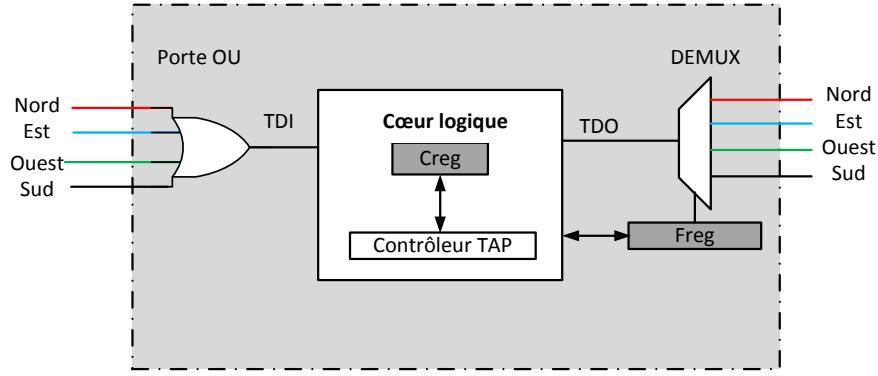

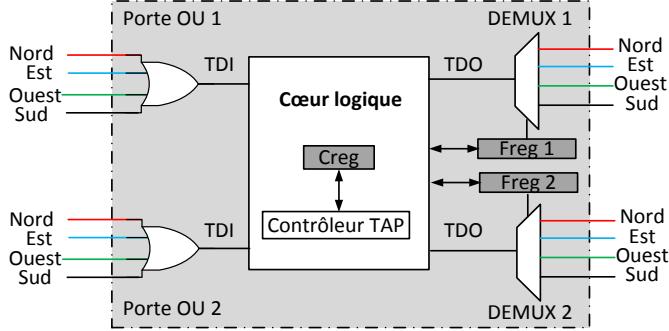

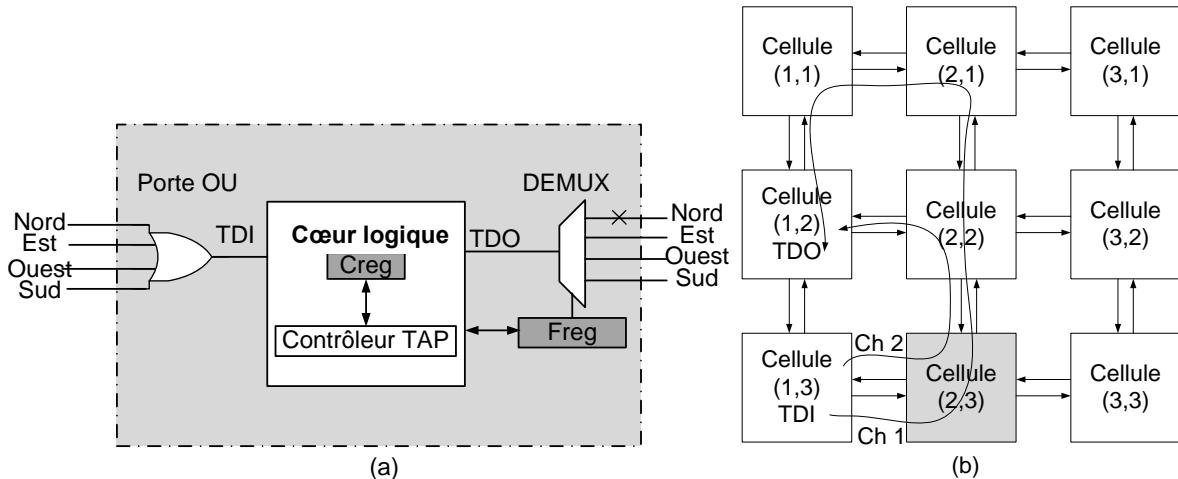

| Figure 1-9: Architecture interne d'une cellule. ....                                                                                                                                                            | 22 |

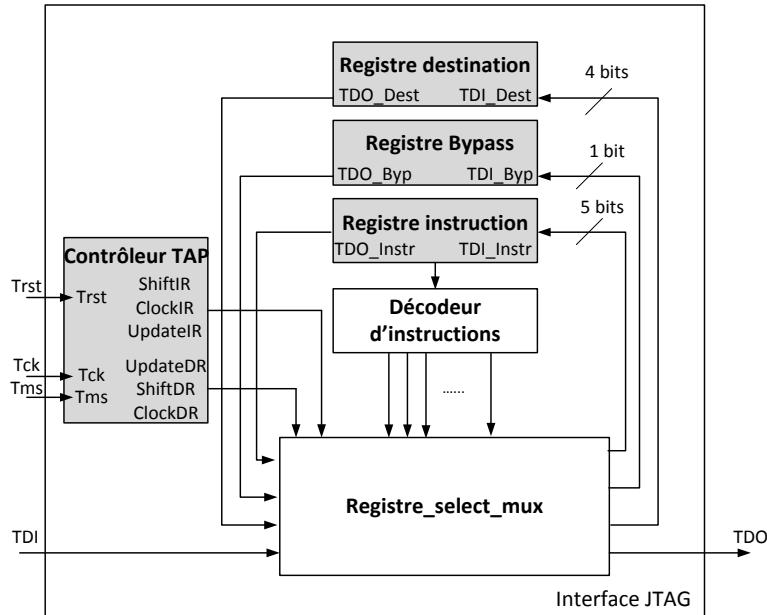

| Figure 1-10: Interface JTAG. ....                                                                                                                                                                               | 22 |

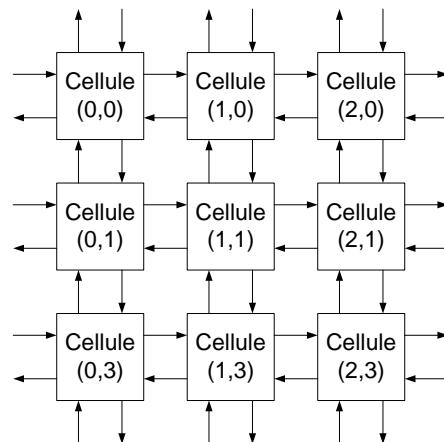

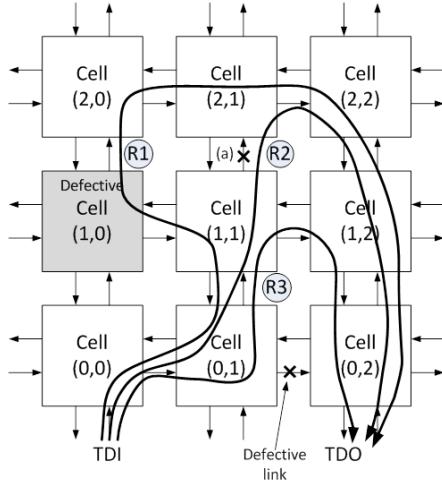

| Figure 1-11: Réseau d'interconnexions simplifié dans une matrice de $3 \times 3$ . ....                                                                                                                         | 23 |

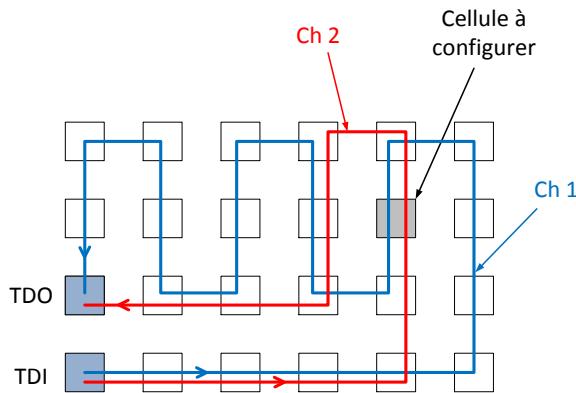

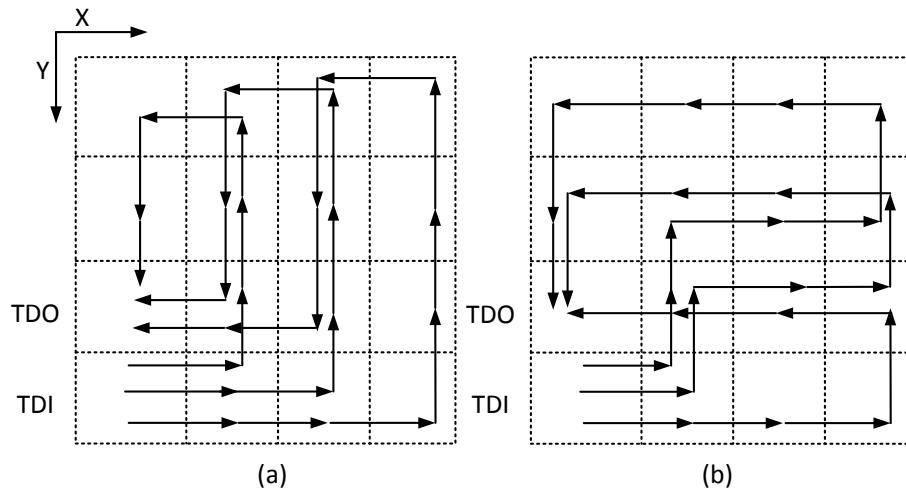

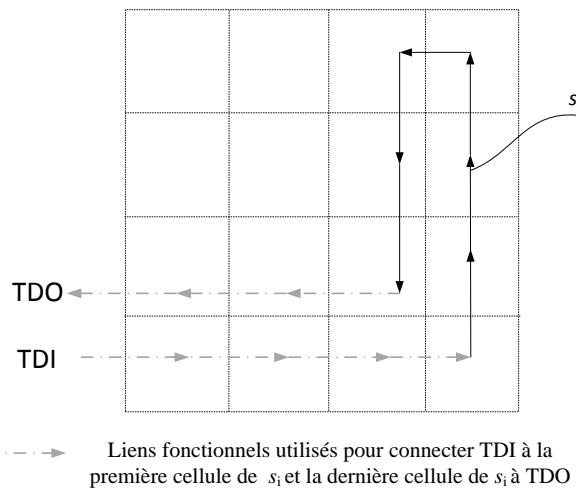

| Figure 1-12: Exemple de chemins au sein d'une structure multicellulaire. ....                                                                                                                                   | 24 |

| Figure 1-13: Architecture interne d'une cellule qui permet d'avoir une chaîne JTAG bidirectionnelle.....                                                                                                        | 25 |

| Figure 1-14: Matrice de $3 \times 3$ cellules avec des liens (x) et un contrôleur TAP (Cellule en gris) défectueux. Trois chaînes différentes (R1, R2, R3) parcourent la matrice. Figure extraite de [21]. .... | 26 |

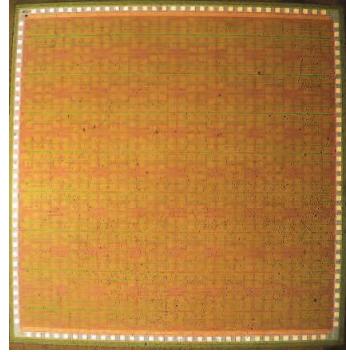

| Figure 1-15: Prototype du WaferIC (mini-WaferIC) réalisé par l'équipe DreamWafer <sup>TM</sup> .....                                                                                                            | 28 |

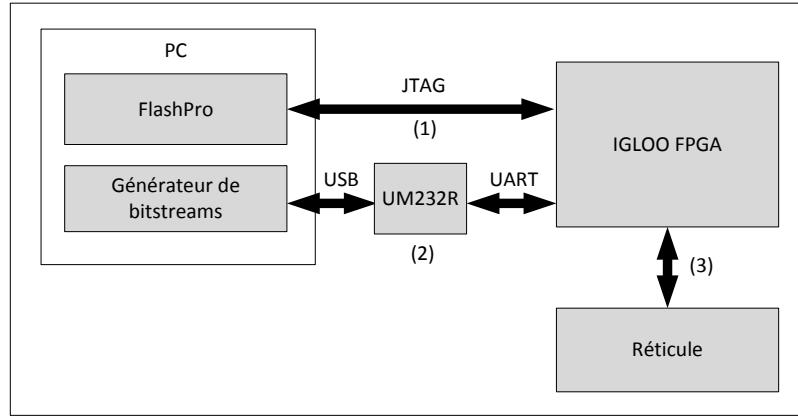

| Figure 1-16: L'environnement de test du mini-WaferIC réalisé par l'équipe.....                                                                                                                                  | 28 |

|                                                                                                                                                                                                                 |    |

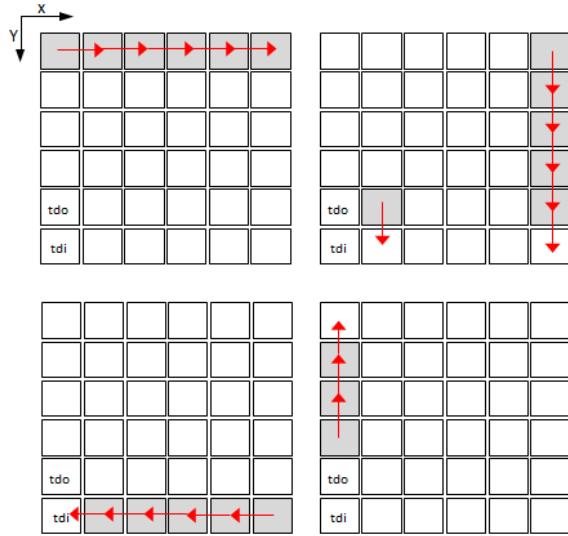

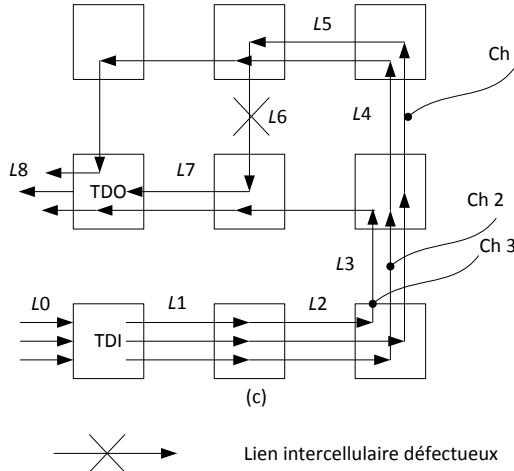

| Figure 2-1: Défectuosité au niveau d'un lien intercellulaire (a) Architecture interne de la cellule (2,3) (b) matrice de $3 \times 3$ cellules. ....                                                            | 35 |

|                                                                                                                                                                                                                                                                                                                                                    |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

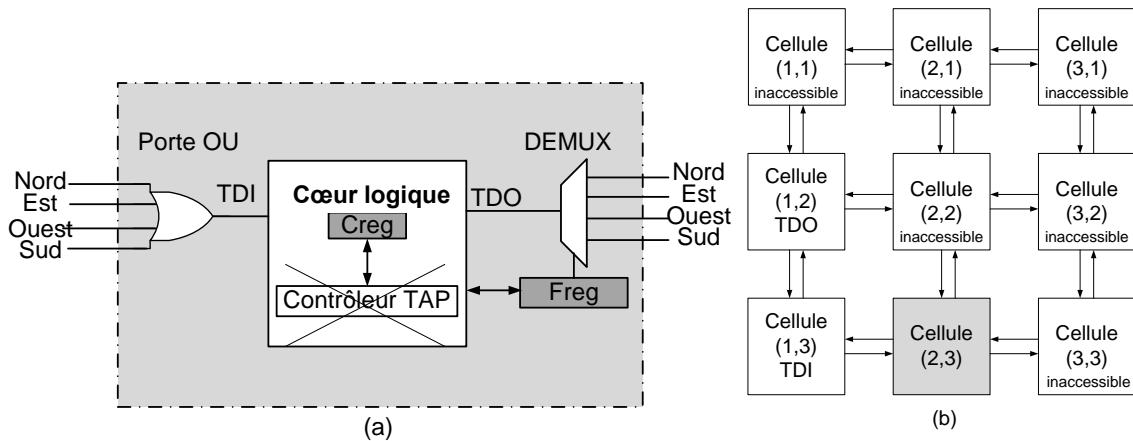

| Figure 2-2: Cellules ayant des liens sortants « non diagnosticables » : (a) Cellules dont le lien sortant EST est « non diagnosticable », (b) Cellules dont le lien sortant SUD est « non diagnosticable », (c) Cellules dont le lien sortant Ouest est « non diagnosticable », (d) Cellules dont le lien sortant Nord est « non diagnosticable ». | 37 |

| Figure 2-3: Défectuosité au niveau du contrôleur TAP de la cellule (a) Architecture interne de la cellule (2,3) (b) matrice de $3\times 3$ cellules.                                                                                                                                                                                               | 37 |

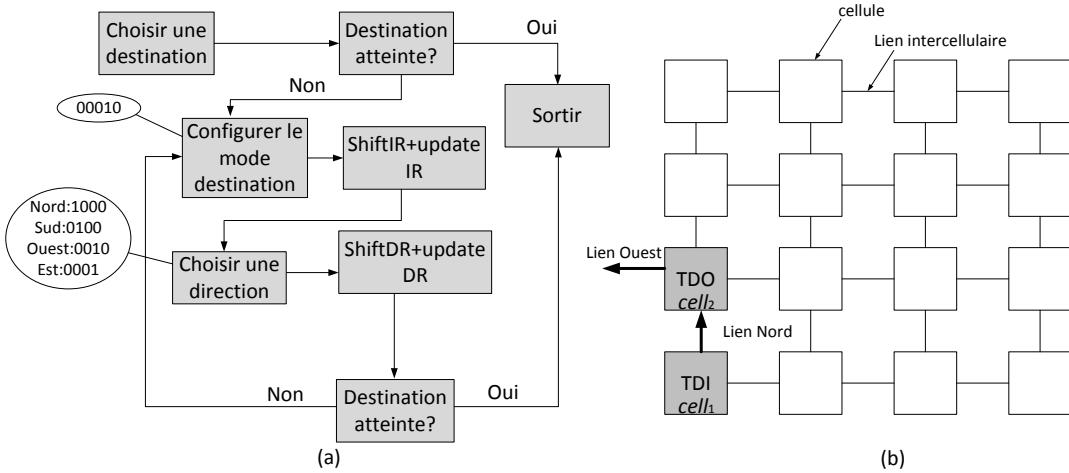

| Figure 2-4: Création d'un flux de bits JTAG (a) Organigramme de création d'un flux de bits JTAG (b) Exemple de chemin contenant deux cellules (TDI-TDO).                                                                                                                                                                                           | 41 |

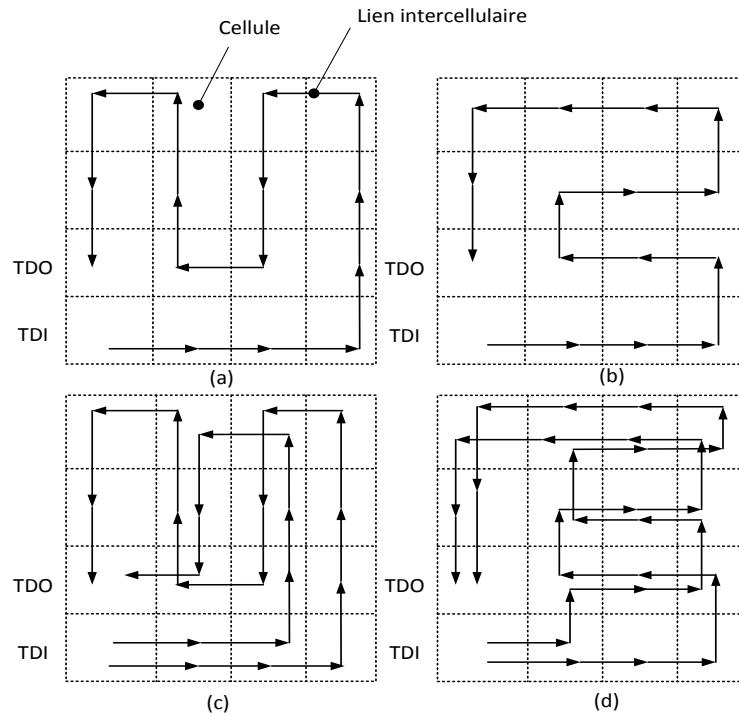

| Figure 2-5: Chemins en serpentins (a) serpentin vertical (b) serpentin horizontal (c) deux serpentins verticaux pour parcourir la majorité des liens Nord et Sud (d) deux serpentins horizontaux pour parcourir la majorité des liens Est et Ouest.                                                                                                | 44 |

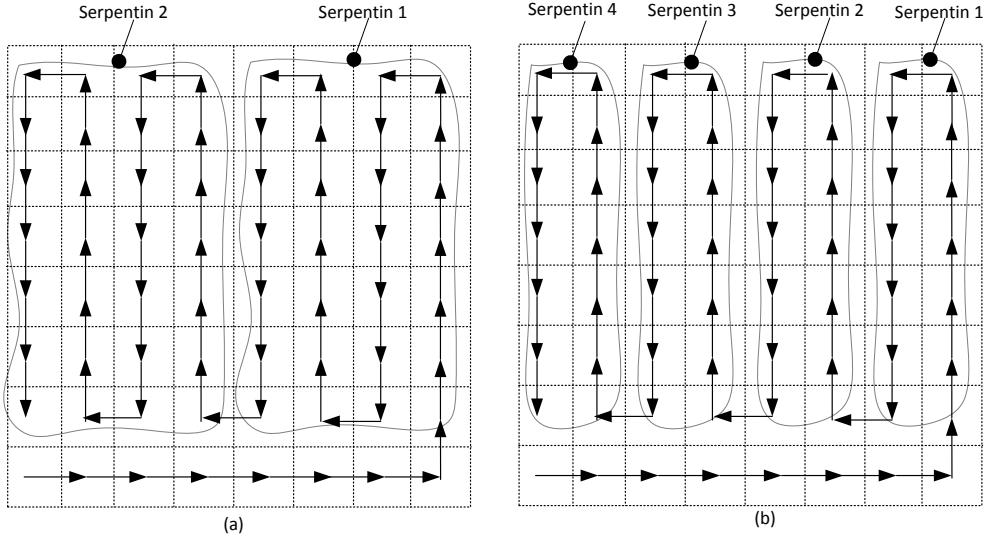

| Figure 2-6: Segmentation d'un serpentin (a) Segmentation en deux serpentins ( $k=2$ ) (b) Segmentation en quatre serpentins ( $k=4$ ).                                                                                                                                                                                                             | 45 |

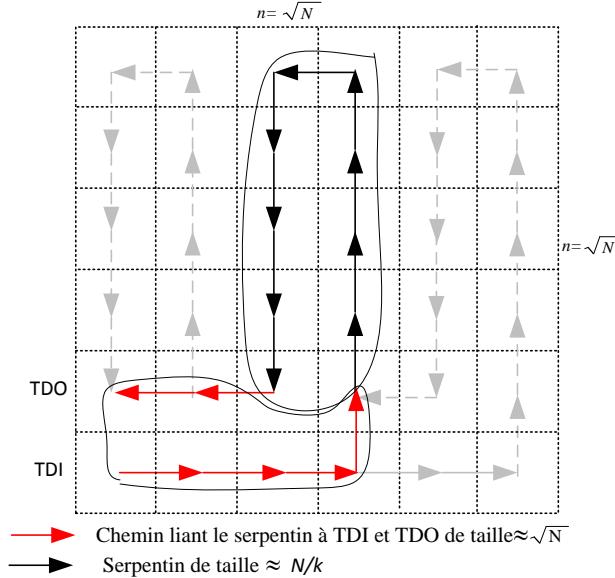

| Figure 2-7: Taille moyenne d'un serpentin.                                                                                                                                                                                                                                                                                                         | 46 |

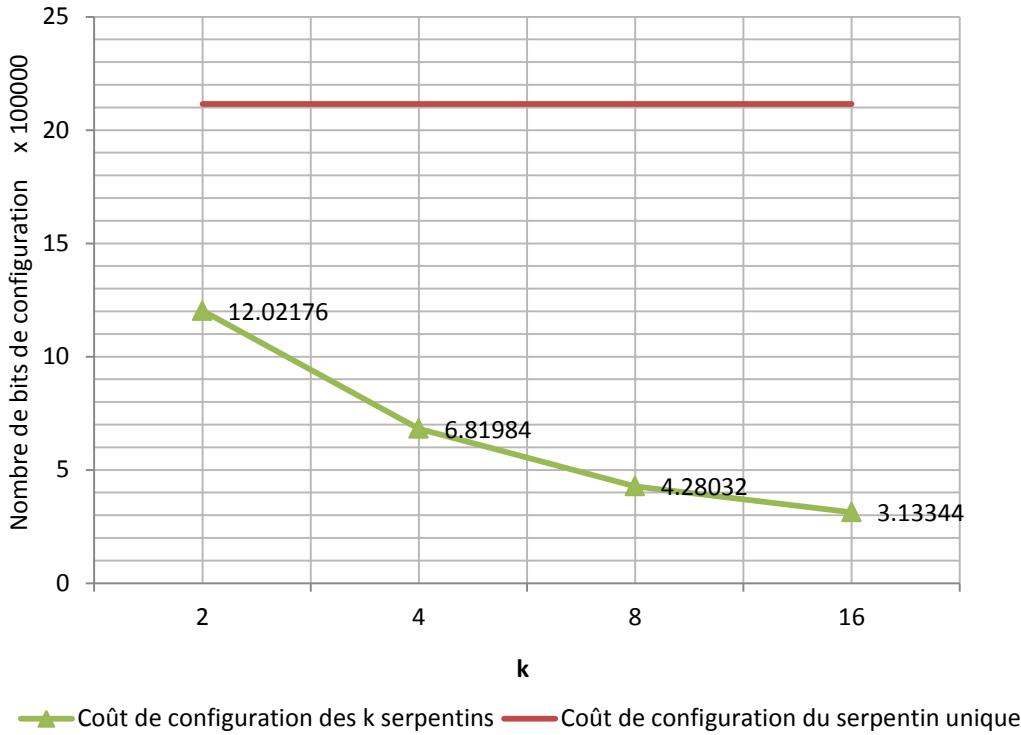

| Figure 2-8: Coût de configuration d'un serpentin parcourant toutes les cellules et coût de configuration de $k$ serpentins dans un réticule de 1024 cellules.                                                                                                                                                                                      | 47 |

| Figure 2-9: Ensemble des chemins en rectangles (a) Rectangles verticaux (b) rectangles horizontaux.                                                                                                                                                                                                                                                | 49 |

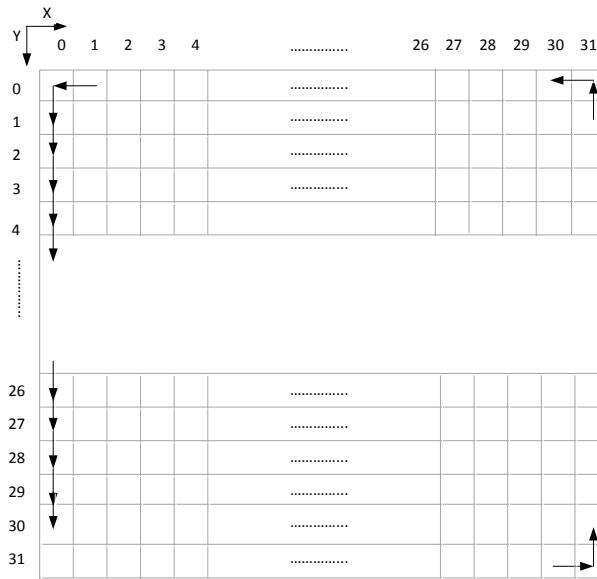

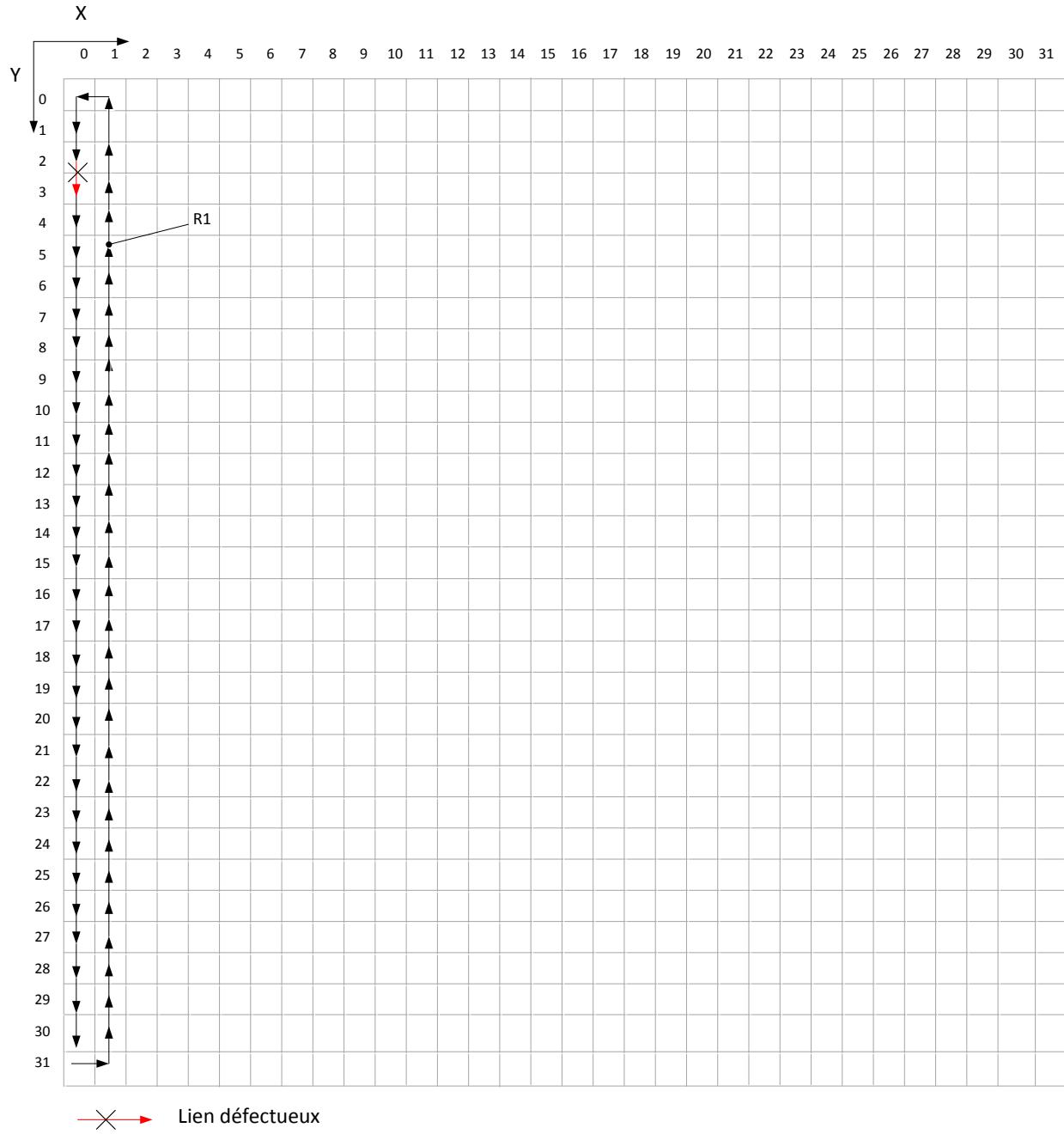

| Figure 2-10: Modélisation des $32\times 32$ cellules et des chemins rectangulaires avec le logiciel MATLAB.                                                                                                                                                                                                                                        | 50 |

|                                                                                                                                                                                                                                                                                                                                                    |    |

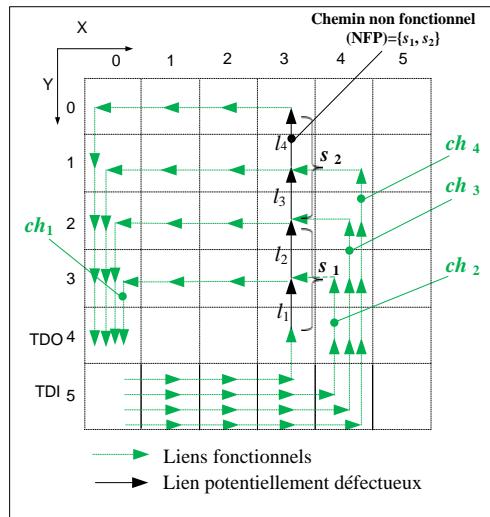

| Figure 3-1: Application de la théorie des ensembles pour identifier un lien intercellulaire défectueux.                                                                                                                                                                                                                                            | 57 |

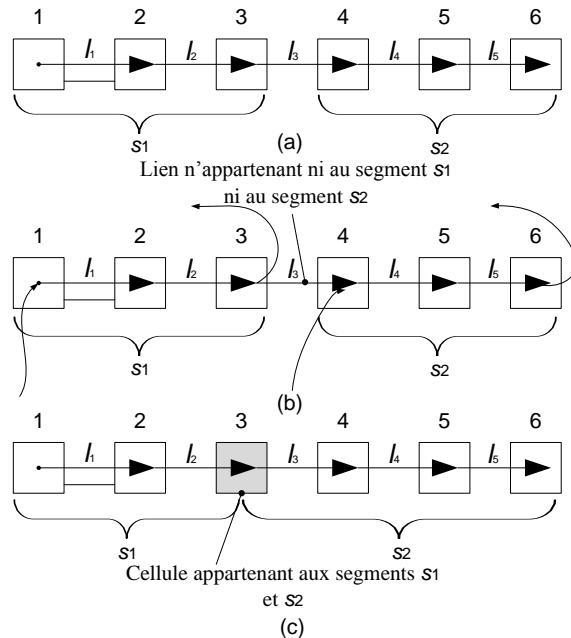

| Figure 3-2: Division d'un chemin en deux segments.                                                                                                                                                                                                                                                                                                 | 58 |

| Figure 3-3: Connexion d'un segment aux cellules TDI et TDO.                                                                                                                                                                                                                                                                                        | 59 |

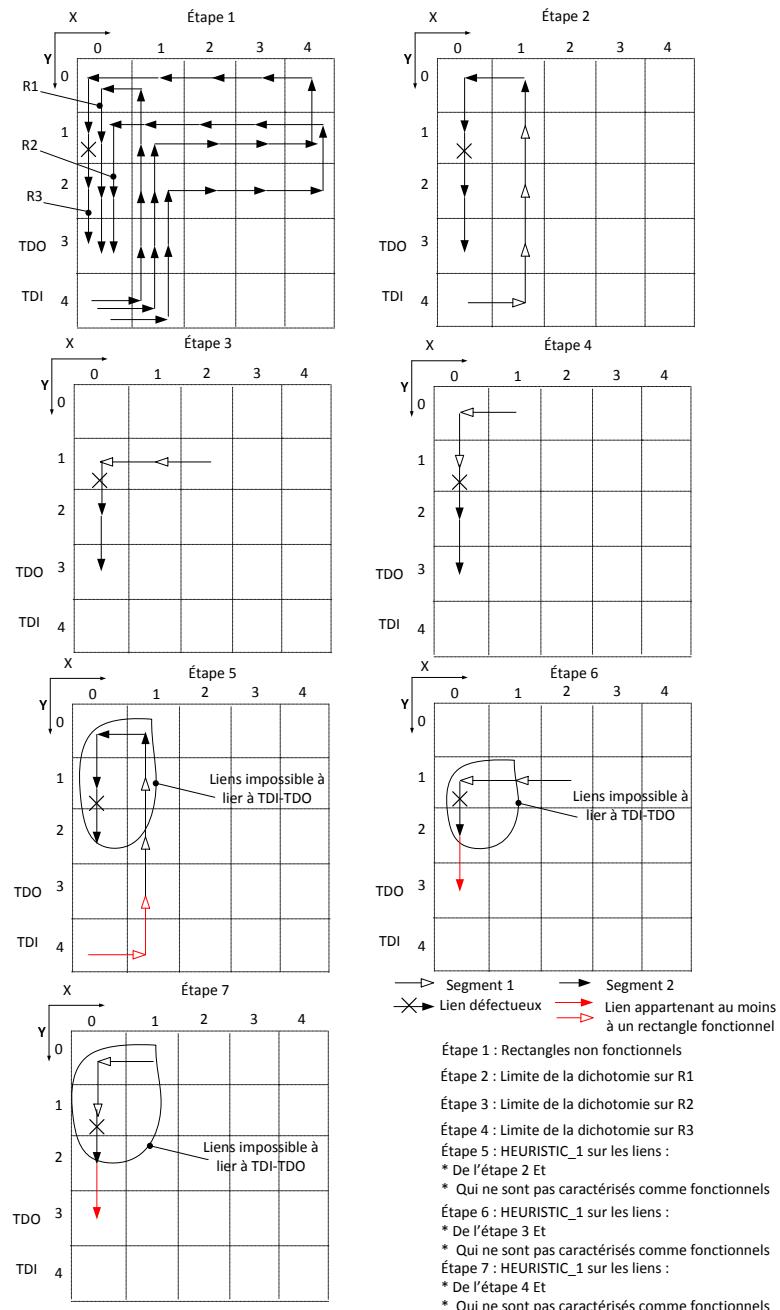

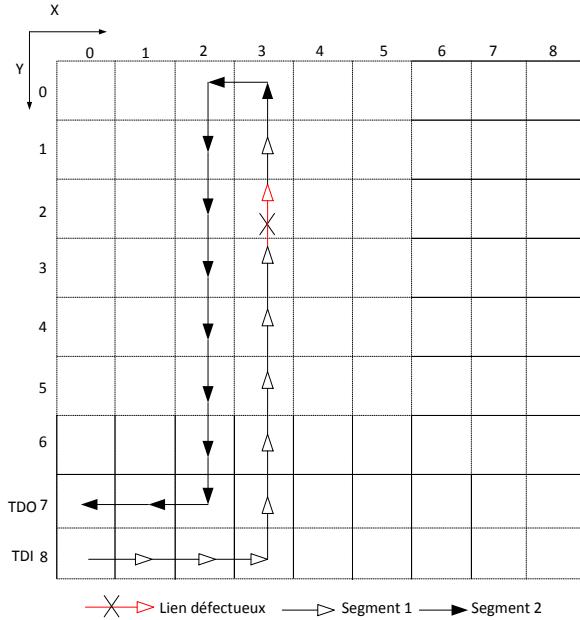

| Figure 3-4: Exemple d'application de l'algorithme HEURISTIC_1.                                                                                                                                                                                                                                                                                     | 62 |

| Figure 3-5: Pseudo code de l'algorithme HEURISTIC_1.                                                                                                                                                                                                                                                                                               | 63 |

|                                                                                                                                                                                                                                                                                                                                   |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

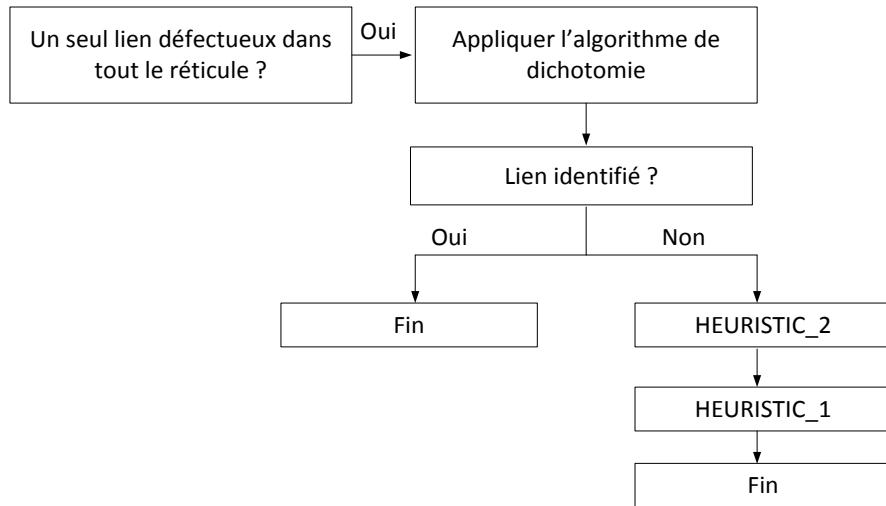

| Figure 3-6: Pseudo code de l'algorithme de diagnostic.....                                                                                                                                                                                                                                                                        | 63 |

| Figure 3-7: Localisation d'un lien défectueux par dichotomie et HEURISTIC_1.....                                                                                                                                                                                                                                                  | 66 |

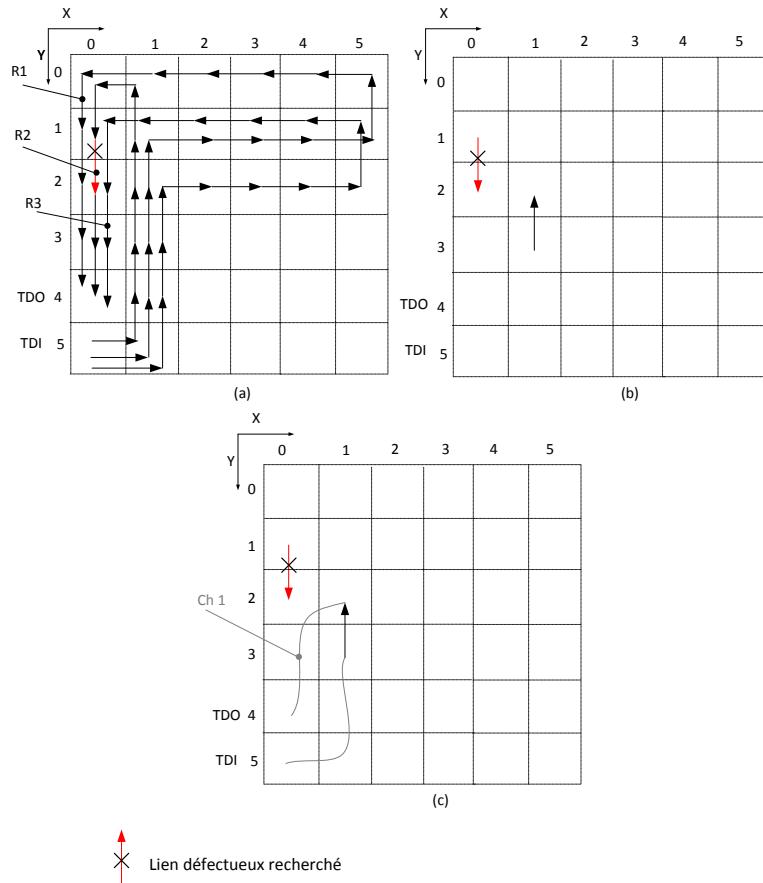

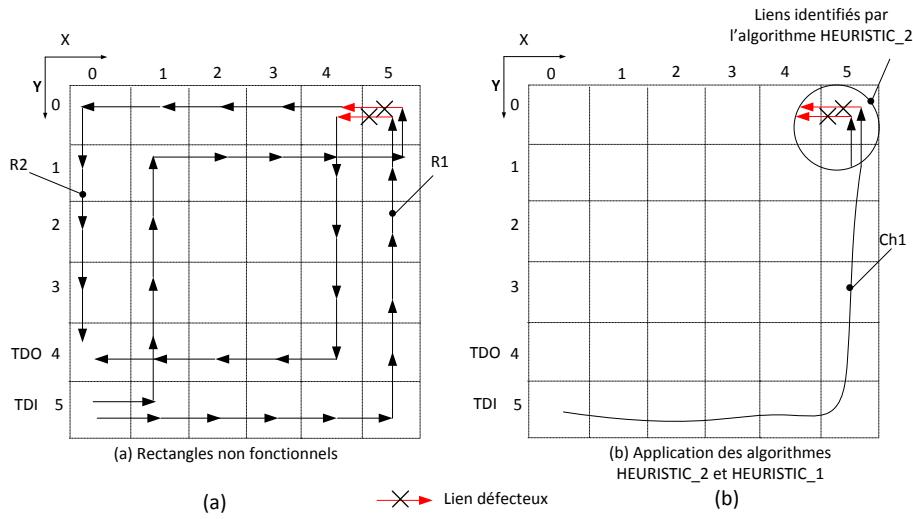

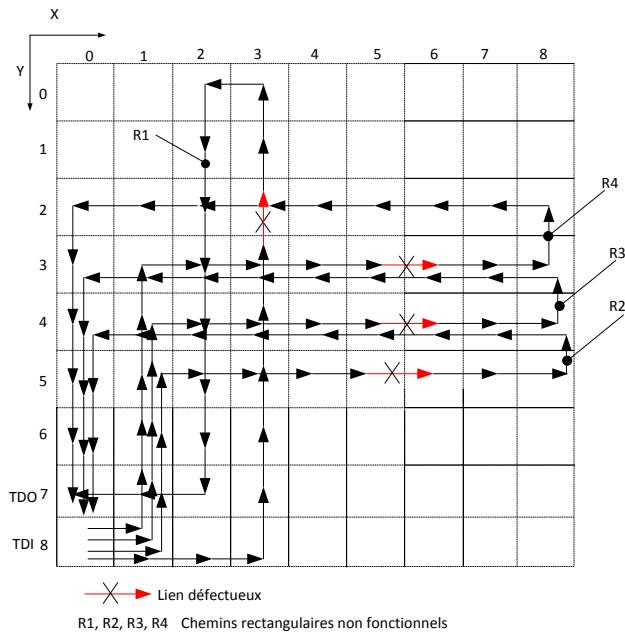

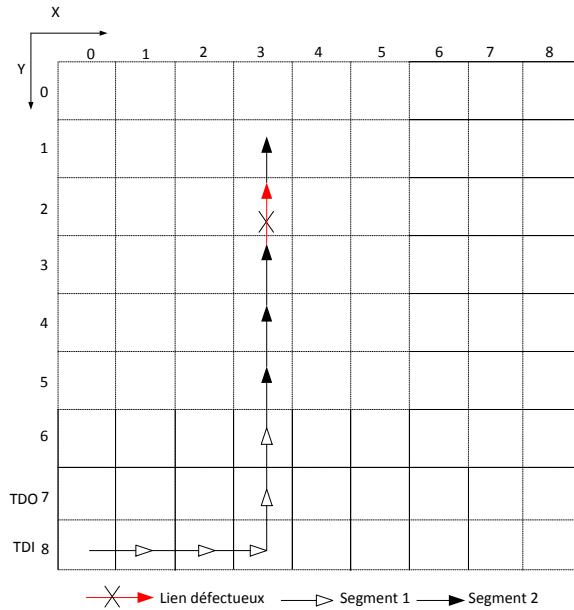

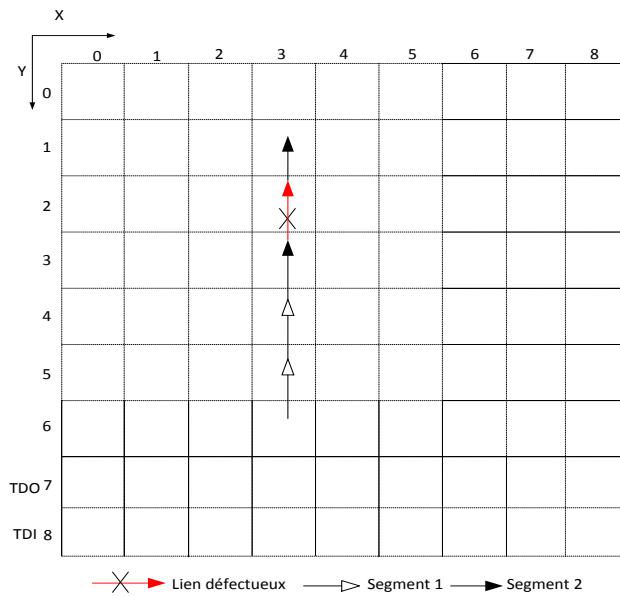

| Figure 3-8: Identification d'un lien intercellulaire défectueux avec les algorithmes heuristiques<br>(a) Rectangles non fonctionnels (b) Liens identifiés par l'algorithme HEURISTIC_2 (c)<br>Application de l'algorithme HEURISTIC_1.....                                                                                        | 69 |

| Figure 3-9: Recherche du seul lien défectueux du réticule.....                                                                                                                                                                                                                                                                    | 70 |

| Figure 3-10 : Pseudo code de l'algorithme de diagnostic dans le cas où un seul lien défectueux est présent dans le réticule.....                                                                                                                                                                                                  | 71 |

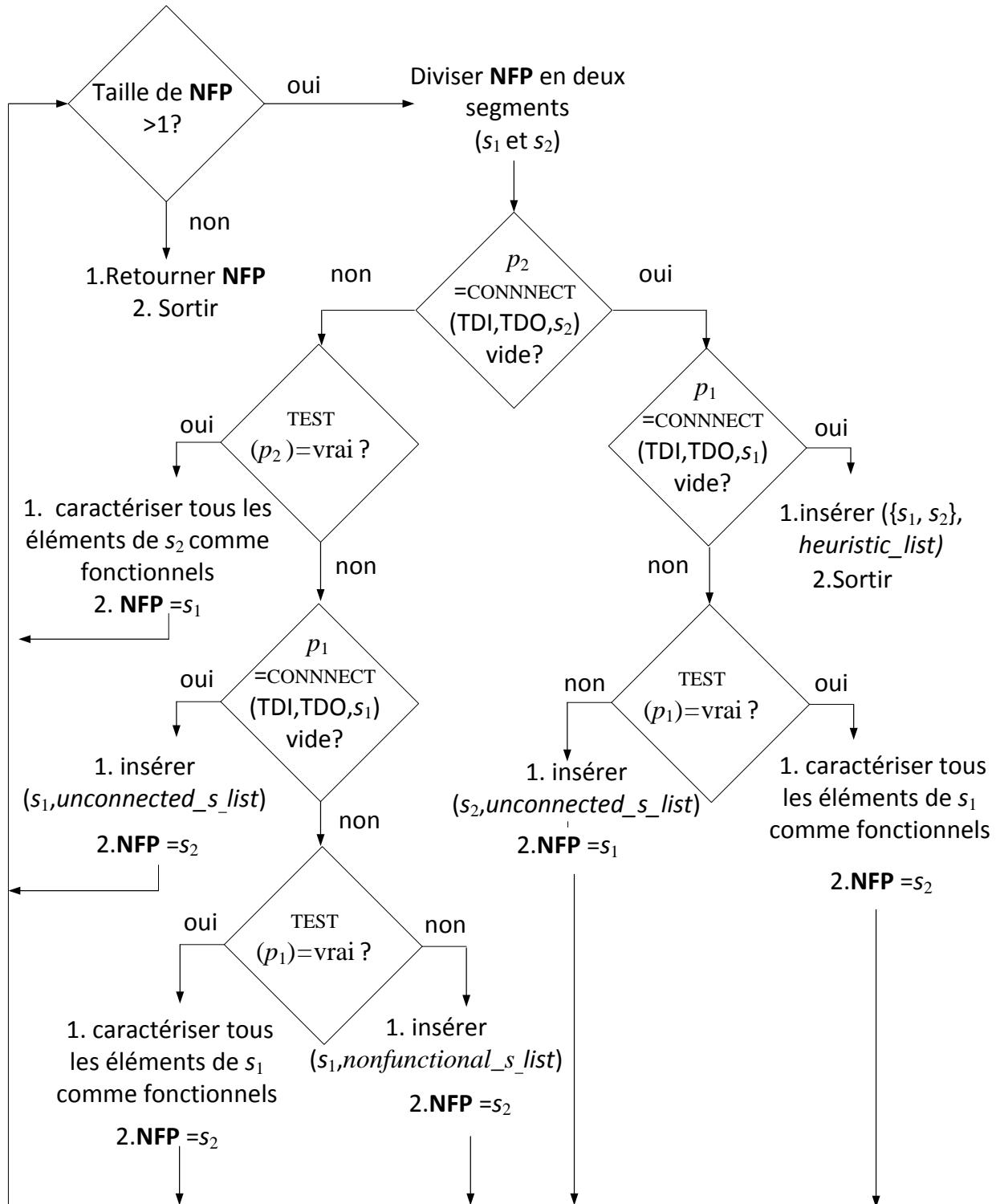

| Figure 3-11: Organigramme de l'algorithme de dichotomie.....                                                                                                                                                                                                                                                                      | 72 |

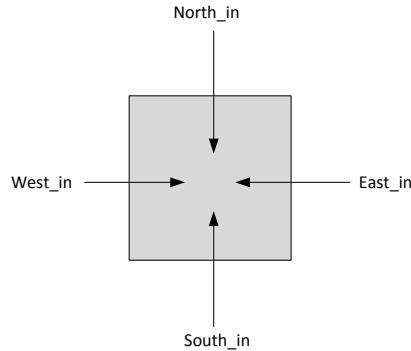

| Figure 3-12: Cellule marquée par quatre index (North_in, West_in, South_in, et East_in).....                                                                                                                                                                                                                                      | 74 |

| Figure 3-13: Pseudo code de l'algorithme de LEE développé.....                                                                                                                                                                                                                                                                    | 75 |

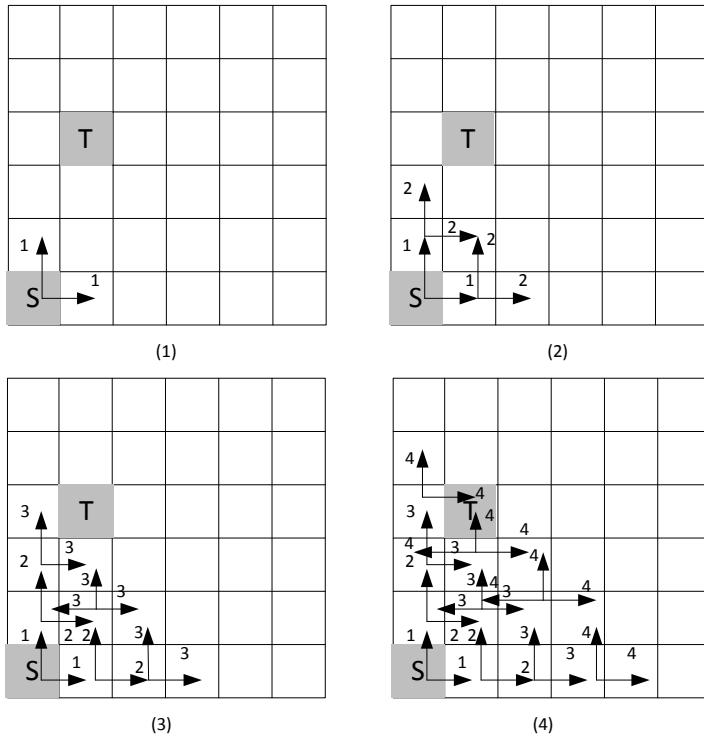

| Figure 3-14: Exemple de la phase d'exploration dans l'algorithme de LEE développé.....                                                                                                                                                                                                                                            | 76 |

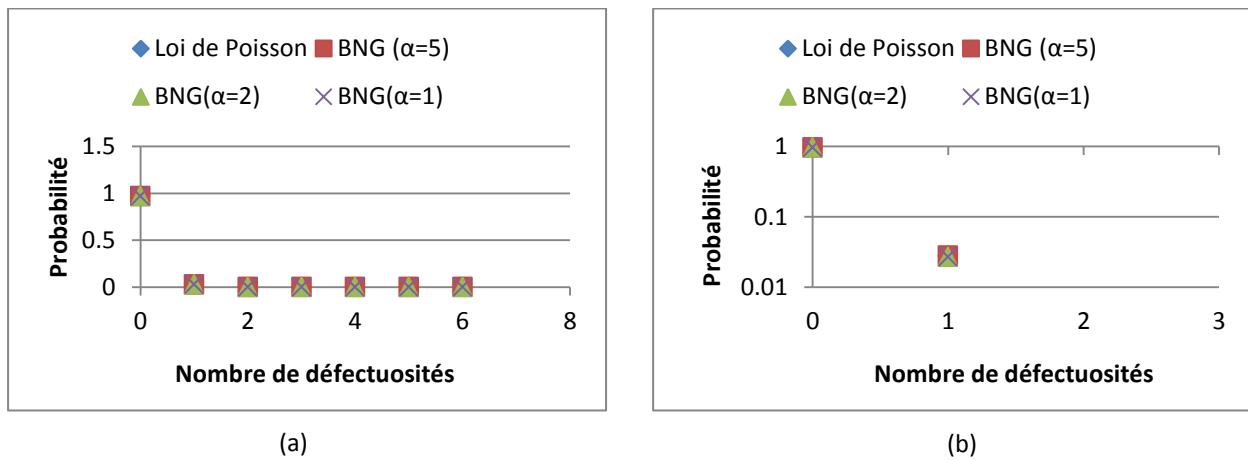

| Figure 4-1: Estimation du nombre de défectuosités par la loi de Poisson et la loi binomiale négative pour $\lambda=0.018$ (a) L'axe des ordonnées en échelle linéaire (b) L'axe des ordonnées en échelle logarithmique.....                                                                                                       | 80 |

| Figure 4-2: Pseudo code de l'environnement de simulation.....                                                                                                                                                                                                                                                                     | 81 |

| Figure 4-3: Liens non localisés par l'algorithme de dichotomie.....                                                                                                                                                                                                                                                               | 83 |

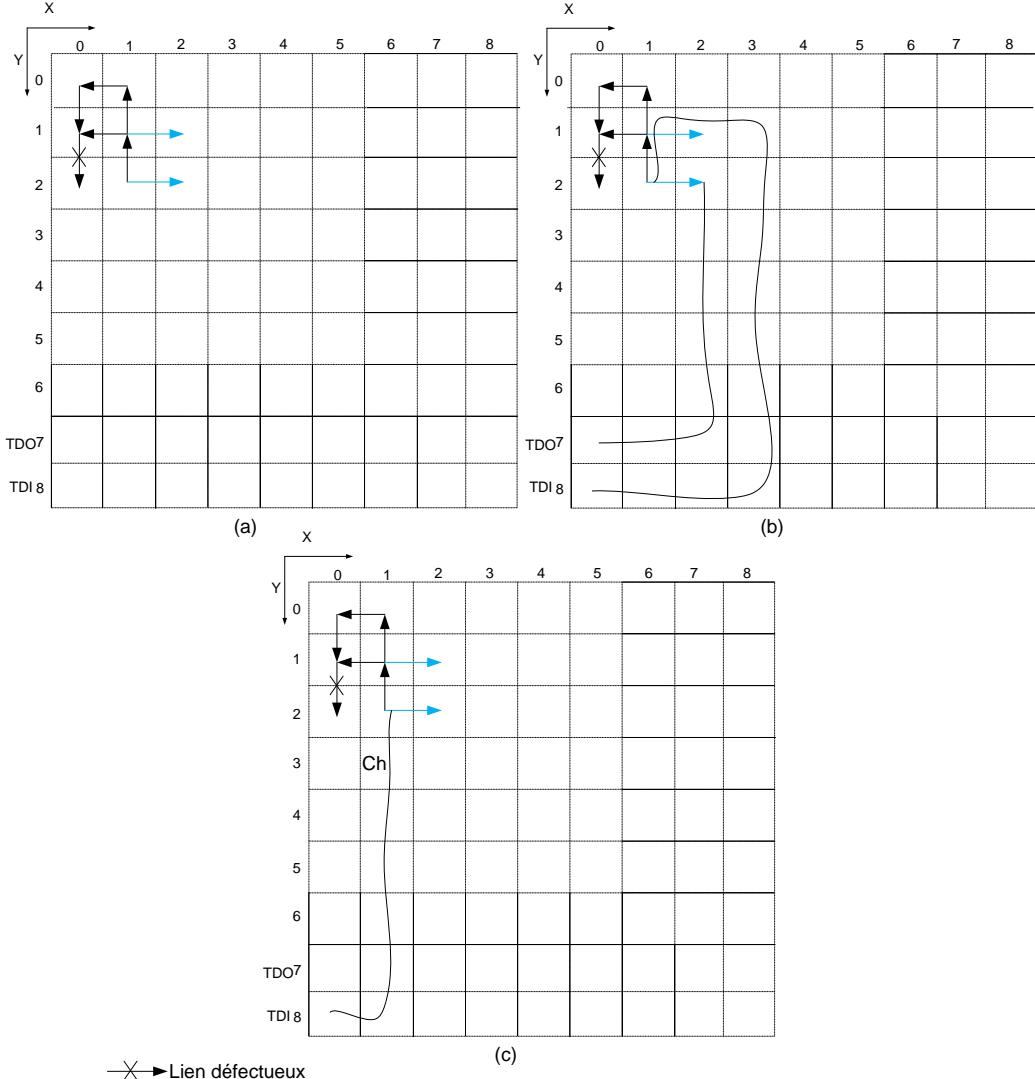

| Figure 4-4: Exemple d'application des algorithmes heuristiques pour localiser un lien défectueux appartenant aux liens de la figure 4-3 et situé dans le coin du réticule (a) rectangles non fonctionnels (b) application de l'algorithme HEURISTIC_1 sur les liens identifiés par l'algorithme HEURISTIC_2.....                  | 85 |

| Figure 4-5 Exemple illustrant une limite de l'algorithme de LEE (a) liens déclarés potentiellement défectueux par l'algorithme de LEE (b) Exemple de chemin complet constitué uniquement de liens fonctionnels et couvrant le lien (1,2) Est (c) chemin créé par l'algorithme de LEE, liant la cellule TDI au lien (1,2) Est..... | 88 |

|                                                                                                                                                                                                                                                                                                                                |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

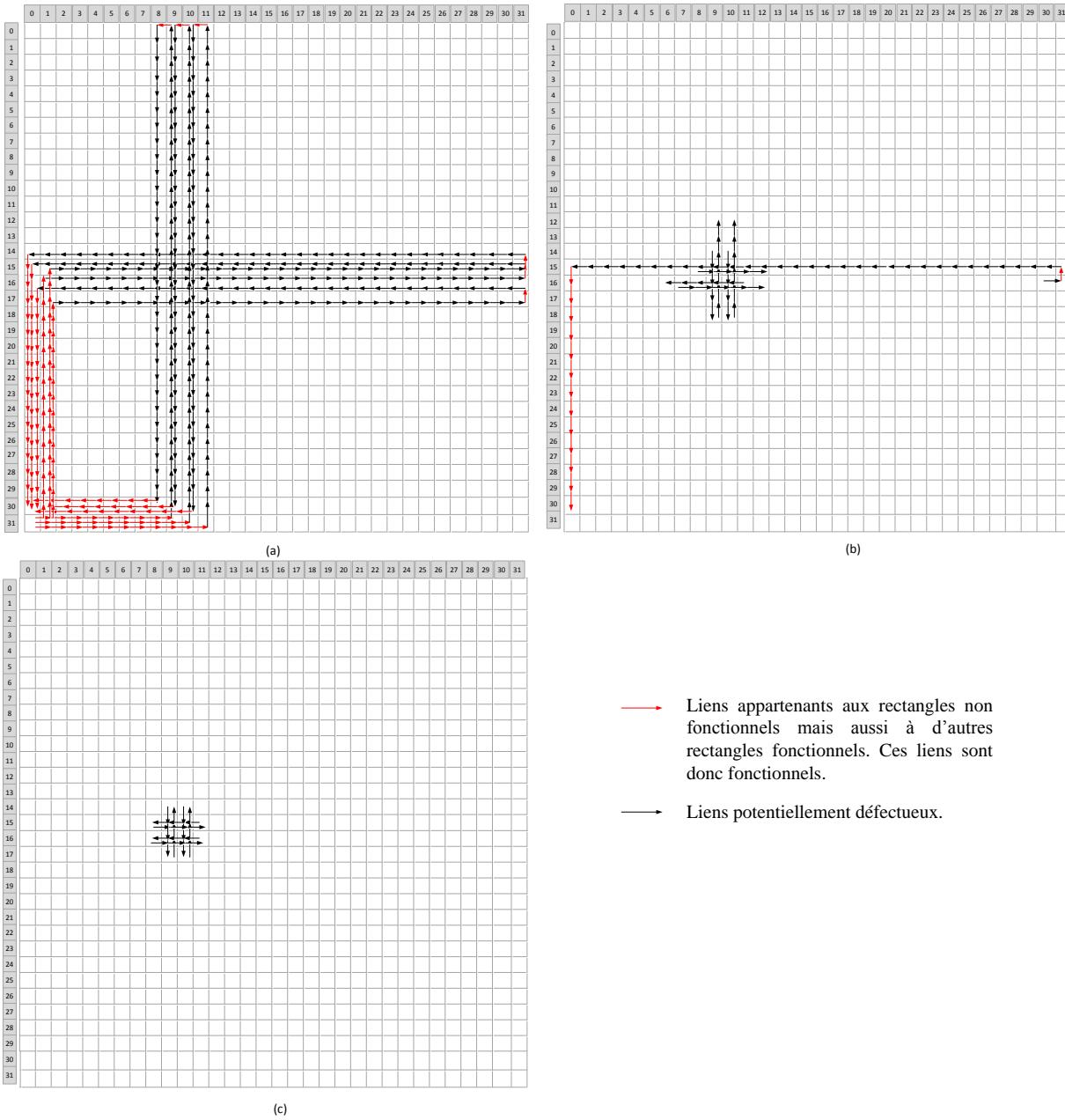

| Figure 4-6: Performances de l'algorithme de dichotomie dans le cas où plusieurs liens défectueux sont injectés dans le réticule.....                                                                                                                                                                                           | 89  |

| Figure 4-7: Résultat de l'application de l'algorithme de diagnostic sur un réticule du mini-WaferIC (a) Chemins rectangulaires trouvés non fonctionnels (b) Liens potentiellement défectueux trouvés par l'algorithme de dichotomie (c) Liens potentiellement défectueux trouvés après l'appel à l'algorithme HEURISTIC_1..... | 93  |

| Figure 4-8: Évolution du nombre des liens fonctionnels et des liens potentiellement défectueux durant le diagnostic du réticule du mini-WaferIC.....                                                                                                                                                                           | 94  |

|                                                                                                                                                                                                                                                                                                                                |     |

| Figure A-1 Exemple de liens défectueux engendrant des chemins rectangulaires non fonctionnels.<br>.....                                                                                                                                                                                                                        | 103 |

| Figure A-2 Division du chemin rectangulaire R1 en deux segments .....                                                                                                                                                                                                                                                          | 105 |

| Figure A-3 Division du segment 1 de la figure A-2 en deux segments .....                                                                                                                                                                                                                                                       | 105 |

| Figure A-4 Division du segment 2 de la figure A-3 en deux segments. ....                                                                                                                                                                                                                                                       | 105 |

|                                                                                                                                                                                                                                                                                                                                |     |

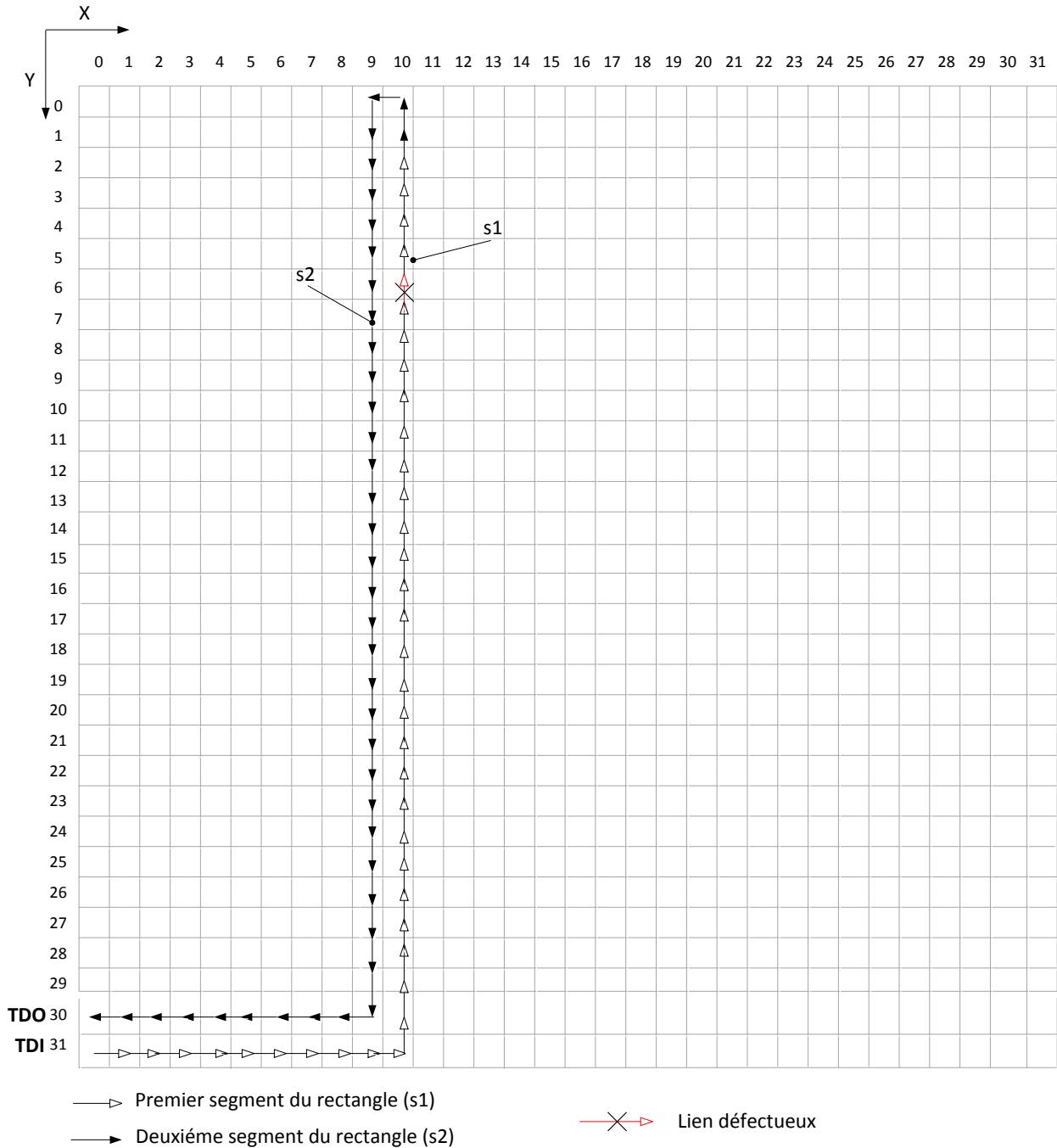

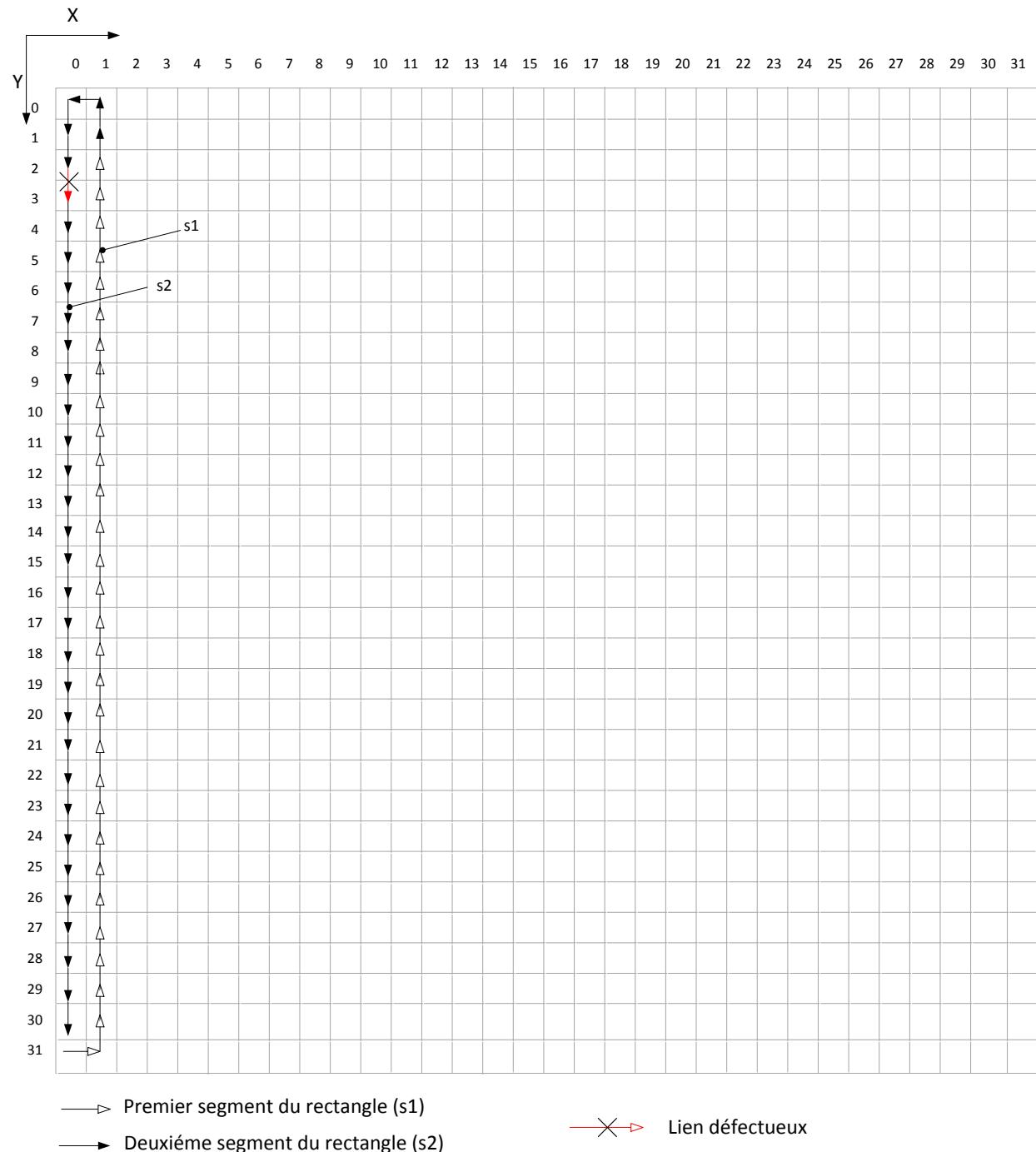

| Figure B-1: Un rectangle vertical non fonctionnel (R1) à cause d'un lien défectueux (Lien Sud de la cellule (0,2)). .....                                                                                                                                                                                                      | 110 |

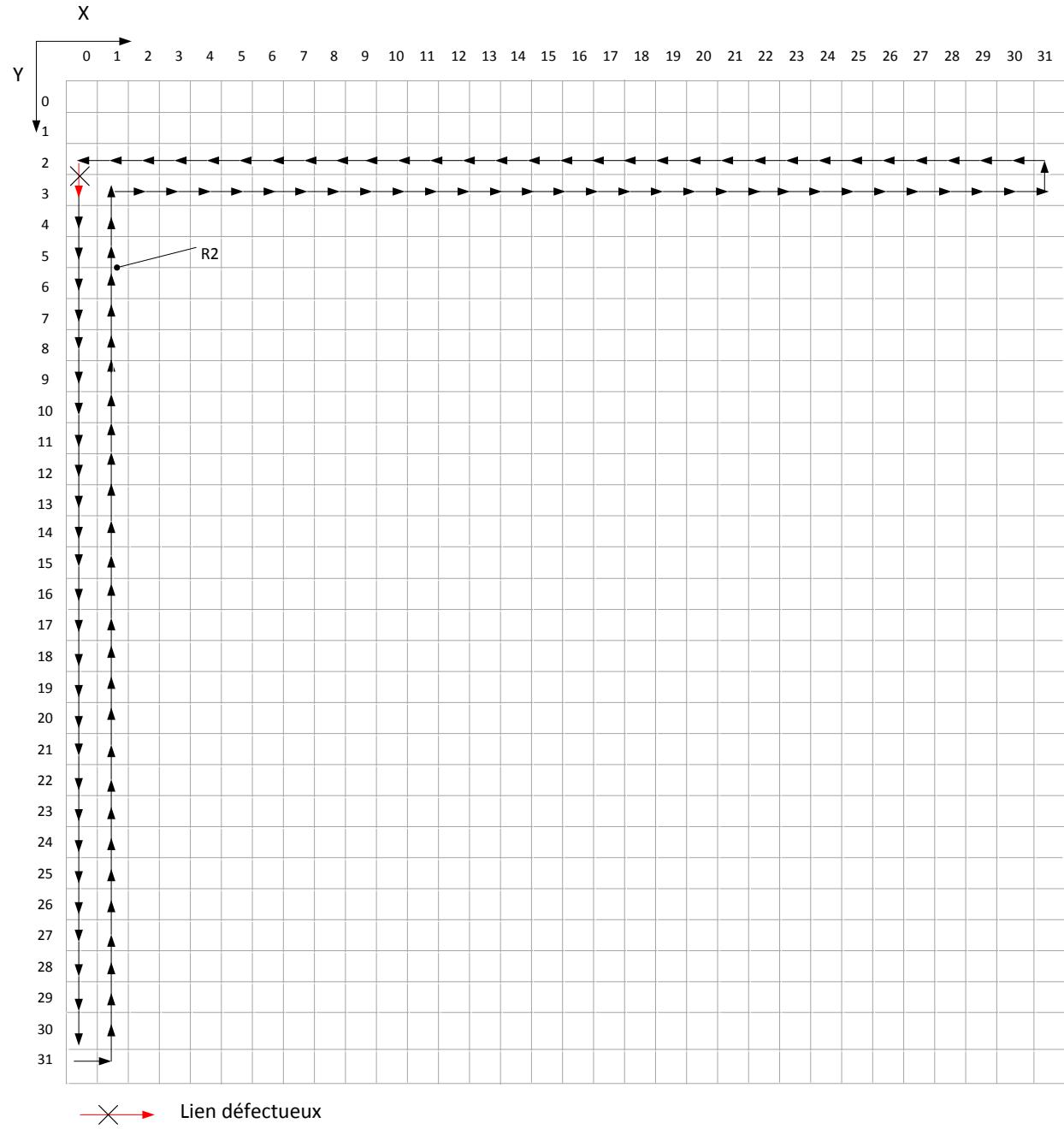

| Figure B-2: Un rectangle horizontal non fonctionnel (R2) à cause d'un lien défectueux (Lien Sud de la cellule (0,2)).....                                                                                                                                                                                                      | 111 |

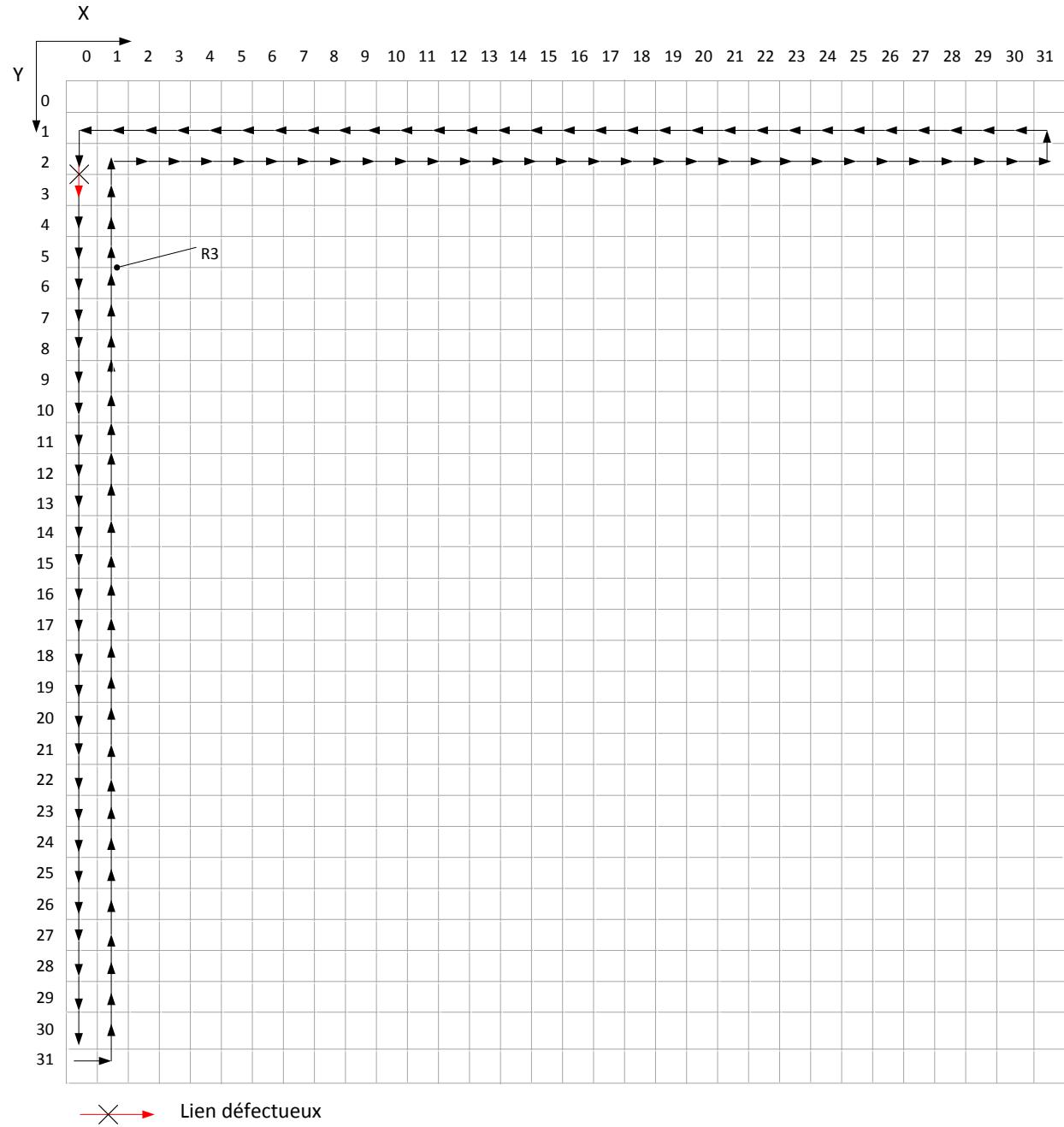

| Figure B-3: Un rectangle horizontal non fonctionnel (R3) à cause d'un lien défectueux (Lien Sud de la cellule (0,2)).....                                                                                                                                                                                                      | 112 |

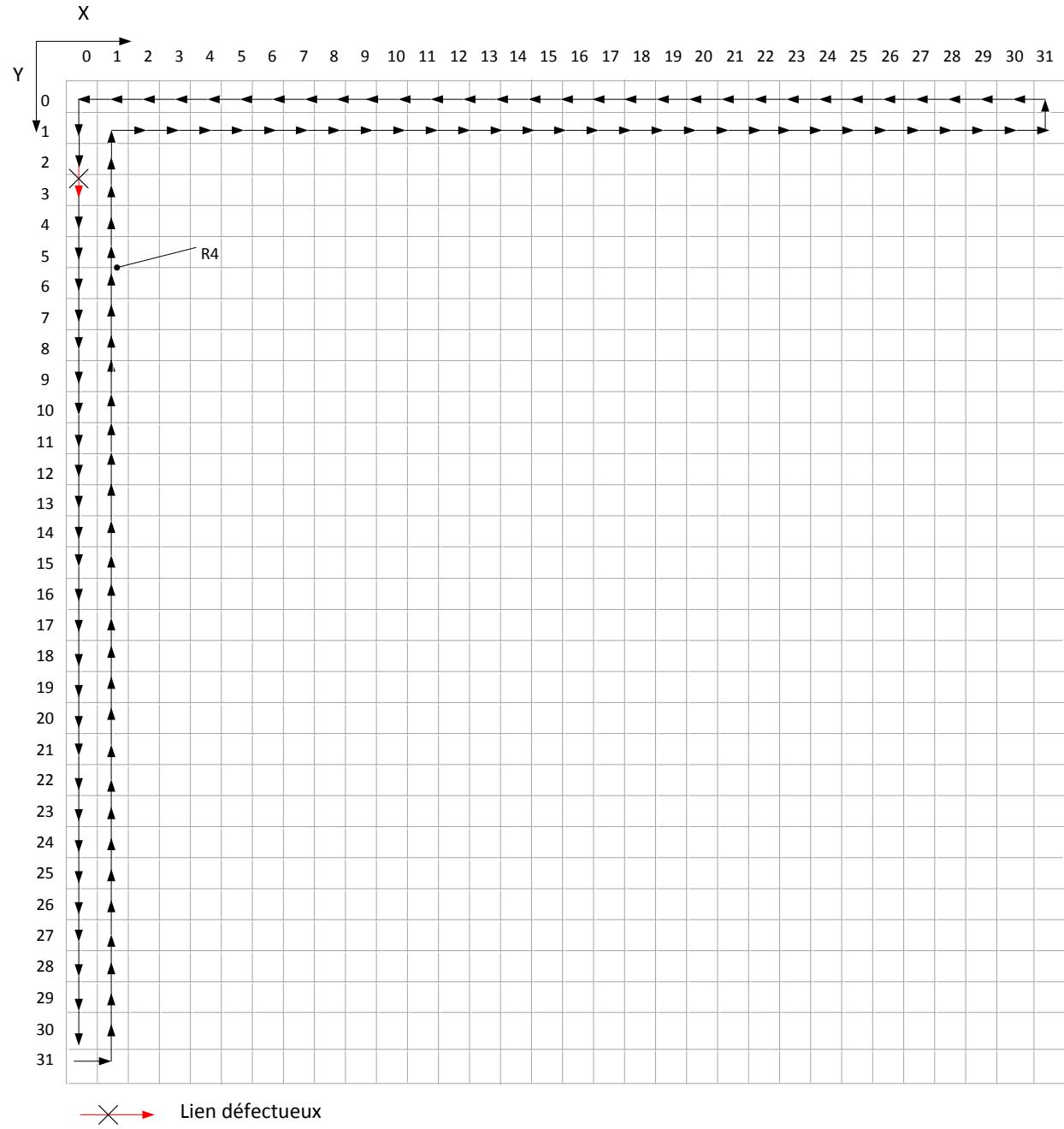

| Figure B-4: Un rectangle horizontal non fonctionnel (R4) à cause d'un lien défectueux (Lien Sud de la cellule (0,2)).....                                                                                                                                                                                                      | 113 |

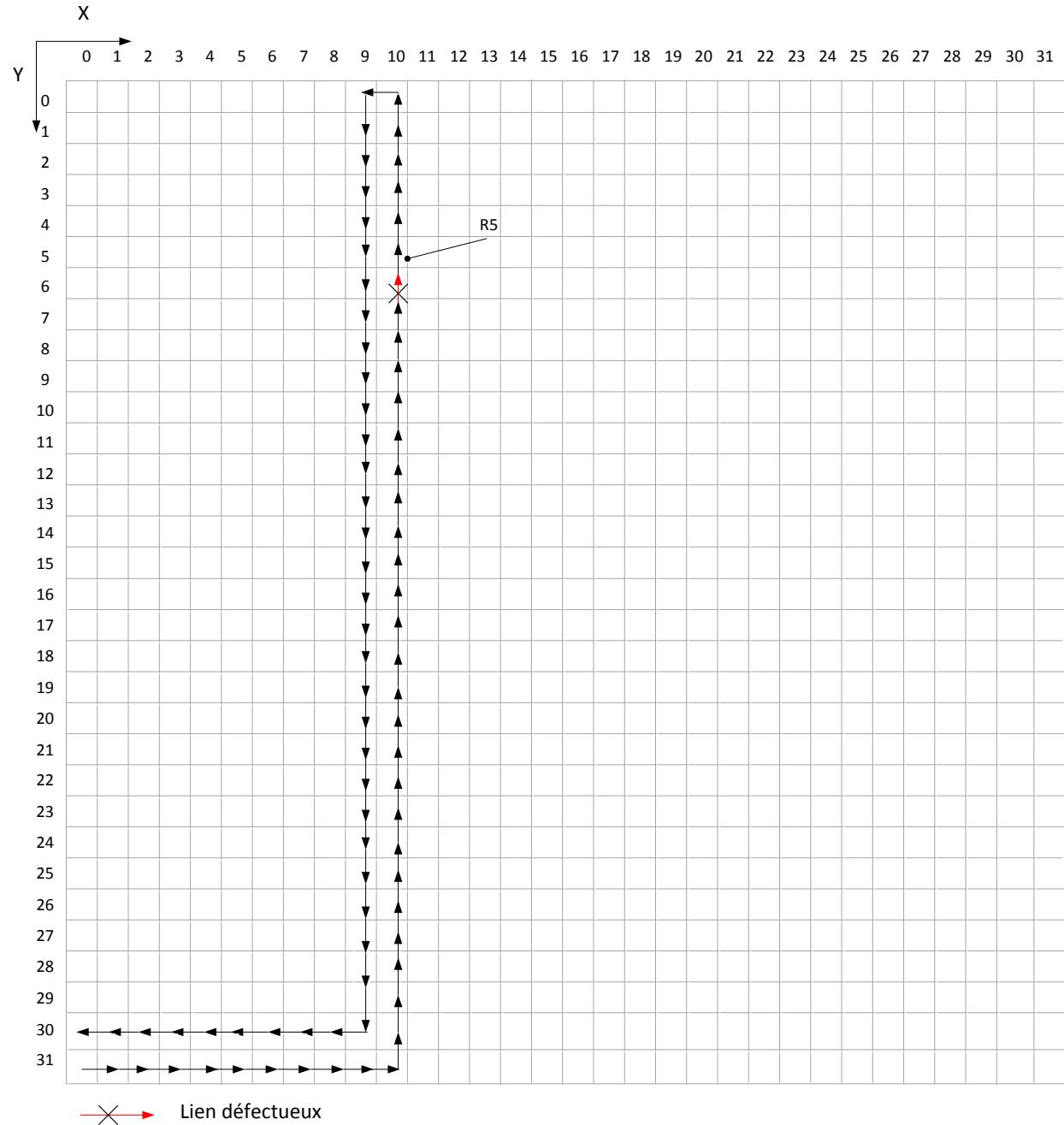

| Figure B-5: Un rectangle vertical non fonctionnel (R5) à cause d'un lien défectueux (Lien Nord de la cellule (10,7))......                                                                                                                                                                                                     | 114 |

| Figure B-6: Division du rectangle (R5) en deux segments s1 et s2. ....                                                                                                                                                                                                                                                         | 115 |

| Figure B-7: Division du rectangle (R1) en deux segments s1 et s2. ....                                                                                                                                                                                                                                                         | 116 |

## **LISTE DES SIGLES ET ABRÉVIATIONS**

|      |                                  |

|------|----------------------------------|

| BGA  | Ball Grid Array                  |

| CDSP | Circuit Discret Sous Prototypage |

| FPGA | Field Programmable Gate Array    |

| IC   | Integrated Circuit               |

| JTAG | Joint Test Action Group          |

| LAIC | Large Area Integrated Circuit    |

| MCM  | Multi-Chip Module                |

| PCB  | Printed Circuit Board            |

| SiP  | System in Package                |

| SoC  | System on Chip                   |

| SoW  | System on Wafer                  |

| TSV  | Through Silicon Via              |

| UUT  | Unit Under Test                  |

| VLSI | Very Large System Integration    |

| WSI  | Wafer Scale Integration          |

## LISTE DES ANNEXES

|                                                                                               |     |

|-----------------------------------------------------------------------------------------------|-----|

| Annexe A - Cas de figure où l'algorithme HEURISTIC_1 est appelé.....                          | 103 |

| Annexe B - Cas de figure où l'algorithme de dichotomie ne retrouve pas les défectuosités..... | 106 |

## INTRODUCTION

Les systèmes électroniques actuels, à la fine pointe de la technologie, sont des systèmes très complexes contenant parfois un grand nombre de puces électroniques. Les puces sont traditionnellement montées et interconnectées moyennant une carte imprimée appelée PCB (*Printed Circuit Board*). Rassembler plusieurs puces sur une carte imprimée est une tâche laborieuse. En effet, plusieurs difficultés surgissent. On peut citer par exemple :

- Plus le nombre de puces est élevé, plus la taille du circuit global est grande. Ceci augmente le coût de fabrication.

- Pour interconnecter un grand nombre de modules sur une petite surface, il faut miniaturiser la taille des composants électroniques. Ceci est limité par des contraintes physiques.

- Dans les PCB très dense, la phase de test est une tâche ardue vu que certaines broches sont inaccessibles (typiquement sous les puces quand on utilise des boîtiers de haute densité comme les BGA (*Ball Grid Array*)).

- Afin de répondre à la demande d'intégration des systèmes électroniques dans des volumes de plus en plus petits, les PCB actuels comportent plusieurs couches de métallisation. Ceci rend non seulement les processus de routage et de test plus difficiles, mais aussi amène des coûts plus élevés lors de la fabrication.

- Plus le système électronique réalisé est dense, plus il est difficile de résoudre les problèmes qui peuvent surgir, que ce soit au niveau matériel ou logiciel. Le test et la validation de tels systèmes deviennent donc assez longs et coûteux.

Devant les difficultés rencontrées avec les PCB, le prototypage rapide à l'aide d'un circuit intégré à l'échelle de la tranche (*Wafer Scale Integrated (WSI)*) est donc apparu comme une alternative intéressante à considérer. C'est dans le cadre des circuits intégrés à l'échelle de la tranche que Richard Norman a proposé une solution [4] à l'ensemble des problèmes cités. Il introduit un nouveau concept de circuit intégré nommé le « WaferIC ». C'est un circuit intégré à l'échelle de la tranche de Silicium capable d'interconnecter un très grand nombre de plots sur un ensemble de circuits électroniques ayant chacun jusqu'à 2000 plots et même plus. C'est en quelque sorte un substrat intelligent permettant de connecter des puces déposées sur sa surface suivant une

spécification des interconnexions communément appelée *netlist* fournie par l'utilisateur. Ces interconnexions sont reprogrammables autant de fois que l'utilisateur le souhaite. Cette solution brevetée par Norman est la propriété de Gestion TechnoCap Inc et cette technologie est nommée « WaferBoard<sup>TM</sup> ».

Le WaferBoard<sup>TM</sup> est une plateforme de prototypage rapide des systèmes numériques. Cette plateforme a été prototypée dans le cadre d'un projet de recherche nommé DreamWafer<sup>TM</sup> réalisé en coopération entre plusieurs universités canadiennes (notamment Polytechnique Montréal, Université du Québec à Montréal, Université du Québec en Outaouais et McGill) ainsi qu'en compagnie de Gestion TechnoCap Inc société basée à Montréal. Plusieurs étudiants et professeurs ont contribué au projet depuis 2006 chacun dans son domaine.

La plateforme WaferBoard<sup>TM</sup> offre un réseau d'interconnexion reprogrammable. Les interconnexions entre les puces sont effectuées à l'aide de la plateforme conformément à une spécification des interconnexions désirées communément appelée une *netlist* fournie par l'utilisateur. Le WaferBoard<sup>TM</sup>, une fois mis sur le marché, permettrait de réduire le coût de prototypage ainsi que le temps de commercialisation des systèmes électroniques. Le WaferBoard<sup>TM</sup> permettrait aux ingénieurs logiciels de travailler sur un système fonctionnel pendant que les ingénieurs matériels en conçoivent le circuit imprimé. Ceci permettrait de réaliser un gain économique non négligeable.

Les puces à interconnecter, qu'on appelle aussi CDSP (Circuit Discret Sous Prototypage), sont déposées sur la surface active du WaferIC. Le dépôt des puces est insensible à l'alignement, c'est-à-dire que les puces sont déposées dans n'importe quel sens. Le WaferIC, breveté par Monsieur Richard Norman, comporte 76 images de réticule, où chaque réticule est une mer de cellules identiques au niveau physique. Ces cellules sont interconnectées par des liens intercellulaires formant ainsi un vaste réseau d'interconnexions. Chaque cellule contient des petits plots appelés « *NanoPads* » qui peuvent alimenter en tension les broches des puces avec lesquelles ils sont en contact.

Pour obtenir les interconnexions nécessaires entre les puces déposées, il faut programmer les cellules du WaferIC qui sont en contact avec ces puces. La programmation du WaferIC se fait moyennant une chaîne conforme à un sur-ensemble de la norme de test JTAG [1]. Une seule

chaîne commence par le port d'entrée du contrôleur de test, configure toutes les cellules (qui sont en contact avec les puces) puis ressort par le port de sortie du contrôleur de test. La chaîne JTAG est donc composée d'un ensemble de cellules et de liens intercellulaires. La chaîne est un sur-ensemble de JTAG qui est reconfigurable (c'est-à-dire qu'elle peut être reprogrammée pour parcourir n'importe quelle cellule) et tolérante aux pannes. Ces deux caractéristiques ne sont pas présentes dans des chaînes JTAG standard. Deux aspects de la tolérance aux pannes qui supportent la chaîne JTAG étudiée dans ce mémoire sont à mentionner :

- Si une cellule particulière est défectueuse, elle peut toujours être programmée (configurée) à partir d'une cellule voisine fonctionnelle.

- La chaîne JTAG ne peut passer que par des éléments (cellules et liens) dont la fonctionnalité est validée. En effet, si la chaîne JTAG rencontre ne serait-ce qu'une seule défectuosité, elle sera brisée et complètement inutilisable.

Ces deux aspects de la tolérance aux pannes nécessitent un diagnostic préalable pour repérer les éléments (cellules et liens) fonctionnels du WaferIC.

### **Objectif :**

Le diagnostic de la chaîne JTAG est le sujet de recherche de cette maîtrise. Ce mémoire présente des algorithmes et des heuristiques qui ont été développés avec le langage C++ pour diagnostiquer un réticule du WaferIC. Ces algorithmes peuvent être appliqués sur tous les réticules diagnostiquant ainsi la totalité de la surface active du WaferIC. Le but du diagnostic est de trouver le plus d'éléments fonctionnels possible pour pouvoir configurer la totalité des cellules du réticule.

### **Méthodologie :**

L'idée de base est d'injecter des flux de bits conformes à la norme JTAG étendue selon nos besoins au sein du réticule afin d'établir un ensemble de « chemins » qui seront utilisés par l'algorithme de diagnostic. Les chemins à établir doivent satisfaire à deux conditions :

- Le flux de bits JTAG nécessaire à la création du chemin devrait demeurer petit et de taille acceptable. Pour cela une analyse de complexité temporelle a été dressée dans ce mémoire et

elle en représente une contribution théorique. Cette analyse a montré que la taille d'un flux de bits JTAG nécessaire pour créer (établir) un chemin de  $N$  cellules est de  $2N^2+18N$  bits.

- L'ensemble des chemins doit couvrir la totalité du réticule (c'est-à-dire que chaque cellule et chaque lien est parcouru par au moins un chemin).

Ces deux conditions nous ont amené à comparer deux manières possibles pour couvrir l'ensemble des cellules du réticule : La méthode basée sur des chemins rectangulaires et la méthode basée sur des chemins en serpentins. Suite à l'analyse de complexité temporelle élaborée, la couverture basée sur des chemins rectangulaires a été choisie.

Le diagnostic se fait en trois étapes successives :

Étape 1: Des données sont envoyées à travers les chemins créés (rectangulaires) et la sortie de chacun est comparée à ce qui est attendu. Si les données en sortie correspondent à ce qui est attendu, alors tous les éléments (cellules et liens) constituant le chemin sont caractérisés, par l'algorithme, comme fonctionnels, sinon il existe un ou plusieurs éléments défectueux dans le chemin. Ces chemins non fonctionnels sont sauvegardés dans une liste.

Étape 2 : Afin d'élargir l'espace des éléments fonctionnels, un algorithme de recherche basé sur le principe de la dichotomie est déployé pour localiser le(s) élément(s) défectueux dans les chemins trouvés non fonctionnels (les chemins sauvegardés dans la liste). La recherche de l'élément défectueux se fait au niveau des liens intercellulaires. En effet, l'état des cellules sera déduit à partir des liens : une cellule défectueuse est une cellule ayant tous les liens entrants ou sortants défectueux.

Étape 3 : Des algorithmes heuristiques ont également été développés dans le cas où le lien défectueux n'est pas étroitement repéré par l'algorithme de dichotomie. Ces algorithmes ont pour but d'améliorer la résolution du diagnostic.

Les algorithmes de diagnostic développés ont été testés sur un prototype miniaturisé du WaferIC. Parmi les 1024 cellules du réticule, seulement une zone comportant 4 cellules a été identifiée comme étant une zone potentiellement défectueuse. Le reste du réticule a été trouvé fonctionnel. Des résultats de simulation sont également dressés montrant le comportement de l'algorithme en présence d'un et de plusieurs liens intercellulaires défectueux.

Ce mémoire comporte quatre chapitres et une conclusion :

- Le chapitre 1 est une revue de littérature. Il décrit en détail les fonctionnalités de la plateforme WaferBoard™ ainsi que l'architecture du WaferIC. Dans ce chapitre on y trouve également l'architecture de la chaîne JTAG reconfigurable du WaferIC.

- Le chapitre 2 présente l'analyse de complexité temporelle pour configurer (créer) un chemin de  $N$  cellules ainsi qu'une comparaison entre deux méthodes pour obtenir une couverture du réticule : La méthode par des chemins en serpentins et la méthode par des chemins rectangulaires.

Dans ce chapitre une modélisation des chemins rectangulaires avec le logiciel MATLAB a également été faite.

- Le chapitre 3 présente en détail l'algorithme de recherche de(s) lien(s) défectueux basé sur le principe de la dichotomie. On y trouve également les algorithmes heuristiques développés dans le cas où l'algorithme de dichotomie n'arrive pas à localiser étroitement le lien défectueux.

- Le chapitre 4 présente une étude basée sur des lois probabilistes pour estimer au mieux le nombre de défectuosités qui peuvent être présentes dans un réticule du WaferIC. Ce chapitre résume également les résultats de simulation ainsi que les résultats expérimentaux des algorithmes développés.

- Finalement une conclusion résumant les principales contributions de cette recherche est dressée.

# CHAPITRE 1 REVUE DE LITTÉRATURE

## 1.1 Introduction

Ce présent chapitre est une revue de littérature. Il est constitué essentiellement de cinq sections. La première section traite de quelques limitations des systèmes basés sur des cartes imprimées (PCB) ainsi que les solutions qui sont apparues pour résoudre au mieux ces limitations. Parmi ces solutions on cite les MCM, les SOC, les SIP et les circuits intégrés à l'échelle de la tranche. C'est dans le contexte des circuits intégrés à l'échelle de la tranche qu'est apparu le concept de la technologie WaferIC qui est au cœur du projet de recherche DreamWafer<sup>TM</sup>. Ce projet vise à élaborer une plateforme de prototypage rapide des systèmes électroniques nommée WaferBoard<sup>TM</sup>. Cette plateforme est décrite en détail dans la section 2. Étant donné que la base de ce projet de maîtrise est le diagnostic de la chaîne JTAG au sein du WaferIC, une présentation du protocole JTAG est introduite dans la troisième section. On y trouve une brève description de cette norme ainsi que quelques architectures des chaînes de balayage existantes et quelques techniques de tolérance aux pannes. La quatrième section traite de l'architecture de la chaîne JTAG adoptée au sein du projet afin de configurer et tester les cellules du WaferIC. Finalement, dans les cinquième et sixième sections, la problématique est posée et les contributions de ce mémoire sont soulignées. Les grands titres de la contribution sont l'élaboration d'une analyse de complexité temporelle de diagnostic et le développement des algorithmes de diagnostic de la chaîne JTAG au sein du WaferIC.

## 1.2 Les limitations des systèmes sur PCB

Depuis la découverte du transistor par William Shockley et ses collègues en 1947, la microélectronique n'a pas cessé d'évoluer. Des systèmes de plus en plus complexes et performants sont conçus. Traditionnellement, pour réaliser un système électronique assez complexe, plusieurs circuits intégrés sont rassemblés et interconnectés sur une carte imprimée appelée PCB (*Printed Circuit Board*). Néanmoins plus le système à concevoir est complexe, plus l'utilisation des PCB est laborieuse. En effet, les PCB présentent un certain nombre d'inconvénients, on peut citer par exemple que :

- Plus le nombre de puces à interconnecter est élevé, plus la taille du circuit global est grande et plus le coût de fabrication est élevé.

- Dans les PCB très denses, la phase de test est généralement une tâche ardue. En effet, il est parfois impossible de tester certaines parties du design parce qu'elles sont inaccessibles et cachées sous des couches de métallisation.

- Le routage est difficile à faire dans les PCB très denses.

- Les PCB consomment de l'énergie à cause des délais dans les connexions inter-puces.

- Le temps de conception ainsi que les délais de fabrication d'un système sur PCB est assez long. Les coûts associés aux délais et aux itérations quand un PCB doit être refait plusieurs fois sont considérables.

- Les opérations de déverminage et de test sont difficiles dans un PCB très dense.

Pour pallier les problèmes rencontrés avec les PCB, quelques solutions sont apparues. On peut citer par exemple :

- Les MCM (*multi-chip modules*) où plusieurs puces et circuits intégrés sont montés sur un même substrat. L'ensemble est considéré comme étant un seul module. Ce module résultant sera ensuite soudé sur un PCB afin d'améliorer la densité et la performance. Plusieurs technologies modernes utilisent les MCM comme les processeurs POWER5 et POWER7 d'IBM.

- Les systèmes sur puce (*Systems on chip SOC*) [2]. Cette approche permet de rassembler un ensemble de fonctionnalités diverses sur une même puce. Les composants peuvent être des mémoires, des composants passifs (résistance, capacité), des microprocesseurs, des circuits logiques, analogiques etc... Bien que les systèmes sur puces augmentent considérablement la densité et permettent des gains en performances, connecter des composants qui ne sont pas de même nature peut être assez complexe et coûteux.

- L'approche SIP (*System in package*) permet de rassembler plusieurs puces dans un même boîtier. L'intégration 3D est une forme plus récente des SIP. Elle permet d'occuper moins d'espace et d'augmenter la vitesse et la performance des systèmes électroniques en empilant plusieurs puces verticalement (les unes sur les autres) et en assurant leurs interconnexions à travers des TSV (*Through Silicon Vias*). Cette solution reste limitée par le nombre de puces à empiler.

Les circuits intégrés à l'échelle de la tranche ont vu le jour dans les années 1970 lorsque des technologies à base de semi-conducteurs ont commencé à se développer. Une des promesses des circuits à l'échelle de la tranche est une amélioration de la fiabilité des systèmes complexes à cause d'une réduction du nombre de connexions externes généralement moins fiables que les interconnexions intégrées. En 2009, le système sur tranche (*System on Wafer SoW*) [3] a été introduit. Avec ce concept, les circuits intégrés sont interconnectés à l'aide d'un substrat qui peut être aussi grand qu'une tranche complète qui conduit à la technique dite WLCSP (*Wafer Level Chip Scale Package*). Les avantages majeurs par rapport aux PCB conventionnels, sont l'élimination de plusieurs connexions inter-puces, une augmentation de la densité et une diminution des délais et de la dissipation en lien avec les interconnexions. Dans ce cas, un substrat de Silicium sert de support mécanique et effectue également les interconnexions nécessaires entre les divers composants.

C'est dans le contexte des circuits intégrés à l'échelle de la tranche que le brevet de Richard Norman [4] a été développé en 2006. Ce brevet présente plusieurs innovations en lien avec les circuits intégrés à grande surface, aussi appelés *Large Area Integrated Circuits* (LAIC). Le LAIC qui fait l'objet de recherches dans la présente maîtrise est nommé WaferIC. Les circuits à l'échelle de la tranche rassemblent plusieurs dizaines ou centaines de millions de transistors. Il existe plusieurs types de LAIC. On peut citer par exemple le LAIC monolithique nommé MAXPE9 [5]. Il contient neuf processeurs et sa taille est de  $16.6 \text{ cm}^2$ . Ce circuit est dédié pour des applications de codage vidéo en temps réel. Plus tard, un autre LAIC monolithique [6] a été proposé. Il contient 16 processeurs et 64 Mbits de DRAM. En 2011, un circuit intégré à l'échelle de la tranche à base de transistors en graphène [7] a été proposé. Grâce aux propriétés thermiques et électriques du graphène, de tels circuits intégrés permettraient probablement d'augmenter la fréquence d'opération des systèmes jusqu'à 400GHz. Il existe également des LAIC optoélectroniques constitués de pixels ou bien des LAIC constitués d'éléments capteurs. On trouve aussi des LAIC constitués de réseaux de neurones analogiques [8]. Contrairement aux LAIC précédents [5-8], le WaferIC n'a pas pour but d'améliorer la puissance de calcul ou bien la fréquence d'opération, mais plutôt de permettre une densité d'interconnexion très importante. En effet, c'est un substrat intelligent permettant d'interconnecter plusieurs circuits intégrés, chaque circuit pouvant avoir jusqu'à 2000 broches. Le WaferIC est né dans le cadre du projet de

recherche DreamWafer™ qui vise à élaborer une plateforme de prototypage rapide des systèmes électroniques. La plateforme est nommée WaferBoard™.

### 1.3 Le WaferBoard™

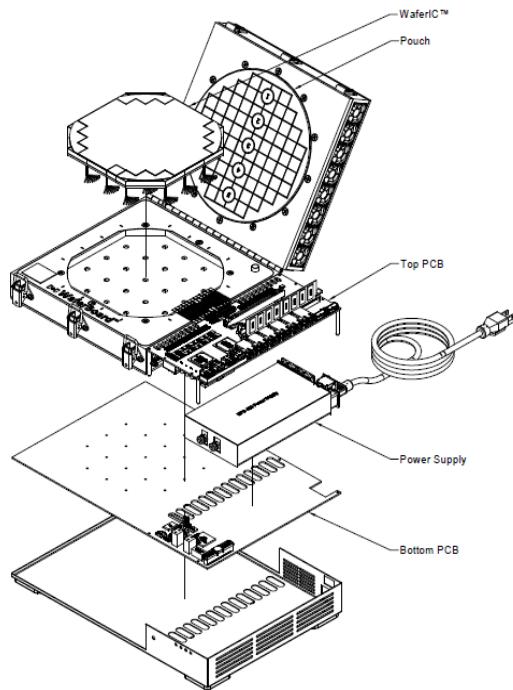

La figure 1-1 illustre les quatre principaux blocs de la plateforme WaferBoard™ : Le WaferIC, le PCB supérieur (*Top PCB*), le module de puissance (*Power supply*) et le PCB inférieur (*Bottom PCB*). Le PCB supérieur fournit une interface externe pour communiquer avec un ordinateur tandis que le PCB inférieur distribue la puissance. La plateforme est constituée d'une tranche entière de Silicium (WaferIC) de 200 mm de diamètre. Avec cette technologie sous-développement, l'utilisateur dépose simplement des circuits intégrés (IC) sur la surface active (WaferIC) puis la plateforme détecte automatiquement les positions des broches et les envoie à l'utilisateur. Ensuite moyennant un logiciel dédié à ce projet, nommé WaferConnect l'utilisateur retourne au WaferIC une *netlist* contenant les interconnexions à faire, que ce soit entre les circuits intégrés eux-mêmes ou entre les circuits et le substrat. Ainsi le réseau d'interconnexion au sein du WaferIC sera configuré selon la demande de l'utilisateur.

Figure 1-1: Modèle éclaté du WaferBoard™ (figure extraite de [9]).

Que les composants électroniques soient de la nouvelle technologie ou non, le WaferBoard™ simplifie le prototypage de tels systèmes électroniques en fournissant tout ce dont les divers composants ont besoin : alimentation, masse, connexions entre les puces et avec le monde externe. Un tel système peut être rapidement testé et modifié. Le WaferBoard™, tel qu'envisagé, permettrait ainsi de réduire considérablement les coûts de développement et de déverminage des systèmes électroniques. Ultimement, cette technologie promet de réduire les temps requis dans les itérations de conception et validation des systèmes complexes.

Le mode d'utilisation du Waferboard™ est assez simple. Le Waferboard™ ressemble à un boîtier. Une fois que le couvercle du boîtier est ouvert, les composants électroniques peuvent être déposés sur le WaferIC. Le système est insensible à l'alignement, c'est-à-dire que les composants peuvent être déposés de façon approximative et pas parfaitement alignés avec les connexions internes. Une fois les composants déposés, le couvercle est bien fermé pour exercer de la pression sur les circuits afin de les maintenir en place. Le WaferIC est un substrat actif, qui comporte des circuits permettant de détecter la présence des billes des puces électroniques et de repérer leurs emplacements. Une fois les billes détectées, la plateforme peut reconnaître les composants déposés sur sa surface si ceux-ci sont dans un catalogue de circuits connus, ce qui est le cas pour la majorité des circuits intégrés présents sur le marché. La plateforme envoie à l'utilisateur, via le logiciel de configuration WaferConnect, une carte permettant de visualiser l'emplacement des circuits et des broches ainsi que des propositions sur la manière de placer les circuits déposés. L'utilisateur confirme l'identité des circuits déposés et spécifie les connexions entre les circuits, que ce soit par la souris ou en important une *netlist*. Le logiciel WaferConnect permet de programmer la plateforme pour implémenter les interconnexions telles que demandées par l'utilisateur. Le prototype est ainsi prêt à fonctionner.

Dans les paragraphes suivants, les principaux éléments du WaferBoard™, à savoir le WaferIC, le WaferNet, le WaferConnect et les PowerBlocks sont décrits en détail.

### 1.3.1 WaferIC

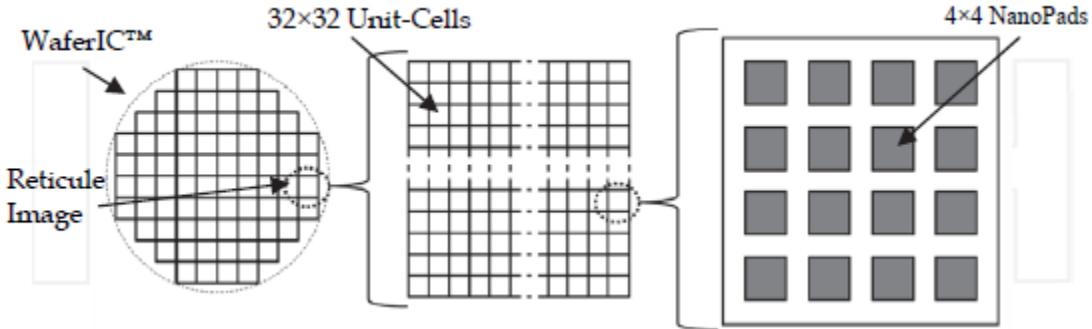

La figure 1-2 décrit l'architecture interne du WaferIC. C'est un circuit intégré à l'échelle de la tranche créée par la photo-répétition de soixante-seize (76) images de réticules par le principe de la photo-lithographie [10]. Chaque réticule contient 1024 (32×32) cellules toutes identiques au niveau physique et ne sont différencierées que par le contenu de leurs mémoires internes. Au total,

le WaferIC contient 77 824 cellules. Chaque cellule contient 16 ( $4 \times 4$ ) plots conducteurs très fins appelés *NanoPads* qui fournissent aux circuits intégrés une tension Vdd stable et régulée ou bien la masse dont ils ont besoin. Le WaferIC contient au total 1, 245,184 *NanoPads*. Grâce à ces *NanoPads*, le WaferIC permet d'alimenter en tension les puces déposées sur sa surface.

Figure 1-2: Zoom au niveau d'un réticule et d'une cellule (figure extraite de [9]).

La base de ce substrat programmable repose sur une technique nommée le "*reticle stitching*"[11]. Cette technique consiste à interconnecter les réticules voisins par une couche de métal définie à partir des masques de photolithographie pour assurer les connexions entre les différents réticules. La surface du WaferIC est égale à  $24\ 500\ mm^2$  et elle est couverte par un tissu conducteur anisotropique appelé film axe- Z (en anglais *Z-axis film*) [12]. Ce film adhésif contient près de 80 millions de fibres conductrices (64 fibres par *NanoPad*) afin d'établir un contact électrique entre les *NanoPads* et les billes des puces déposées sur la surface du WaferIC.

### 1.3.2 WaferNet

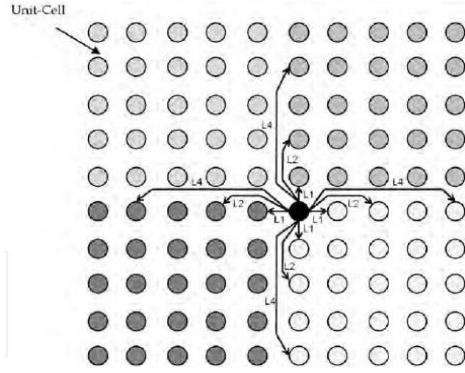

Le WaferNet est le réseau interne reconfigurable du WaferIC. Il a été conçu pour supporter les circuits intégrés les plus utilisés, à savoir les processeurs, les FPGA et les mémoires. C'est en quelque sorte un réseau maillé multidimensionnel qui peut faire un très grand nombre d'interconnexions. La figure 1-3 illustre les interconnexions entre les cellules au sein du WaferNet.

Figure 1-3: Interconnexions au sein du WaferNet (figure extraite de [9]).

Une cellule est liée à sa voisine immédiate mais aussi à des cellules distantes de 2, 4, 6, 8... cellules et ceci dans les quatre directions (Nord, Est, Ouest, et Sud). Chaque cellule contient dans son architecture interne des répéteurs pour préserver l'intégrité du signal des nombreuses interconnexions qui la traverse. Ces répéteurs servent aussi à minimiser les temps de propagation sur les longues interconnexions. Les cellules sont reliées entre elles par ce qu'on appelle des liens intercellulaires. Chaque cellule est dotée d'une porte logique OU en entrée pour sélectionner un lien entrant et d'un démultiplexeur en sortie pour rediriger un lien sortant vers une cellule de destination. Puisque le WaferIC est configuré en utilisant la norme JTAG [1], chaque cellule contient en dehors de sa logique interne, un contrôleur TAP. L'architecture interne d'une cellule unitaire est décrite plus loin dans ce chapitre.

### 1.3.3 PowerBlock

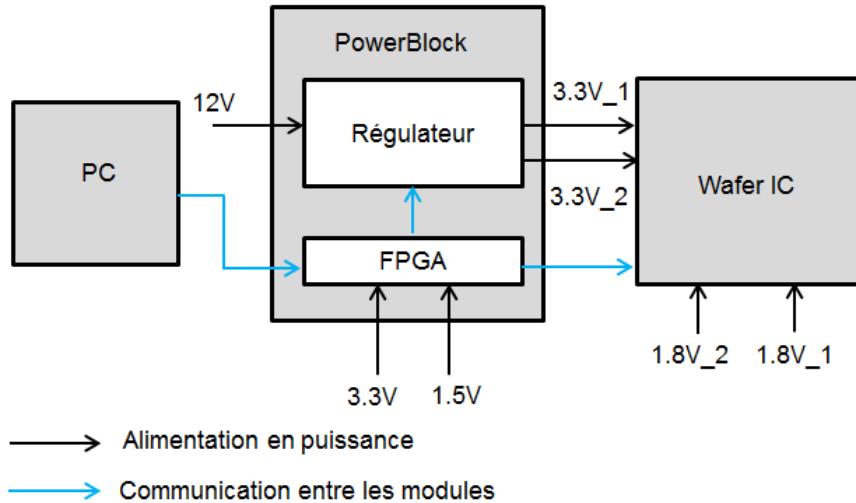

La plateforme contient 21 modules d'alimentation appelés Power blocks qui sont situés sous le WaferIC pour assurer la régulation de la tension. Un Power Block est un PCB de taille 35mm × 35mm qui alimente en tension le WaferIC par l'intermédiaire d'un régulateur de tension (Figure 1-4). Il assure également la communication entre le WaferConnect (logiciel dédié au projet) et le WaferIC moyennant le protocole JTAG et par l'intermédiaire d'un FPGA.

Figure 1-4: Alimentations requises au PowerBlock et au WaferIC.

On retrouve ainsi, sur chaque réticule, cinq « ports » correspondants aux signaux JTAG :

- TCK : signal d'horloge

- TRST : reset

- TMS : signal de commande

- TDI : données entrantes

- TDO : données sortantes

L'alimentation en puissance (VDD3.3, VDD1.8 et GND) et les cinq fils JTAG parviennent au réticule par des trous gravés dans le silicium appelés TSV (*Through Silicon Vias*). Chaque réticule contient 64 TSV. Au total, le WaferIC nécessite 4864 TSV.

### 1.3.4 WaferConnect

Afin d'exploiter les fonctionnalités de la plateforme, une suite d'outils logiciels appelée WaferConnect [13] a été mise en place.

Le flux de travail du logiciel WaferConnect se compose de sept étapes :

1. Démarrer et diagnostiquer la plateforme.

2. Déetecter les points de contact Broche-NanoPad.

3. Reconnaître les circuits déposés.

4. Envoyer une *netlist*.

5. Calculer la longueur des interconnexions.

6. Configurer le réseau.

7. Générer les rapports.

La présentation qui suit élabore brièvement sur chacune de ces étapes.

#### Démarrer et diagnostiquer la plateforme

Une fois que les circuits à interconnecter sont déposés sur le WaferIC, la plateforme est alors alimentée en tension et la phase de diagnostic commence automatiquement. La phase de diagnostic a pour but de localiser les défauts qui peuvent surgir lors de la dernière utilisation de la plateforme.

#### Détecter les points de contact broche-*NanoPad*

Une fois les circuits intégrés déposés sur le WaferIC et que la plateforme a été mise sous tension, le logiciel WaferConnect détecte les contacts entre les broches des circuits à interconnecter et les *NanoPads*. En effet, puisque le WaferIC contient 1 245 184 *NanoPads* de très petite taille une broche déposée sur le WaferIC est en contact avec plusieurs *NanoPads*. Donc une broche crée un court-circuit entre les *NanoPads* sur lesquels elle se pose. Pour détecter les contacts broche-*NanoPad*, chaque *NanoPad* contient un capteur pour repérer les courts circuits avec les *NanoPads* voisins. À peu près un million de détecteurs de court-circuit sont implémentés dans le WaferIC.

#### Reconnaitre les circuits déposés

Un outil de reconnaissance de boîtiers peut à l'aide des informations recueillies lors de la détection des broches et en comparant ces informations avec celles des circuits présents dans une bibliothèque, identifier de façon certaine, ou faire des suggestions à l'utilisateur que ce dernier devrait valider pour confirmer la nature de chacune des puces détectées. Dans le cas où le boîtier (*package*) n'est pas reconnu par le WaferConnect, il est possible d'assigner les broches et d'enregistrer l'information pour une utilisation future.

#### Envoyer une *netlist*

L'utilisateur fournit à la plateforme, à travers le logiciel WaferConnect, une *netlist* contenant les interconnexions à faire entre les différents circuits intégrés déposés sur la surface WaferIC ainsi

que les contraintes à respecter. La *netlist* peut être définie manuellement ou bien importée (par exemple d'un fichier GRB, EDIF, etc.).

#### Calculer les longueurs des interconnexions

Après que la *netlist* soit envoyée à la plateforme, WaferConnect peut calculer la longueur des routes pour configurer les cellules et il peut éventuellement proposer dans certains cas de déplacer certains circuits afin de réduire la longueur des interconnexions.

#### Configurer le réseau

Une chaîne JTAG est envoyée vers la plateforme en passant par un FPGA afin de configurer les cellules qui sont en contact avec des broches. La chaîne JTAG commence par la cellule connectée physiquement au port TDI, parcourt les cellules à configurer, puis se termine par la cellule connectée au port TDO. Lors de la configuration, la chaîne doit éviter de passer par les éléments défectueux repérés lors de l'étape de diagnostic.

#### Générer les rapports

À la fin, des rapports sont générés pour permettre à l'utilisateur de vérifier si le prototypage a été fait conformément aux spécifications demandées ou pas.

## 1.4 Protocole de test avec les chaînes JTAG

### 1.4.1 Brève introduction à la norme JTAG

Étant donné que le test, le diagnostic ainsi que la configuration du WaferIC se basent sur le protocole JTAG, un survol rapide de ce protocole est nécessaire. Dans ce paragraphe, un bref résumé du JTAG est dressé. Pour s'approfondir dans le sujet, le lecteur peut toujours se référer à la dernière version de la norme [1] sortie en 2013 et qui contient de légères modifications par rapport à l'ancienne version [14].

Le standard JTAG (*Joint Test Action Group*) appelé aussi « *Boundary scan* » a été normalisé en 1990 dans le but de faciliter le test des PCB. Aujourd'hui cette norme est utilisée pour tester et programmer des systèmes électroniques de plus en plus complexes. Chaque broche du circuit intégré est connectée à une « cellule JTAG » pour être testée. Ces cellules sont interconnectées par un seul bus formant un registre à décalage. Des données sont envoyées depuis le contrôleur de test à travers le port TDI, parcourent les cellules JTAG et ressortent par le port TDO. Si la

séquence de données au niveau de TDO correspond à la séquence attendue, alors tous les circuits sous test sont fonctionnels. Un tel registre à décalage peut être aussi utilisé pour programmer des FPGA ou des microcontrôleurs. Cinq signaux de contrôle sont à la base du protocole JTAG :

- TMS (Test Mode Select) : C'est le signal qui commande les cellules JTAG. Il sélectionne le mode sous lequel la cellule fonctionne.

- TRST (Test Reset) : C'est un signal de réinitialisation (optionnel).

- TDI : Les données en entrée.

- TDO : Les données en sortie.

- TCK : L'horloge du système.

Plusieurs circuits intégrés compatibles avec la norme JTAG peuvent être interconnectés et testés en liant le TDO sortant d'un circuit au TDI entrant du circuit voisin. Une telle liaison crée une « chaîne JTAG ».

### **1.4.2 Différentes architectures de chaînes JTAG existantes**

La base de ce projet de maîtrise est le diagnostic des défauts au sein d'une chaîne JTAG. Diagnostiquer revient à localiser les pannes détectées lors de la phase de test. Les techniques de test sont donc à la base du diagnostic. Puisque ce projet repose sur une architecture spéciale de la chaîne de balayage, il est donc pertinent de faire un survol rapide des différentes architectures des chaînes de balayage utilisées pour des fins de test.

Plusieurs types de chaînes de balayage existent comme la chaîne serielle complète (en anglais *Full scan chain*) où tous les registres (*Flip-flops*) du circuit sont inclus dans la chaîne. Un problème avec cette chaîne élémentaire, c'est qu'elle peut nécessiter un temps de test relativement long, puisque les données doivent être décalées dans tous les registres du circuit. Comme alternative à l'architecture de chaîne complète, on trouve l'architecture « *Shadow* » où les registres sont dupliqués. Un ensemble de registres est utilisé pour le mode normal du circuit tandis que l'autre ensemble est utilisé pour le test. Les deux modes (normal/test) fonctionnent avec deux horloges séparées. Entre la préparation des données de test et la collecte des données en sortie, le circuit fonctionne en mode normal. Alterner les deux modes permet de gagner en temps de test [15]. D'autres types d'architectures de chaîne existent comme la chaîne partielle qui passe à travers quelques registres seulement. Certes la chaîne partielle réduit le temps de test,

puisque les bits sont décalés dans un nombre réduit de registres, mais le fait de trouver les « bons » registres à inclure dans la chaîne nécessite un traitement topologique du circuit, ce qui peut s'avérer coûteux [16]. Une architecture à chaînes multiples [17] peut aussi être adoptée où les registres sont mis dans des chaînes séparées. Chacune possède sa propre broche d'entrée et sa propre broche de sortie. Comparées à la chaîne serielle élémentaire, les chaînes en parallèle réduisent le temps de test, mais elles nécessitent des broches de test supplémentaires. Dans le cas où les registres ne sont pas de même taille, les chaînes sont dites indépendantes et chacune devrait avoir son propre signal d'horloge.

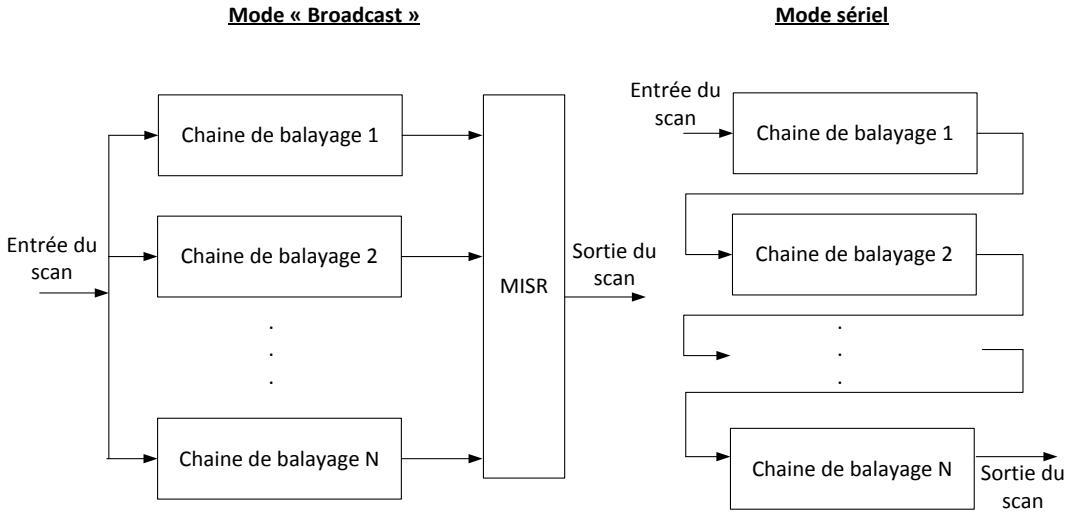

D'autres architectures de chaînes existent comme la chaîne « ILLINOIS » [18] appelée aussi « Broadcast ». L'idée de base de cette architecture est que dans un circuit donné, plusieurs sous modules sont indépendants les uns des autres, donc ils peuvent être testés parallèlement (simultanément) par le même vecteur de test. La figure 1-5 illustre la chaîne de balayage de type ILLINOIS. Le principe est de diviser une longue chaîne de balayage serielle en plusieurs chaînes en gardant la même broche de balayage. Les données provenant des différentes chaînes de balayage sont récupérées dans un MISR (*Multiple Input Signature Register*) pour être compressées. Le fait de connecter plusieurs modules à la même broche de balayage permet de réduire le nombre de broches utilisées. L'architecture ILLINOIS fonctionne en deux modes : Mode « *Broadcast* » et mode sériel. Dans le mode « *Broadcast* » quelques pannes logiques sont non-testables, le mode sériel est alors utilisé pour avoir une couverture quasi totale de toutes les pannes. Une telle architecture réduit le nombre de broches nécessaires pour le test ainsi que la quantité de mémoire requise pour stocker les données. Le temps de test est également réduit par un facteur  $N$  ( $N$  étant le nombre de chaînes).