**Titre:** Traçage logiciel assisté par matériel

Title:

**Auteur:** Adrien Vergé

Author:

**Date:** 2014

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Vergé, A. (2014). Traçage logiciel assisté par matériel [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/1360/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/1360/>

PolyPublie URL:

**Directeurs de recherche:** Michel Dagenais

Advisors:

**Programme:** Génie informatique

Program:

UNIVERSITÉ DE MONTRÉAL

TRAÇAGE LOGICIEL ASSISTÉ PAR MATÉRIEL

ADRIEN VERGÉ

DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

AVRIL 2014

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

TRAÇAGE LOGICIEL ASSISTÉ PAR MATÉRIEL

présenté par : VERGÉ Adrien

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. BOIS Guy, Ph.D., président

M. DAGENAIS Michel, Ph.D., membre et directeur de recherche

Mme NICOLESCU Gabriela, Doct., membre

## REMERCIEMENTS

Je tiens à remercier mon directeur de recherche, Michel Dagenais, pour le parc à vélos qu'il a fait installer devant l'École et qui m'a permis de venir chaque jour 15 minutes plus tôt et avec bonne humeur. Ses conseils, sa disponibilité et son engouement pour le partage des connaissances font du laboratoire DORSAL un environnement de travail convivial et stimulant.

J'aimerais aussi adresser des remerciements à tous mes collègues du laboratoire, tout d'abord pour la très bonne ambiance qui régnait au sein de l'équipe, mais aussi pour le soutien qu'ils apportaient toujours avec le sourire. En particulier, mes travaux ont pu être menés grâce à l'aide de François, Francis, Raphaël, Simon, Suchakra et Yannick, qui ont guidé mes réflexions et fait de ma maîtrise une expérience enrichissante.

Je souhaite aussi remercier nos partenaires Ericsson, EfficiOS ainsi que le Conseil de Recherches en Sciences Naturelles et en Génie du Canada (CRSNG), pour le soutien financier qui a rendu possible ma maîtrise.

Je remercie enfin chaleureusement tous mes proches, amis et rencontres qui ont fait de mon séjour au Québec une expérience inoubliable. Finalement, merci à ma « blonde » qui pensait bien faire en corrigeant mes fautes d'orthographe et qui finalement m'a donné plus de travail.

## RÉSUMÉ

Les logiciels deviennent de plus en plus complexes. Avec l'avènement de l'informatique embarquée, la limitation des ressources les constraint à s'exécuter en économisant le temps, la mémoire et l'énergie. Dans ce contexte, les développeurs ont besoin d'outils pour déboguer et optimiser les programmes qu'ils écrivent. Parmi ces outils, le traçage est une solution particulièrement adaptée qui enregistre l'occurrence d'événements, en interagissant peu avec l'exécution. Elle permet de mettre en évidence les causes de bogues ou les goulots d'étranglement qui ralentissent le programme. LTTng est un traceur focalisé sur les performances : grâce à des structures de données propres à chaque cœur et à des verrous non-bloquants, l'enregistrement d'un événement prend moins d'une microseconde sur une machine récente. Ce délai est toutefois non-négligeable, il empêche de tracer un nombre arbitraire de points sans affecter les performances. De plus, le code et les données liées au traçage sont stockés dans l'espace mémoire du processus étudié, ce qui cause un impact sur son exécution.

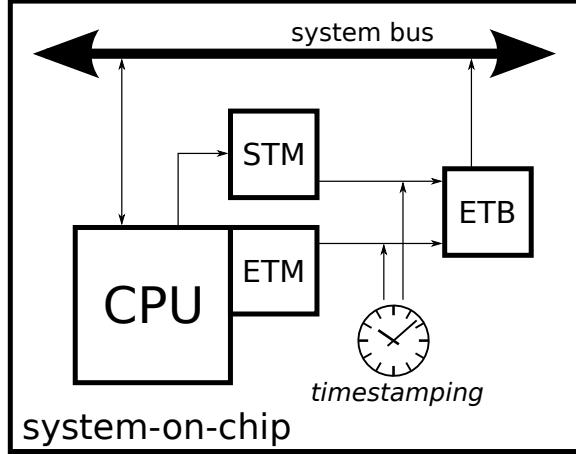

L'utilisation de blocs matériels dédiés au débogage pallie à ces limitations. Il existe une multitude de ces circuits, présents sur la plupart des processeurs du marché, à des fins de débogage et de profilage. En réutilisant leurs capacités à des fins de traçage, nous proposons de soulager la partie logicielle d'outils comme LTTng, et ainsi d'accroître leurs performances. Pour ce faire, nous utilisons les modules matériels STM, ETM et ETB de la suite CoreSight sur les processeurs ARM, ainsi que BTS sur les processeurs x86 d'Intel. Certains offrent une fonctionnalité de traçage d'exécution, c'est-à-dire d'enregistrement de la liste des instructions exécutées ; d'autres fournissent des ressources spécialisées pour l'estampillage de temps, l'envoi de messages sur des canaux dédiés, et le stockage de traces.

Dans ce mémoire, nous proposons des implémentations de traçage logiciel s'aidant du matériel pour être moins intrusifs que les outils purement logiciels. Nous visons à réduire le surcoût en temps engendré par le traçage, c'est-à-dire le nombre de cycles ajoutés à une exécution normale, tout en gardant le même détail d'information que fournit une trace. Nous montrons que l'utilisation conjointe des modules STM et ETB pour faire transiter les traces par des circuits matériels dédiés économise la mémoire du processus et que la durée des points de trace est divisée par dix par rapport à LTTng. En utilisant ETM et ETB, le surcoût du traçage est lui aussi réduit : entre -30% et -50% par rapport à notre traceur de référence. En revanche, les capacités du traceur d'exécution ETM limitent notre système à seulement quelques points de trace enregistrables dans tout le programme. Finalement, l'utilisation de BTS sur les processeurs Intel est aussi plus efficace : les points de trace sont presque deux fois plus rapides que ceux de LTTng. Cependant, ce système ne permet pas de

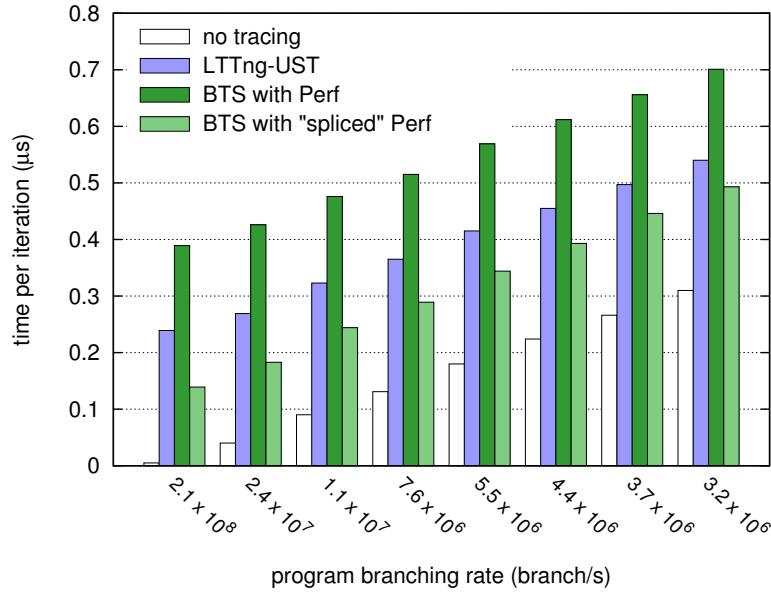

choisir quels événements tracer : tous les branchements pris par le processeur sont enregistrés. Cette lourdeur rend BTS inutilisable pour faire du traçage d'événements ; néanmoins pour du traçage d'exécution, la ré-implémentation que nous proposons est 65% plus rapide que celle de Perf, l'outil par défaut sous Linux.

## ABSTRACT

Software is becoming increasingly complex. With the advent of embedded computing, resource limitations force it to run in a way saving time, memory and energy. In this context, developers need tools to debug and optimize the programs they write. Among these tools, tracing is a particularly well suited solution that records the occurrence of events, while minimally interacting with the execution. It allows to identify the causes of bugs or bottlenecks that slow down the program. LTTng is a tracer focused on performance: through per-core data structures and non-blocking locks, recording an event takes less than one microsecond on a typical computer. However, this delay is not negligible, and tracing an arbitrary number of points is not possible without affecting performance. In addition, the code and data related to tracing are stored in the memory space of the process being studied, causing an impact on its execution.

The use of dedicated debug hardware blocks overcomes these limitations. There are a multitude of these circuits, present on most processors on the market, for of debugging and profiling purposes. By reusing their capacity for tracing purposes, we propose to alleviate the software part of tracing tools such as LTTng, and thereby increase their performance. To do this, we use STM, ETM and ETB hardware modules from the CoreSight suite on ARM processors, as well as BTS on Intel x86 processors. Some offer an execution tracing feature, i.e. recording the list of executed instructions; others provide specialized resources for timestamping, transferring messages on dedicated channels, and storing traces.

In this thesis, we propose implementations of software tracing that take advantage of hardware to be less intrusive than pure-software tools. We aim to reduce the time overhead induced by tracing, i.e. the number of cycles added to a normal execution, while keeping the same detailed information as a trace provides. We show that the combined use of STM and ETB modules to send traces through dedicated hardware circuits saves process memory and that each tracepoint duration is divided by ten as compared to LTTng. Using ETM and ETB, the overhead of tracing is also reduced: between -30% and -50% as compared to our reference tracer. However, the capacity of the ETM execution tracer limits our system to only a few recordable tracepoints throughout the program. Finally, the use of BTS on Intel processors is also more efficient: tracepoints are almost two times faster than LTTng. However, it is not possible to choose which events to trace with this system: all branches taken by the processor are stored. This limitation makes BTS unusable for event tracing; however, for execution tracing the re-implementation we offer is 65% faster than Perf, the default tool on Linux.

## TABLE DES MATIÈRES

|                                                     |     |

|-----------------------------------------------------|-----|

| REMERCIEMENTS . . . . .                             | iii |

| RÉSUMÉ . . . . .                                    | iv  |

| ABSTRACT . . . . .                                  | vi  |

| TABLE DES MATIÈRES . . . . .                        | vii |

| LISTE DES TABLEAUX . . . . .                        | x   |

| LISTE DES FIGURES . . . . .                         | xi  |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .          | xii |

| <br>                                                |     |

| CHAPITRE 1 INTRODUCTION . . . . .                   | 1   |

| 1.1 Définitions et concepts de base . . . . .       | 1   |

| 1.2 Éléments de la problématique . . . . .          | 4   |

| 1.3 Objectifs de recherche . . . . .                | 5   |

| 1.4 Plan du mémoire . . . . .                       | 6   |

| <br>                                                |     |

| CHAPITRE 2 REVUE DE LITTÉRATURE . . . . .           | 7   |

| 2.1 Les infrastructures matérielles . . . . .       | 7   |

| 2.1.1 Traçage d'exécution . . . . .                 | 7   |

| 2.1.2 Traçage d'événements . . . . .                | 13  |

| 2.2 Les traceurs logiciels sous Linux . . . . .     | 17  |

| 2.2.1 Ftrace . . . . .                              | 17  |

| 2.2.2 Perf . . . . .                                | 17  |

| 2.2.3 SystemTap . . . . .                           | 18  |

| 2.2.4 LTTng . . . . .                               | 18  |

| 2.3 Les logiciels s'aidant du matériel . . . . .    | 19  |

| 2.3.1 Perf et BTS . . . . .                         | 19  |

| 2.3.2 Linux et ETM . . . . .                        | 20  |

| 2.3.3 Outils à source fermée . . . . .              | 21  |

| 2.4 Conclusion de la revue de littérature . . . . . | 22  |

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| CHAPITRE 3 MÉTHODOLOGIE . . . . .                                                | 23 |

| 3.1 Environnement de travail . . . . .                                           | 23 |

| 3.1.1 Station de contrôle . . . . .                                              | 23 |

| 3.1.2 Machine de test Intel x86 . . . . .                                        | 24 |

| 3.1.3 Machine de test Beagleboard-xM . . . . .                                   | 25 |

| 3.1.4 Machine de test Pandaboard . . . . .                                       | 25 |

| 3.2 Traçage d'une application . . . . .                                          | 26 |

| 3.2.1 Définition du surcoût . . . . .                                            | 26 |

| 3.2.2 Mesure du surcoût . . . . .                                                | 26 |

| CHAPITRE 4 ARTICLE 1 : HARDWARE-ASSISTED SOFTWARE EVENT TRACING . . . . .        | 29 |

| 4.1 Introduction . . . . .                                                       | 30 |

| 4.2 Related work . . . . .                                                       | 30 |

| 4.2.1 Software tracing . . . . .                                                 | 31 |

| 4.2.2 Hardware-assisted tracing . . . . .                                        | 32 |

| 4.2.3 Other tracing hardware . . . . .                                           | 33 |

| 4.2.4 Existing use of CoreSight and BTS . . . . .                                | 33 |

| 4.3 Test environments . . . . .                                                  | 34 |

| 4.3.1 ARM CoreSight . . . . .                                                    | 35 |

| 4.3.2 Intel . . . . .                                                            | 36 |

| 4.3.3 Measuring the overhead of tracing . . . . .                                | 36 |

| 4.4 Using system tracing hardware . . . . .                                      | 37 |

| 4.4.1 System Trace Macrocell . . . . .                                           | 38 |

| 4.5 Using execution path tracing hardware . . . . .                              | 41 |

| 4.5.1 Embedded Trace Macrocell . . . . .                                         | 41 |

| 4.5.2 Branch Trace Store . . . . .                                               | 42 |

| 4.6 Conclusion and future work . . . . .                                         | 46 |

| CHAPITRE 5 RÉSULTATS COMPLÉMENTAIRES . . . . .                                   | 48 |

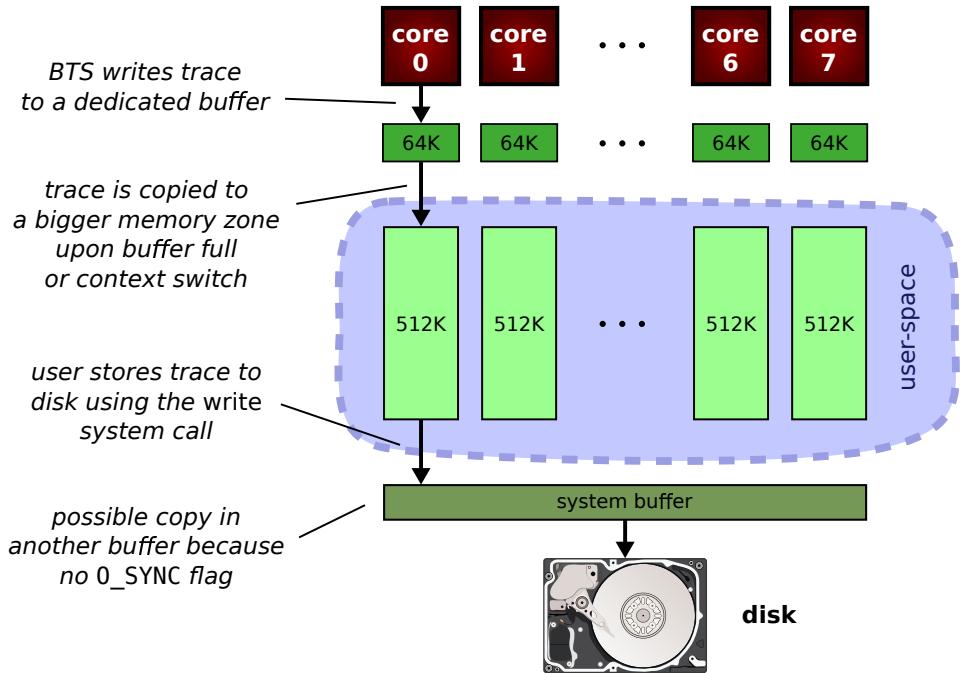

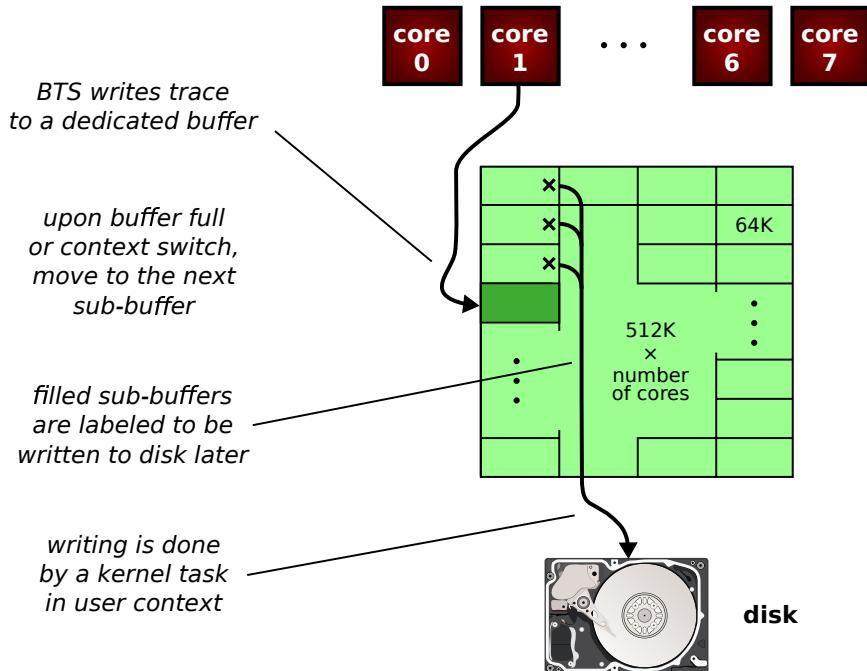

| 5.1 Double copie dans l'ABI Perf avec BTS . . . . .                              | 48 |

| 5.1.1 Étude de l'implémentation originale . . . . .                              | 48 |

| 5.1.2 Ré-implémentation sans double copie . . . . .                              | 49 |

| 5.2 Taux de branchement . . . . .                                                | 50 |

| 5.2.1 Taux de branchement de programmes usuels . . . . .                         | 50 |

| 5.2.2 Programmes à taux de branchement arbitraires . . . . .                     | 51 |

| 5.3 Modification du noyau Linux pour un traçage avec ETM plus flexible . . . . . | 51 |

|                                                                    |    |

|--------------------------------------------------------------------|----|

| 5.4 Rétro-ingénierie du format STP . . . . .                       | 52 |

| CHAPITRE 6 DISCUSSION GÉNÉRALE . . . . .                           | 54 |

| 6.1 Impact des résultats . . . . .                                 | 54 |

| 6.1.1 Traçage d'événements avec STM . . . . .                      | 54 |

| 6.1.2 Traçage d'événements avec ETM . . . . .                      | 55 |

| 6.1.3 Traçage d'exécution avec BTS . . . . .                       | 55 |

| 6.2 Intégration dans LTTng . . . . .                               | 56 |

| 6.2.1 Utilisation des ressources . . . . .                         | 56 |

| 6.2.2 Choix dynamique de l'utilisation du matériel dédié . . . . . | 56 |

| 6.2.3 Décodage des traces . . . . .                                | 57 |

| 6.2.4 Architecture . . . . .                                       | 58 |

| CHAPITRE 7 CONCLUSION ET RECOMMANDATIONS . . . . .                 | 59 |

| 7.1 Synthèse des travaux . . . . .                                 | 59 |

| 7.2 Limitations des solutions proposées . . . . .                  | 60 |

| 7.3 Améliorations futures . . . . .                                | 61 |

| RÉFÉRENCES . . . . .                                               | 63 |

**LISTE DES TABLEAUX**

|             |                                                                     |    |

|-------------|---------------------------------------------------------------------|----|

| Tableau 2.1 | Principales solutions matérielles de traçage d'exécution . . . . .  | 9  |

| Tableau 2.2 | Principales solutions matérielles de traçage d'événements . . . . . | 14 |

| Tableau 3.1 | Caractéristiques de l'ordinateur de bureau . . . . .                | 24 |

| Tableau 3.2 | Caractéristiques de la Beagleboard-xM . . . . .                     | 25 |

| Tableau 3.3 | Caractéristiques de la Pandaboard . . . . .                         | 25 |

| Tableau 5.1 | Surcoût décomposé des étapes du traçage avec Perf et BTS . . . . .  | 49 |

| Tableau 5.2 | Taux de branchement de programmes usuels . . . . .                  | 51 |

## LISTE DES FIGURES

|            |                                                                                                                  |    |

|------------|------------------------------------------------------------------------------------------------------------------|----|

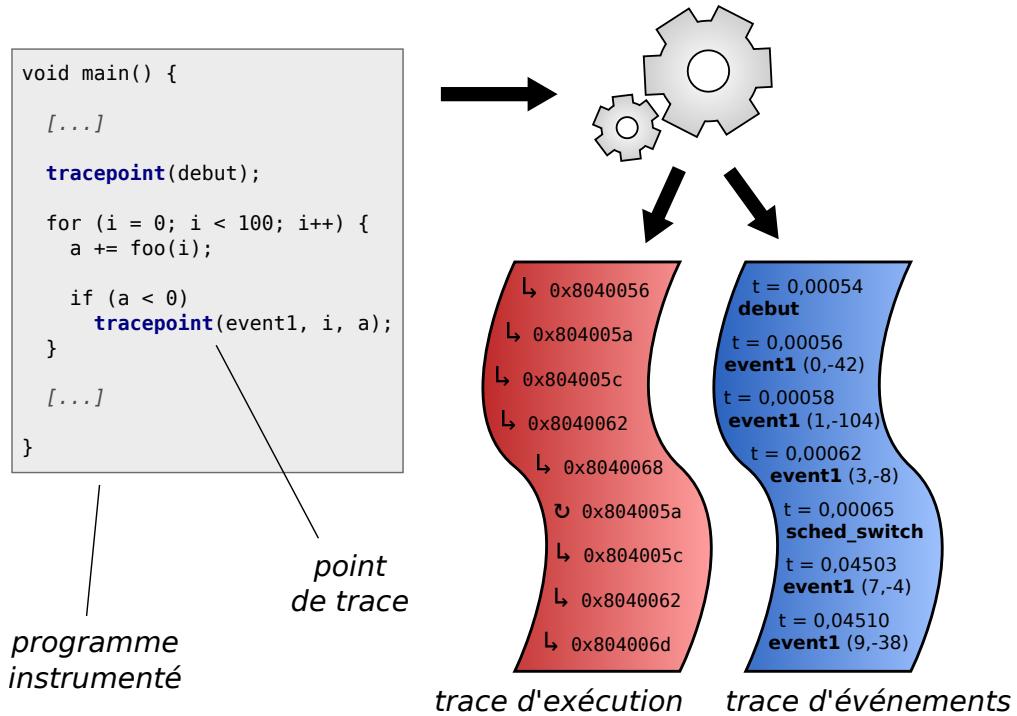

| Figure 1.1 | Différence entre trace d'exécution et une trace d'événements . . . . .                                           | 3  |

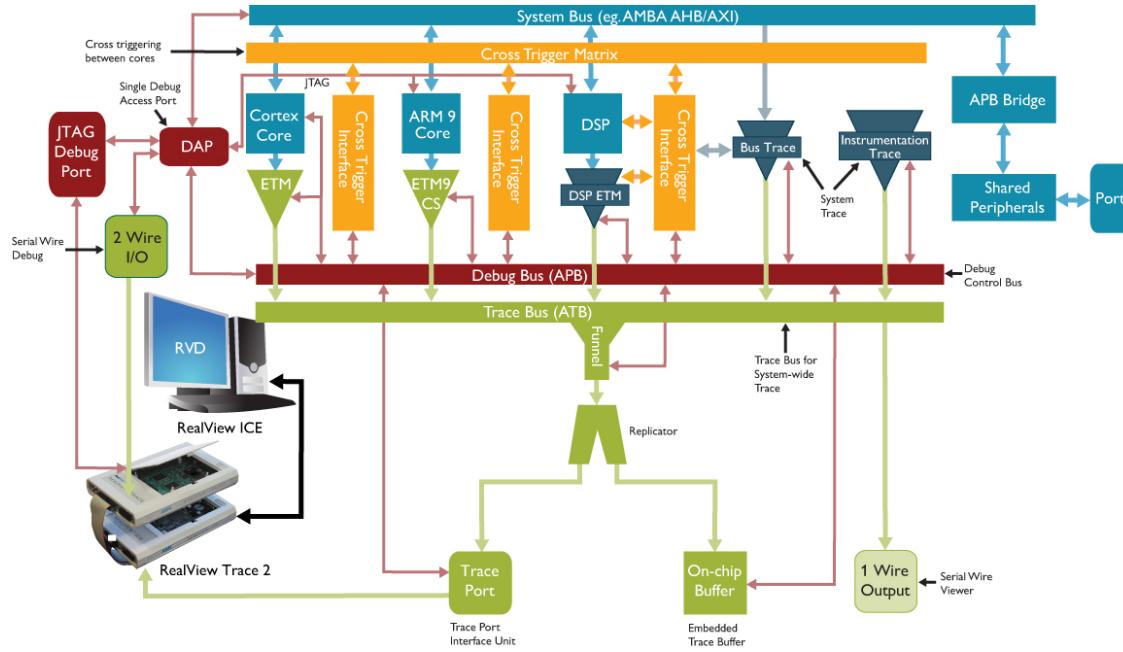

| Figure 2.1 | Vue générale des macrocellules de CoreSight . . . . .                                                            | 12 |

| Figure 3.1 | Photographies des machines de test . . . . .                                                                     | 24 |

| Figure 4.1 | Overview of the CoreSight components used . . . . .                                                              | 36 |

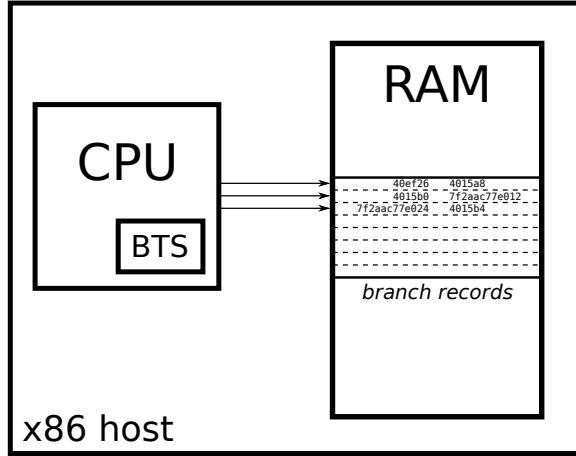

| Figure 4.2 | Overview of Intel Branch Trace Store . . . . .                                                                   | 37 |

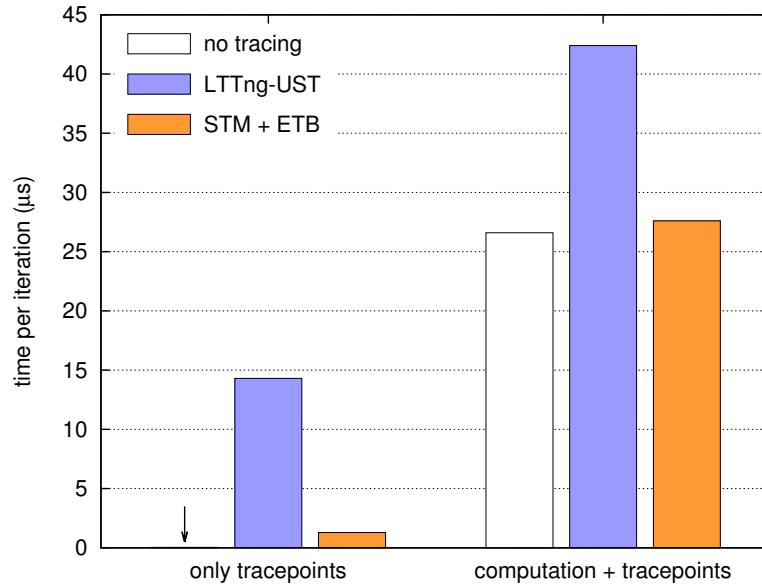

| Figure 4.3 | Comparison of tracing with LTTng-UST, with hardware (STM+ETB)<br>and no tracing w.r.t. event frequency . . . . . | 40 |

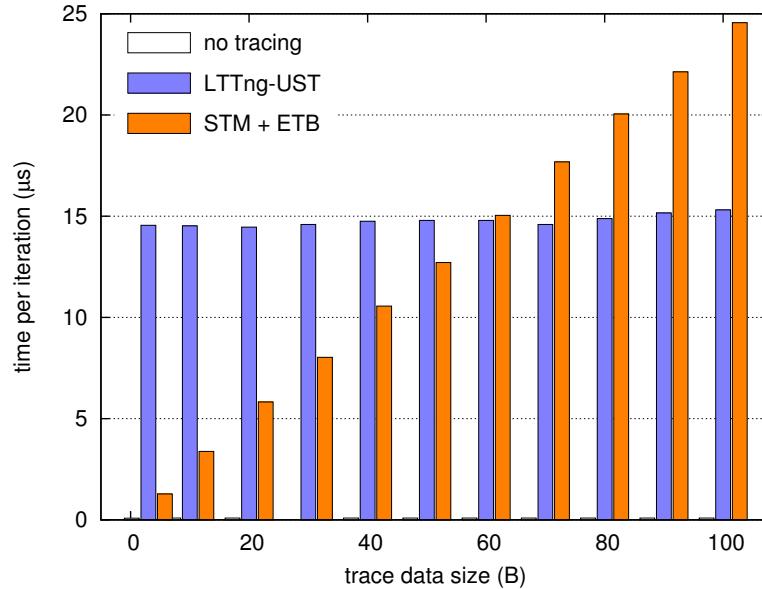

| Figure 4.4 | Comparison of tracing with LTTng-UST, with hardware (STM+ETB)<br>and no tracing w.r.t. payload size . . . . .    | 40 |

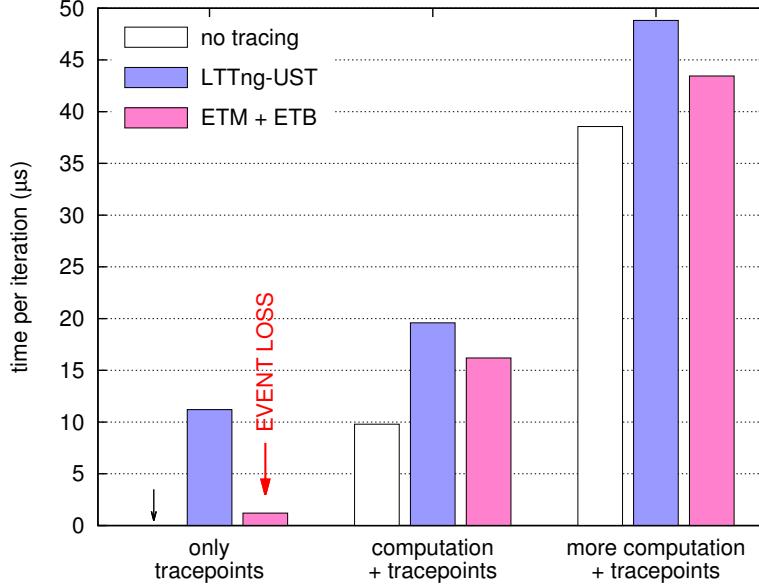

| Figure 4.5 | Comparison of tracing with LTTng-UST, with hardware (ETM+ETB)<br>and no tracing . . . . .                        | 43 |

| Figure 4.6 | Operation of Perf and BTS in the original implementation . . . . .                                               | 45 |

| Figure 4.7 | Operation of Perf and BTS in our new “splice” implementation . . . . .                                           | 45 |

| Figure 4.8 | Comparison of tracing with LTTng-UST, with hardware (BTS) and<br>with our “splice” implementation . . . . .      | 46 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|         |                                                             |

|---------|-------------------------------------------------------------|

| ABI     | Application Binary Interface                                |

| AHB     | Advanced High-performance Bus                               |

| AXI     | Advanced eXtensible Interface                               |

| BTS     | Branch Trace Store                                          |

| CPU     | Central Processing Unit                                     |

| CR3     | Control Register number 3 (processeurs x86)                 |

| CTF     | Common Trace Format                                         |

| DDR     | Double Data Rate                                            |

| DebugFS | Debug File System                                           |

| DNS     | Domain Name System                                          |

| DORSAL  | Distributed Open Reliable Systems Analysis Lab              |

| ETB     | Embedded Trace Buffer                                       |

| ETM     | Embedded Trace Macrocell                                    |

| FIFO    | First In, First Out                                         |

| HTM     | AHB Trace Macrocell                                         |

| ITM     | Instrumentation Trace Macrocell                             |

| JTAG    | Joint Test Action Group                                     |

| LBR     | Last Branch Record                                          |

| LKML    | Linux Kernel Mailing List                                   |

| LPDDR   | Low Power Double Data Rate                                  |

| LTT     | Linux Trace Toolkit                                         |

| LTTrng  | Linux Trace Toolkit next generation                         |

| MD5     | Somme de contrôle Message Digest 5                          |

| MIPI    | Mobile Industry Processor Interface                         |

| MSR     | Model-Specific Register                                     |

| NFS     | Network File System                                         |

| NSERC   | Natural Sciences and Engineering Research Council of Canada |

| OMAP    | Open Multimedia Applications Platform                       |

| OS      | Operating System                                            |

| PID     | Process IDentifier                                          |

| PMU     | Performance Monitoring Unit                                 |

| PT      | Processor Trace                                             |

| PTM     | Program Trace Macrocell                                     |

|        |                                                         |

|--------|---------------------------------------------------------|

| PXE    | Pre-boot eXecution Environment                          |

| RAM    | Random-Access Memory                                    |

| RCU    | Read-Copy Update                                        |

| SDRAM  | Synchronous Dynamic Random Access Memory                |

| SHA256 | Somme de contrôle Secure Hash Algorithm à 256 bits      |

| SSH    | Secure Shell                                            |

| STM    | System Trace Module ou System Trace Macrocell           |

| STP    | System Trace Protocol                                   |

| SWIT   | Software Instrumentation Trace                          |

| SysFS  | Système de fichiers virtuel pour le contrôle du système |

| TFTP   | Trivial File Transfer Protocol                          |

| TI     | Texas Instruments                                       |

| TMC    | Trace Memory Controller                                 |

| TMF    | Tracing and Monitoring Framework                        |

| VDSO   | Virtual Dynamically linked Shared Objects               |

## CHAPITRE 1

### INTRODUCTION

Dans les domaines nécessitant des logiciels optimisés pour s'exécuter le plus rapidement possible et consommer moins de ressources (serveurs à haute disponibilité, centres de calcul, applications embarquées), le traçage est une solution efficace pour améliorer le logiciel. Ce procédé d'enregistrement d'événements à certains points d'intérêt du système d'exploitation et du logiciel permet d'avoir des renseignements très précis sur les conditions de l'exécution. Ils mettent en évidence les problèmes à bas niveau tels qu'une mauvaise gestion de la mémoire, mais aussi ceux à plus haut niveau tels que l'accès concurrent à une ressource partagée. Les traces sont alors très utiles pour aider les développeurs à corriger des erreurs et accélérer leurs applications.

Les outils de traçage d'événements sont optimisés pour influer le moins possible sur les logiciels tracés. Pourtant, ils interfèrent quand même avec l'exécution car l'enregistrement des points de trace nécessite au minimum l'exécution de code supplémentaire et la réservation de mémoire. L'utilisation de ressources matérielles dédiées est une solution pour contourner ces coûts. La plupart des processeurs récents embarquent des circuits spécialisés dans le débogage, dont l'usage peut être adapté ou détourné afin d'assister les traceurs logiciels dans leur tâche.

#### 1.1 Définitions et concepts de base

Dans cette section, nous introduisons différents concepts qui seront utilisés tout au long de ce mémoire.

#### Événements et points de trace

Un **événement** est un point précis de l'exécution d'un programme, auquel sont associées une date et la production d'une action. La date fixe l'occurrence de l'action dans le temps, et est généralement représentée sous la forme d'une estampille de temps (*timestamp*). L'action associée, quant à elle, précise le type d'événement enregistré. Cela peut être un appel système, une interruption, ou l'appel d'une fonction spécifique. Lors de leur enregistrement, les événements peuvent être accompagnés de valeurs donnant des informations sur l'état du programme à ce moment précis. Il peut s'agir de l'identifiant du processus, du nombre de cycles écoulés, etc. Ces données additionnelles sont appelées « contexte ».

Dans la pratique, les événements sont enregistrés par des **points de trace**, caractérisés

par des emplacements précis dans le code du programme ou du système d'exploitation. L'atteinte d'un tel emplacement provoque l'enregistrement de l'événement correspondant dans une trace.

## Trace

Il faut distinguer deux concepts caractérisés par la même appellation :

1. Une **trace d'événements** rassemble une succession d'événements (tels que définis dans le paragraphe précédent). Elle enregistre les points marquants de la vie d'un programme ou d'un système pour permettre son étude ultérieure. Contrairement à l'écriture de fichiers journaux (*logs*), le traçage d'événements se veut très léger, pour ne pas interférer avec l'exécution normale du programme. Alors que la journalisation induit de fortes latences (notamment à cause du coût de l'accès disque), l'enregistrement de traces affecte beaucoup moins les performances grâce à un format compact et des mécanismes optimisés. Le traçage permet ainsi l'enregistrement de plusieurs milliers d'événements par seconde.

2. Une **trace d'exécution** liste les adresses de toutes les instructions exécutées par le processeur. Il s'agit d'une information exhaustive, beaucoup plus complète qu'une trace d'événements : on peut retracer la vie d'un programme dans sa totalité. Enregistrer un tel volume de données a néanmoins un coût important en termes de dégradation de performance et de quantité de trace à stocker, ce qui rend le traçage d'exécution en continu inapplicable en production. Toutefois, ce procédé peut être utilisé par intermittence pour tracer des portions spécifiques de code.

La figure 1.1 illustre la différence entre traçage d'exécution et traçage d'événements. Elle montre que pour une même exécution, les deux types de trace ne fournissent pas les mêmes données.

Notre recherche se concentre sur le **traçage d'événements**. Pour cette raison, dans la suite de ce mémoire, les termes « traçage » et « trace » feront référence au traçage d'événements. Cependant, nous présenterons différents outils matériels dont certains sont conçus pour faire du **traçage d'exécution** ; dans ce cas nous utiliserons l'appellation complète pour clarifier.

## Instrumentation

L'**instrumentation** est la technique consistant à modifier un logiciel pour enregistrer des événements. En pratique, elle consiste en l'ajout de points de trace dans le code du programme ou du noyau de système d'exploitation tracé. Nous verrons que l'instrumentation

Figure 1.1 Différence entre trace d'exécution et une trace d'événements

n'est parfois pas nécessaire pour tracer un logiciel, car certains modules matériels permettent de détecter le passage par des points spécifiques du programme.

## Surcoût

Le **surcoût** (*overhead*) d'une méthode de traçage est l'ensemble des modifications qu'elle provoque sur l'exécution du programme tracé. Sauf conditions exceptionnelles, ces modifications sont néfastes pour les performances du programme, d'où la qualification de « surcoût ». Elles comprennent entre autres une pollution de l'espace mémoire du programme, des ajouts dans le code exécuté, des interruptions supplémentaires et une consommation d'énergie accrue. Tous ces désagréments résultent en général en une augmentation du temps d'exécution, c'est pourquoi on utilise souvent le terme « surcoût » comme raccourci pour « surcoût temporel ».

Les concepteurs d'outils de traçage cherchent à le minimiser. Les valeurs typiques des surcoûts temporels des traceurs logiciels peu intrusifs sont inférieures à une microseconde par point de trace. Notre recherche vise à trouver des méthodes pour limiter l'impact du traçage, c'est-à-dire à en réduire le surcoût.

## Matériel dédié

Nous utilisons les termes circuit matériel dédié ou **matériel dédié** pour désigner les ressources physiques embarquées sur une puce électronique pour assister une tâche particulière. De tels composants spécialisés sont aujourd’hui présents sur presque tous les nouveaux processeurs et systèmes sur puce, par exemple pour accélérer le calcul de sommes de contrôle ou traiter des flux vidéos.

Ceux qui nous intéressent sont conçus pour le débogage, le traçage et la mesure des performances. En pratique, il va s’agir de tampons de mémoire, de comparateurs d’adresses ou encore de générateurs d’estampilles de temps, dont la fonction est effectuée plus rapidement par matériel que par logiciel. Notre but est d’utiliser les capacités offertes par ce matériel dédié pour accélérer l’enregistrement de traces d’événements.

### 1.2 Éléments de la problématique

Des solutions matérielles de débogage et de profilage ont été proposées depuis les années 1970. Alors que les premières n’existait que sous la forme de modules coûteux et peu répandus, de nouveaux circuits ont lentement pris place dans les processeurs destinés au grand public, notamment des compteurs de performance qui établissent des statistiques sur l’utilisation des processeurs et de la mémoire. Depuis une dizaine d’années, on assiste à une inclusion quasi-systématique de modules matériels de traçage d’exécution : *Last Branch Record*, *Branch Trace Store* et *Processor Trace* chez Intel, *Embedded Trace Macrocell* et *Program Trace Macrocell* sur les systèmes ARM, ou encore *Nexus Trace* dans les processeurs de Freescale. Plus récemment, des éléments matériels pour accélérer le traçage d’événements ont fait leur apparition : *Instrumentation Trace Macrocell*, *System Trace Module* et d’autres sont présents sur des puces largement répandues. Avec le développement de l’informatique embarquée, friande de débogage et de profilage pour économiser des ressources limitées, on risque de voir ce phénomène s’accroître davantage.

Les outils de traçage logiciel connaissent quant à eux un usage de plus en plus répandu, dû à la fois à une intrusivité de plus en plus faible et à une simplicité d’utilisation grandissante. Des fonctions spécifiques au traçage logiciel sont aujourd’hui présentes dans le code de nos systèmes d’exploitation. Cependant, l’impact du traçage n’est pas nul : l’exécution d’un programme tracé est altérée par les quelques dixièmes de microseconde pris par chaque point de trace. Ce surcoût a plusieurs facteurs, principalement l’exécution de code supplémentaire pour l’enregistrement des points de trace, mais aussi des appels système induits par le calcul des estampilles de temps (si l’appel `gettimeofday` n’est pas implémenté en VDSO) ou par les fautes de page si les données de trace ont été évincées de la mémoire principale. À cause

de ces désagréments, le nombre d'actions enregistrables est limité et il n'est pas possible de tracer un nombre arbitraire d'événements sans induire un ralentissement.

Là où les solutions purement logicielles ne peuvent plus rien améliorer car elles sont déjà optimisées au maximum, l'emploi de matériel dédié peut s'avérer efficace. Pour réduire encore l'impact du traçage d'événements, certaines étapes logicielles peuvent être accélérées par des modules matériels, à condition que ceux-ci comprennent des ressources adaptées. En effet, la plupart sont conçus pour du débogage et non du traçage, et doivent être reconfigurés pour les détourner de leur usage principal. Toutes leurs fonctionnalités matérielles ne seront pas forcément utilisées, et certaines pourront même être remaniées afin de mieux répondre aux besoins du traçage. Enfin, les traceurs logiciels n'étant pas faits pour utiliser ces ressources, leur architecture doit être repensée pour intégrer ces modifications. De plus, chaque élément matériel étant spécifique à une plateforme, les données qu'ils apportent diffèrent. Tous ces éléments de problématique demandent une étude rigoureuse, notamment pour concevoir un système unifiant les différents types de traces matérielles en un format commun.

### 1.3 Objectifs de recherche

Dans le contexte présenté dans la section précédente, le déroulement de la maîtrise était axé autour de la question de recherche suivante :

*L'utilisation du matériel dédié au débogage présent dans les processeurs récents permet-il de réduire l'impact du traçage d'événements par logiciel ?*

Pour répondre à cette problématique, nous avons défini les objectifs de recherche suivants :

1. Dresser une liste des modules matériels potentiellement intéressants.

2. Étudier les caractéristiques techniques de chaque infrastructure matérielle pour déterminer les possibilités en termes de traçage.

3. Pour les modules retenus, proposer des implémentations tirant profit du matériel tout en donnant un résultat équivalent au traçage purement logiciel.

4. Évaluer les différences de performance apportées par ces modifications.

L'ensemble de ces objectifs a pour but de répondre à la question de recherche, et si possible de proposer des améliorations pour les solutions de traçage existantes. Si ces améliorations sont efficaces, un objectif complémentaire est de les intégrer au traceur LTTng.

## 1.4 Plan du mémoire

Au chapitre 2, nous présentons une revue de littérature faisant le point sur le matériel dédié au débogage, profilage et traçage, ainsi que sur les solutions logicielles de traçage d'événements. Le chapitre 3 décrit notre démarche de recherche en présentant la méthodologie employée pour obtenir les résultats de l'article de revue « *Hardware-Assisted Software Event Tracing* » au chapitre 4. Certains résultats complémentaires ne sont pas inclus dans l'article mais détaillés au chapitre 5. Enfin, le chapitre 6 discute nos travaux et la portée de nos résultats, tandis que le chapitre 7 conclut notre mémoire et envisage de futures évolutions.

## CHAPITRE 2

### REVUE DE LITTÉRATURE

#### 2.1 Les infrastructures matérielles

Depuis les premiers programmes informatiques, la recherche de la cause des erreurs et leur résolution ont fait naître de nombreuses techniques de débogage qui permettent de s’imiscer dans l’exécution du processus et éventuellement d’interagir avec celui-ci. De nos jours, ces techniques peuvent aussi servir pour faire du profilage et optimiser les performances des programmes. Tout ceci peut aussi être fait de manière logicielle, ce qui nécessite une modification du code originel, ou au moins, une altération de l’exécution. Cela a pour conséquence de ne pas observer le programme étudié dans son état normal, et peut conduire aux fameux *heisenbugs* (bogues qui ne se manifestent plus lorsqu’on active le débogage). Pour éviter ces désagréments, de nombreuses solutions matérielles ont été imaginées. Aujourd’hui, elles existent sur la plupart des processeurs grand public.

Les systèmes matériels que nous avons étudiés se divisent en deux catégories : les traceurs d’exécution, qui enregistrent les adresses des instructions exécutées, et les traceurs d’événements, dont le but est d’accélérer l’enregistrement de points de trace déclenchés par logiciel.

##### 2.1.1 Traçage d’exécution

Le traçage du flot d’exécution fut l’une des premières solutions de débogage. Dès les années 1970, des articles et brevets décrivent des architectures pour intégrer de nouveaux circuits dans les processeurs, afin d’enregistrer des informations sur l’exécution [53, 11]. Introduite sous les noms de traçage d’instruction (*instruction tracing*), traçage de programme (*program tracing*) ou traçage d’exécution (*execution tracing*), cette technique consiste à enregistrer les adresses des instructions exécutées par un processeur. La liste de ces adresses, corrélée avec la connaissance du code binaire tracé, permet de reconstituer le flot de contrôle pendant une exécution donnée. Une telle information peut servir à des fins de simple débogage, pour s’assurer que le déroulement d’un programme s’effectue normalement ou déterminer la cause d’un dysfonctionnement. Lorsque des données temporelles sont ajoutées à la trace, par exemple des estampilles de temps (*timestamps*) placées à intervalles réguliers, on peut aussi procéder à l’évaluation des performances du programme et faire du profilage [14].

Compte tenu du volume des traces générées, le choix de la destination de stockage est crucial. Alors que certaines implémentations choisissent de la mémoire sur la puce, certaines

stockent les traces en mémoire principale (RAM). D'autres exportent ces données en dehors de la machine, *via* une connexion JTAG [24], ce qui a l'avantage de ne pas modifier l'utilisation des ressources de la machine tracée. De manière à réduire la taille des traces et la bande passante consommée, certains modules matériels n'enregistrent que les déviations au flot normal d'exécution, ce qui évite de tracer le passage évident d'une adresse à la celle qui la suit immédiatement. D'autres réduisent encore le nombre d'instructions tracées, considérant par exemple que les branchements inconditionnels et les appels de fonctions peuvent être déduits de l'analyse statique du programme. Certains blocs matériels plus récents comme CoreSight ETM [2] optimisent l'encodage des traces pour réduire la production à environ 1 bit par cycle [7]. Enfin, des propositions pas encore implémentées intègrent un véritable système de compression qui permet de réduire la taille des données générées jusqu'à 454 fois [30], ou encore repensent l'architecture de traçage pour arriver à 0,15 bit par instruction [59].

Il est important de préciser que la plupart des solutions matérielles de traçage d'exécution supposent que l'utilisateur a connaissance du binaire exécuté, et peut lier chaque adresse d'exécution à l'instruction correspondante dans le code binaire. Ainsi, les traceurs matériels présentés ici ne sauvegardent jamais des instructions, mais leurs adresses, ce qui permet un encodage beaucoup plus compact.

L'ensemble de solutions matérielles de traçage présentées dans cette section est résumé dans le tableau 2.1.

### Branch Trace Store (BTS) d'Intel

Sur les processeurs Intel, les unités de contrôle de performance (PMU) sont familières aux développeurs, notamment grâce à leur prise en charge par des outils de profilage comme Perf. Ces derniers permettent de calculer des statistiques sur des grandeurs comme le nombre d'instructions exécutées ou l'occurrence de fautes de cache. Pourtant, elles ne constituent pas l'ensemble des solutions de débogage : d'autres ressources sont à disposition, en particulier pour les traceurs.

La fonctionnalité *Branch Trace Store* permet de faire du traçage d'exécution. Après avoir configuré une zone tampon de taille arbitraire en mémoire principale, le processeur sauvegarde chaque branchement pris dans un enregistrement de 24 octets comprenant l'adresse de départ, celle de destination, ainsi que des drapeaux (*flags*) de contexte. Elle est présente sur les nouveaux processeurs d'Intel implémentant les registres MSR depuis le Pentium 4 [28]. Une interruption peut être soulevée en cas de dépassement d'un certain seuil de remplissage du tampon.

BTS étant initialement prévu pour tracer de petites portions de code, il présente de sérieuses limitations en termes de performance. En effet, il ne permet pas de limiter l'en-

Tableau 2.1 Principales solutions matérielles de traçage d'exécution

| Nom           | Plateforme | Compression | Stockage dans tampon dédié | Stockage en mémoire principale | Export <i>via</i> JTAG | Documentation disponible | Depuis     |

|---------------|------------|-------------|----------------------------|--------------------------------|------------------------|--------------------------|------------|

| BTS           | Intel      |             |                            | ✓                              |                        | ✓                        | 2000       |

| LBR           | Intel      |             | ✓                          |                                |                        | ✓                        | 2000       |

| PT            | Intel      | ✓           | ✓                          | ✓                              |                        | ✓                        | pas encore |

| Program Trace | Freescale  | ✓           | ✓                          | ✓                              | ✓                      |                          | 2010       |

| CoreSight ETM | ARM        | ✓           | ✓                          |                                | ✓                      | ✓                        | 1999       |

| CoreSight PTM | ARM        | ✓           | ✓                          |                                | ✓                      | ✓                        | 2008       |

registrement des branchements à une fonction ou à un processus donné, ni à un type de branchement particulier, ce qui produit un nombre très élevé d'enregistrements. De plus, l'encodage de ces entrées n'étant pas optimisé (ce qui pourrait par exemple être fait en n'encodant que des décalages (*offsets*) d'adresses), leur poids est de 24 octets, ce qui contribue à la production de traces très volumineuses. La taille des données de trace entraîne de nombreux effets néfastes comme une pollution de la mémoire cache, une utilisation importante du bus de communication avec la mémoire principale, et la nécessité de vider le tampon d'enregistrement fréquemment. Les spécialistes de l'embarqué s'accordent à dire que BTS induit un surcoût de 20% à 100% [45], mais notre étude montre que celui-ci peut atteindre plusieurs milliers de pourcents pour des programmes ayant des hauts taux de branchement (de l'ordre de  $10^8$  branchements par seconde). De tels taux sont facilement atteints par des programmes usuels, voir la section 5.2.1 à ce sujet.

Une autre limitation de BTS est l'absence d'estampilles de temps (*timestamps*) dans la trace, ce qui impose une datation logicielle lors du vidage du tampon. Une telle datation étant faite ponctuellement et pour un large nombre d'enregistrements à la fois, elle est évidemment peu précise.

### Last Branch Record (LBR) d'Intel

Tout comme BTS, la fonctionnalité *Last Branch Record* enregistre la trace d'exécution logicielle sur les processeurs Intel depuis la micro-architecture NetBurst (prédécesseuse de l'architecture Core). La différence majeure est que LBR sauvegarde les données dans des registres dédiés (et non en mémoire principale), ce qui élimine le surcoût dû à l'accès au bus et au partage de la cache et de la mémoire avec le processus tracé. En revanche, le

nombre de ces registres est très limité : 4 à 16 enregistrements peuvent être stockés, selon le processeur [27]. Ceci donne accès à une rétrotrace (*backtrace*), ce qui est utile si on veut remonter à la cause d'un bogue précis, inspecter le flot de contrôle avant une interruption, ou lorsqu'on examine un programme « pas à pas » [45]. Outre le fait que LBR n'induit pas de ralentissement, il est aussi possible de choisir quel type de branchement enregistrer, et ainsi faire une sélection parmi les appels de fonctions, les sauts ou les retours.

En revanche, ce système est totalement inadapté au traçage d'événements pendant une exécution normale, car il demanderait de lire les registres LBR tous les 16 branchements pour vérifier si l'adresse de l'événement recherché a été atteinte. Pour cette raison, nous n'avons pas inclus LBR dans nos expérimentations.

## Processor Trace (PT) d'Intel

*Processor Trace* est une nouvelle solution matérielle de traçage d'exécution conçue par Intel, qui améliore et unifie les fonctionnalités de ses précédentes implémentations. Cette extension écarte les limitations de BTS et LBR en misant sur la performance et la flexibilité. Selon Intel, PT cause une perturbation minimale sur les programmes tracés [26] grâce à des ressources dédiées et à des filtres pour ne tracer que les portions d'intérêt.

Parmi ces ressources, Intel a fait le choix d'inclure des tampons dans l'unité de calcul pour stocker les traces de petite taille sans accéder à la mémoire principale [47], ce qui évite les importants délais de communication sur le bus. Le contrôle du traçage peut être fait avec des événements tels que le changement du niveau de privilège ou du contenu du registre CR3, ce qui permet respectivement de suivre du code en espace utilisateur ou noyau, ou bien un processus particulier. Ainsi, les ressources ne sont pas surchargées par des données qui n'intéressent pas l'utilisateur. Enfin, les paquets de trace produits peuvent contenir des estampilles de temps et des informations de contexte qui viennent enrichir la trace avec des données de performance.

Les caractéristiques de PT présentées par Intel semblent très prometteuses, et avec des fonctions assez similaires à ce que ARM propose déjà avec CoreSight ETM et PTM (présentés à la section 2.1.1). Malheureusement, aucun processeur implementant Intel PT n'est disponible à l'heure actuelle. En attendant, Intel fournit des bibliothèques et exemples de code source ouvert pour générer et décoder des traces PT [47]. La prise en charge de cette fonctionnalité dans Linux est aussi prévue, en utilisant l'ABI (interface application-binaire) de Perf [52].

Quand Intel PT sera disponible, l'étude de ses performances pour une application de traçage d'événements présentera un fort intérêt.

## CoreSight d'ARM

CoreSight est un ensemble de modules matériels destinés à apporter des solutions de débogage et de profilage. Chacun de ces modules, appelés macrocellules (*macrocells*), est destiné à une fonction spécifique et est indépendant des autres. Ils ont été conçus avec un fort accent sur la non-intrusivité, grâce à des ressources dédiées, et le débogage sans avoir à arrêter le processeur. Ainsi, CoreSight permet l'analyse des programmes dans leurs conditions réelles d'utilisation, ce qui permet en outre de profiler leurs performances.

En général, une combinaison de plusieurs macrocellules est intégrée dans un système embarqué en fonction des besoins de débogage de la plateforme. Une vue générale des macrocellules de CoreSight est présentée à la figure 2.1, mais nous ne nous intéresserons par la suite qu'à celles qui sont utiles au traçage.

La macrocellule *Embedded Trace Macrocell* (ETM) permet de tracer l'activité d'un processeur par le biais des instructions exécutées et des données accédées en mémoire. ETM existe depuis les premières versions de CoreSight, ce qui la rend disponible sur de nombreuses plateformes basées sur l'architecture ARM. La particularité de ce système est qu'il « écoute » le bus pour détecter les accès d'intérêt, sans agir de manière active avec l'unité de calcul. Ceci résulte en la production d'une trace qui transcrit le chemin d'exécution suivi, et qui date chaque élément avec un estampille précise au cycle près. Grâce à des déclencheurs, ETM est en mesure de n'activer le traçage que dans les conditions désirées, par exemple lorsque le contenu du registre *Context ID* correspond à un motif (pour le suivi d'un processus ou groupe de processus), selon les priviléges (espace noyau et/ou espace utilisateur) ou à l'intérieur d'un intervalle d'adresses donné (traçage d'une portion de code uniquement). Enfin, des filtres autorisent de choisir quelles informations sont à exporter dans la trace, ce qui permet d'y intégrer plus de détails ou au contraire de l'alléger pour gagner en performance [2].

Le bloc *Program Trace Macrocell* (PTM) peut être considéré comme une évolution d'ETM. Disponible seulement depuis les processeurs Cortex-A9, il est spécialisé dans le traçage d'exécution et ne permet pas d'enregistrer les accès mémoire pour des données [6]. En revanche, le traçage d'instructions a été repensé pour accroître les performances, notamment grâce à un protocole plus compact [58].

La macrocellule HTM (*AHB Trace Macrocell*) est l'équivalent de ETM pour surveiller le bus système (AHB pour *Advanced High-performance Bus*) au lieu des cœurs de processeur. Tout comme ETM, elle permet de surveiller certaines données ou adresses d'intérêt, mais à des fins de débogage et de profilage [4]. Elle met en avant les détails de l'exécution concernant le bus, qui ne sont pas déductibles de l'analyse du flot de contrôle. Notre étude portant sur le traçage d'événements, nous avons laissé HTM de côté.

source : arm.com

Figure 2.1 Vue générale des macrocellules de CoreSight

Pour collecter les données produites par toutes ces sources de trace, le modèle CoreSight propose deux options. La première est l'export des traces hors de la machine tracée, à destination d'un ordinateur « cible » qui collecte les traces *via* une interface JTAG. Autre option, les données de trace peuvent être lues directement depuis la machine hôte *via* un tampon sur la puce, appelé *Embedded Trace Buffer* (ETB) [3]. À l'intérieur de ce tampon commun, les paquets en provenance des différentes sources (ETM, HTM, etc.) sont multiplexés. Ceci présente l'avantage de corrélérer les événements d'origines différentes, qui n'ont pas parfois pas d'estampilles de temps ou bien des horloges de datation à fréquences différentes. Cette mémoire sur puce sert aussi de zone de transit où l'information est stockée rapidement, en attendant d'être récupérée à un moment propice. Cependant, le tampon ETB est assez petit (typiquement entre 4 et 16 Kio [58]), ce qui est trop réduit pour contenir la trace de l'exécution d'un programme courant. Par conséquent, ETB doit être sondé souvent et la mémoire vidée régulièrement pour éviter les débordements.

### Nexus Trace de Freescale

Tout comme ARM, Freescale conçoit des semi-conducteurs à destination des systèmes embarqués. Pour répondre aux forts besoins de débogage et d'optimisation de ce domaine, ses processeurs embarquent plusieurs solutions comme des *Performance Monitor*, un ensemble de registres qui collectent des statistiques sur des événements matériels (faute de cache, nombre

de branchements pris ou d'instructions exécutées par unité de temps) [22]. Ceux-ci permettent de faire du profilage sur les performances d'une application.

En ce qui concerne le traçage d'exécution, les processeurs Freescale fournissent une aide matérielle au travers du système Nexus [43], un standard de modules matériels et de connecteurs pour déboguer les systèmes sur puce dans leur ensemble, indépendamment du type de processeur ou de sa marque. Nexus comprend une solution de traçage d'exécution sobrement appelée *Program Trace*, dont les données peuvent être écrites en mémoire principale ou bien exportées vers une autre machine [29]. De manière similaire à ARM CoreSight, *Program Trace* intègre des comparateurs d'adresses et de données, pour cibler la trace sur un processus ou une fonction de choix, ainsi qu'un tampon sur la puce pour accélérer le stockage de la trace produite [22]. Cette fonctionnalité est présente sur certains processeurs membres de la famille QorIQ : les séries P3 et P5 ainsi que les séries T.

Malheureusement, nous n'avons pas pu expérimenter avec *Program Trace*, car la documentation pour configurer l'accès aux traces n'est pas disponible publiquement.

### 2.1.2 Traçage d'événements

La section précédente présentait différents systèmes pour obtenir la trace d'exécution d'un programme. Celle-ci donne accès à l'ensemble des instructions exécutées, et permet de reconstituer le flot de contrôle. Cette information est très complète mais a un impact lourd en termes de dégradation de performance ; parfois, seuls certains événements représentent un intérêt, et l'altération du comportement normal du programme n'est pas souhaitée.

Le traçage d'événements est une solution pour enregistrer le passage par des points spécifiques d'un programme, que le développeur choisit pour ses besoins personnels : élimination d'erreur, profilage ou sécurité. Ces événements moins fréquents relatent le comportement du logiciel tracé d'une vue à un plus haut niveau, par opposition à la liste de toutes les instructions exécutées. Historiquement purement logicielle (voir la section 2.2), cette méthode bénéficie aujourd'hui d'appuis matériels : des circuits électroniques conçus pour accélérer l'enregistrement des points de trace logiciels. « Trace Système » (*System Trace*) ou « Trace d'Instrumentation » (*Instrumentation Trace*) sont les noms donnés par les constructeurs à ces blocs matériels.

N'offrant pas le flot de contrôle entier, mais seulement une sous-partie choisie par le développeur pour répondre à ses besoins, le traçage d'événements assisté par matériel offre un compromis moins intrusif.

L'ensemble des solutions matérielles de traçage présentées dans cette section est résumé au tableau 2.2.

Tableau 2.2 Principales solutions matérielles de traçage d'événements

| Nom              | Plateforme | Stockage dans tampon dédié | Stockage en mémoire principale | Export <i>via</i> JTAG | Documentation disponible | Depuis |

|------------------|------------|----------------------------|--------------------------------|------------------------|--------------------------|--------|

| Data Acquisition | Freescale  | ✓                          | ✓                              | ✓                      |                          | 2010   |

| CoreSight ITM    | ARM        | ✓                          |                                | ✓                      | ✓                        | 2004   |

| CoreSight STM    | ARM        | ✓                          | ✓                              | ✓                      | ✓                        | 2010   |

| TI STM           | ARM        | ✓                          |                                | ✓                      |                          | 2011   |

## CoreSight d'ARM

Le système CoreSight, déjà présenté dans la section 2.1.1, comprend des modules spécialisés dans le traçage d'événements. Leur utilisation se fait *via* une zone mémoire directement adressable depuis le processeur, où chaque écriture va générer un paquet de trace pouvant contenir des données arbitraires ainsi qu'une estampille de temps (*timestamp*). Les paquets ainsi créés sont stockés dans un tampon dédié, pour ne pas interférer avec la mémoire principale. La présence d'un collecteur commun présente l'intérêt d'avoir des traces d'exécution et des traces d'événements corrélées dans le temps, et de ne nécessiter qu'un seul outil pour récupérer les données. L'avantage principal que fournit le traçage d'événements avec CoreSight, par comparaison avec un traçage purement logiciel, est l'inclusion automatique d'estampilles de temps dans les paquets de trace. Cette opération est assez coûteuse à réaliser de manière logicielle, nécessitant dans le pire des cas un appel système, ce qui induit une intrusion significative dans l'exécution du programme. Les estampilles de temps des modules CoreSight sont lues directement depuis une horloge matérielle, ce qui a l'avantage de ne pas prendre de temps processeur et d'avoir une précision au cycle près.

La première implémentation d'un tel système fut la macrocellule *Instrumentation Trace Macrocell* (ITM). Elle rassemble les caractéristiques présentées ci-dessus, et produit des paquets de données, entrelacés de paquets d'estampilles de temps [5]. Ceux-ci sont envoyés vers le tampon ETB (décrit dans la section 2.1.1), c'est-à-dire au même endroit que ceux issus des autres sources de trace.

ITM a depuis été remplacée par le bloc *System Trace Macrocell* (STM), qui apporte plusieurs améliorations [9]. Premièrement, STM est accessible directement depuis le bus système à haut débit (AXI), ce qui augmente la vitesse d'enregistrement des traces. Cette ré-implémentation est compatible avec les systèmes à coeurs multiples et à plusieurs fils d'exé-

cution, en proposant 65536 canaux où l'écriture induit un point de trace, chaque canal pouvant être accédé indépendamment. D'autres fonctionnalités sont apportées par cette nouvelle version, comme la possibilité d'arrêter le processeur en cas de débordement du tampon de traçage, et la datation des paquets eux-mêmes au lieu de paquets d'estampille de temps intercalés dans les données [40]. Enfin, STM exporte la trace vers le *Trace Memory Controller* (TMC), un tampon flexible qui peut se comporter classiquement (comme ETB), mais aussi comme une file premier arrivé premier sorti (FIFO) ou un routeur qui envoie les paquets en mémoire principale [8]. Ces améliorations rendent CoreSight STM peu intrusive et hautement configurable, des qualités très prometteuses pour améliorer les logiciels de traçage d'événements.

Seuls les systèmes sur puce OMAP5 et plus récents disposent de la version CoreSight de STM (une autre version moins performante existe : TI STM, présentée dans la section 2.1.2). N'ayant accès qu'à des puces des familles OMAP3 et OMAP4, nous n'avons pas expérimenté avec CoreSight STM, mais il serait intéressant d'acquérir de nouvelles cartes de développement intégrant cette fonctionnalité.

### System Trace Module de Texas Instruments

*System Trace Module*, dont l'acronyme est aussi STM, est une version antérieure à *System Trace Macrocell* mise au point par Texas Instruments (TI) pour la même finalité : tracer des événements logiciels. Tout comme CoreSight STM, TI STM est accessible par une zone mémoire où les écritures génèrent des paquets de trace automatiquement datés avec des estampilles de temps (*timestamps*). Contrairement à l'implémentation d'ARM, les paquets produits par TI STM sont directement envoyés vers le tampon ETB, il est alors nécessaire de les récupérer à intervalles réguliers. La version de Texas Instruments, bien que moins flexible, reste très performante et protège les accès concurrents grâce à un nombre élevé de canaux d'écriture.

Pour résumer, le *System Trace Module* de Texas Instruments fournit la même fonction que la version d'ARM décrite dans la section précédente, avec une performance légèrement réduite et moins de flexibilité. C'est cette version que nous avons utilisée au cours de notre recherche.

### Nexus Trace de Freescale

Parmi les éléments du système Nexus [43] décrit plus haut, la fonction *Data Acquisition Messages* autorise du code logiciel à écrire des données arbitraires dans le canal de débogage. Freescale implémente *Data Acquisition Messages* en exposant des registres à usage spécial

où l'écriture va générer un paquet *Data Acquisition* [22]. Selon la configuration de Nexus, ce paquet est récupérable par la suite par un débogueur externe *via* une interface JTAG, ou bien accessible directement en mémoire principale. Les messages produits par ce système peuvent être agrémentés d'un identifiant de 8 bits, configurable lui aussi par logiciel, ce qui autorise jusqu'à 256 sources de trace distinctes.

Ici encore, nous n'avons pas pu expérimenter avec les *Data Acquisition Messages* car la documentation nécessaire à la récupération des traces n'est pas disponible publiquement.

## Encodage des traces d'événements

Les traces générées par un outil purement logiciel comme ceux de la section 2.2 sont dans un format arbitraire, qui peut être axé sur la réduction de l'espace occupé ou au contraire, la lisibilité. Ce format est défini par le logiciel traceur selon les besoins, et peut être redéfini *a posteriori*. Dans le cas d'une infrastructure matérielle comme celles que nous étudions, la représentation binaire doit être bien pensée dès le départ, pour convenir aux usages nécessitant une grande précision ou bien des traces compactes. Les modules de CoreSight et TI présentés dans les deux sections précédentes atteignent cet objectif grâce à des traces constituées de paquets modulaires, dont le contenu dépend du type et dont la taille se base sur une unité d'un demi-octet.

Le bloc ITM de CoreSight génère des paquets de synchronisation, de débordement, de datation et de données, dans des formats décrits dans un manuel de référence publiquement accessible [5]. Par exemple, les données sont intégrées dans des paquets de type SWIT, dont la taille peut varier entre 2 et 5 octets.

La *System Trace Macrocell* ainsi que le *System Trace Module*, quant à eux, produisent une trace au format STP (*System Trace Protocol*). Le module STM de Texas Instruments respecte la version 1 de STP, tandis que la macrocellule STM de CoreSight se conforme à la version 2. La spécification de ce format est fermée [41], au sens que son accès est réservé aux industriels membres de l'Alliance MIPI, un consortium comprenant des entreprises telles que ARM ou STMicroelectronics. Nous avons tenté d'en obtenir une copie, sans succès car MIPI exige pour cela une inscription à l'Alliance à un coût significatif, et surtout ne permet pas nécessairement de publier le code source composé à l'aide de cette information. Pour utiliser STM, il a donc été nécessaire d'effectuer un travail de rétro-ingénierie pour comprendre l'encodage des traces STP. Ceci est détaillé en section 5.4.

## 2.2 Les traceurs logiciels sous Linux

Le traçage logiciel est une technique consistant à récupérer des informations au cours de la vie d'un programme. Contrairement au débogage, pendant lequel une application est exécutée pas à pas, un traceur enregistre des événements à la volée tout en laissant le programme s'exécuter. Cette faible intrusivité vise à laisser le logiciel tracé dans ses conditions normales d'exécution, de manière à reproduire le même comportement et les mêmes problèmes que dans une configuration réelle. Le traçage logiciel apporte donc une solution complémentaire au débogage ; il ne faut pas non plus le confondre avec le traçage d'exécution évoqué dans la section 2.1.1. Alors que ce dernier consistait à enregistrer tous les branchements pris par le processeur, les traceurs logiciels se concentrent sur des événements à plus haut niveau, qui se produisent beaucoup moins fréquemment.

Dans cette section, nous présentons les principaux outils de traçage d'événements disponibles sur les systèmes Linux.

### 2.2.1 Ftrace

L'outil Ftrace [49] permet de tracer des événements du noyau tels que les appels système, les gestionnaires d'interruption ou les fonctions d'ordonnancement. Il fait partie intégrante de Linux, qu'il instrumente en des points précis, représentatifs de toutes les fonctions du noyau [12]. Les événements à enregistrer sont sélectionnables *via* des entrées dans le pseudo-système de fichiers DebugFS. Une fois lancé, le traceur détecte ces événements et les affiche à l'utilisateur avec leur temps d'exécution, permettant ainsi de mesurer les performances. Leur affichage peut se faire sous différentes formes, par exemple une représentation graphique des appels de fonctions successifs et imbriqués. Cependant, Ftrace a été pensé pour une analyse des traces en temps réel, avec un format de sortie conçu pour la lecture en direct par l'utilisateur. Il n'y a pas de représentation compacte de la trace, ce qui rend cet outil inadapté pour un traçage de longue durée ou en continu. De plus, Ftrace n'est pas optimisé pour les systèmes à plusieurs coeurs car il se synchronise grâce à des verrous tournants (*spin locks*) avec les interruptions désactivées, ce qui peut induire de fortes latences [16]. Enfin, ce traceur ne peut pas être utilisé sur des applications en espace utilisateur.

### 2.2.2 Perf

L'outil Perf est lui aussi intégré au noyau Linux [17]. Ce n'est pas à proprement parler un traceur : sa fonction première est de récolter des statistiques sur certains événements de la vie d'un programme, comme le nombre de fautes de cache ou le nombre de cycles processeur utilisés. Perf fonctionne par échantillonnage : la production d'événements à bas

niveau incrémenté des compteurs matériels, dont le dépassement est enregistré grâce à une interruption. Cet outil n'est donc pas fait pour retracer la succession de ces événements, mais indique le nombre de fois où ils se sont produits.

Perf a toutefois des fonctions secondaires : il est capable de tracer une application, mais en réutilisant l'interface de Ftrace [32]. Depuis 2010, il peut aussi faire du traçage d'exécution avec BTS [42]. Voir la section 2.3.1 à ce sujet.

### 2.2.3 SystemTap

SystemTap [19] est un outil à destination des administrateurs qui souhaitent recueillir des informations sur le comportement du système. Son mécanisme se base sur les Kprobes [23], des sondes placées dynamiquement à différents endroits du noyau Linux. Depuis peu, SystemTap est aussi capable d'instrumenter des programmes en espace utilisateur *via* Uprobes [31], un équivalent des sondes noyau. Il est possible de connecter des scripts à ces sondes, de manière à programmer des actions arbitraires lors de l'occurrence des événements associés aux Kprobes. Ainsi, au lieu d'enregistrer tous les points sondables dans une trace très dense, un administrateur peut se limiter aux événements d'intérêt, et choisir une action adaptée : agréger des statistiques, écrire une trace en ajoutant des estampilles de temps, etc. SystemTap mise donc sur la flexibilité, et non sur les performances. Ceci se manifeste par un surcoût non-négligeable sur le temps d'exécution, notamment dû à un mécanisme de synchronisation par verrouillage à verrous tournants (*spin locks*), mais aussi par des données trop volumineuses lorsque l'on souhaite enregistrer la trace en continu. Effet connexe, SystemTap ne possède aucun moyen de visualisation pour de larges traces (de l'ordre du Gio).

### 2.2.4 LTTng

LTTng [15] est un traceur axé sur la non-intrusivité avec le logiciel tracé. Pour atteindre ce but, il utilise des mécanismes optimisés pour les performances. Par exemple, la synchronisation est faite par des opérations atomiques plutôt que par des verrouillages. Ces verrouillages étant une des principales causes de latences, le mécanisme RCU [39] est utilisé partout où cela est possible pour les éviter. Afin d'atteindre une mise à l'échelle efficace, des tampons sont alloués pour chaque processeur, et ceux-ci sont utilisés circulairement (*ring buffers*).

LTTng peut tracer des événements du noyau comme les fonctions d'ordonnancement, les fautes de page, les interruptions. Pour cela il utilise des points de trace statiques ou les sondes Kprobes, comme SystemTap. Il est aussi possible de tracer un programme en espace utilisateur avec la version adéquate de l'outil (LTTng-UST), en instrumentant l'application *via* des points de trace positionnés aux endroits voulus dans le code.

La trace générée se conforme au format CTF [18], une spécification qui autorise à la fois flexibilité et compacité. Elle peut ensuite être lue par plusieurs outils, avec une interface graphique ou en ligne de commande. Cette dernière méthode, très légère, permet de travailler avec des traces de plusieurs dizaines de Gio.

### 2.3 Les logiciels s’aidant du matériel

Certains outils existants tirent déjà profit des solutions matérielles offertes par les nouveaux processeurs. Chaque fonctionnalité matérielle est généralement accompagnée d'un logiciel qui la prend en charge ; malheureusement il s'agit bien souvent de logiciels propriétaires dont les fabricants espèrent tirer profit en gardant la source fermée. Néanmoins, pour la majorité du matériel de traçage que nous avons présenté, une documentation complète est disponible, ce qui a permis des implémentations accessibles à tous. La disponibilité du code de ces logiciels nous a autorisé à les étudier.

Dans cette section, nous décrivons certaines implémentations logicielles existantes, qui utilisent le matériel de traçage BTS et ETM.

#### 2.3.1 Perf et BTS

Le système *Branch Trace Store* (BTS) d'Intel, présenté dans la section 2.1.1, est pris en charge par le logiciel Perf et le noyau Linux. Il est ainsi possible d'enregistrer la trace d'exécution de n'importe quel programme sous Linux, c'est-à-dire de connaître l'intégralité des branchements que le processeur a suivi.

Les deux commandes suivantes en donnent une illustration : la première enregistre la trace dans un fichier temporaire, tandis que la deuxième l'affiche dans un format lisible par l'utilisateur.

```

perf record -e branches:u -c 1 -d PROGRAMME

perf script -f ip,addr,time

```

Un exemple de résultat, présenté ci-après, affiche les adresses source et destination des branchements, ainsi que les estampilles de temps correspondantes. Le fait que toutes ces estampilles aient la même valeur montre bien que BTS ne fournit pas de datation : celle-ci est ajoutée de manière logicielle lors du vidage du tampon, une fois de temps en temps.

```

# _____

# nrcpus online : 8

# cpudesc : Intel(R) Core(TM) i7-3610QM CPU @ 2.30GHz

# total memory : 12223968 kB

```

```

# =====

#

29968.676878: ffffffff8166deec => 34b4401420

29968.676878: ffffffff8166deec => 34b4401420

29968.676878: 34b4401423 => 34b4404920

29968.676878: ffffffff8166deec => 34b4404920

29968.676878: ffffffff8166deec => 34b440493f

29968.676878: ffffffff8166deec => 34b4404946

29968.676878: 34b44049b2 => 34b44049cf

29968.676878: 34b44049d3 => 34b44049b8

29968.676878: 34b44049d3 => 34b44049b8

29968.676878: 34b44049d3 => 34b44049b8

29968.676878: 34b44049d3 => 34b44049b8

29968.676878: 34b44049df => 34b4404bb8

29968.676878: 34b4404bc0 => 34b4404be0

29968.676878: 34b4404bea => 34b4404c00

29968.676878: 34b4404c17 => 34b44049c3

29968.676878: 34b44049d3 => 34b44049b8

29968.676878: 34b44049d3 => 34b44049b8

29968.676878: 34b44049d3 => 34b44049b8

29968.676878: 34b44049d3 => 34b44049b8

[ ... ]

```

L'implémentation du mécanisme de traçage est faite à la fois du côté du noyau Linux et du côté utilisateur, c'est-à-dire dans le code de Perf. Celle-ci effectue une double copie des données générées par BTS, qui est selon nous une cause de fort ralentissement. Nous décrivons davantage ce problème dans la section 5.1.

### 2.3.2 Linux et ETM

Linux fournit une prise en charge basique de l'*Embedded Trace Macrocell* (ETM), présentée en section 2.1.1. Au travers d'entrées dans le pseudo-système de fichiers SysFS, un utilisateur peut activer le traçage du noyau, et récupérer les données produites en lisant un fichier dans `/dev`. Plusieurs outils à source ouverte peuvent ensuite être utilisés pour décoder la trace et l'afficher dans un format lisible par un humain [51, 46].

Les commandes ci-dessous montrent comment le traçage peut être activé, et à quoi ressemble le début d'une trace d'exécution enregistrée grâce à ETM.

```

# Démarrer le traçage

echo 1 > /sys/devices/etm/trace_running

# Provoquer un appel système

touch /tmp/nouveaufichier

# Arrêter le traçage

echo 0 > /sys/devices/etm/trace_running

# Lire la trace et la décoder

cat /dev/tracebuf | ./etmdecoder --etm

Cycle count 0

I-sync Context 006ce2c4, IB 29, Addr 000085e8

E(000085e8) Waited 2

Cycle count 527

I-sync Context 006ce2c4, IB 29, Addr 00008900

E(00008900) Waited 1

Branch 000085e8 ARM

E(000085e8)

Cycle count 248

I-sync Context 006ce2c4, IB 29, Addr 00008900

E(00008900) Waited 1

Branch 000085e8 ARM

E(000085e8)

Cycle count 248

I-sync Context 006ce2c4, IB 29, Addr 00008900

E(00008900) Waited 1

Branch 000085e8 ARM

E(000085e8)

Cycle count 248

[...]

```

Avec l'implémentation originale de Linux, il n'était pas possible de tracer autre chose que le code du noyau, ni de se restreindre à une portion de code d'intérêt. Pour ces raisons, nous avons modifié le noyau Linux pour lui donner plus de flexibilité. Ce travail est présenté dans la section 5.3.

### 2.3.3 Outils à source fermée

Plusieurs logiciels propriétaires permettent de configurer les infrastructures de traçage matériel pour générer et récupérer des traces. Ils sont en général conçus par les fabricants

de ce matériel eux-mêmes, et vendus à des prix pouvant dépasser 19000 US\$ [57]. Nous présentons ici ceux liés aux blocs de traçage décrits dans cette revue de littérature.

Les quatre logiciels suivants sont des environnements de développement qui prennent en charge certaines des macrocellules de CoreSight sur des systèmes embarqués :

- *Code Composer Studio* de Texas Instruments ;

- *DS-5 Development Studio* d'ARM ;

- *STWorkbench* de STMicroelectronics ;

- *TRACE32-ICD* de Lauterbach.

L'environnement de développement *CodeWarrior Development Studio* de Freescale permet quant à lui d'utiliser les éléments Nexus des processeurs Freescale tels que *Program Trace* et *Data Acquisition*.

## 2.4 Conclusion de la revue de littérature

Au cours de notre revue de littérature, nous avons présenté les infrastructures matérielles dédiées au traçage, qu'il s'agisse d'enregistrement du flot d'exécution ou bien d'événements à plus haut niveau. Ces systèmes étant relativement nouveaux, ils ne sont pas encore très utilisés et peu d'études ont été faites dessus. De façon analogue, les outils en tirant profit sont rares, surtout dans le domaine du logiciel libre.

D'autre part, nous avons présenté différents outils logiciels dédiés au traçage. Un de leurs points communs était de chercher à réduire le surcoût lié à leur utilisation, de manière à étudier des programmes dans leurs conditions normales d'utilisation.

Il semble donc important d'étudier comment des logiciels de traçage comme LTTng peuvent bénéficier des capacités prometteuses offertes par le matériel dédié, présent sur la plupart des nouveaux processeurs. Tirer profit de ce potentiel rendrait le traçage plus transparent et moins intrusif, et pourrait favoriser son utilisation par les développeurs, pour rendre leurs programmes plus performants.

## CHAPITRE 3

### MÉTHODOLOGIE

L'amélioration des performances d'un traceur logiciel en utilisant des blocs matériels passe d'abord par la mise en place d'une méthodologie. Celle-ci doit notamment définir la manière de mesurer les performances, et proposer une échelle objective pour comparer les résultats et affirmer si oui ou non il y a amélioration.

#### 3.1 Environnement de travail

Le laboratoire DORSAL avait à sa disposition plusieurs machines intégrant des modules matériels de traçage. La première étape a été de déterminer comment utiliser au mieux ces ordinateurs pour évaluer le surcoût lié à l'utilisation d'un traceur. Chacune de ces machines ayant les capacités d'un vrai ordinateur, deux possibilités s'offraient à nous :

- installer un système d'exploitation complet sur chaque machine de test pour produire et analyser les résultats ;

- installer un système minimal sur les machines de test et analyser les résultats sur une station de contrôle.

Nous avons choisi la deuxième solution, de manière à ce que nos mesures influent le moins possible sur le comportement des machines de test. Notre configuration matérielle comprenait ainsi quatre machines : deux ordinateurs de bureau (l'un servant de station de contrôle), et deux cartes de développement à système sur puce.

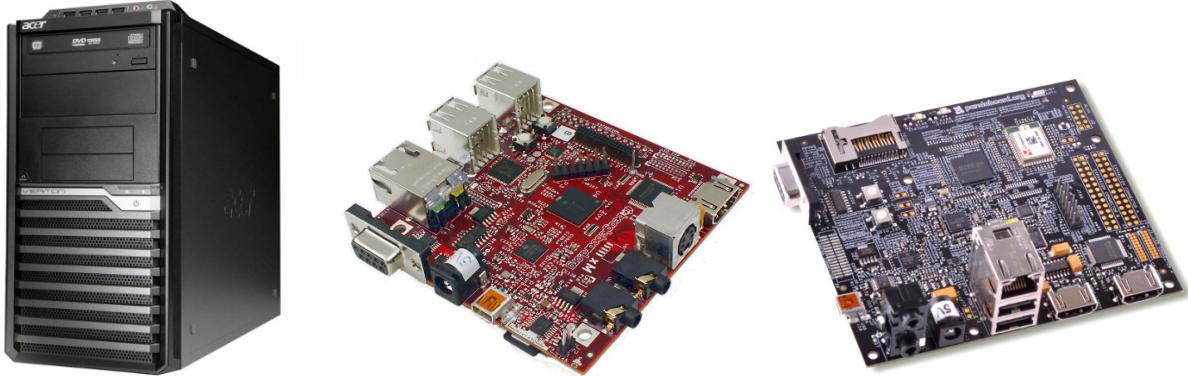

La figure 3.1 illustre les trois machines de test utilisées.

##### 3.1.1 Station de contrôle

Les expériences ont été lancées depuis une station de contrôle, qui était simplement un ordinateur de bureau. C'est depuis cette machine que les tests étaient lancés à distance, et que les traces étaient récupérées pour analyse.

La station de contrôle était connectée aux machines de test par un lien Ethernet à 100 Mbit/s, en utilisant les services suivants.

- Une connexion SSH pour administrer le système d'exploitation une fois la machine démarrée.

- Un serveur NFS pour « partager » des fichiers et répertoires communs entre la station de contrôle et les machines de test, sans avoir à les copier explicitement à chaque

sources : [jrlinton.co.uk](http://jrlinton.co.uk), [liquidware.com](http://liquidware.com), [prnewswire.com](http://prnewswire.com)

Figure 3.1 Photographies des machines de test. De gauche à droite : un ordinateur de bureau à processeur Intel x86 ; une carte Beagleboard-xM ; une carte Pandaboard.

modification.

- Des serveurs DNS et TFTP pour un démarrage en PXE (*via* le réseau). Ainsi lors d'une réinitialisation, les machines de test téléchargent le noyau Linux à démarrer depuis la station de contrôle. Ceci était particulièrement utile car nous avons parfois compilé plusieurs centaines de noyaux différents pour une même machine ; une réinstallation de Linux « à la main » aurait été extrêmement fastidieuse.

### 3.1.2 Machine de test Intel x86

L'ordinateur de bureau choisi pour expérimenter sur le module *Branch Trace Store* d'Intel comprenait un processeur à 4 cœurs (8 cœurs virtuels grâce à l'*hyperthreading*) et 6 Gio de mémoire principale. Ce processeur récent dispose de nombreuses fonctionnalités de débogage et profilage, notamment BTS et LBR.

Tableau 3.1 Caractéristiques de l'ordinateur de bureau

|                        |                                       |

|------------------------|---------------------------------------|

| Carte mère             | DX58SO d'Intel                        |

| Processeur             | Intel Core i7-3770 cadencé à 3,4 GHz  |

| Cœurs physiques        | 4                                     |

| Mémoire vive           | 6 Gio, Kingston DDR3 SDRAM à 1333 MHz |

| Système d'exploitation | Arch Linux                            |

| Matériel de traçage    | BTS, LBR                              |

Pour cette machine comme pour les autres, nous avons installé le système d'exploitation Arch Linux, reconnu pour sa légèreté. Arch Linux n'a en effet ni environnement graphique, ni module superflu installé par défaut, et occupe un volume total inférieur à 350 Mio une

fois installé. Ceci nous a permis de disposer des logiciels dont nous avions besoin, mais rien d'autre, afin de perturber au minimum nos tests.

### 3.1.3 Machine de test Beagleboard-xM