|                 | On-Chip Integrated Functional Near Infra-Red Spectroscopy (fNIRS)<br>Photoreceiver for Portable Brain Imaging                                                                                                                                                                         |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author: | Ehsan Kamrani                                                                                                                                                                                                                                                                         |

| Date:           | 2014                                                                                                                                                                                                                                                                                  |

| Type:           | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                             |

| iterer enee.    | Kamrani, E. (2014). On-Chip Integrated Functional Near Infra-Red Spectroscopy (fNIRS) Photoreceiver for Portable Brain Imaging [Ph.D. thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/1346/">https://publications.polymtl.ca/1346/</a> |

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

| <b>URL de PolyPublie:</b> PolyPublie URL: | https://publications.polymtl.ca/1346/ |

|-------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors:  | Mohamad Sawan, & Frédéric Lesage      |

| Programme:                                | Génie biomédical                      |

## UNIVERSITÉ DE MONTRÉAL

# ON-CHIP INTEGRATED FUNCTIONAL NEAR INFRA-RED SPECTROSCOPY (fNIRS) PHOTORECEIVER FOR PORTABLE BRAIN IMAGING

# EHSAN KAMRANI INSTITUT DE GÉNIE BIOMÉDICAL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR

(GÉNIE BIOMÉDICAL)

JANVIER 2014

## UNIVERSITÉ DE MONTRÉAL

## ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée:

## ON-CHIP INTEGRATED FUNCTIONAL NEAR INFRA-RED SPECTROSCOPY (fNIRS) PHOTORECEIVER FOR PORTABLE BRAIN IMAGING

présentée par: KAMRANI Ehsan

en vue de l'obtention du diplôme de :  $\underline{Philosophiae\ Doctor}$

a été dûment acceptée par le jury d'examen constitué de :

- M. SAVARD Pierre, Ph.D., président

- M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

- M. LESAGE Frédéric, Ph.D., membre et codirecteur de recherche

- M. AUDET Yves, Ph.D., membre

- M. NABKI Frédéric, Ph.D., membre

## **DEDICATION**

To My Beloved Family and Friends

and All My Former Professors and Teachers...

#### **ACKNOWLEDGMENTS**

The author would like to acknowledge those who aided in the definition, development, and realization of this thesis. Without the support of these people, this thesis would not have been as complete.

Thanks to Prof. Mohamad Sawan, my supervisor and the director of the Polystim Neurotechnologies laboratory, for aiding in the inception of this project and for giving valuable guidance and insightful suggestions throughout the project's duration.

Thanks to Prof. Frederic Lesage, of Optical and molecular imaging Lab, the project cosupervisor, for his invaluable help, comments, inputs and sharing his expertise.

Thanks to Prof. Seok-Hyun (Andy) Yun, of Harvard-MIT health science and technology, for sharing his expertise in optics and photonics and for his assistance in measurement setups.

Thanks to Dr. Afrin Sultana, past postdoctorate fellow, for her help and invaluable inputs in the first phase of the project regarding to the APD modeling and fabrication.

Thanks to Dr. Mohamad Hamady, past postdoctorate fellow at Lab, for his help in circuit analysis and modeling.

Thanks to Dr. Philippe Pouliot, researcher at Polytechnique Montreal, for his help in NIR signal analysis and modeling.

Thanks to Ms. Amiri, master student in the Polystim Lab, for her help in simulation of the quench and control system for photon-counting block of the system.

Thanks to Mrs. Marie-Yannick Laplante, the Polystim Lab secretary, for her help and valuable assistant.

Thanks to Mr. Rejean Lepage and Mr. Laurent Mouden, offering technical supports to Polystim Lab, for their help and input regarding practical testing setup.

We acknowledge financial support from the Heart and Stroke Foundation of Canada (HSFC), the Canadian Institutes of Health Research (CIHR) and ReSMiQ (Regroupement stratégique en microélectronique du Québec).

## **RÉSUMÉ**

L'imagerie cérébrale fonctionnelle utilisant la Spectroscopie Fonctionnelle Proche-Infrarouge (SFPI) propose un outil portatif et non invasif de surveillance de l'oxygénation du sang. SFPI est une technique de haute résolution temporelle non invasive, sûr, peu intrusive en temps réel et pour l'imagerie cérébrale à long terme. Il permet de détecter des signaux hémodynamiques à la fois rapides et neuronaux ou lents. Outre les avantages importants des systèmes SFPI, ils souffrent encore de quelques inconvénients, notamment d'une faible résolution spatiale, d'un bruit de niveau modérément élevé et d'une grande sensibilité au mouvement. Afin de surmonter les limites des systèmes actuellement disponibles de SFPI non-portables, dans cette thèse, nous en avons introduit une nouvelle de faible puissance, miniaturisée sur une puce photodétecteur frontal destinée à des systèmes de SFPI portables. Elle contient du silicium photodiode à avalanche (SiAPD), un amplificateur de transimpédance (TIA), et « Quench-Reset », circuits mis en œuvre en utilisant les technologies CMOS standards pour fonctionner dans les deux modes : linéaire et Geiger. Ainsi, elle peut être appliquée pour les deux fNIRS : en onde continue (CW- SFPI) et pour des applications de comptage de photon unique. Plusieurs SiAPDs ont été mises en œuvre dans de nouvelles structures et formes (rectangulaires, octogonales, double APDs, imbriquées, netted, quadratiques et hexadecagonal) en utilisant différentes techniques de prévention de la dégradation de bord prématurée. Les principales caractéristiques des SiAPDs sont validées et l'impact de chaque paramètre ainsi que les simulateurs de l'appareil (TCAD, COMSOL, etc) ont été étudiés sur la base de la simulation et de mesure des résultats. Proposées SiAPDs techniques d'exposition avec un gain de grande avalanche, tension faible ventilation et une grande efficacité de détection des photons dans plus de faibles taux de comptage sombres. Trois nouveaux produits à haut gain, bande passante (GBW) et à faible bruit TIA sont introduits basés sur le concept de gain distribué, d'amplificateur logarithmique et sur le rejet automatique du bruit pour être appliqué en mode de fonctionnement linéaire. Le TIA proposé offre une faible consommation, un gain de haute transimpédance, une bande passante ajustable et un très faible bruit d'entrée et de sortie. Le nouveau circuit mixte trempe-reset (MQC) et un MQC contrôlable (CMQC) frontaux offrent une faible puissance, une haute vitesse de comptage de photons avec un commandable de temps de hold-off et temps de réinitialiser. La première intégration sur puce de SiAPDs avec TIA et Photon circuit de comptage a été démontrée et montre une amélioration de l'efficacité de la photodétection, spécialement en ce qui concerne la sensibilité, la consommation d'énergie et le rapport signal sur bruit.

#### **ABSTRACT**

Optical brain imaging using functional near infra-red spectroscopy (fNIRS) offers a direct and noninvasive tool for monitoring of blood oxygenation. fNIRS is a noninvasive, safe, minimally intrusive, and high temporal-resolution technique for real-time and long-term brain imaging. It allows detecting both fast-neuronal and slow-hemodynamic signals. Besides the significant advantages of fNIRS systems, they still suffer from few drawbacks including low spatialresolution, moderately high-level noise and high-sensitivity to movement. In order to overcome the limitations of currently available non-portable fNIRS systems, we have introduced a new low-power, miniaturized on-chip photodetector front-end intended for portable fNIRS systems. It includes silicon avalanche photodiode (SiAPD), Transimpedance amplifier (TIA), and Quench-Reset circuitry implemented using standard CMOS technologies to operate in both linear and Geiger modes. So it can be applied for both continuous-wave fNIRS (CW-fNIRS) and also single-photon counting applications. Several SiAPDs have been implemented in novel structures and shapes (Rectangular, Octagonal, Dual, Nested, Netted, Quadratic and Hexadecagonal) using different premature edge breakdown prevention techniques. The main characteristics of the SiAPDs are validated and the impact of each parameter and the device simulators (TCAD, COMSOL, etc.) have been studied based on the simulation and measurement results. Proposed techniques exhibit SiAPDs with high avalanche-gain (up to 119), low breakdown-voltage (around 12V) and high photon-detection efficiency (up to 72% in NIR region) in additional to a low darkcount rate (down to 30Hz at 1V excess bias voltage). Three new high gain-bandwidth product (GBW) and low-noise TIAs are introduced and implemented based on distributed-gain concept, logarithmic-amplification and automatic noise-rejection and have been applied in linear-mode of operation. The implemented TIAs offer a power-consumption around 0.4 mW, transimpedance gain of 169 dBQ, and input-output current/voltage noises in fA/pV range accompanied with ability to tune the gain, bandwidth and power-consumption in a wide range. The implemented mixed quench-reset circuit (MQC) and controllable MQC (CMQC) front-ends offer a quenchtime of 10ns, a maximum power-consumption of 0.4 mW, with a controllable hold-off and resettimes. The on-chip integration of SiAPDs with TIA and photon-counting circuitries has been demonstrated showing improvement of the photodetection-efficiency, specially regarding to the sensitivity, power-consumption and signal-to-noise ratio (SNR) characteristics.

## TABLE OF CONTENTS

| DEDICATION                                                          | III  |

|---------------------------------------------------------------------|------|

| ACKNOWLEDGMENTS                                                     | IV   |

| RÉSUMÉ                                                              | V    |

| ABSTRACT                                                            | VI   |

| TABLE OF CONTENTS                                                   | VII  |

| LIST OF TABLES                                                      | XI   |

| LIST OF FIGURES                                                     | XII  |

| LIST OF ABBREVIATIONS                                               | XVII |

| LIST OF APPENDICES                                                  | XX   |

| CHAPTER 1 INTRODUCTION                                              | 1    |

| 1.1 Motivation and General Background                               | 1    |

| 1.2 Background Theory of NIR Photodetectors (Theoretical framework) | 7    |

| 1.2.1 Photodetection using Solid-State Materials                    | 7    |

| 1.2.2 CMOS Image Sensors                                            | 10   |

| 1.2.3 Avalanche Photodiodes (APDs) and Impact Ionization            | 11   |

| 1.2.4 Dark-Current and Tunneling                                    | 13   |

| 1.2.5 CMOS Silicon Avalanche Photodiodes: Operation Modes           | 16   |

| 1.2.6 Infra-Red Detection using CMOS Silicon Avalanche Photodiodes  | 23   |

| 1.3 Problems studied and previous works                             | 24   |

| 1.3.1 Bulky systems                                                 | 24   |

| 1.3.2 Non-configurability and non-controllability                   | 24   |

| 1.3.3 Bulky or inefficient photodiodes                              | 26   |

| 1.3.4   | Inefficient photoreceiver and amplifier                                       | 28     |

|---------|-------------------------------------------------------------------------------|--------|

| 1.3.5   | 5 Slow quench-reset systems                                                   | 30     |

| 1.3.6   | 6 Low depth and spatial resolution                                            | 31     |

| 1.3.7   | 7 Noise problems                                                              | 32     |

| 1.4     | Conclusion                                                                    | 33     |

| СНАРТЕ  | R 2 RESEARCH METHODOLOGY AND ORGANIZATION                                     | 35     |

| 2.1     | Purpose of the Study: Objectives and Hypothesis                               | 35     |

| 2.2     | Proposed Work and Methodology                                                 | 36     |

| 2.3     | Methodology                                                                   | 37     |

| 2.3.1   | Design and implementation of a CMOS avalanche photodiode                      | 37     |

| 2.3.2   | 2 Designing an integrated circuit for operating in both Linear and Geiger mod | les of |

| opera   | ation                                                                         | 37     |

| 2.3.3   | 3 Integrate a complete one-channel photoreceiver circuit                      | 38     |

| 2.4     | Summary of Contributions and Outcomes                                         | 38     |

| 2.4.1   | New SiAPDs in 0.35 μm and 0.18 μm CMOS technologies                           | 38     |

| 2.4.2   | New integrated circuits for CW-fNIRS                                          | 39     |

| 2.4.3   | New integrated circuit for TR-fNIRS: Photon-Counting                          | 40     |

| 2.4.4   | On-chip integration of APD with CW and Photon-counting circuits               | 40     |

| 2.5     | Thesis Organization                                                           | 41     |

| СНАРТЕ  | CR 3 CMOS SILICON AVALANCHE PHOTODIODES: DESIGN                               | AND    |

| FABRICA | ATION                                                                         | 43     |

| 3.1     | Introduction                                                                  | 43     |

| 3.2     | Design Challenges of Near Infra-Red Detectors                                 | 43     |

| 3.3     | Premature Edge-Breakdown (PEB) Effects                                        | 45     |

| 3 4     | APD Structures                                                                | 47     |

| 3.5    | Wavelength-Specific Design                                             | 50         |

|--------|------------------------------------------------------------------------|------------|

| 3.6    | CMOS Silicon Avalanche Photodiodes: Modeling and Simulation            | 51         |

| 3.7    | Characterization of Silicon Avalanche Photodiodes (SiAPDs)             | 56         |

| 3.8    | Design, Implementation and Characterization of New SiAPDs: Fabrication | on in CMOS |

| 0.35 إ | ım Technology                                                          | 60         |

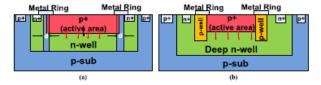

| 3.8    | .1 p+/n-well and n+/p-sub SiAPDs                                       | 61         |

| 3.9    | Design, Implementation and Characterization of New SiAPDs: Fabrication | on in CMOS |

| ر 0.18 | ım Technology                                                          | 64         |

| 3.9    | .1 Design Overview                                                     | 64         |

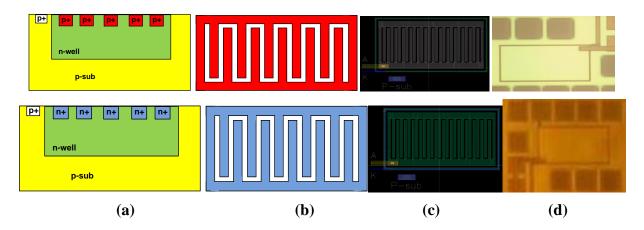

| 3.9    | .2 Rectangular p+/n-well SiAPDs without Guard-Ring                     | 66         |

| 3.9    | .3 Rectangular p+/n-well SiAPDs with p-sub Guard-Ring                  | 68         |

| 3.9    | .4 Rectangular/Octagonal n+/n-well and n+/p-sub SiAPDs                 | 70         |

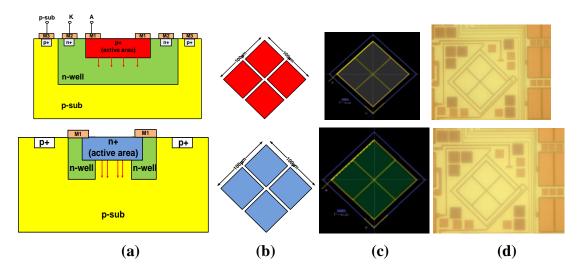

| 3.9    | .5 Hybrid Octagonal n+p+/p-sub SiAPD                                   | 74         |

| 3.9    | .6 Netted (Reticulated) SiAPDs                                         | 75         |

| 3.9    | .7 Nested (Maze-Shape) SiAPDs                                          | 76         |

| 3.9    | .8 Quadratic SiAPDs                                                    | 77         |

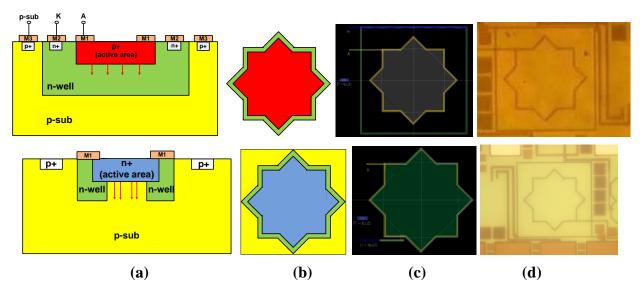

| 3.9    | .9 Hexadecagonal SiAPDs                                                | 78         |

| 3.10   | Comparison of the Implemented SiAPDs                                   | 80         |

| 3.11   | Conclusion                                                             | 81         |

| СНАРТ  | ER 4 DESIGN AND IMPLEMENTATION OF FRONT-END CIRCU                      | ITRIES FOR |

| CW-FN  | IRS (LINEAR-MODE SIAPD FRONT-END)                                      | 82         |

| 4.1    | Introduction                                                           | 82         |

| 4.2    | Transimpedance Amplifiers                                              | 82         |

| 4.3    | Implemented TIAs                                                       | 85         |

| 4.3    | .1 The First TIA circuit (TIA1)                                        | 85         |

| 4.3.2 The Second TIA circuit (TIA2)                         | 89  |

|-------------------------------------------------------------|-----|

| 4.3.3 Logarithmic TIA (LogTIA)                              | 91  |

| 4.4 Multi-Building Blocks Integration (APD and TIA)         | 95  |

| 4.5 Conclusion                                              | 98  |

| CHAPTER 5 GEIGER-MODE SIAPD AND PHOTON-COUNTER INTEGRATION  |     |

| 5.1 Introduction                                            | 99  |

| 5.2 Single-Photon Counter: Geiger-Mode SiAPD Implementation | 101 |

| 5.2.1 Implemented passive-quench circuits                   | 101 |

| 5.2.2 Implemented active and mixed quench circuits          | 103 |

| 5.2.3 The new controllable mixed quench technique           | 106 |

| 5.3 Conclusion                                              | 114 |

| CHAPTER 6 GENERAL CONCLUSION AND RECOMMENDATIONS            | 115 |

| 6.1 Conclusion.                                             | 115 |

| 6.2 Future Work                                             | 117 |

| REFERENCES                                                  | 120 |

| APPENDICES                                                  | 134 |

## LIST OF TABLES

| Table 1.1: Comparison of various brain imaging techniques.    2                                                                |

|--------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2: Performance comparison of the LM-SiAPD and GM-SiAPD.    23                                                          |

| Table 3.1: Comparison of different APD structures.    49                                                                       |

| Table 3.2: Comparison of dedicated and planar APD structures.    49                                                            |

| Table 3.3: Estimated characteristics of the TSMC and AMS CMOS 0.35-μm technology61                                             |

| Table 3.4: Characteristics of the proposed SiAPDs Implemented in CMOS 350 nm Technology      62                                |

| Table 3.5: Estimated characteristics of the TSMC and AMS CMOS 0.18-μm technology65                                             |

| <b>Table 3.6:</b> Main specifications of the rectangular p+/n-well SiAPDs (Area= $100 \times 100 \mu m2$ )68                   |

| <b>Table 3.7:</b> Main specifications of the rectangular p+/n-well SiAPDs with p-sub Guard-Ring (Area= $100\times100~\mu m2$ ) |

| <b>Table 3.9:</b> Main specifications of the Octagonal $n+/n$ -well and $n+/p$ -sub SiAPDs (Area= $100\times100\mu m2$ )       |

| <b>Table 3.10:</b> Main specifications of the Hybrid Octagonal $n+p+/p$ -sub SiAPDs (Area=100×100 $\mu m2$ )                   |

| <b>Table 3.11:</b> Main specifications of the Netted (Reticulated) SiAPDs (Area= $100 \times 100 \mu m^2$ )76                  |

| <b>Table 3.12:</b> Main specifications of the Nested (Maze-Shape) SiAPDs (Area=100×100 μm2)77                                  |

| <b>Table 3.13:</b> Main specifications of the Quadratic SiAPDs (Area=100×100 μm2)78                                            |

| <b>Table 3.14:</b> Main specifications of the hexadecagonal SiAPDs (Area= $100 \times 100 \mu m^2$ )79                         |

| <b>Table 4.1:</b> General characteristics of the proposed and implemented TIAs    94                                           |

| <b>Table 4.2:</b> The general characteristics of the implemented integrated SiAPDs with TIA97                                  |

| <b>Table 5.1:</b> General Characteristics of the Proposed Mixed Quench Circuit         105                                     |

| <b>Table 5.2:</b> Characteristics of the proposed system                                                                       |

## LIST OF FIGURES

| <b>Figure 1-1:</b> The NIR optical window (a), and the banana shape path of light between optodes is different deparation distances (b).                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Figure 1-2:</b> Different types of NIRS systems: CW-fNIRS (a), FD-fNIRS (b), and TR-fNIRS (c)                                                                                                                                                                                                                                                                                                                                                |

| <b>Figure 1-3:</b> The cross-section view of a p-n junction showing the photogeneration region forming the photo-current and the band-diagram (a), and the I-V curves of a p-n junction photodiode in dark and illuminated conditions. Ev and Ec indicate the valence-band and the conduction-band energies, respectively. Voc and Isc are the open-circuit voltage and short circuit current when there is illumination applied, respectively. |

| <b>Figure 1-4:</b> The illustration of concerns for pixel design (a), and the block diagrams of (b) APS (c) PPS, and (d) DPS with in-pixel ADC structures.                                                                                                                                                                                                                                                                                      |

| <b>Figure 1-5:</b> Representation of impact-ionization process in an APD (a), and the Energy Bandiagram of a reverse biased PIN structure where impact-ionization process occurs as the electrons travels through the high electric-field region (b).                                                                                                                                                                                           |

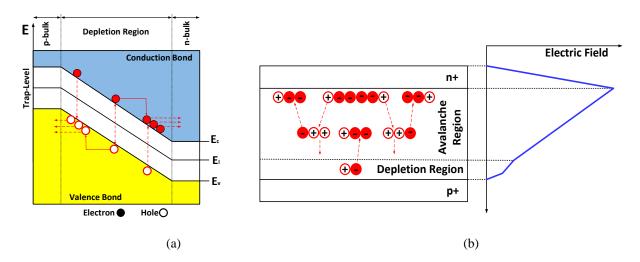

| <b>Figure 1-6:</b> Schematic representation of the Shockley-Read-Hall (SRH) generation, the trap assisted tunneling (TAT), and the band-to-band tunneling (BTBT) processes (a), and the I-characteristics of the tunnel diode. It has negative resistance in the shaded voltage region between $v_1$ and $v_2$ (b).                                                                                                                             |

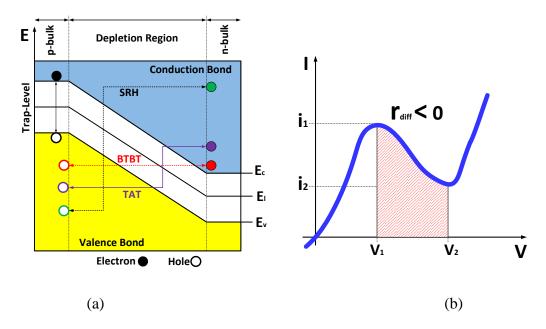

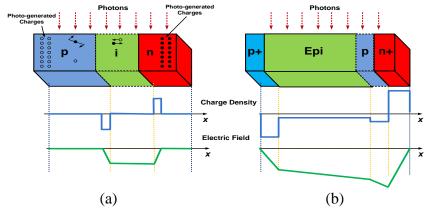

| Figure 1-7: Structure of PIN (a) and Reach-through SiAPD (b) and their charge density an electric field distribution.                                                                                                                                                                                                                                                                                                                           |

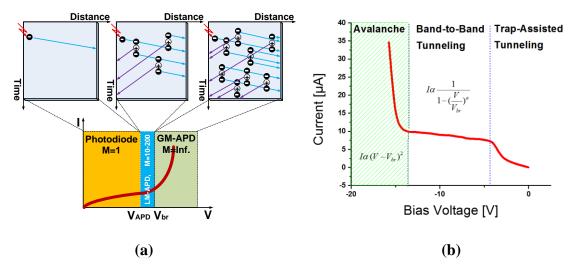

| <b>Figure 1-8:</b> Operation principle of an APD and Avalanche multiplication (a), and the APD current which is originated from trap-assisted tunneling, band-to-band tunneling and avalanche impact ionization processes (b).                                                                                                                                                                                                                  |

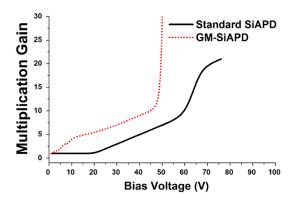

| Figure 1-9: Gain vs. Bias Voltage for GM-SiAPD and standard operation APDs2                                                                                                                                                                                                                                                                                                                                                                     |

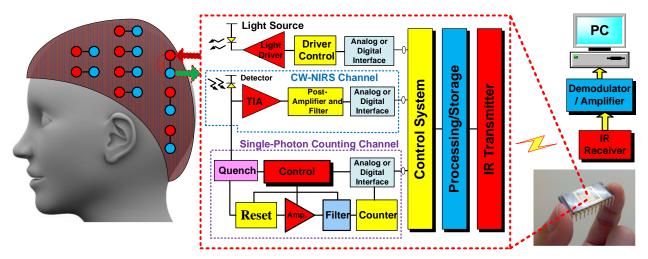

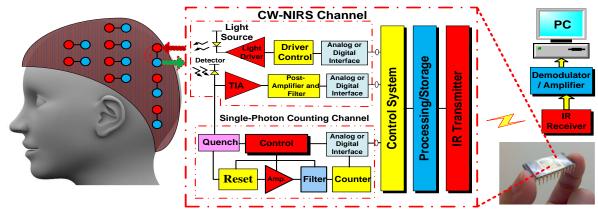

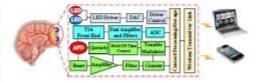

| Figure 2-1: Block diagram of the proposed integrated CW/TR fNIRS for real-time Braing                                                                                                                                                                                                                                                                                                                                                           |

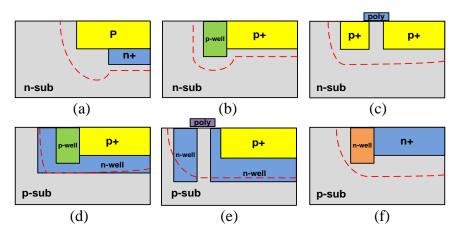

| Figure 3-1: Premature edge breakdown prevention mechanisms in planar processes: (a) n+, (b)                                                                                                                                                                                                                                                                                                                                                     |

| p-well, (c) n-sub, (d) p-well in p+/n-well APD, (e) p-sub, (f) n-well4                                                                                                                                                                                                                                                                                                                                                                          |

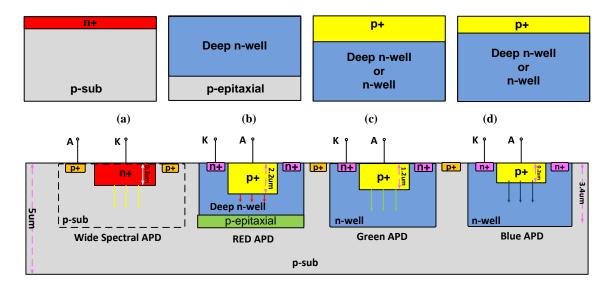

| Figure 3-2: Wavelength-specific design of APD structures: (a) Wide-spectral, (b) RED-IF                                     |

|-----------------------------------------------------------------------------------------------------------------------------|

| sensitive, (c) Green-sensitive, (d) Blue-sensitive APD structures. The doping is: 1 >                                       |

| $1015\text{cm} - 3$ for p-sub, $2 \times 1017\text{cm} - 3$ for n-well, and $5 \times 1019\text{cm} - 3\text{in}$ n+ and p- |

| regions                                                                                                                     |

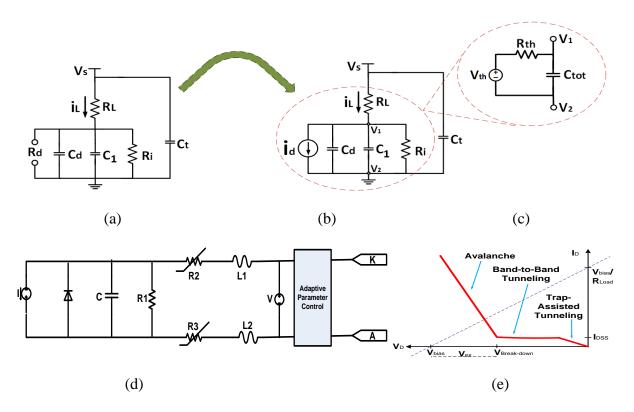

| Figure 3-3: The APD equivalent circuit before avalanche (a), and after avalanche (b), and after                             |

| reset (c). Here the Cd is the APD depletion-capacitance. Rd is the APD equivalent-resistance                                |

| (ideally infinite) and id is the APD current during avalanche. The implemented equivalen                                    |

| circuit model of APD (d), and the I-V characteristics (e)                                                                   |

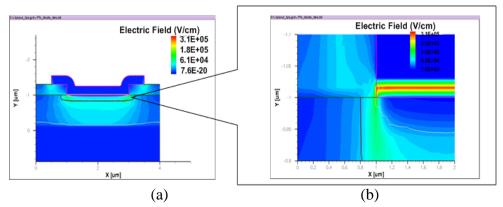

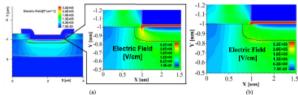

| <b>Figure 3-4:</b> The device simulation of the SiAPD under 62V reverse bias-voltage using Sentaurus TCAD (a)-(b)           |

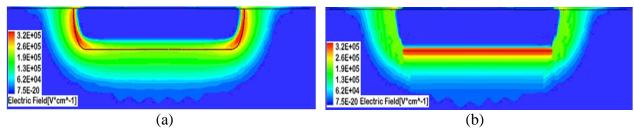

| Figure 3-5: Device simulation of the SiAPD under reverse bias: (a) the electric distribution while                          |

| no guard-ring is used. (b) Using guard-ring the maximum electric field distribution is mainly                               |

| located at active region of the device under reverse bias (the first row: TCAD, the second                                  |

| row: COMSOL)55                                                                                                              |

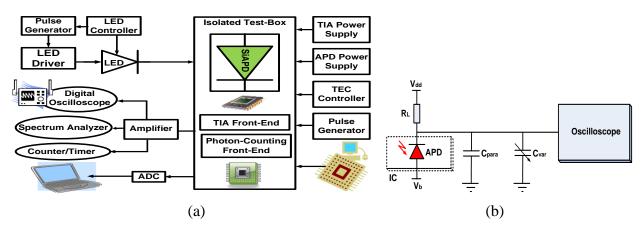

| Figure 3-6: The general experimental set-up (a) and APD connection to oscilloscope                                          |

| configuration (b)56                                                                                                         |

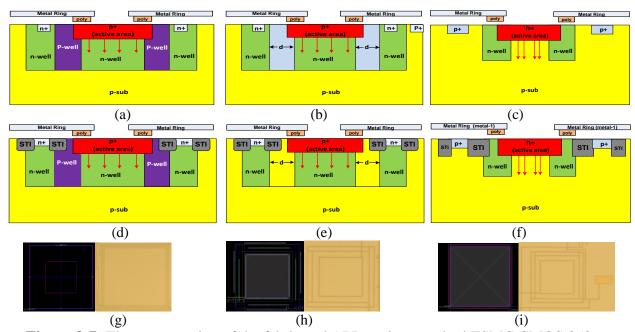

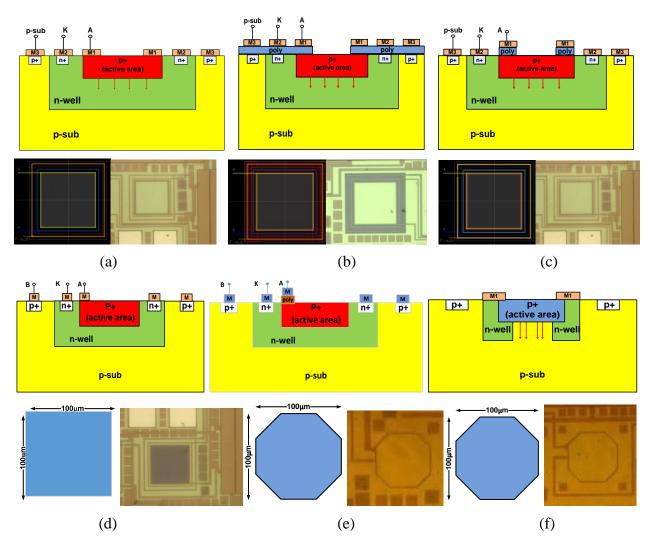

| Figure 3-7: The cross-section of the fabricated APDs using standard CMOS 350nm technology                                   |

| The p-well: APD1 (a), d-tub: APD2 (b), and n-well: APD3 (c) guard-rings. The same                                           |

| structures with STI (d)-(f). The layout-microphotograph of the APD1-3 (g)-(i)61                                             |

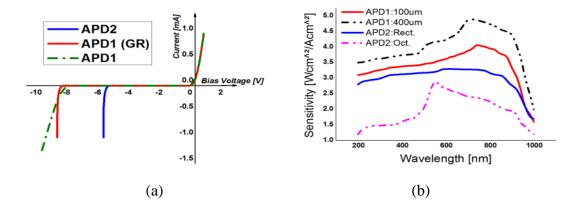

| Figure 3-8: The simulated I-V characteristics (a), and Sensitivity (b) of the SiAPDs63                                      |

| Figure 3-9: The breakdown-voltage variation in different temperatures: The breakdown due to                                 |

| avalanche (a) and tunneling (b)64                                                                                           |

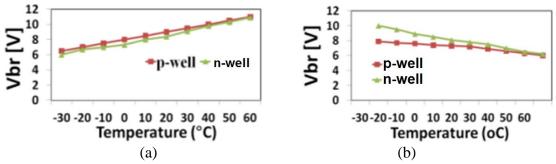

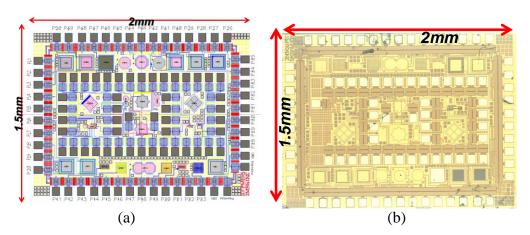

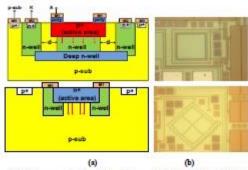

| Figure 3-10: The layout (a) and the microphotograph (b) of the integrated circuit developed                                 |

| using 0.18µm CMOS technology65                                                                                              |

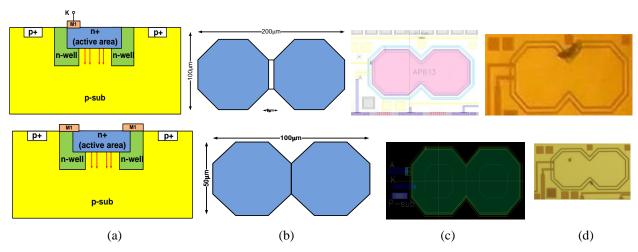

| Figure 3-11: The cross-section (first row), the layout (second row), and the microphotograph                                |

| (third row) of the fabricated APD1 (a), APD2 (b), and APD3 (c), APD6 (d), APD7 (e), and                                     |

| APD8 (f)67                                                                                                                  |

|                                                                                                                             |

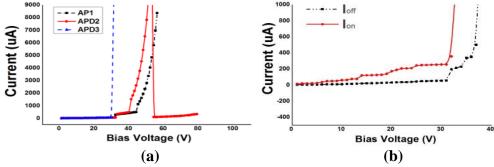

| Figure 3-12: The I-V characteristics of APD1-3 (a), and the multiplication-gain measurement technique (b)                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

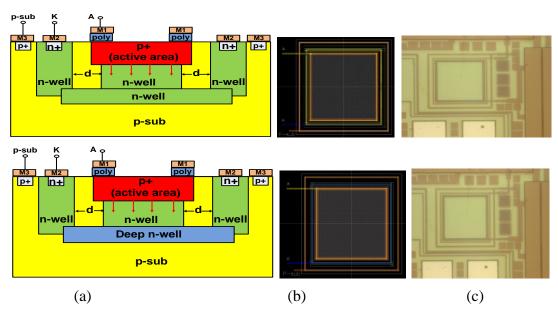

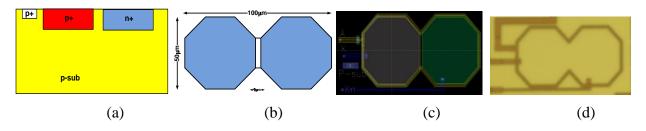

| <b>Figure 3-13:</b> The cross-section (a), the layout (b), and the microphotograph (c) of the fabricated APD4 (first row) and the APD5 (second row)                                                                                                                                                                                                                                                                                                                                                            |

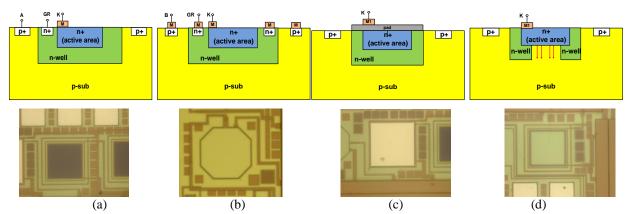

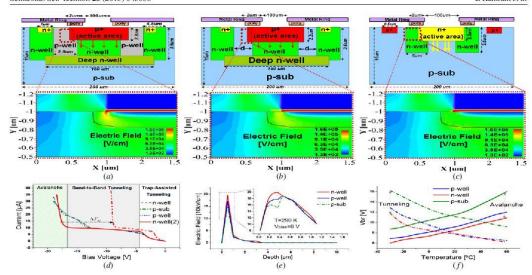

| <b>Figure 3-15:</b> The cross-section (first row), and the microphotograph (second row) of the fabricated APD9 (a), APD10 (b), APD11 (c) and APD12 (d)                                                                                                                                                                                                                                                                                                                                                         |

| <b>Figure 3-16:</b> The cross-section (a), the top view (b), the layout (c), and the microphotograph (d) of the fabricated APD13 (first row) and APD14 (second row)                                                                                                                                                                                                                                                                                                                                            |

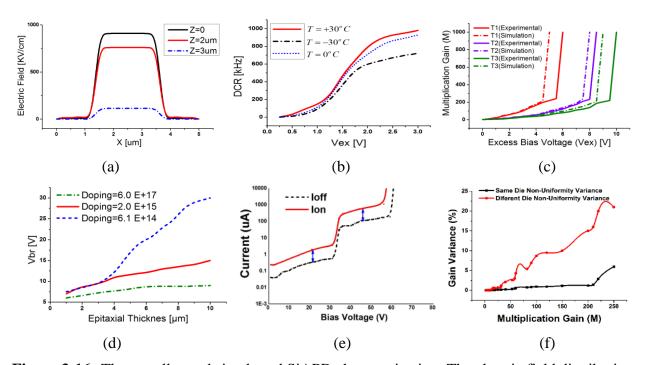

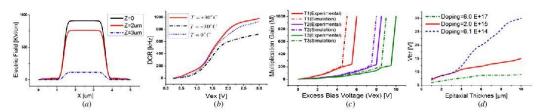

| <b>Figure 3-17:</b> The n-well guard-ring based SiAPD characterization: The electric field distribution (a), DCR-Vex variation (b). The M-V plot in different temperatures where $T1 = -250C$ , $T2 = -250C$ , $T3 = -250C$ (c), and the TCAD simulated Vbr dependence on the epitaxial layer thickness in different epitaxial p-type doping (d). The multiplication gain measurement (e), the Gain uniformity between APDs fabricated on the same die and on different dies in the same production batch (f). |

| <b>Figure 3-18:</b> The cross-section (a), the top view (b), the layout (c), and the microphotograph (d) of the fabricated APD15                                                                                                                                                                                                                                                                                                                                                                               |

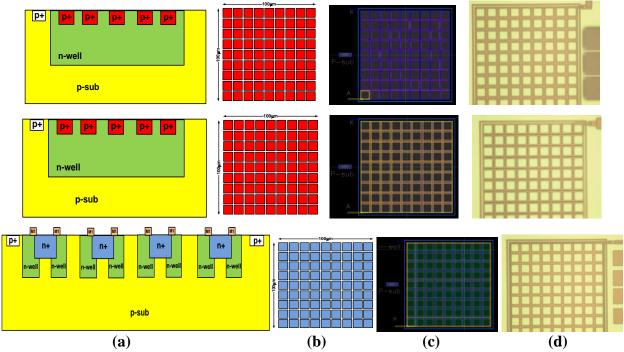

| <b>Figure 3-19:</b> The cross-section (a), the top view (b), the layout (c), and the microphotograph (d) of the fabricated APD16 (first row), APD17 (second row), and APD18 (third row)                                                                                                                                                                                                                                                                                                                        |

| <b>Figure 3-20:</b> The cross-section (a), the top view (b), the layout (c), and the microphotograph (d) of the fabricated APD19 (first row) and APD20 (second row)                                                                                                                                                                                                                                                                                                                                            |

| <b>Figure 3-21:</b> The cross-section (a), the top view (b), the layout (c), and the microphotograph (d) of the fabricated APD21 (first row) and APD22 (second row)                                                                                                                                                                                                                                                                                                                                            |

| <b>Figure 3-22:</b> The cross-section (a), the top view (b), the layout (c), and the microphotograph (d) of the fabricated APD23 (first row) and APD24 (second row)                                                                                                                                                                                                                                                                                                                                            |

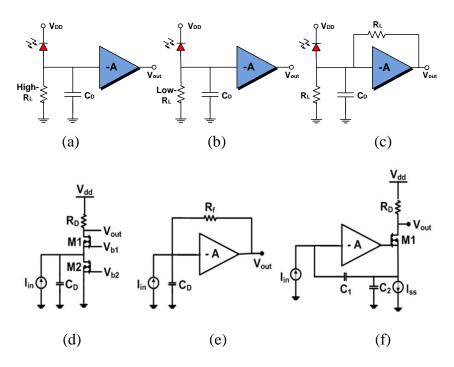

| <b>Figure 4-1:</b> Typical Optical amplifier structures: (a) High-impedance, (b) Low-impedance termination-resistor, (c) transimpedance amplifier. (d) common-gate TIA, (e) resistive-feedback TIA, (f) capacitive-feedback TIA                                                                                                                                                                                                                                                                                |

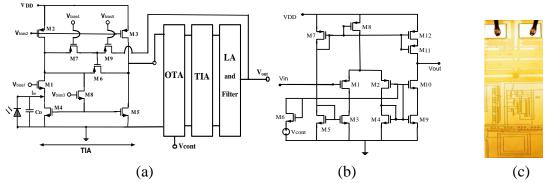

| Figure 4-2: Schematic diagram of the implemented tuneable distributed-gain TIA (a) and the                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTA (b). The microphotograph of the fabricated IC (c)88                                                                                                                                                                                                                                                                                                                                     |

| Figure 4-3: The gain (a), the input noise (b) and the output noise (c) of the implemented circui                                                                                                                                                                                                                                                                                            |

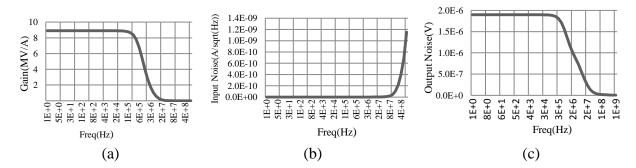

| Figure 4-4: The schematic of the implemented optoreceiver amplifier: TIA2 (a), and the                                                                                                                                                                                                                                                                                                      |

| microphotograph of the fabricated TIA (b). Here $M1, M4, M7$ : $WL = 2.50.35$ $M2, M5, M8$ : $WL = 100.35$ and for all other transistors $WL = 10.35$ 90                                                                                                                                                                                                                                    |

| <b>Figure 4-5:</b> The TIA gain (a), Frequency-response of the output voltage (b), the input-noise (c and the output-noise (d)                                                                                                                                                                                                                                                              |

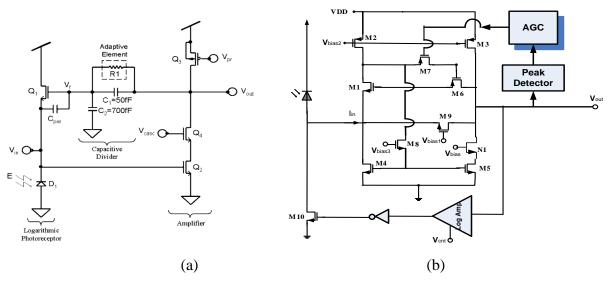

| <b>Figure 4-6:</b> (a) Circuit schematic of a state-of-the-art logarithmic transimpedance photoreceptor (b) Introduced logarithmic TIA (TIA3) with ambient light rejection and AGC loops91                                                                                                                                                                                                  |

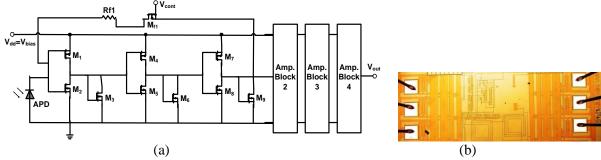

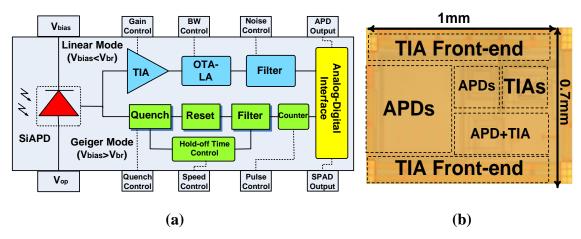

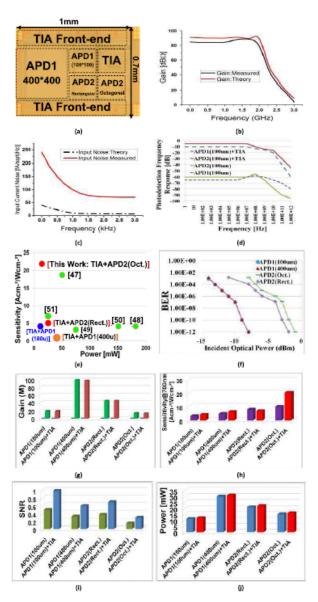

| <b>Figure 4-7:</b> Block diagram of proposed front-end photoreceiver IC working in linear and Geiger mode (a), and the microphotograph of the fabricated IC (b)                                                                                                                                                                                                                             |

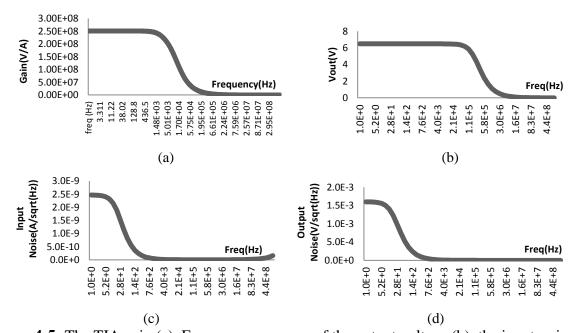

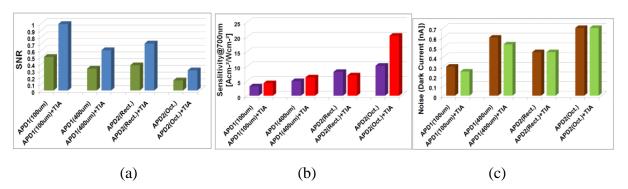

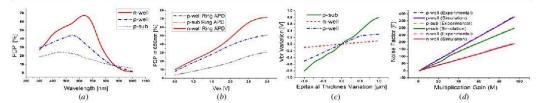

| <b>Figure 4-8:</b> Comparison the impact of integration on different parameters: the impact of integration on SNR (a), Sensitivity (b), and the dark-current noise (c)                                                                                                                                                                                                                      |

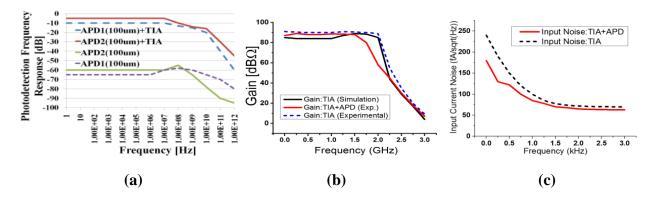

| <b>Figure 4-9:</b> Comparison of the PFR (a), gain (b) and input-current noise (c) characteristics of the integrated and individual TIA front-ends.                                                                                                                                                                                                                                         |

| Figure 5-1: Photon-Counting applications                                                                                                                                                                                                                                                                                                                                                    |

| Figure 5-2: Block diagram of the proposed NIRS brain imaging system                                                                                                                                                                                                                                                                                                                         |

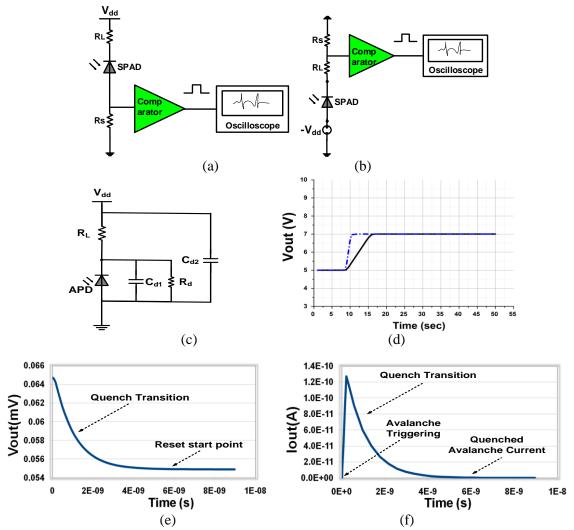

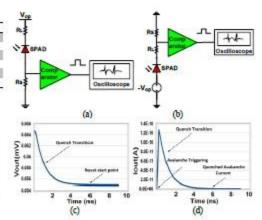

| <b>Figure 5-3:</b> Schematic of the passive quench circuit in two possible current-mode (a) and voltage-mode (b) configurations. The PQ equivalent circuit (c) and its simulated output signal (d). The output signal (d)-(g) with Cd1 = 3 pF, Cd2= 5 pF, VBR = 9 V, Vdd = 3 V RL= 200 kΩ, and Rd = 1 MΩ. The APD cathode voltage (g) and current (h) in response to single-photon arrival. |

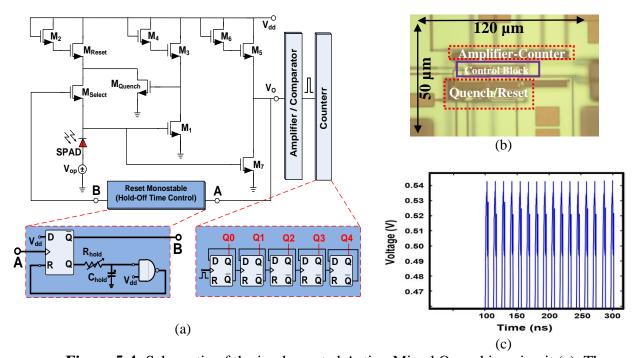

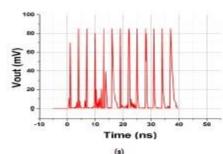

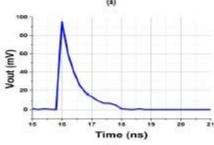

| <b>Figure 5-4:</b> Schematic of the implemented Active-Mixed Quenching circuit (a). The microphotograph of the fabricated IC (b), and the circuit response to multiple-photons arrival (d).                                                                                                                                                                                                 |

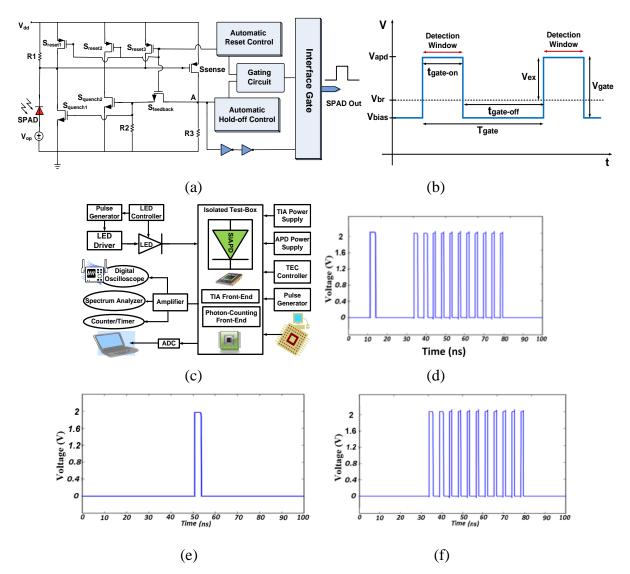

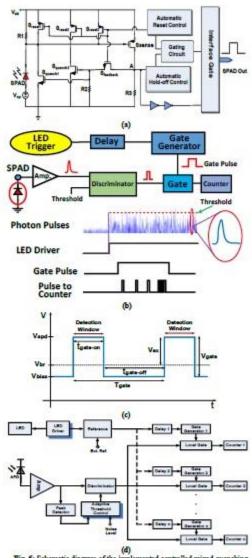

| Figure 5-5: Schematic diagram of the proposed controlled mixed quenching circuit (a) and the    |

|-------------------------------------------------------------------------------------------------|

| applied Gated SPAD biasing technique (b). The applied measurement set-up (c) and the            |

| output response (d). The APD cathode voltage in response to single-photon arrival (e) and       |

| multiple-photon arrivals between 35ns-80ns (f)                                                  |

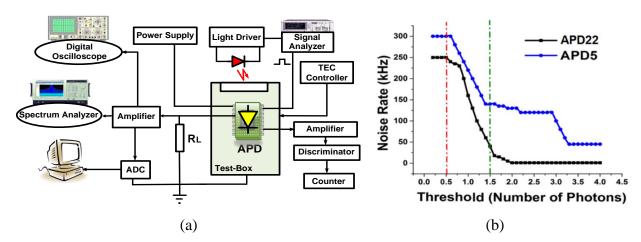

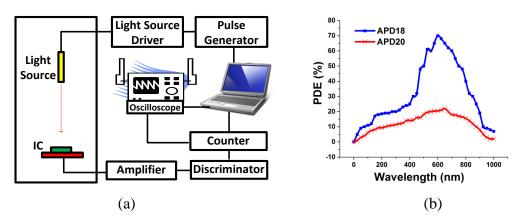

| Figure 5-6: Experimental setup for DCR measurement (a), and the measured noise rate vs          |

| threshold for APD5 and APD22 (b)                                                                |

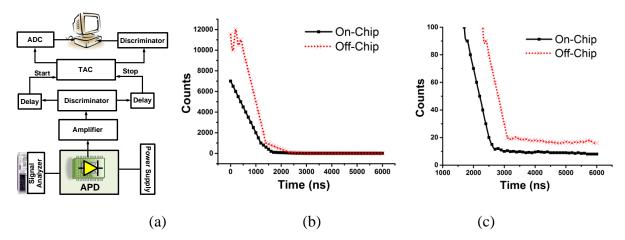

| Figure 5-7: Experimental setup for afterpulse measurement (a), and the measured noise rate vs   |

| threshold for APD5 (b) and with zoom in steady-state (c)                                        |

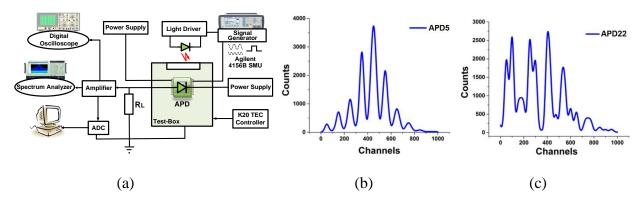

| Figure 5-8: Experimental setup for the multiplication-gain measurement (a), and the measured    |

| gain for APD5 (b) and APD22 (c)                                                                 |

| Figure 5-9: (a) Schematic view of the PDE measurement setup. (b) The PDE characteristics of     |

| the APD18 and APD20113                                                                          |

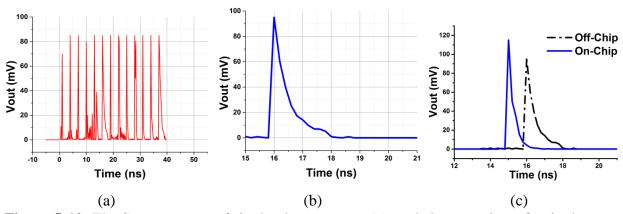

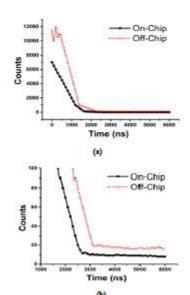

| Figure 5-10: The Scope capture of single-photon events (a), and close-up view of a single event |

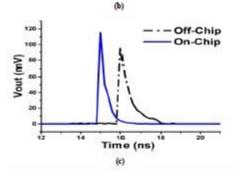

| (b). Comparison of off-chip and on-chip integrated photon-counter responses (c)113              |

#### LIST OF ABBREVIATIONS

ABC Automatic (adaptive) bias control

ADC Analog to digital converter

AGC Automatic gain control

APD Avalanche photodiode

AQC Active quenching circuit

AQRC Active quench and reset circuit

BER Bit error rate

BW Bandwidth

CF-TIA Capacitive-feedback TIA

CG-TIA Common-gate TIA

CMC Canadian microelectronic corporation

CMQR Controlled Mixed Quench-Reset

CMOS Complementary metal-oxide semiconductor

CMRR Common Mode Rejection Ratio

CSF Cerebrospinal fluid

CW Continuous wave

DA Discrete Amplifier

DAD Dual APD detector

DGTIA Distributed-gain TIA

DMUX Demultiplexer

DTMOS Dynamic-threshold voltage MOSFET

EEG Electro-encephalography

FD Frequency-domain

FEC Forward error correction

fMRI Functional magnetic resonance imaging

fNIRS Functional near infrared spectroreflectometry

GBW Gain-bandwidth product

GM-APD Geiger-mode avalanche photodiode

GM-SiAPD Geiger-mode silicon avalanche photodiode

GPC Gated photon-counting

HCI Human-computer interface

HPF High-Pass Filter

ICMR Input common-mode range

LA Limiting Amplifier

LED Light-emitting diode

LogTIA Logarithmic transimpedance amplifier

LPF Low-Pass Filter

MEG Magneto-encephalography

MGPC Multi-Gate Photon-Counting

MQC Mixed quenching circuit

NAF Negative Avalanche Feedback

NEP Noise equivalent power

NIR Near-infrared

NSDD Null source-detector distance

NSDS Null source-detector separation

OTA Operational Transconductance Amplifier

PD normal PIN photodiode

PDE Photon Detection Efficiency

PDP Photon Detection Probability

PET Positron emission tomography

PQ Passive quenching

PQC Passive quenching circuit

PMT Photomultiplier tubes

RF Radio frequencies

RF-TIA Resistive-feedback TIA

SAM Separate absorption multiplication

SAPD Single-photon avalanche photodiode

SDD Source-detector distance

SiAPD Silicon CMOS avalanche photodiode

SNR Signal-to-noise ratio

SPAD Single-photon avalanche photodiode

TCSPC Time-correlated single-photon counting

TD Time-domain

TIA Transimpedance amplifier

TR Time-resolved

## LIST OF APPENDICES

| APPENDIX 1 – LIST OF PUBLICATIONS                          | 134         |

|------------------------------------------------------------|-------------|

| APPENDIX 2 – PAPER #1: EFFICIENT PREMATURE EDGE BREAKDOWN  | PREVENTION  |

| IN SIAPD FABRICATION USING THE STANDARD CMOS PROCESS       | 142         |

| APPENDIX 3 – PAPER #2: LOW-NOISE, HIGH-GAIN TRANSIMPEDANCI | E AMPLIFIER |

| INTEGRATED WITH SIAPD FOR LOW-INTENSITY NEAR-INFRA         | RED LIGHT   |

| DETECTION                                                  | 149         |

| APPENDIX 4 – PAPER #3: A LOW-POWER PHOTON-COUNTER          | FRONT-END   |

| DEDICATED TO NEUROVASCULAR BRAIN IMAGING                   | 162         |

#### CHAPTER 1 INTRODUCTION

### 1.1 Motivation and General Background

The circulatory system is one of the main building blocks of the human body which is controlled by both brain and heart. Due to the importance of these two critical organs, monitoring neurovascular dynamics is of great value for clinical and brain-machine interface (BMI) applications, and is a challenge in biomedical imaging endeavors. The neurovascular diseases are of great social impact, as they are the frequent cause of death in the world and the most frequent cause of disability in adults [1], [2]. Stroke (cerebrovascular accident or CVA) is a leading cause of adult disability and the third leading cause of death in the United States, causing death off around 157,000 people per year with an estimated society cost of 58 billion dollars only in 2006 [3]. The medical imaging techniques have widespread applications include diagnosing diseases. Thanks to new technologies such as radio-frequency (RF), electromagnetic, ultrasound, and infrared detection, the new bio-imaging systems are applied in different aspects and activities of neurological and cardiovascular monitoring and treatment [1].

The use of diagnostic brain imaging has increased dramatically over the past decade. Table 1.1 shows the comparison of the most common brain imaging techniques [1]. Common brain monitoring systems are bulky, non-portable and invasive and require sophisticated and expensive hardware and software tools (e.g. a typical 1.5 Tesla MRI cost is up to 3M\$) [4]. The commonly used non-invasive brain imaging techniques are electro-encephalography (EEG), positron emission tomography (PET), functional magnetic resonance imaging (fMRI), and functional near-infrared spectroscopy (fNIRS) [5]. Only EEG and fNIRS can be realized using equipment that is small and light enough to be worn continuously while allowing body movements which is important especially for neonates, long-term monitoring and BMI applications. Some portable EEG systems have been developed for brain imaging [6], however EEG is not ideal for human-computer interface (HCI) [7], it is susceptible to artifacts from eye and facial movement, as well as by electronic devices, it requires gel in the participant's hair, and a long set-up time, and it is not spatially determined [8].

**Table 1.1:** Comparison of various brain imaging techniques.

|            | Image/Data Quality | Temporal<br>Resolution | Spatial<br>Resolution              | Mobility<br>Tolerance | Scale  | Safety        | Cost               |

|------------|--------------------|------------------------|------------------------------------|-----------------------|--------|---------------|--------------------|

| MRI        | High               | Low (~30s)             | Very-High<br>(3-6 mm)              | Medium                | Bulky  | High          | High               |

| fMRI       | High               | Low (~30s)             | Very-High<br>(3-6 mm)              | Medium                | Bulky  | High          | High               |

| X-Ray      | Low                | Medium (1s-10s)        | Very-High<br>(1 mm)                | Low                   | Bulky  | Low*          | Low                |

| CT-Scan    | Low                | Medium<br>(10s)        | Very-High<br>(1mm)                 | Low                   | Bulky  | Low*          | Low                |

| Ultrasound | Low                | Hi (~1ms)              | Depends on the probe element width | Low                   | Medium | Very-<br>High | Low                |

| PET        | High               | Low<br>(30s-40s)       | High<br>(5mm)                      | Very-high             | Bulky  | Low*          | Very-high (1-2M\$) |

| SPECT      | Medium             | Very-Low               | Medium<br>(1cm)                    | Medium                | Bulky  | Low           | High<br>(0.5-1M\$) |

| MEG        | Medium             | Very-High<br>(~1ms)    | Low (1cm - 2cm)                    | Medium                | Bulky  | Low           | High               |

| EEG/ERP    | Medium             | Very-High (~1ms)       | Medium<br>(1cm)                    | Low                   | Small  | High          | Low                |

| fNIRS      | High               | High<br>(0.5s-1s)      | Low-Medium (0.5cm-2cm)             | Medium                | Small  | Very-High     | Very-low           |

\*Ionizing Radiation

In contrast to the other bulky and high-voltage brain-imaging systems suffering from electromagnetic interferences and slight movement artifacts, fNIRS is relatively robust against motion artefact, compact (portable), low-voltage and immune to electromagnetic interferences with the advantages of ease of use, low-absorption (no heating), and low-energy (no ionization) [8]. It offers a direct non-invasive, minimally intrusive and safe tool for real-time and long-term continuously monitoring of biological signals (such as HbO, HbR and HbT) with high temporal-resolution and low-cost. fNIRS obtain information on cerebral oxygenation, activation and blood volume, not otherwise obtained with any single method and at a remarkably low-cost. It can be considered as a diagnosis and investigation technique for different neurological diseases, such as, stroke and epilepsy seizures that require continuous monitoring of patients at the hospital, which is a costly endeavor. It is a potential neuroimaging technique that can non-invasively monitor the rapid changes in both fast-neuronal (with ms temporal-resolution) and slow-hemodynamic signals (regional cerebral blood volume and tissue oxygenation).

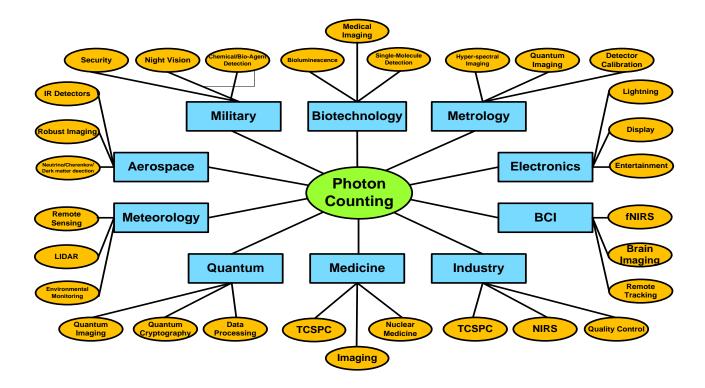

Since cerebral blood volume and tissue oxygenation are indirect indicators of neuronal activity, such imaging information is of great value in the understanding, evaluation, and treatment of the common neurological diseases such as stroke and epileptic seizures. It is the best choice for Neonatology and auditory studies. NIRS can also be applied in light detection and ranging (LIDAR), photon-counting, fiber-optic communication, brain-computer interface, tele-control by thought, brain imaging (epilepsy, seizure, migran, schizophernia, credibility assessment, lie detection), human performance assessment, depth of anesthesia monitoring, pain assessment, virtual reality, neurorehabilitation, autism, breast cancer screening, and muscle oxygenation.

All these advantages have made NIRS the system of choice for neuroimaging and a hot topic of research towards developing a miniaturized and portable system for real-time brain imaging applications. Work is going on in different research groups to improve the performance of NIRS system [9], [10], [11]. However, to date the realization of this potential has not materialized with current commercial devices due to high energy-consumption and size issues of the fNIRS photodetector. The Imagine group of Polytechnique Montreal is leading the development of a portable fNIRS system for real-time brain imaging. This thesis covers the design and implementation of the main building blocks of a portable fNIRS photoreceiver including avalanche photodiode, transimpedance amplifier and photon-counting circuits.

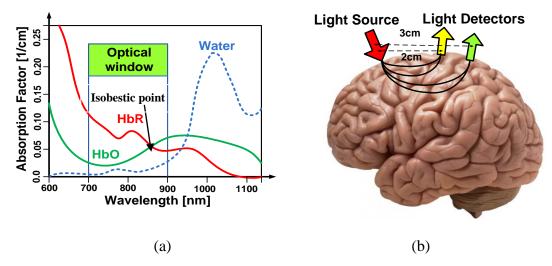

In fNIRS, the brain tissue is penetrated by near-infrared (NIR) radiation and the reflected signal is observed to investigate the brain neurovascular activities. In NIR range (650nm-950nm), water has relatively low absorption while oxy- and deoxy-hemoglobin have high absorption (Figure 1.1 (a)). Due to these properties, NIR light can penetrate biological tissues in the range of 0.5-3 cm allowing investigation of relatively deep brain tissues, and ability to differentiate between healthy and diseased tissues based on their optical properties (Figure 1.1 (b)). When light enters a tissue, its propagation is mainly governed by two physical phenomena, i.e., light absorption and scattering.

**Figure 1-1:** The NIR optical window (a), and the banana shape path of light between optodes in different deparation distances (b).

There are certain substances in human tissues for which the spectra within the NIR wavelengths are well defined. Some of these absorbers such as water, melanin, and bilirubin do not change in concentration with time. But concentrations of some other absorbers such as oxygenated hemoglobin (HbO) and deoxy-hemoglobin (HbR) are strongly related to the tissue oxygenation and metabolism. Thus the absorption changes can provide clinically useful physiological information. The range from 700 nm to 900 nm called optical window (also called Therapeutic or near infrared window) is defined which is considered useful for the non-invasive NIR measurements. The NIRS is based on the Beer-Lambert law that explains the light attenuation (A) when passes through an absorbing medium as follow:

$$I(L) = I(0) e^{-\mu_a L} \Rightarrow A = \mu_a L = \varepsilon CL = \ln\left(\frac{I(0)}{I(L)}\right)$$

(1.1)

where I is the light intensity, L (called path-length) is the distance between the light entrance points and its exit point (source-detector distance), C is the concentration,  $\mu_a$  is the absorption coefficient of the medium, and  $\varepsilon$  is the molar absorption coefficient. For a medium having more than one absorbing compounds, overall attenuation is the linear sum of individual contributions:

$$A = \ln\left(\frac{I(0)}{I(L)}\right) = \left(\varepsilon_1 \, C_1 + \varepsilon_2 \, C_2 + \varepsilon_3 \, C_{31} + \dots + \varepsilon_n \, C_n\right) L \tag{1.2}$$

For human tissues, however, absorption is not the only phenomena. Light scattering also exists and is rather a dominant phenomenon. As scattering changes the optical path-length of the light propagation, absorption characteristics of the medium are difficult to quantify due to light scattering. Thus, Beer-Lambert's law was modified to be applicable in the human tissue. The modified Beer-Lambert's Law is given by:

$$A = \ln\left(\frac{I(0)}{I(L)}\right) = \varepsilon CL. DPF + G = \mu_a L. DPF + G$$

(1.3)

where G is the term added to compensate for scattering losses, and DPF is the differential pathlength factor. The two main chromophores in tissue for the NIR window are HbR and HbO. Thus the absorption coefficients at two wavelengths can be given by:

$$\begin{bmatrix} \mu_a(\lambda_1) \\ \mu_a(\lambda_2) \end{bmatrix} = \begin{bmatrix} \varepsilon_{HbR}(\lambda_1) & \varepsilon_{HbO}(\lambda_1) \\ \varepsilon_{HbR}(\lambda_2) & \varepsilon_{HbO}(\lambda_2) \end{bmatrix} \times \begin{bmatrix} HbR \\ HbO \end{bmatrix}$$

(1.4)

The wavelengths should be selected properly to minimize the cross-talk between HbR and HbO. Usually 2 different wavelengths are chosen in either sides of isobestic point where the absorption are equal (eg. 780nm & 870nm). More wavelengths can differentiate between more chromophores such as water, lipid, melanin, cytochrome c oxidos ( $C_tO_x$ ), HbR and HbO.

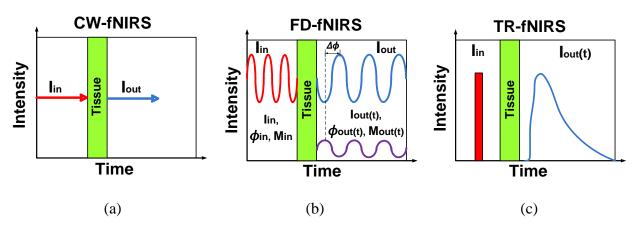

There are currently three fundamental types of NIR instruments used for probing the neurovascular response. A qualifier to each of these systems is its measurement geometry, which can be either transmission geometry or a reflective geometry. These three main types of fNIRS techniques which impose applying different types of instrumentation are:

#### (1) Continuous-wave (CW) or continuous-intensity (CI) fNIRS:

In this technique (Figure 1.2(a)), a continuous-wave light source is used and the intensity variation ( $\Delta I$ ) of the input continuous NIR light are measured at the output to determine only the relative changes. However, using iterative measurements by changing a variable (such as light intensity, wavelength, source-detector distance), the quantitative and absolute variation can also be determined. CW-fNIRS can determine the O2, cytochrome c oxidase ( $C_tO_x$ ) and arterial hemoglobin saturation ( $SaO_2$ ) levels as critical vital signals [12].

Figure 1-2: Different types of NIRS systems: CW-fNIRS (a), FD-fNIRS (b), and TR-fNIRS (c)

#### (2) Intensity-Modulated (IM) or Frequency-Domain (FD) fNIRS:

This technique (Figure 1.2(b)) uses an intensity-modulated light source (usually at RF) and records the intensity (I(t)), the phase-shift ( $\phi$ (t)), and the modulation-depth (or Modulation-Index: M(t)) at the output. Here the intensity (amplitude) of the applied continuous-wave source is modulated at a high radio frequency (~100MHz) or even lower frequencies using heterodyning (combining or mixing two frequencies to create a new desired frequency) to reduce the ADC complexity and improve the SNR. FD intrinsically yields more information than CW but due to high-noise level in phase data its sensitivity to cerebral hemodynamics is weak [13], [14]. Furthermore, the phase information (typically used to measure scattering) has not been shown to provide robust measures of cerebral hemodynamic variation [13].

#### (3) Time-Resolved (TR) or Time-correlated single-photon system (TCSPS):

It measures the temporal distribution of output light (I(t)) resulting from an ultrafast pulse (1-200 ps) input NIR light source (Figure 1.2(c)). Measurements at multiple wavelengths enable estimations of the concentrations of different absorbers. This technique, which is called the time-domain (TD) or time-pulsed NIRS, measures the time-of-flight (TOF) of photons and acquires information at all frequencies simultaneously at desired depth. CW and TD have the same contrast to noise ratio [13], but TD have a better contrast to background ratio and also better depth sensitivity and resolution with the cost of using more complicated circuitry and higher expense [13].

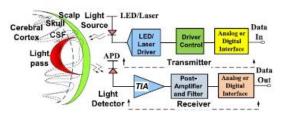

Towards developing a miniaturized and low-power portable fNIRS with low-cost, the CW-fNIRS would be a proper technique comparing to other bulky and high-power methods requiring more complicated circuits and extra building blocks. The typical CW-fNIRS system consists of NIR light source, photodetector, data acquisition module, control unit, and a processing block. The light source is placed on the surface of the head (scalp) and it generates light in the NIR range. Generally, the light sources used for NIRS system are either LEDs or laser diodes that emit NIR light with optical power within a range of 5 mW to 17 mW at discrete wavelengths (for example 735, 840, and 940 nm). In comparison to laser diodes, LEDs are easy to reproduce, less expensive, have lower-power and larger emitting regions, and longer lifetimes. The fNIRS photodetector front-end includes a photodetector that monitors the intensity of the reflected NIR signal, Quench-Reset circuit, Transimpedance Amplifier (TIA), Limiting Amplifier (LA), post amplifiers and filters. Although fNIRS is compact when compared to other brain imaging systems, but current commercially available NIRS devices are not miniaturized enough in order to be integrated with other wireless and portable medical imaging systems intended for bedside long-term brain monitoring. It also suffers from low-spatial resolution, high-level noise (movement, heart-rate, breathing rate, and low-frequency oscillations), susceptible to the internal and ambient light/temperature and bias voltage variations. Integrating the photodiode and corresponding circuitries on the same chip and on-chip multi-mode operation using smart CMOS image sensor concept has not been considered yet in the literature for fNIRS application. Using smart CMOS image sensor concept for fabrication of photodiode and photodetection circuitry and integrating them on the same chip with ability to works on different modes of operations, leads to a more compact and miniaturized design.

## 1.2 Background Theory of NIR Photodetectors (Theoretical framework)

## 1.2.1 Photodetection using Solid-State Materials

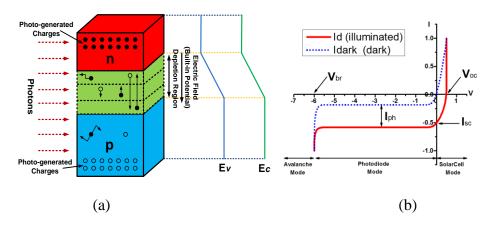

Semiconductor materials are used to fabricate photodetectors in order to detect photons (light) by their photo-sensitive characteristics and converting light into electricity. They can be used for direct detection of light, X-ray, gamma-rays, and particles such as electrons or neutrons. A photodiode is a reverse biased p—n junction as shown in Figure 1.3(a), whereas photons are absorbed everywhere and an electron-hole pair (EHP) is generated [15]. An electron in the

valence-band moves to the conduction band by absorbing energy from a photon upon generation of an EHP. Wherever the electric-field is present, electrons and holes are separated and transported in the opposite directions. Since the electric-field impact in a p-n junction occurs mostly in the depletion-region, the photocarrier-generation region is mostly confined to the depletion-region [16], [17]. Photodiodes can be produced from different materials such as Si, Ge, and III-V semiconductor compounds (obtained by combining group III elements (eg. Al, Ga, In) with group V elements (eg. N, P, As, Sb)) [18]. The direction of the incident-light and the p-n junction are often designed to be perpendicular to the p-n surface, instead of parallel to it. As shown in Figure 1.3(b), the photodiode has an I-V relation as[16]:

$$i = i_s \left[ exp\left(\frac{eV}{k_BT}\right) - 1 \right] - i_p \tag{1.5}$$

The photocurrent  $(i_p)$  is proportional to the photon-flux [17]. The depletion-region in a p-n junction constructed in common CMOS technology is formed when the free holes/electrons in ptype/n-type materials diffuse across the junction. The holes diffuse into the n-type region and leave negatively charged ions in the p-type region, and the reverse applies to the electrons. This creats the depletion-region, which introduces a built-in potential to realize the photodetector. When a photon is absorbed anywhere close to the depletion-region, an electron-hole pairs (EHPs) separation occurs, and they move based on the direction of the electric-potential. Some photons reaching the depletion-region are absorbed, transferring their energy to the outer-shell electrons, and generating EHPs. The built-in potential then forces the holes to move toward the p-type region and the electrons toward the n-type region, and the moving holes and electrons result in an electrical current which is called the photocurrent. In order to utilize a p-n junction as a photodiode, its bias condition has to be carefully chosen. Three modes can be observed as plotted in Figure 1.3(b), which are the avalanche (large reverse-bias) [19], photodiode or image sensor (slight reverse-bias) [20] and solar-cell (forward-bias) [21] modes. The photodiode itself can be divided into three different regions of operation: open-circuit (photovoltaic), short-circuit, and reverse-biased (photoconductive-mode). When no light emits and the photodiode is in darkness, the current is negative but very close to zero which is mostly the thermally-activated diffusioncurrent of the junction and called the dark-current. When the photodiode is illuminated, the absolute net current becomes larger because of the photo-current  $(I_{ph})$ , which is subject to change with different amounts of electron-hole pairs generated and separated by the built-in potential

[15]. The increase of the photo-current is proportional to the incident-light intensity. Common silicon photodetectors are essentially PIN diodes that the incident-light generates EHPs in the depletion-region contributing to the reverse current. They can work on the same aforementioned three bias-regions as mentioned for p—n diodes. A PIN diode is a p—n junction with a wide intrinsic (lightly-doped) layer sandwiched between p and n layers, in which the p-type and n-type regions are typically heavily-doped because they are used for ohmic-contacts.

The wide intrinsic-region makes the PIN diode suitable for attenuators, fast-switches, photodetectors, and high-voltage power-electronics applications with the cost of less rectification. Using the intrinsic-region increases the depletion-width which increases the photon-absorption depth so improves the sensitivity to red and IR light. It also decreases the junction-capacitance, thereby reducing the RC-delay constant and the response-time of the photodetector [22]. The Photo-transduction in a photodiode is based on the EHPs generation when the energy of the incident-photon on the detector is greater than the bandgap of the material ( $h\nu > E_g$ ). Due to the indirect-gap nature of silicon (where the photon-absorption transitions typically take place from valence to conduction band states which are above the conduction band edge), in silicon-based photodetectors, the maximum responsivity occurs on wavelengths which are substantially shorter than the bandgap-wavelength [17].

**Figure 1-3:** The cross-section view of a p-n junction showing the photogeneration regions forming the photo-current and the band-diagram (a), and the I-V curves of a p-n junction photodiode in dark and illuminated conditions.  $E_v$  and  $E_c$  indicate the valence-band and the conduction-band energies, respectively.  $V_{oc}$  and  $I_{sc}$  are the open-circuit voltage and short-circuit current when there is illumination applied, respectively.

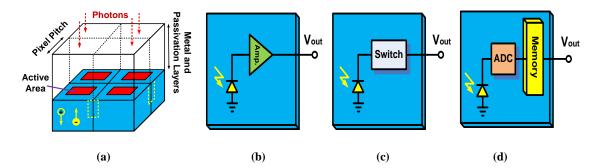

#### 1.2.2 CMOS Image Sensors

In general, several concerns are linked to the pixel design, such as its size (pixel pitch), active region (where photons penetrate and get absorbed), and periphery effect. Smaller pixel size however offers a better image quality with more details but suffer from higher noise and crosstalk and also non-uniformity and sensitivity issues[15]. The CMOS image sensors (called pixel as well) construct the building blocks of many imaging devices like digital cameras and camera modules. A pixel usually includes a photodetector and the necessary circuit to perform signal readout and/or processing. Depending on the principle of pixel operation, it can be referred to as an active pixel sensor (APS), a passive pixel sensor (PPS), or a digital pixel sensor (DPS) as shown in Figure 1.4 and explained more in the details in [15], [23]. The PPS (the simplest and the earliest CMOS image sensor), includes a photodiode and a switch (row-select transistor). The APS (the most popular CMOS image sensor) usually equips the pixel with an active-device including an amplifier or a buffer and can be built with only one (or up to several) transistor(s). The DPS consists of more complex blocks, normally an analog-to-digital converter (ADC) and a memory cell, to perform in-pixel signal processing. The image sensors offer simple circuitry with high fill-factor (FF) and low-noise for different imaging applications, however their sensitivity and speed are limited. So for the low-level light detection (LLLD), the avalanche photodiode (APD) can be used as a highly-sensitive and fast alternative detector, which has been explained in follow.

**Figure 1-4:** The illustration of concerns for pixel design (a), and the block diagrams of (b) APS, (c) PPS, and (d) DPS with in-pixel ADC structures.

#### 1.2.3 Avalanche Photodiodes (APDs) and Impact Ionization

An avalanche photodiode is a strongly reverse-biased photodiode, where the applied electric-field across the junction, exceeds the critical value necessary to cause impact-ionization. The APD operation is based on conversion of the energy of photons into free charge carriers in the semiconductor bulk and their further multiplication via the process of impact-ionization. In contrast to the normal photodiodes, APD has a built-in region with very high electric-field. The charge-carriers by passing through this region acquire enough energy to produce more EHPs by impact-ionization and generate the avalanche of EHPs leading to a high output photo-current [24]. Figure 1.5 shows the principle operation of APDs. The absorbed photon, generates an EHP (an electron in the conduction-band and a hole in the valence-band). The electron ionizes an atom causes generating another EHP and so on. The required energy for an electron to ionize an atom is defined by relaxing the kinetic-energy of the electron in a high electric-field. The ability of an electron or a hole to trigger ionization is quantified by ionization-coefficients which increase with electric field and decrease with temperature. The increase of the ionization coefficient by electricfield is due to electron acceleration by electric-field and its decrease by increasing temperature is due to an increasing frequency of collision that decreases the probability of a carrier gaining enough energy to cause ionization.

**Figure 1-5:** Representation of impact-ionization process in an APD (a), and the Energy Band diagram of a reverse biased PIN structure where impact-ionization process occurs as the electrons travels through the high electric-field region (b).

Widening the depletion-region (to maximizing the photon-detection probability) and reducing the thickness of the multiplication-region (to minimize the possibility of localized uncontrolled avalanches cause instabilities and microplasmas) elevate the APD performance and sensitivity [25], [26]. Maximizing the ratio of electrons to holes injected in the multiplying region reduces the noise generated in the APD due to the higher ionization-coefficient of electron [24]. The "Impact Ionization" is the process by which one energetic charge carrier (an electron or hole) can lose energy by the creation of other charge carriers (other EHPs) [27]. The electron and hole ionization coefficients ( $\alpha$  and  $\beta$  respectively), determine the avalanche multiplication-gain and breakdown characteristics of APD [28], [29]. APDs use the impact ionization principle to detect and amplify very low light signals. In order to have a high-gain, low-noise APD, the ionizationrate for electrons and holes needs to be very different. The silicon has the largest ionization rate difference between electrons and holes among all semiconductors (electrons can ionize 50 times to 1000 times more readily than holes depending on the electric field amplitude), with the cost of its low cut-off wavelength around 1 µm. So it is an ideal material to implement highly-sensitive and low-noise photodetectors. The probability for initiating impact ionization is quantified as the impact ionization coefficient. It is defined as the reciprocal of the average distance travelled by an electron or hole to produce an electron-hole pair. Materials with very different value for  $\alpha$  and β, such as in silicon can create less impact ionization noise because only one type of carrier is dominant during the ionization process. The ionization coefficients ( $\alpha$  and  $\beta$ ) are strong function of electric field in the multiplication region. Electric field, however, also depends on the bias voltage, doping-profile, and the device geometry. Electron ionization is measured by shining light from the p+ side. Photon-excited electrons are injected into the intrinsic layer while holes are swept to the left. The hole-ionization is measured by illuminating light from the n+ side, injecting holes into the intrinsic layer. Wide bandgap semiconductors (such as GaAs) are associated with a high breakdown voltage. This is due to a larger electric field required to generate carriers through impact mechanism. InGaAs with narrow band gap is also a popular material in infrared detectors and some short wave infrared cameras. It also has lower multiplication noise than germanium when used as the active multiplication layer of an avalanche photodiode, and it also has a low breakdown-voltage [30], [31]. If an APD has the internal gain of M, for a single detected photon, the avalanche process produces M carriers [32]. The maximum value of M is equal to  $\alpha/\beta$ , in which  $\alpha$  is the ionization coefficient of electrons and  $\beta$  is the ionization coefficient of holes. Increasing the avalanche-gain of M is achievable by widening the multiplication-region. A wider Multiplication-region increases the M (accompanied with a higher noise-level) and reduces the response-bandwidth. By further increasing the bias, an APD gain becomes virtually infinite. This biasing regime is known as Geiger-mode of operation and the APD called Single-Photon Avalanche Diode (SPAD). In this case a single electron can start the avalanche process until an external circuit (Quench circuit) limits the avalanche current and preventing the device damage. [33], [32].

### 1.2.4 Dark-Current and Tunneling

A dark-count is an avalanche event caused by non-photogenerated carriers, which as depicted in Figure 1.6(a), can be originated from: diffusion from neutral-regions, thermal-generation, release from a charge-trap, Shockley-Read-Hall (SRH) generation via impurities, or from band-to-band tunnelling in the depletion-region [34], [35]. Very-high electric-fields can also increase the dark-count rate (DCR), since the carrier-emission probability from generation centers is strongly enhanced by barrier-lowering, Frenkel-Poole effect and the photon-assisted tunneling [36]. The DCR can produce an output-pulse indistinguishable from the one originated by a detection-event. Dark-count noise increases with temperature, as the thermal carrier generation increases and so the probability of avalanche. The thermal-generation is strongly dependent on the fabrication process, which determines the concentration of traps, the breakdown-voltage and the avalanche probability. On the contrary, tunnelling-generation depends on the doping-profile and the bias-voltage, and its temperature dependence is weak [31]. Designing an APD with low-DCR is critical especially for photon-starved applications. However, a medium range noise can be acceptable as it is applied in current commercial imaging systems which can sustain relatively high DCRs (around few kHz) due to the relatively high-level of background noise [37].

The carrier transport in solid-state electronic devices can be explained based on the quantum and statistical mechanics. The role of quantum mechanics is calculating the carrier-density by introducing the density of states, and filling-factor of the carriers [38]. Beside the role of quantum mechanics in carrier transport calculation, some particular quantum behaviors affect single-photon counter responses [39]. The main quantum effects observed in SPADs include Tunneling phenomena and Bistability/multistability phenomena. The Quantum-dot single-photon detectors (QD-SPDs) are based on a transistor structure in which the conducting channel is close to a layer