**Titre:** Opérateurs et engins de calcul en virgule flottante et leur application à la simulation en temps réel sur FPGA

Title: application à la simulation en temps réel sur FPGA

**Auteur:** Tarek Ould-Bachir

Author:

**Date:** 2013

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Ould-Bachir, T. (2013). Opérateurs et engins de calcul en virgule flottante et leur application à la simulation en temps réel sur FPGA [Ph.D. thesis, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/1231/>

Citation:

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/1231/>

PolyPublie URL:

**Directeurs de recherche:** Jean Pierre David, Jean Mahseredjian, & Frédéric Sirois

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

OPÉRATEURS ET ENGINS DE CALCUL EN VIRGULE FLOTTANTE ET LEUR

APPLICATION À LA SIMULATION EN TEMPS RÉEL SUR FPGA

TAREK OULD BACHIR

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIÆ DOCTOR

(GÉNIE ÉLECTRIQUE)

AOÛT 2013

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée:

OPÉRATEURS ET ENGINS DE CALCUL EN VIRGULE FLOTTANTE ET LEUR

APPLICATION À LA SIMULATION EN TEMPS RÉEL SUR FPGA

présentée par: OULD BACHIR Tarek

en vue de l'obtention du diplôme de: Philosophiæ Doctor

a été dûment acceptée par le jury d'examen constitué de:

M. BRAULT Jean-Jules, Ph.D., président

M. DAVID Jean Pierre, Ph.D., membre et directeur de recherche

M. MAHSEREDJIAN Jean, Ph.D., membre et codirecteur de recherche

M. SIROIS Frédéric, Ph.D., membre et codirecteur de recherche

M. LANGLOIS Pierre, Ph.D., membre

M. LE-HUY Hoang, Dr. Eng., membre

*It's simple. We... kill the Batman.*

— Heath Ledger, a.k.a The Joker.

Oh ! les gens bienheureux !... Tout à coup, dans l'espace,

Si haut qu'il semble aller lentement, un grand vol

En forme de triangle arrive, plane et passe.

Où vont-ils ? Qui sont-ils ? Comme ils sont loin du sol !

Regardez-les passer ! Eux, ce sont les sauvages.

Ils vont où leur désir le veut, par-dessus monts,

Et bois, et mers, et vents, et loin des esclavages.

L'air qu'ils boivent ferait éclater vos poumons.

— Extraits des oiseaux de passage, poème de Jean Richépin.

Cette thèse est dédiée aux étudiants qui

ont pris massivement la rue en 2012.

Ils ont fait éclore le printemps québécois

et redonné espoir aux gens comme moi.

Elle l'est aussi à toi, mon petit Tristan,

qui as défié l'antiémeute

et ses gaz lacrymogènes

depuis le douillet ventre de maman.

## REMERCIEMENTS

Une thèse de doctorat est une longue aventure qui ne se mène pas seul. Les remerciements qui suivent lèvent le chapeau à tous ceux qui ont participé par leur gentillesse, leur temps, leurs discussions, leur amour à ces années de labeur que concluent en quelques pages ce document. Mes remerciements premiers iront aux membres du jury qui ont bien voulu lire ces pages et y porter leurs jugement et sanction. Je les remercie de leur temps et de l'apport indispensable de leur travail. Mes remerciements iront également aux commanditaires de la thèse : les fonds gouvernementaux du CRSNG et du FQRNT et la compagnie Opal-RT Technologies, et plus particulièrement Jean Bélanger dont l'intuition a si souvent été juste, lui qui en plus d'apporter le concours des finances de la compagnie qu'il a fondée, n'a jamais hésité à payer de son temps, d'un verre, d'idées jetées comme autant de destinations où diriger sa barque. Je remercie également mes directeurs qui ont joué un rôle déterminant dans la réalisation de ce travail. Chacun d'eux a contribué d'une façon ou d'une autre à la bonne réussite de ce projet, et je les en remercie chaleureusement.

Je souhaiterais remercier toutes ces personnes à Opal qui m'ont aidé à avancer et à réaliser les différentes contributions de la thèse. Je remercie Handy Fortin Blanchette, aujourd'hui professeur à l'ÉTS et chef de l'équipe eDriveSim au moment où je débutais ma thèse. Handy m'a aidé à voir plus clair dans un domaine qui m'était en grande partie étranger, et il le fit du temps qu'il était employé d'Opal et même après. Je remercie également Christian Dufour qui a pris le relais de Handy dans mon encadrement à Opal. Notre collaboration a été très fructueuse, ponctuée de projets industriels répondant aux commandes des clients, et riche de discussions autour d'un poste d'ordinateur, d'une bière ou par Skype interposé. Je remercie aussi Sébastien Cense qui a aidé à la réalisation matérielle de mes prototypes, particulièrement l'eHS. Je ne manquerai non plus de remercier les amis du laboratoire : pour sa patience et sa pugnacité dans des conversations souvent musclées, Marc-André Daigneault ; pour son cynisme rieur et esprit volontaire, Jonas Lerebours ; pour sa gentillesse et disponibilité, Adrien Larbanet ; pour sa cinéphilie et son humour, Mathieu Allard ; pour son entregent et sa bonhomie, Hani Saad.

Sur une note plus intime, j'aimerais remercier les miens, Mahdi Khelfaoui et Imad Safi, amis de tous les temps qui donnent une tape sur l'épaule et écoutent avec la patience et les encouragements que seuls les amis savent témoigner ; et finalement ma compagne et amie Fanny Lalonde, qui sait l'indulgence lorsqu'arrive une fin de semaine de travail, elle qui, en complétant sa maîtrise et sans compter ses heures pour l'association étudiante, a donné la vie et illuminé la nôtre.

## RÉSUMÉ

La simulation en temps réel des réseaux électriques connaît un vif intérêt industriel, motivé par la réduction substantielle des coûts de développement qu'offre une telle approche de prototypage. Ainsi, la simulation en temps réel permet d'intégrer dans la boucle de la simulation du matériel au fur et à mesure sa conception, permettant du même coup d'en vérifier le bon fonctionnement dans des conditions réalistes. Néanmoins, la simulation en temps réel au moyen de CPU, telle qu'elle a été pensée depuis une quinzaine d'années, souffre de certaines limitations, notamment dans l'atteinte de pas de calcul de l'ordre de quelques micro-secondes, un requis important pour la simulation fidèle des transitoires rapides qu'exigent les convertisseurs de puissance modernes.

Pour tenter d'apporter une réponse à ces difficultés, les industriels ont adopté les circuits FPGA pour la réalisation d'engins de calcul dédiés à la simulation rapide des réseaux électriques, ce qui a permis de franchir la barrière de la fréquence de commutation de 5 kHz qui était caractéristique de la simulation sur CPU. La simulation sur FPGA offre à ce titre différents avantages telle que la réduction de la latence de la boucle de simulation du matériel sous test, particulièrement du fait que le FPGA donne un accès direct aux senseurs et aux actuateurs du dispositif en cours de prototypage.

Les paradigmes usuels du traitement de signal sur FPGA font qu'il est d'usage d'y opérer une arithmétique à virgule fixe. Ce format des nombres pénalise le temps de développement puisqu'il requiert du concepteur une évaluation complexe de la précision nécessaire pour représenter l'ensemble des variables du modèle mathématique. C'est pourquoi l'arithmétique à virgule flottante suscite un certain intérêt dans la simulation des réseaux sur FPGA. Cependant, les opérateurs en virgule flottante imposent de longues latences, particulièrement handicapantes dans la réalisation de lois d'intégration (trapézoïdale, Euler-arrière, etc.) pour lesquelles l'utilisation d'un accumulateur à un cycle est cruciale. En cela, la problématique de l'addition et de l'accumulation en virgule flottante forme le cœur de notre travail de recherche. Ce travail a permis l'élaboration des architectures d'accumulateurs, de plusieurs accumulateurs (MAC) et d'opérateurs de produit scalaire (OPS) en virgule flottante, qui joueront un rôle déterminant dans la mise en œuvre de nos engins de calcul pour la simulation des réseaux électriques.

Ainsi, le travail présenté dans cette thèse propose différentes contributions scientifiques au domaine de la simulation en temps réel sur FPGA. D'une part, il contribue à la formulation d'un algorithme de sommation qui est une généralisation de la technique d'auto-alignement, nantie ici d'une formulation et d'une réalisation matérielle simplifiées. Le travail établit les

critères permettant de garantir la bonne exactitude des résultats, critères que nous avons établis par des démonstrations théoriques et empiriques. La thèse propose également une analyse exhaustive de l'utilisation du format redondant *high radix carry-save* (HRCS) dans l'addition de mantisses larges, format pour lequel deux nouveaux opérateurs arithmétiques sont proposés : un additionneur endomorphique ainsi qu'un convertisseur HRCS à conventionnel.

Une fois l'addition en virgule flottante à un cycle réalisée, la thèse propose de concevoir sur FPGA des engins de calcul exploitant une architecture SIMD (*single instruction, multiple data*) et disposant de plusieurs MAC ou opérateurs de produit scalaire (OPS) en virgule flottante. Ces opérateurs présentent une latence très courte, permettant l'atteinte de pas de calcul de quelques centaines de nanosecondes dans la simulation de convertisseurs de puissance de moyenne complexité. Le travail se conclut par l'analyse de la modélisation de circuits d'électronique de puissance et la présentation d'un engin de calcul versatile permettant de simuler des convertisseurs de topologie arbitraire, pouvant contenir jusqu'à 24 interrupteurs avec des pas de temps en deçà du  $1 \mu\text{s}$ , tout en admettant des fréquences de commutations de plusieurs kilohertz. Cette réalisation a abouti à une commercialisation par le partenaire industriel de la thèse.

## ABSTRACT

The real-time simulation of electrical networks gained a vivid industrial interest during recent years, motivated by the substantial development cost reduction that such a prototyping approach can offer. Real-time simulation allows the progressive inclusion of real hardware during its development, allowing its testing under realistic conditions. However, CPU-based simulations suffer from certain limitations such as the difficulty to reach time-steps of a few microsecond, an important challenge brought by modern power converters.

Hence, industrial practitioners adopted the FPGA as a platform of choice for the implementation of calculation engines dedicated to the rapid real-time simulation of electrical networks. The reconfigurable technology broke the 5 kHz switching frequency barrier that is characteristic of CPU-based simulations. Moreover, FPGA-based real-time simulation offers many advantages, including the reduced latency of the simulation loop that is obtained thanks to a direct access to sensors and actuators.

The fixed-point format is paradigmatic to FPGA-based digital signal processing. However, the format imposes a time penalty in the development process since the designer has to assess the required precision for all model variables. This fact brought an import research effort on the use of the floating-point format for the simulation of electrical networks. One of the main challenges in the use of the floating-point format are the long latencies required by the elementary arithmetic operators, particularly when an adder is used as an accumulator, an important building bloc for the implementation of integration rules such as the trapezoidal method. Hence, single-cycle floating-point accumulation forms the core of this research work. Our results help building such operators as accumulators, multiply-accumulators (MACs), and dot-product (DP) operators. These operators play a key role in the implementation of the proposed calculation engines.

Therefore, this thesis contributes to the realm of FPGA-based real-time simulation in many ways. The research work proposes a new summation algorithm, which is a generalization of the so-called self-alignment technique. The new formulation is broader, simpler in its expression and hardware implementation. Our research helps formulating criteria to guarantee good accuracy, the criteria being established on a theoretical, as well as empirical basis. Moreover, the thesis offers a comprehensive analysis on the use of the redundant high radix carry-save (HRCS) format. The HRCS format is used to perform rapid additions of large mantissas. Two new HRCS operators are also proposed, namely an endomorphic adder and a HRCS to conventional converter.

Once the mean to single-cycle accumulation is defined as a combination of the self-alignment technique and the HRCS format, the research focuses on the FPGA implementation of SIMD calculation engines using parallel floating-point MACs or DPs. The proposed operators are characterized by low latencies, allowing the engines to reach very low time-steps. The document finally discusses power electronic circuits modelling, and concludes with the presentation of a versatile calculation engine capable of simulating power converter with arbitrary topologies and up to 24 switches, while achieving time steps below 1  $\mu\text{s}$  and allowing switching frequencies in the range of tens kilohertz. The latter realization has led to commercialization of a product by our industrial partner.

## TABLE DES MATIÈRES

|                                                                |      |

|----------------------------------------------------------------|------|

| ÉPIGRAPHE . . . . .                                            | iii  |

| DÉDICACE . . . . .                                             | iv   |

| REMERCIEMENTS . . . . .                                        | v    |

| RÉSUMÉ . . . . .                                               | vi   |

| ABSTRACT . . . . .                                             | viii |

| TABLE DES MATIÈRES . . . . .                                   | x    |

| LISTE DES TABLEAUX . . . . .                                   | xiii |

| LISTE DES FIGURES . . . . .                                    | xiv  |

| LISTE DES ANNEXES . . . . .                                    | xvi  |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                     | xvii |

| INTRODUCTION . . . . .                                         | 1    |

| CHAPITRE 1 Revue de littérature . . . . .                      | 6    |

| 1.1 Introduction . . . . .                                     | 6    |

| 1.2 Contexte . . . . .                                         | 6    |

| 1.2.1 Simulation des réseaux électriques . . . . .             | 6    |

| 1.2.2 Simulation en temps réel . . . . .                       | 7    |

| 1.2.3 Utilité des FPGA dans les simulateurs HIL . . . . .      | 9    |

| 1.3 Techniques propres à la simulation en temps réel . . . . . | 9    |

| 1.3.1 Réseaux à interrupteurs . . . . .                        | 9    |

| 1.3.2 Découplage du réseau . . . . .                           | 11   |

| 1.4 Simulation sur FPGA . . . . .                              | 13   |

| 1.4.1 Représentation des nombres réels sur FPGA . . . . .      | 13   |

| 1.4.2 Opérateurs arithmétiques en virgule flottante . . . . .  | 14   |

| 1.4.3 Tendances émergentes . . . . .                           | 15   |

| 1.4.4 Accumulation en virgule flottante . . . . .              | 15   |

| 1.5 Conclusion . . . . .                                       | 16   |

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| CHAPITRE 2 Analyse du problème . . . . .                                    | 17 |

| 2.1 Introduction . . . . .                                                  | 17 |

| 2.2 Équations du réseau . . . . .                                           | 17 |

| 2.2.1 Approche des équations d'états . . . . .                              | 18 |

| 2.2.2 Circuit compagnon discrétréisé . . . . .                              | 19 |

| 2.2.3 Analyse nodale du réseau . . . . .                                    | 22 |

| 2.3 Caractérisation des engins de calcul . . . . .                          | 24 |

| 2.3.1 Esquisse d'une architecture d'engin de calcul . . . . .               | 24 |

| 2.3.2 Impact des séquences de lecture sur le pas de temps . . . . .         | 27 |

| 2.3.3 Taille du modèle et opérateurs arithmétiques . . . . .                | 29 |

| 2.3.4 Influence de la latence des opérateurs . . . . .                      | 32 |

| 2.4 Conclusion . . . . .                                                    | 33 |

| CHAPITRE 3 Opérateurs de sommation en virgule flottante . . . . .           | 34 |

| 3.1 Introduction . . . . .                                                  | 34 |

| 3.2 Problématique . . . . .                                                 | 34 |

| 3.2.1 Additionneur en virgule flottante . . . . .                           | 34 |

| 3.2.2 Exactitude de la sommation en virgule flottante . . . . .             | 35 |

| 3.2.3 Accumulation à un cycle par l'auto-alignement des mantisses . . . . . | 38 |

| 3.3 Généralisation de la TAA . . . . .                                      | 41 |

| 3.3.1 Le format d'auto-alignement . . . . .                                 | 41 |

| 3.3.2 Sommation de type TAA d'exactitude K-tuple . . . . .                  | 43 |

| 3.4 Résultats . . . . .                                                     | 45 |

| 3.4.1 Exactitude de l'accumulation de type TAA . . . . .                    | 45 |

| 3.4.2 Opérateurs de type TAA . . . . .                                      | 48 |

| 3.5 Conclusion . . . . .                                                    | 49 |

| CHAPITRE 4 Addition redondante des mantisses . . . . .                      | 50 |

| 4.1 Introduction . . . . .                                                  | 50 |

| 4.2 Problématique . . . . .                                                 | 50 |

| 4.2.1 Chemin critique de l'additionneur . . . . .                           | 50 |

| 4.2.2 L'addition redondante . . . . .                                       | 51 |

| 4.2.3 Additionneurs à virgule flottante avec système redondant . . . . .    | 53 |

| 4.3 Le système HRCS . . . . .                                               | 54 |

| 4.3.1 Illustration du principe du système HRCS . . . . .                    | 54 |

| 4.3.2 Définition du format HRCS . . . . .                                   | 55 |

| 4.3.3 Additions dans le système HRCS . . . . .                              | 56 |

|                                                                                |                                                                        |            |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------|------------|

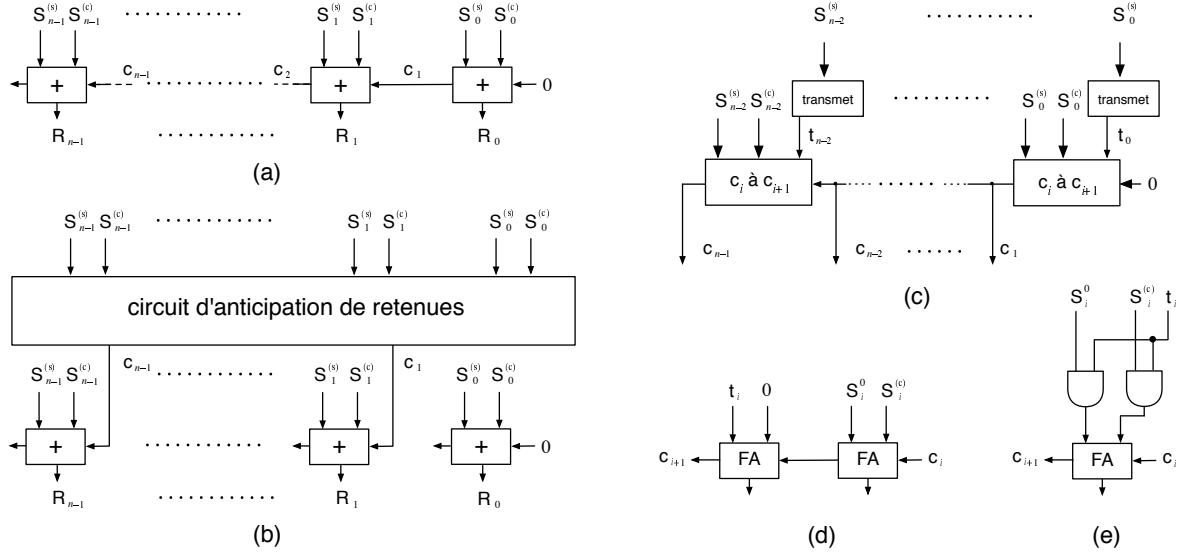

| 4.3.4                                                                          | Conversion . . . . .                                                   | 60         |

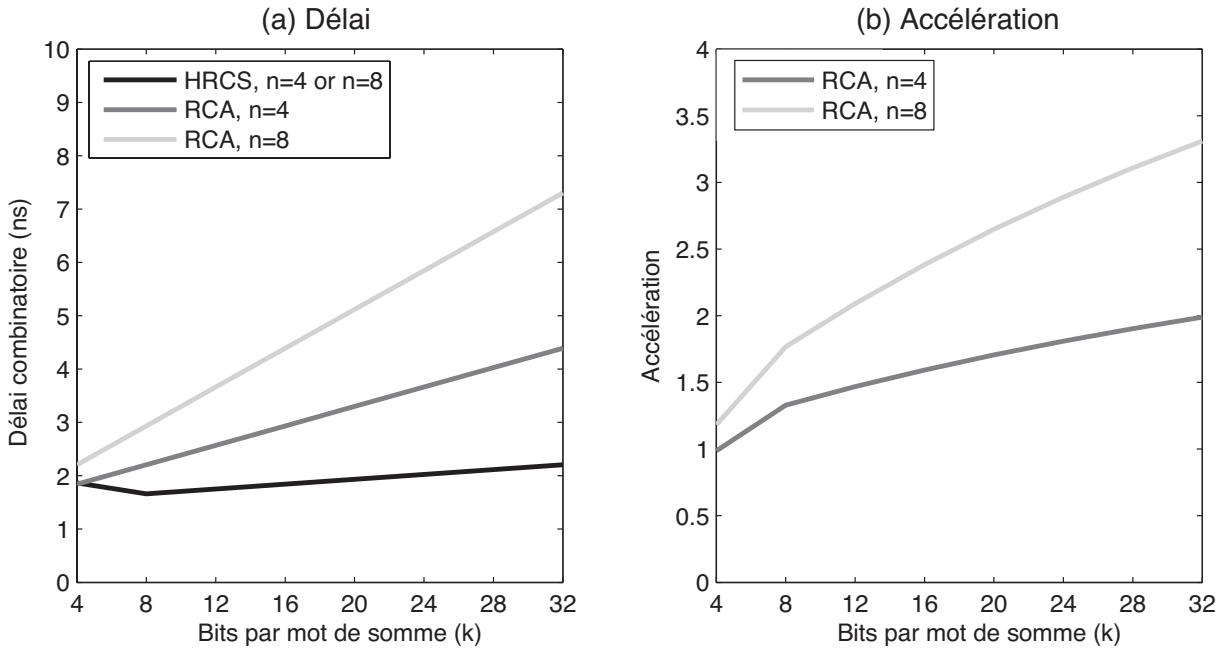

| 4.4                                                                            | Résultats . . . . .                                                    | 62         |

| 4.4.1                                                                          | Additionneur hétérogène . . . . .                                      | 62         |

| 4.4.2                                                                          | Additionneur endomorphique . . . . .                                   | 63         |

| 4.4.3                                                                          | Convertisseur HRCS à format conventionnel . . . . .                    | 64         |

| 4.4.4                                                                          | Implémentation HRCS des opérateurs de type TAA . . . . .               | 66         |

| 4.5                                                                            | Conclusion . . . . .                                                   | 71         |

| <b>CHAPITRE 5     Engins de calcul employant l'approche TAA/HRCS . . . . .</b> |                                                                        | <b>72</b>  |

| 5.1                                                                            | Introduction . . . . .                                                 | 72         |

| 5.2                                                                            | Usage de la mémoire embarquée . . . . .                                | 72         |

| 5.3                                                                            | Modèle d'interrupteur à matrice fixe . . . . .                         | 74         |

| 5.3.1                                                                          | Formulation mathématique du modèle . . . . .                           | 74         |

| 5.3.2                                                                          | Manipulation des équations MANA . . . . .                              | 76         |

| 5.3.3                                                                          | Limites du modèle à matrice fixe . . . . .                             | 77         |

| 5.3.4                                                                          | Méthode pour surmonter les limites du modèle à matrice fixe . . . . .  | 79         |

| 5.4                                                                            | Implémentation FPGA . . . . .                                          | 82         |

| 5.4.1                                                                          | Le format des nombres . . . . .                                        | 82         |

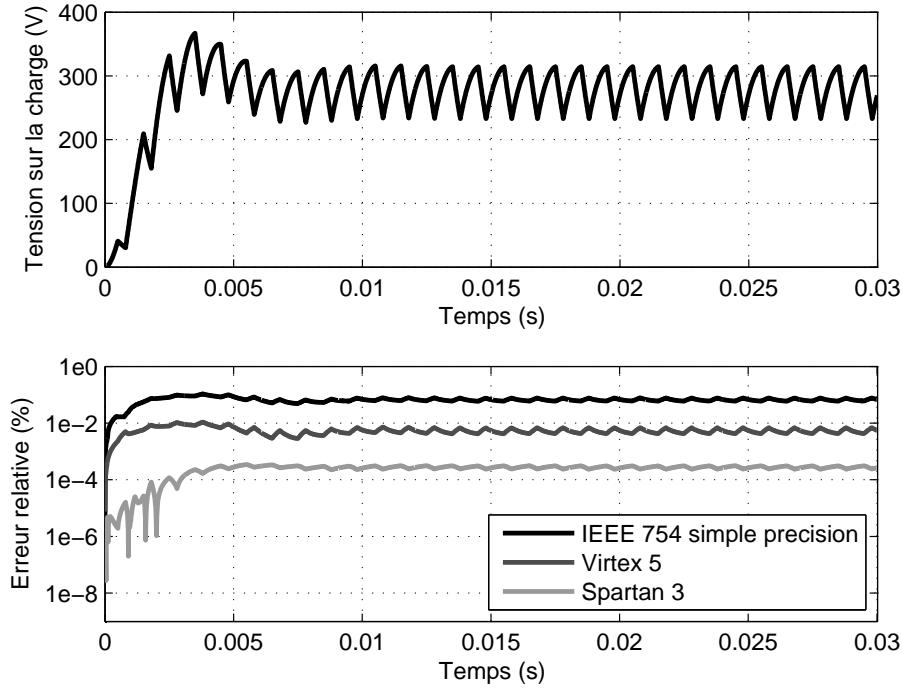

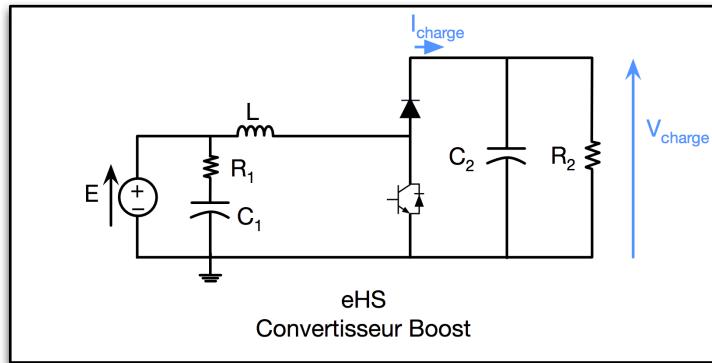

| 5.4.2                                                                          | Implémentation d'un convertisseur boost . . . . .                      | 84         |

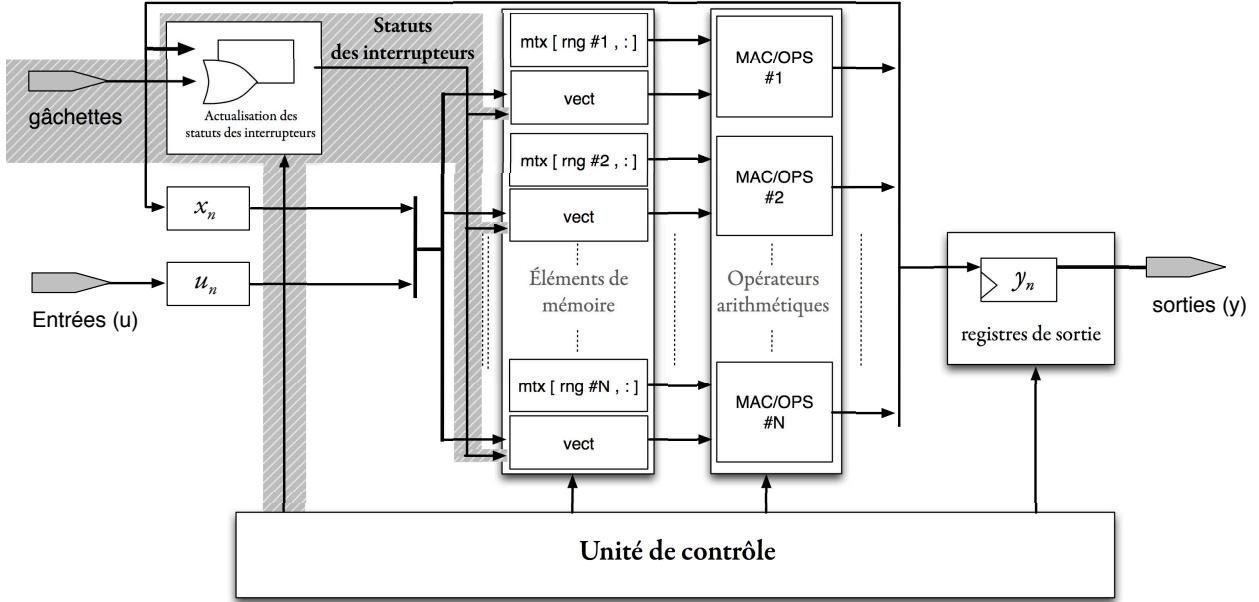

| 5.4.3                                                                          | Engin de calcul versatile . . . . .                                    | 85         |

| 5.5                                                                            | Études de cas utilisant le modèle résistif de l'interrupteur . . . . . | 91         |

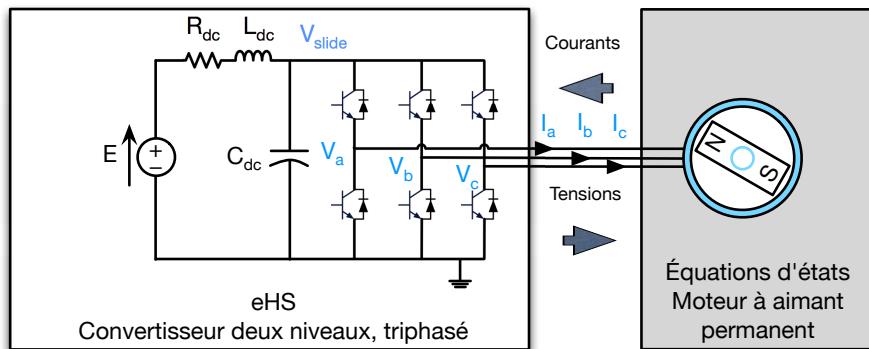

| 5.5.1                                                                          | Pont à deux niveaux . . . . .                                          | 92         |

| 5.5.2                                                                          | Convertisseur multi-niveaux . . . . .                                  | 95         |

| 5.6                                                                            | Conclusion . . . . .                                                   | 101        |

| <b>CONCLUSION . . . . .</b>                                                    |                                                                        | <b>103</b> |

| <b>PUBLICATIONS DE L'AUTEUR . . . . .</b>                                      |                                                                        | <b>105</b> |

| <b>BIBLIOGRAPHIE . . . . .</b>                                                 |                                                                        | <b>107</b> |

| <b>ANNEXES . . . . .</b>                                                       |                                                                        | <b>119</b> |

**LISTE DES TABLEAUX**

|     |                                                                        |     |

|-----|------------------------------------------------------------------------|-----|

| 3.1 | Logique de contrôle de l'accumulateur à virgule flottante. . . . .     | 40  |

| 3.2 | Architectures matérielles utilisées pour les tests numériques. . . . . | 45  |

| 3.3 | Occupation de surface d'opérateurs à virgule flottante. . . . .        | 49  |

| 4.1 | Paramètres et caractéristiques des opérateurs évalués. . . . .         | 69  |

| 4.2 | Opérateurs à virgule flottante exploitant le format HRCS . . . . .     | 70  |

| 5.1 | Paramètres du buck-boost. . . . .                                      | 77  |

| 5.2 | Paramètres du boost. . . . .                                           | 84  |

| 5.3 | Résultats d'implémentation pour le convertisseur boost . . . . .       | 85  |

| 5.4 | Résultats d'implémentation de l'eHS. . . . .                           | 89  |

| 5.5 | Circuits considérés pour démontrer la versatilité de l'eHS . . . . .   | 90  |

| 5.6 | Résultats d'implémentation du pont à deux niveaux . . . . .            | 94  |

| 5.7 | Résultats d'implémentation du MMC . . . . .                            | 101 |

## LISTE DES FIGURES

|      |                                                                                           |    |

|------|-------------------------------------------------------------------------------------------|----|

| 1.1  | Différence entre le temps réel et le temps différé. . . . .                               | 7  |

| 1.2  | Configuration typique d'un simulateur HIL. . . . .                                        | 8  |

| 1.3  | Découplage d'un circuit en deux parties distinctes. . . . .                               | 12 |

| 1.4  | Latence de l'additionneur et intégration. . . . .                                         | 16 |

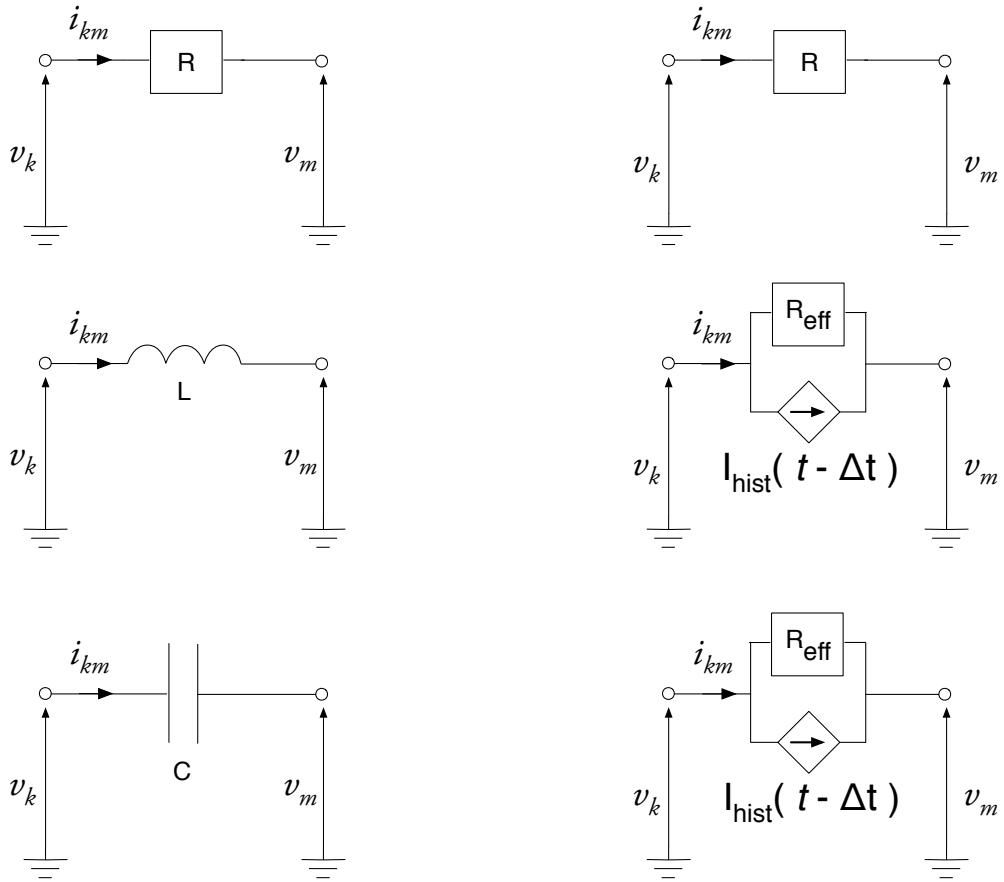

| 2.1  | Équivalents Norton de composants de base. . . . .                                         | 20 |

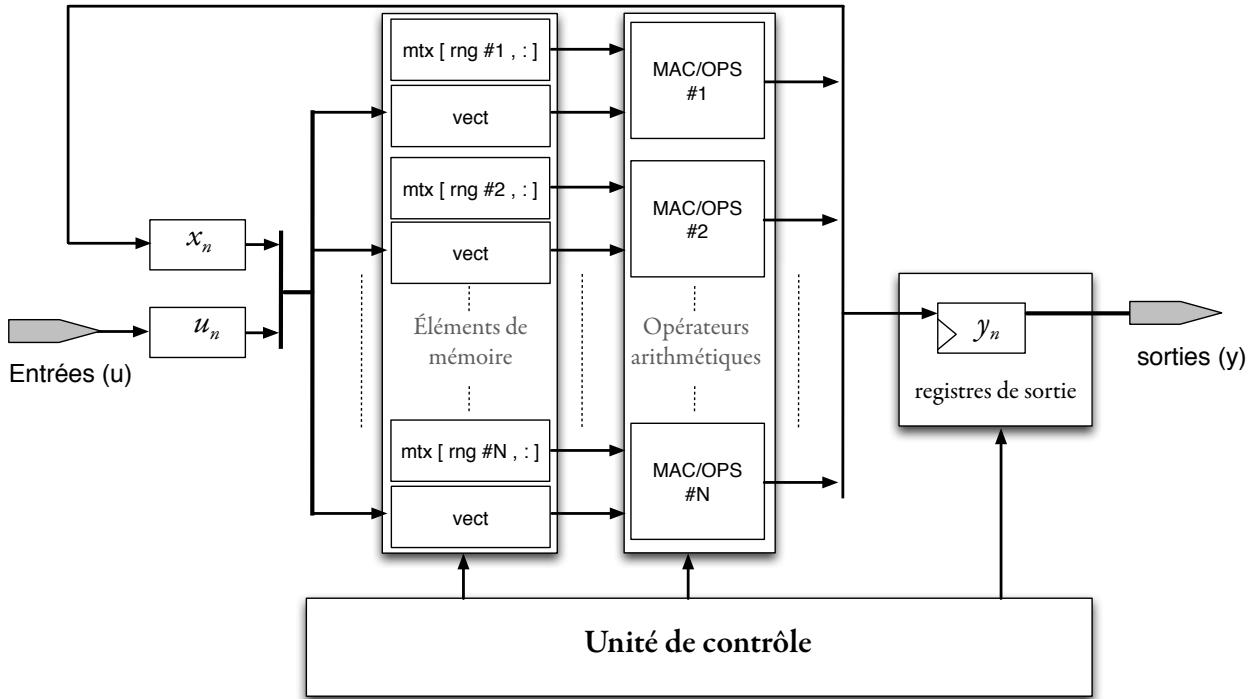

| 2.2  | Esquisse d'engin de calcul pour la simulation des réseaux. . . . .                        | 24 |

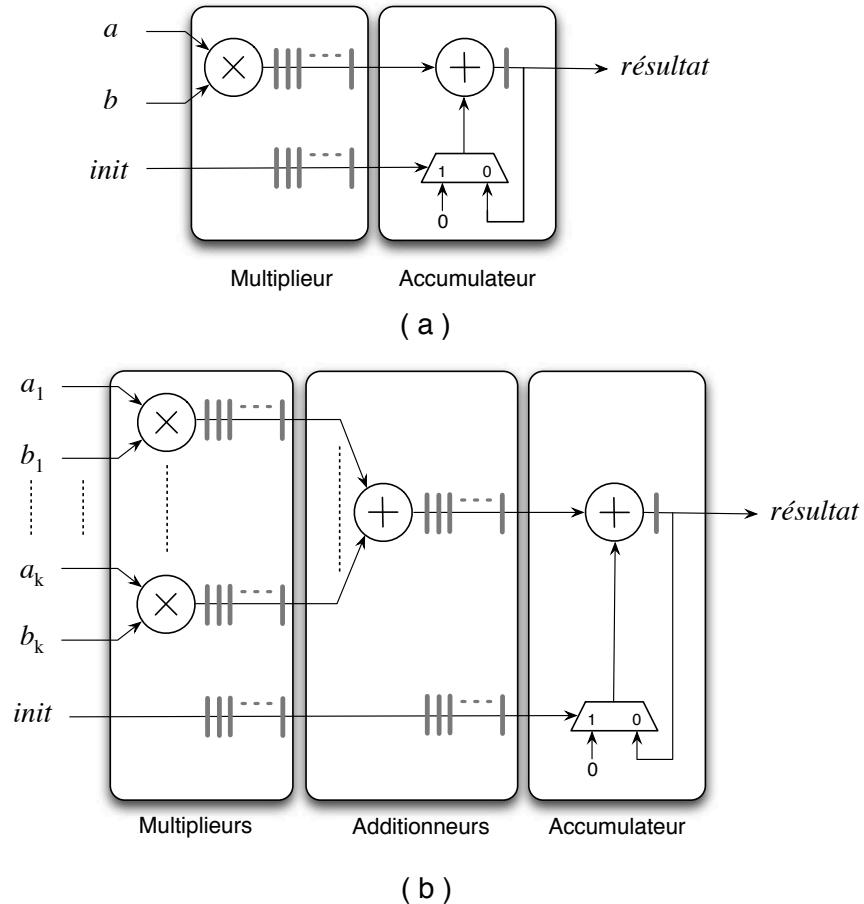

| 2.3  | Opérateurs utilisés par les engins de calcul. . . . .                                     | 26 |

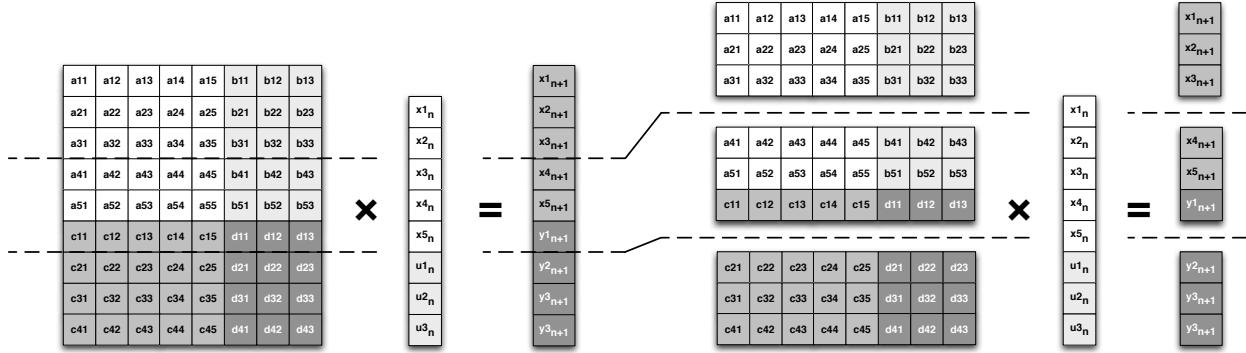

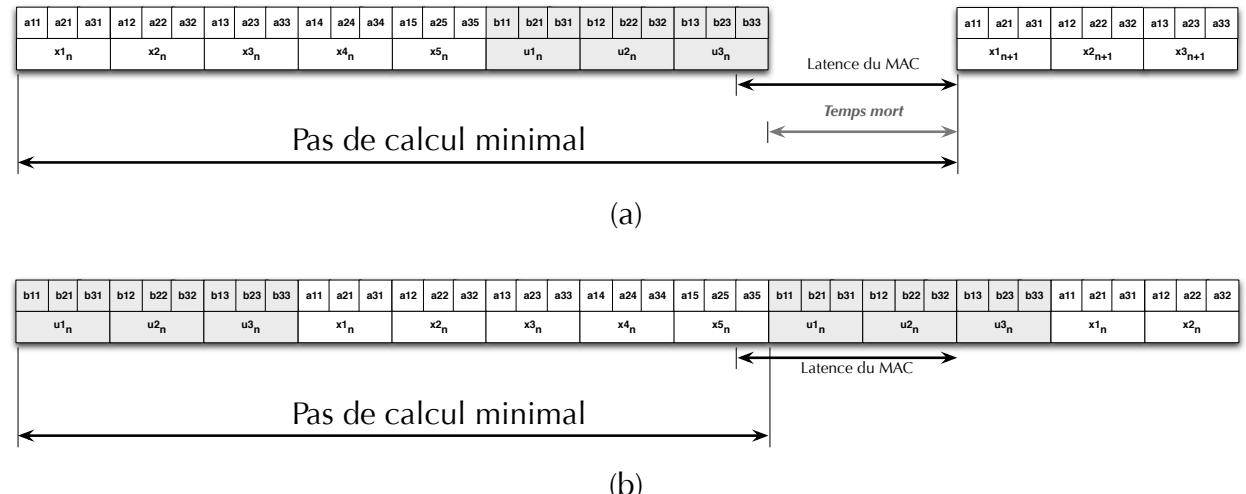

| 2.4  | Partitionnement d'un système d'états sur de multiples MAC. . . . .                        | 28 |

| 2.5  | Principe d'optimisation d'une résolution multi-MAC. . . . .                               | 28 |

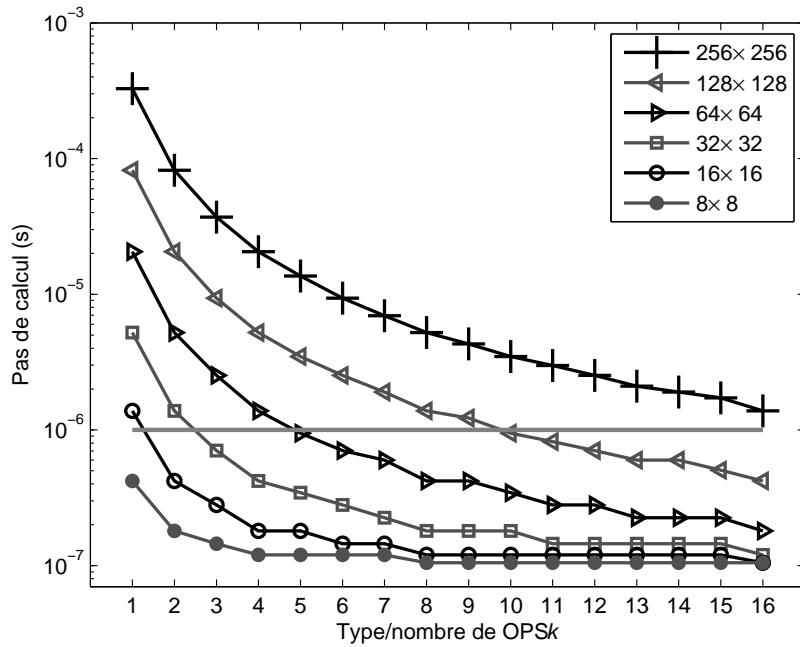

| 2.6  | Pas de calcul fonction du type/nombre d'opérateurs OPS <sub>k</sub> . . . . .             | 30 |

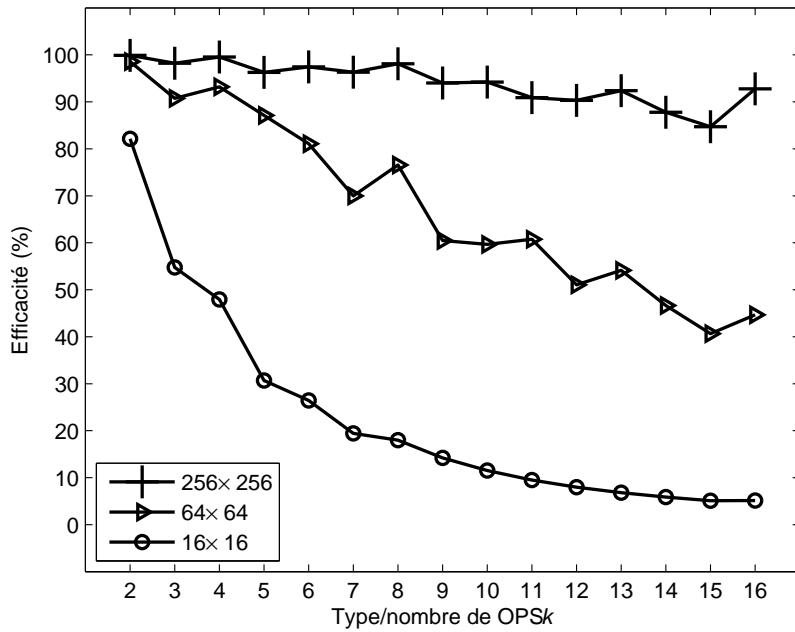

| 2.7  | Efficacité des opérateurs OPS <sub>k</sub> . . . . .                                      | 31 |

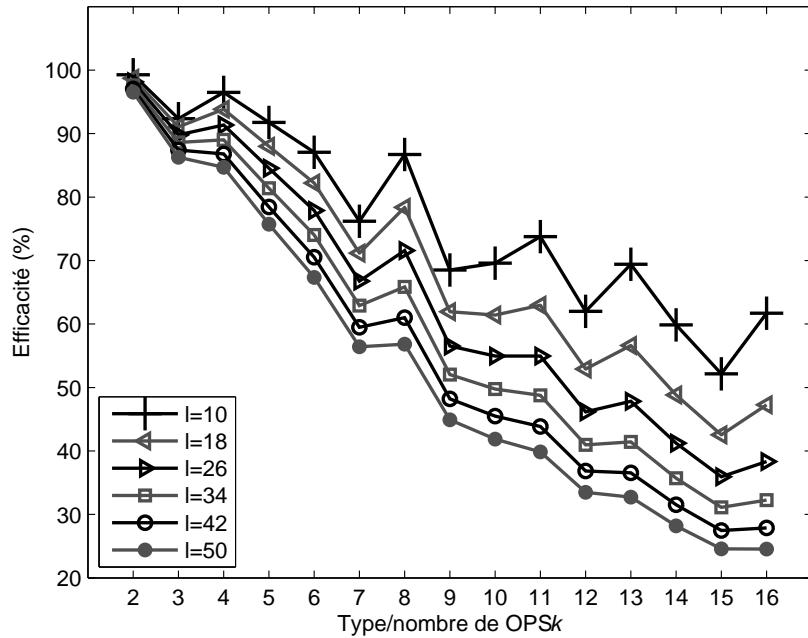

| 2.8  | Impact de la latence de l'OPS <sub>k</sub> sur l'efficacité des engins de calcul. . . . . | 32 |

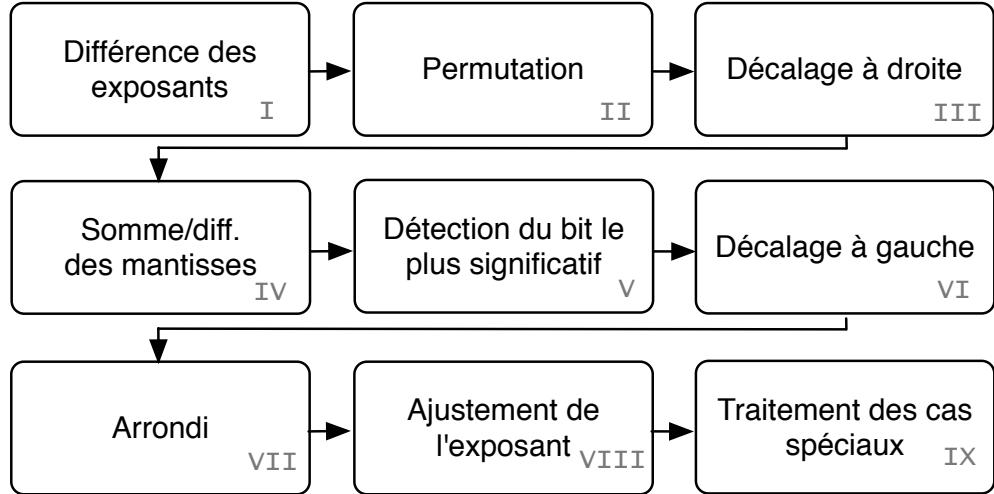

| 3.1  | Algorithme d'addition en virgule flottante. . . . .                                       | 35 |

| 3.2  | Exemples d'addition en virgule flottante. . . . .                                         | 36 |

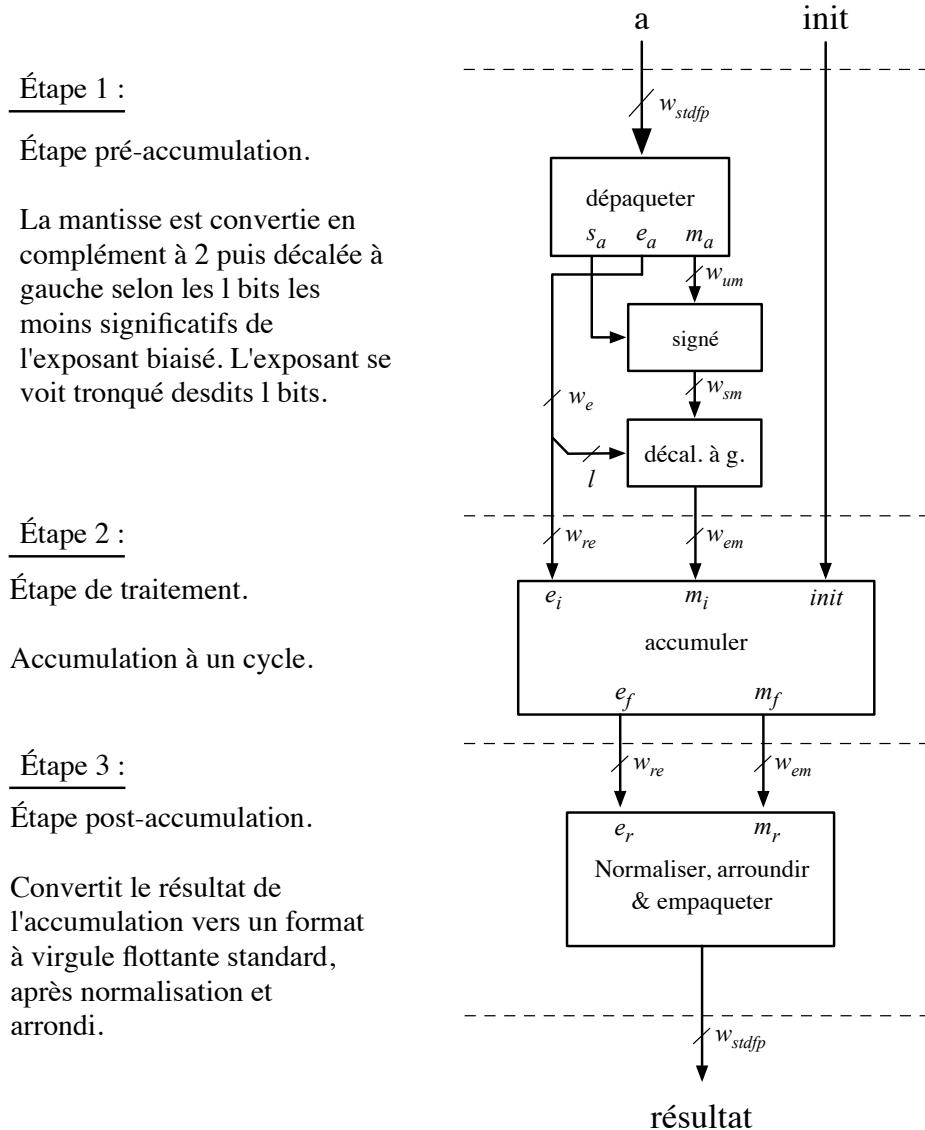

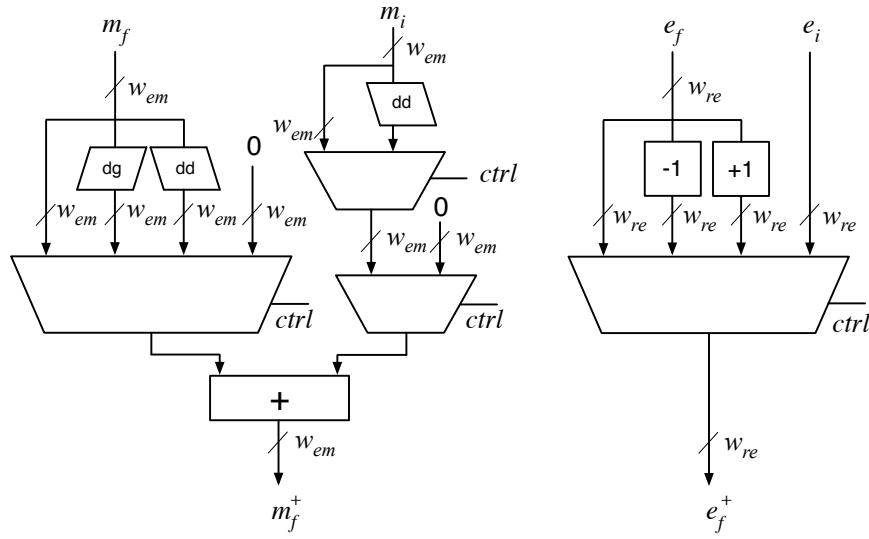

| 3.3  | Étapes principales d'un accumulateur TAA. . . . .                                         | 39 |

| 3.4  | Chemin de données d'un accumulateur à virgule flottante. . . . .                          | 40 |

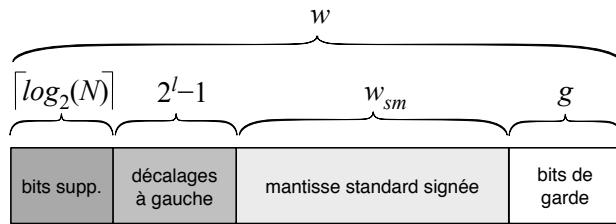

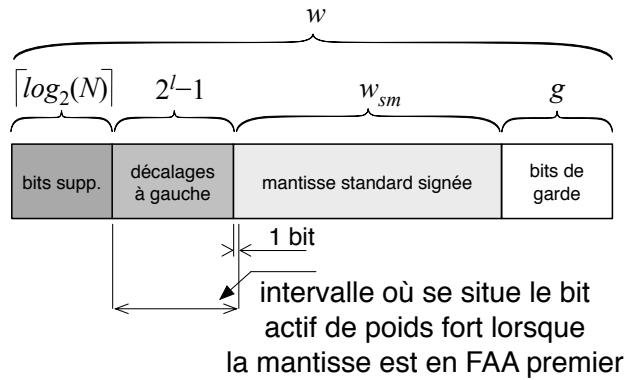

| 3.5  | Composition de la mantisse élargie en FAA. . . . .                                        | 42 |

| 3.6  | Position du bit de poids fort dans le FAA premier. . . . .                                | 43 |

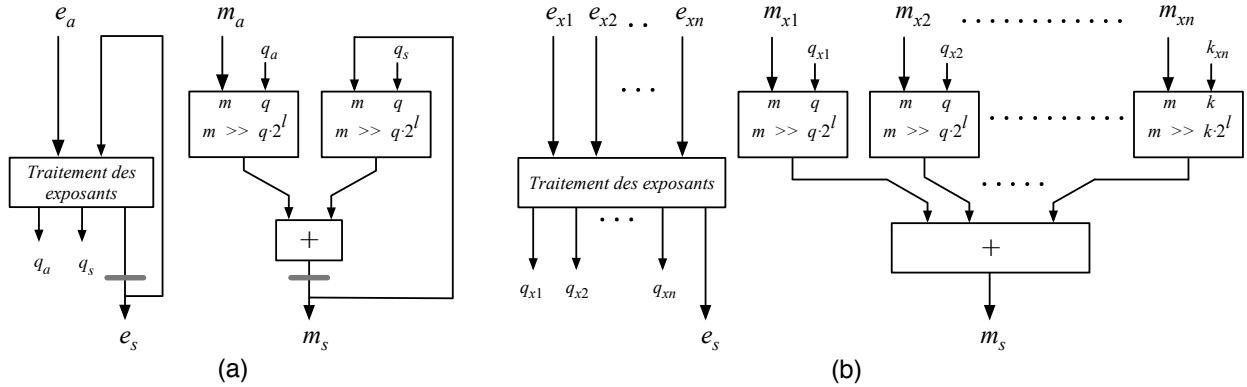

| 3.7  | Opérateurs TAA . . . . .                                                                  | 44 |

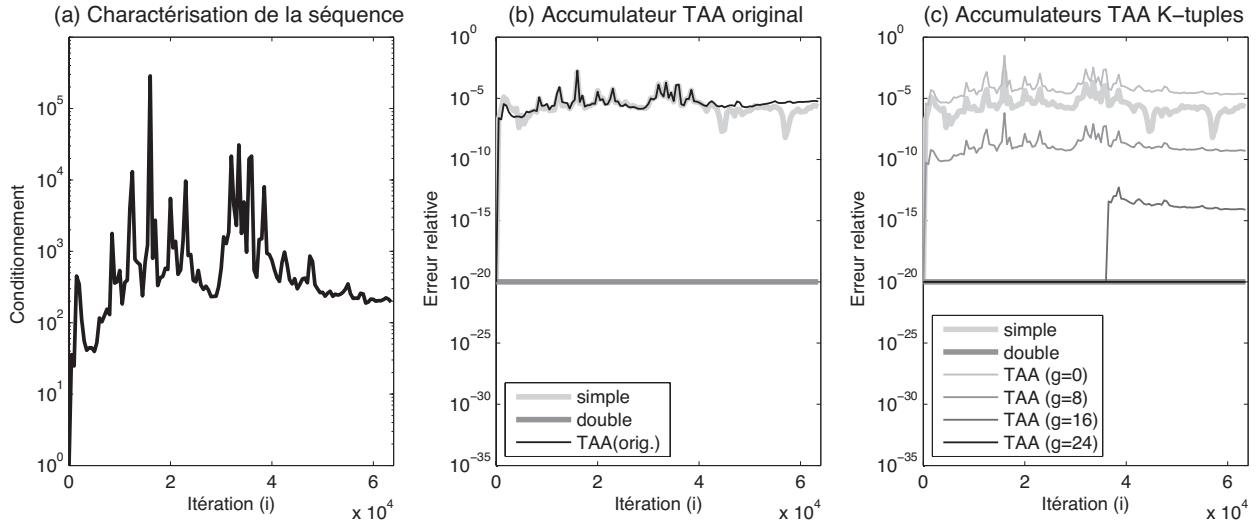

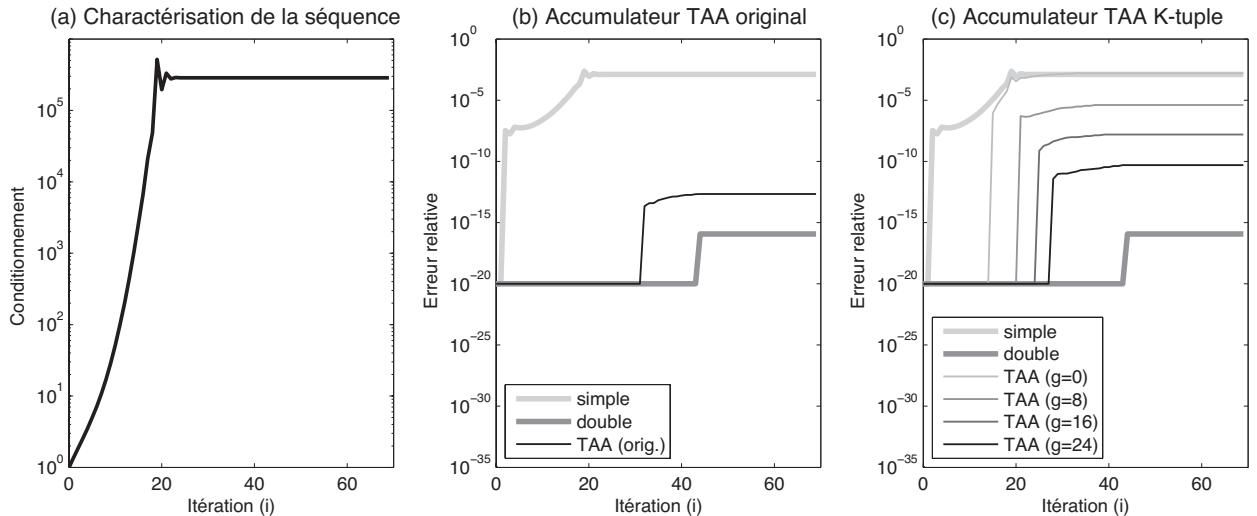

| 3.8  | Test sur des valeurs normalement distribuées. . . . .                                     | 47 |

| 3.9  | Test sur des valeurs tirées de la série de Taylor de $e^{-x}$ . . . . .                   | 47 |

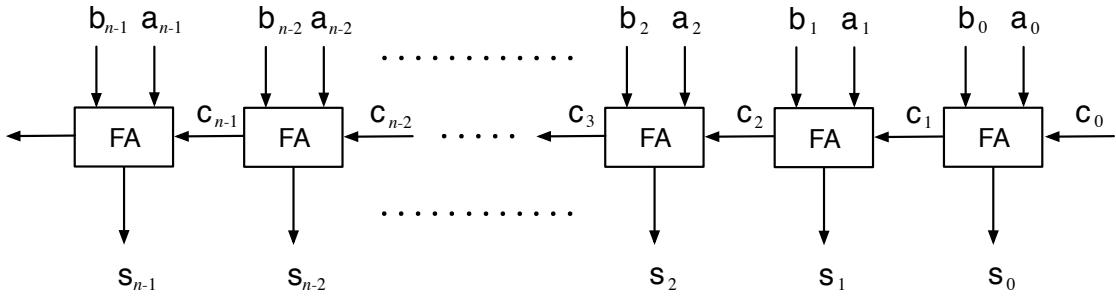

| 4.1  | Additionneur RCA . . . . .                                                                | 51 |

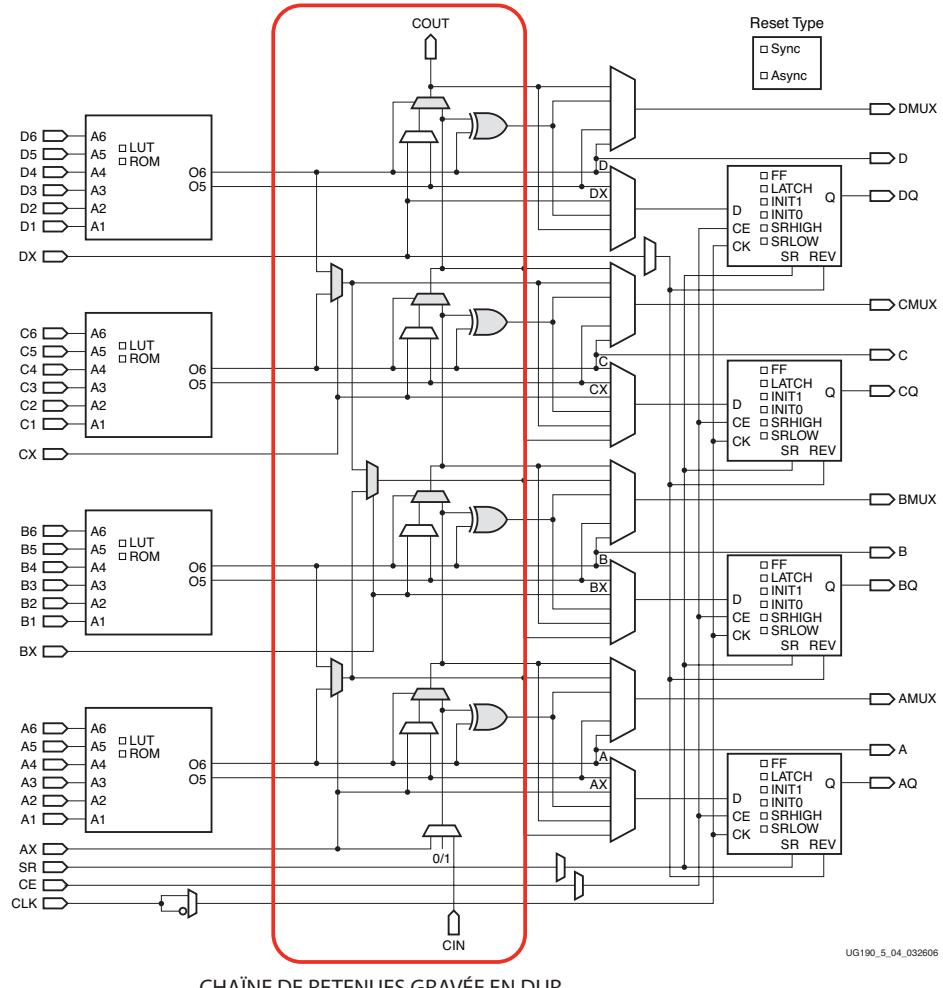

| 4.2  | Chaîne de retenues dans le Virtex 5 . . . . .                                             | 52 |

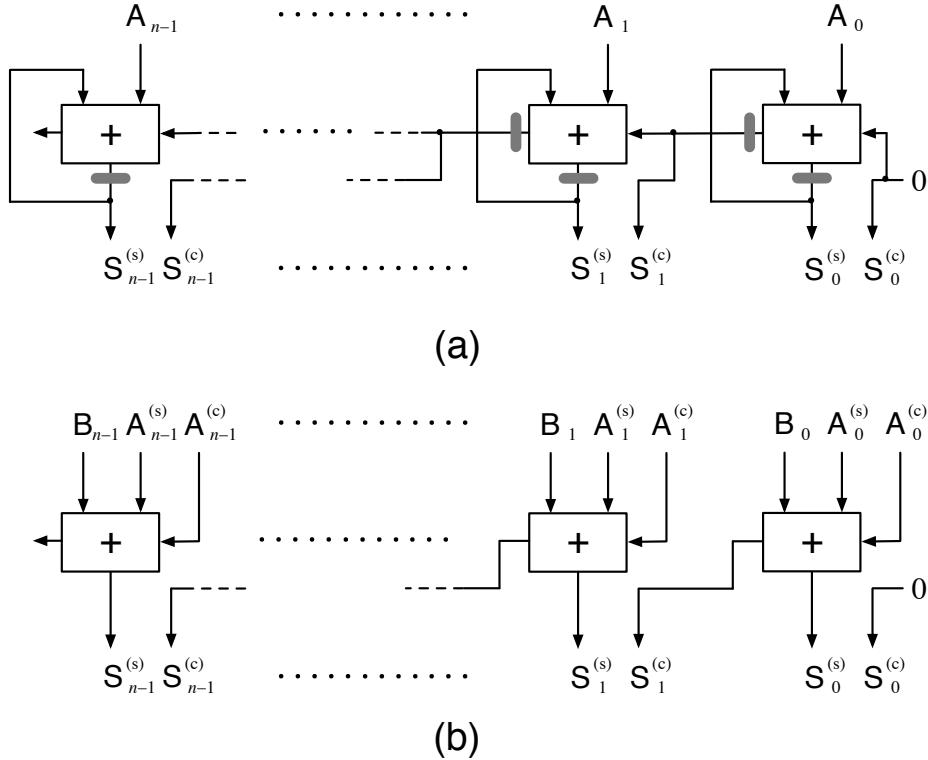

| 4.3  | Illustration de l'addition en HRCS. . . . .                                               | 54 |

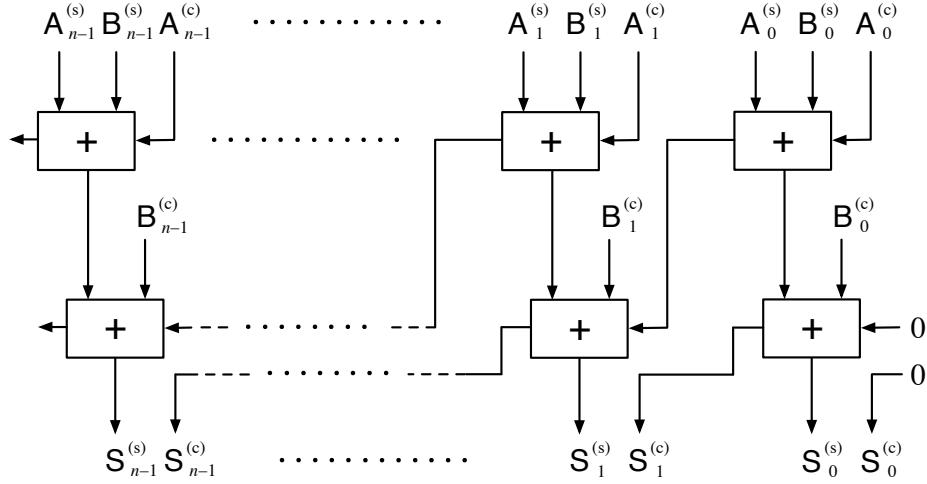

| 4.4  | Additionneurs HRCS classiques. . . . .                                                    | 56 |

| 4.5  | Additionneur endomorphique à deux chaînes de retenues. . . . .                            | 57 |

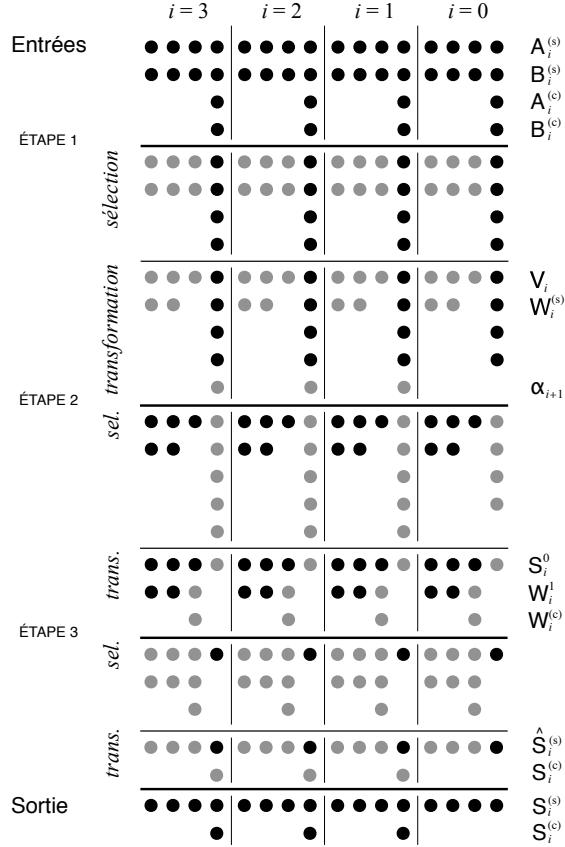

| 4.6  | Transformations pour la réalisation de l'additionneur endomorphique. . . . .              | 58 |

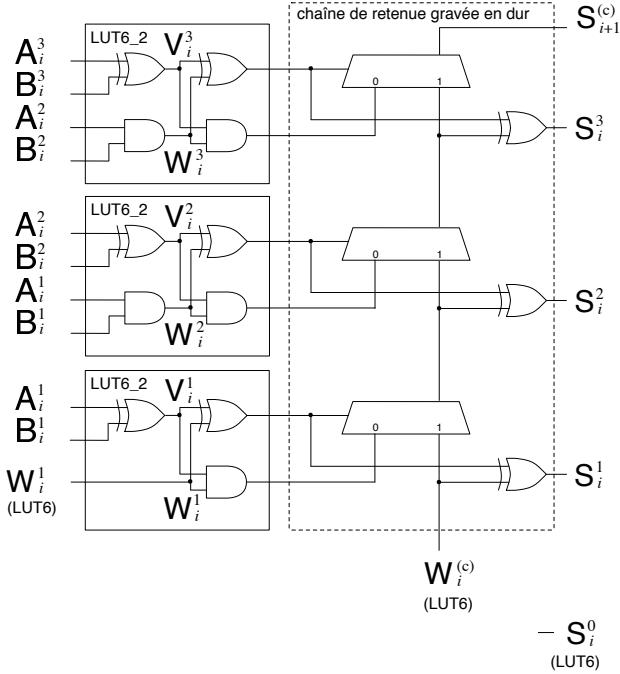

| 4.7  | Additionneur endomorphique implémenté grâce aux LUT à six entrées. . . . .                | 59 |

| 4.8  | Convertisseurs HRCS à format conventionnel. . . . .                                       | 60 |

| 4.9  | Comparaison du délai de l'additionneur hétérogène et du RCA. . . . .                      | 62 |

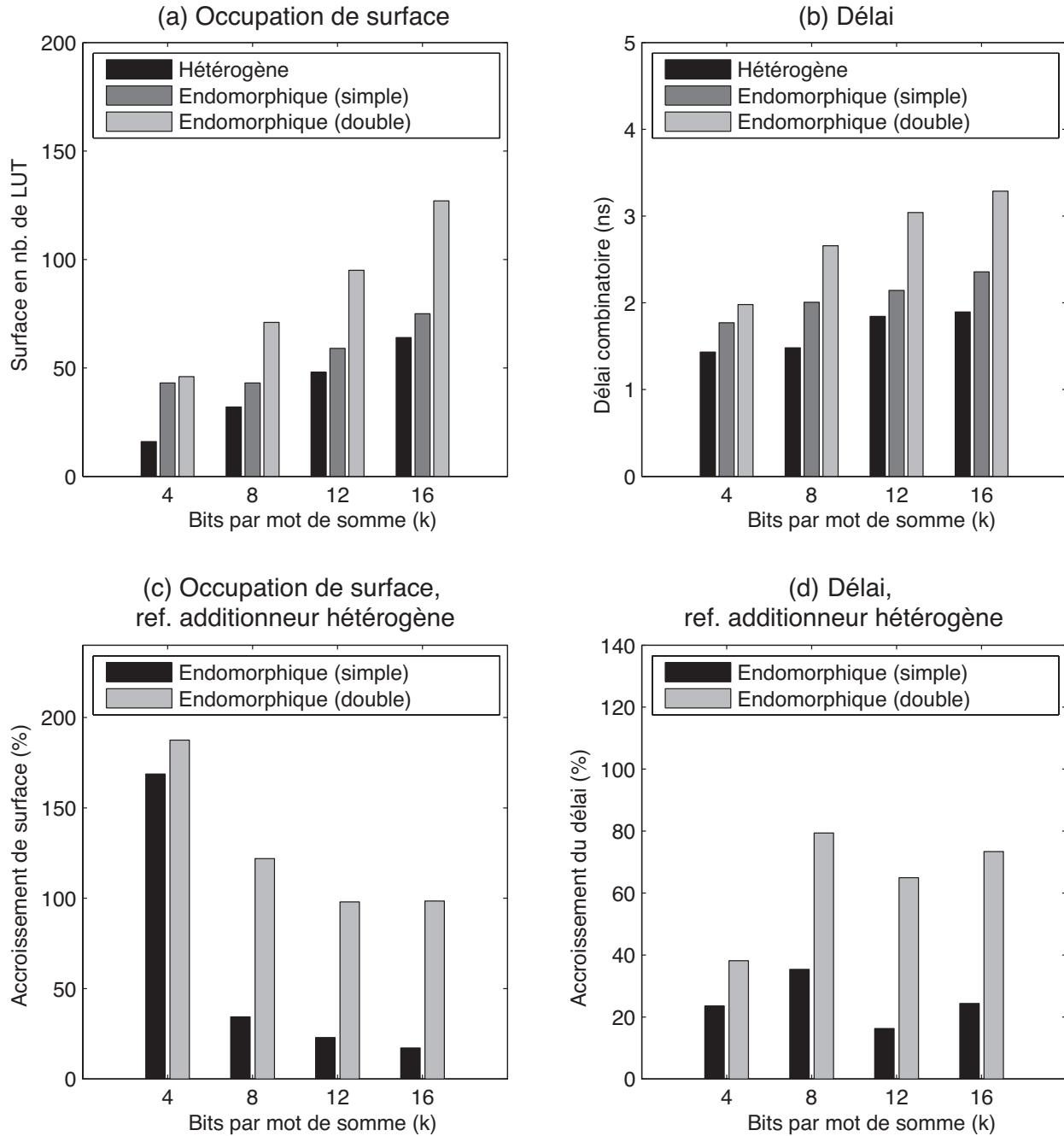

| 4.10 | Comparaison des additionneurs hétérogène et endomorphique. . . . .                        | 64 |

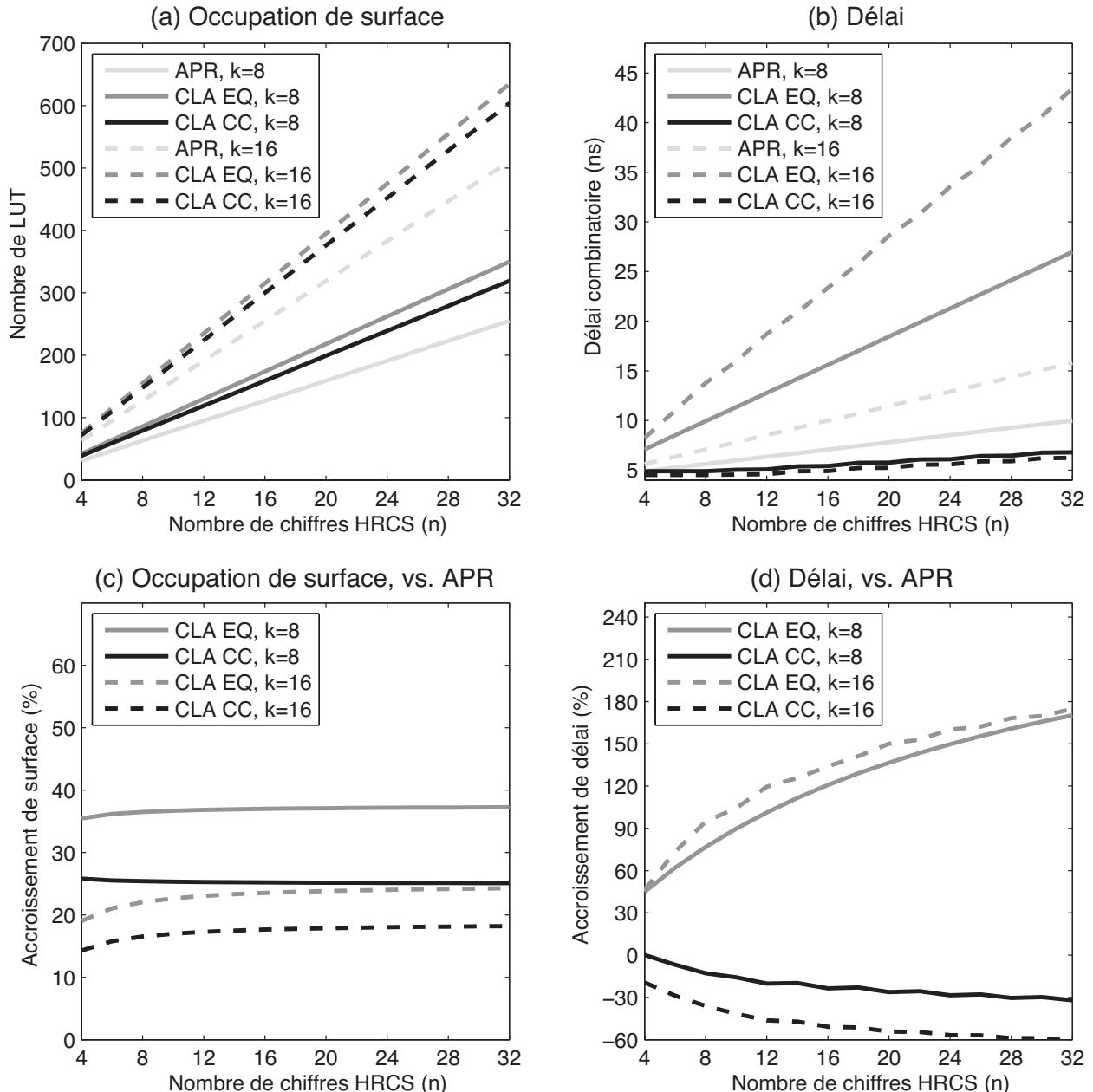

| 4.11 | Comparison de trois types de convertisseur HRCS. . . . .                                  | 65 |

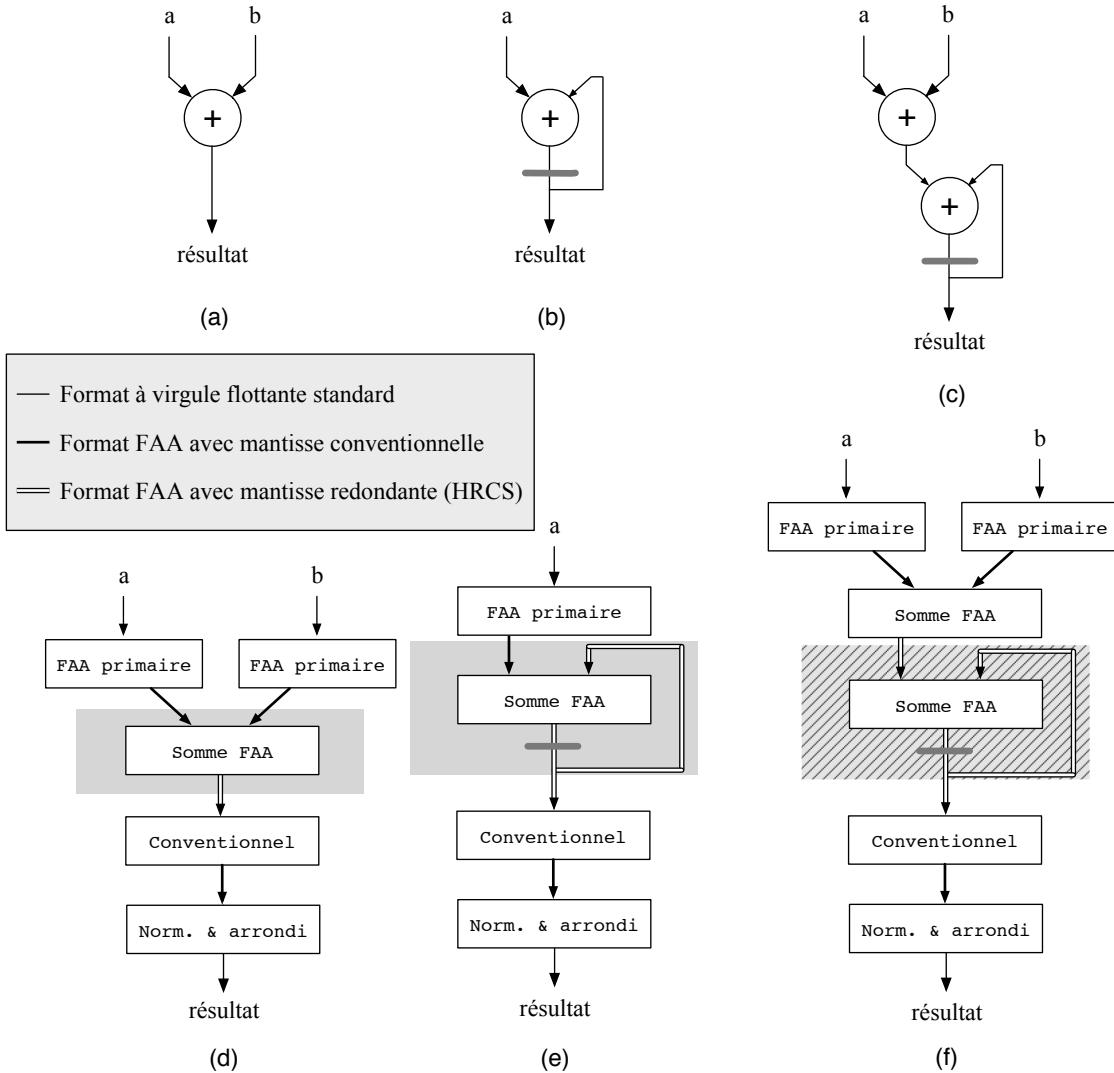

| 4.12 | Opérateurs à virgule flottante de type FAA réalisés. . . . .                              | 67 |

|      |                                                                           |     |

|------|---------------------------------------------------------------------------|-----|

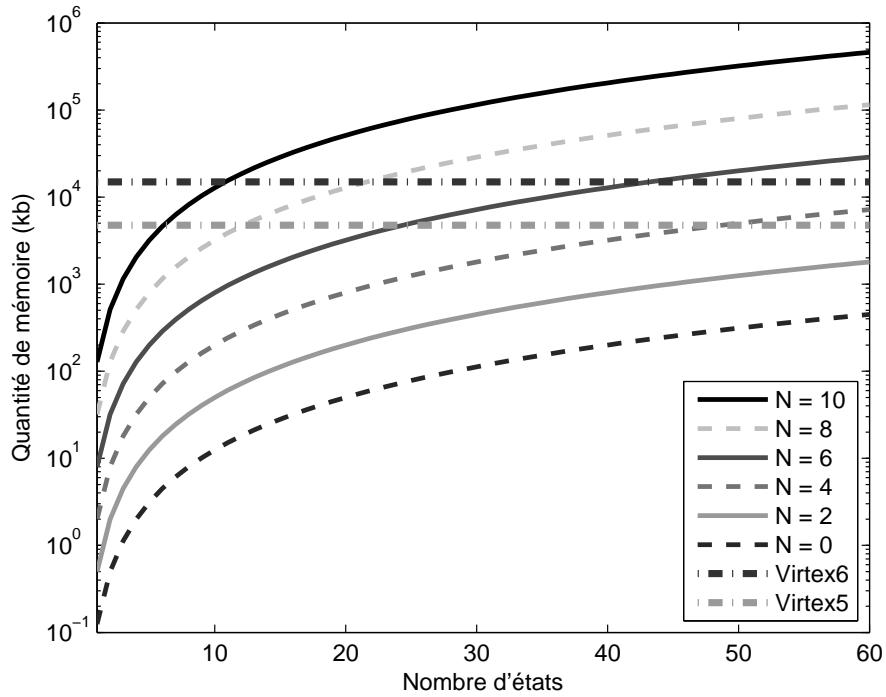

| 5.1  | Utilisation de la mémoire embarquée. . . . .                              | 73  |

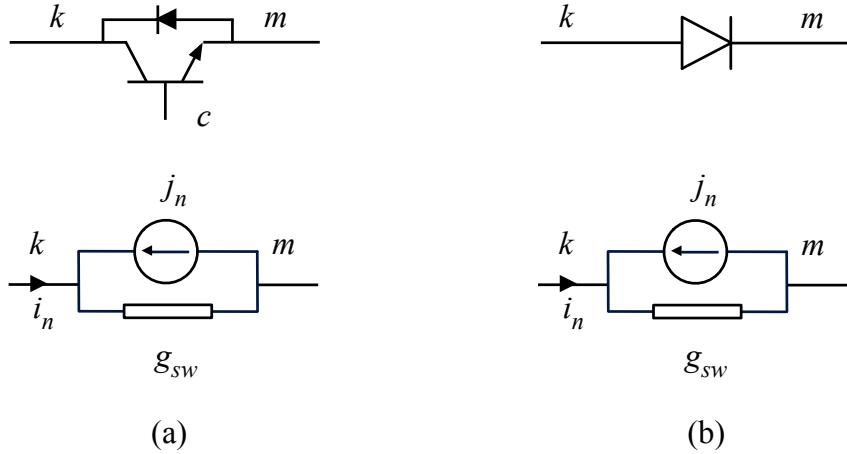

| 5.2  | Exemples de discréétisation d'interrupteurs. . . . .                      | 75  |

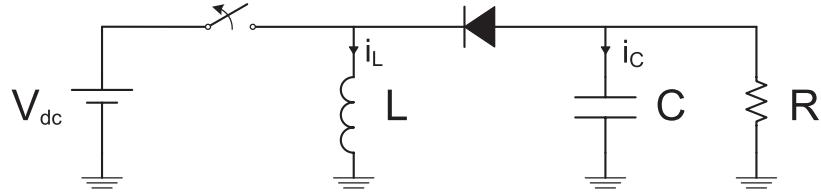

| 5.3  | Convertisseur buck-boost. . . . .                                         | 77  |

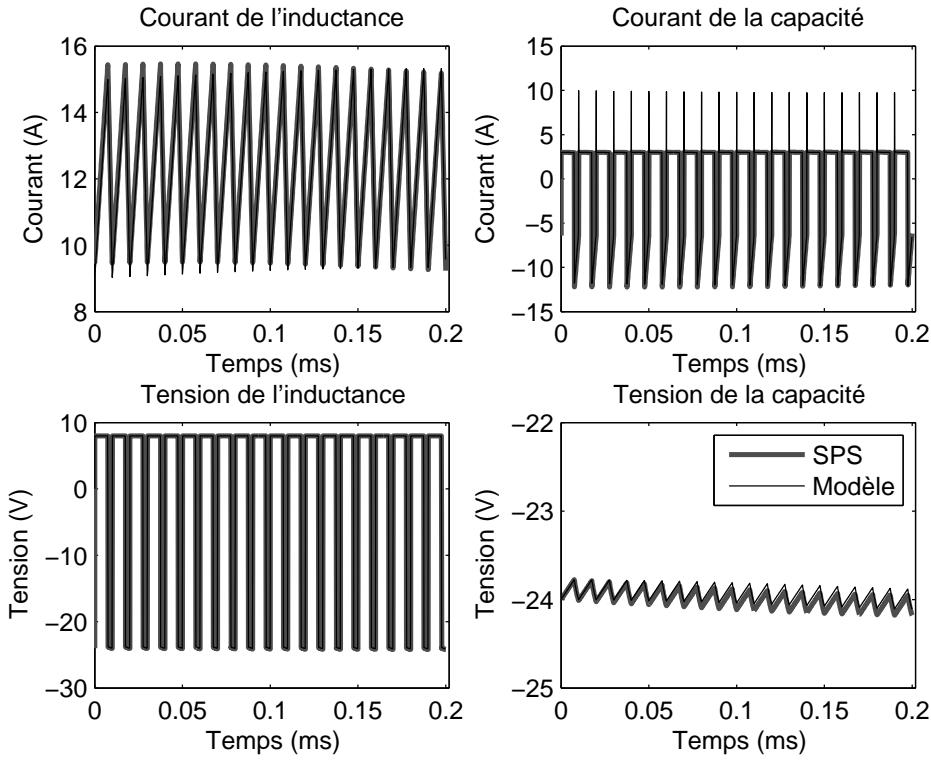

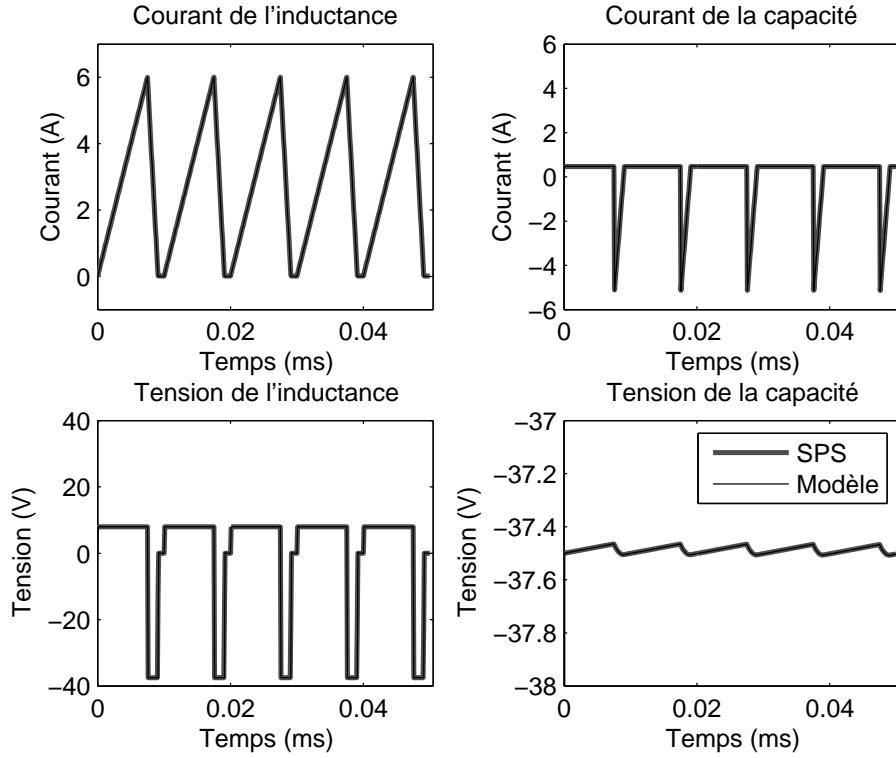

| 5.4  | Résultats de simulation du buck-boost en mode continu. . . . .            | 78  |

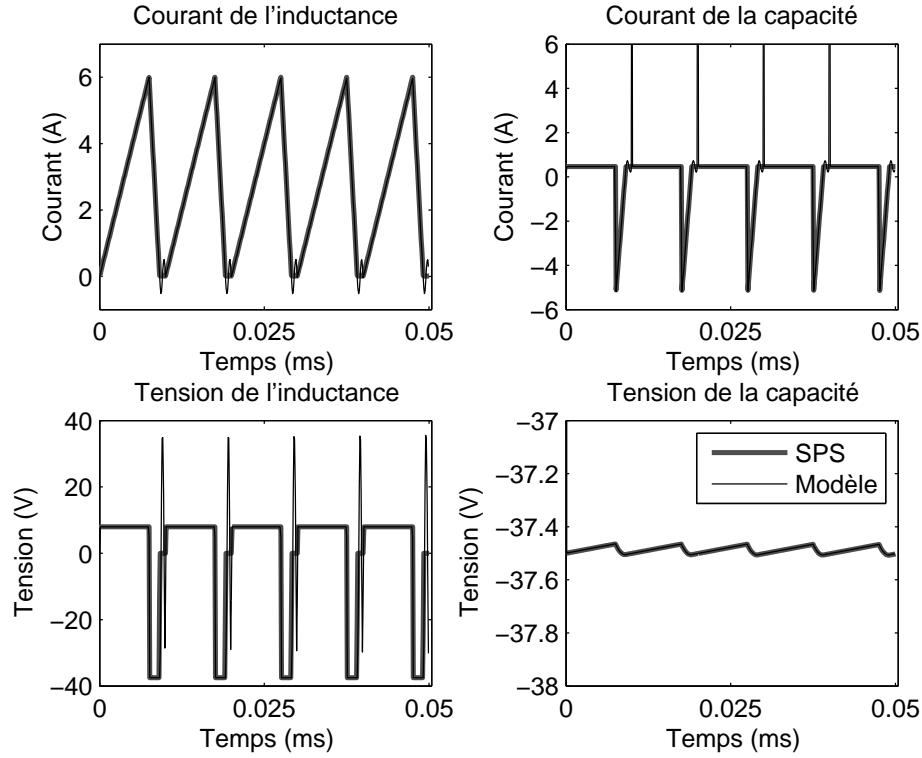

| 5.5  | Résultats de simulation du buck-boost en mode discontinu. . . . .         | 79  |

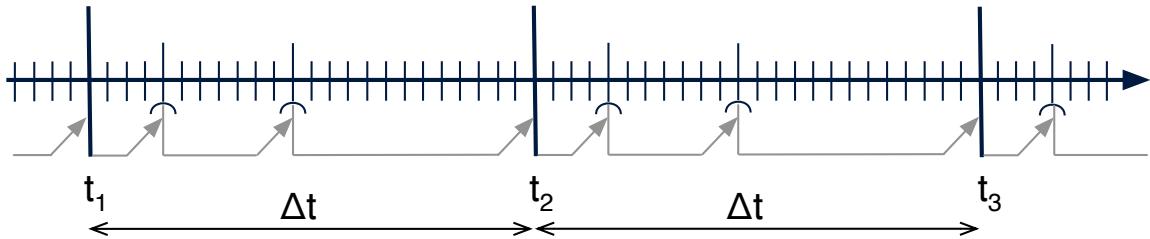

| 5.6  | Illustration du principe de la simulation par multiples sous-pas. . . . . | 80  |

| 5.7  | Résultats de simulation corrigés du buck-boost. . . . .                   | 81  |

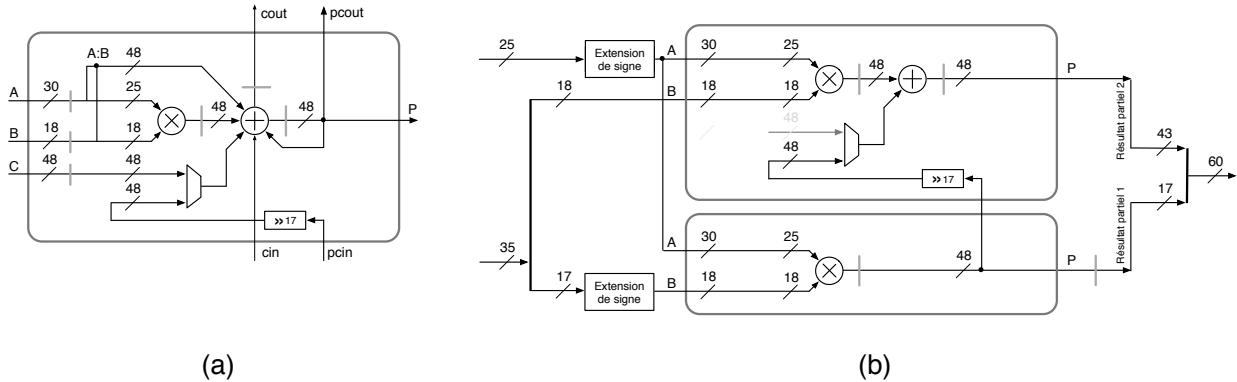

| 5.8  | Résultats d'un multiplieur large. . . . .                                 | 83  |

| 5.9  | Convertisseur boost. . . . .                                              | 84  |

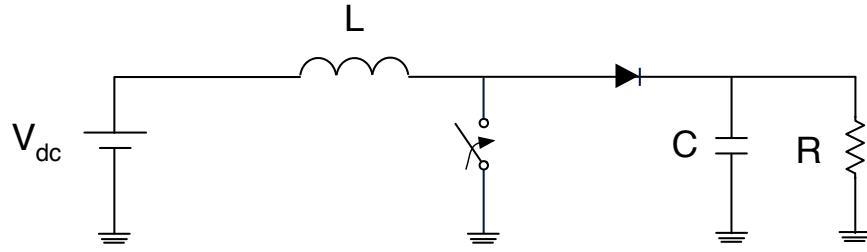

| 5.10 | Erreur relative dans la simulation du convertisseur boost . . . . .       | 86  |

| 5.11 | Topologie d'un engin de calcul pour résoudre les équations MANA. .        | 87  |

| 5.12 | Trois circuits d'électronique de puissance servant à tester l'eHS . . . . | 88  |

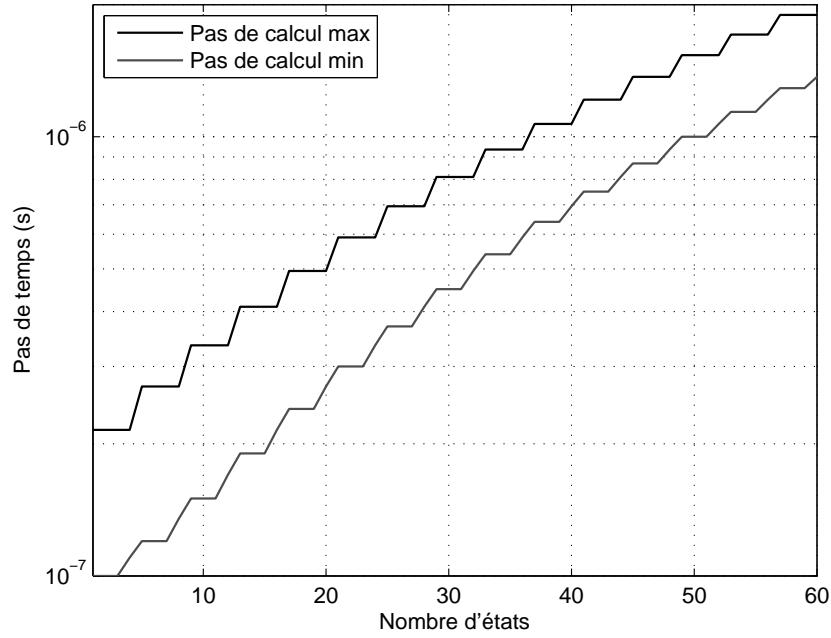

| 5.13 | Évolution du pas de calcul de l'eHS. . . . .                              | 89  |

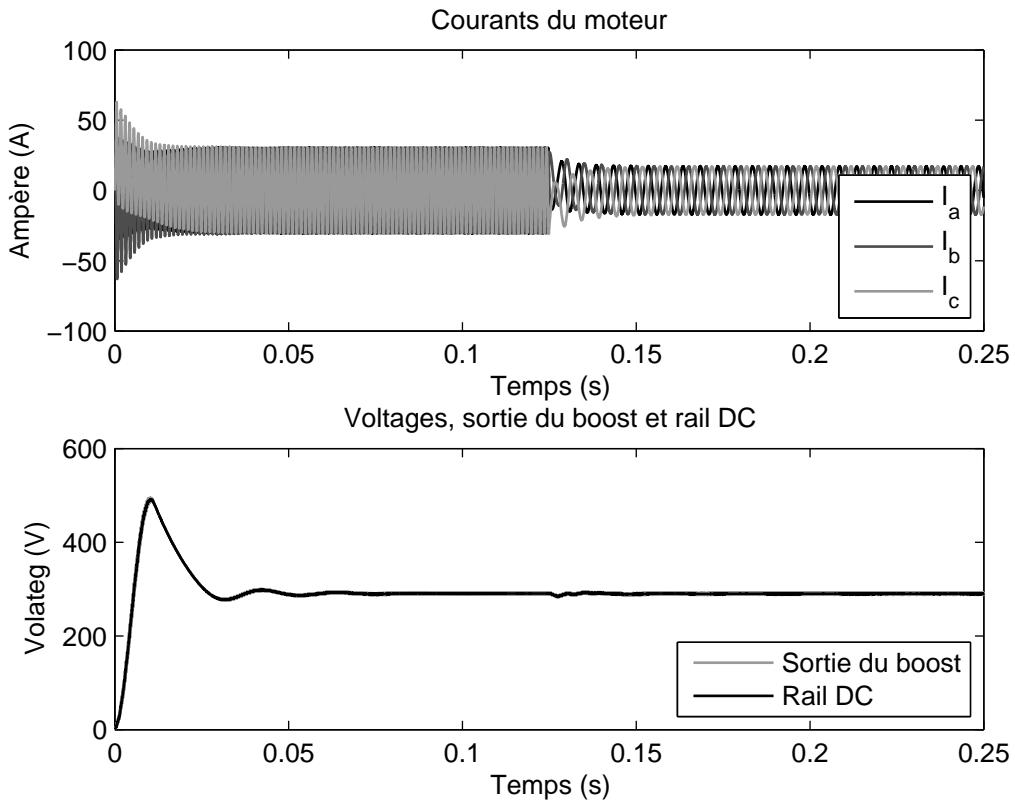

| 5.14 | Résultats de simulation du circuit #3 . . . . .                           | 91  |

| 5.15 | Circuit d'onduleur découplé . . . . .                                     | 92  |

| 5.16 | Simulation d'onduleur alimentant un moteur PMSM . . . . .                 | 93  |

| 5.17 | Simulation en temps réel d'un onduleur . . . . .                          | 94  |

| 5.18 | Structure du MMC. . . . .                                                 | 95  |

| 5.19 | Relation entre le pas de temps et le nombre de SM. . . . .                | 97  |

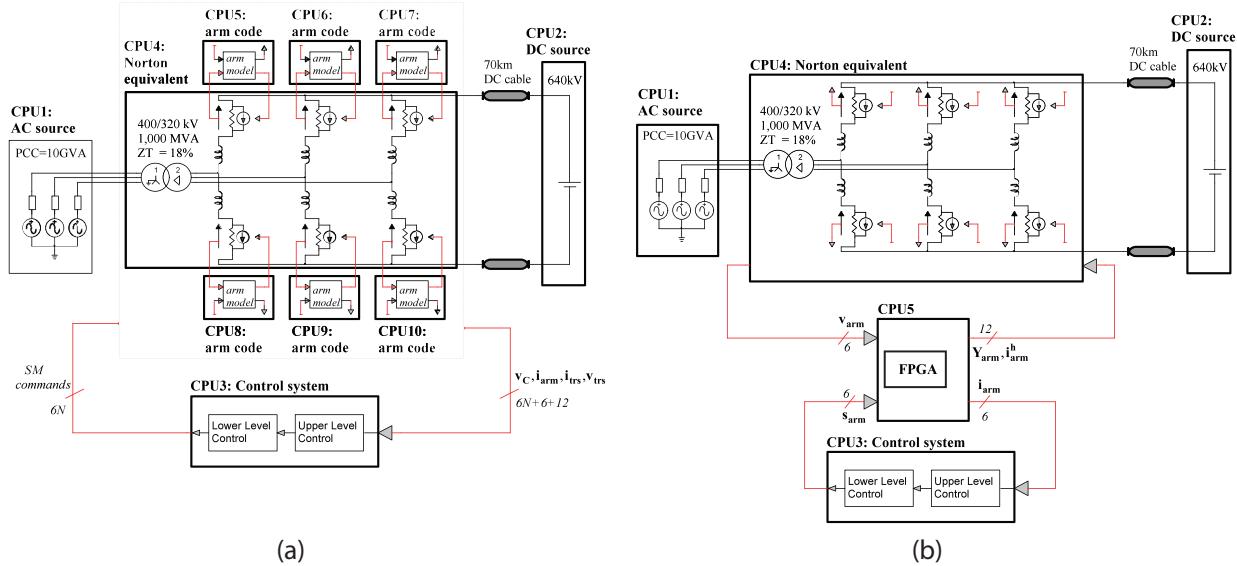

| 5.20 | Infrastructure matérielle pour la simulation du MMC . . . . .             | 98  |

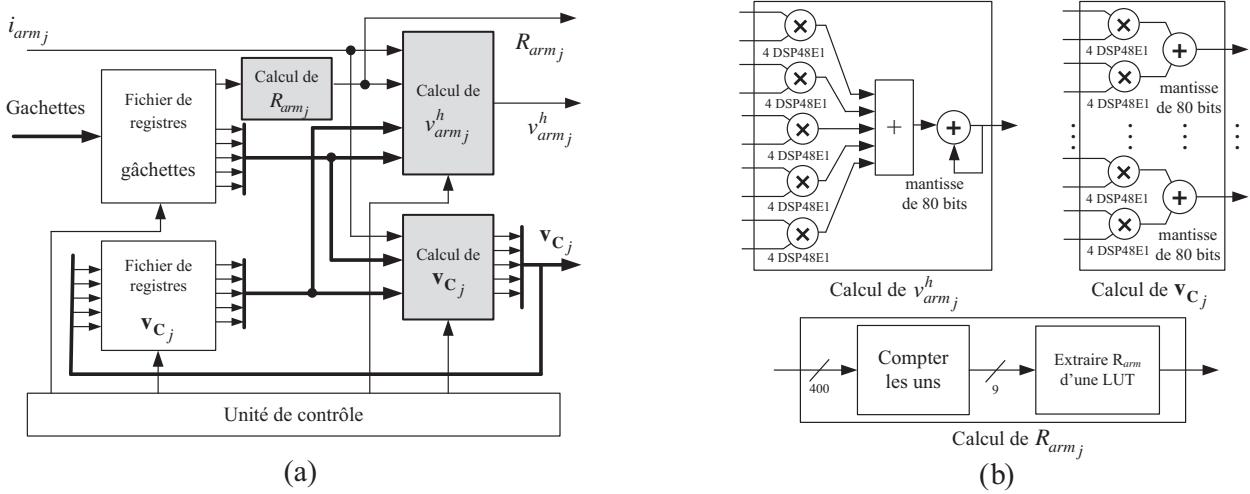

| 5.21 | Engin de calcul pour la simulation du MMC . . . . .                       | 99  |

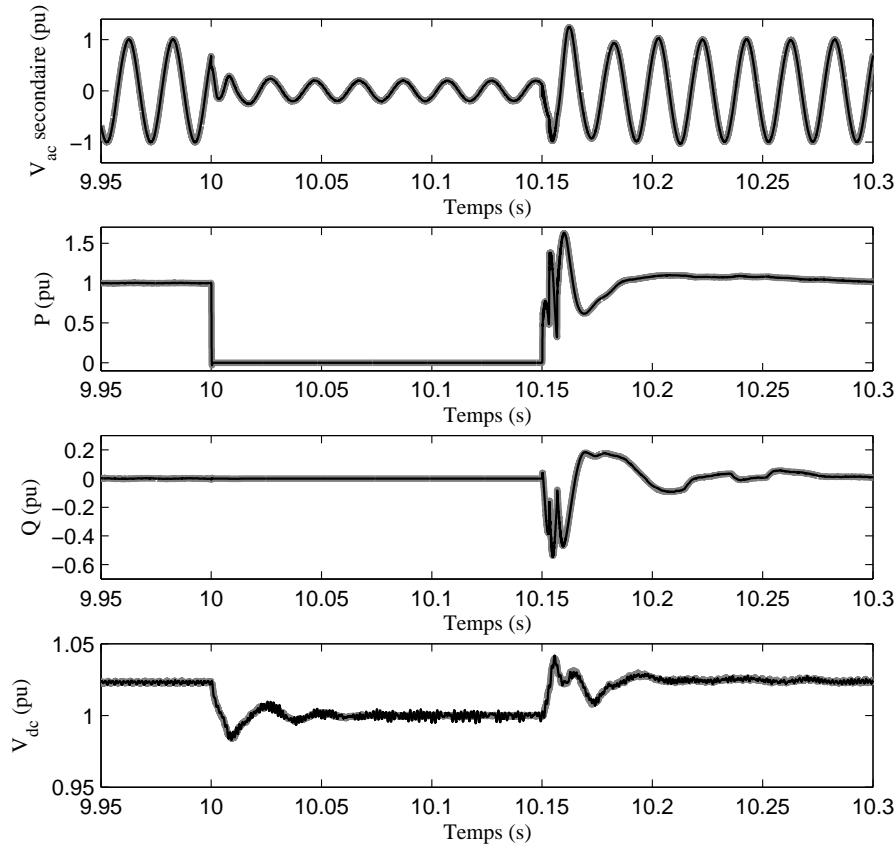

| 5.22 | Résultats de simulation du MMC . . . . .                                  | 100 |

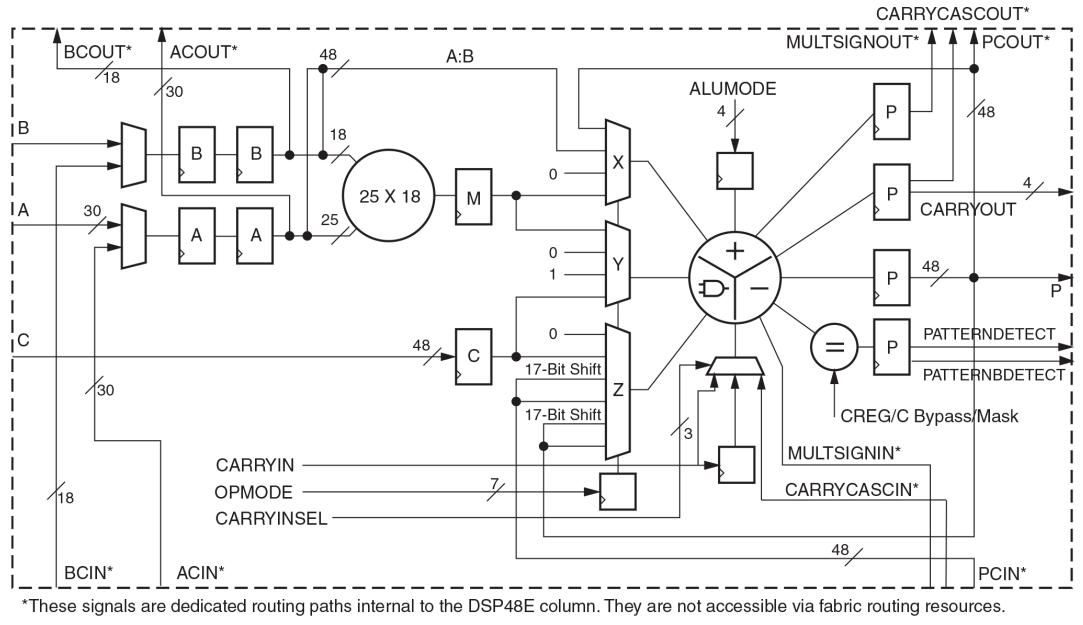

| A.1  | Bloc DSP du Virtex 5. . . . .                                             | 121 |

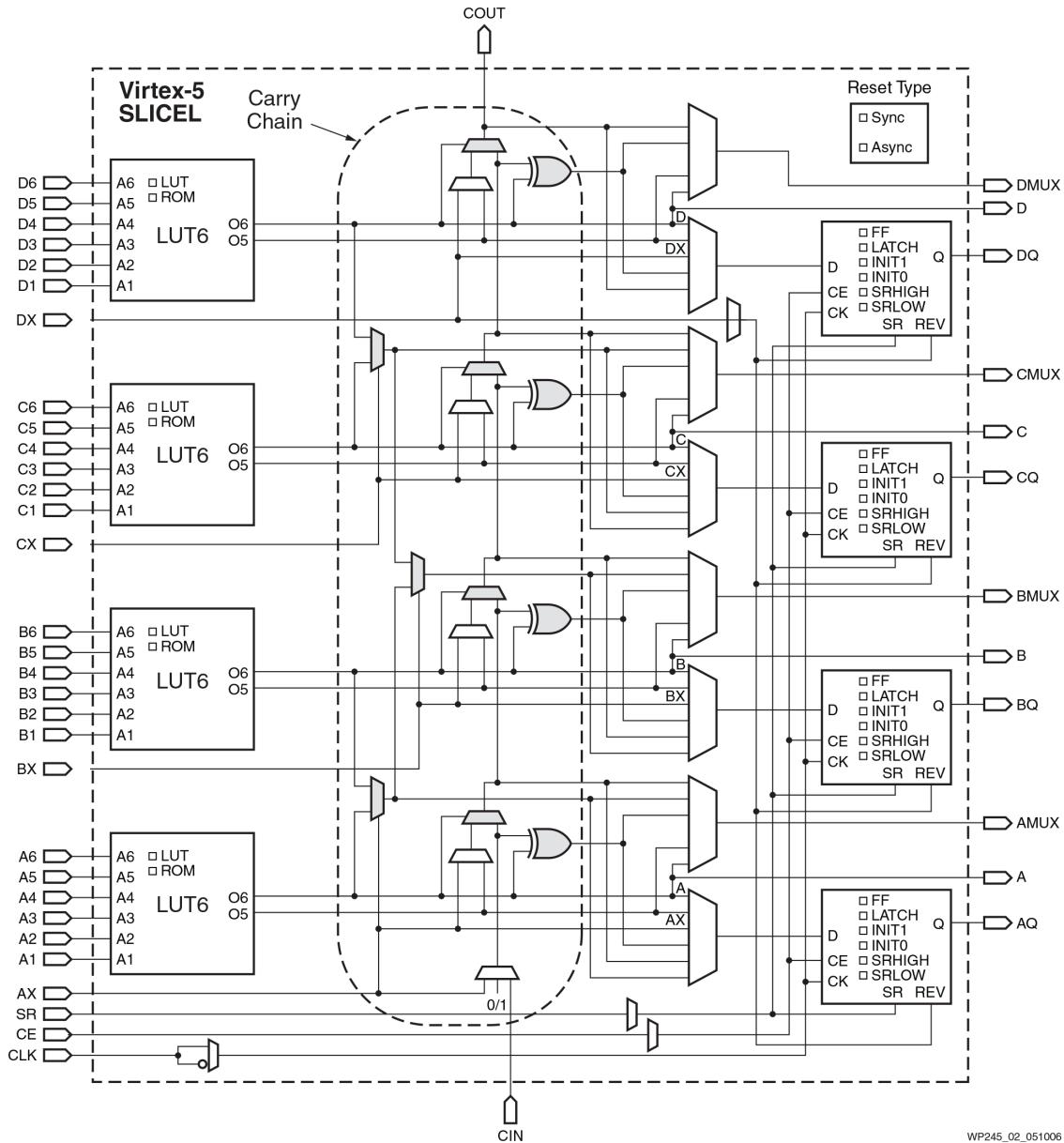

| A.2  | Schéma d'une <i>slice</i> du Virtex 5. . . . .                            | 122 |

## LISTE DES ANNEXES

|                                                                |     |

|----------------------------------------------------------------|-----|

| ANNEXE A      Technologie FPGA . . . . .                       | 119 |

| A.1 Marché mondial . . . . .                                   | 119 |

| A.2 Altera vs. Xilinx . . . . .                                | 119 |

| A.3 Technologie de FPGA chez Xilinx . . . . .                  | 120 |

| A.3.1 Blocs DSP . . . . .                                      | 120 |

| A.3.2 Blocs RAM . . . . .                                      | 121 |

| A.3.3 Circuits dédiés à la propagation de la retenue . . . . . | 121 |

| A.4 Outils de conception . . . . .                             | 123 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|              |                                                                                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>APR</b>   | Additionneur à propagation de retenue                                                                                                                                                       |

| <b>BRAM</b>  | Bloc RAM : bloc de mémoire gravé en dur dans le FPGA                                                                                                                                        |

| <b>clk</b>   | Abréviaison anglaise de <i>clock</i> : référence au signal d'horloge                                                                                                                        |

| <b>CS</b>    | Carry-Save : format redondant utilisant la sauvegarde de la retenue                                                                                                                         |

| <b>CAN</b>   | Convertisseur analogique à numérique                                                                                                                                                        |

| <b>CLA</b>   | Carry Look-ahead : Anticipateur de retenues                                                                                                                                                 |

| <b>CNA</b>   | Convertisseur numérique à analogique                                                                                                                                                        |

| <b>CPU</b>   | Central Processing Unit : acronyme anglais servant à désigner un PUG, et par métonymie un ordinateur de bureau                                                                              |

| <b>dd</b>    | Décalage à droite                                                                                                                                                                           |

| <b>dg</b>    | Décalage à gauche                                                                                                                                                                           |

| <b>DP</b>    | Dot-product (operator) : acronyme utilisé dans nos publications anglophones pour désigner un OPS                                                                                            |

| <b>DSP</b>   | Digital Signal Processing : traitement de signal numérique                                                                                                                                  |

| <b>DUT</b>   | Device Under Test : dispositif sous test                                                                                                                                                    |

| <b>ECU</b>   | Electronic Control Unit : unité de contrôle électronique, acronyme répandu dans le domaine de l'automobile et de l'aérospatial                                                              |

| <b>eHS</b>   | acronyme de eHardwareSolver, nom commercial de l'engin de calcul versatile développé dans le cadre de la présente thèse et commercialisé par le partenaire industriel, Opal-RT Technologies |

| <b>EMT</b>   | Electromagnetic Transient : méthodes numériques de modélisation des réseaux électriques employant l'analyse nodale                                                                          |

| <b>EMTP</b>  | Electromagnetic Transient Program : logiciel de simulation des réseaux électriques de type EMT                                                                                              |

| <b>E/S</b>   | Entrées/sorties                                                                                                                                                                             |

| <b>FA</b>    | Full Adder : additionneur complet                                                                                                                                                           |

| <b>FAA</b>   | Format d'auto alignement, associé à la TAA                                                                                                                                                  |

| <b>FLOPS</b> | Floating-point Operations Per Second : mesure de la puissance de calcul évaluée par la quantité d'opérations en virgule flottante pouvant être effectuées en une seconde                    |

|               |                                                                                                                                                                                             |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>FMA</b>    | Fused Multiply-Adder : multiplieur additionneur fusionnés                                                                                                                                   |

| <b>FPGA</b>   | Field Programmable Gate Array : circuit numérique fait de réseaux pré-diffusés programmables                                                                                                |

| <b>HIL</b>    | Hardware-in-the-Loop : réfère à une configuration particulière de la simulation en temps réel où du matériel est connecté au simulateur et se retrouve dans la boucle de simulation         |

| <b>HRCS</b>   | High Radix Carry-Save : sauvegarde de retenues à base élevée                                                                                                                                |

| <b>IEEE</b>   | Institute of Electrical and Electronics Engineers : société professionnelle regroupant les ingénieurs électriciens et électroniciens en charge notamment d'établir les normes industrielles |

| <b>IGBT</b>   | Insulated Gate Bipolar Transistor : transistor bipolaire à grille isolée                                                                                                                    |

| <b>ISE</b>    | Logiciel de synthèse et d'implémentation des FPGA de la compagnie Xilinx                                                                                                                    |

| <b>LUT</b>    | Look-Up Table : table des correspondances                                                                                                                                                   |

| <b>GFLOPS</b> | GigaFLOPS : un milliard de FLOPS                                                                                                                                                            |

| <b>Matlab</b> | Logiciel mathématique de la compagnie Mathworks                                                                                                                                             |

| <b>MAC</b>    | Multiply-accumulator : multiplieur-accumulateur                                                                                                                                             |

| <b>MANA</b>   | Modified-augmented nodal analysis : analyse nodal modifiée et augmentée                                                                                                                     |

| <b>MEE</b>    | Méthode explicite d'Euler                                                                                                                                                                   |

| <b>MIE</b>    | Méthode implicite d'Euler                                                                                                                                                                   |

| <b>MLI</b>    | Modulation de largeur d'impulsion, PWM en anglais                                                                                                                                           |

| <b>MMC</b>    | Modular Multilevel Converter : convertisseur de puissance multi-niveaux                                                                                                                     |

| <b>MNA</b>    | Modified nodal analysis : analyse nodal modifiée                                                                                                                                            |

| <b>OPS</b>    | Opérateur de produit scalaire                                                                                                                                                               |

| <b>PMSM</b>   | Permanent magnet synchronous motor : moteur à aimant permanent                                                                                                                              |

| <b>PUG</b>    | Processeur à usage général : processeur tels que ceux que l'on retrouve dans les ordinateurs personnels, par opposition aux processeurs à usage spécifiques                                 |

| <b>PUS</b>    | Processeur à usage spécifique : processeur spécialisé destiné à l'exécution d'un d'algorithme ou d'une tâche spécifique                                                                     |

| <b>PWM</b>    | Pulse-width modulation, acronyme anglais de MLI                                                                                                                                             |

| <b>RAM</b>    | Random access memory : mémoire à accès aléatoire                                                                                                                                            |

| <b>ROM</b>    | Read only memory : mémoire à accès aléatoire permettant uniquement les accès en lecture                                                                                                     |

|                 |                                                                                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>RCA</b>      | Ripple Carry Adder : additionneur à propagation de retenue                                                                                                     |

| <b>slice</b>    | Unité reconfigurable des FPGA de Xilinx, tranche en français                                                                                                   |

| <b>SD</b>       | Signed-Digit : format redondant utilisant des chiffre signés                                                                                                   |

| <b>SIMD</b>     | Single Instruction, Multiple Data : architecture de processeur où des unités de calcul parallèles exécutent les mêmes instructions sur des données différentes |

| <b>Simulink</b> | Logiciel de simulation numérique de la compagnie Mathworks                                                                                                     |

| <b>SM</b>       | Sous-module : cellule d'un convertisseur MMC                                                                                                                   |

| <b>SPS</b>      | SimPower System : logiciel de simulation des réseaux électriques commercialisé sous la forme d'une boîte à outils Matlab/Simulink                              |

| <b>TAA</b>      | Technique d'auto alignement, technique permettant d'accumuler des opérandes en virgule flottante avec une boucle d'accumulation à un cycle                     |

| <b>TNA</b>      | Transient Network Analyzer : simulateur analogique                                                                                                             |

| <b>ulp</b>      | Unit in the Last Place : poids du plus petit bit de la mantisse d'une représentation en virgule flottante                                                      |

| <b>VF</b>       | Virgule flottante                                                                                                                                              |

## INTRODUCTION

La simulation en temps réel des réseaux électriques connaît un intérêt industriel marqué. Cet engouement est motivé par la réduction substantielle des coûts de développement qu'une telle approche permet. Pour avoir une idée de la chose, il suffit de penser à des systèmes tels que les véhicules électriques, les aéronefs modernes ou les réseaux de distribution électrique, domaines d'application où la complexité et le coût élevé des systèmes donnent la préférence à la simulation plutôt qu'au prototypage physique. De plus, la simulation en temps réel permet d'intégrer dans la boucle de la simulation du matériel au fur et à mesure de la conception de ce dernier, ce qui permet d'en vérifier le bon fonctionnement dans des conditions réalistes. C'est d'ailleurs là une des spécificités du domaine : la simulation en temps réel permet l'adjonction d'un matériel au simulateur dans une configuration dite de matériel dans la boucle (*hardware-in-the-loop* : HIL) que ne permet pas (ou difficilement) une simulation en temps différé.

Durant la première moitié du XX<sup>e</sup> siècle, la simulation des transitoires dans les réseaux électriques se fait au moyen de simulateurs analogiques appelés TNA (*Transient Network Analyser*). Ces simulateurs résolvaient les équations différentielles par l'interaction d'unités analogiques interconnectées (additionneurs, intégrateurs) ou en recourant à des modèles réduits permettant la reproduction à l'exact, mais à des échelles moindres, des phénomènes à l'étude. Les simulateurs analogiques eurent leur temps de gloire et continuèrent d'être utilisés jusqu'à l'adoption récente des méthodes numériques de simulation qui rendit possible l'apparition des calculateurs puissants que sont nos ordinateurs modernes. Progressivement, les simulateurs numériques se développèrent sous la forme de grappes d'ordinateurs interconnectés par des liens rapides, offrant une puissance de calcul confortable et permettant la prise en charge de modèles de plus en plus complexes.

Néanmoins, la simulation en temps réel au moyen de processeurs à usage général (PUG) souffre de certaines limitations inhérentes à l'infrastructure matérielle et aux systèmes physiques à l'étude. D'une part, la puissance de calcul brute des PUG s'avère parfois insuffisante pour l'atteinte d'un pas de calcul de l'ordre de quelques micro-secondes, ce qui est un requis important pour la simulation fidèle des transitoires rapides telles que celles des réseaux commutés à haute fréquence. Une autre limitation provient des liens de communication liant le PUG à ses périphériques et dont la latence intrinsèque ralentit l'accès aux interfaces (sensors et actuators) du dispositif sous test. Cet état de fait est alors répercuté sur la durée totale de la boucle de simulation, rendant impossible la simulation des transitoires rapides.

Pour tenter d'apporter une réponse à ces difficultés, la pratique industrielle a adopté les circuits reconfigurables de type FPGA (Field Programmable Gate Array) pour la mise en œuvre de processeurs à usage spécifique (PUS) dédiés aux applications de simulation des réseaux électriques. Cette approche offre différents avantages : d'une part, les FPGA sont aujourd'hui suffisamment denses pour accueillir des engins de calcul de grande capacité (quelques dizaines de GFLOPS), ce qui laisse espérer que le modèle à simuler peut être déplacé en partie ou en totalité du PUG vers le PUS ; d'autre part, un FPGA peut disposer d'un accès direct aux entrées/sorties (E/S) du simulateur, réduisant considérablement les latences d'accès aux senseurs et aux actuateurs du dispositif sous test et permettant du même coup la simulation de systèmes à dynamiques rapides.

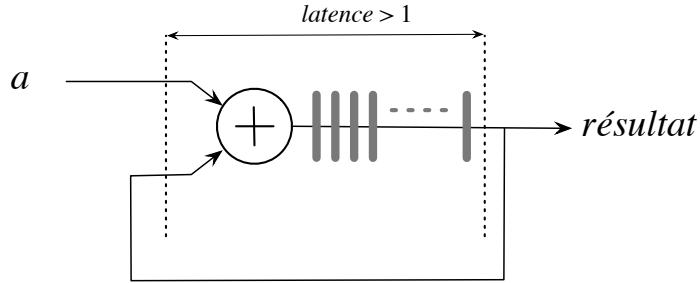

Il convient de relever que l'utilisation des circuits reconfigurables pour des applications de calcul connaît un vif intérêt. Cet intérêt est justifié d'une part par la croissance impressionnante des ressources matérielles disponibles sur ces dispositifs. De plus, le caractère reconfigurable des FPGA leur confère une flexibilité architecturale qui, dans les cas favorables, permet d'atteindre des performances de calcul meilleures que celles offertes par des processeurs commerciaux. Néanmoins, les paradigmes usuels du traitement de signal sur FPGA introduisent certaines restrictions. Ainsi, il est d'usage d'opérer sur FPGA une arithmétique à virgule fixe qui pénalise le temps de développement puisqu'elle requiert du concepteur (qui, dans le cas de figure qui nous intéresse, n'est souvent pas un expert) un redimensionnement de l'ensemble des variables du modèle mathématique. Une façon de contourner ce problème est d'utiliser une arithmétique à virgule flottante. En effet, il est aujourd'hui possible de disposer sur FPGA d'opérateurs à virgule flottante que l'usager peut obtenir grâce aux librairies commerciales du manufacturier de la puce. Cependant, l'emploi de ces opérateurs impose des latences qui peuvent s'avérer handicapantes, particulièrement dans le cas de l'addition car les techniques de modélisation considérées ici emploient des lois d'intégration (trapézoïdale, Euler-arrière, etc.) pour lesquelles l'utilisation d'un accumulateur est cruciale. Or, les additionneurs en virgule flottante nécessitent en général plusieurs cycles opératoires, restreignant d'une certaine façon la rétroaction directe de la sortie de l'additionneur à une de ses entrées. La problématique de l'addition et de l'accumulation en virgule flottante forme le cœur de notre travail de recherche et deux chapitres de la thèse lui sont consacrés. Quatre objectifs guideront notre démarche dans l'étude de cette problématique :

1. l'exactitude des calculs ;

2. la compacité des opérateurs d'addition ;

3. la célérité de ces derniers en termes de fréquences et de latence ; et

4. la possibilité de disposer d'une boucle d'accumulation à un cycle.

Ce travail permettra notamment d'élaborer des architectures d'accumulateurs, de multiplieurs accumulateurs (MAC) et d'opérateurs de produit scalaire (OPS) en virgule flottante, qui joueront un rôle déterminant dans la mise en œuvre de nos engins de calcul pour la simulation des réseaux électriques.

Les équations de réseau utilisées pour modéliser les systèmes susmentionnés sont généralement formulées suivant deux approches distinctes : *i*) les équations d'état ; et *ii*) l'analyse nodale. Les deux méthodes sont considérées dans le présent travail. Leur solution repose sur les techniques de résolution des systèmes d'équations différentielles linéaires ou linéaires par parties. Nous démontrons ici que celles-ci s'expriment sous la forme d'un produit matrice-vecteur constraint temporellement sur la rétroaction des états du circuit. Ce qui est entendu par la contrainte temporelle est l'importance d'actualiser au plus vite les variables du système avant de débuter un nouveau pas de temps. La méthode des équations d'états retiendra notre attention surtout pour la modélisation des moteurs électriques d'une part, et du fait qu'elle est au cœur de la librairie SimPowerSystem (SPS) qu'exploite dans ses produits le partenaire industriel de la présente thèse, la compagnie montréalaise Opal-RT Technologies. La méthode nodale quant à elle est caractérisée par la simplicité de sa formulation (facilitant d'autant son automatisation) et sera utilisée dans notre travail pour la modélisation des réseaux à interrupteurs. Nous présentons à cette fin une réécriture des équations de la méthode nodale pour alléger la contrainte sur le chemin de données de nos engins de calcul.

Étant données les contraintes temporelles susmentionnées, il est d'usage de pré-calculer la solution des équations du réseau ou, dans le cas de circuits à interrupteurs, les solutions des différentes topologies du réseau que ces interrupteurs induisent. Ce dernier point nous poussera à étudier des approches permettant de réduire la quantité de mémoire nécessaire à la simulation sur puce des systèmes à l'étude. Il motivera également la recherche de solutions permettant de repousser les limites usuelles imposées aux problèmes considérés dans la simulation en temps réel sur FPGA.

Ainsi, l'implémentation matérielle d'engins de calcul en virgule flottante implique plusieurs défis architecturaux qu'il convient d'étudier et d'évaluer adéquatement. Les paramètres à considérer sont :

1. La taille des ressources reconfigurables disponibles (slices, blocs DSP, blocs RAM) ;

2. La taille de la mémoire embarquée (blocs RAM) nécessaire pour simuler un problème donné et la manière de l'exploiter ;

3. La latence des opérateurs arithmétiques (MAC/OPS) réalisés et leur impact sur la latence globale des engins de calcul ;

4. L'exactitude des calculs, tant au niveau unitaire des opérateurs (MAC/OPS) qu'au niveau système ;

5. Les techniques de modélisation des réseaux électriques, et plus particulièrement des réseaux à interrupteurs.

Notre travail de thèse offre différentes contributions scientifiques que nous pouvons énumérer comme suit :

1. Au domaine de l'arithmétique des ordinateurs, nous avons contribué à la formulation d'un algorithme de sommation qui est une généralisation de la technique d'auto-alignement précédemment publiée dans la littérature. Nous avons à ce titre simplifié son expression et sa réalisation matérielle, établi des critères permettant de garantir la bonne exactitude de ses résultats, critères que nous avons énoncés en les appuyant de démonstrations théoriques et empiriques.

2. Au domaine de l'arithmétique des ordinateurs également, nous avons contribué à l'analyse du format redondant *high radix carry-save* (HRCS) et à l'étude de son implémentation sur FPGA. Nous avons également contribué à définir deux nouveaux opérateurs au format HRCS. D'une part, nous avons défini un additionneur endomorphique, prenant en entrée deux opérandes en HRCS et produisant un résultat en HRCS. Ce résultat permet de réaliser des arbres d'additionneurs recevant des nombres de grande largeur (80 bits par exemple) et de les sommer avec une latence réduite. Le second opérateur proposé est un convertisseur HRCS à format conventionnel qui permet de convertir un résultat en HRCS en un format binaire standard. L'avantage de cet opérateur est qu'il a peu d'impact sur le chemin critique de l'additionneur et garantit une latence quasi-constante (un à trois cycles) pour une grande gamme de largeurs du format des nombres (jusqu'à 1024 bits).

3. Au domaine de la simulation en temps réel sur FPGA, nous avons contribué en unifiant l'écriture des équations du réseau, qu'elles soient exprimées selon l'analyse nodale ou les équations d'états. Cette réalisation a permis de formuler une architecture d'engins de calcul de type SIMD (*single instruction, multiple data*) faits à base d'opérateurs MAC et OPS en virgule flottante.

4. Nos contributions au domaine de l'arithmétique des ordinateurs ont permis de réaliser des opérateurs arithmétiques en virgule flottante complexes tels que MAC et OPS qui sont à la base des engins de calcul que nous proposons pour la simulation en temps réel des équations du réseau.

5. Finalement, nos travaux ont permis la réalisation d'un engin de calcul versatile permettant de simuler des convertisseurs de puissance de topologie arbitraire avec des pas

de temps en deçà du  $1 \mu\text{s}$ , tout en admettant des fréquences de commutations de plusieurs kilohertz. Cette réalisation a abouti une commercialisation par notre partenaire industriel.

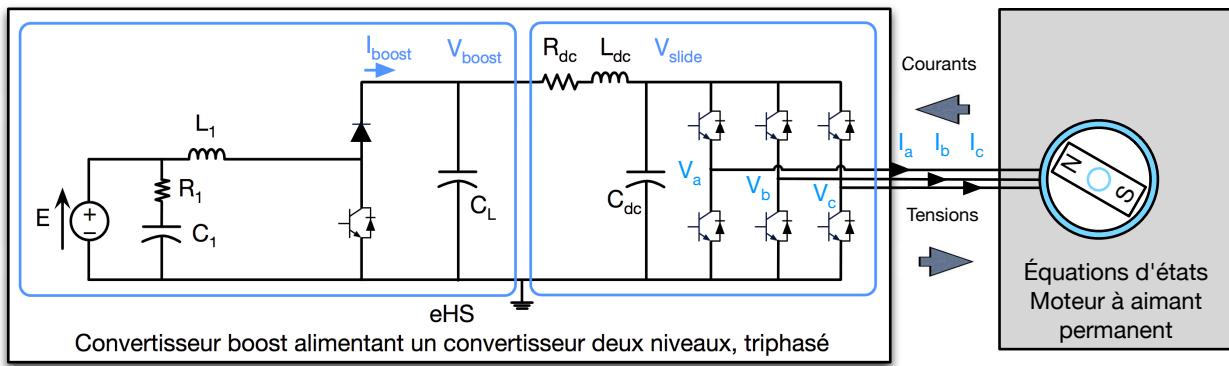

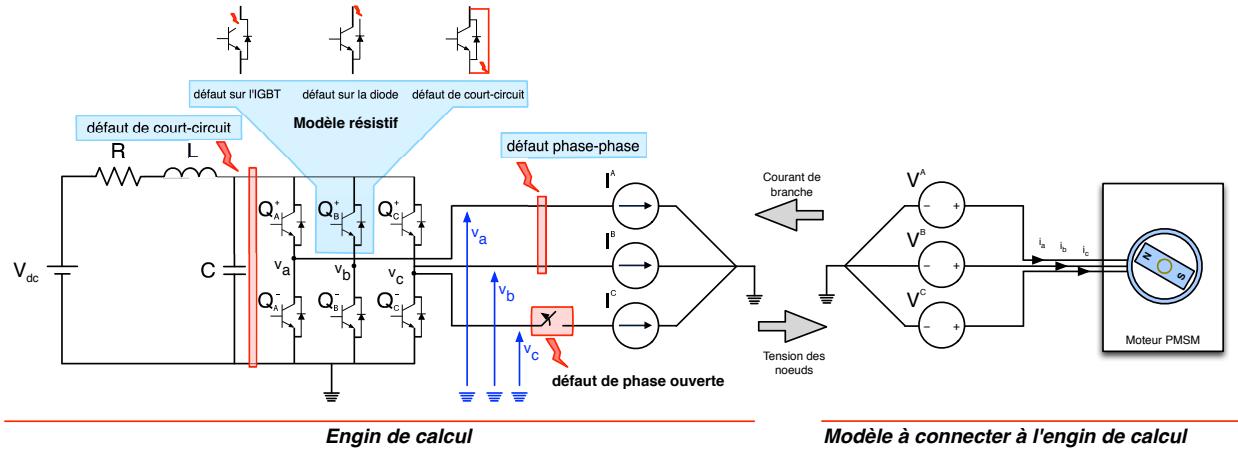

La présente thèse est organisée comme suit. Le Chapitre 1 propose une revue de la littérature touchant le domaine de la simulation en temps réel, de la simulation sur FPGA, des méthodes de modélisation des circuits à interrupteurs et des techniques rattachées à la représentation en virgule flottante sur FPGA. Le Chapitre 2 s'attaque ensuite à la problématique de la simulation sur FPGA. Les méthodes nodales et des équations d'états y sont présentées, ainsi que les méthodes proposées pour réécrire leur solution sous la forme d'un produit matrice-vecteur. L'analyse du partitionnement d'un tel problème sur plusieurs opérateurs arithmétiques est alors détaillée, démontrant le rôle de l'accumulateur à un cycle, celui du MAC et le rôle primordial joué par l'OPS. Le Chapitre 3 traite de la technique d'auto-alignement (TAA) qui fut proposée au début des années 2000 pour l'accumulation à un cycle d'opérandes en simple précision. Le chapitre en propose une reformulation et la généralisation de la portée algorithmique au format en double précision et aux formats intermédiaires, tout en identifiant les conditions garantissant la qualité de ses résultats. Le Chapitre 4 quant à lui traite du format HRCS, utilisé dans notre travail pour implémenter efficacement la TAA sur FPGA. Le Chapitre 5 exploite les résultats des trois chapitres précédents pour implémenter des engins de calcul destinés à la simulation en temps réel de circuits à interrupteurs modélisés au moyen de l'analyse nodale modifiée et augmentée (*modified-augmented nodal analysis* : MANA). Ce chapitre se termine avec la présentation d'un engin de calcul versatile permettant de simuler des convertisseurs de topologie arbitraire ayant jusqu'à 24 interrupteurs et qui est actuellement commercialisé par le partenaire industriel de cette thèse sous le nom eHS (eHardwareSolver).

# CHAPITRE 1

## REVUE DE LITTÉRATURE

### 1.1 Introduction

La revue de littérature présentée ici tente de faire un point sur l'état de l'art de la simulation des réseaux électriques sur FPGA. Dans un premier temps, nous traiterons des techniques de simulation des réseaux et tâcherons de relever les spécificités associées à la simulation en temps réel. Il est entendu ici par simulation des réseaux la simulation de systèmes aussi variés que les moteurs électriques, les convertisseurs de puissance ou les réseaux de distribution électriques. Cet examen nous portera à traiter des techniques de simulation des réseaux sur FPGA et des considérations qui leur sont propres. Notre revue de littérature portera finalement sur l'emploi de la virgule flottante sur FPGA, où nous veillerons à faire ressortir les paradigmes émergents dans ce domaine, notamment l'utilisation de formats non standards. Cette revue de littérature sera complétée dans les chapitres subséquents afin de couvrir plus en détail certains sujets plus pointus et de conférer au présent chapitre un caractère plus général.

### 1.2 Contexte

#### 1.2.1 Simulation des réseaux électriques

À partir des années 1930, la simulation des transitoires dans les réseaux électriques se fait au moyen des simulateurs analogiques appelés TNA. Un simulateur TNA est réalisé au moyen de modèles réduits du réseau électrique où les lignes de transmissions sont émulées par des sections en  $\pi$ . Les TNA sont suffisamment sophistiqués pour permettre l'évaluation de scénarios de court-circuit, de fautes ou de soudaine perte de charge. Un de leurs avantages majeurs est leur fonctionnement en temps réel puisqu'il permet une évaluation rapide de différents scénarios de fonctionnement des systèmes à l'étude, sans compter la possibilité d'y connecter physiquement des contrôleurs aux fins de leur validation empirique [73, 115].

L'avènement des ordinateurs numériques et la constante croissance de leurs capacités de calcul fit en sorte que les simulateurs numériques ont progressivement supplanté les TNA dans la pratique industrielle. L'émergence de la simulation numérique des réseaux électriques est souvent attribuée à l'article de Dommel [20] qui appliquait la discréétisation des éléments à l'analyse nodale du réseau. L'analyse nodale recourt à la relation courant-tension aux divers

noeuds du circuit en utilisant la discréttisation numérique des divers composants du circuit. Du point de vue du circuit, cela équivaut à recourir à l'équivalent Norton de l'ensemble des composants du réseau pour ensuite déterminer les tensions inconnues aux différents noeuds. On appelle généralement EMTP (*Electromagnetic Transients Program*) les logiciels utilisant les méthodes numériques pour la simulation des réseaux électriques. De nombreux logiciels de type EMT existent, un des plus connus étant EMTP-RV, développé sous les auspices d'Hydro-Québec sur la base des travaux du Professeur Mahseredjian [72].

Vers la fin des années 1990 et parallèlement au développement d'EMTP-RV, Mathworks commercialisait une boîte à outils Simulink/Matlab appelée SimPowerSystems (SPS), et dont le but est la simulation des réseaux de taille modeste. SPS exploite la représentation d'états pour la modélisation des réseaux électriques. Le chapitre 2 traitera plus en détail de ces deux méthodes de modélisation des réseaux et de leur utilisation potentielle sur FPGA.

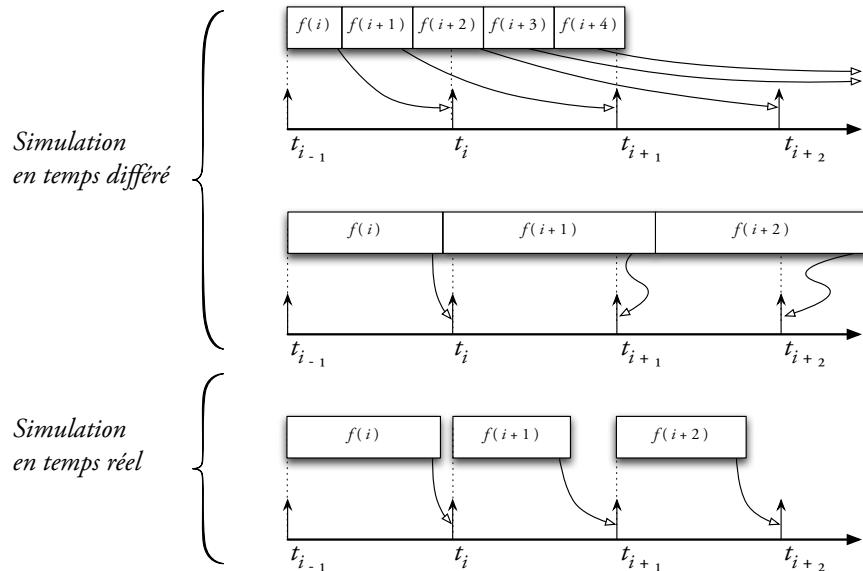

Figure 1.1 – Différence entre la simulation en temps différé et la simulation en temps réel.

### 1.2.2 Simulation en temps réel

Un des avantages majeurs des TNA est leur fonctionnement en temps réel qui permet d'y adjoindre des contrôleurs physiques. Les méthodes de simulation numériques ne sont pas forcément exécutées en temps réel et peuvent tout autant se concevoir dans le cadre d'une simulation en temps différé. Si l'on se fie à la Figure 1.1, il apparaît qu'une simulation en temps différé produit les états du système à chaque fois qu'une itération termine, ce qui signifie que la simulation peut être soit plus rapide que le temps réel (cas où les calculs ne

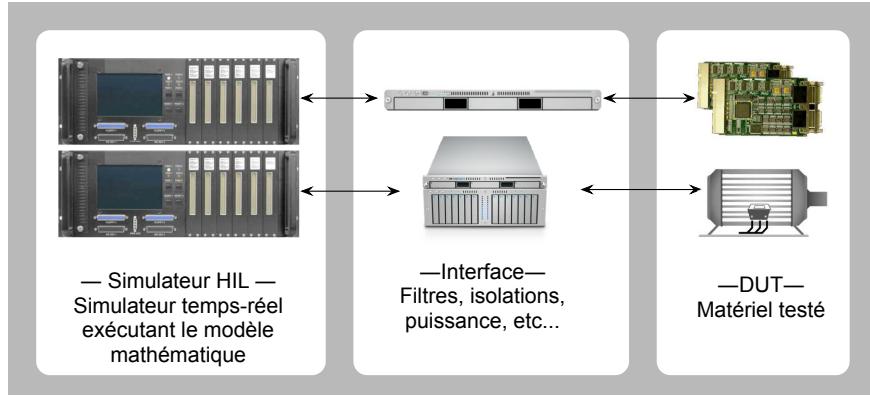

Figure 1.2 – Configuration typique d'un simulateur HIL.

sont pas trop longs), soit plus lente que le temps réel (cas de charge de calcul importante). Dans le cas d'une simulation numérique en temps réel, il est admis que le temps de calcul associé à chaque itération ne doit pas être plus long que le pas de calcul lui-même. De plus, le début de chaque itération est synchronisé sur le début du pas de calcul.

La simulation numérique en temps réel a connu un essor important durant les dix à vingt dernières années, c'est-à-dire depuis l'avènement de simulateurs à base de grappes d'ordinateurs personnels qui permirent d'en réduire le coût tout en offrant des puissances de calcul confortables [68, 90]. Étant donné que ce type de simulateurs sert principalement à interfaçer du matériel à des fins de tests et de validation, les simulateurs en temps réel sont souvent appelés simulateurs HIL (acronyme anglais de *Hardware in the Loop*). La Figure 1.2 présente la configuration typique d'un simulateur HIL, où une station de travail est connectée à un dispositif sous test (DUT). Le dispositif sous test peut tout autant être un contrôleur électronique ou un dispositif de puissance (par exemple un panneau solaire). Le dispositif sous test est connecté au simulateur au travers d'une interface d'isolation ou de conditionnement de signal.

Les simulateurs HIL sont largement employés dans les industries automobile et aérospatiale pour valider le bon fonctionnement d'unités de contrôle appelées ECU (*Electronic Control Unit*) sur un modèle mathématique du réseau. L'objectif principal d'une simulation HIL est la réduction des coûts de conception en effectuant des tests sur le prototype réel durant son développement dans des conditions réalistes d'opération [68, 73]. La simulation HIL permet également une couverture de test la plus large possible, incluant les cas limites d'opération qui seraient dangereux voire impossibles à réaliser sur du vrai matériel (cas de faute phase-phase sur une des bornes du moteur, par exemple) [24].

### 1.2.3 Utilité des FPGA dans les simulateurs HIL

Durant les dix dernières années, les FPGA ont fait leur apparition sur les simulateurs HIL comme une composante importante. Les FPGA sont adjoints à ces simulateurs pour servir divers objectifs :

1. Offrir au modèle simulé sur le PUG un accès aux entrées/sorties (E/S), tant analogiques que numériques ;

2. Servir d'interface d'accès aux cartes de conversion analogiques (CAN/CNA) du simulateur qui emploient généralement des protocoles de communication sérielle tel que SPI ou I<sup>2</sup>C ;

3. Générer des fonctions spécialisées telle que des sinus, des signaux de résolveur ou des signaux de modulation de largeur d'impulsion (MLI) ;

4. Détection des événements inter-pas (gâchette de contrôle s'ouvrant ou se refermant au milieu du pas de calcul) pour les besoins de certaines méthodes d'interpolation [23].

La littérature indique qu'il est aujourd'hui envisageable de déplacer, en tout ou en partie, la charge de calcul depuis les CPU du simulateur vers le FPGA [75, 84]. Nous discutons à la Section 1.4 de cette problématique qu'on appellera «la simulation sur puce».

## 1.3 Techniques propres à la simulation en temps réel

Les contraintes physiques et temporelles auxquelles est soumise la simulation en temps réel nécessitent certains artifices de modélisation qui méritent d'être considérés plus en détail. Cette section propose de revoir les techniques les plus souvent employées dans le domaine et qui nous seront d'une grande utilité dans le reste du travail. Ce faisant, la section se propose également de brosser un portrait de l'état de l'art du domaine.

### 1.3.1 Réseaux à interrupteurs

Il est fréquent dans la pratique industrielle de considérer des réseaux à interrupteurs, notamment dans la modélisation des convertisseurs de puissance. Ces réseaux sont de plus en plus présents dans le domaine des réseaux électriques et se retrouvent tout autant dans les systèmes à faible ou moyenne tension que les systèmes à très haute tension. Un réseau commuté pose des contraintes de simulation du fait que la topologie du réseau est modifiée à chaque fois qu'un interrupteur change de statut (ouvert/fermé). Il est généralement admis que la simulation de réseaux commutés peut suivre deux modes distincts : le mode détaillé et le mode comportemental [54]. On retrouve le mode détaillé dans des logiciels tels que

SPICE ou EMTP-RV où le modèle de l'interrupteur est une fonction non linéaire analytique ou linéaire par segments. Ce mode de simulation est très demandant en temps de calcul et se prête mal à la simulation en temps réel. Le mode comportemental quant à lui est consubstantiel à la simulation HIL et se caractérise par une complexité de calcul modérée.

Trois modèles d'interrupteur produisent une simulation en mode comportemental [54] : 1) le modèle idéal ; 2) le modèle de fonction de commutation ; 3) le modèle moyen. Dans le contexte de la simulation en temps réel, la littérature rapporte l'utilisation de chacun de ces modèles pour la modélisation de circuits d'électroniques de puissance. On relèvera cependant que le modèle moyen ne donne aucune information sur le comportement détaillé des transitoires et s'intéresse simplement aux niveaux de tension ou de courant correspondant au fonctionnement au niveau système d'un convertisseur de puissance [95]. Le modèle de fonction de commutation permet au contraire d'atteindre un niveau de détail suffisamment appréciable, avec souvent un niveau de résolution de l'ordre de quelques nanosecondes [24]. Ce modèle est cependant très dépendant de la topologie du convertisseur, ne considère que des convertisseurs avec un nombre d'interrupteurs modeste (moins de 8<sup>1</sup>) et peut difficilement se généraliser. Il reste finalement le modèle idéal. Ce dernier se traduit soit par un interrupteur idéal, soit par une résistance binaire ( $R_{on}/R_{off}$ ). Un tel modèle offre différents avantages, notamment de permettre la simulation des cas de faute de court-circuit ou de circuit ouvert [49]. Cependant, un tel modèle nécessite la reformulation des équations du réseau pour chaque combinaison des statuts des interrupteurs [25, 110], ce qui implique généralement de mémoriser les équations de chacune des topologies ainsi induites, limitant de ce fait le nombre d'interrupteurs à 6 ou 7. De plus, dès lors que le circuit inclut des dispositifs à commutation naturelle (des diodes par exemple), la simulation en temps réel nécessite que ce modèle soit adjoint d'une fonction de commutation. Ainsi, le problème retourne à la restriction du modèle d'interrupteur à mode comportemental, soit une limite sur les différentes topologies pouvant être considérées due à la nécessité d'opérer une étude relativement élaborée des différents modes de fonctionnement du convertisseur [49].

Au début des années 1990, un effort conjoint de deux équipes de recherche a abouti à la formulation d'un modèle d'interrupteur qui connaît un regain d'intérêt dans le domaine de la simulation en temps réel [45, 47, 94]. Ce modèle procède en deux temps. D'une part, il choisit de modéliser l'interrupteur soit comme une petite capacité  $C_{sw}$  (pour indiquer que l'interrupteur est ouvert), soit comme une petite inductance  $L_{sw}$  (pour indiquer que l'interrupteur est fermé). En choisissant adéquatement les valeurs de  $C_{sw}$  et  $L_{sw}$ , il est possible d'obtenir des équations du réseau totalement indépendantes des statuts des interrupteurs, apportant ainsi une solution aux limitations de mémoire évoquées précédemment. D'autre

---

1. Cette limite sera justifiée au Chapitre 5.

part, ce modèle d'interrupteur est accompagné d'une règle de mise à jour du statut de l'interrupteur pour différents types de semi-conducteurs [94] exprimée de manière relativement simple puisqu'elle ne dépend que de la gâchette, du statut courant de l'interrupteur et des signes du courant et de la tension aux bornes du dispositif. Ce modèle a été largement utilisé et constitue l'approche algorithmique principalement adoptée dans notre travail de thèse. Il convient cependant de mentionner que cette approche souffre de certaines limitations que nous aurons soin de considérer plus en détails au Chapitre 5.

### 1.3.2 Découplage du réseau

Le découplage du réseau est une technique qui consiste à découper le réseau en deux ou plusieurs parties dans le but d'atteindre différents objectifs. D'une part, la charge de calcul nécessaire à la simulation d'un réseau complet est souvent supérieure à la charge de calcul que nécessite la simulation de ses multiples sous-réseaux. Dans le cas d'une simulation en temps réel, cet allègement de la charge de calcul par le découpage du réseau peut permettre une réduction éventuelle du pas de temps de la simulation, améliorant par conséquent la précision de cette dernière. D'autre part, le découplage simplifie la parallélisation du calcul sur plusieurs processeurs. Le parallélisme peut tout autant se considérer dans le contexte de simulateurs à base de grappes d'ordinateurs que de simulateurs à base de processeurs multi-coeurs. Un autre intérêt du découplage, dans le cas des réseaux commutés tels les convertisseurs de puissance, provient du fait que le découplage du réseau permet de circonscrire des sous-ensembles d'interrupteurs et de réduire la quantité de mémoire nécessaire pour conserver les équations du réseau.

Une fois le découplage du réseau obtenu — et en supposant une exécution parallèle de la simulation —, il est établi que le pas de temps de la simulation est au minimum le pas de temps le plus lent des pas des sous-réseaux. De plus, tous les processeurs sont synchronisés par un processeur maître qui se charge de cadencer la simulation [73]. Pour ce faire, il faut que tous les échanges d'information entre les processeurs soient conclus avant de débuter un nouveau pas de temps. La durée de la communication dépend de la technologie adoptée : les communications inter-processeurs au travers d'une mémoire partagée (aujourd'hui disponibles sur les ordinateurs de bureau) étant plus rapides que celles exploitant des liens de communication standards telles que PCIe ou Infiniband [90]. Il en ressort que les meilleurs pas de calcul que l'on puisse observer durant une simulation en temps réel avoisinent les 2 à 3  $\mu\text{s}$ <sup>2</sup>, mais elles ne sont possibles qu'au moyen d'une mémoire partagée et excluent la présence de matériel dans la boucle. Aussi, dès lors qu'on est en présence de signaux E/S

---

2. Cet énoncé s'appuie sur l'expérience que l'auteur a eue avec les outils de simulation de la compagnie partenaire de la thèse, Opal-RT Technologies.

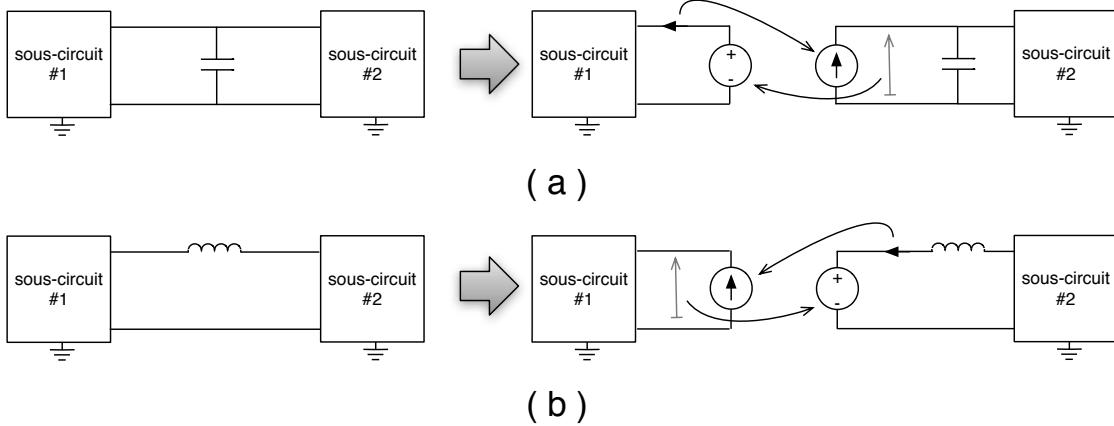

Figure 1.3 – Découplage d'un circuit en deux parties distinctes au travers d'un composant (a) capacitif; (b) inductif.

interfaçant du matériel, la littérature rapporte des pas de calcul qui sont de l'ordre de 5 à 10  $\mu\text{s}$  au mieux [74, 91].

Le découplage du réseau est traditionnellement effectué au niveau des lignes de transmission. Dans ce cas, la ligne de transmission joue un rôle de délai que peut répliquer avantageusement le délai de la communication [42]. Cette technique est très répandue et couramment utilisée dans les simulations des réseaux de transport de l'énergie électrique, mais elle se prête plus difficilement aux convertisseurs de puissance que l'on retrouve dans des réseaux de moyenne tension.

Une autre technique de découplage consiste à diviser le circuit aux points de variation lente de la tension ou du courant, c.-à-d. les capacités ou les inductances du circuit [46]. Les deux parties du circuit découpé retrouvent de part et d'autre l'information relative à l'autre moitié au moyen d'une source de courant et d'une source de tension, respectivement [49]. Ce procédé est illustré à la Figure 1.3. Contrairement aux techniques de découplage par lignes de transmission, ce type de découplage n'est qu'une approximation du véritable comportement du réseau. Des techniques d'interpolation peuvent être exploitées pour raffiner le résultat [58], mais elles ne sont envisageables que dans le cas d'une simulation en temps différé.

La littérature rapporte également des techniques de déchirement du réseau (*network tearing*) dites diakoptiques [11]. Des variantes de ces techniques ont été récemment proposées et implémentées avec succès dans un contexte de simulation en temps réel [26, 114]. Cependant, ces techniques sont difficilement envisageables sur FPGA car elles requièrent l'inversion de matrices, limitant considérablement le pas de calcul de la simulation et le champ d'application de la technologie.

## 1.4 Simulation sur FPGA

Une des grandes difficultés rencontrées dans la simulation en temps réel provient de la non-linéarité du réseau en présence des discontinuités dues aux commutations des interrupteurs. Comme nous avons pu le voir à la Section 1.3.1, différentes approches existent pour répondre à cette question. Dans les industries de l'automobile et de l'aérospatiale (très demanderesses de la méthodologie de prototypage HIL), la simulation en temps réel des convertisseurs de puissance nécessite des pas de calcul inférieurs à la microseconde. De tels contraintes temporelles sont dues aux fréquences de commutations de ces convertisseurs qui se trouvent dans l'intervalle des 10 kHz à 200 kHz [38, 123]. Aussi, si l'on se fie aux directives de bonne pratique admises par la communauté scientifique [35], les pas de calcul devraient être 10 à 20 fois plus petits que la période de la fréquence de commutation. Cela conduit à des pas de calcul dans l'intervalle de  $0.25 \mu\text{s}$  à  $5 \mu\text{s}$ . Comme nous avons pu le mentionner précédemment, de tels pas de calcul sont inconcevables dans un contexte de simulation sur CPU. C'est ainsi que les FPGA sont devenus de plus en plus utilisés dans le domaine de la simulation HIL, avec des pas de calcul rapportés dans l'intervalle  $0.1\text{-}1 \mu\text{s}$  [97, 100].

Ainsi, la croissance de la taille des FPGA durant les récentes années a rendu la simulation sur puce une solution à la fois envisageable et attrayante. Elle suscite de ce fait un important effort de recherche, comme le démontre la riche littérature s'y rapportant [2, 75, 74, 98]. La méthode de modélisation des interrupteurs à matrice constante [45, 47, 94] y a trouvé un terreau fertile [13, 66, 75, 85] pour des raisons évidentes de rareté de la mémoire embarquée. Nous reviendrons à cette technique avec plus de détails au Chapitre 5.

### 1.4.1 Représentation des nombres réels sur FPGA

Une des difficultés imposées par la simulation sur FPGA provient de la représentation des réels. La représentation en virgule fixe est naturelle dans ce contexte, mais elle impose des limitations sur les pas de calcul dues à des raisons de quantifications [75]. Il est possible d'éviter ces écueils en utilisant une approche de modélisation sans unité (p.u.) [24, 52]. Cette solution demeure néanmoins fastidieuse tant du point de vue de la conception que du point de vue de l'entretien et du déverminage. Le format à virgule flottante offre un potentiel intéressant. Avec la disponibilité des ressources matérielles sur les FPGA modernes, l'idée de recourir à la représentation en virgule flottante devient réaliste. Dans le contexte de la simulation des réseaux électriques, on mentionne une telle implémentation aussi tôt qu'en 2004 [52], où une approche mixte (combinant virgule flottante et virgule fixe) était utilisée pour la simulation d'un moteur d'induction. Aujourd'hui, les exemples d'implémentation en virgule flottante sont légion [2, 10, 74, 98], démontrant l'intérêt pour cette solution.

### 1.4.2 Opérateurs arithmétiques en virgule flottante

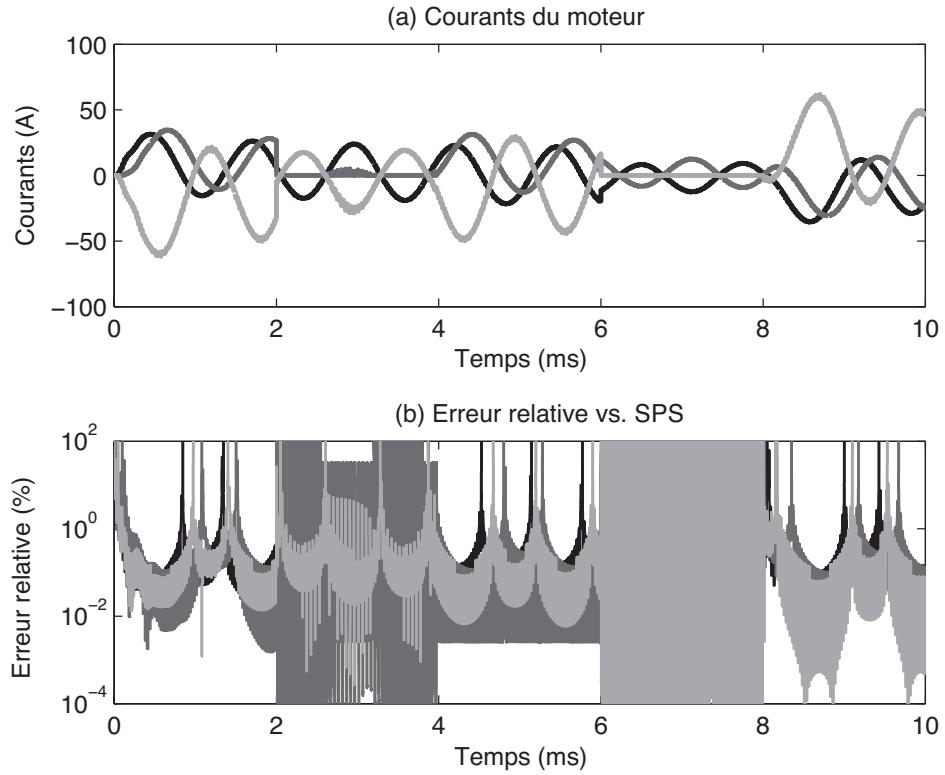

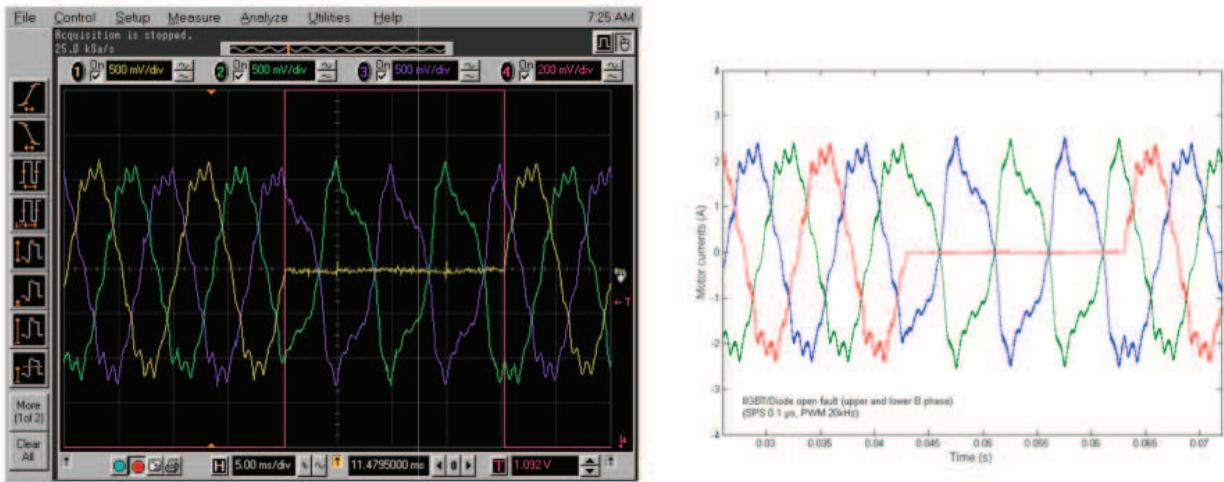

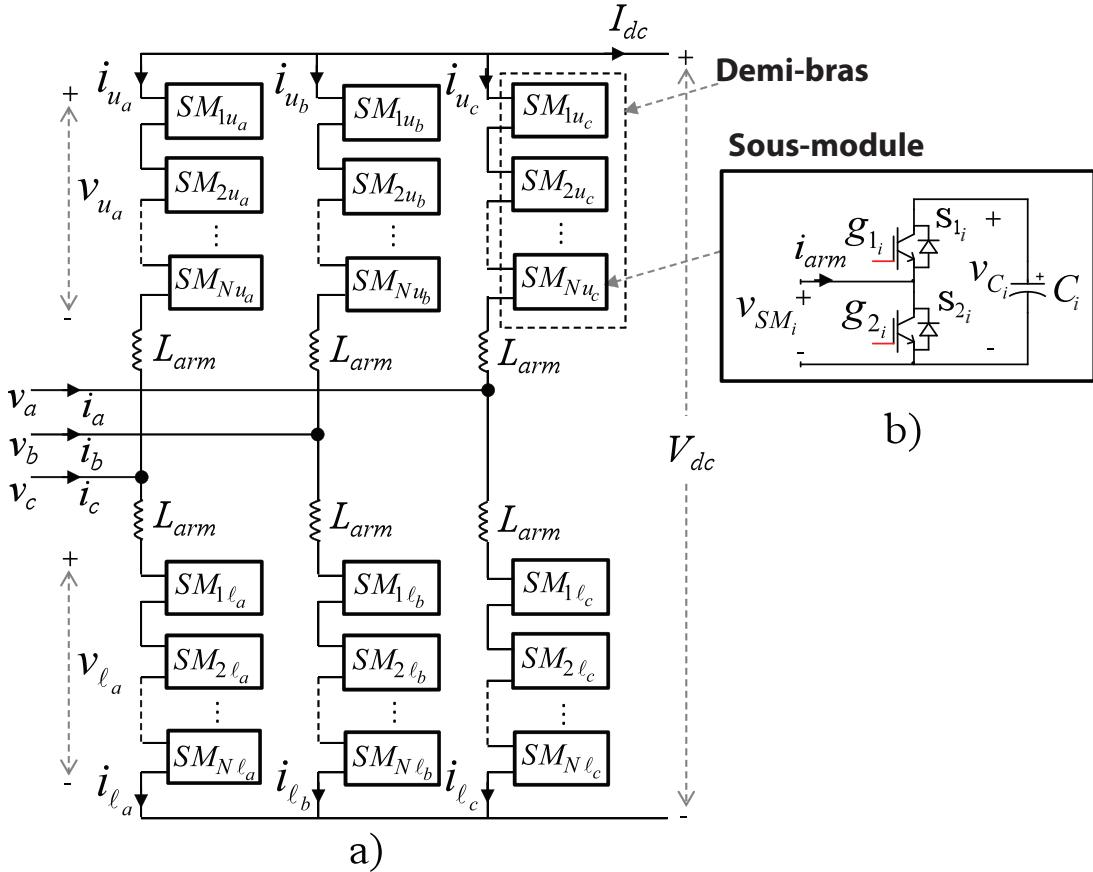

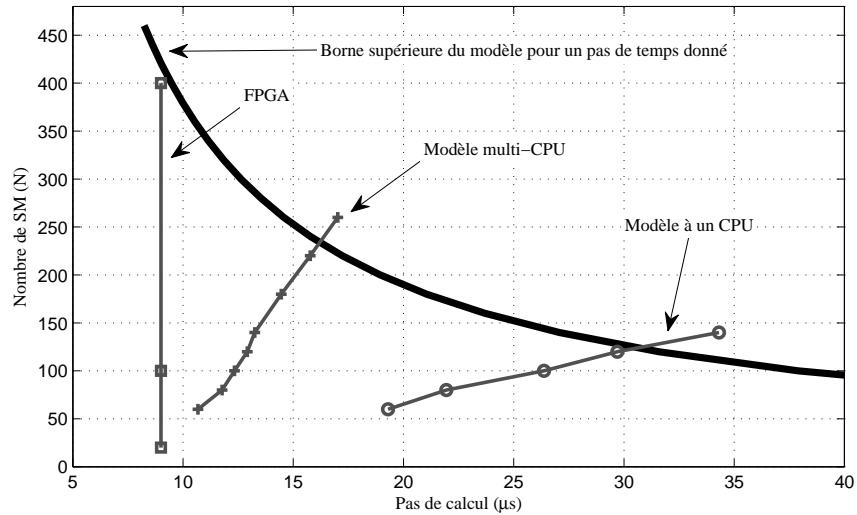

Afin de comprendre les enjeux portés par l'utilisation de la virgule flottante sur FPGA, nous allons procéder à un bref survol des concepts importants qui y prévalent. Nous aurons donc à cœur de discuter des quelques généralités qu'il sied de connaître, les librairies d'opérateurs à la disposition du concepteur ainsi que les paradigmes émergents.