**Titre:** Système de tomographie d'impédance électrique modulaire et

Title: reconfigurable réalisé à l'aide d'un FPGA

**Auteur:** Jean-Christophe Gervais

Author:

**Date:** 2013

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Gervais, J.-C. (2013). Système de tomographie d'impédance électrique modulaire et reconfigurable réalisé à l'aide d'un FPGA [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/1219/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/1219/>

PolyPublie URL:

**Directeurs de recherche:** Robert Guardo, & Hervé Gagnon

Advisors:

**Programme:** Génie biomédical

Program:

UNIVERSITÉ DE MONTRÉAL

SYSTÈME DE TOMOGRAPHIE D'IMPÉDANCE ÉLECTRIQUE MODULAIRE

ET RECONFIGURABLE RÉALISÉ À L'AIDE D'UN FPGA

JEAN-CHRISTOPHE GERVAIS

INSTITUT DE GÉNIE BIOMÉDICAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE BIOMÉDICAL)

AOÛT 2013

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

SYSTÈME DE TOMOGRAPHIE D'IMPÉDANCE ÉLECTRIQUE MODULAIRE

ET RECONFIGURABLE RÉALISÉ À L'AIDE D'UN FPGA

présenté par : GERVAIS Jean-Christophe

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. SAVARD Pierre, Ph.D., président

M. GUARDO Robert, Ph.D., membre et directeur de recherche

M. GAGNON Hervé, Ph.D., membre et codirecteur de recherche

M. BERTRAND Michel, Ph.D., membre

*“Live as if you were to die tomorrow. Learn as if

you were to live forever.”*

— Mahatma Gandhi

## REMERCIEMENTS

Tout d'abord, je souhaiterais remercier mon directeur de recherche, monsieur Robert Guardo. Son dévouement et sa grande disponibilité font de lui un directeur hors pair. Je voudrais aussi remercier mon codirecteur, monsieur Hervé Gagnon, sans qui ce projet n'aurait pu voir le jour. Je vais m'ennuyer de nos séances de discussions devant le tableau blanc. J'espère un jour accéder au même niveau de connaissances et de perfectionnisme que ces derniers.

Je voudrais aussi remercier monsieur Pierre Savard pour m'avoir permis d'être chargé de laboratoire en instrumentation biomédicale au cours de ma maîtrise. Cette expérience d'enseignement fut très enrichissante. Je le remercie aussi d'avoir su me convaincre, lors d'une certaine journée de portes ouvertes en 2005, d'embarquer dans cette aventure que fut l'École Polytechnique.

Je dois aussi remercier toutes les personnes que j'ai côtoyées dans notre laboratoire, ainsi que Claude Turcotte, mon technicien en informatique préféré. Un merci, tout spécial, à ces collègues qui sont aussi mes amis personnels : Julien Jéhanne-Lacasse et Yannick Sigmen.

Finalement, merci à ma famille, de toujours croire en moi et d'être une source inépuisable d'encouragements et de soutien. Et un merci bien particulier à ma plus grande partenaire, Audrey, il y a un peu d'elle dans ce projet aussi.

## RÉSUMÉ

La tomographie d'impédance électrique (TIE) est une technique d'imagerie médicale qui permet de visualiser la distribution de conductivité électrique d'une section du corps. Les principales applications de la TIE sont le monitorage de la ventilation pulmonaire, de l'activité cardiaque et de l'activité cérébrale ainsi que le dépistage du cancer du sein et de la peau. Les trois premières applications exploitent les variations de conductivité engendrées par le déplacement physiologique de fluides (air ou sang) qui sont de mauvais ou de bons conducteurs électriques. Les deux dernières utilisent les variations spécifiques du profil de conductivité des tissus en fonction de la fréquence. Ces profils dépendent de l'état physiologique ou pathologique des tissus. Chacune de ces applications nécessitent une variante différente de la TIE : multifréquentielle, tridimensionnelle ou synchrone à un événement physiologique. Jusqu'à récemment, chaque variante nécessitait la réalisation d'un système d'acquisition de données spécifique.

L'objectif de ce projet de maîtrise est de concevoir un système modulaire qu'on peut facilement reconfigurer selon l'application envisagée afin d'optimiser le rapport signal sur bruit ou la vitesse d'exécution.

L'approche choisie pour ce nouveau système est de réaliser tout le traitement numérique des signaux à l'aide d'un FPGA. À terme, ce système permettra de choisir le nombre de porteuses de fréquences différentes utilisées pour les mesures d'impédance (opération mono-, bi-, ou multifréquence), le nombre d'électrodes et leur distribution dans l'espace (mode bi- ou tridimensionnel) ainsi que l'acquisition de données synchronisée ou non à des signaux externes.

## ABSTRACT

Electrical impedance tomography (EIT) is a medical imaging technique that may be used to visualize the electrical conductivity distribution of a body section. EIT is mainly used for monitoring pulmonary ventilation, cardiac activity and cerebral activity as well as for screening breast and skin cancer. Pulmonary, cardiac and cerebral EIT monitoring relies on the variation of conductivity caused by physiological movement of body fluids (air or blood) which are respectively poor or good electrical conductors. EIT applications to cancer screening are based on specific variations of tissue conductivity as a function of frequency. These specific variations are also affected by the physiological or pathological state of tissues. Each of these applications requires a different type of EIT system: multifrequency, tridimensional or synchronous to a physiological event. Until now, a custom-designed data acquisition system had to be built for each different application.

The objective of this master's project is to design a modular system that can be easily reconfigured according to the EIT application to optimize signal to noise ratio or frame rate.

A Field Programmable Gate Array (FPGA) based approach has been selected to implement all digital signal processing for this new system. Once finalized, this system will allow selection of the number of carrier frequencies for measuring impedance (single frequency, dual frequency, and multifrequency modes), the number of electrodes and their distribution in space (bidimensional or tridimensional modes), as well as data acquisition synchronized to external signals or not.

## TABLE DES MATIÈRES

|                                                                                  |     |

|----------------------------------------------------------------------------------|-----|

| REMERCIEMENTS .....                                                              | IV  |

| RÉSUMÉ.....                                                                      | V   |

| ABSTRACT .....                                                                   | VI  |

| TABLE DES MATIÈRES .....                                                         | VII |

| LISTE DES TABLEAUX.....                                                          | IX  |

| LISTE DES FIGURES.....                                                           | X   |

| LISTE DES SIGLES ET ABRÉVIATIONS .....                                           | XII |

| INTRODUCTION.....                                                                | 1   |

| 1.1    Introduction à la tomographie d'impédance électrique.....                 | 2   |

| 1.1.1    Applications médicales de la TIE.....                                   | 3   |

| 1.1.2    Applications non médicales de la TIE.....                               | 5   |

| 1.1.3    Principe de mesure .....                                                | 6   |

| 1.1.4    TIE bifréquence.....                                                    | 10  |

| 1.2    Contexte du projet .....                                                  | 11  |

| 1.3    Définition du projet .....                                                | 13  |

| 1.4    Structure du mémoire .....                                                | 14  |

| CHAPITRE 2 MÉTHODES.....                                                         | 15  |

| 2.1    Description générale du système TIE5-USB .....                            | 15  |

| 2.2    Description du module d'électrodes actives.....                           | 18  |

| 2.3    Description matérielle du module de synthèse et de démodulation .....     | 21  |

| 2.3.1    Blocs d'alimentation .....                                              | 21  |

| 2.3.2    Isolation électrique .....                                              | 21  |

| 2.3.3    Convertisseurs analogique-numérique et numérique-analogique .....       | 22  |

| 2.3.4    FPGA.....                                                               | 23  |

| 2.3.5    Microcontrôleur USB .....                                               | 26  |

| 2.4    Architecture proposée pour le module de synthèse et de démodulation ..... | 26  |

| 2.4.1    Architecture globale .....                                              | 28  |

|                                   |                                                                              |           |

|-----------------------------------|------------------------------------------------------------------------------|-----------|

| 2.4.2                             | Flux des données sortantes : génération de la porteuse de référence .....    | 30        |

| 2.4.3                             | Flux des données entrantes : démodulation de la porteuse de mesure .....     | 31        |

| 2.4.4                             | Flux des données entrantes : transmission des données de TIE.....            | 36        |

| 2.4.5                             | Modules de coordination.....                                                 | 40        |

| 2.5                               | Description de l'interface informatique .....                                | 42        |

| <b>CHAPITRE 3 RÉSULTATS.....</b>  |                                                                              | <b>44</b> |

| 3.1                               | Montage expérimental.....                                                    | 44        |

| 3.2                               | Résultats des tests de caractérisation.....                                  | 47        |

| 3.3                               | Rapport signal sur bruit.....                                                | 50        |

| 3.4                               | Précision des mesures.....                                                   | 52        |

| 3.5                               | Images différentielles sur fantôme .....                                     | 54        |

| 3.6                               | Images <i>in vivo</i> .....                                                  | 56        |

| 3.7                               | Optimisation en fonction de la période inactive.....                         | 57        |

| 3.8                               | Comparaison au système TIE4-USB.....                                         | 58        |

| <b>CHAPITRE 4 CONCLUSION.....</b> |                                                                              | <b>60</b> |

| 4.1                               | Synthèse des travaux actuels .....                                           | 60        |

| 4.2                               | Suggestions de travaux futurs .....                                          | 63        |

| 4.2.1                             | Optimisation de la TIE-SF .....                                              | 63        |

| 4.2.2                             | Réalisation d'un système de TIE synchrone à un événement physiologique ..... | 65        |

| 4.2.3                             | Réalisation d'un système de TIE-BF .....                                     | 67        |

| 4.2.4                             | Réalisation d'un système de TIE-3D .....                                     | 68        |

| <b>BIBLIOGRAPHIE .....</b>        |                                                                              | <b>71</b> |

## **LISTE DES TABLEAUX**

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

| Tableau 1.1 Conductivité électrique de différents tissus.....                            | 3  |

| Tableau 2.1 Signaux du bus numérique reliant le MSD au MEA.....                          | 19 |

| Tableau 2.2 Affectation des bits dans une variable point-flottant double précision.....  | 37 |

| Tableau 2.3 Définition des différentes durées paramétrables par le module SEQUENCER..... | 40 |

| Tableau 4.1 Utilisation des ressources logiques du FPGA .....                            | 68 |

## LISTE DES FIGURES

|                                                                                                      |    |

|------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 Prisme rectangulaire composé de deux matériaux de conductivités différentes .....         | 6  |

| Figure 1.2 Schémas représentant les électrodes apposées au prisme.....                               | 7  |

| Figure 1.3 Séquence d'acquisition de données pour un système à seize électrodes .....                | 8  |

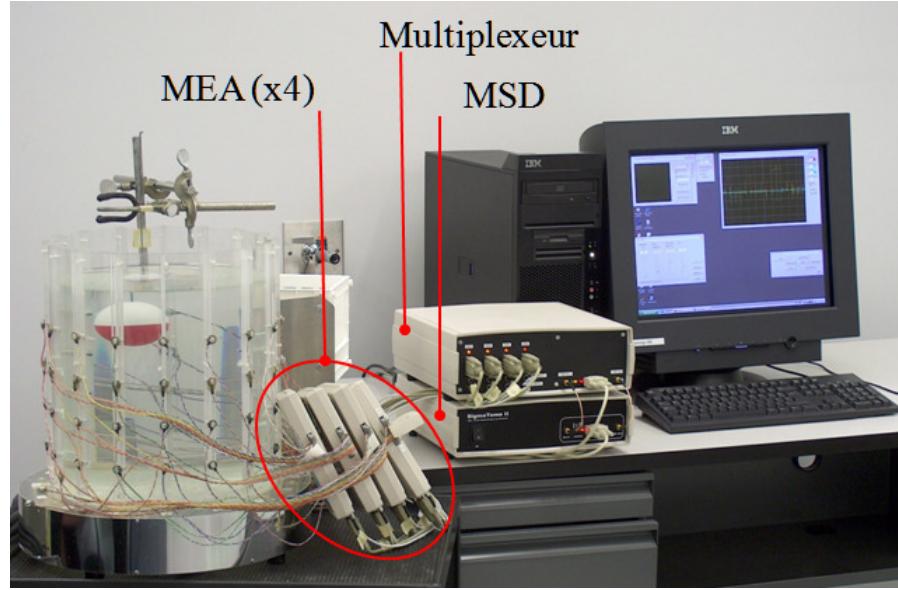

| Figure 1.4 Système de TIE développé dans notre laboratoire.....                                      | 9  |

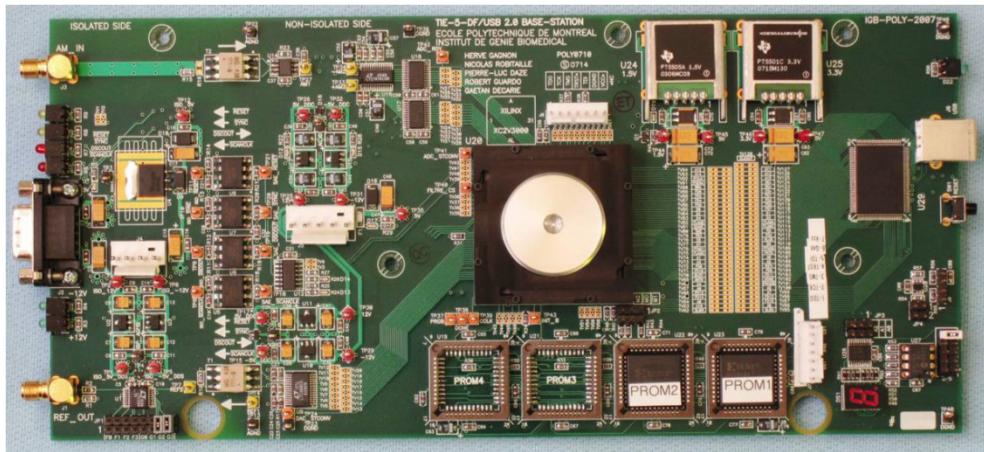

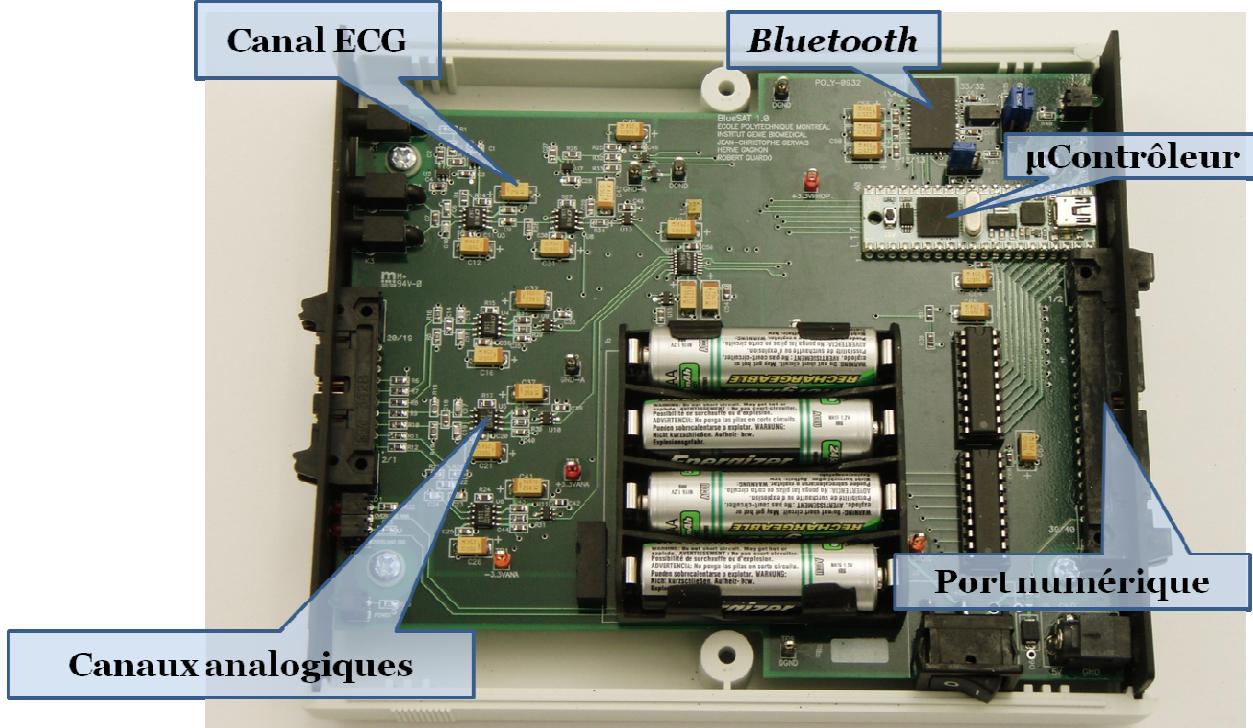

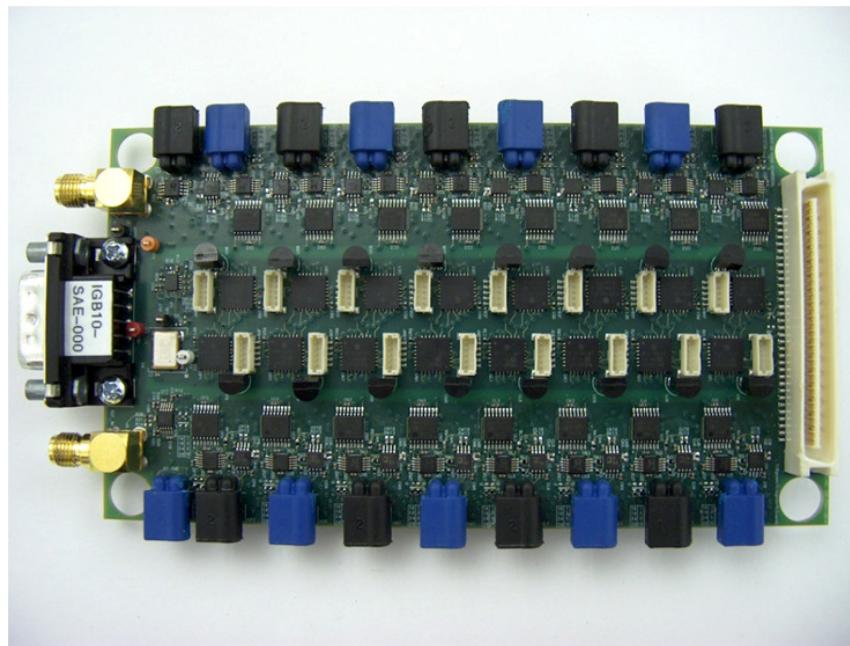

| Figure 1.5 Carte électronique du MSD des systèmes de TIE de 5 <sup>e</sup> génération.....           | 12 |

| Figure 2.1 Représentation schématique du système TIE5-USB .....                                      | 15 |

| Figure 2.2 Schéma fonctionnel du MEA.....                                                            | 19 |

| Figure 2.3 Représentation schématique d'un circuit d'électrode active (EA) .....                     | 20 |

| Figure 2.4 Schéma fonctionnel du circuit imprimé du MSD .....                                        | 21 |

| Figure 2.5 Architecture globale des modules VHDL se trouvant dans le FPGA du MSD .....               | 29 |

| Figure 2.6 Schéma fonctionnel du flux des données du générateur de porteuse .....                    | 30 |

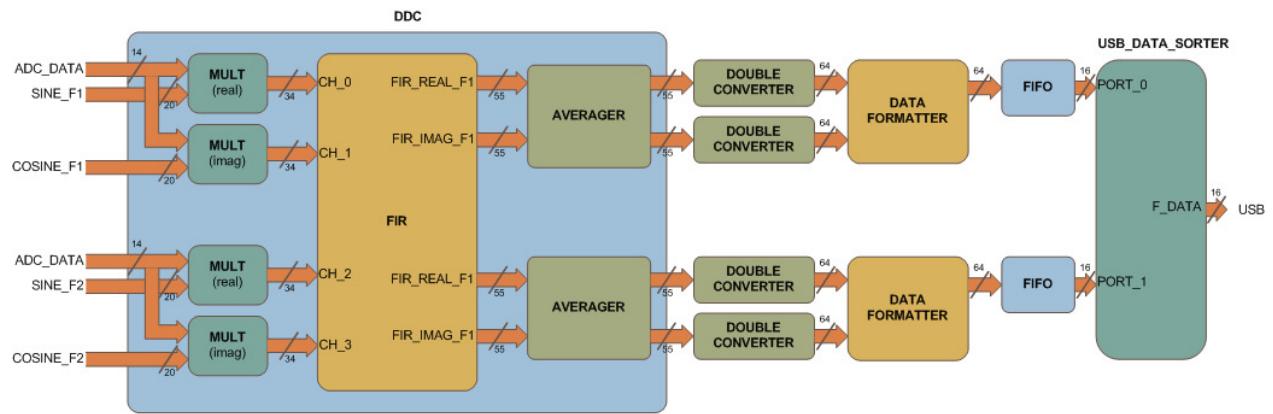

| Figure 2.7 Schéma fonctionnel représentant l'architecture interne du DDC .....                       | 33 |

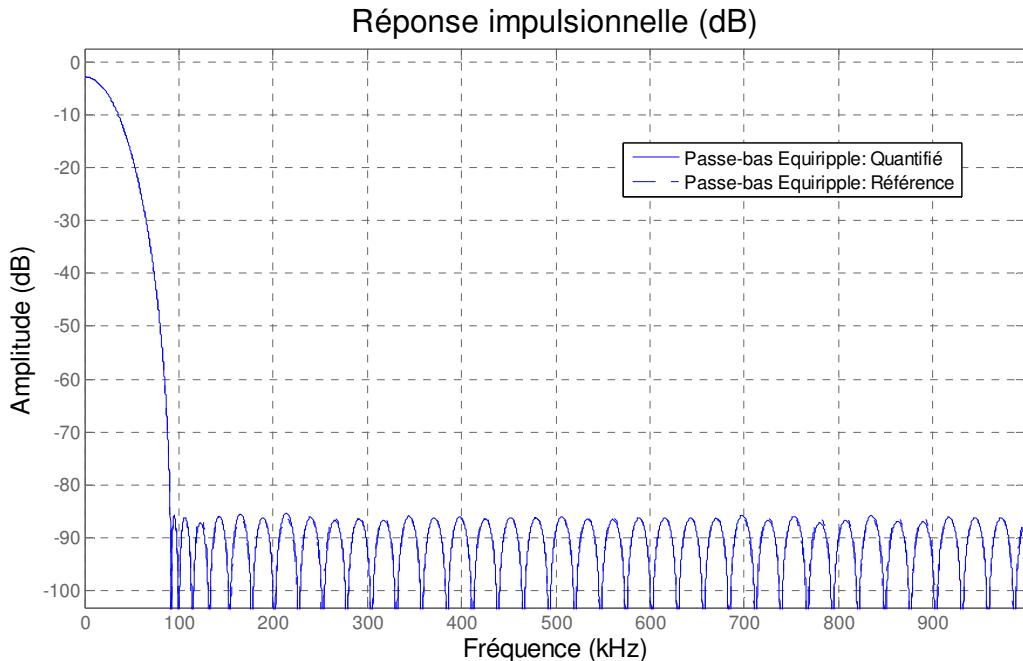

| Figure 2.8 Réponse en amplitude du filtre FIR .....                                                  | 35 |

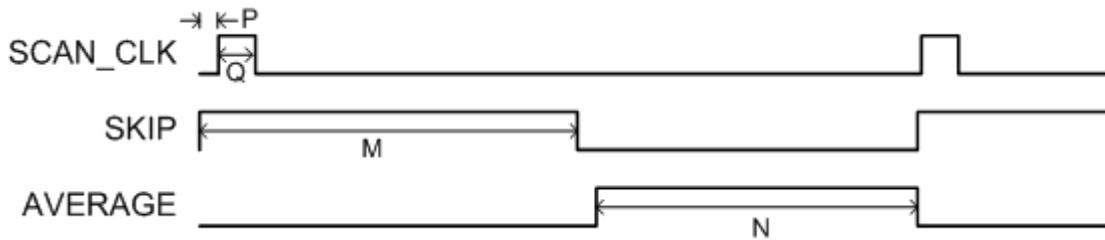

| Figure 2.9 Chronogramme des signaux de sortie du module SEQUENCER .....                              | 40 |

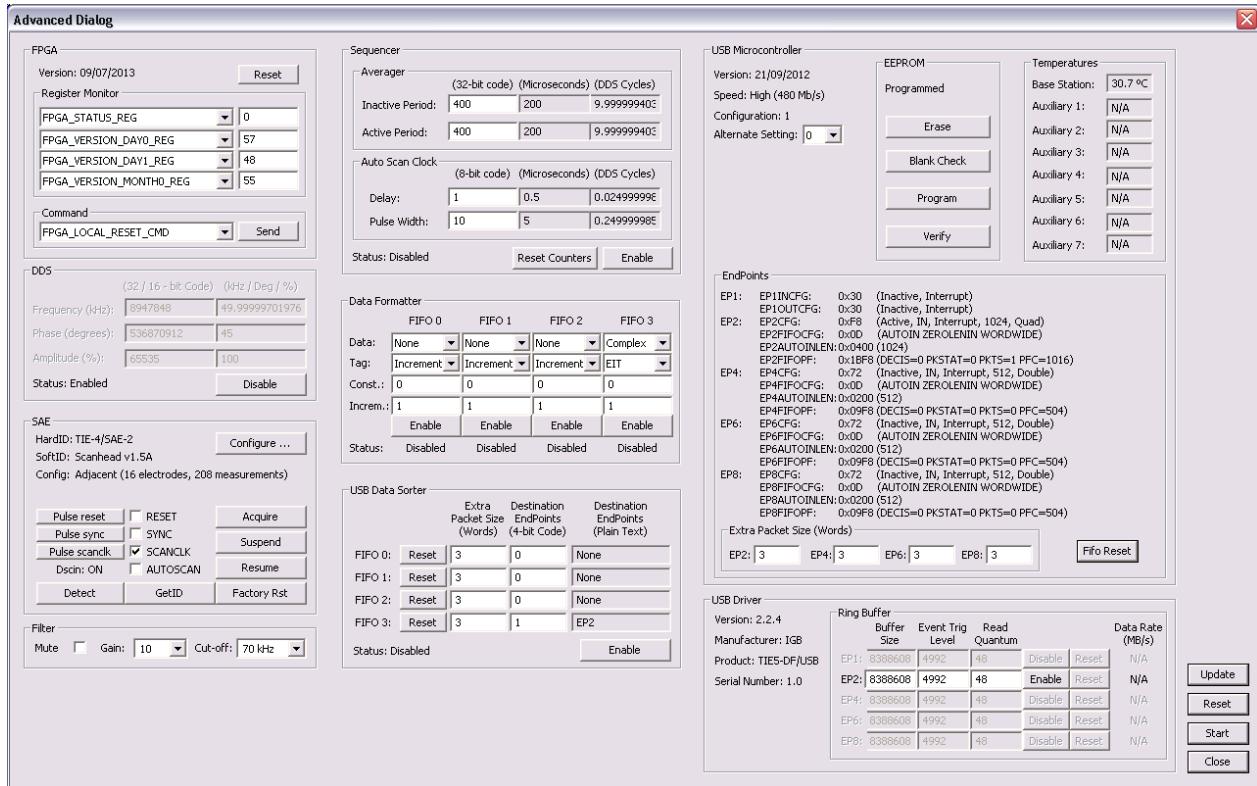

| Figure 2.10 Panneau de contrôle avancé du MSD .....                                                  | 43 |

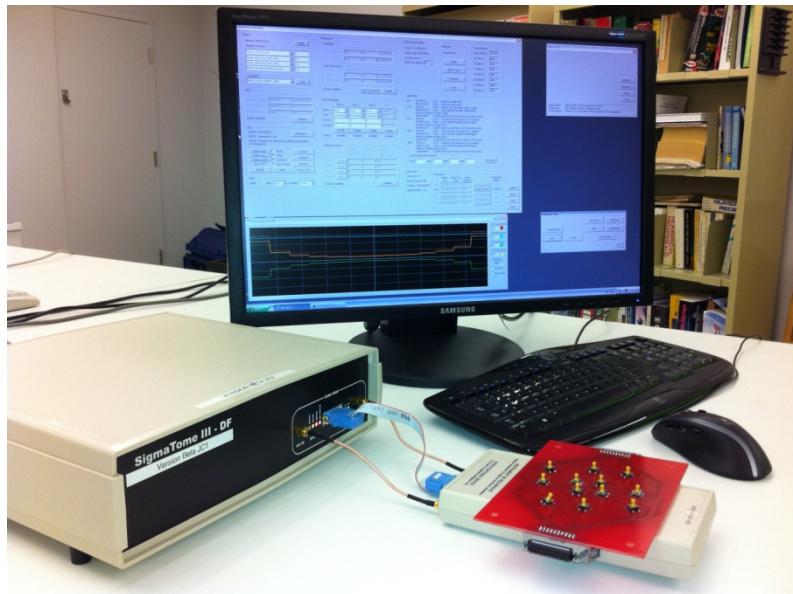

| Figure 3.1 Montage expérimental pour les interconnexions entre le MSD,<br>le MEA et le fantôme. .... | 45 |

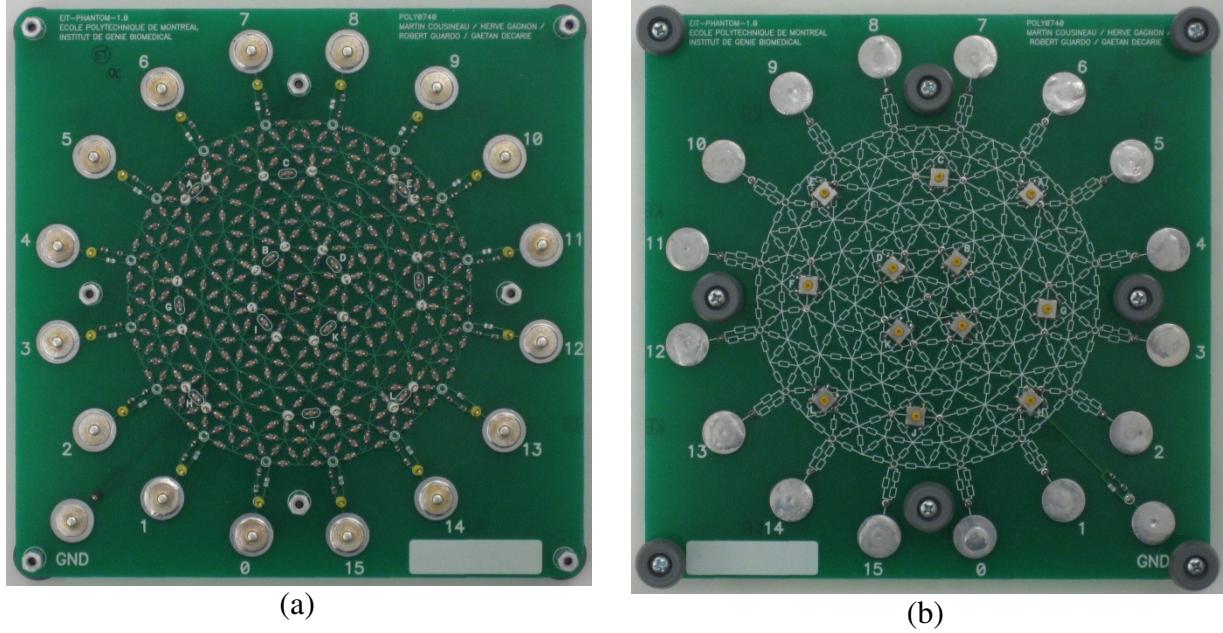

| Figure 3.2 Fantôme résistif.....                                                                     | 47 |

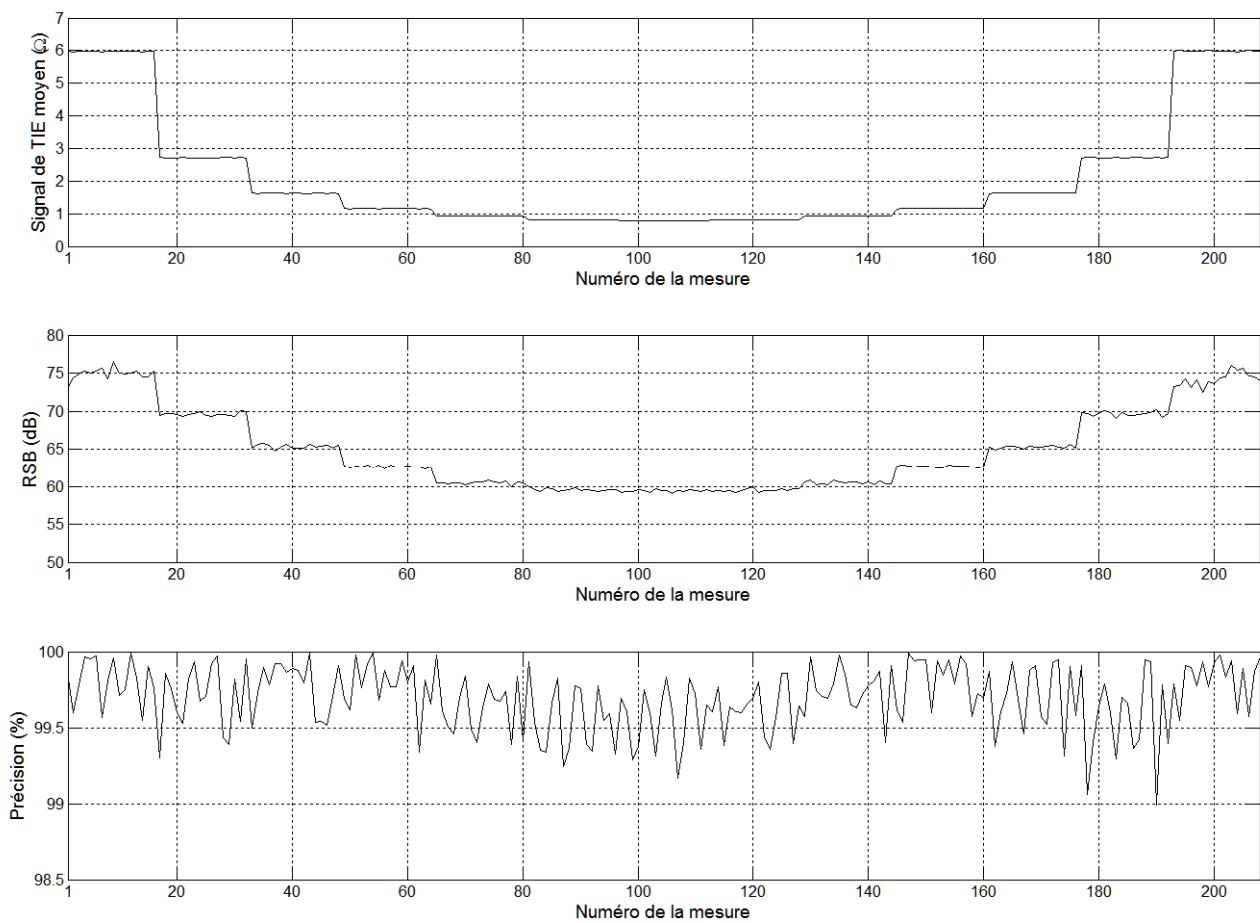

| Figure 3.3 Courbes représentant le signal moyen de TIE, le RSB et la précision des mesures.....      | 48 |

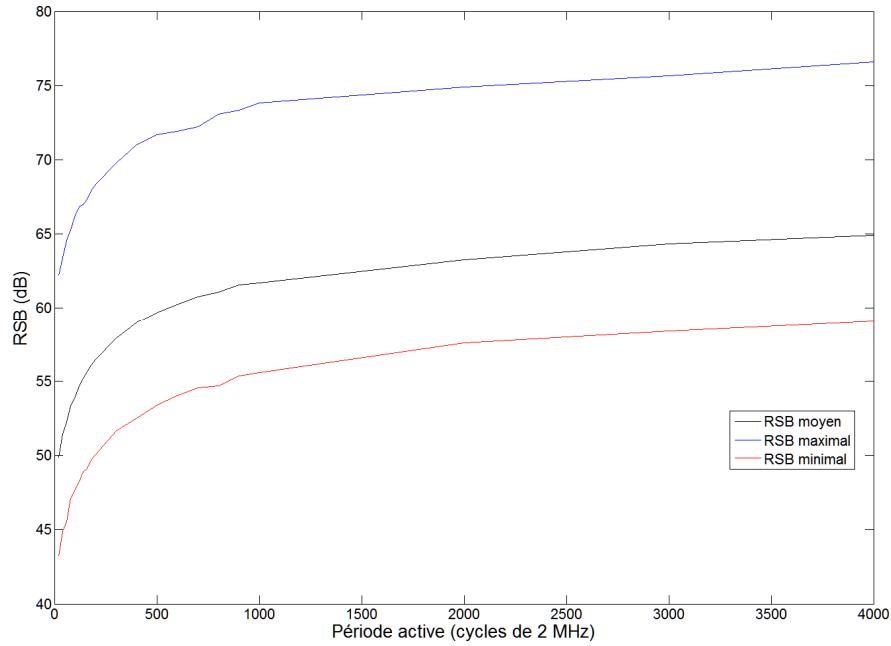

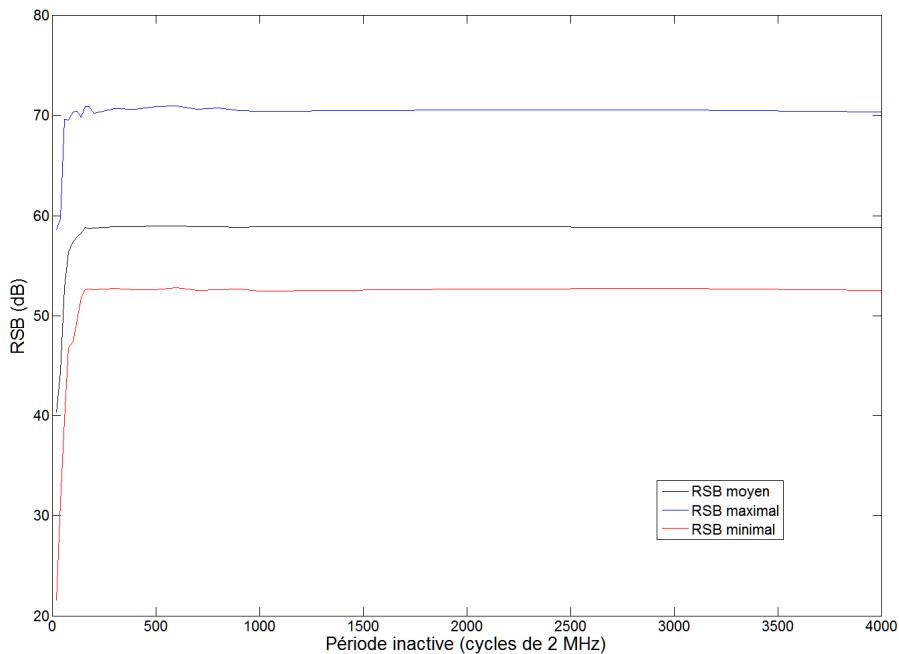

| Figure 3.4 RSB en fonction de la période active.....                                                 | 51 |

| Figure 3.5 RSB en fonction de la période inactive .....                                              | 51 |

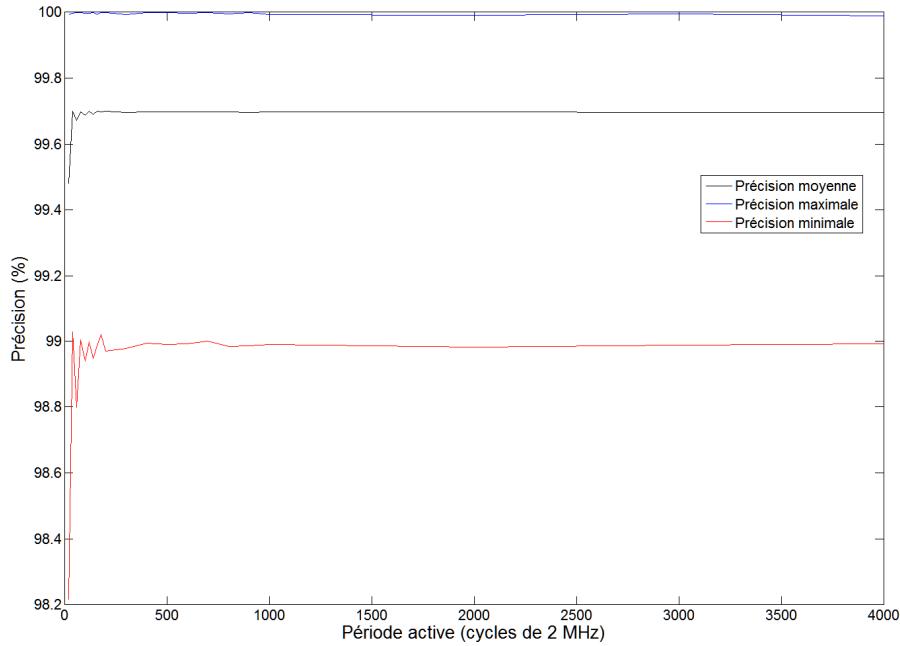

| Figure 3.6 Précision globale en fonction de la période active .....                                  | 53 |

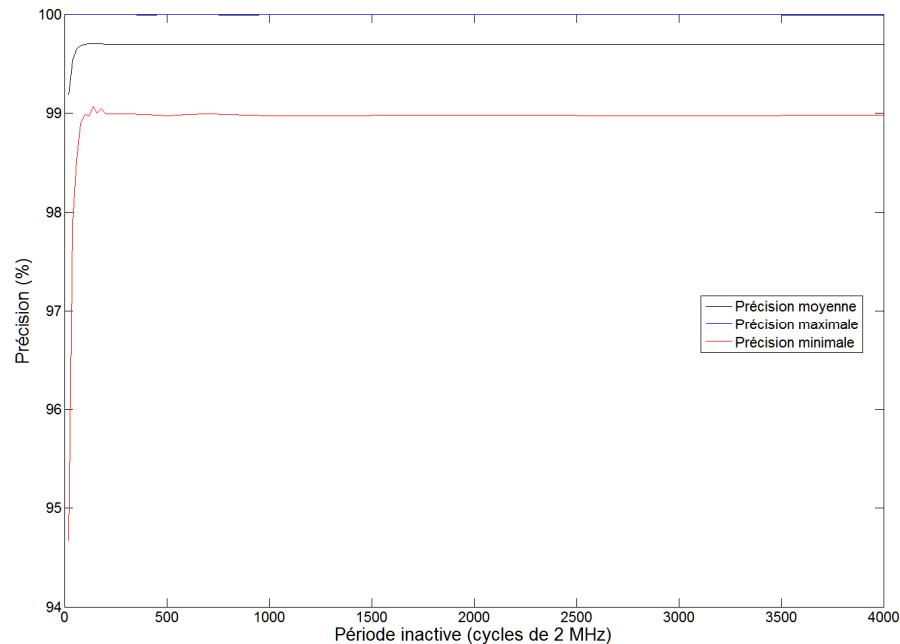

| Figure 3.7 Précision globale en fonction de la période inactive .....                                | 53 |

|                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------|----|

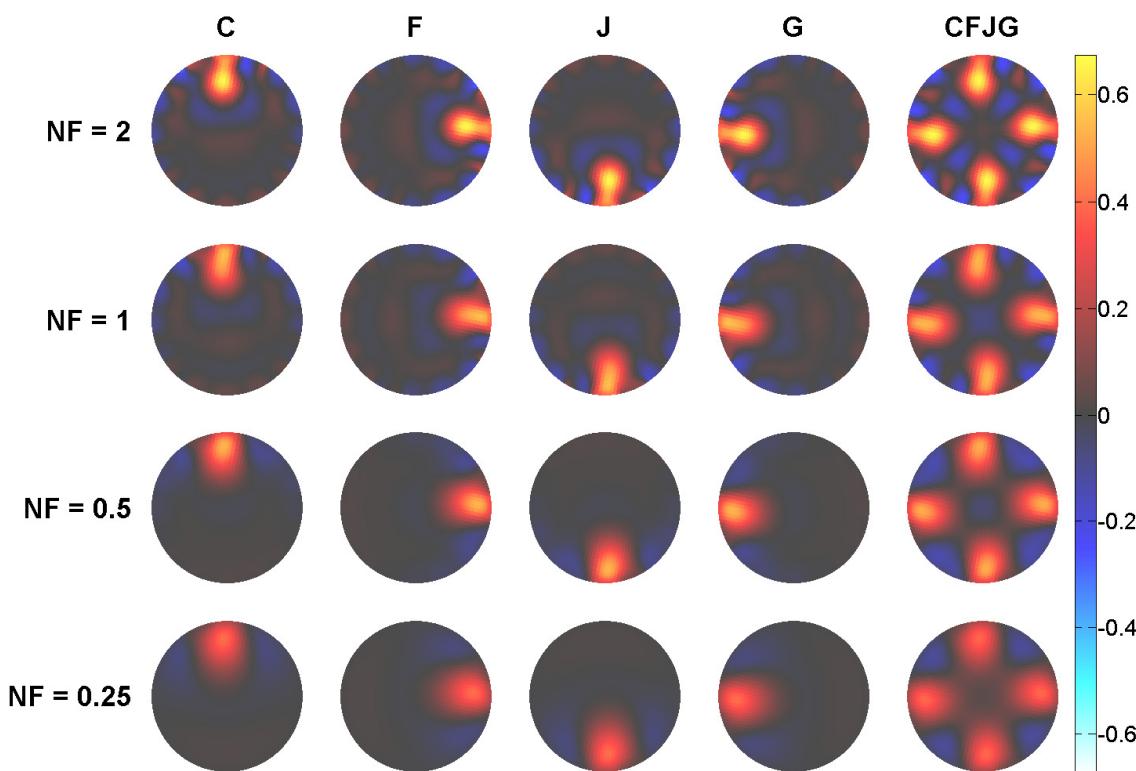

| Figure 3.8 Images différentielles de conductivité obtenues en appuyant sur les interrupteurs du fantôme .....     | 55 |

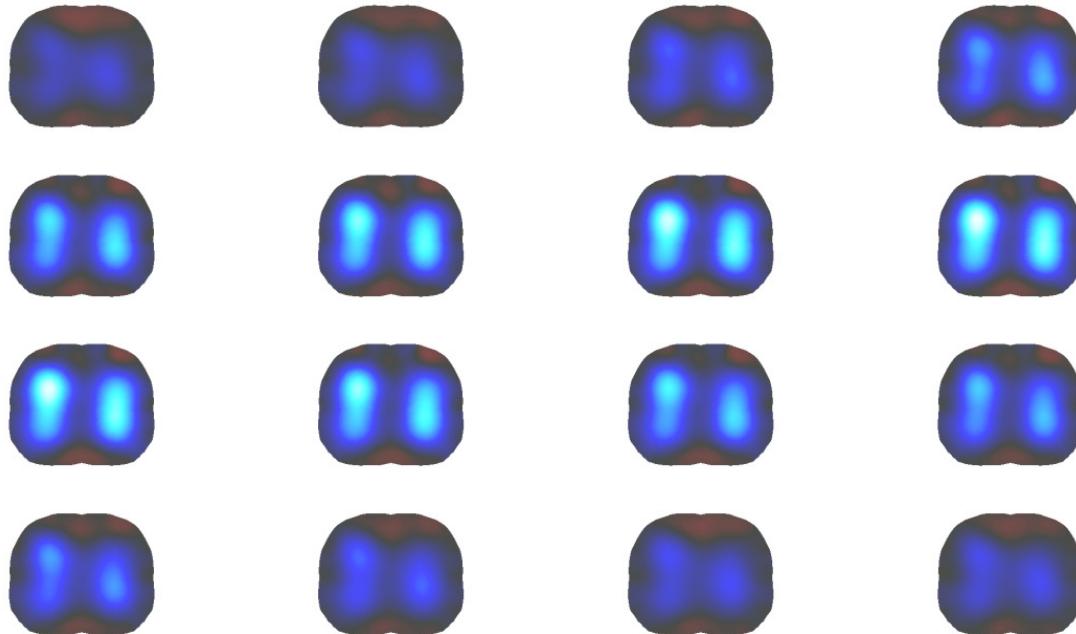

| Figure 3.9 Images différentielles de la ventilation pulmonaire sur un sujet normal .....                          | 56 |

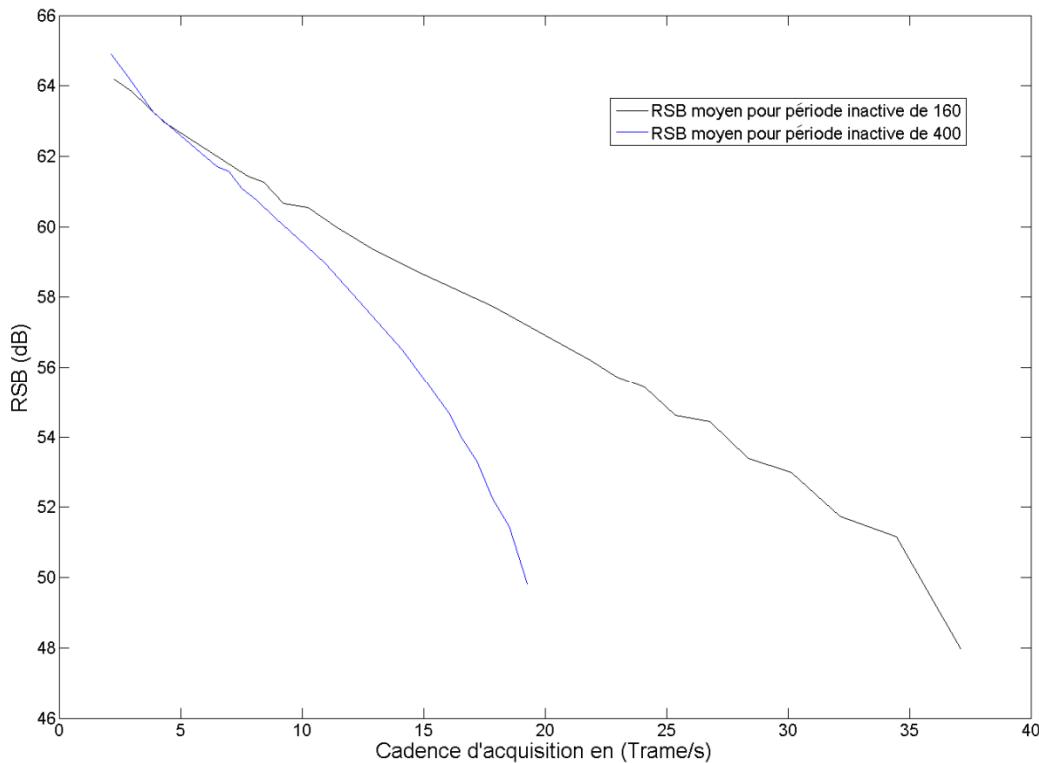

| Figure 3.10 RSB en fonction de la cadence d'acquisition pour deux valeurs différentes de périodes inactives ..... | 57 |

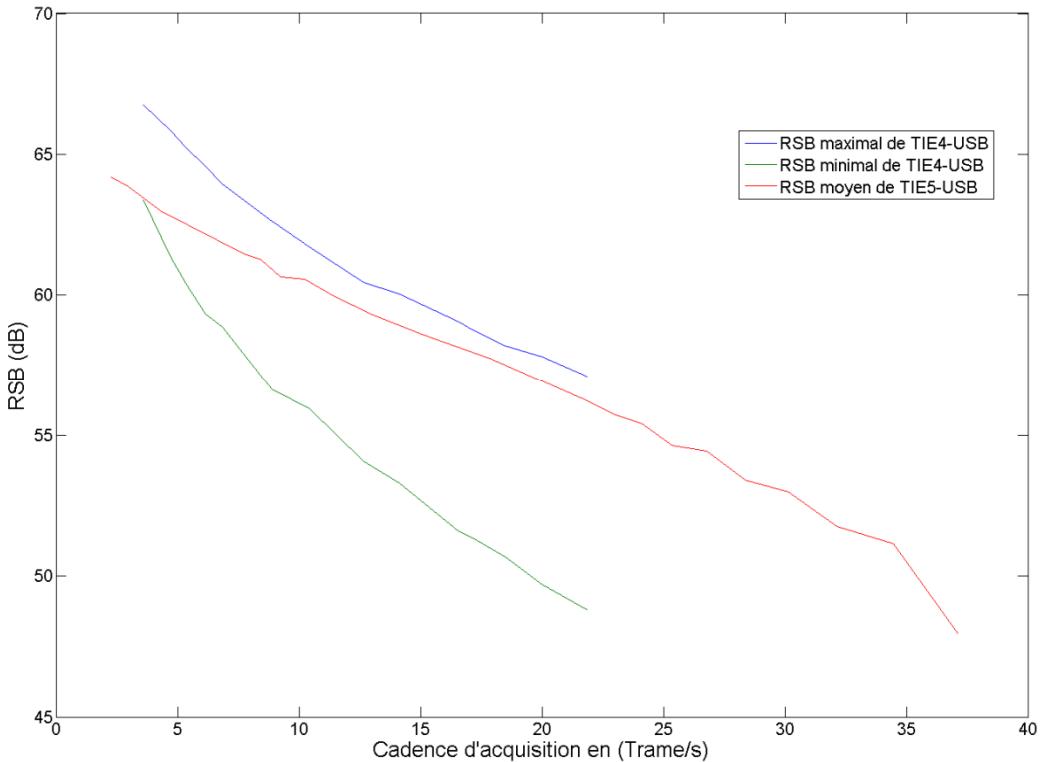

| Figure 3.11 RSB en fonction de la cadence d'acquisition pour TIE4-USB et TIE5-USB .....                           | 58 |

| Figure 4.1 Vue interne du module BlueSAT.....                                                                     | 66 |

| Figure 4.2 Schéma fonctionnel pour un système de TIE bifréquence. ....                                            | 67 |

| Figure 4.3 Photo d'un montage de TIE-3D réalisé avec le système TIE4-USB .....                                    | 69 |

| Figure 4.4 Photo de la carte électronique du MEA de nouvelle génération.....                                      | 69 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|                |                                                         |

|----------------|---------------------------------------------------------|

| $\epsilon$     | Permittivité relative                                   |

| $\theta(t)$    | Phase du signal en fonction du temps                    |

| $\mu\text{V}$  | Microvolt                                               |

| $\sigma$       | Conductivité                                            |

| $\sigma_{m_i}$ | Écart-type de la $i^{\text{e}}$ mesure d'une trame      |

| $\Omega$       | Ohm                                                     |

| $\omega$       | Fréquence angulaire                                     |

| A+             | Composante positive de la porteuse modulée en amplitude |

| A-             | Composante négative de la porteuse modulée en amplitude |

| ADC            | <i>Analog Digital Converter</i>                         |

| Ag             | Symbol chimique de l'argent                             |

| AgCl           | Formule chimique du chlorure d'argent                   |

| AM_IN          | <i>Amplitude Modulated Input</i>                        |

| CEI            | Commission électrotechnique internationale              |

| CLB            | <i>Configurable Logic Block</i>                         |

| CT             | <i>Computed Tomography</i>                              |

| DAC            | <i>Digital Analog Converter</i>                         |

| dB             | Décibel                                                 |

| DCM            | <i>Digital Clock Manager</i>                            |

| DDC            | <i>Digital Down Converter</i>                           |

| DDS            | <i>Direct Digital Synthesizer</i>                       |

| DSC_OUT        | <i>Daisy-Chained Output</i>                             |

| EA             | Électrode active                                        |

|          |                                                            |

|----------|------------------------------------------------------------|

| ECG      | Électrocardiogramme                                        |

| EEG      | Électroencéphalogramme                                     |

| EEPROM   | <i>Electrically-Erasable Programmable Read-Only Memory</i> |

| EIT      | <i>Electrical Impedance Tomography</i>                     |

| <i>f</i> | Fréquence                                                  |

| FIFO     | <i>First-In, First-Out</i>                                 |

| FIR      | <i>Finite Impulse Response</i>                             |

| FPGA     | <i>Field Programmable Gate Array</i>                       |

| HAL      | <i>Hardware Abstraction Layer</i>                          |

| Hz       | Hertz                                                      |

| IA       | <i>Instrumentation Amplifier</i>                           |

| IGB      | Institut de génie biomédical                               |

| IOB      | <i>Input Output Block</i>                                  |

| IP       | <i>Intellectual Property</i>                               |

| IRM      | Imagerie par résonance magnétique                          |

| ISE      | <i>Integrated Software Environment</i>                     |

| KB       | <i>Kilobytes</i>                                           |

| kHz      | Kilohertz                                                  |

| LED      | <i>Light Emitting Diode</i>                                |

| mA       | Milliampère                                                |

| MAP      | Maximum <i>a posteriori</i>                                |

| MEA      | Module d'électrodes actives                                |

| MEMTA    | <i>Modular Expandable Multi-Threaded Architecture</i>      |

| MHz      | Megahertz                                                  |

|          |                                             |

|----------|---------------------------------------------|

| MSD      | Module de synthèse et de démodulation       |

| NF       | <i>Noise Figure</i>                         |

| OC       | Opto-coupleur                               |

| PEPS     | Premier entré, premier sorti                |

| RAM      | <i>Random Access Memory</i>                 |

| REF_OUT  | <i>Reference Output</i>                     |

| RESET    | Signal de réinitialisation du MEA           |

| ROM      | <i>Read-Only Memory</i>                     |

| RSB      | Rapport signal sur bruit                    |

| RTL      | <i>Register Transfer Level</i>              |

| SAE      | <i>Smart Active Electrode</i>               |

| SCAN_CLK | Signal d'horloge du MEA                     |

| SFDR     | <i>Spurious Free Dynamic Range</i>          |

| SNR      | <i>Signal to Noise Ratio</i>                |

| SYNC     | Signal de synchronisation du MEA            |

| TI       | Transformateur d'isolation                  |

| TIE      | Tomographie d'impédance électrique          |

| TIE-3D   | TIE tridimensionnelle                       |

| TIE-CF   | TIE par courants de Foucault                |

| TIE-MF   | TIE multifréquence                          |

| TIE4-USB | Système de TIE de 4 <sup>e</sup> génération |

| TIE5-USB | Système de TIE de 5 <sup>e</sup> génération |

| UAC      | Unité arbitraire de conductivité            |

| USB      | <i>Universal Serial Bus</i>                 |

|       |                                            |

|-------|--------------------------------------------|

| V     | Volt                                       |

| VCCS  | <i>Voltage-Controlled Current Source</i>   |

| VHDL  | <i>VHSIC Hardware Description Language</i> |

| VHSIC | <i>Very High Speed Integrated Circuit</i>  |

## INTRODUCTION

Les techniques d'imagerie médicale ont connu un progrès phénoménal aux cours des dernières décennies. Les cliniciens ont maintenant accès à une multitude de modalités d'imagerie pour établir ou confirmer leurs diagnostics. Certaines technologies, telles la radiographie conventionnelle, la tomodensitométrie et la résonance magnétique permettent d'obtenir des images à haute résolution faisant ressortir des détails au niveau de l'anatomie. D'autres techniques permettent de faire de l'imagerie fonctionnelle, c'est-à-dire d'observer des processus physiologiques en action. On retrouve dans cette catégorie l'échographie, différentes techniques d'imagerie utilisées en médecine nucléaire, ainsi que l'imagerie par résonance magnétique fonctionnelle. Le choix d'une technique plutôt qu'une autre se fait en fonction des processus et/ou des anomalies physiologiques et anatomiques qu'on désire observer.

Comme la plupart des nouvelles technologies, les techniques d'imagerie médicale découlent d'abord de l'observation d'un phénomène physique lié à une propriété particulière des tissus biologiques. La découverte par Wilhelm Röntgen au début du 20<sup>e</sup> siècle de l'atténuation des rayons X par les tissus denses, comme les os, est un exemple de la première phase du développement d'une nouvelle technologie. Suite à l'observation d'un phénomène physique, des développements d'instruments et de techniques de mesure font en sorte que ce phénomène peut être étudié et éventuellement expliqué pour enfin être introduit dans la pratique médicale. Dans le cas des rayons X, on n'a qu'à citer le développement de capteurs photoniques numériques qui remplacent les pellicules photographiques et qui produisent directement des données servant à reconstruire les images par ordinateur. Ces technologies font en sorte qu'on a aujourd'hui des appareils de radiographie d'une grande sensibilité, permettant des diagnostics précis. On utilise notamment ces appareils pour l'étude du système musculo-squelettique et en médecine dentaire.

Par une logique similaire, des scientifiques ont tenté de développer de nouvelles technologies basées sur l'interaction entre les tissus biologiques et d'autres formes d'énergie. Par exemple, les origines de la tomographie d'impédance électrique peuvent être attribuées au développement d'une caméra d'impédance par Henderson et Webster en 1978. Il s'agissait d'un système permettant de mesurer des variations d'impédance thoracique au moyen d'une matrice d'électrodes recouvrant le devant du thorax et d'une électrode située au milieu du dos. Le système appliquait un courant alternatif de faible amplitude entre l'électrode dorsale et une des

électrodes de la matrice et mesurait au moyen des autres électrodes les différences de potentiel engendrées par ce courant. Avec ce système, les auteurs ont produit des cartes d'équipotentielles leur permettant d'observer des changements de conductivité reliés à la respiration (Henderson et Webster, 1978).

Les expériences de Henderson et Webster ont ouvert la voie au développement de la tomographie d'impédance électrique (TIE). La principale amélioration apportée par la TIE sur la caméra d'impédance était l'introduction d'un algorithme de reconstruction d'images dans le processus de traitement de données. Ceci a permis d'obtenir la distribution de conductivité à l'intérieur de la section du corps étudiée, plutôt qu'une simple cartographie des équipotentielles produites par le courant appliqué. La première image de TIE *in vivo*, représentant un avant-bras humain, a été obtenue par Barber et Brown en 1984. Ces auteurs sont reconnus d'ailleurs comme les pionniers de la TIE par l'ampleur et la qualité de leurs contributions à ce domaine.

## 1.1 Introduction à la tomographie d'impédance électrique

Comme son nom l'indique, la tomographie d'impédance électrique est une technique d'imagerie qui permet de reconstruire des images d'une section du corps. Puisque le corps humain est composé de tissus ayant une conductivité électrique caractéristique, il est possible d'imager des structures internes du corps en appliquant des courants électriques et en mesurant les différences de potentiel qui en résultent. La technique est non invasive puisque les électrodes sont placées à la surface du corps et l'amplitude ainsi que la fréquence des courants appliqués ne produisent aucun effet physiologique indésirable. Plus précisément, les systèmes actuels de TIE produisent des images de changements de conductivité (en fonction du temps, de la fréquence d'excitation ou des deux) et non pas de la conductivité absolue des tissus. Un système de TIE comporte essentiellement des circuits électroniques pour appliquer des courants électriques à un ensemble d'électrodes et pour enregistrer les potentiels qui résultent de la répartition du courant dans les tissus du corps. Le système est relié à un ordinateur qui coordonne les phases d'acquisition des données, d'enregistrement et de reconstruction des images.

Le tableau 1.1 indique les valeurs moyennes de conductivité électrique pour différents tissus aux fréquences d'excitation couramment utilisées en TIE (quelques dizaines de kilohertz). On note que ces valeurs couvrent approximativement trois ordres de grandeur. On pourrait donc

discerner les types de tissus si des mesures absolues de conductivité pouvaient être réalisées avec suffisamment de précision.

Tableau 1.1 Conductivité électrique de différents tissus.

| Tissu                  | Conductivité<br>(mS/m) |

|------------------------|------------------------|

| Liquide cérébro-spinal | 1539                   |

| Plasma                 | 1515                   |

| Muscle                 | 56 à 800               |

| Sang                   | 667                    |

| Poumon                 | 42 à 138               |

| Graisse                | 40                     |

| Os                     | 6                      |

Ces valeurs ont été tirées de Webster (1990). La conductivité moyenne de certains tissus varie pour diverses raisons. Dans le cas des poumons, la conductivité dépend du volume d'air qu'ils contiennent, l'air étant peu conducteur. Dans le cas des muscles, la conductivité dépend du sens des fibres musculaires, elle est plus faible dans le sens transversal et plus élevée dans le sens longitudinal.

### 1.1.1 Applications médicales de la TIE

Une des principales applications médicales de la TIE, en termes d'efforts de recherche et de développement qui y ont été investis, est le monitorage de la ventilation pulmonaire. Idéalement, ce monitorage permet d'enregistrer de façon continue le volume instantané d'air dans les poumons des patients qui sont sous ventilation mécanique aux soins intensifs. Or, il n'y a présentement aucun appareil qui permet d'observer en temps réel comment les poumons d'un patient réagissent à ce traitement. Les cliniciens ont donc recours à l'observation des signes vitaux et à des mesures indirectes, comme le taux de saturation du sang en oxygène. La TIE offre une réponse partielle aux exigences de ce type de monitorage, en permettant de visualiser en temps réel les variations de conductivité thoracique et d'en déduire un indice des variations du volume d'air dans chaque poumon.

Un article de synthèse de Frerichs (2000) fait un compte rendu exhaustif des connaissances en matière d'applications de la TIE au monitorage cardiorespiratoire. Après avoir examiné les résultats d'essais cliniques à petite échelle réalisés dans plusieurs pays, l'auteur

conclut que la TIE a un avenir prometteur pour les applications pulmonaires à condition de résoudre certains problèmes d'ordre pratique. Elle insiste entre autre sur l'importance de développer des systèmes d'acquisition de données offrant une plus grande stabilité de performances afin de permettre des comparaisons significatives des résultats obtenus par divers groupes d'utilisateurs. Certaines recommandations contenues dans cet article ont servi à définir les objectifs du présent projet.

Une deuxième application médicale importante de la TIE concerne l'étude du système circulatoire. Comme pour les poumons dont la conductivité change selon qu'ils soient remplis ou vides d'air, la conductivité du cœur change tout au long du cycle cardiaque selon la quantité de sang qu'il contient. Il est donc possible d'évaluer le volume d'éjection systolique par TIE. Ceci peut permettre de diagnostiquer plusieurs anomalies cardiovasculaires : l'insuffisance cardiaque congestive, l'hypertension ou même des maladies des artères coronaires (Zlochiver *et al*, 2006). Des chercheurs du *Rensselaer Polytechnic Institute* ont d'ailleurs réalisé par TIE des images tridimensionnelles de la distribution de conductivité du thorax dans le but d'étudier l'activité cardiaque (Newell *et al*, 2002).

Une troisième application intéressante de la TIE concerne l'évaluation de la vidange gastrique. Dans ce cas-ci, c'est le déplacement d'aliments dans le système digestif qui produit un changement de la conductivité électrique de l'estomac. Les aliments utilisés pour accroître le contraste de conductivité consistent généralement en des morceaux de viande ou bien des purées (par exemple, de pommes de terre) contenant un léger excédent de sel. Lors d'une étude récente, la TIE s'est avérée aussi performante que la scintigraphie dans l'évaluation de la vidange gastrique chez des patients soumis à une nutrition liquide par voie nasogastrique (Soulsby *et al*, 2006). L'avantage de la TIE dans ce cas-ci est d'éviter l'ingestion de radio-isotopes tout en utilisant une instrumentation beaucoup plus simple et moins coûteuse.

Un nouveau domaine d'application de la TIE, auquel se consacrent plusieurs groupes de recherche depuis une dizaine d'années, est le monitorage de l'activité cérébrale. On conçoit que certaines pathologies du cerveau, telles les ischémies ou, à l'inverse, les hémorragies peuvent être détectées par TIE en raison des variations locales de flux sanguin qu'elles engendrent. Ces recherches ont relativement peu progressé, principalement en raison de la difficulté d'obtenir des mesures précises lorsqu'on tente de mesurer, par des électrodes placées sur le cuir chevelu, l'effet

de variations de conductivité se produisant à l'intérieur de la boîte crânienne. Les systèmes de TIE actuels n'ont pas une sensibilité et une stabilité suffisamment grandes pour envisager de telles mesures.

Les applications précédentes ont un point en commun : elles se basent sur un changement temporel de la conductivité électrique du milieu pour réaliser des images différentielles. Le principe de cette technique, connue dans la littérature anglaise de TIE sous le nom de *time-difference imaging* est que l'ensemble de données enregistrées à l'instant zéro définit une distribution de conductivité de référence. Chaque ensemble de mesures enregistré par la suite permet de reconstruire une image de la variation de conductivité dans la section du corps étudiée par rapport à la distribution de conductivité de référence. Il est important de souligner que la majorité des études cliniques en TIE ont jusqu'à maintenant été réalisées en utilisant cette technique d'imagerie différentielle.

La TIE permet aussi de réaliser des images illustrant les variations de conductivité en fonction de la fréquence. Ainsi, au lieu d'appliquer un courant sinusoïdal à une fréquence unique, on appliquera des courants à différentes fréquences, soit de façon séquentielle ou bien simultanée par la superposition de sinusoïdes à plusieurs fréquences. Dans le cas le plus simple, soit l'enregistrement séquentiel d'ensembles de données obtenues à deux fréquences, on parlera d'imagerie différentielle bifréquence (en anglais, *frequency-difference imaging*). Dans le second cas, on parlera d'imagerie TIE multifréquence (TIE-MF). Une application médicale de la TIE-MF est le dépistage de tumeurs puisque les tissus cancéreux ne conduisent pas l'électricité de la même façon que les tissus sains. En effet, les tissus cancéreux ont souvent une structure plutôt désorganisée, parfois aussi plus vascularisée. Le courant électrique se distribue donc alors différemment selon la fréquence dans les tissus sains et cancéreux.

### 1.1.2 Applications non médicales de la TIE

Afin de compléter le portrait des applications de la TIE, il est bon de mentionner que cette technique d'imagerie dépasse le domaine médical. Dans les faits, la TIE peut être employée pour imager n'importe quel phénomène produisant une variation de conductivité électrique dans un milieu. On l'utilise entre autre pour le monitorage de procédés industriels (par exemple, dans des bioréacteurs). À l'instar du dépistage de tissus cancéreux, la TIE-MF peut être employée pour

l'inspection non destructive des matériaux. On retrouve également de nombreuses applications en géophysique, en prospection minière et même dans la détection de mines antipersonnel.

### 1.1.3 Principe de mesure

Le principe de mesure de la TIE peut être facilement compris grâce à l'analogie suivante. Supposons un prisme rectangulaire fait d'un matériau de conductivité  $\sigma$  inconnue. La longueur du prisme  $L$  est connue, de même que son aire transverse  $A$ . On désire calculer  $\sigma$  à partir de mesures de courants et/ou de potentiels. Dans le cas le plus simple, on placerait des électrodes à chaque extrémité du prisme et on appliquerait un courant  $I$  connu. Par la loi d'Ohm, la différence de potentiel aux électrodes serait :

$$V = RI \quad (1.1)$$

où la résistance électrique  $R$  du prisme dans cette configuration est donnée par :

$$R = \frac{L}{\sigma A} \quad (1.2)$$

On obtient alors la conductivité électrique  $\sigma$  à partir du potentiel mesuré  $V$  par :

$$\sigma = \frac{LI}{AV} \quad (1.3)$$

Si on complexifie quelque peu le problème en considérant un prisme composé de deux prismes juxtaposés de conductivités différentes, on peut déterminer ces conductivités par une expérience similaire à celle du prisme simple.

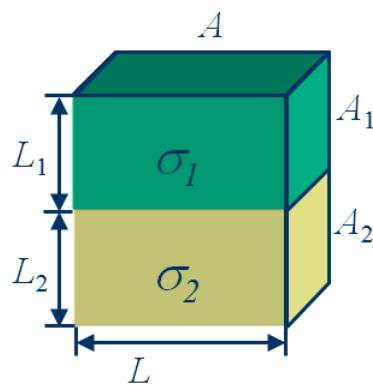

Figure 1.1 Prisme rectangulaire composé de deux matériaux de conductivités différentes.

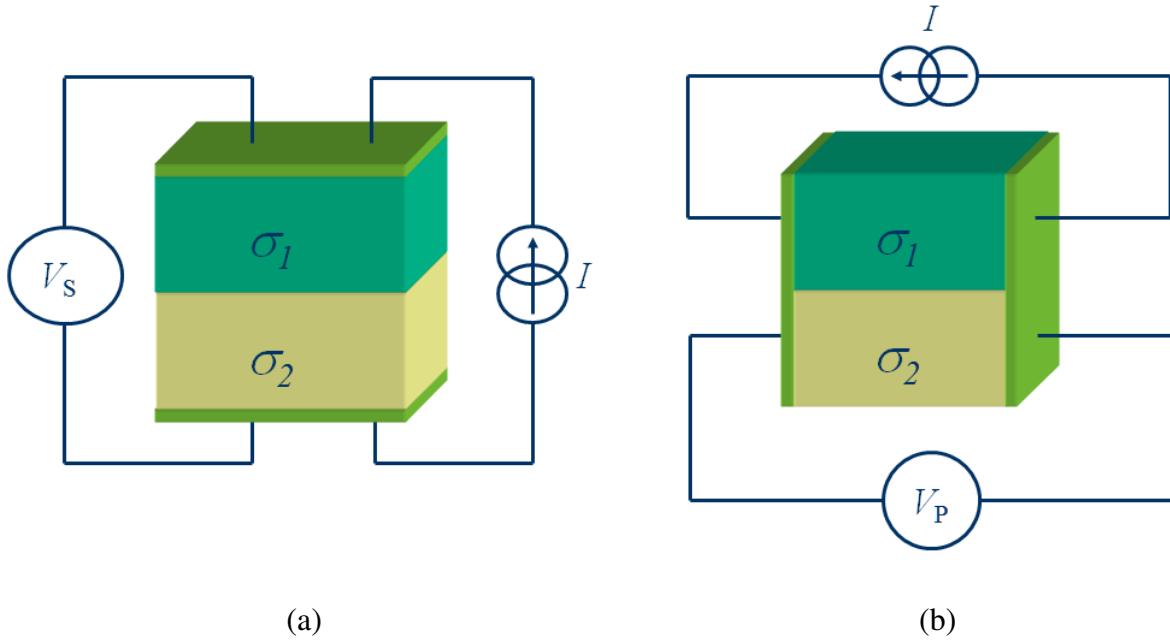

Il s'agit d'effectuer deux mesures de différences de potentiel : la première où le courant est appliqué de façon à traverser les deux prismes en série (figure 1.2 (a)), la seconde en faisant passer le courant dans les deux prismes en parallèle (figure 1.2 (b)).

Figure 1.2 Schémas représentant les électrodes apposées au prisme afin de déterminer les conductivités des deux sections : a) Mesure en série. b) Mesure en parallèle.

De cette façon, on se retrouvera avec un système à deux équations et deux inconnues :

$$V_S = (R_{1S} + R_{2S})I \text{ où } R_{1S} = \frac{L_1}{\sigma_1 A} \text{ et } R_{2S} = \frac{L_2}{\sigma_2 A} \quad (1.4)$$

$$V_P = \left( \frac{R_{1P}R_{2P}}{R_{1P} + R_{2P}} \right) I \text{ où } R_{1P} = \frac{L}{\sigma_1 A_1} \text{ et } R_{2P} = \frac{L}{\sigma_2 A_2} \quad (1.5)$$

duquel on peut déterminer les conductivités des matériaux. Bien sûr, il s'agit ici d'une situation idéale qui ne peut s'appliquer directement à la TIE. Dans les cas d'intérêt pratique en médecine, on se retrouve à effectuer des mesures sur un milieu continu où la conductivité est fonction de l'espace et du temps. Une forme plus générale de la loi d'Ohm, découlant des équations de Maxwell, doit alors être utilisée. Un plus grand nombre d'électrodes seront aussi nécessaires pour obtenir l'ensemble des mesures qui serviront à la reconstruction d'une image de la distribution de conductivité.

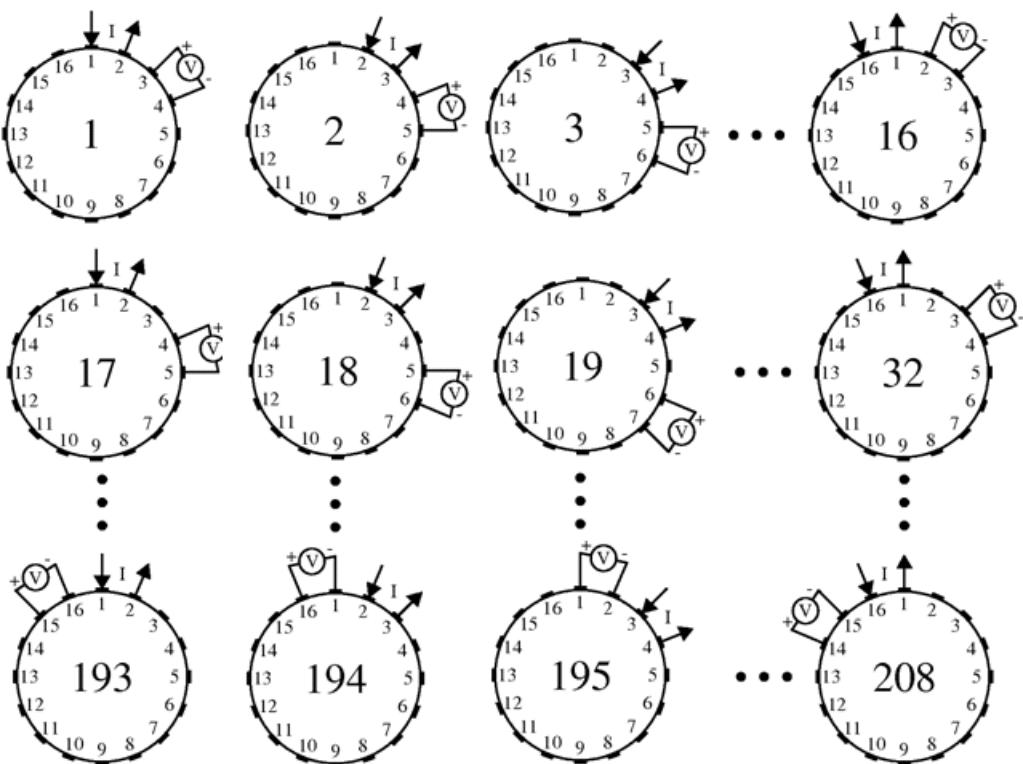

Par exemple, pour réaliser des images de TIE pour le monitorage de la ventilation pulmonaire, on dispose les électrodes autour du thorax en suivant un plan passant sous les aisselles. Pour cette application, la plupart des systèmes de TIE actuels utilisent 16 ou 32 électrodes. Nous illustrons ci-dessous le cas d'un système à seize électrodes. Lors de chaque mesure quatre électrodes doivent assurer les rôles suivants: 1) source de courant, 2) puits de courant, 3) suiveur de tension et 4) inverseur de tension. Les autres électrodes non requises se mettent alors en mode haute impédance. La figure 1.3 illustre une séquence typique d'acquisition des mesures.

Figure 1.3 Séquence d'acquisition de données pour un système à seize électrodes. Les électrodes servant à mesurer une différence de potentiel sont représentées reliées à un voltmètre. Celles agissant comme source et puits de courant sont indiquées par des flèches représentant le sens du courant.

L'équation suivante permet de calculer le nombre de mesures linéairement indépendantes ( $M$ ) qu'on peut réaliser avec  $N$  électrodes :

$$M = \frac{N(N - 3)}{2} \quad (1.6)$$

Le facteur 2 au dénominateur provient du fait que certaines mesures sont, dans le cas idéal, identiques à d'autres en raison du principe de réciprocité tension-courant (Geselowitz, 1971). Pour un système à seize électrodes, on obtient donc 104 mesures indépendantes qui constituent une trame. La reconstruction d'images se fait à partir d'une ou de plusieurs trames de mesures par des algorithmes mathématiques qui solutionnent un problème inverse qui consiste à déterminer la distribution de conductivité du milieu connaissant sa géométrie, la valeur du courant appliqué et le potentiel enregistré à chaque mesure.

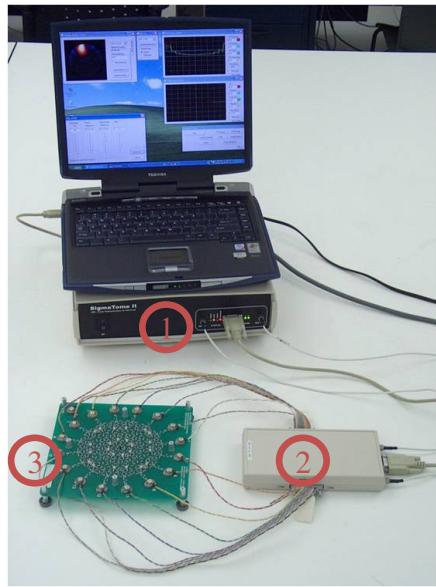

Figure 1.4 Système de TIE développé dans notre laboratoire.

Afin de donner au lecteur une idée de l'aspect physique d'un système de TIE, la figure 1.4 montre un des systèmes développés par notre laboratoire. Ce système comporte deux modules principaux : le module de synthèse et de démodulation (MSD) (1) et le module d'électrodes actives (MEA) (2). L'objet en avant-plan (3) est un fantôme résistif utilisé lors de tests du système.

Le MSD est le module principal de contrôle du système. Il sert à générer une porteuse sinusoïdale qui définit l'amplitude et la fréquence des courants appliqués par le MEA. En plus de coordonner la séquence des mesures, le MSD effectue la démodulation des signaux enregistrés par des amplificateurs différentiels dans le MEA. Enfin, le MSD envoie les données prétraitées (les résultats de la démodulation en quadrature de phase) à l'ordinateur. Le fonctionnement détaillé du MSD sera expliqué à la section 2.3.

Le MEA contient les circuits de conditionnement des signaux nécessaires aux électrodes. Il est composé d'une carte électronique sur laquelle on retrouve pour chacun des seize canaux d'électrodes trois circuits différents : un circuit de contrôle, un circuit de stimulation (application du courant) et un circuit de mesure de potentiel. Pour de plus amples détails sur ce module, le lecteur est invité à consulter le mémoire de maîtrise de Sigmen (2012) qui décrit le MEA le plus récent conçu dans notre laboratoire.

#### 1.1.4 TIE bifréquence

Afin de compléter cette introduction à la TIE, nous nous attardons maintenant à la TIE bifréquence (TIE-BF). La version du MEA, réalisée par Yannick Sigmen (2012), avait pour but de permettre d'effectuer des mesures d'impédance sur une grande plage de fréquences (idéalement, 1 kHz à 1 MHz), ce qui nous ouvrait la voie à l'imagerie multiréquence (TIE-MF). La plage de fréquences effectivement atteinte avec ce MEA est légèrement inférieure à notre objectif initial mais amplement suffisante pour réaliser l'imagerie bifréquence.

On retrouve dans la littérature les valeurs d'admittance de plusieurs tissus biologiques pour des fréquences allant de 10 Hz à 20 GHz (Martinsen et Grimnes, 2011). L'admittivité ( $\gamma$ ) est une valeur complexe, fonction de la fréquence angulaire ( $\omega$ ), définie par l'équation suivante :

$$\gamma(\omega) = \sigma(\omega) + j\epsilon_0\epsilon_r(\omega) \quad (1.7)$$

où  $\sigma$  et  $\epsilon_r$  sont respectivement la conductivité électrique et la permittivité relative. Le coefficient  $j$  représente  $\sqrt{-1}$  et  $\epsilon_0$  est la permittivité du vide. Effectivement, il se produit pour chaque tissu une distribution spécifique du courant d'excitation qui dépend de sa structure cellulaire et du milieu interstitiel. Lorsqu'on représente une cellule par un modèle électrique équivalent, la membrane cellulaire prend la forme d'une résistance très élevée en parallèle avec

un condensateur (Malmivuo et Plonsey, 1995). Intuitivement, on comprend alors qu'à plus haute fréquence le courant passe surtout à travers les cellules (c'est-à-dire, par un courant de déplacement à travers la membrane cellulaire) plutôt que par le milieu interstitiel. Ce dernier étant composé surtout d'ions mobiles, c'est le premier terme de l'équation 1.7 qui affecte davantage l'admittance du tissu. En résumé, le comportement des tissus selon la fréquence dépend de la configuration des cellules, de la concentration des ions, de leur mobilité et de la viscosité du milieu (Rigaud *et al*, 1995). L'avantage de la TIE-BF sur la TIE conventionnelle est donc de pouvoir réaliser des images de processus physiologiques qui produisent des changements de conductivité sur de très longues périodes de temps (par exemple, l'évolution d'une tumeur), mais qui mettent en présence des tissus avec des signatures fréquentielles distinctes. Ainsi, la TIE-BF permettrait de distinguer certains tissus selon leur structure et leur état physiologique, ce qui s'avère un élément essentiel pour le diagnostic de cancers de la peau ou du sein.

## 1.2 Contexte du projet

Cinq générations de systèmes de TIE ont été développées au laboratoire d'imagerie et d'instrumentation biomédicales de l'École Polytechnique de Montréal depuis une vingtaine d'années. Les trois premières générations ont permis de perfectionner l'instrumentation afin d'obtenir des systèmes pleinement fonctionnels. Le lecteur intéressé par l'historique de ces développements est invité à consulter le mémoire de maîtrise de Moumbe (2011).

Chaque nouvelle génération présentait une amélioration sur la version précédente, tant au niveau des performances d'enregistrement qu'au niveau de la conception matérielle de l'appareil. Ainsi, le système se renouvelait constamment dans l'optique d'être utilisé au chevet des patients. En plus des aspects ergonomiques spécifiques à ce rôle, il fallait développer la capacité de réaliser des enregistrements de longue durée et de grande fiabilité. Ces exigences sont dues entre autre au fait que le monitorage de la ventilation pulmonaire se fait dans une unité de soins intensifs sur des patients fortement instrumentés (ventilateur, cathéters, moniteurs de signes vitaux, etc.). De plus, les interventions fréquentes du personnel soignant rendent les conditions d'enregistrement de données de TIE difficiles.

Nous considérons que le système de la quatrième génération (TIE4-USB) est le premier système suffisamment robuste et polyvalent pour les applications médicales. Ceci est dû principalement à l'instauration d'un protocole de communication pour l'interface entre le MSD et

le MEA et à l'utilisation dans le MSD de puces électroniques réalisant la synthèse numérique directe de la porteuse d'excitation et la démodulation numérique des signaux enregistrés par les électrodes de mesure. Ce système a permis d'explorer d'autres formes de TIE sans nécessiter des modifications majeures au matériel. Par exemple, un système de TIE par courants de Foucault (TIE-CF) a pu être réalisé en remplaçant le MEA par un autre module, tout en conservant le même MSD (Tanguay, 2004). La TIE-CF ressemble à la TIE conventionnelle, mais le courant d'excitation est induit par un champ magnétique généré par des bobines (donc, sans contact) au lieu d'être appliqué par des électrodes.

Bien que la 4<sup>e</sup> génération constitue une approche plus évolutive que les précédentes, la 5<sup>e</sup> génération, dont fait partie le présent projet, présente un avantage majeur grâce au développement d'une nouvelle carte électronique pour le MSD. Un prototype préliminaire de cette carte dont le développement a débuté en 2002 est décrit dans le mémoire de Pierre-Luc Dazé (2004). On peut en voir une photo à la figure 1.5. Elle a pour avantage d'utiliser un réseau de portes logiques programmable (en anglais, *Field Programmable Gate Array*, FPGA) comme élément central du MSD. Bien que la 4<sup>e</sup> génération emploie aussi un FPGA dans le MSD, la différence majeure est que le FPGA de cette version servait uniquement à interfaçer les divers composants du MSD. Dans la 5<sup>e</sup> génération, le FPGA a un rôle central en ce qui a trait au traitement numérique des signaux. L'architecture du FPGA comme tel sera décrite en détail au chapitre 2.

Pour la 5<sup>e</sup> génération de système de TIE, un nouveau MEA a été conçu par Sigmen (2012). Ce MEA comporte des circuits électroniques de stimulation et d'enregistrement à large bande pouvant être employés pour des applications de TIE-BF.

Suite au prototype réalisé par Dazé (2004), un autre projet a eu pour mandat de concevoir la logique interne d'un FPGA afin de réaliser le MSD du système TIE5-USB. Ce projet devait également permettre l'enregistrement d'électroencéphalogrammes (EEG) par les mêmes électrodes utilisées pour la TIE (Moumbe, 2011). Malgré que ce MSD ait permis des enregistrements de TIE conjointement à l'EEG, une révision du FPGA s'est avérée nécessaire pour résoudre des problèmes de stabilité. Effectivement, cette version du système TIE5-USB n'a pu remplacer le système TIE4-USB pour des raisons de fiabilité des mesures lors des enregistrements. De plus, les techniques de programmation employées pour concevoir la logique interne du FPGA n'offraient pas une grande flexibilité au MSD, rendant ardu tout développement futur.

### **1.3 Définition du projet**

En lien avec le contexte présenté dans la section précédente, il a donc été décidé de faire une refonte complète de l'architecture logicielle du MSD. Cela consiste à concevoir l'ensemble des circuits internes du FPGA nécessaires au bon fonctionnement du système TIE5-USB. Par bon fonctionnement, on entend ici que le MSD remplisse les rôles suivants :

1. Générer une porteuse contrôlant le courant à appliquer aux électrodes par l'intermédiaire des circuits du MEA.

2. Contrôler la séquence de mesures.

3. Démoduler les signaux (différences de potentiel captées par les électrodes) provenant du MEA pour obtenir les composantes réelle et imaginaire de la porteuse de mesure (ou des deux porteuses de mesures dans le cas de la TIE-BF). Cette démodulation sera expliquée en détail au chapitre 2.

4. Transmettre les données à l'ordinateur pour enregistrement et traitement d'images.

5. Communiquer avec l'interface graphique réalisée sur l'ordinateur hôte afin de permettre à l'usager de changer divers paramètres lors des enregistrements.

En plus de ce mandat de base, de nouvelles spécifications ont été établies pour amener le système à un niveau opérationnel plus élevé. D'abord, une des priorités est que le système soit conçu selon une architecture modulaire et facilement reconfigurable. Ceci fait en sorte que le même MSD pourra servir pour développer d'autres applications de la TIE.

Un autre objectif est que le MSD facilite la réalisation de la TIE-MF. Pour ce faire, il faut que le MSD puisse gérer plus d'une porteuse, ce qui permettra d'expérimenter avec des variantes de la TIE, comme la TIE multifréquence, tridimensionnelle et synchronisée à un événement physiologique. Au niveau de l'acquisition synchrone à un événement physiologique, une attention particulière sera portée à la coordination du signal de déclenchement (en anglais *trigger*) et de la séquence de mesures afin que l'enregistrement des données demeure cohérent.

## 1.4 Structure du mémoire

Ce mémoire suit le cheminement suivant. D'abord, on parlera au chapitre 2 du MSD et de sa conception, mais on expliquera surtout l'architecture du FPGA. On décrira ensuite les stratégies de conception qui ont été employées pour répondre au mandat. Le chapitre 3 portera sur les résultats des différents tests qui ont été réalisés pour démontrer que le MSD répond bien aux objectifs du projet. Le chapitre 4 présentera une discussion sur l'état actuel du projet et fera des suggestions pour des développements futurs.

## CHAPITRE 2 MÉTHODES

Les méthodes utilisées pour réaliser un système de TIE répondant au mandat spécifié dans l'introduction sont discutées dans ce chapitre qui débute par une description du fonctionnement général du système. Les modules MEA et MSD sont ensuite décrits. Le MSD est décrit en détail puisqu'il constitue la principale réalisation de ce projet. On expliquera l'approche de conception des circuits contenus dans le réseau de portes programmables (FPGA), l'élément central du MSD, et le rôle que ces circuits jouent dans le système. Enfin, on décrira l'interface de communication avec l'ordinateur et l'interface graphique par laquelle l'usager contrôle le système.

### 2.1 Description générale du système TIE5-USB

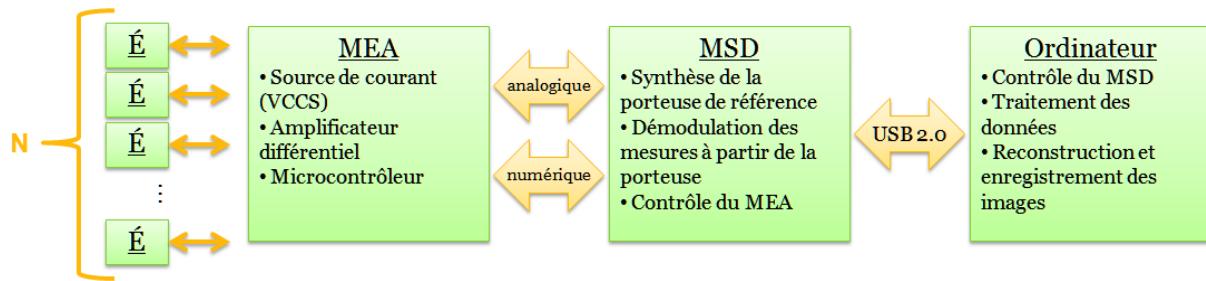

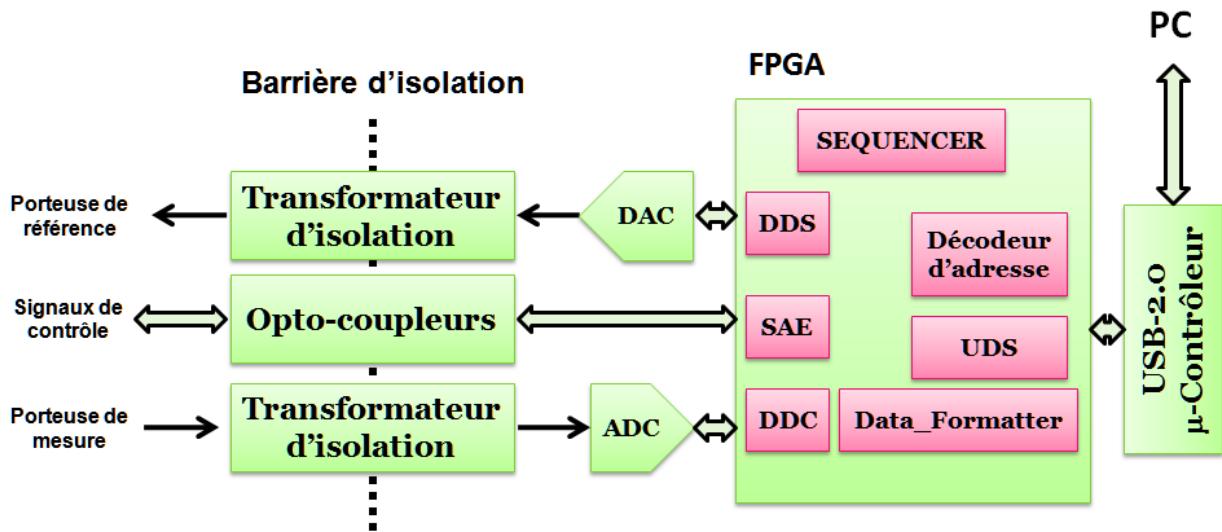

La figure 2.1 présente le flux des signaux entre les divers modules du système TIE5-USB, depuis les électrodes jusqu'à l'ordinateur hôte. Nous utiliserons ce schéma pour expliquer le fonctionnement général du système.

Figure 2.1 Représentation schématique du système TIE5-USB. On retrouve de gauche à droite, N électrodes reliées à des circuits d'interface situés dans le MEA. Ce dernier est relié au MSD par un bus analogique et un bus numérique. Le MSD est relié à l'ordinateur par un port de communication USB 2.0.

### Électrodes

L'interface entre le patient et le système de TIE est constituée d'électrodes Ag/AgCl à usage unique du même type que celles qui sont couramment utilisées pour l'enregistrement d'électrocardiogrammes (ECG). La connexion des électrodes au système est effectuée par des câbles d'environ 1 m de longueur terminés par des connecteurs à pression. Le même type de

connecteur est utilisé pour le fantôme résistif (figure 1.4), ce qui facilite l'acquisition de données lors des tests.

## **Module d'électrodes actives**

Le MEA utilisé dans notre projet est constitué de seize canaux identiques comprenant chacun une source de courant commandée par une tension, un amplificateur différentiel et un microcontrôleur. Ce dernier détermine le rôle de l'électrode Ag/AgCl reliée au canal à chaque étape de l'acquisition de données : a) application du courant d'excitation, b) mesure d'une différence de potentiel ou c) inactivité. Chaque microcontrôleur exécute le même microcode pour déterminer le rôle de l'électrode. Toutefois, ce rôle dépend du numéro du canal et du numéro de la mesure en cours. L'algorithme qui le détermine est conçu de façon à ce que, pour chaque mesure, il y ait deux électrodes pour appliquer le courant (une source et un puits), deux électrodes pour mesurer la différence de potentiel et douze électrodes inactives, c'est-à-dire qui présentent une haute impédance. Par défaut, l'algorithme utilise des paires d'électrodes adjacentes pour l'excitation et la mesure. Avec seize canaux, il génère une séquence de 208 mesures par trame. La séquence peut être modifiée à partir de l'interface usager en transmettant aux microcontrôleurs des paramètres définissant l'intervalle (nombre d'électrodes) entre les paires d'excitation et de mesure. On peut ainsi obtenir des séquences où l'excitation se fait par des électrodes opposées et les mesures par des électrodes adjacentes ainsi que plusieurs autres configurations.

Le MEA communique avec le MSD par quatre signaux numériques formant un port numérique de quatre bits et deux signaux analogiques. Le port numérique permet d'initialiser les paramètres dans la mémoire des microcontrôleurs et de cadencer la séquence de mesures. Les signaux analogiques sont une porteuse de référence et une porteuse de mesure. La première porteuse sert à déterminer le spectre du courant d'excitation. Dans un système de TIE conventionnel, elle correspond à un sinus d'amplitude et de fréquence fixe, qui sont prédéterminées par l'usager. Son spectre est plus complexe pour les systèmes multifréquences. La seconde porteuse est le signal de sortie d'un amplificateur différentiel large bande dont les entrées sont les signaux provenant des canaux qui jouent le rôle d'électrodes de mesure. C'est cette porteuse qui sera démodulée par des circuits du MSD et qui fournira ultimement les données pour la reconstruction d'images. Une description plus détaillée du MEA est donnée à la section 2.2.

## Module de synthèse et de démodulation

Le MSD étant l'objet principal de ce mémoire nous lui consacrons une description détaillée à la section 2.3. Pour une explication du fonctionnement général du système, il suffit de mentionner les principaux rôles que joue ce module qu'on pourrait qualifier d'unité centrale : 1) initialisation du MEA et contrôle de la séquence de mesures, 2) synthèse de la porteuse de référence, 3) démodulation de la porteuse de mesure, 4) mise en forme et transmission des données acquises vers l'ordinateur et 5) matérialisation des choix faits par l'usager par l'intermédiaire de l'interface graphique. Du point de vue du flux des signaux, le MSD transmet et reçoit deux signaux analogiques (les porteuses mentionnées plus haut), gère un port bidirectionnel à faible débit (le port de quatre bits servant à contrôler le MEA) et un port bidirectionnel à haut débit : le port USB qui le relie à l'ordinateur.

## Communication USB

Toutes les communications entre le MSD et l'ordinateur s'effectuent par un port USB 2.0. La diversité d'informations qui transitent par ce port (commandes et états du système, données acquises, etc.) nécessitent un protocole de communication que nous décrivons à la section 2.4.

## Ordinateur

Nous utilisons pour notre système de TIE un ordinateur de bureau standard. En effet, l'efficacité du traitement de données par le MSD, des communications par le port USB et celle de l'interface graphique permet d'utiliser un PC aux performances et au coût modestes.

Le contrôle du système par l'usager se fait par une interface graphique réalisée à l'aide d'un logiciel appelé MEMTA (*Modular Expandable Multi-Threaded Architecture*). Ce logiciel est décrit en détail dans la thèse de doctorat de son concepteur (Gagnon, 2003). MEMTA consiste en un environnement de développement d'applications supportant l'usage de processus légers (en anglais, *threads*) pour effectuer plusieurs tâches en temps réel. L'environnement permet d'exercer une approche hautement modulaire et parallèle pour réaliser de nouvelles applications à partir d'une bibliothèque de modules de base et un script qui définit l'usage des modules et leurs interconnexions. Bien entendu, le programmeur peut créer de nouveaux modules pour des cas spécifiques. Par exemple, dans notre projet, un seul nouveau module a été créé, le module *HAL* (*Hardware Abstraction Layer*) qui sert d'interface aux multiples circuits contenus dans le MSD.

Tous les autres modules de l'interface graphique ont été conçus pour des systèmes d'acquisition de données antérieurs. On retrouve dans la librairie de base des modules *oscilloscope* pour afficher en temps réel les données du système, des modules de lecture et de sauvegarde de données en format *Matlab*, des modules pour la reconstruction et l'affichage d'images de TIE, et plusieurs autres. Dans un autre environnement de développement, ces modules auraient vraisemblablement dû être conçus de toute pièce, augmentant grandement la difficulté et le temps de développement du système.

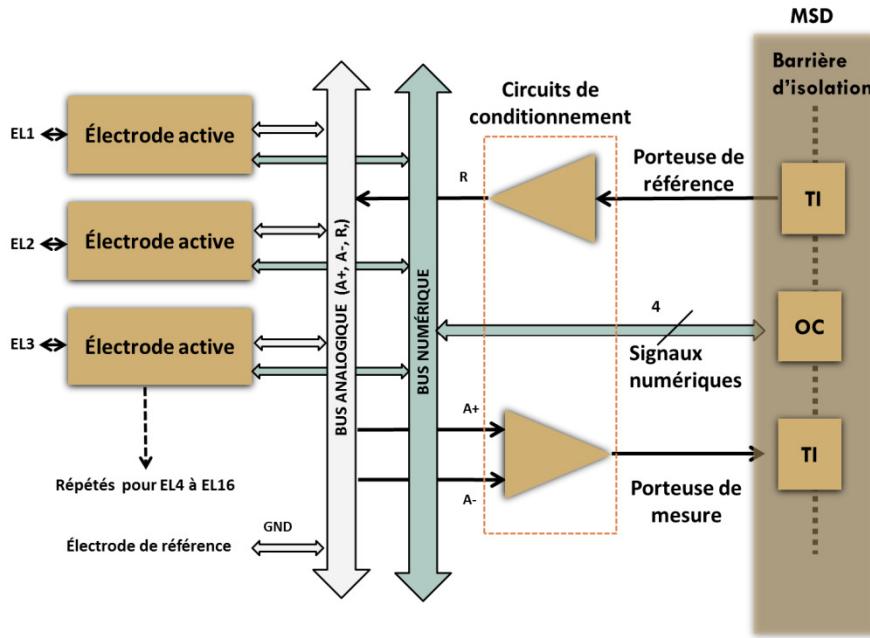

## 2.2 Description du module d'électrodes actives

La figure 2.2, tiré du mémoire de Yannick Sigmen (2012), représente de façon schématique les circuits qu'on retrouve à l'intérieur du MEA. Par contre, la barrière d'isolation qu'on aperçoit à la droite se trouve à l'intérieur du MSD et sera décrite dans la section 2.3.2. Il y a donc deux signaux analogiques : la porteuse de référence et la porteuse de mesure. Les circuits de conditionnement effectuent l'amplification et le filtrage de ces signaux analogiques. Les signaux numériques provenant du MSD (DSC\_OUT, SCAN\_CLK, SYNC et RESET) permettent la communication avec le MEA et gèrent la séquence de mesure. Leur rôle est décrit au tableau 2.1.

Notons que les microcontrôleurs peuvent se trouver dans deux modes différents : initialisation et acquisition. Le mode initialisation permet aux microcontrôleurs de déterminer leur position dans la chaîne de canaux (configuration de circuits en guirlande). C'est durant cette phase que le MSD définit la séquence de mesures en transmettant des paramètres au MEA par un protocole de communication série synchrone qui utilise SCAN\_CLK comme signal d'horloge et SYNC et DSC\_OUT comme signaux de données d'entrée et de sortie respectivement.

Figure 2.2 Schéma fonctionnel du MEA.

Tableau 2.1 Signaux du bus numérique reliant le MSD au MEA.

| Signal   | Description                                                                                                                                                                                                                                                                                                                                                    |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSC_OUT  | <ul style="list-style-type: none"> <li>- Signal de sortie du MEA</li> <li>- Utilisé pour les communications entre le MSD et le MEA. Indique la fin d'une trame de mesures lors de l'acquisition de données.</li> <li>- DSC vient du terme anglais <i>Daisy-Chained</i>, soit une connexion en guirlande entre les seize canaux d'électrodes actives</li> </ul> |

| RESET    | <ul style="list-style-type: none"> <li>- Signal d'entrée du MEA</li> <li>- Réinitialise les seize microcontrôleurs du MEA.</li> </ul>                                                                                                                                                                                                                          |

| SCAN_CLK | <ul style="list-style-type: none"> <li>- Signal d'entrée du MEA</li> <li>- Utilisé pour les communications entre le MSD et le MEA. Cadence la séquence de mesures lors de l'acquisition de données.</li> </ul>                                                                                                                                                 |

| SYNC     | <ul style="list-style-type: none"> <li>- Signal d'entrée du MEA</li> <li>- Utilisé pour les communications entre le MSD et le MEA. Indique au MSD un arrêt prématuré de l'acquisition de données.</li> </ul>                                                                                                                                                   |

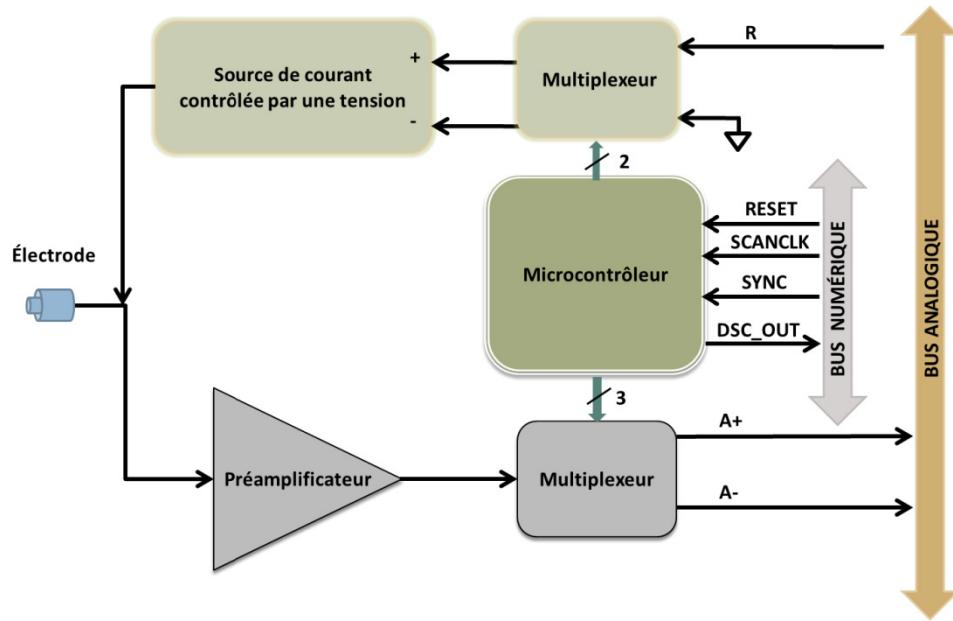

Figure 2.3 Représentation schématique d'un circuit d'électrode active (EA).

La figure 2.3 montre les circuits d'une électrode active. La source de courant contrôlée par une tension (VCCS) est un circuit doté d'une entrée différentielle. Le multiplexeur qui précède ce circuit permet de le faire fonctionner selon trois modes : i) source de courant (le signal R, soit la porteuse de référence générée par le MSD, est appliquée à l'entrée + et l'entrée – est reliée à la masse), ii) puits de courant (l'entrée + est reliée à la masse et le signal R, à l'entrée –), et iii) inactif (les entrées + et – sont reliées à la masse). Dans le mode inactif, aucun courant n'est appliqué à l'électrode. Celle-ci est alors essentiellement déconnectée du système en raison de la haute impédance de sortie du VCCS. La porteuse de mesure est pour sa part produite par un amplificateur différentiel large bande situé sur le MEA. Les entrées de cet amplificateur sont les lignes A+ et A- du bus analogique. Durant l'acquisition de données, les microcontrôleurs qui dirigent les deux canaux servant à mesurer une différence de potentiel programment le multiplexeur situé au bas du schéma de façon à connecter le préamplificateur du premier canal à la ligne A+ et le préamplificateur du second canal à la ligne A-. C'est ce signal qui est envoyé au MSD. Il s'agit du signal brut de TIE. Il a l'aspect d'une sinusoïde modulée par une série de plateaux. Chaque plateau représente un changement d'amplitude dû à la variation de la distance entre les électrodes qui appliquent le courant et celles qui mesurent les différences de potentiel.

## 2.3 Description matérielle du module de synthèse et de démodulation

### 2.3.1 Blocs d'alimentation

Le boîtier du système de TIE contient trois composants : la carte électronique du MSD et deux blocs d'alimentation : un bloc à découpage et un bloc linéaire. Ces blocs alimentent le MSD et le MEA respectivement. Ils sont de qualité médicale et répondent à la norme CEI-60601 qui décrit les règles de sécurité et de performances essentielles pour les appareils médicaux. La figure 2.4 illustre les composants électroniques qui se trouvent sur le circuit imprimé du MSD.

Figure 2.4 Schéma fonctionnel du circuit imprimé du MSD.

### 2.3.2 Isolation électrique

L'emploi de deux blocs d'alimentation distincts pour le MSD et le MEA est un premier élément des mesures prises pour assurer la sécurité du patient. Le second élément est l'établissement d'une barrière d'isolation entre les circuits du MEA et ceux du MSD. Comme son nom l'indique, cette barrière a pour but d'empêcher le passage de courant électrique entre les circuits du MEA, qui se trouvent en contact avec le patient par l'intermédiaire des électrodes, et les circuits du MSD qui sont reliés au secteur par le port USB de l'ordinateur hôte. En pratique, le courant qui traverse la barrière d'isolation n'est pas nul (en raison de couplages capacitifs inévitables) mais il revient aux concepteurs de s'assurer qu'il ne dépasse pas les limites imposées par la norme CEI-60601 (par exemple, un maximum de 10 µA rms à 60 Hz). Pour que les signaux nécessaires au fonctionnement du système puissent traverser la barrière d'isolation, ils

doivent être convertis sous une autre forme : champ magnétique, photons, etc. Dans notre système, les porteuses de référence et de mesures sont isolées au moyen de transformateurs à large bande passante, tandis que les signaux numériques sont isolés par des opto-coupleurs.

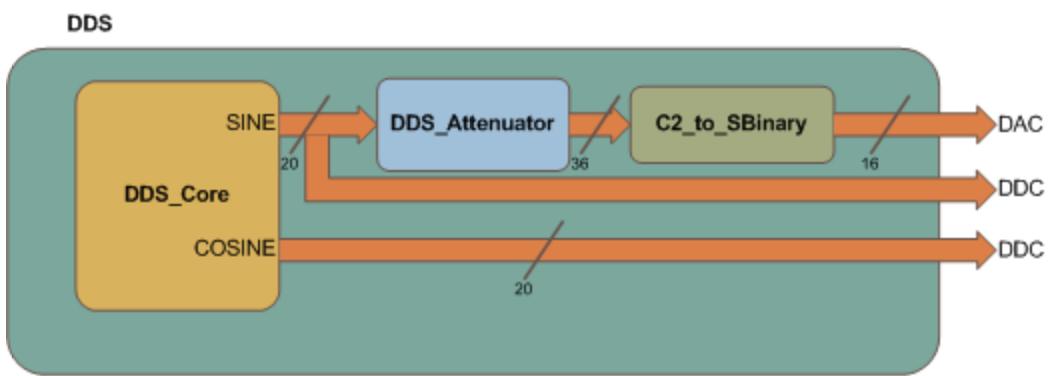

### 2.3.3 Convertisseurs analogique-numérique et numérique-analogique

En plus des circuits électroniques formant la barrière d'isolation, on retrouve sur la carte du MSD des convertisseurs analogique-numérique (ADC) et numérique-analogique (DAC). Comme le montre la figure 2.4, le DAC sert à générer la porteuse de référence à partir des données numériques synthétisées par le DDS (*Direct Digital Synthesizer*), un des modules du FPGA qui sera expliqué à la section 2.4. Nous avons utilisé un DAC de seize bits (LTC1668, *Linear Technology*) pouvant fonctionner à un taux d'écriture de 50 MHz. Un des paramètres de performance utilisé pour caractériser les DACs est la plage dynamique sans parasite ou SFDR (*Spurious Free Dynamic Range*). Dans notre cas, les données du DDS sont écrites au DAC au taux de 24 MHz. La fréquence de porteuse de référence couramment utilisée en TIE est de 50 kHz. La fiche technique du LTC1668 nous indique un SFDR de 90 dB pour un sinus de 1 MHz. On peut donc s'attendre à un SFDR plus élevé pour un sinus de 50 kHz mais cette valeur représente néanmoins la valeur minimale du SFDR qu'on peut atteindre. Il est à noter que cette mesure de SFDR est valide directement à la sortie du DAC. Dans notre système, ce signal passe par un transformateur d'isolation suivi d'un filtre passe-bas, ce qui peut réduire quelque peu le SFDR de la porteuse de référence transmise au MEA. Le filtre passe-bas est réalisé par une puce LTC1564 (*Linear Technology*) qui comprend un filtre du 8<sup>e</sup> ordre et un amplificateur à gain programmable. La fréquence de coupure du filtre (seize valeurs allant de 10 kHz à 160 kHz) et le gain de l'amplificateur (seize valeurs allant de 0 à 15 V/V) sont fixés par des cavaliers permettant des ajustements seulement lorsque le système est hors-tension

Pour le conditionnement de la porteuse de mesure, le signal provenant du MEA passe d'abord par un transformateur d'isolation puis un filtre passe-bas. Une deuxième puce LTC1564 est utilisée pour cette fonction et sert essentiellement de filtre antirepliement (en anglais, *antialiasing*). La fréquence de coupure du filtre et le gain de l'amplificateur sont dans ce cas-ci contrôlés par des signaux provenant du FPGA. On peut ainsi optimiser l'utilisation de la plage dynamique de l'ADC à partir de l'interface usager. Le signal à la sortie du filtre antirepliement est numérisé par un ADC (LTC1414, *Linear Technology*) de quatorze bits pouvant fonctionner au

taux de 2,2 MHz. Selon les spécifications du manufacturier, le rapport signal sur bruit (en anglais, *Signal to Noise Ratio*, SNR) à cette cadence est de 70 dB. Dans notre système, cet ADC fonctionne au taux de 2 MHz sous le contrôle d'un signal d'horloge de 2 MHz généré par le FPGA.

### 2.3.4 FPGA

Tel que mentionné précédemment, la principale innovation de cette 5<sup>e</sup> génération du système de TIE réside dans l'intégration complète dans un FPGA des tâches qui auparavant étaient exécutées par des composants électroniques distincts. Ceci entraînait un fonctionnement sous-optimal du système à cause des difficultés à réaliser la synchronisation parfaite de ses composantes. Le FPGA choisi lors de la conception de la carte électronique du MSD est un Virtex-II de *Xilinx*. Il s'agit de la 2<sup>e</sup> génération de FPGA hautes performances fabriquées par cette compagnie. Malgré qu'il existe maintenant des FPGA beaucoup plus performants, nous n'utilisons qu'environ 30% des ressources de ce FPGA pour cette nouvelle version du système de TIE. Le Virtex-II est donc amplement suffisant pour l'application envisagée.

Un FPGA est un circuit de logique programmable constitué de plusieurs blocs de logique configurable (en anglais, *configurable logic block*, CLB) et de blocs d'entrées sorties (en anglais, *input/output block*, IOB). On programme ces blocs pour qu'ils remplissent le rôle d'un élément logique d'un circuit. Une fois ces éléments logiques reliés ensemble, le FPGA peut accomplir les mêmes tâches qu'un assemblage complexe de circuits logiques. Un avantage important des FPGA est qu'il est possible de changer les éléments de circuits logiques autant de fois qu'on le désire par une simple reprogrammation. C'est un atout majeur dans le développement de nouvelles technologies et le prototypage rapide de systèmes numériques.

En plus des CLBs et des IOBs, on retrouve les éléments suivants dans les FPGA de la famille Virtex-II :

- des DCM (en anglais, *Digital Clock Manager*) qui permettent d'ajuster de façon numérique la propagation des horloges à l'intérieur du système en développement. On peut alors contrôler les délais de phase et l'effet d'obliquité (en anglais, *skew*).

- des blocs de multiplication dédiés qui permettent d'effectuer directement des multiplications d'entiers de 18 bits  $\times$  18 bits.

- des blocs de mémoire vive (en anglais, *Block SelectRAM*) qui permettent de créer des structures de registres pour conserver des données.

Afin de définir un circuit logique à l'intérieur d'un FPGA, on se sert d'un langage de description de matériel, comme le VHDL dont le sigle signifie *VHSIC Hardware Description Language*, où VHSIC est l'abréviation de *Very High Speed Integrated Circuit*. Il est à noter qu'on ne parle pas ici d'un langage de programmation mais bien d'un langage permettant de définir des composants matériels, ce qui est complètement différent. Pour marquer la différence, considérons un programme écrit pour une certaine application dans un langage comme le C par exemple. Un compilateur va transformer les instructions du programme C en instructions d'un langage de plus bas niveau (généralement, en assembleur) puis en un code numérique (le module objet) qui sera exécuté par un ordinateur. En VHDL, les instructions écrites par le concepteur de système servent à définir des circuits logiques et leurs interconnexions. Ces circuits seront synthétisés et traduits par un outil logiciel qui générera des données numériques permettant de programmer les blocs du FPGA en fonction de l'application. Le FPGA pourra alors remplir la tâche définie par les instructions du concepteur au moyen des circuits logiques choisis.

Lorsqu'on fait la description d'une architecture pour une nouvelle application en VHDL, plusieurs choix s'offrent à nous. On doit d'abord déterminer le niveau d'abstraction avec lequel on décrira la logique. On peut faire une description de très bas niveau en implémentant, par exemple, des compteurs et des multiplexeurs à l'aide de portes et de bascules. Ce choix permet d'exercer un contrôle plus complet sur le circuit obtenu du synthétiseur et dans certains cas d'en optimiser les performances. Cette approche s'avère beaucoup trop ardue pour des applications complexes. On peut décider d'utiliser un niveau de description un peu plus élevé, en décrivant des machines à états et des structures de décisions. On se fie alors davantage aux capacités de traduction en logique simple du synthétiseur. Finalement, on peut utiliser des blocs de propriété intellectuelle (en anglais, *Intellectual property (IP) cores*) qui sont des modules VHDL conçus par le fabricant du FPGA. Ils permettent d'effectuer des tâches génériques qui sont souvent requises pour des applications de traitement de signal. Ces modules sont accessibles dans le logiciel de développement intégré du fabricant. Pour Xilinx, ce logiciel se nomme *ISE*. Pour ce

projet, on a évidemment choisi un niveau de description VHDL élevé tel qu'il sera décrit pour chacun des modules à la section 2.4.

Une autre décision importante qui doit être prise lors de la réalisation d'un FPGA est l'utilisation ou non du *Schematic Editor* de l'*ISE*. Le *Schematic Editor* permet de concevoir les différents modules selon une approche graphique. Essentiellement, on dessine des blocs, par exemple un DDS, et on définit ensuite le code VHDL de ce module. Il ne reste alors qu'à le relier aux autres modules du système. Bien que cette approche semble intéressante à première vue, l'utilisation de cet outil a été rejetée pour deux raisons. Premièrement, il rendait la seule version disponible de l'environnement de développement *ISE* instable (précisons que nous avons été limités à la version 10.1 de l'*ISE* puisqu'elle est la dernière version de l'environnement de développement de *Xilinx* supportant les FPGA de type *Virtex-II*). Deuxièmement, certains *IP Cores* n'étaient pas compatibles avec cet outil. En optant pour une approche complète en VHDL, c'est-à-dire une architecture où tous les modules et même l'entité de plus haut niveau (représentant tout le FPGA) sont décrits en VHDL, on a pu éviter les problèmes de stabilité de l'*ISE* et générer un code entièrement transférable à d'autres familles de FPGA de *Xilinx* ou d'autres fabricants. Même les blocs de propriété intellectuelle de *Xilinx* qui ont été employés ont été intégrés en VHDL. On peut donc affirmer que le projet est réalisé à 100% en VHDL.

Voici les étapes que l'*ISE* utilise pour traduire le code VHDL en circuits logiques :

1. Le synthétiseur interprète le code VHDL et le traduit en une logique correspondante qu'on nomme RTL de l'anglais *Register Transfer Level*.

2. L'outil d'implémentation de l'*ISE* prend la logique RTL et tente de la convertir en circuits en fonction des éléments logiques disponibles sur le FPGA choisi pour ce design. Il doit aussi faire le routage des différents modules afin que l'information puisse se déplacer entre chacun d'eux tout en respectant les contraintes de temps de propagation. Il peut alors optimiser ce routage en fonction de deux paramètres : vitesse d'exécution ou utilisation des ressources.

3. Des fichiers de programmation sont générés et peuvent être envoyés directement au FPGA ou écrits sur des supports mémoire. Pour le système de TIE5-USB, des mémoires mortes (EEPROMS) ont été prévues pour conserver le code de programmation du FPGA. Chaque fois que le système est mis sous tension, les

mémoires transfèrent automatiquement leur contenu dans la mémoire vive interne du FPGA.

### 2.3.5 Microcontrôleur USB

Les derniers composants électroniques qui font partie du MSD sont un microcontrôleur USB (CY7C68013-128C, *Cypress Semiconductor*) et une mémoire *flash* (24LC64, *Microchip*). Le microcontrôleur USB est en fait une puce électronique qui contient un microprocesseur 8051 d'*Intel*, un émetteur-récepteur USB 2.0 et une mémoire vive de 64 KB. Cette mémoire est divisée en deux parties. La première moitié est dédiée au fonctionnement du microcontrôleur USB. Tandis que l'autre moitié permet de référencer les registres contrôlant les différents paramètres du FPGA. La mémoire *flash* externe a deux rôles :

- Elle contient les descripteurs USB des systèmes. Ces derniers indiquent à l'ordinateur quel est le périphérique qu'on vient d'y connecter et comment il doit s'interfacer avec ce dernier.

- Elle contient aussi le microcode du microcontrôleur USB. Ce dernier peut être modifié et reprogrammé à partir de l'interface usager.

Cette section conclut la description des composants électroniques du MSD. On abordera maintenant l'architecture logique du FPGA.

## 2.4 Architecture proposée pour le module de synthèse et de démodulation

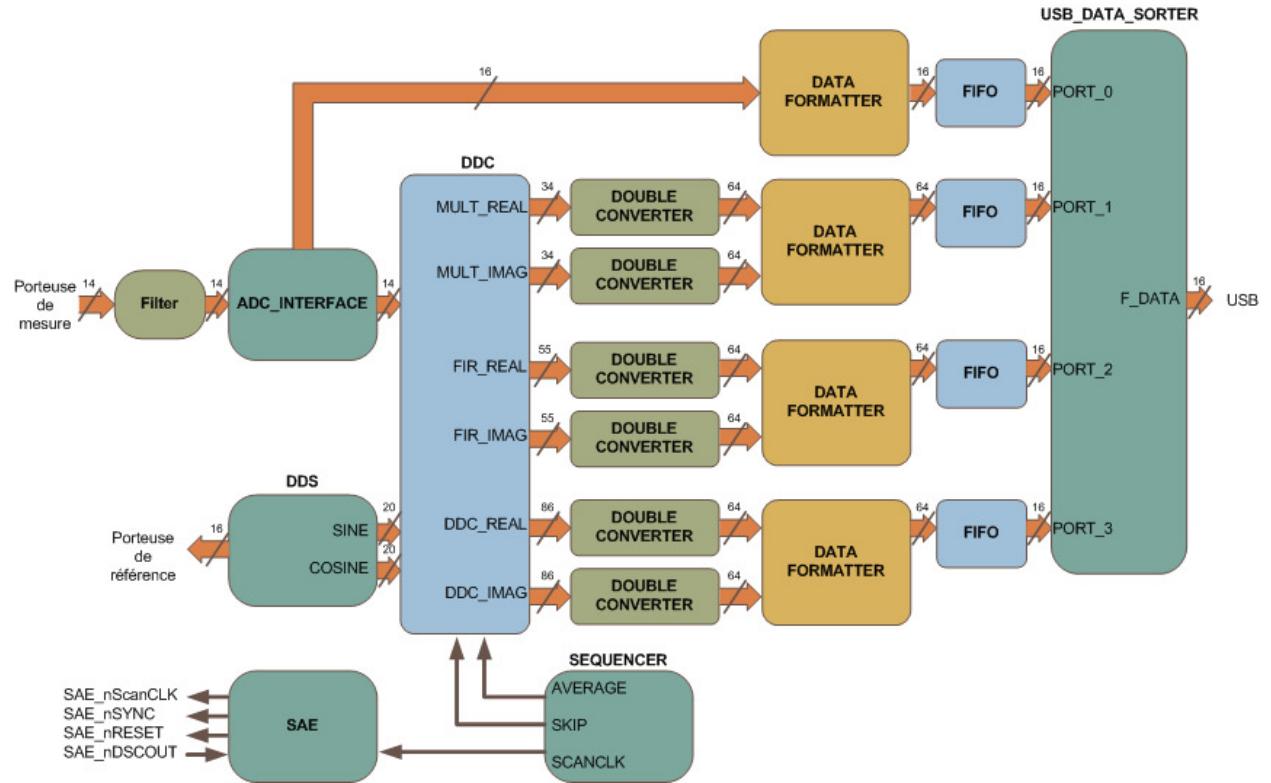

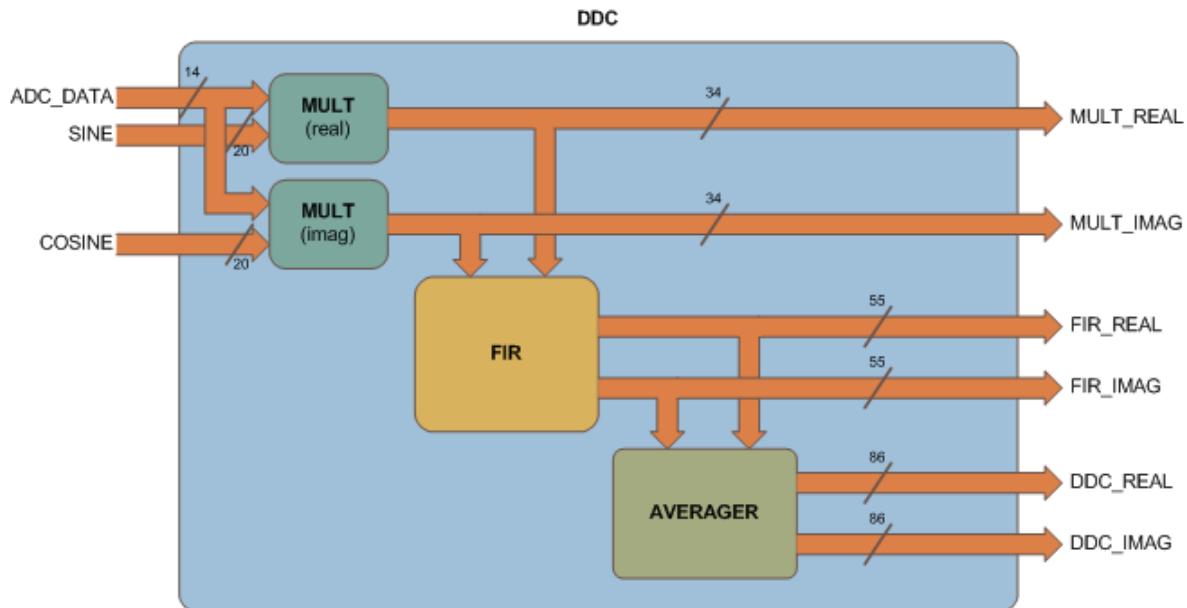

Cette section décrit l'architecture interne du FPGA du système TIE5-USB. On y explique les différents modules logiques qui ont été développés pour programmer le FPGA du MSD. Cependant, avant d'entamer une description détaillée, on expliquera brièvement la philosophie de conception ayant mené à l'agencement des modules.

Afin de comprendre cette philosophie de conception, il faut d'abord expliquer comment l'ordinateur interagit avec le système. Les paramètres qui sont entrés par l'usager dans l'interface graphique MEMTA sont projetés (en anglais, *memory mapped*) dans la section de mémoire du microcontrôleur USB réservée au FPGA. Nous désignerons ces cases de mémoire de registres de contrôle du système TIE5-USB. Ces registres sont référencés par des adresses de seize bits. On utilise les huit bits les plus significatifs de l'adresse pour désigner le module du FPGA visé par

une opération et les huit bits les moins significatifs pour référencer les divers registres que ce module comporte.