| <b>Titre:</b><br>Title: | Look-Up Table Based Neural Networks For Fast Inference                                                                                                                            |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Auteur:<br>Author:      | Moussa Traore                                                                                                                                                                     |  |

| Date:                   | Date: 2022                                                                                                                                                                        |  |

| Туре:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                         |  |

| Référence:<br>Citation: | Traore, M. (2022). Look-Up Table Based Neural Networks For Fast Inference<br>[Mémoire de maîtrise, Polytechnique Montréal]. PolyPublie.<br>https://publications.polymtl.ca/10547/ |  |

# **Document en libre accès dans PolyPublie** Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/10547/     |

|------------------------------------------|--------------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | J. M. Pierre Langlois, & Jean Pierre David |

| Programme:<br>Program:                   | Génie informatique                         |

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Look-Up Table Based Neural Networks For Fast Inference

# MOUSSA TRAORE

Département de génie informatique et génie logiciel

Mémoire présenté en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* Génie informatique

> A out 2022

© Moussa Traore, 2022.

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Ce mémoire intitulé :

# Look-Up Table Based Neural Networks For Fast Inference

## présenté par Moussa TRAORE

en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* a été dûment accepté par le jury d'examen constitué de :

Guy BOIS, président Pierre LANGLOIS, membre et directeur de recherche Jean Pierre DAVID, membre et codirecteur de recherche Tarek OULD BACHIR, membre

# DEDICATION

To my people, that inspired me not to become someone else, but to be more thoroughly myself...

#### ACKNOWLEDGEMENTS

Leaving my job, and looking for my backpack on the first day back to school is memorable. The excitement I felt, the constant hunger for knowledge and the passion I had for discovery brought me to Professor Langlois and Professor David on a cold winter of January 2020. For the warm welcome to their laboratory, the constant guidance and support I would like to thank Professor Langlois and Professor David. Going through this entire program despite COVID-19 would not have happened without their dedication, their sustained push for improvement and their relentless pursuit of excellency. Thank you.

Working alongside brilliant people with the same dreams and aspirations as me had never felt better. I would like to thank Alexandre, Hossein, Mehdi and Su who have shared ideas and never hesitated to jump on a white board with me for a heated discussion on the next best step.

I would like to thank my mother for never letting me down.

I would like to thank and congratulate my father, Traore Mamadou, for achieving his Doctorate degree while I was working on this thesis. It showed me that no matter a person's age, his success and the respect he receives from his peers, having the humility to learn is something to thrive for. It pushed me to where I am today.

I would like to thank my sister and my brother that put up with my sleepless nights, and my constant stress. Thanks for the support and for believing in me.

## RÉSUMÉ

La dernière décénie a connu de fulgurants dévelopements dans le domaine de l'intelligence artificielle, plus précisément de l'apprentissage profond. Bien qu'ayant été un sujet de recherche depuis les années 80, ce domaine ne connait son essor que depuis 2012 lorsqu'un modèle d'apprentissage profond gagne la compétition ImageNet de reconnaissance d'image. Depuis, de nombreux chercheurs se sont penchés sur la question. Plusieurs problèmes majeurs restent encore sans solution, dont celui de la performance de ces modèles et de leur consommation importante d'énergie. Dans le cadre de ce travail, nous explorons l'efficacité de ces modèles dans le contexte des systèmes embarqués qui ont un budget énergétique et une puissance de calculs relativement limités. Pour tenter d'apporter une solution à certains de ces problèmes, nous explorons des techniques de quantification binaire, d'élagage, et des réseaux maître-élève. Généralement, lors de la conception d'un réseau binaire, l'architecture du système sous-jacent n'est pas prise en compte. Cependant, l'exploration récente de l'application des réseaux binaires sur des FPGA a mené à de nouvelles architectures de réseaux pouvant être contenus complètement dans les tables de vérités d'un FPGA. Pour construire ce type de modèles, plusieurs algorithmes d'apprentissage existent. PoET-BiN, l'un de ces algorithmes, est au coeur de notre travail. Dans ce travail, nous commençons par explorer une nouvelle forme d'algorithme visant à compresser les réseaux de neurones binaires. Nous apportons ensuite des améliorations sur le modèle algorithmique de PoET-BiN, dans le but d'améliorer la précision de ses prédictions et explorons comment ce modèle peut être appliqué sur les couches de convolution d'un réseau neural convolutif. Nous démontrons des améliorations en terme de précision d'apprentissage par rapport à l'algorithme original de PoET-BiN sur MNIST. Finalement, nous étudions des améliorations matérielles, notamment en termes d'architecture processeur pouvant améliorer grandement le traitement des prédictions faites par les réseaux de neurones basés sur les tables de vérité. Nous atteignons une une accélération maximale d'un facteur de 2994× lorsque le temps de calcul de notre processeur spécialisé est comparé à celui d'un processeur standard ne possédant pas notre unité de calculs spécialisée.

#### ABSTRACT

The last decade has seen tremendous developments in the field of artificial intelligence, more specifically deep learning. Although deep learning had been a research subject since the 1980s, the field only took off in 2012 when a deep leaning model won the ImageNet competition. However, several key problems still exist including that of the performance of these models with respect to their energy and power consumption. In this work, we explore the effectiveness of these models in the context of embedded systems that have a constrained energy and power budget. In an attempt to provide a solution to common problems, we explore techniques of binary quantification, pruning and master-networks students. Generally, when designing a binary network, the architecture of the underlying system is not taken into account. But, lately the exploration of the application of binary networks using FPGAs has led to new network architectures that can exclusively be contained in the look-up tables of an FPGA. Several learning algorithms exist to build such models. One of which, PoET-BiN, is at the heart of our work. In this work, we begin by exploring a new form of algorithm aimed at compressing binary neural networks. Then, we bring improvements to the algorithmic model of PoET-BiN, in order to improve the accuracy of the predictions made by PoET-BiN and explore how this model can be applied on the convolutional layers of a convolutional neural network. We demonstrate improvements in terms of learning accuracy compared to the original PoET-BiN algorithm on MNIST. Finally, we study hardware improvements, in particular in terms of processor architecture that can greatly improve the processing speed of these models. We achieve a  $2994 \times$  speedup when comparing our specialized processor to a standard processor, which does not have our processing unit.

# TABLE OF CONTENTS

| DEDIC  | ATION  |                                     | iii |

|--------|--------|-------------------------------------|-----|

| ACKNO  | OWLEI  | DGEMENTS                            | iv  |

| RÉSUN  | 1É     |                                     | v   |

| ABSTR  | ACT    |                                     | vi  |

| TABLE  | OF C   | ONTENTS                             | vii |

| LIST O | F TAB  | BLES                                | х   |

| LIST O | F FIG  | URES                                | xi  |

| LIST O | F SYM  | IBOLS AND ACRONYMS                  | xii |

| СНАРТ  | FER 1  | INTRODUCTION                        | 1   |

| СНАРТ  | FER 2  | BACKGROUND                          | 3   |

| 2.1    | Vanill | a neural networks                   | 3   |

|        | 2.1.1  | Forward propagation                 | 3   |

|        | 2.1.2  | Back propagation                    | 4   |

|        | 2.1.3  | Classification                      | 6   |

| 2.2    | Convo  | blutional neural networks           | 6   |

| 2.3    | Binari | ized neural networks                | 7   |

| 2.4    |        | ion trees                           | 9   |

|        | 2.4.1  | Bagging: Random forests             | 9   |

|        | 2.4.2  | Boosting: Adaboost                  | 9   |

| 2.5    | Tenso  |                                     | 13  |

|        | 2.5.1  | Rank of a tensor                    | 13  |

|        | 2.5.2  | Tensor-Train format                 | 13  |

| 2.6    | Summ   | nary                                | 14  |

| СНАРТ  |        | LITERATURE REVIEW                   | 15  |

| 3.1    | Pruni  | ng                                  | 15  |

|        | 3.1.1  | Structured and unstructured pruning | 16  |

| 3.1.3Scoring173.2Quantization173.3Knowledge distillation193.3.1Knowledge representation193.3.2Distillation strategy203.4Tensor-Train decomposition and tensor factorization203.5LUT-based neural networks223.6Summary233.6Summary25CHAPTER 4BTNN : BINARIZED TENSOR DECOMPOSITION OF NEURAL NET-<br>WORKS264.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.4.1Application to the MNIST dataset294.4.2Application to the CIFAR-10 dataset30 |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 3.3Knowledge distillation193.3.1Knowledge representation193.3.2Distillation strategy203.4Tensor-Train decomposition and tensor factorization203.5LUT-based neural networks223.5.1PoET-BiN233.6Summary25CHAPTER 4BTNN : BINARIZED TENSOR DECOMPOSITION OF NEURAL NET-<br>WORKS264.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.1Application to the MNIST dataset29                                                                         |   |

| 3.3.1Knowledge representation193.3.2Distillation strategy203.4Tensor-Train decomposition and tensor factorization203.5LUT-based neural networks223.5.1PoET-BiN233.6Summary25CHAPTER 4BTNN : BINARIZED TENSOR DECOMPOSITION OF NEURAL NET-WORKS264.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.4.1Application to the MNIST dataset29                                                                                                      |   |

| 3.3.2Distillation strategy203.4Tensor-Train decomposition and tensor factorization203.5LUT-based neural networks223.5.1PoET-BiN233.6Summary25CHAPTER 4BTNN : BINARIZED TENSOR DECOMPOSITION OF NEURAL NET-<br>WORKS264.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.4.1Application to the MNIST dataset29                                                                                                                                 |   |

| 3.4Tensor-Train decomposition and tensor factorization203.5LUT-based neural networks223.5.1PoET-BiN233.6Summary25CHAPTER 4BTNN : BINARIZED TENSOR DECOMPOSITION OF NEURAL NET-WORKS264.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.4.1Application to the MNIST dataset29                                                                                                                                                                 |   |

| 3.5LUT-based neural networks223.5.1PoET-BiN233.6Summary25CHAPTER 4BTNN : BINARIZED TENSOR DECOMPOSITION OF NEURAL NET-<br>WORKS264.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.4.1Application to the MNIST dataset29                                                                                                                                                                                                                     |   |

| 3.5.1PoET-BiN233.6Summary25CHAPTER 4BTNN : BINARIZED TENSOR DECOMPOSITION OF NEURAL NET-<br>WORKS264.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.4.1Application to the MNIST dataset29                                                                                                                                                                                                                                                   |   |

| 3.6Summary25CHAPTER 4BTNN : BINARIZED TENSOR DECOMPOSITION OF NEURAL NET-<br>WORKS264.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.4.1Application to the MNIST dataset29                                                                                                                                                                                                                                                                  |   |

| CHAPTER 4       BTNN : BINARIZED TENSOR DECOMPOSITION OF NEURAL NET-         WORKS       26         4.1       Introduction       26         4.2       Tensorizing neural networks       27         4.3       Binarized TT-decomposition of neural networks       28         4.4       Experiments       29         4.1       Application to the MNIST dataset       29                                                                                                                                          |   |

| WORKS264.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.1Application to the MNIST dataset29                                                                                                                                                                                                                                                                                                                                                 |   |

| 4.1Introduction264.2Tensorizing neural networks274.3Binarized TT-decomposition of neural networks284.4Experiments294.1Application to the MNIST dataset29                                                                                                                                                                                                                                                                                                                                                        |   |

| 4.2       Tensorizing neural networks       27         4.3       Binarized TT-decomposition of neural networks       28         4.4       Experiments       29         4.1       Application to the MNIST dataset       29                                                                                                                                                                                                                                                                                      |   |

| 4.3 Binarized TT-decomposition of neural networks       28         4.4 Experiments       29         4.4.1 Application to the MNIST dataset       29                                                                                                                                                                                                                                                                                                                                                             |   |

| 4.4 Experiments       29         4.4.1 Application to the MNIST dataset       29                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| 4.4.1 Application to the MNIST dataset                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| 4.4.2 Application to the CIFAR-10 dataset                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| 4.5 Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| 4.5.1 MNIST dataset results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| 4.5.2 CIFAR-10 dataset results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| 4.6 Conclusion $\ldots \ldots 33$                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| CHAPTER 5 APPLYING POET-BIN TO CONVOLUTIONAL NEURAL NETWORKS 3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5 |

| 5.1 PoET-BiN's depth challenge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| 5.2 Making PoET-BiN deeper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| 5.2.1 The curse of depth $\ldots \ldots 39$                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| 5.2.2 Early exit $\ldots$ 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 5.2.3 Conclusion $\ldots \ldots 39$                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| CHAPTER 6 ASIP ACCELERATOR FOR LUT-BASED NEURAL NETWORKS IN-                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| FERENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| 6.1 Specialized processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| 6.1.1 ASIP Designer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| 6.1.2 Base processor: TVLIW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| 6.1.3 Added hardware components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

|       | 6.1.4 Specialized instructions | 13 |

|-------|--------------------------------|----|

| 6.2   | Evaluation                     | 15 |

| 6.3   | Conclusion                     | 18 |

|       |                                |    |

| СНАРТ | TER 7 CONCLUSION               | 19 |

| 7.1   | Summary of works               | 19 |

| 7.2   | Limitations                    | 50 |

| 7.3   | Future research                | 50 |

|       |                                |    |

| REFER | RENCES                         | 52 |

# LIST OF TABLES

| Table 2.1 | XNOR operation                                                             | 8  |

|-----------|----------------------------------------------------------------------------|----|

| Table 3.1 | Side-by-side comparison of different tensor factorization methods. $\ .$ . | 22 |

| Table 4.1 | Experiment results of BTNN on MNIST                                        | 31 |

| Table 4.2 | Experiment results of BTNN on CIFAR-10, BTNNx indicates the TT             |    |

|           | ranks                                                                      | 33 |

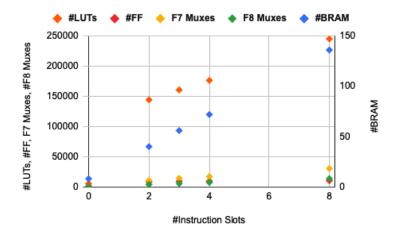

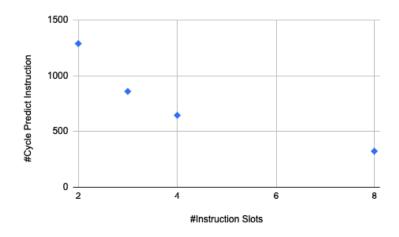

| Table 6.1 | LUTs, BRAM, Flip-Flops, F7 Mutiplexers, F8 Mutiplexers Count and           |    |

|           | number of cycles of predict instruction With regards to the number of      |    |

|           | Slots of the predict Instructions © 2022 IEEE $\ldots$                     | 46 |

# LIST OF FIGURES

| Figure 2.1 | Vanilla feed forward neural network with 2 hidden layers                             | 4  |  |  |

|------------|--------------------------------------------------------------------------------------|----|--|--|

| Figure 2.2 | Convex loss function and gradient descent.                                           | 5  |  |  |

| Figure 2.3 | Example filter of a CNN                                                              |    |  |  |

| Figure 2.4 | Convolution operation on a two dimensional input and a two dimen-                    |    |  |  |

|            | sional filter.                                                                       | 7  |  |  |

| Figure 2.5 | Regular decision tree and input features space partitioning                          | 10 |  |  |

| Figure 2.6 | Example space                                                                        | 11 |  |  |

| Figure 2.7 | Tensor-Train format of a $n$ dimensional tensor                                      |    |  |  |

| Figure 2.8 | Common matrix and vector multiplications in the Tensor-Train format.                 | 14 |  |  |

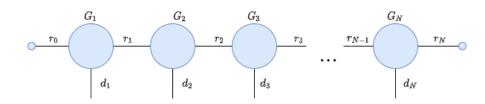

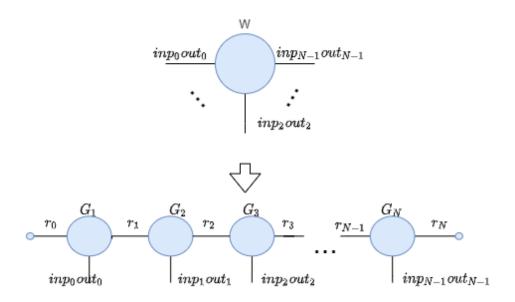

| Figure 3.1 | Tensor network representation of TT decomposition, $G$ tensors are the               |    |  |  |

|            | cores while $r_n$ indicate TT ranks                                                  | 21 |  |  |

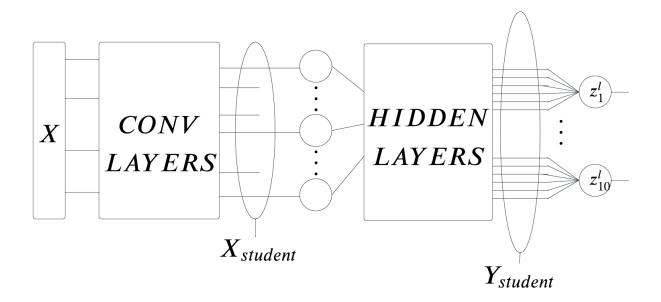

| Figure 3.2 | PoET-BiN BNN teacher-student architecture.                                           | 24 |  |  |

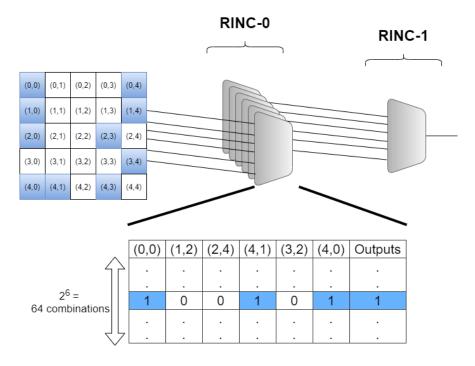

| Figure 3.3 | Selected inputs for a LUT in PoET-BiN © 2022 IEEE                                    | 25 |  |  |

| Figure 4.1 | Tensor network representation of reshape of the weights matrix $W$ to                |    |  |  |

|            | a tensor                                                                             | 28 |  |  |

| Figure 4.2 | TT-decomposition of weight matrix of the weights matrix in tensor                    |    |  |  |

|            | network representation                                                               | 29 |  |  |

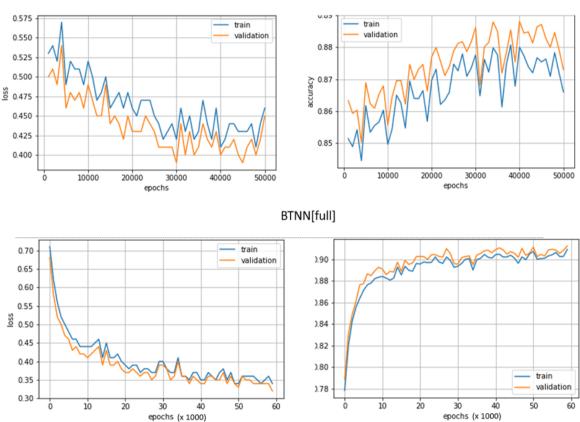

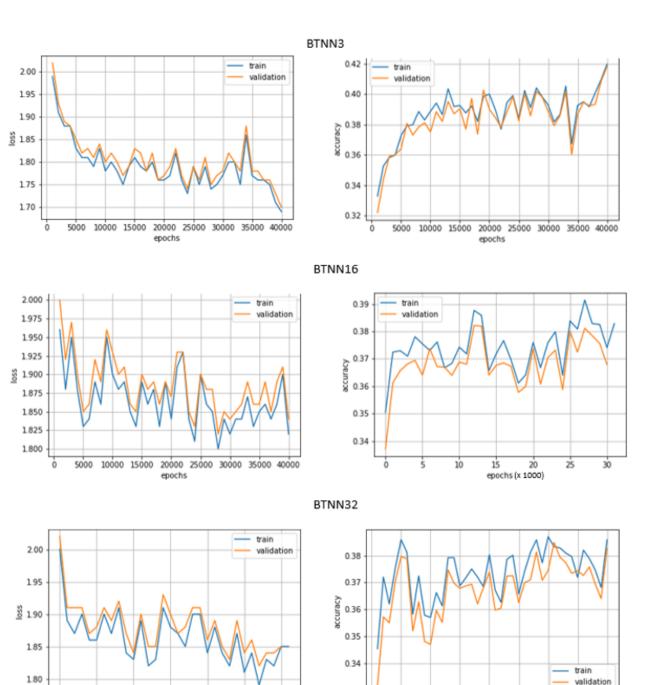

| Figure 4.3 | Loss and accuracy vs. epoch for the MNIST dataset                                    | 32 |  |  |

| Figure 4.4 | Loss and accuracy vs. epoch for the CIFAR-10 dataset $\ .$                           | 34 |  |  |

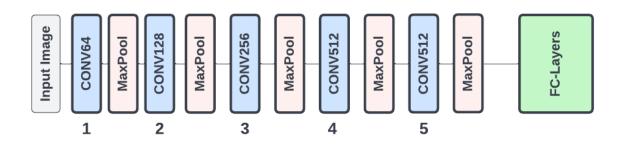

| Figure 5.1 | VGG13 Architecture                                                                   | 36 |  |  |

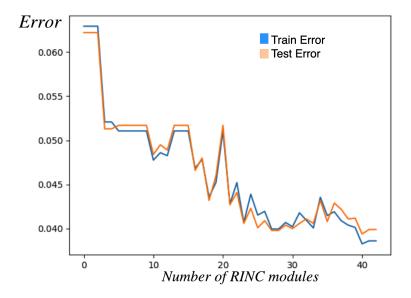

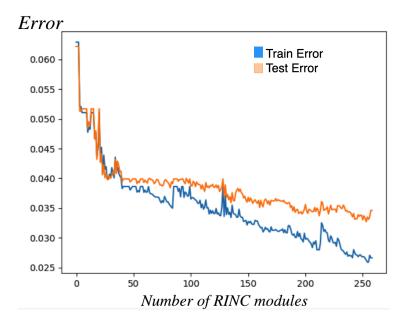

| Figure 5.2 | Accuracy of a single RINC-2 module                                                   |    |  |  |

|            | The blue curve shows the accuracy on the training set and the orange                 |    |  |  |

|            | curve shows the accuracy on the test set $\ldots \ldots \ldots \ldots \ldots \ldots$ | 38 |  |  |

| Figure 5.3 | Accuracy of a single RINC-3 module                                                   |    |  |  |

|            | The blue curve shows the accuracy on the training set and the orange                 |    |  |  |

|            | curve shows the accuracy on the test set $\ldots \ldots \ldots \ldots \ldots \ldots$ | 38 |  |  |

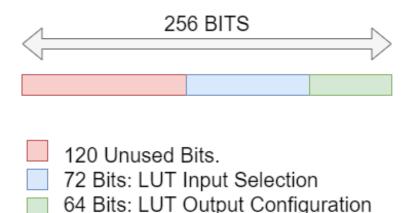

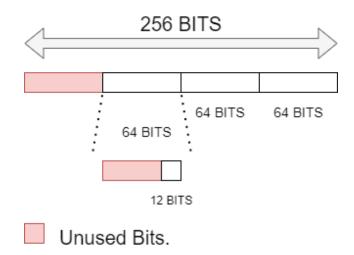

| Figure 6.1 | Data Alignment in Specialized Data Memories                                          | 43 |  |  |

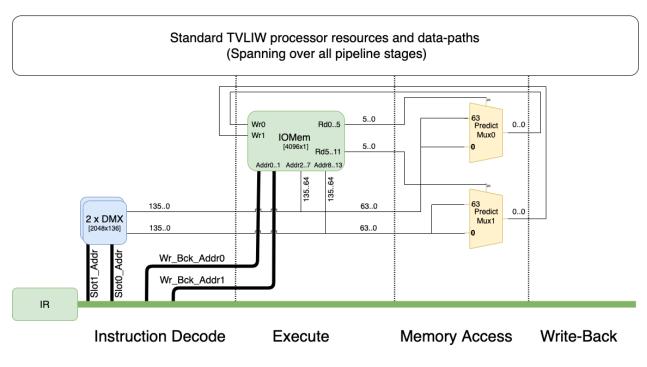

| Figure 6.2 | Overall Processor Architecture © 2022 IEEE $\ldots$                                  | 44 |  |  |

| Figure 6.3 | Data Memory Store Instruction Breakdown                                              | 45 |  |  |

| Figure 6.4 | Resource usage with respect to the number of slots $@$ 2022 IEEE                     | 47 |  |  |

| Figure 6.5 | Cycle count for predictions with respect to the number of slots $@$ 2022             |    |  |  |

|            | IEEE                                                                                 | 47 |  |  |

# LIST OF SYMBOLS AND ACRONYMS

| ASIC          | Application-Specific Integrated Circuit                   |  |  |

|---------------|-----------------------------------------------------------|--|--|

| ASIP          | Application-Specific Instruction-set Processor            |  |  |

| BNN           | Binarized Neural Network                                  |  |  |

| BTNN          | Binarized Tensor decomposition of Neural Networks         |  |  |

| CIFAR         | Canadian Institute for Advanced Research                  |  |  |

| CNN           | Convolutional Neural Network                              |  |  |

| CPU           | Central Processing Unit                                   |  |  |

| DL            | Deep Learning                                             |  |  |

| DNN           | Deep Neural Network                                       |  |  |

| $\mathbf{FC}$ | Fully Connected                                           |  |  |

| FPGA          | Field-Programmable Gate Array                             |  |  |

| FSP           | Flow of Solution Procedure                                |  |  |

| HOSVD         | Higher-Order Singular Value Decomposition                 |  |  |

| KD            | Knowledge Distillation                                    |  |  |

| KL            | Kullback–Leibler                                          |  |  |

| LUT           | Look-Up Table                                             |  |  |

| MAC           | Multiply And Accumulate                                   |  |  |

| MNIST         | Modified National Institute of Standards and Technologies |  |  |

| PoET-BiN      | Power Efficient Tiny Binary Neurons                       |  |  |

| RINC          | Reduced Input Neural Circuit                              |  |  |

| SIMD          | Single Instruction Multiple Data                          |  |  |

| SGD           | Stochastic Gradient Descent                               |  |  |

| SOTA          | State-Of-The-Art                                          |  |  |

| SVD           | Singular Value Decomposition                              |  |  |

| TT            | Tensor-Train                                              |  |  |

| VLIW          | Very Long Instruction Word                                |  |  |

#### CHAPTER 1 INTRODUCTION

The adequacy of machine learning algorithms, neural networks (NN) in particular, to process and extract useful information from the abundance of available data in all types of natural, human and industrial activities, has been clearly demonstrated in recent years [1] [2] [3]. More specifically, with recent hardware improvements, Deep learning (DL) algorithms, where several neural network layers are successively stacked in a single neural network, have become the state-of-the-art (SOTA) solution for many data intensive tasks, outperforming many classical learning techniques and expert systems. However, they involve an immense amount of computations and memory to store the model parameters. For example, EfficientNet-L2 has 480 million parameters and GPT-3 has 175 billion parameters [1] [3]. Implementing deep learning algorithms using general purpose architectures such as CPUs poses difficult problems [4] [5]. Deep neural networks (DNNs) are very resource hungry. Due to the von Neumann architecture used by modern CPUs, the sequential loading of data in CPU registers makes the inference process slower than the streaming oriented massively parallel architecture of GPUs [2] [4]. Still, GPUs energy usage tends to be relatively high [5] [6]. This leads to the requirement for more specialized hardware to be able to implement deep learning algorithms and achieve high performance with low energy, especially in the context of embedded devices where the energy budget is limited.

Several researchers are now focusing on developing computer hardware better suited to the realities of deep learning implementation [7]. Application-Specific Integrated Circuit (ASICs) have become the most commonly explored solution, integrating techniques such as in-memory computing, network on-chip, high bandwidth memory and data reuse [5] [7].

The fact that specialized hardware for DNNs depends on the ever changing algorithms and system requirements makes the non-recurring engineering costs of developing ASICs unreasonably high. Consequently, Field-Programmable Gate Arrays (FPGAs) have become increasingly adopted to accelerate machine learning algorithms [8] [9] [10]. They offer a high level of re-configurability making them a preferable solution to ASICs which is desirable in this research area. Jointly with research on hardware accelerators, researchers have been focusing on improving deep learning algorithms, with techniques such as quantization and binarization [11]. Binarized Neural Networks (BNNs) [12] have emerged as a practical solution. Hence, several adaptations to BNNs have been explored. Recently, Look-Up Tables (LUT) have been considered to adapt BNNs to the underlying architecture of FPGAs [13] [14]. In particular, the teacher-student knowledge distillation (KD) approach developed by Chidambaram et al. to build power efficient tiny binary neurons (PoET-BiN) demonstrated interesting results in the context of image classification with a convolutional neural network (CNN) [13]. However, their approach was subject to inherent limitations that made it unsuitable for a direct application on the convolutional layers of a CNN.

In light of these challenges, we define the main objectives of this thesis to be threefold: explore, enhance and exploit.

In the exploration phase, we look at a different network compression algorithms. Particularly, we combine tensor factorization and binarization and try to derive a LUT-based NN from there.

Therefore, in the enhancement phase, we worked on making PoET-BiN a more suitable candidate for an application on the convolutional layers of a CNN. More specifically, we modified the original work done by Chidambaram et al. to let PoET-BiN's training algorithm account for more features present from the input features space.

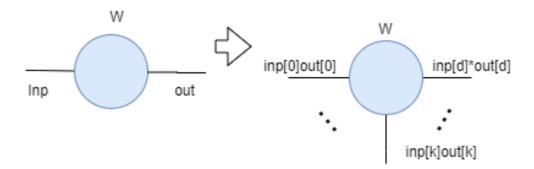

Finally, we realized that a regular CPU is ill-suited to exploit LUT-based NNs without an FPGA. Furthermore, even FPGAs with a limited number of LUTs may be ill-suited. Therefore, to exploit LUT-based NNs, we introduce a novel process architecture capable of processing the inference of up to 21 LUTs per clock cycle.

The thesis outlines as follows:

- Chapter 2 introduces key concepts needed to understand the remainder of the thesis.

- Chapter 3 provides a thorough overview of the SOTA in various DNN optimization domains ranging from pruning to knowledge distillation (KD) and tensor factorization.

- Chapter 4 introduces a novel compression approach, binarized tensorized neural networks (BTNN).

- Chapter 5 analyzes the limitation of the PoET-BiN training process and explores various optimizations to the original algorithm.

- Chapter 6 presents a specialized processor architecture designed for the purpose of LUT-based NNs.

- Chapter 7 synthesizes and concludes the thesis. The chapter also describes some limitations encountered in this work and provides some avenues for future works.

#### CHAPTER 2 BACKGROUND

To better understand the contents of this thesis, a few concepts need to be introduced. In this chapter, we describe how regular NNs learn. We then go over CNNs and BNNs before introducing decision trees and exploring two common learning algorithms, Adaboost and random forests. Finally, we introduce some concepts related to tensors which are used to explore a novel compression technique for neural networks in chapter 4.

#### 2.1 Vanilla neural networks

NNs are able to learn and apply knowledge acquired during a training process. The process relies on partial derivations of a loss function with respect to the parameters of the network and error propagation. In the context of the training algorithm, the network requires a prior mapping of inputs, X, to outputs, Y known as training data. In the following sections, we describe how this algorithm learns patterns. We start by describing the forward propagation of data in a neural network which tries to predict some properties of an input value X.

The known output that is mapped to X, namely Y, is then used to compute the prediction error. This error is then propagated backward in the network and used to update its parameters.

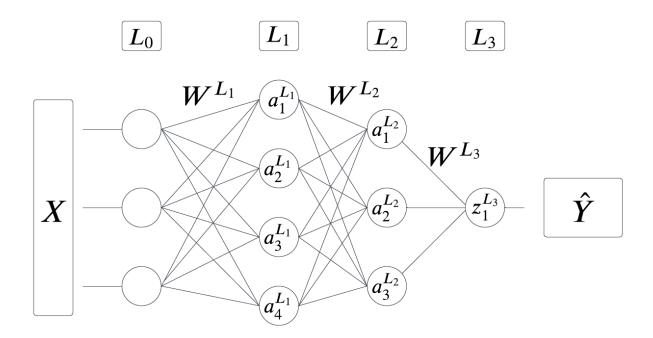

A four-layer neural network is shown in Fig. 2.1. The input is represented by the matrix X and the predicted output of the network by the matrix  $\hat{Y}$ . The layer-wise parameters of the networks are represented by the matrices  $W^{L_1}$ ,  $W^{L_2}$  and  $W^{L_3}$  with dimensions {3x4}, {4x3} and {3x1}, respectively.

#### 2.1.1 Forward propagation

Forward propagation represents the propagation of values in the network from left to right. The first layer is the input layer and the last layer is the output layer ( $L_0$  and  $L_3$ , respectively, in Fig. 2.1). Layers in-between are the hidden layers.  $L_0$ 's input values are the training examples X. In the upper layers, neurons apply activation functions to their inputs to compute their outputs.

Figure 2.1 Vanilla feed forward neural network with 2 hidden layers.

The output of a neuron  $a_n^l$ , where l is the index of the layer and n is index of the specific neuron on that layer, is computed using equations (2.1) and (2.2):

$$z^{l} = (W^{l})^{T} \times a^{l-1} + b^{l}, \qquad (2.1)$$

$$a_n^l = \sigma(z^l), \tag{2.2}$$

where  $z^l$  is the pre-activation vector input of the neuron,  $\sigma$  is the activation function,  $a^{l-1}$  the vector containing the outputs of the previous layer,  $W^l$  the weight matrix of the current layer and  $b^l$  the bias of the current layer. At the end of the forward propagation, we get an estimated value of the property we were trying to predict,  $\hat{Y}$ .

#### 2.1.2 Back propagation

The weights in the network are learned during training using an optimizer. A popular optimizer is the gradient descent optimizer. To apply gradient descent, we start by forwarding a single data point in the network before computing the estimation error. The error will then be propagated backward in the network to update the weights. A popular error function is

the L2 loss function C shown in equation (2.3):

$$C(W_{L_1}, ..., W_L) = \frac{1}{2} \sum ||\hat{y} - y_i||^2 = \frac{1}{2} \sum ||\sigma(W_L^T ... \sigma(W_{L_2}^T \sigma(W_{L_1}^T x_i))) - y_i||^2, \qquad (2.3)$$

where  $x_i, y_i$  are the *i*th training input and outputs respectively.

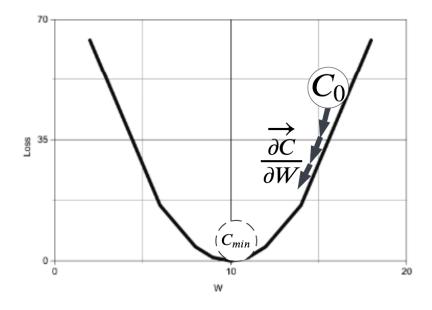

Note that C must be a convex function and therefore has a minimum as seen in Fig. 2.2.

The goal of this process is to minimize the error by bringing the estimated value  $\hat{Y}$  closer to the actual value Y. The minimum value of the error can be found by finding the right set of parameters W that minimizes the overall loss. When applying gradient descent, we update the weights by moving the error in the direction opposed to the gradient of the loss function. Each weight matrix is updated using equation (2.4):

$$W_{L_x}^{t+1} = W_{L_x}^t - \alpha \vec{\nabla} C(W_{L_x}^t, W_{L_{x-1}}^t, ..., W_{L_1}^t).$$

(2.4)

In Fig. 2.2, we observe the loss, C, with respect to the parameters of the network. The initial estimation error is  $C_0$ . The target minimum value is  $C_{min}$  and the gradients,  $\frac{\partial C}{\partial W}$ , successively bringing the predicted values closer to the target values by updating the network parameters.

Figure 2.2 Convex loss function and gradient descent.

#### 2.1.3 Classification

The previous section introduced an approach that can be used for regression as-is. However, in the case of a multi-class classification problem, the output layer of the network has multiple neurons. The output of those neurons are called logits. To evaluate the class associated to the input, each logit will contain the probability of the input being of a particular class. In such a case, the number of output neurons equals the number of classes in the dataset. To assign a class to the prediction, the model applies a softmax function, shown in equation 2.5, that associates each logit to a probability of that logit being of a particular class:

$$\sigma(z_i) = \frac{e^{z_i}}{\sum_{j=1}^{Q} e^{z_j}},$$

(2.5)

where i is the output of the *i*th neuron on the output layer and Q is the number of classes in the dataset.

#### 2.2 Convolutional neural networks

The fully-connected (FC) layers of a neural network perform well at classifications and estimations. However, they lack in their ability to retrieve spatially related information from input features. Convolutional layers introduce filters that can extract information from the input features [15]. A convolutional layer consists of a learnable set of filters.

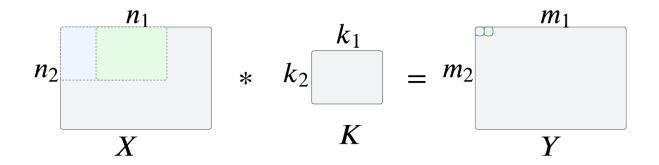

A simple filter is a matrix  $K \in \mathbb{R}^{k_1 \times k_2}$  as shown in Fig. 2.3 in which the set of parameters  $w_i$  are learnable during training.

| $w_0$ | $w_1$ | $w_2$ |

|-------|-------|-------|

| $w_3$ | $w_4$ | $w_5$ |

| $w_6$ | $w_7$ | $w_8$ |

Figure 2.3 Example filter of a CNN.

An output feature map is generated by applying a convolution operation sequentially to the input features while sliding the filter through it. In Fig. 2.4, we can observe this operation

where a convolution is applied on an image X with a filter K producing an output feature map Y. An example of the sliding principle shows a convolution on the blue and green areas of the image generating a blue and a green output, respectively.

Figure 2.4 Convolution operation on a two dimensional input and a two dimensional filter.

In practice,  $n_1 = n_2$ ,  $m_1 = m_2$  and  $k_1 = k_2$ . Dumoulin et al. found that in this case, the output size  $m_1, m_2$  can be calculated using equation (2.6) [16]:

$$m_1 = \lfloor \frac{n_1 + 2 \times padding - k_1}{stride} \rfloor + 1, \qquad (2.6)$$

where the *padding* is the amount of pixels (rows and columns) added to the input image and the *stride* is the amount of pixels by which to move the kernel K in horizontal and vertical directions during the convolution operation. In Fig. 2.4, *padding* = 0 and *stride* is about half the kernel size. Generally, the inputs and outputs of a convolutional layer and the filter are three dimensional tensors with the third dimension representing different channels.

#### 2.3 Binarized neural networks

In a binarized neural network (BNN), we reduce the available range of values to only 2 bits for the weight matrices and the neuron activations.

There are mainly two approaches to binarize the weight matrices: stochastic and deterministic. In stochastic binarization, the binary value of a floating point input is expressed as a probability density function. This usually leads to better accuracy of the network predictions. However, it requires more resources during training and therefore deterministic binarization

$$W_b = \begin{cases} -1, & \text{if } W_r < 0\\ 1, & \text{otherwise} \end{cases}$$

(2.7)

$W_r$  and  $W_b$  are the real and binary weights, respectively.

To binarize the activations, the hard-tanh activation is used. On an embedded device, switching the representation of -1 to zero helps in applying multiplications using only Boolean operations [17]. More specifically, they can be performed using XNOR operations as shown in Table 2.1.

| $x_1$ | $x_2$ | Z     |

|-------|-------|-------|

| 0(-1) | 0(-1) | 1     |

| 0(-1) | 1     | 0(-1) |

| 1     | 0(-1) | 0(-1) |

| 1     | 1     | 1     |

Table 2.1 XNOR operation

Furthermore, a pop-count operation is used to count the number of ones in a bit sequence replacing the accumulation. Courbariaux et al. also demonstrated that batch-normalization was costly in terms of operation on an embedded device [18]. They developed a new approach that relies on bit-shifts to compute the batch normalization.

Finally, the computation of the gradient w.r.t. the network parameters need to take binarization into account. The same applies to the activations. To avoid having most of the gradients being equal to zero by derivating the sign function, Courbariaux et al. proposed to use a straight through estimator shown in equation (2.8) [18]:

$$\frac{\partial C}{\partial W_r} = \frac{\partial C}{\partial W_b}.$$

(2.8)

Equation (2.8) effectively bypasses the sign function while computing the gradient of the loss function C. For activations, the same straight-through estimator is used, furthermore the saturating effect is taken into account:

$$\frac{\partial C}{\partial a_r} = \frac{\partial C}{\partial a_b} \times \mathbb{1}_{|a| \le 1},\tag{2.9}$$

where 1 is the indicator function. It is important to note that the gradients are then applied on the real-valued weights which are kept in memory and binarized in the forward pass.

#### 2.4 Decision trees

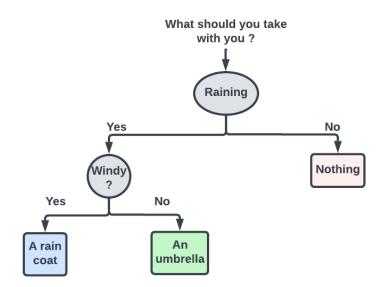

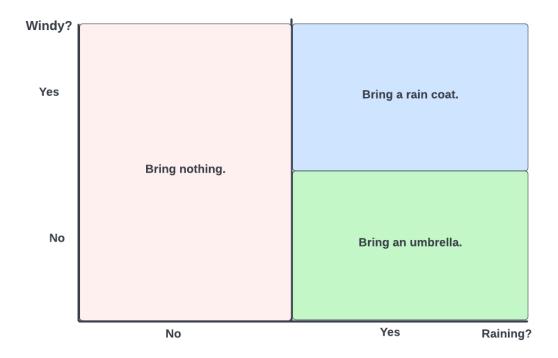

A decision tree is a graphical learning model in which alternative outcomes are visualizable. In this model, a hierarchical graph is build based on the importance of the input features. The advantage of such a model is that it is easily interpretable. To classify an input, a decision tree partitions the feature space into classes as shown in Fig. 2.5.

A popular algorithm for training decision trees is C4-5 [19]. It builds a decision tree by sequentially selecting input features based on the information gain they provide to the model. However, the computational feasibility of such a decision tree is subject to the dimensionality of the input feature space since the depth of a tree is directly proportional to it [20]. To alleviate this issue and diminish the high variance deeper decision trees suffer from, ensemble learning techniques are explored. There exist three types of ensemble learning techniques: bagging, boosting and stacking [20]. For the purpose of this thesis, we explore bagging with random forests and boosting with Adaboost.

#### 2.4.1 Bagging: Random forests

When building a classifier H(x) for a data-set D that has a certain distribution, P, a problem we may encounter is that we build a classifier that instead of generalizing from the data-set, learns the data-set. This causes high variance in the estimation of unseen data-points. The model overfits. To mitigate this issue, by sampling the original data-set with replacement we can build multiple data-sets  $D_i$ , each having their own independent classifier  $h_i(x)$ . Following this process, we re-combine the multiple weaker classifiers into a strong classifier by averaging their estimations.

$$H(x) = \frac{1}{m} \sum_{i=1}^{m} h_i(x)$$

(2.10)

Random forests are a type of bagging algorithm that use decision trees as the weak classifiers. The decision trees are restricted to use k features selected at random to build the trees, which restricts the trees to a specific depth.

#### 2.4.2 Boosting: Adaboost

Boosting is another technique to combine multiple weak learners to build a strong leaner for classification. The general boosting classifier is defined by equation 2.11:

$$H(x) = \sum_{t=1}^{T} \alpha_t h_t(x),$$

(2.11)

Figure 2.5 Regular decision tree and input features space partitioning.

where  $h_t(x)$  is a weak classifier and  $\alpha_t$  an adaptable step-size.

The general idea is to aggregate multiple classifiers that each emphasise on the classification of certain examples of the data-set and neglect others. The classifiers are built sequentially and not in parallel like random forest.

During training, Adaboost builds a strong classifier by iterativally aggregating weaker classifiers. The weaker classifiers are selected based on the output accuracy of the current classifier at time t. Each training example is associated with a weight and each weak classifier is selected based on these weights.

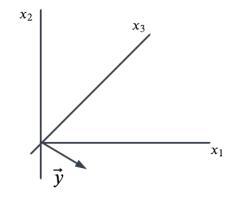

The classification outputs is represented as a vector in the input example space (rather than the input feature space). As an example, imagine a data-set  $(x_i, y_i)$  with a single feature  $x_i$ and 3 examples:  $\{(x_1, y_1 = 1), (x_2, y_2 = -1), (x_3, y_3 = 1)\}$ , then the vector  $\vec{y} = [y_1, y_2, y_3]$ represents the classified data-set. This is shown in Fig. 2.6.

Figure 2.6 Example space.

The prediction vector  $\vec{h}_t(x)$  is the vector containing the predictions of every single example  $[h(x_1), h(x_2), h(x_3)]$ . Note that  $y_i \in \{-1, +1\}$  and  $h(x_i) \in \{-1, +1\}$ .

The loss function in Adaboost is the exponential loss as seen in equation (2.12):

$$l(H) = \sum_{i} e^{-y_i H_i(x_i)}.$$

(2.12)

By minimizing this loss, we move our predicted vector closer to the target. Since this is a sequential process and H is gradually stronger, we define a step size to move towards the minimum of the loss function at each iteration, we compute the next optimal classifier, update the example weights. These are detailed in the following sub-sections.

## Next optimal classifier

To find the next best classifier  $h_t(x)$  that is added to our sum of classifiers as defined in equation (2.11), we solve the following objective function:

$$h_t = \underset{h \in \Psi}{\operatorname{arg\,min}} (l(H + \alpha h)), \tag{2.13}$$

where l is the exponential loss shown in equation (2.12), and  $\Psi$  is the set of all valid decision trees, defined by some properties of our model. Using a Taylor approximation, we can solve equation (2.13) and find that the next best classifier is given by equation (2.14):

$$h_t = \underset{h \in \Psi}{\operatorname{arg\,min}} (\sum_{h(x_i) \neq y_i} w_i), \qquad (2.14)$$

where:

$$w_i = \frac{e^{-y_i H_i(x_i)}}{\sum_j e^{-y_j H_j(x_j)}}.$$

(2.15)

Thus, the next best classifier is the classifier that minimizes the weighted error of the training examples.

#### Step size

To compute the optimal step size  $\alpha_t$ , we solve the following objective function:

$$\alpha_t = \underset{\alpha}{\arg\min}(l(H + \alpha h)), \qquad (2.16)$$

which solves to:

$$\alpha_t = \frac{1}{2} ln(\frac{1-\epsilon}{\epsilon}), \qquad (2.17)$$

where:

$$\epsilon = \sum_{h(x_i) \neq y_i} w_i. \tag{2.18}$$

## Weight update

The final step is to update the weights of each example,  $w_i$  under the constraint that  $\sum w_i = 1$ . The weight update rule is a function of the classification error. If an example was classified its weight value is decreased:

$$w_{i}^{t} = \frac{w_{i}^{t-1}e^{-\alpha_{t}}}{2\sqrt{\epsilon(1-\epsilon)}},$$

(2.19)

otherwise it is increased:

$$w_i^t = \frac{w_i^{t-1} e^{\alpha_t}}{2\sqrt{\epsilon(1-\epsilon)}}.$$

(2.20)

#### 2.5 Tensors

A tensor is a concept representing a set of values in a specified vector space. A vector, a matrix and a cube are tensors. However, it becomes useful when referring to spaces that are of dimension higher than three. The dimension of a tensor is called its order and this term will be used in the remainder of the thesis.

#### 2.5.1 Rank of a tensor

The rank of a tensor represents the number of linearly independent vectors that constitute the tensor. The other vectors being linearly dependent on the former.

#### 2.5.2 Tensor-Train format

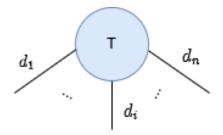

The tensor-train (TT) format is a graphical representation of tensors [21]. It is a convenient notation when working with high order tensors. A tensor  $T \in \mathbb{R}^{d_1 \times \ldots \times d_n}$  is represented by a circle with n legs as shown in Fig. 2.7. A scalar is simply represented by a circle.

Figure 2.7 Tensor-Train format of a n dimensional tensor.

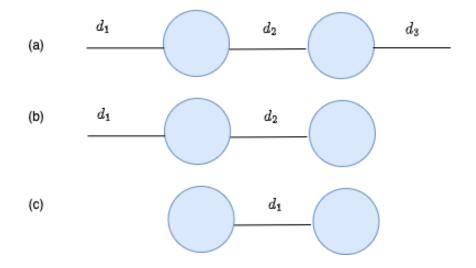

In Fig. 2.8, we can observe common tensor products represented in their tt format where:

- (a) is the product of two matrices.

- (b) is the product of a matrix and a vector.

- (c) is the inner product of two vectors.

Figure 2.8 Common matrix and vector multiplications in the Tensor-Train format.

## 2.6 Summary

In this chapter, we have introduced the basic concepts that are necessary for the rest of the thesis to be well understood. We have talked about NNs, CNNs and BNNs. We also introduced decision trees with an emphasis on two common learning methods, bagging and boosting. Finally, we talked about tensors. In the following chapter, we build on top of these basic concepts to present a thorough review of the SOTA in DNN optimization.

#### CHAPTER 3 LITERATURE REVIEW

Deep Neural Networks (DNNs) are versatile in their requirements across applications. Depending on the desired outcome, their accuracy, latency, throughput, energy and power requirements diverge significantly. With several approaches taken to optimize DNNs, three main optimization types have emerged [22]:

- 1. Model Optimization

- 2. System Optimization

- 3. Joint Model and System Optimization

In the case of model optimization, improvement is made at the algorithmic level of DNNs. They include but are not limited to quantization, pruning and low-rank factorization. The algorithmic modifications can either be hardware aware, meaning that the algorithm is tied to the underlying hardware or hardware agnostic. System optimization works at the deployment level by adapting DNNs to the entire system. When working at this level, the factors taken into consideration are the operating system preemption, the device-server load distribution, and other system dependent variables such as voltage level and energy consumption. These considerations can be statically or dynamically considered to modify the execution of the inference process. To dynamically improve system level processes, one interesting approach is to include an early exit mechanism that outputs a neural network's (NN) prediction and terminates the process once the confidence on the output accuracy is satisfying enough. The junction of these two approaches incorporates model level optimizations and system level optimizations by combining some of the previously mentioned techniques.

In the present work, both of these optimizations types are used making our approach a joint model and system optimization type. In the following sections, different optimization methods that move us steps towards the efficient execution of DNN algorithms on embedded devices are presented.

#### 3.1 Pruning

Pruning compresses and optimizes a neural network inference and training process by removing a set of parameters. Consider a NN model characterized by function  $f(x;\theta)$ , where  $\theta$  represents all the parameters of the model. Applying a filter  $M \in \{0,1\}^{|\theta|}$  to the model's parameters results in a pruned network such that the model is now defined as  $f(x; M \odot \theta)$  which denotes a sparse network [23]. The induced sparsity can either be structured or unstructured. Other distinctive characteristics of pruning algorithms in the literature involve the scoring schemes used to decide which parameters to remove, the number of times the pruning is applied throughout the training process and the way fine tuning is applied in between each pruning iteration.

#### 3.1.1 Structured and unstructured pruning

Unstructured pruning works by removing individual weights from neurons by zeroing them out such that the filter has no inherent structure. Although unstructured pruning ends up reducing memory usage, it leads to a sparse representation of the NN parameters which ultimately does not reduce computation power as the number of multiply and accumulate (MACs) operations remains the same [23]. Another problem with unstructured pruning is the indexing of non-zero parameters that is involved to store the networks parameters after training. Thus, an impact is observed on the computation and memory complexity since all the stored weights now have the index of the parameter in the sparse matrix as a second parameter. The fetching of a single weight then involves a two step operation where the index is fetched followed by the actual parameter [24].

Structured pruning reduces both memory and computation footprint on existing hardware [23]. Instead of removing specific weights, different sets of spatially connected weights, such as all the parameters associated to a specific neuron or a complete filter in a convolutional layer [25] are discarded such that the resulting parameters matrices are structured and the operations can be done using commonly available hardware. However, the compression ratio achieved by unstructured pruning tends to be higher than structured pruning [24].

#### 3.1.2 One-Shot pruning, iterative pruning, fine-tuning

Pruning algorithms can either be One-Shot or iterative. The lottery ticket hypothesis [26] describes an approach to find a pruned network from an initial dense network. Their assumption is that since a pruned network is a smaller version of a larger network, there should be an existing sub-network constructed from the original network that when trained separately should have the same accuracy. Although, the reported results stem from an iterative process, their algorithm describes a One-Shot approach. [27] develop a one-shot pruning scheme that solves an induced structured sparsity problem with a Half-Space Projected Gradient approach. Iterative approaches are more commonly found in the literature. The training of a pruned network is done by gradually compressing the network after each iteration at a

certain scheduling rate [23]. To obtain the desired sparsity, the network is first trained then pruned and retrained again to recover the accuracy lost by pruning through a fine-tuning process.

However, the authors of [9] argue that, for structured pruning, a single iteration (One-Shot) has the same outcome as the iterative approach.

## 3.1.3 Scoring

Different scoring schemes determine the parameters to remove. For structured pruning, the importance of the layer-wise parameters or channel-wise parameters is determined by the magnitude of the 11 or 12 regularizers. Some methods consider the scoring of parameters locally, while others apply it globally without regards to where they reside relative to each other [23].

## 3.2 Quantization

In Deep Learning, data values (inputs, outputs, activations, gradients, and weights) are usually represented using 32-bit floating point numbers. Quantization was introduced as a means to reduce the size of a network by replacing the traditional floating-point representation of data by other representation strategies that would allow for smaller data sizes. In the literature, 16-bit, 8-bit, 4-bit, 3-bit quantization schemes have been explored [28] [29] [30] [31]. An extreme form of quantization where all values are restricted to binary values has also gained tremendous popularity in recent years [12] [32] [33] [34].

An adequate classification of quantization schemes can be done based on the following factors:

1. Quantization-Aware Training And Post-Training Quantization:

Quantization-Aware training involves quantizing a model at training time while posttraining quantization quantizes pre-trained models [35]. One of the advantages of the later is that it allows for data-free optimization [29] [36] [37]. Depending on the setting, training data might not be available to the model optimizer (i.e. a pre-trained model on cloud). Quantization-Aware training usually renders better performance since the model can be fine-tuned and its hyper-parameters optimized while applying quantization [35].

2. Fixed-Point, Vector And Product Quantization:

In fixed-point precision quantization, every single data point is quantized to a fixedpoint representation, either using scalar values or fixed-point floating point values [30]. Vector quantization on the other hand will derive a vector of values and assign every single data point to their closest representative in that vector using k-means algorithms [38] or other clustering strategies [39] [40]. Product quantization is done by applying vector quantization after partitioning the input matrix into multiple sub-matrices [36] [38]. While most quantization approaches try to minimize the following objective function

$$||W - \hat{W}||_2^2 = \sum_j ||w_j - q(w_j)||_2^2, \qquad (3.1)$$

which minimizes the error on the quantized data with regards to the original data, Stock et al. apply a per-layer product quantization where they minimize the error on the output of the layer after quantization instead by minimizing the following objective function [36]:

$$||y - \hat{y}||_2^2 = \sum_j ||x \times (w_j - q(w_j))||_2^2$$

(3.2)

Stock et al. use knowledge distillation techniques (section 3.3) on a trained network to iteratively quantize each layer independently before quantizing the entire network for a final calibration of the generated quantization vectors (codebooks).

3. Single-Precision and Mixed-Precision Quantization:

Single-precision quantization methods apply the same quantization strategy to all the data points whereas mixed-precision quantization allows for different schemes depending on a per data-point basis [35]. The mixed-precision approach is applied on a per layer or a per channel basis [35] [41]. Nagel et al. adequately explain that mixed-precision quantization methods usually have better performance because they account for the range of the data to compress [37]. As an example, they explain that a layer may have its weights in the range [-0.5, 0.5] while another one may lay in the range [-128,128]. If 8-bit quantization is similarly applied on these ranges, the weights in the former may mostly be assigned a value of zero and thus the network may lose an entire layer's information.

In the above classification of quantization methods, a focus was made on weight quantization. However, quantization is not limited to the weights of neural network. Generally, quantization can be applied on weights, activations and gradients or a combination of them [28]. Applying quantization on weights or activations reduces memory footprint. When applied on weights and activations in the same network, quantization leads to a reduction of computation with the introduction of fixed-point multiplications and additions [28] [30]. Formerly, quantizing was done to optimize the forward propagation of DNNs but recently gradients have also been undergoing this process to optimize training, more specifically, in the case of distributed training on multiple machines [28].

#### 3.3 Knowledge distillation

A popular approach to compressing DNNs is knowledge distillation (KD), where a pair of models work in tandem to transfer knowledge from one, the teacher network, to another, the student network. Two main components play a crucial role in knowledge distillation: the representation of knowledge and the distillation strategy [42].

#### 3.3.1 Knowledge representation

In a NN, knowledge is contained inside the output of the entire model, the outputs of each layer of the model, and the parameters of the model. Gou et al. distinguish three types of knowledge depending on where it is located in a NN: response-based knowledge, feature-based knowledge and relation-based knowledge [42].

A response-based KD model uses the response of the entire network (logits) as information used by the student network to evaluate the gradient of the loss as shown in (3.3) [43]:

$$\frac{\partial C}{\partial z_i} = \frac{1}{T}(q_i - p_i), \qquad (3.3)$$

where  $z_i$  is the *ith* logit of the student network, T is a temperature factor (usually 1),  $q_i$  and  $p_i$  are the logits associated with the *ith* class by a the student network and the teacher network, respectively. One can also use the popular Kullback–Leibler (KL) divergence [44]:

$$C = (1 - \lambda)C_{st} - \lambda C_{KL}, \qquad (3.4)$$

where  $\lambda$  is an hyper-parameter that serves as a selective trade-off between the student's loss and the KL divergence loss,  $C_{st}$  is the student loss and  $C_{KL}$  is the KL divergence loss.

• A feature-based KD model uses the intermediate representation of knowledge contained in the output in the hidden layers of a teacher network to train a student network [42]. Particularly, Romero et al. develop a hint-based model where they extract intermediate layer knowledge from the teacher network described as hints to train a student network's guided layers [45]. Then, they recursively train the student network from the first layer up to the guided layer. • Finally, a relation-based KD algorithm models the relation between pairs of feature maps in a network as a flow of the solution procedure (FSP) matrix where values in the matrix can be computed using equation (3.5) [42] [46]:

$$G_{i,j}(x;W) = \sum_{i} \sum_{j} \frac{F_i^1(x;W) \times F_j^2(x;W)}{h \times w},$$

(3.5)

where  $F^1$  and  $F^2$  are the input and output feature maps, respectively, *i* and *j* are the index in the input and output feature maps, respectively and *h* and *w* are the width and height of the feature maps. Furthermore, by representing the relation between feature maps as a correlation matrix, Lee et al. use singular value decomposition (SVD) to capture latent information in the relationship between the layers present in the FSP matrix [47]. Following that information gathering, the student network is trained to capture the knowledge present in the FSP matrix.

## 3.3.2 Distillation strategy

Gou et al. identify three types of distillation strategies: the offline, online, and self-distillation strategies [42]. They categorize self-distillation as a specialized type of online strategy. The KD models previously described are offline strategies. However, for a larger teacher architecture, offline training is not always convenient since the potential consequent training process of the teacher network is still necessary. Furthermore, Mirzadeh et al. empirically validate that a larger teacher model does not always lead to a better performing student model [44]. They introduce an online training strategy that uses a teacher assistant model that is of a relatively bigger size than the target student network to close the gap in network between a pre-trained teacher and the student network. Zhang et al. introduced a novel type of ensemble learning techniques that leverages the sharing of knowledge between an ensemble of models [48].

Going further, in 2019, Zhang et al. propose a self-distillation strategy where a network passes knowledge in between its own layers [42] [49]. This is done by introducing classifiers at the output of target layers such that the each layer as a teacher and a student in an online training fashion while developing a response-based KD model.

#### 3.4 Tensor-Train decomposition and tensor factorization

Tensor-Train decomposition, first described by Oseledets et al., is one of many tensor factorization techniques [50]. TT decomposition factorizes a high-order tensor of dimension N into N low-order matrices. More precisely, a tensor  $B \in \mathbb{R}^{d_1 \times d_2 \times \cdots \times d_N}$  is factorized into N core tensors. In Fig. 3.1, we can visualize the tensor-train format (as described in Section 2.5.2) of N tensors resulting from the decomposition of a tensor of order N.

Figure 3.1 Tensor network representation of TT decomposition, G tensors are the cores while  $r_n$  indicate TT ranks.

Each tensor  $G_i$  is composed of matrices of dimensions  $r_{i-1} \times r_i$ , where  $r_0 = r_N = 1$ . Therefore, the first and last core tensors are two dimensional tensors. The total number of matrices for a tensor  $G_i$  is given by the value of the *i*th dimension where  $i_n \in [1 \dots d_n]$ . The tensors  $G_i$ that are not at the extremeties are three dimensional tensors and the ones at the extremeties are two dimensional tensors. Finally, an element of B can be computed from core tensors as follows:

$$W(i_1, i_2, \dots, i_N) = \underbrace{G_1[i_1]}_{r_0 \times r_1} \times \underbrace{G_2[i_2]}_{r_1 \times r_2} \times \dots \times \underbrace{G_N[i_N]}_{r_{N-1} \times r_N}$$

(3.6)

The collection of ranks  $(r_1, \ldots, r_N)$  is called the TT-rank of the tensor. TT-ranks determine the number of parameters and by careful selection, the original tensor can be expressed in its compressed format. The TT-rank is subject to the following restriction:  $r_n \leq \min(d1 \ldots d_n, d_{n+1} \ldots d_N)$ . The low-rank approximation of the original tensor can then be performed by multiplying these low-rank tensors. TT-decomposition reduces the total number of parameters in the original tensor by exploiting correlations in the eigenspace. By thoughtfully selecting the ranks  $r_n$  of the resulting core tensors, we can control the final compression ratio.

Other decomposition techniques provide varying degrees of compression with different tradeoffs. In Table 3.1, TT-decomposition is compared to two popular decomposition techniques: CP-decomposition [51] and Tucker decomposition [52].

|                         | CP-Decomposition     | Tucker-<br>Decomposition                    | TT-Decomposition                     |

|-------------------------|----------------------|---------------------------------------------|--------------------------------------|

| Computing the rank      | NP-Hard              | Polynomial                                  | Polynomial                           |

| Low-Rank Approx.        | NP-Hard              | Np-Hard but<br>HOSVD is<br>quasi-optimal    | quasi-optimal                        |

| Set of low-rank tensors | Not closed           | Closed                                      | Closed                               |

| Number of Parameters    | $\sum_{n=1}^{N} (R)$ | $\frac{R_1R_2R_N +}{\sum_{n=1}^N (d_nR_n)}$ | $\mathcal{O}(R^2\sum_{n=1}^N (d_n))$ |

| Unicity                 | True                 | False                                       | False                                |

Table 3.1 Side-by-side comparison of different tensor factorization methods.

## 3.5 LUT-based neural networks

Portions of this section are excerpted from our article presented at NEWCAS 2022 [53], 0 2022 IEEE.

Several hardware architectures have adapted the original works of BNNs for a faster and more energy efficient inference [10]. Xilinx introduced FINN [17] that integrates multiple approaches to map binarized neural networks to FPGA more efficiently. In particular, the authors of FINN altered the original BNN inference flow by replacing multiply and accumulate (MAC) operations with XNOR operations and a pop-count operation [34] [54]. Since all the values are binary, instead of accumulating over an entire bitstring that represents a NN layer's response, only the number of ones need to be counted. Pop-count halves the total number of LUTs required. Furthermore, the computation of the batch-norm step was changed to a simple threshold comparison and max-pooling was replaced by a Boolean OR.

Although these algorithms speed up the original algorithm execution time on the FPGA architecture, the intrinsic BNN architecture is not modified. Because the basic building-block of FPGAs are LUTs, a more FPGA-specific type of BNNs are LUTs based neural networks. Inherently, these components can evaluate any Boolean function. Although different LUT size exist, the common 6 input to 1 output LUTs is used as a reference throughout the rest of this section. To leverage the LUTs present in FPGAs, researchers have tried to develop algorithms that would exclusively use LUTs in the inference phase of DNNs.

Nazemi et al. (NullaNet) [14] and Umuroglu et al. (LogicNets) [55] have taken two similar approaches where they implement complete neural networks using only LUTs. They trim a regular neural network by using quantization and reduced fan-in approaches to achieve the ideal case where 6-input neurons produce single outputs. Depending on the requirements,

they can use more than a single LUT per neuron. Since the number of utilized LUTs is exponential with respect to the number of inputs, as shown in equation (3.7) [55]:

$$LUTCost(X,Y) = \frac{Y}{3} \times (2^{X-4} - (-1)^X), \qquad (3.7)$$

where X is the number inputs and Y the number of outputs. Using equation (3.7), it can be observed that six-bit inputs and a single output bit is convenient as this configuration renders exactly one LUT used per neuron.

However when using input-output mappings other than six inputs to one output, the required number of LUTs can be relatively high as the equation suggests. NullaNet uses "don't cares" to ignore input combinations that are not relevant based on the data-set while LogicNets optimizes the architecture by building neural networks that only have the desired input-output mapping. To achieve this, the authors randomly select input connections from previous layers in quantized neural networks. Wang et al. have taken a similar approach to utilize LUT boolean functions as much as possible [56]. However, they differ from NullaNet and LogicNets because they still have data-paths for various components of their architecture (i.e. accumulators).

#### 3.5.1 PoET-BiN