**Titre:** Optimisation de la compilation de déparseurs pour processeurs réseau implémentés sur FPGA

Title: [Optimisation de la compilation de déparseurs pour processeurs réseau implémentés sur FPGA](#)

**Auteur:** Thomas Luinaud

Author: [Thomas Luinaud](#)

**Date:** 2022

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Luinaud, T. (2022). Optimisation de la compilation de déparseurs pour processeurs réseau implémentés sur FPGA [Thèse de doctorat, Polytechnique Montréal]. PolyPublie. <https://publications.polymtl.ca/10357/>

Citation: [Luinaud, T. \(2022\). Optimisation de la compilation de déparseurs pour processeurs réseau implémentés sur FPGA \[Thèse de doctorat, Polytechnique Montréal\]. PolyPublie. https://publications.polymtl.ca/10357/](#)

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/10357/>

PolyPublie URL: [https://publications.polymtl.ca/10357/](#)

**Directeurs de recherche:** J. M. Pierre Langlois, & Yvon Savaria

Advisors: [J. M. Pierre Langlois](#), [Yvon Savaria](#)

**Programme:** Génie informatique

Program: [Génie informatique](#)

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

**Optimisation de la compilation de déparseurs

pour processeurs réseau implémentés sur FPGA**

**THOMAS LUINAUD**

Département de génie informatique et génie logiciel

Thèse présentée en vue de l'obtention du diplôme de *Philosophiæ Doctor*

Génie informatique

Mai 2022

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

Cette thèse intitulée :

**Optimisation de la compilation de déparseurs

pour processeurs réseau implémentés sur FPGA**

présentée par **Thomas LUINAUD**

en vue de l'obtention du diplôme de *Philosophiæ Doctor*

a été dûment acceptée par le jury d'examen constitué de :

**Samuel PIERRE**, président

**Pierre LANGLOIS**, membre et directeur de recherche

**Yvon SAVARIA**, membre et codirecteur de recherche

**Guy BOIS**, membre

**Mohamed-Faten ZHANI**, membre externe

## DÉDICACE

*À mes grands-parents, à mes parents,

à mon frère, à mes amis

et à mon amoureuse.*

## REMERCIEMENTS

Je tiens tout d'abord à remercier mon directeur de recherche, Pierre Langlois, et mon codirecteur, Yvon Savaria, qui m'ont accompagné tout au long de la réalisation de cette thèse. Je voudrais notamment les remercier pour l'encadrement, les conseils reçus au cours de ce doctorat ainsi que le soutien sans lequel ce manuscrit n'aurait pas vu le jour. Aussi un merci particulier à Pierre pour s'être toujours rendu disponible.

Merci à Kaloom, et particulièrement à Laurent Marchand, Ludovic Béliveau et Bochra Boughzala pour la confiance qu'ils nous ont accordés ainsi que l'accès à un environnement stimulant pour nous aider à mener nos recherches. Je voudrais également remercier Normand Bélanger pour ses conseils et les échanges aussi bien personnels que techniques que nous avons eux, mais aussi pour son soutien. Un merci particulier à Martine Bellaïche pour m'avoir écouté et encouragé pendant ces années de doctorat.

Je veux exprimer toute mon amitié à mes collègues de laboratoires qui m'ont soutenu durant la réalisation de ce doctorat. Merci Bachir, Charles, Imad, Erika, Mickaël, Vincent et Patrick. Un énorme merci à Thibaut et Jeferson pour m'avoir encouragé et soutenu au cours de cette expérience. Je suis fier de ce que nous avons accompli ensemble. J'espère que nous continuerons à partager de bons moments ensemble.

Un énorme merci à ma famille qui m'a soutenu tout au long de ce parcours malgré la distance. Un merci particulier à mon frère qui est toujours là quand il y a besoin. Un grand merci à mes parents pour m'avoir toujours soutenu et encouragé dans mes projets. Un grand merci à Sylvie, Stephen et Danielle pour votre soutien.

Un grand merci à tous mes ami.e.s. Merci à Paul de m'avoir aidé à garder le moral. Merci à Sylvain, Élodie, Yann, Adrien, Mélissa et Johanna pour toutes ces activités et les moments d'évasion passés ensemble et pour votre soutien.

Finalement un énorme merci à Laurie. Je te remercie particulièrement pour tout ton soutien au cours de ces années de doctorat . Tu m'as encouragé, motivé tout au long de ce projet, et tu as mis de côté certains de tes projets. Pour tout ça merci !

## RÉSUMÉ

Les réseaux de télécommunication ont vu leur taille, leur complexité et leur débit augmenter de façon très importante ces dernières années. Pour suivre cette évolution, les commutateurs, responsables d'aiguiller les paquets, ont perdu en flexibilité ce qui a rendu l'intégration de nouveaux protocoles plus compliquée. Afin de redonner de la flexibilité aux réseaux, le paradigme du réseau défini par logiciel — *Software Defined Networking* (SDN) a été introduit. Avec le SDN, le plan des données et le plan de contrôle sont séparés et peuvent donc être modifiés de manière indépendante. Récemment, afin de rendre le plan des données programmables, l'architecture de commutateur indépendante des protocoles — *Protocol Independent Switch Architecture* (PISA) a été introduite avec le langage P4 permettant de la programmer. Dans cette thèse, nous nous intéressons à l'optimisation de la compilation d'applications décrites dans le langage P4 en vue de leur implémentation sur des réseaux prédiffusés programmables — *Field Programmable Gate Array* (FPGA).

Tout d'abord, nous cherchons à définir les limites des FPGA pour l'implémentation d'applications décrites avec le langage P4. Pour cela, nous proposons une évaluation des différents éléments composant l'architecture PISA, et des pistes de travail afin d'améliorer l'implémentation de plans des données sur FPGA. Les résultats de notre évaluation montrent que la microarchitecture actuelle des FPGA limite l'implémentation de certains types de comparaisons ainsi que le débit maximum qui peut être atteint. Également, nos résultats montrent que l'implémentation du déparseur, responsable de générer le paquet à émettre, peut être améliorée.

À la suite de notre analyse de l'implémentation de programmes P4 sur FPGA, nous avons identifié deux éléments limitant les implementations actuelles du déparseur. D'une part, le graphe de déparsage généré depuis P4 est trop séquentiel. D'autre part, les architectures de déparseurs ne tirent pas suffisamment avantage de la structure interne des FPGA.

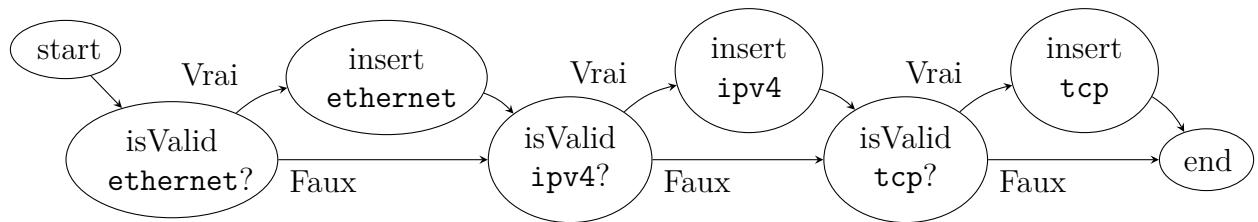

Pour augmenter le parallélisme exprimé par le graphe de déparsage, nous proposons d'effectuer une fermeture transitive du graphe. Cette transformation permet d'exposer le parallélisme pour l'évaluation des conditions de transition entre les sommets du graphe.

Avec la transformation du graphe de déparsage, nous proposons une nouvelle architecture de déparseur générée depuis le graphe. L'architecture proposée maximise l'utilisation de connexions fixes afin de tirer avantage de la capacité de reconfiguration du FPGA. Notre approche permet ainsi de générer des déparseurs depuis des programmes P4 utilisant de  $4 \times$  à  $10 \times$  moins de ressources que les travaux précédents.

Afin de réduire le coût d'implémentation de notre nouvelle architecture, nous proposons d'élaguer le graphe de déparsage en effectuant la spécialisation de programmes P4. La spécialisation est effectuée à l'aide de l'évaluation symbolique de certaines variables du programme P4. L'élagage du graphe de déparsage permet de réduire de 50 % l'utilisation de ressources par le déparseur comparé à la première approche proposée.

## ABSTRACT

Computer networks have, in recent years, significantly increased in size, complexity and throughput. To keep up with this evolution, switches, which route network packets, have lost in flexibility, hence making the integration of new protocols more complex. To restore flexibility into the network, the Software Defined Networking (SDN) paradigm has been introduced. With SDN, the data and control planes are separated and can therefore evolve independently. Recently, to bring programmability to the data plane, the Protocol Independent Switch Architecture (PISA) has been proposed alongside the P4 language to program it. In this thesis, we focus on the optimization of the compilation of applications described using the P4 language with regards to their implementation on Field Programmable Gate Arrays (FPGAs).

First of all, we seek to determine the limits of FPGAs concerning the implementation of applications described with the P4 language. For this purpose, we propose an evaluation of the different elements composing the PISA architecture, and avenues to improve implementation of network data planes on FPGA. Our evaluation results demonstrate that the current microarchitecture of FPGAs limits the implementation of certain types of comparisons as well as the maximum achievable throughput. Also, our results indicate that the implementation of the deparser, which generates the packet to be emitted, can be improved.

Resulting from our analysis of the implementation of P4 programs on FPGAs, we have identified two elements limiting current deparser implementations. Firstly, the deparser graph generated from the P4 code is too sequential. Secondly, deparser architectures do not take sufficient advantage of the internal structure of FPGAs.

To increase the parallelism expressed in the deparser graph, we propose to perform a transitive closure on the graph. With this transformation it is possible to expose the parallelism of the transition conditions evaluation between the vertices of the graph.

Along with the transformation of the deparser graph, we propose a new deparser architecture generated from the graph. The proposed architecture maximizes the use of fixed connections in order to take advantage of the reconfiguration capability of the FPGA. Our approach makes it possible to generate deparsers from P4 programs using  $4\times$  to  $10\times$  fewer resources compared to previous work.

In order to reduce the cost of our new architecture, we propose to prune the deparsing graph by performing P4 program specialization. The specialization is carried out by applying

symbolic evaluation on certain variables of the P4 program. Pruning the deparsing graph reduces the deparser resource usage by 50 % compared to the first approach we proposed.

## TABLE DES MATIÈRES

|                                                                             |      |

|-----------------------------------------------------------------------------|------|

| DÉDICACE . . . . .                                                          | iii  |

| REMERCIEMENTS . . . . .                                                     | iv   |

| RÉSUMÉ . . . . .                                                            | v    |

| ABSTRACT . . . . .                                                          | vii  |

| LISTE DES TABLEAUX . . . . .                                                | xii  |

| LISTE DES FIGURES . . . . .                                                 | xiii |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                                  | xiv  |

| <br>CHAPITRE 1 INTRODUCTION . . . . .                                       | 1    |

| 1.1 Contexte . . . . .                                                      | 1    |

| 1.2 Éléments de la problématique . . . . .                                  | 3    |

| 1.3 Objectifs de recherche . . . . .                                        | 5    |

| 1.4 Contributions de cette thèse . . . . .                                  | 5    |

| 1.5 Plan de la thèse . . . . .                                              | 6    |

| <br>CHAPITRE 2 PRÉLIMINAIRES ET REVUE DE LA LITTÉRATURE . . . . .           | 8    |

| 2.1 Le réseau programmable . . . . .                                        | 8    |

| 2.1.1 La programmation du plan de contrôle . . . . .                        | 8    |

| 2.1.2 Les processeurs réseau . . . . .                                      | 9    |

| 2.1.3 Une architecture de commutateur indépendante des protocoles . . . . . | 10   |

| 2.2 Les langages pour les plans des données . . . . .                       | 12   |

| 2.2.1 L'évolution des langages pour le plan des données . . . . .           | 12   |

| 2.2.2 Le langage P4 . . . . .                                               | 13   |

|                                                             |                                                                          |    |

|-------------------------------------------------------------|--------------------------------------------------------------------------|----|

| 2.3                                                         | Les architectures P4 . . . . .                                           | 15 |

| 2.4                                                         | Compilation de P4 . . . . .                                              | 17 |

| 2.4.1                                                       | La structure d'un compilateur P4 . . . . .                               | 17 |

| 2.4.2                                                       | Les cibles pour la compilation de P4 . . . . .                           | 18 |

| 2.4.3                                                       | L'analyse de programmes P4 . . . . .                                     | 20 |

| 2.5                                                         | Conclusion . . . . .                                                     | 21 |

| CHAPITRE 3 IMPLÉMENTER DES PROGRAMMES P4 SUR FPGA . . . . . |                                                                          | 23 |

| 3.1                                                         | Analyse de l'implémentation de PISA sur FPGA . . . . .                   | 23 |

| 3.1.1                                                       | Le parseur de paquets . . . . .                                          | 23 |

| 3.1.2                                                       | Les tables de comparaisons . . . . .                                     | 24 |

| 3.1.3                                                       | Les actions . . . . .                                                    | 27 |

| 3.1.4                                                       | Le déparseur de paquets . . . . .                                        | 28 |

| 3.2                                                         | Évaluation des FPGA comme commutateurs réseaux . . . . .                 | 28 |

| 3.2.1                                                       | Méthodologie d'évaluation du FPGA comme commutateur . . . . .            | 29 |

| 3.2.2                                                       | Évaluation de l'implémentation des différents blocs de PISA . . . . .    | 30 |

| 3.2.3                                                       | Impact de la largeur du bus sur la fréquence d'opération . . . . .       | 31 |

| 3.3                                                         | Les solutions pour améliorer l'implémentation de PISA sur FPGA . . . . . | 32 |

| 3.3.1                                                       | Intégrer de nouveaux blocs aux FPGA . . . . .                            | 33 |

| 3.3.2                                                       | Revoir l'implémentation du déparseur . . . . .                           | 34 |

| CHAPITRE 4 UNE MICROARCHITECTURE DE DÉPARSEUR POUR FPGA . . |                                                                          | 37 |

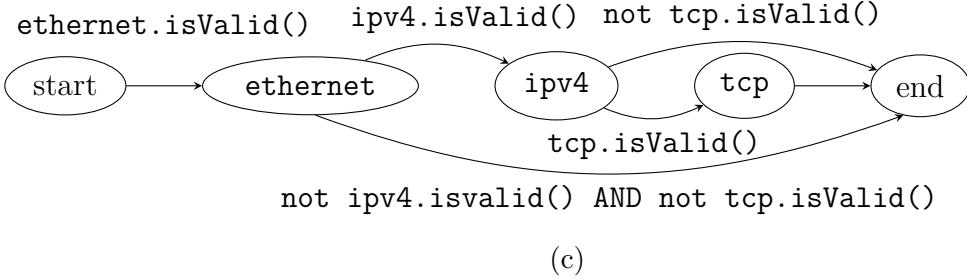

| 4.1                                                         | Le graphe de déparsage . . . . .                                         | 37 |

| 4.1.1                                                       | La représentation P4 d'un déparseur . . . . .                            | 37 |

| 4.1.2                                                       | Transformer le graphe de déparsage . . . . .                             | 38 |

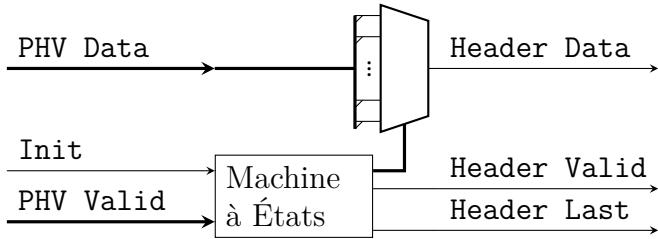

| 4.2                                                         | Les composants de l'architecture . . . . .                               | 40 |

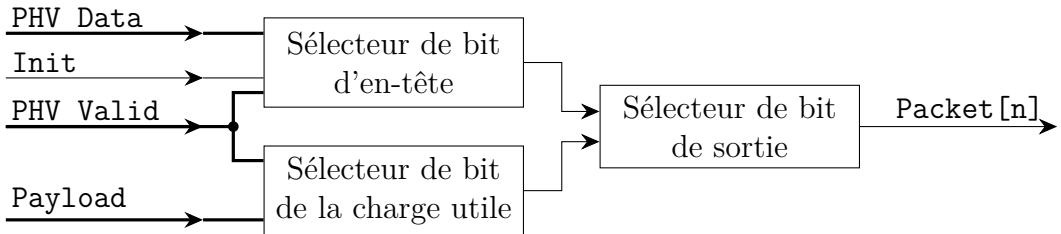

| 4.2.1                                                       | Le sélecteur de bit d'en-tête . . . . .                                  | 41 |

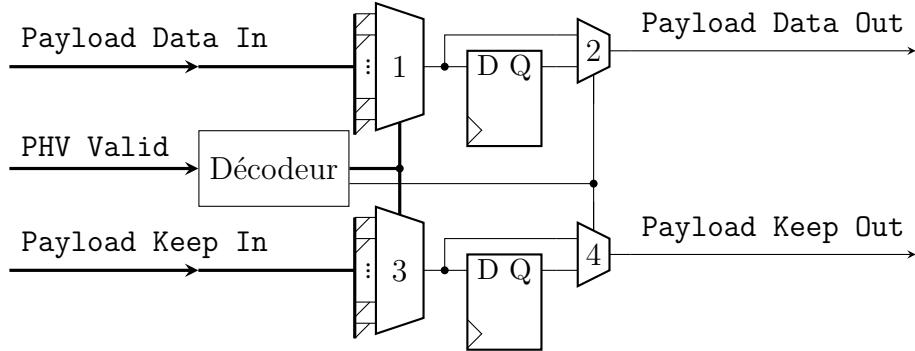

| 4.2.2                                                       | Le sélecteur de bit de la charge utile du paquet . . . . .               | 42 |

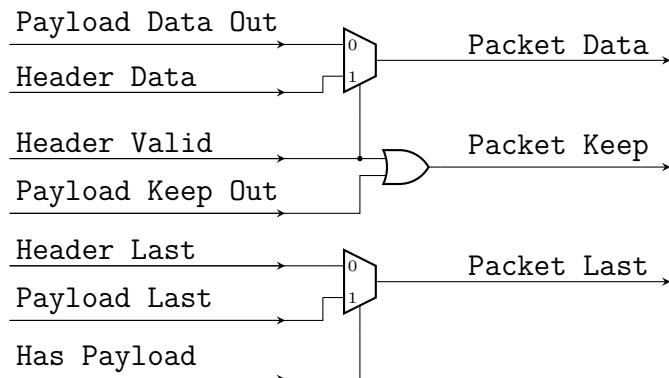

| 4.2.3                                                       | Le sélecteur de bit de sortie . . . . .                                  | 42 |

|                                                                                   |           |

|-----------------------------------------------------------------------------------|-----------|

| 4.3 Générer l'architecture . . . . .                                              | 43        |

| 4.3.1 La décomposition du graphe de déparsage . . . . .                           | 44        |

| 4.3.2 Génération du sélecteur de bit d'en-tête . . . . .                          | 45        |

| 4.3.3 La génération du bloc de sélection de la charge utile . . . . .             | 46        |

| 4.4 Résultats d'implémentation de l'architecture . . . . .                        | 48        |

| 4.4.1 Les paramètres impactant la génération du déparseur . . . . .               | 49        |

| 4.4.2 Tests et résultats . . . . .                                                | 50        |

| <b>CHAPITRE 5 SIMPLIFIER L'IMPLÉMENTATION D'UN DÉPARSEUR . . . . .</b>            | <b>58</b> |

| 5.1 Exemple d'optimisation . . . . .                                              | 58        |

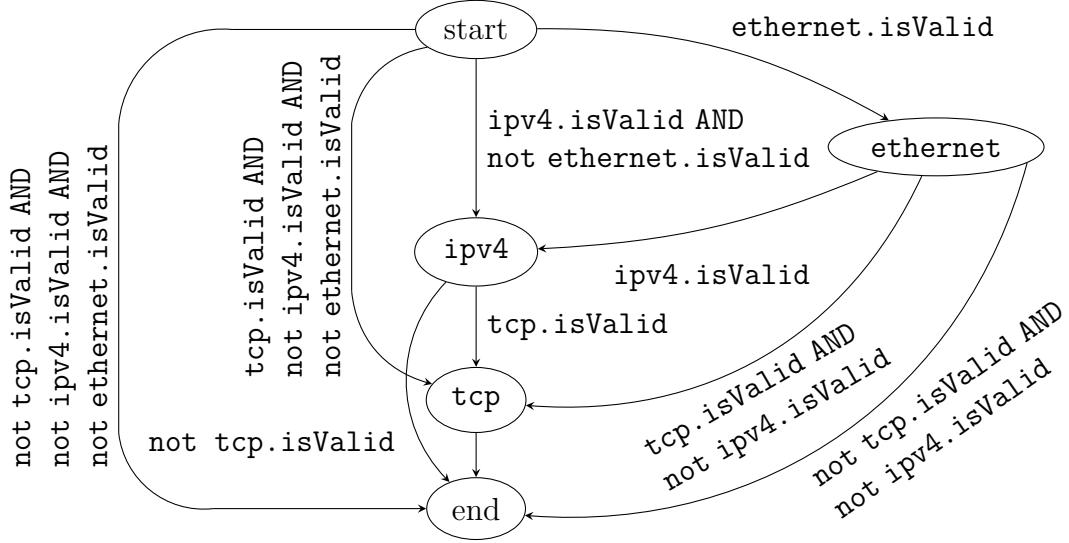

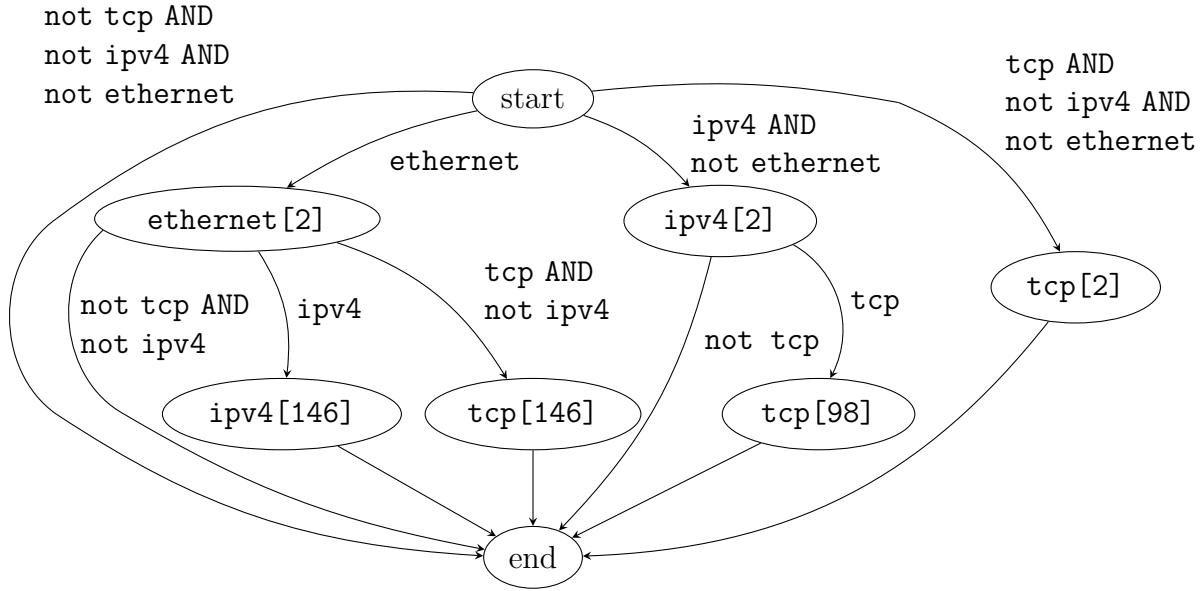

| 5.1.1 Présentation du code de parsage . . . . .                                   | 58        |

| 5.1.2 Un graphe de déparsage réduit valide . . . . .                              | 59        |

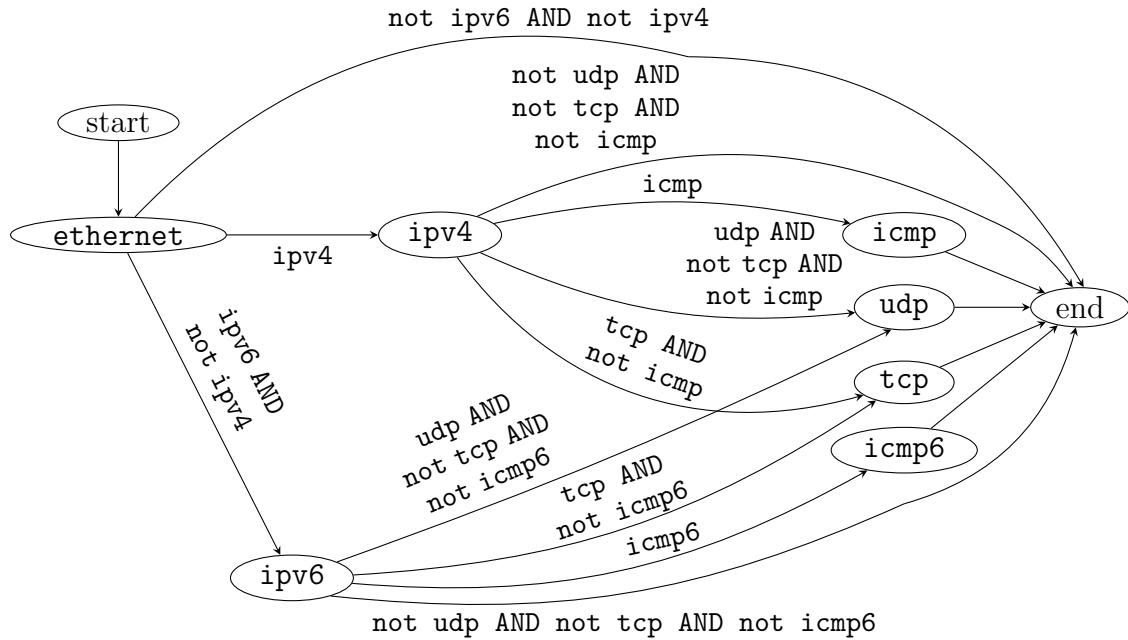

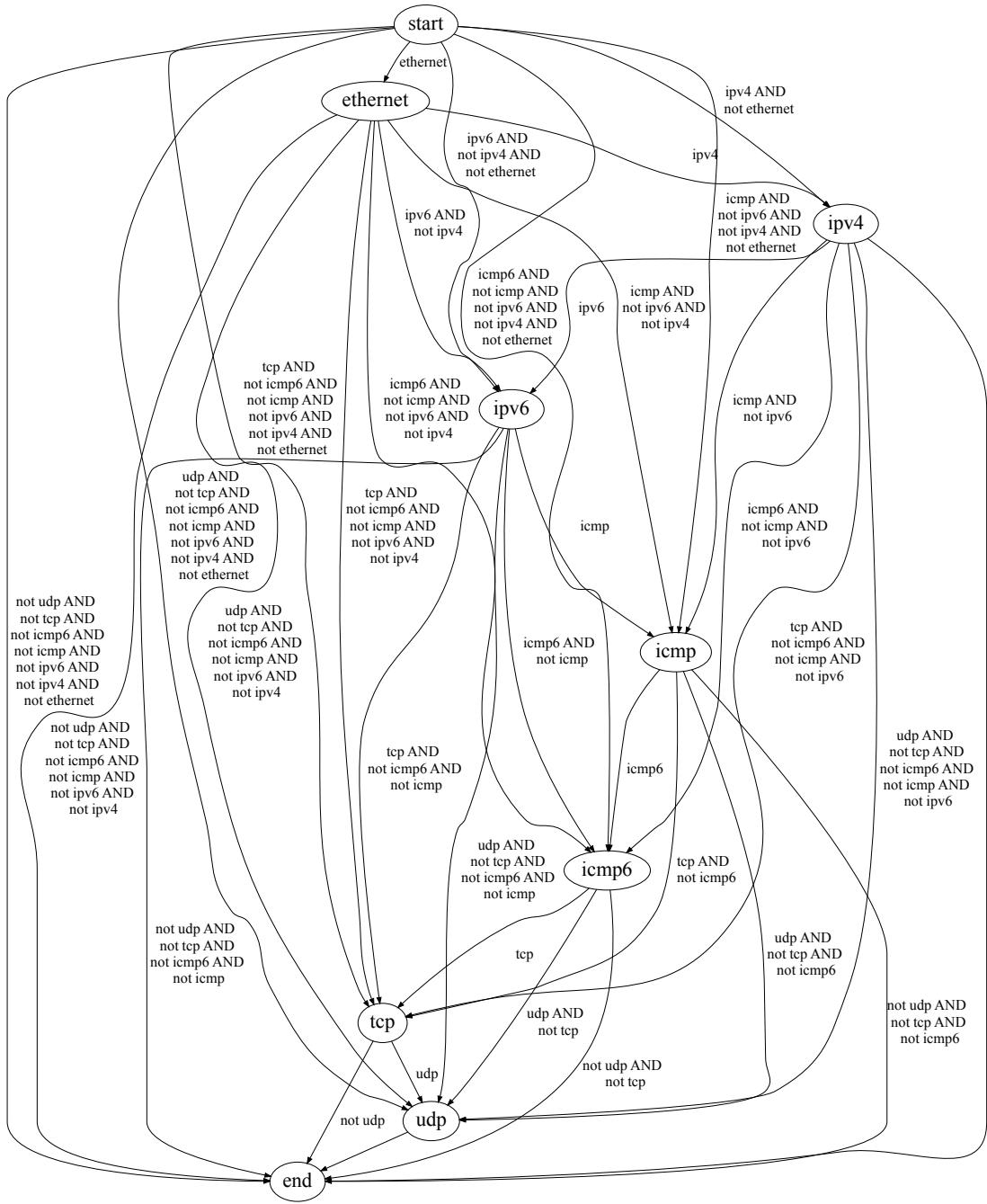

| 5.2 Déterminer les états possibles du vecteur d'en-têtes par l'analyse symbolique | 60        |

| 5.2.1 Vue d'ensemble de l'analyse symbolique d'un programme P4 . . . . .          | 60        |

| 5.2.2 Les fonctions affectant la validité du vecteur d'en-têtes . . . . .         | 61        |

| 5.2.3 L'évaluation symbolique dans les blocs conditionnels . . . . .              | 62        |

| 5.2.4 Exemple d'évaluation symbolique . . . . .                                   | 63        |

| 5.2.5 La complexité de l'analyse symbolique . . . . .                             | 64        |

| 5.3 Élagage du graphe de déparsage . . . . .                                      | 67        |

| 5.3.1 L'évaluation partielle du graphe de déparsage . . . . .                     | 67        |

| 5.3.2 Le graphe de déparsage minimal . . . . .                                    | 68        |

| 5.3.3 Résultats d'implémentation après élagage du graphe . . . . .                | 70        |

| <b>CHAPITRE 6 CONCLUSION . . . . .</b>                                            | <b>75</b> |

| <b>RÉFÉRENCES . . . . .</b>                                                       | <b>79</b> |

## LISTE DES TABLEAUX

|             |                                                                                                                         |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 3.1 | Programmes pour l'évaluation du FPGA pour l'implémentation de PISA                                                      | 30 |

| Tableau 4.1 | Liste et caractéristique des cas de test pour l'implémentation du déparseur . . . . .                                   | 50 |

| Tableau 4.2 | Taille des en-têtes de différents protocoles standards . . . . .                                                        | 51 |

| Tableau 4.3 | Résultats d'implémentation de <b>T0-1008</b> pour différentes largeurs de bus de sortie . . . . .                       | 53 |

| Tableau 4.4 | Résultats d'implémentation de <b>T1</b> pour différentes largeurs de bus de sortie . . . . .                            | 54 |

| Tableau 4.5 | Comparaison de l'implémentation de déparseurs avec d'autres travaux pour un bus de 512 bits. . . . .                    | 57 |

| Tableau 5.1 | Ensemble de VVE après l'analyse symbolique du parseur du listage 5.1                                                    | 64 |

| Tableau 5.2 | Caractéristiques des cas de test pour l'implémentation du déparseur . . . . .                                           | 70 |

| Tableau 5.3 | Résultats après implémentation du déparseur avec et sans élagage sur un FPGA Xilinx Ultrascale+ <i>xcvu3p</i> . . . . . | 73 |

## LISTE DES FIGURES

|             |                                                                                                                                            |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1  | Les différentes abstractions d'un réseau . . . . .                                                                                         | 9  |

| Figure 2.2  | Architecture PISA [7] avec deux étages de comparaison-action . . . . .                                                                     | 11 |

| Figure 2.3  | Vue d'ensemble de l'architecture P4 <code>v1model</code> . . . . .                                                                         | 16 |

| Figure 2.4  | Vue d'ensemble de l'architecture P4 PSA [49] . . . . .                                                                                     | 16 |

| Figure 2.5  | Présentation de l'architecture P4 <code>SimpleSumSwitch</code> [25] . . . . .                                                              | 17 |

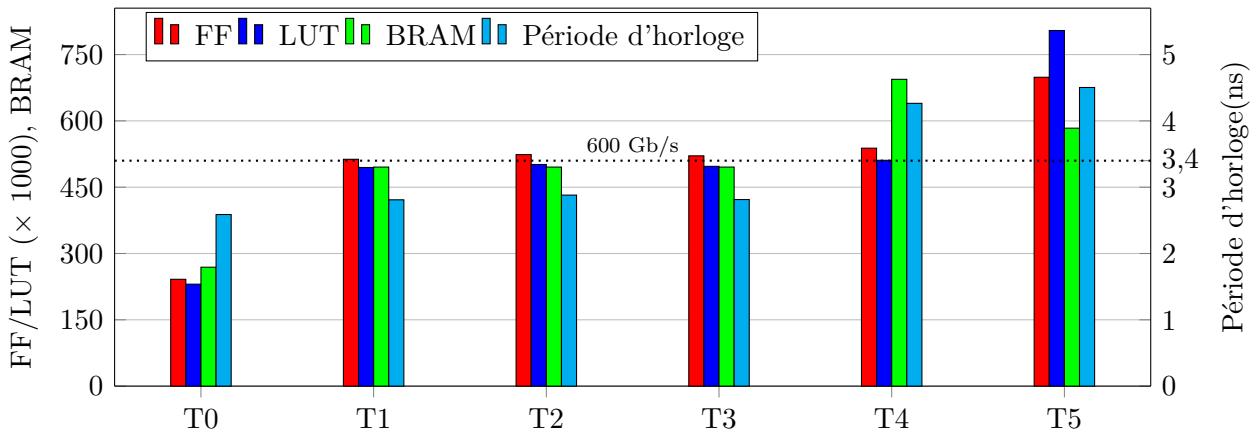

| Figure 3.1  | Résultats d'implémentation des programmes du tableau 3.1 avec un bus d'entrée-sortie de 2048 bits . . . . .                                | 31 |

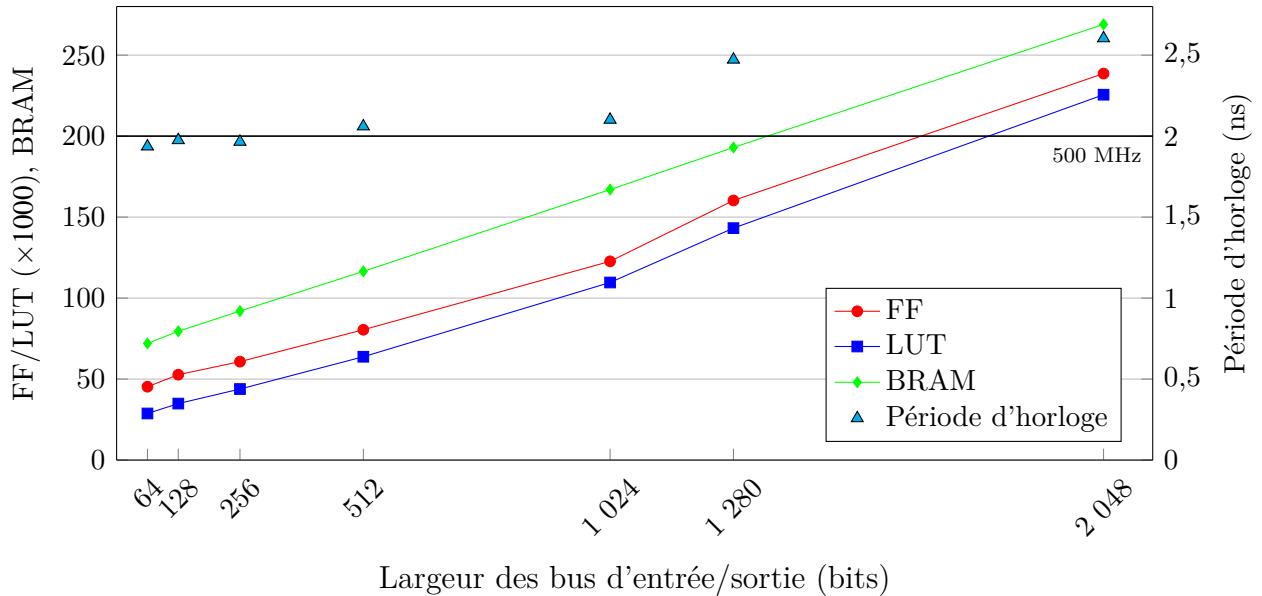

| Figure 3.2  | Résultats d'implémentation de T0 pour différentes largeurs du bus d'entrée-sortie . . . . .                                                | 32 |

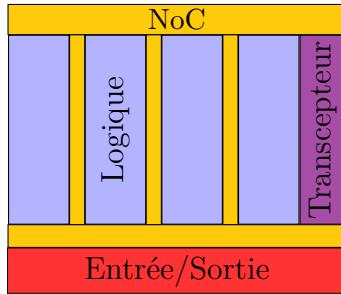

| Figure 3.3  | Présentation de la nouvelle architecture de FPGA proposé par [103] .                                                                       | 35 |

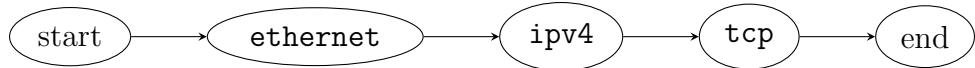

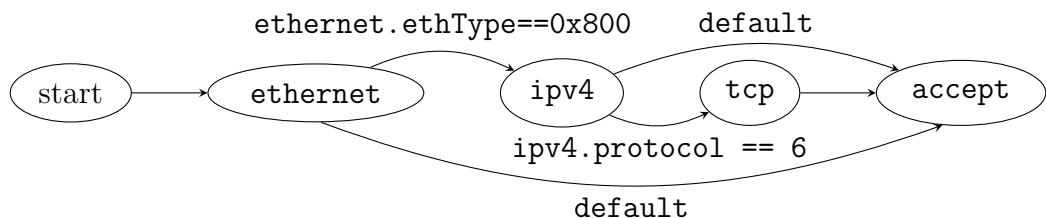

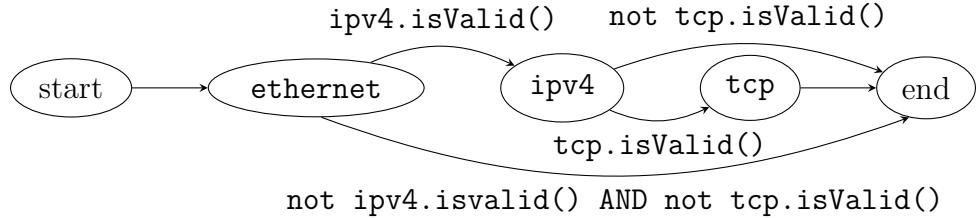

| Figure 4.1  | Graphe de déparsage résultant du Listage 4.1 . . . . .                                                                                     | 38 |

| Figure 4.2  | Graphe de déparsage après développement du GDA de la Figure 4.1 .                                                                          | 38 |

| Figure 4.3  | Fermeture transitive du GDA de déparsage de la figure 4.1 en utilisant l'algorithme 4.1 . . . . .                                          | 40 |

| Figure 4.4  | Structure d'un bloc de déparseur sur FPGA pour reconstituer le bit n du paquet. . . . .                                                    | 41 |

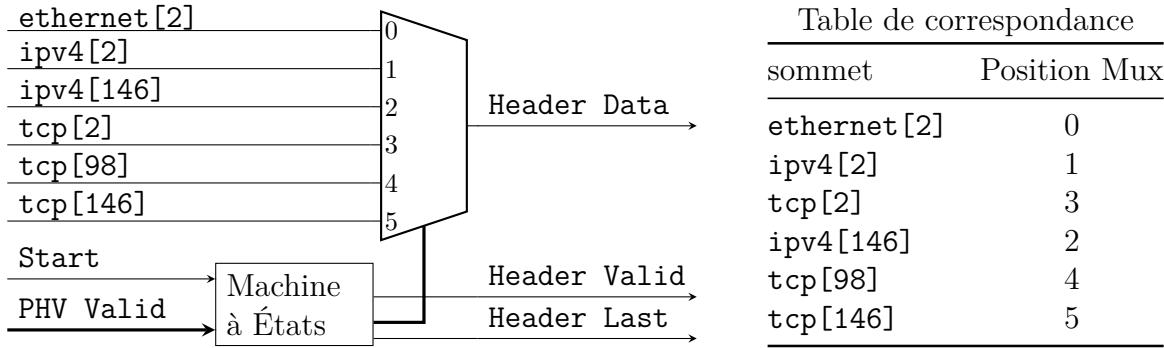

| Figure 4.5  | Le sélecteur de bit d'en-tête pour un bit de sortie . . . . .                                                                              | 42 |

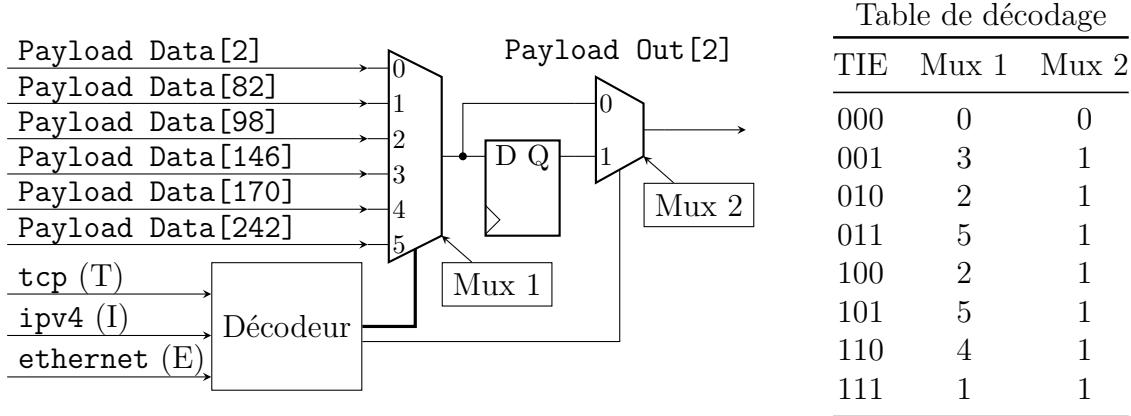

| Figure 4.6  | Le sélecteur de bit de la charge utile du paquet pour un bit de sortie .                                                                   | 43 |

| Figure 4.7  | Le sélecteur de bit de sortie . . . . .                                                                                                    | 43 |

| Figure 4.8  | Sous-graphe pour le bit de sortie numéro 2 résultant de la décomposition du graphe de la figure 4.3 pour un bus de sortie de 256 bits . .  | 46 |

| Figure 4.9  | Sélecteur de bit d'en-tête en utilisant le graphe de la figure 4.8 . . .                                                                   | 47 |

| Figure 4.10 | Bloc de sélection de bit de la charge utile avec la table d'association du décodeur. . . . .                                               | 48 |

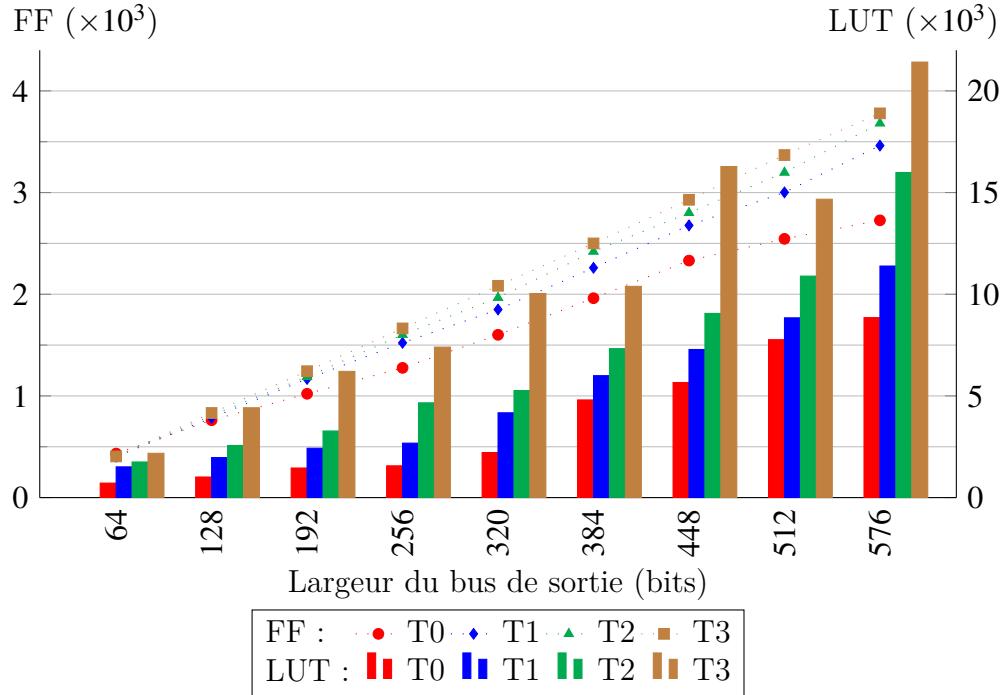

| Figure 4.11 | Utilisations de LUT et FF par l'implémentation de <b>T0</b> , <b>T1</b> , <b>T2</b> et <b>T3</b> pour différentes tailles de bus . . . . . | 52 |

|             |                                                                                                                                                                                 |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

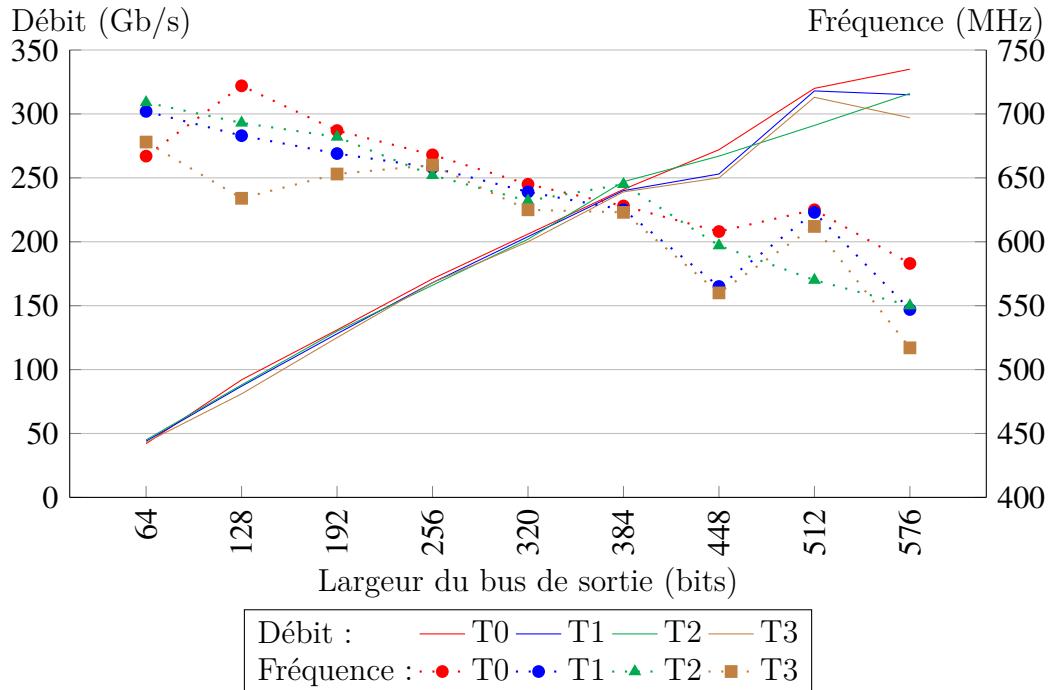

| Figure 4.12 | Fréquence et débit maximum obtenues après l'implémentation de <b>T0</b> , <b>T1</b> , <b>T2</b> et <b>T3</b> pour différentes tailles de bus . . . . .                          | 52 |

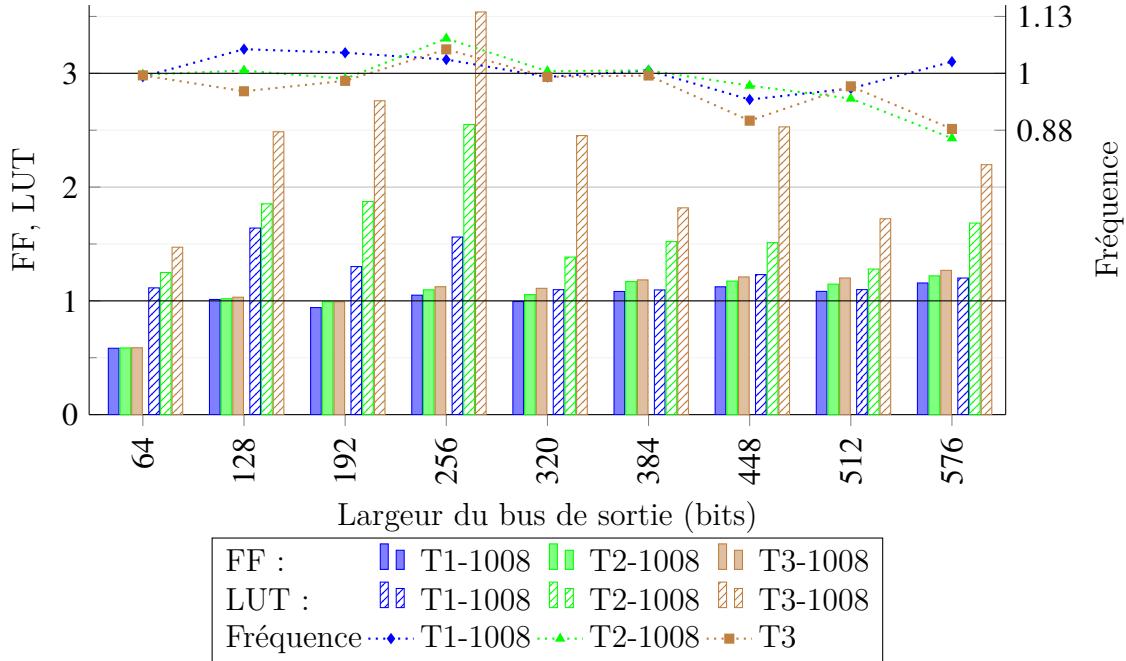

| Figure 4.13 | Ratios des FF, LUT et de la fréquence de <b>T1-1008</b> , <b>T2-1008</b> et <b>T3</b> par rapport à <b>T0-1008</b> , pour différentes largeurs de bus de sortie . . . . .       | 54 |

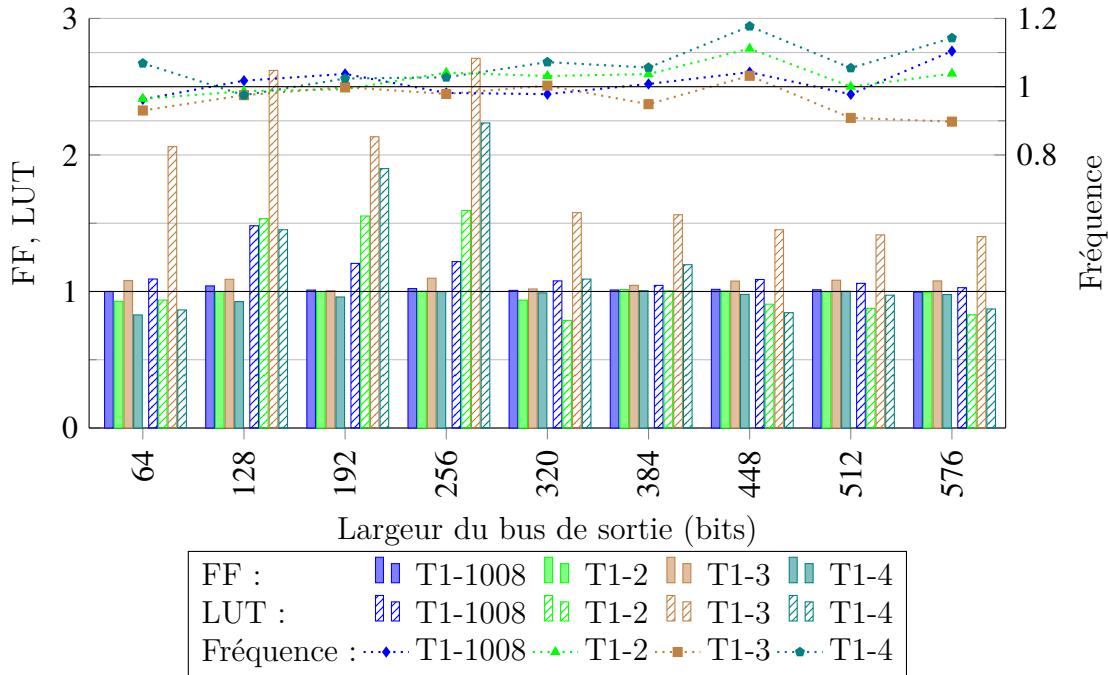

| Figure 4.14 | Ratios des FF, LUT et de la fréquence de <b>T1-1008</b> , <b>T1-2</b> , <b>T1-3</b> et <b>T1-4</b> par rapport à <b>T1</b> pour différentes largeurs de bus de sortie . . . . . | 55 |

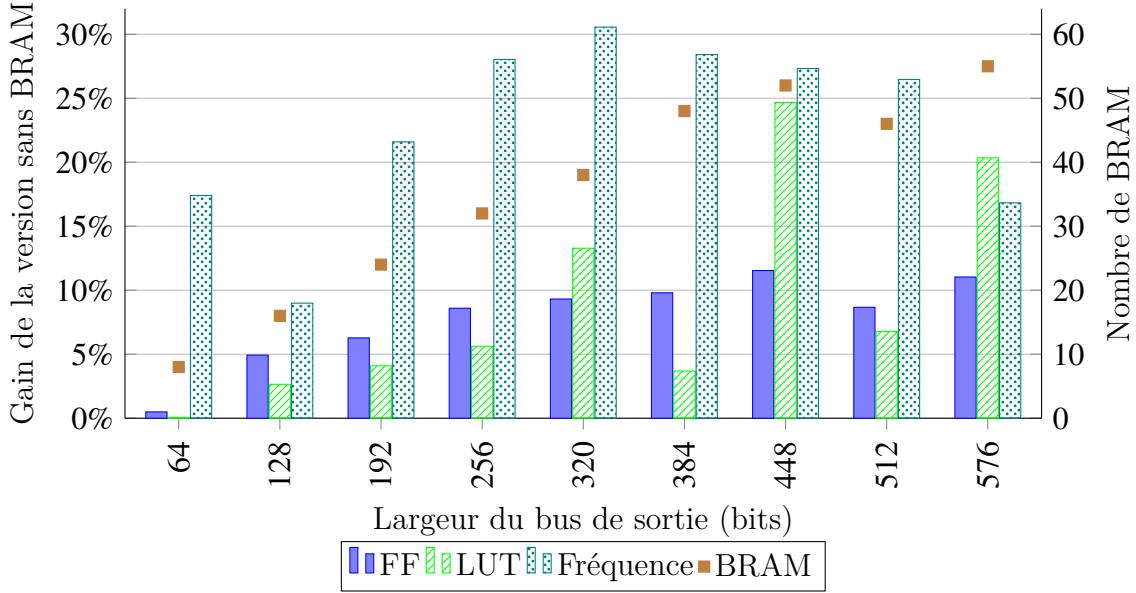

| Figure 4.15 | Résultats d'implémentation de <b>T3</b> avec et sans BRAM . . . . .                                                                                                             | 56 |

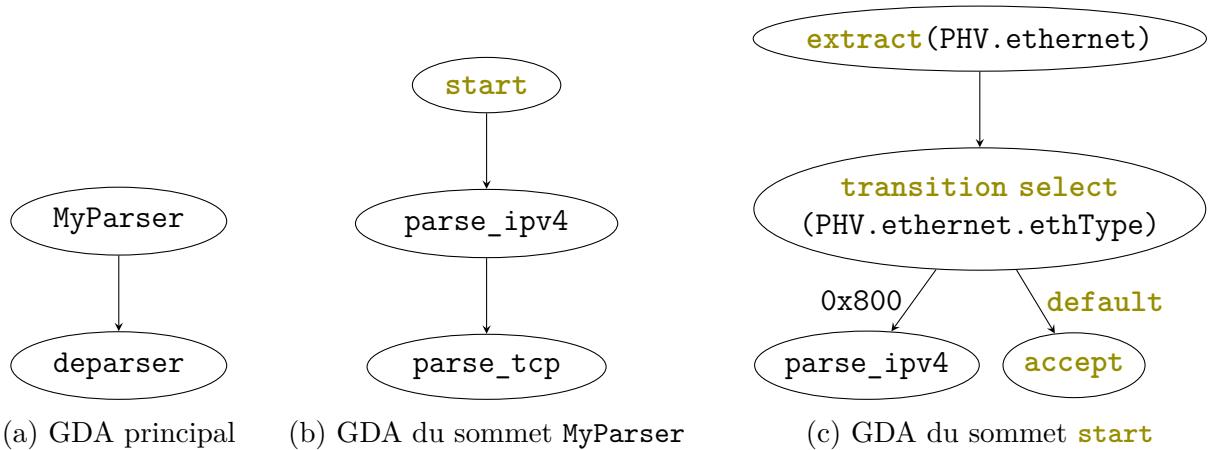

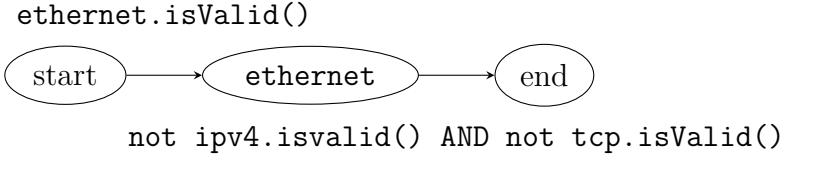

| Figure 5.1  | Graphe de parsage résultant du listage 5.1 . . . . .                                                                                                                            | 59 |

| Figure 5.2  | Exemple d'un graphe de déparsage réduit . . . . .                                                                                                                               | 60 |

| Figure 5.3  | Exemples de GDA et sous GDA pour un programme P4 composé des listages 5.1 et 4.1 . . . . .                                                                                      | 61 |

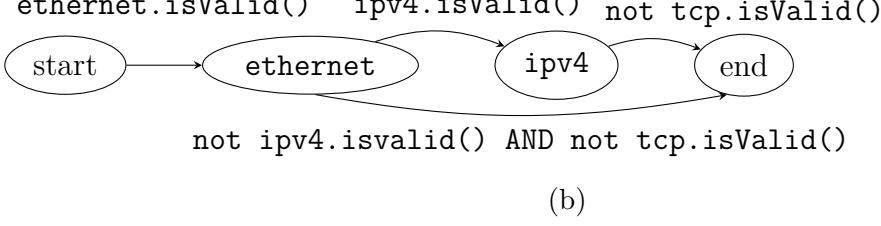

| Figure 5.4  | Les sous-graphes générés après l'analyse de chacun des VVE du tableau 5.1 . . . . .                                                                                             | 69 |

| Figure 5.5  | Graphe de parsage de <b>T2</b> . . . . .                                                                                                                                        | 71 |

| Figure 5.6  | Graphe de déparsage élagué de <b>T2</b> . . . . .                                                                                                                               | 71 |

| Figure 5.7  | Graphe de déparsage non élagué de <b>T2</b> . . . . .                                                                                                                           | 72 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|      |                                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------|

| ASIC | Circuit intégré spécifique à l'application — <i>Application Specific Integrated Circuit</i>               |

| BMv2 | Modèle comportemental version 2 — <i>Behavioral Model version 2</i>                                       |

| BRAM | Bloc RAM                                                                                                  |

| CAM  | Mémoire adressable par contenu — <i>Content Adressable Memory</i>                                         |

| CLB  | Bloc de logique configurable — <i>Configurable Logic Bloc</i>                                             |

| eBPF | BPF étendue — <i>extended BPF</i>                                                                         |

| FPGA | Réseau prédiffusé programmable — <i>Field Programmable Gate Array</i>                                     |

| GDA  | Graphe Dirigé Acyclique                                                                                   |

| LPM  | Comparaison du plus long prefixe — <i>Longest Prefix Match</i>                                            |

| LUT  | Table de conversion — <i>LookUp Table</i>                                                                 |

| NIC  | Carte d'interface réseau — <i>Network Interface Card</i>                                                  |

| NoC  | Réseau sur puce — <i>Network on Chip</i>                                                                  |

| ODG  | Graphe de dépendance des opérations — <i>Operation Dependency Graph</i>                                   |

| OLNE | Optimisation Linéaire en Nombres Entiers                                                                  |

| PHV  | Vecteur d'en-têtes de paquet — <i>Packet Header Vector</i>                                                |

| PISA | Architecture de commutateur indépendante des protocoles — <i>Protocol Independent Switch Architecture</i> |

| PSA  | Architecture portable de commutateurs — <i>Portable Switch Architecture</i>                               |

| RISC | Processeurs à jeu d'instructions réduit — <i>Reduced Instruction Set Computer</i>                         |

| SDN  | Réseau défini par logiciel — <i>Software Defined Networking</i>                                           |

| SRAM | Mémoire à accès aléatoire statiques — <i>Static Random Access Memory</i>                                  |

| TCAM | Mémoire adressable par contenu ternaire — <i>Ternary Content Adressable Memory</i>                        |

| TDG  | Graphe de dépendance de tables — <i>Table Dependency Graph</i>                                            |

| TNA  | Architecture native du Tofino — <i>Tofino Native Architecture</i>                                         |

| VVE  | Vecteur de Validité d'En-tête                                                                             |

## CHAPITRE 1 INTRODUCTION

### 1.1 Contexte

Les réseaux informatiques fournissent un moyen d'échanger des paquets de données entre des utilisateurs et ces paquets sont aiguillés à travers les réseaux de données à l'aide de commutateurs. La taille et la complexité des réseaux a significativement augmenté au cours des dernières années, en passant d'environ 1 million d'équipements connectés dans le monde en 1992 [1] à plus de 15 milliards en 2018 [2]. Cette augmentation s'accompagne également d'une augmentation très importante des débits : en 1995 un port réseau avait un débit de 100 Mb/s [3], aujourd'hui la norme est de 100 Gb/s. En plus de devoir gérer des réseaux plus grands et plus rapides, les commutateurs doivent, aiguiller les paquets, fournir des fonctionnalités pour la sécurité, assurer la qualité de service et surveiller le trafic. Afin de pouvoir effectuer toutes ces opérations et atteindre les hauts débits requis, les commutateurs sont devenus de moins en moins programmables et les réseaux de communication se sont ossifiées [4]. Cette ossification a amené à une incapacité à déployer de nouveaux algorithmes et de nouveau protocoles pour gérer les réseaux.

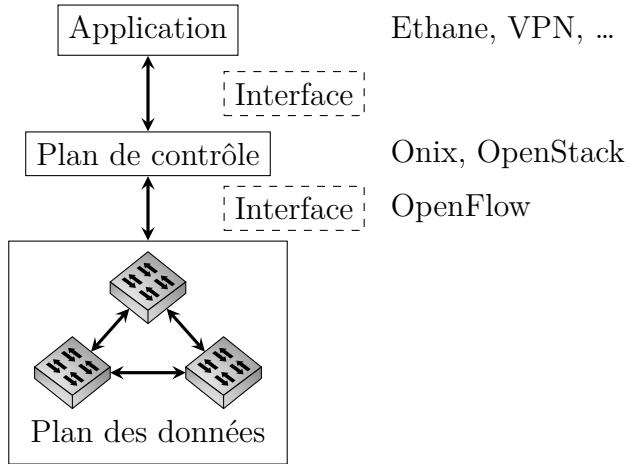

Afin de redonner de la flexibilité aux réseaux, le paradigme du réseau défini par logiciel — *Software Defined Networking* (SDN) a été introduit afin de proposer de nouvelles abstractions [5]. Dans le paradigme SDN, le plan des données, responsable du traitement des paquets, et le plan de contrôle, logiquement centralisé et commandant le plan des données, sont séparés afin de pouvoir les modifier de manière indépendante. Plus précisément, le paradigme SDN permet d'abstraire la gestion d'un réseau en fournissant trois séparations claires pour le développement des applications réseau :

- Un contrôleur centralisé (le plan de contrôle) exécute des applications réseau en configurant le plan des données par l'insertion de règles et en récupérant le statut du réseau.

- Une application réseau qui est exécutée sur le plan de contrôle, et est développée en définissant un ensemble de règles de gestion en fonction du statut du réseau.

- Un plan des données transfère les paquets en fonction des règles définies par le plan de contrôle.

Afin d'avoir une interface standard entre le plan de contrôle et le plan des données, McKeown et al. ont proposé OpenFlow en 2008 [6]. En plus de définir une interface standard, les différentes versions d'OpenFlow définissent des ensembles d'actions et de protocoles qu'un commutateur doit prendre en charge. Par conséquent, pour ajouter de nouveaux protocoles

ou de nouvelles actions sur un commutateur, il faut proposer une nouvelle version de la norme. Cependant, lors de la création d'une nouvelle version de la norme, l'intégration de ces changements peut s'avérer coûteuse et longue. Finalement, si un utilisateur n'a besoin que de certaines fonctionnalités d'une version d'OpenFlow, il est obligé d'utiliser un commutateur qui implémente toutes les fonctionnalités de cette version. Ceci peut obliger les utilisateurs à utiliser des commutateurs qui contiennent plus de ressources que nécessaire.

Pour s'émanciper des limites d'OpenFlow, l'architecture de commutateur indépendante des protocoles — *Protocol Independent Switch Architecture* (PISA), une abstraction pour le traitement des paquets, a été proposée par Bosshart et al. en 2013 [7]. PISA est une architecture de type flux de données — *dataflow* qui définit trois éléments configurables, élémentaires et nécessaires au traitement des paquets sur un commutateur réseau :

1. Un parseur responsable d'extraire les en-têtes du paquet à traiter.

2. Des tables de comparaisons-actions qui comparent les en-têtes avec un ensemble de règles, insérées par le plan de contrôle, et qui exécutent une action en fonction du résultat de la comparaison.

3. Le déparseur qui génère un paquet à transmettre en assemblant les en-têtes modifiés et la charge utile du paquet d'entrée.

PISA se présente comme un pipeline au travers duquel passe un paquet. Le pipeline se compose d'un parseur, puis d'une succession d'étages de comparaison-action, et il se termine par le déparseur. Les étages de comparaison-action sont configurables aussi bien sur la taille des tables que des actions qui peuvent être effectuées, un étage pouvant effectuer plusieurs comparaisons et plusieurs actions en parallèle sur différentes portions des en-têtes. Avec le modèle PISA, il est possible de concevoir des commutateurs programmables qui contiennent uniquement les opérations nécessaires au traitement du paquet. Cela facilite la reconfiguration en fournissant une abstraction claire.

Afin de pouvoir programmer le modèle PISA, Bosshart et al. ont proposé, en 2014, le langage dédié P4 [8]. Ce langage permet de définir l'ensemble des en-têtes que le parseur doit extraire, la taille des tables de comparaison-action, les parties des en-têtes à comparer, les actions qui peuvent être exécutées et comment le paquet en sortie doit être constitué. Ainsi, avec le langage P4, tous les éléments de PISA peuvent être configurés. Le langage P4 permet aussi de générer des interfaces pour le plan de contrôle afin de pouvoir configurer le plan des données.

En 2016, le premier circuit intégré spécifique à l'application — *Application Specific Integrated Circuit* (ASIC) basé sur PISA et programmable en P4, le Tofino™, a été commercialisé. Cette première version du Tofino™ atteint des performances équivalentes à celle d'un com-

mutateur non programmable et peut traiter jusqu'à 6,5 Tb/s de trafic [9]. Toutefois, pour atteindre ces hauts débits, certaines opérations demandant beaucoup d'éléments de calculs, tels que le chiffrement, peuvent nécessiter de faire passer un paquet plusieurs fois dans le commutateur [10], ce qui réduit le débit réel de traitement.

En outre, les centres de données ont besoin d'équipements permettant de traiter des données à haut débit tout en étant programmables afin de s'adapter aux nouvelles applications. À cet effet, les centres de données ont récemment intégré des réseaux prédiffusés programmables — *Field Programmable Gate Array* (FPGA) afin d'alléger la charge de calcul sur les serveurs [11–13]. L'utilisation des FPGA requiert toutefois de bonnes connaissances en développement matériel malgré l'évolution récente des outils de synthèse de haut niveau [14].

Les langages dédiés ont montré par le passé qu'ils permettaient d'élever le niveau d'abstraction pour l'implémentation d'applications sur FPGA [15]. Des travaux récents ont montré qu'il était possible d'implémenter des programmes P4 sur FPGA [16, 17], ce qui permet de s'affranchir des limites liées aux ASIC. Cependant, la performance atteinte par les FPGA reste bien inférieure à celle de puces plus spécialisées comme le Tofino. Ceci est dû d'une part à la microarchitecture des FPGA, mais également à un manque d'optimisations, dans le compilateur P4, adaptées aux spécification de l'architecture des FPGA.

Si le SDN a permis d'ouvrir la voie aux réseaux programmables, P4 et PISA sont les clés de voûte qui permettent de rendre le réseau entièrement programmable. Ainsi PISA est aux commutateurs réseau ce que l'architecture de processeurs à jeu d'instructions réduit — *Reduced Instruction Set Computer* (RISC) est aux processeurs génériques, en fournissant une abstraction claire sur l'interface qui doit être fournie au développeur pour programmer des plans des données. Également, le langage P4 peut être vu comme le C des architectures RISC, un langage qui permet de s'émanciper de l'architecture matérielle. P4 et PISA sont donc des avancés majeures pour rendre les réseaux programmables. Dans ce travail, nous proposons d'évaluer la place que peuvent prendre les FPGA dans ce contexte, mais aussi de proposer des modifications aux compilateurs P4 afin d'améliorer l'implémentation de programmes P4 sur FPGA.

## 1.2 Éléments de la problématique

Les gestionnaires de centres de données ont besoin de matériels configurables afin de pouvoir s'adapter aux différentes applications qu'ils doivent exécuter. En effet, les centres de données sont des environnements dynamiques qui exécutent une variété d'applications [18]. Par conséquent, les gestionnaires ont besoin de pouvoir accélérer divers types d'applications ainsi

que de pouvoir prédire quels types d'accélération doit être disponible à un moment donné. Par exemple, le service Amazon AWS facture ses services à l'heure. Ainsi, des FPGA ont été déployés dans les centres de données afin d'avoir des accélérateurs de calculs flexibles [11, 19]. Cependant, comme les gestionnaires de réseaux veulent pouvoir programmer facilement les FPGA, il leur faut donc des langages et des compilateurs leur permettant de programmer ces plateformes.

En plus des considérations citées, il faut que les réseaux soient flexibles, il faut donc des cartes d'interface réseau — *Network Interface Cards* (NIC) programmables. Cependant les NIC standard ne permettent généralement pas d'atteindre des débits suffisamment élevés lorsqu'on les utilise suivant un modèle programmable [20]. Dans le cas des NIC basés sur des ASIC, l'ajout de nouvelles fonctionnalités prend trop de temps au vu du changement des besoins internes des centres de données. Dans le cas des NIC basées sur des architectures de processeurs multicoeur, la consommation d'énergie est déjà élevée pour des débits de 40 Gb/s, alors que les nouvelles connexions demandent des débits excédant 100 Gb/s [21]. Les FPGA semblent être une plateforme de choix, puisqu'ils peuvent implémenter diverses applications réseau tout en soutenant des débits supérieurs à 400 Gb/s [22].

Également, grâce au langage P4 et à PISA, qui ont rendu le plan des données des réseaux programmables, l'idée du calcul dans le réseau a émergé. Il a même été démontré que cette approche pouvait alléger la charge de traitement sur les serveurs et même réduire la consommation d'énergie [23]. Toutefois, les commutateurs programmables actuels tels que le Tofino™ ne permettent pas de tirer pleinement avantage de cette possibilité. Les FPGA, qui permettent d'implémenter un large panel d'applications, semblent être une solution pour le calcul dans le réseau [24].

Bien que des compilateurs P4 vers FPGA existent [16, 17, 25], il est nécessaire de déterminer si les solutions de compilation actuelles implémentent au mieux les programmes P4 sur FPGA. En effet, les FPGA ont une quantité limitée de ressources qui peuvent être utiles à beaucoup d'applications. Il faut donc déterminer pour chacun des modules de PISA lesquels sont les plus adaptés à une implémentation sur FPGA, il sera ainsi possible de guider les développeurs pour une utilisation plus efficace du FPGA. Également, il est nécessaire d'évaluer sur les compilateurs actuels si des améliorations sont possibles, que ce soit par des transformations du programme lors de la compilation ou bien par l'ajout de nouvelles solutions pour implémenter des parties d'un programme P4 sur le FPGA .

Les FPGA présentent donc un intérêt pour implémenter des applications réseau et ainsi remplacer les NIC. Le fait qu'ils soient programmables en P4 permet aux gestionnaires de réseau d'implémenter plus facilement de nouveaux plans des données. Toutefois, il est néces-

saire de déterminer les modules des applications P4 qui ne s'implémentent pas efficacement sur FPGA, et de savoir si l'inneficacité d'implémentation de ces modules est due à l'architecture des FPGA ou à l'abscence de solutions adaptées pour les FPGA. Plus précisément, dans un pipeline PISA, il est essentiel de pouvoir extraire les en-têtes du paquet, avec le parseur, et d'assembler les en-têtes avec la charge utile du paquet d'entrée pour générer un nouveau paquet en sortie, avec le déparseur. Bien que de nombreux travaux se soient intéressés à la compilation de parseurs de paquets et à leur implémentation sur FPGA [26–30], peu de travaux ont exploré la compilation et l'implémentation du déparseur. Dans ce travail, nous proposons de combler ce manque en évaluant l'implémentation de programme P4 sur FPGA et d'améliorer l'implémentation du déparseur sur FPGA en proposant une nouvelle architecture de déparseur ainsi que des modifications au compilateur P4.

### 1.3 Objectifs de recherche

Dans cette thèse, nous cherchons à déterminer les améliorations pouvant être apportées aux FPGA afin d'accroître leur capacité pour implémenter des plans des données réseau. Pour cela, nous explorons d'une part les contraintes architecturales liées aux FPGA actuels ainsi que les limites des compilateurs générant des plans des données réseau sur FPGA. Par conséquent, les trois objectifs suivants sont considérés :

1. Déterminer les forces et faiblesses des FPGA actuels pour l'implémentation d'application réseau. Proposer des modifications à la microarchitecture des FPGA et des modifications aux architectures implémentées sur FPGA.

2. Proposer un compilateur P4 permettant de générer une architecture de déparseur adaptée à la structure des FPGA.

3. Proposer une passe de compilation permettant de réduire le coût d'implémentation des applications réseau sur FPGA.

### 1.4 Contributions de cette thèse

Les contributions des travaux présentés dans cette thèse peuvent se résumer comme suit :

1. Nous proposons d'évaluer l'implémentation des différents blocs de PISA sur FPGA dans le but de proposer des axes d'amélioration pour mieux prendre en charge des programmes P4 sur FPGA. Suite à cette évaluation, nous proposons certaines transformations qui pourraient aider à mieux adapter les FPGA au traitement d'applications réseau. Également, nous constatons que les solutions actuelles pour l'implémentation

de déparseurs sur FPGA consomment une quantité importante de ressources. Ces travaux sont détaillés dans le troisième chapitre de cette thèse.

2. Nous proposons une transformation au graphe de déparsage d'un programme P4 permettant d'exposer le parallélisme du processus de déparsage et de prendre avantage de l'architecture très parallèle des FPGA. Cette transformation est présentée dans le quatrième chapitre de cette thèse.

3. Nous proposons une nouvelle architecture de déparseur pour FPGA et un compilateur permettant de générer cette architecture depuis le graphe de déparsage proposé à la contribution 2. Cette architecture permet de réduire de  $4\times$  à  $10\times$  l'utilisation de ressources par rapport aux solutions précédentes tout en soutenant des débits de plus de 400 Gb/s. Ces travaux sont présentés dans le quatrième chapitre de cette thèse.

4. Nous proposons de spécialiser un programme P4 afin de diminuer le coût d'implémentation du déparseur présenté à la contribution 3. La spécialisation s'effectue par l'analyse symbolique du programme P4 qui permet de réduire le nombre de chemins dans le graphe de déparsage proposé à la contribution 2. Ces travaux sont présentés dans le cinquième chapitre de cette thèse.

Les différents travaux de cette thèse ont mené à la publication de trois articles :

1. Thomas Luinaud, Thibaut Stimpfling, Jeferson Santiago da Silva, Yvon Savaria et J.M. Pierre Langlois, "Bridging the Gap : FPGAs as Programmable Switches", 2020 IEEE 21st International Conference on High Performance Switching and Routing (HPSR).

2. Thomas Luinaud, Jeferson Santiago da Silva, J.M. Pierre Langlois et Yvon Savaria, "Design Principles for Packet Deparsers on FPGAs", 2021 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA '21). Association for Computing Machinery, New York, NY, USA, 280–286.

3. Thomas Luinaud, Jeferson Santiago da Silva, J.M. Pierre Langlois et Yvon Savaria, "Network data plane program specialization using symbolic analysis", révisé avec demande de modifications majeures au journal ACM Transactions on Architecture and Code Optimization (TACO).

## 1.5 Plan de la thèse

Cette thèse est organisée en six chapitres. Tout d'abord, un survol des réseaux programmables et une revue de la littérature sont présentés dans le chapitre 2. Les chapitres suivants de cette thèse présentent les contributions. Tout d'abord, dans le chapitre 3, l'analyse de l'implémentation de programmes P4 sur FPGA est présentée. Cette analyse montre que

l'implémentation du déparseur sur FPGA peut être améliorée. Dans le chapitre 4, une architecture de déparseur pour FPGA est présentée ainsi qu'une transformation du graphe de déparsage depuis le programme P4 permettant de générer l'architecture. Dans le chapitre 5, la spécialisation du déparseur exprimé dans des programmes P4 en effectuant leur analyse symbolique est présentée. Cette spécialisation permet de réduire le coût d'implémentation du déparseur sur FPGA en réduisant le nombre de chemins dans le graphe de déparsage. Finalement, le chapitre 6 présente la conclusion de cette thèse et propose des axes de travaux futurs.

## CHAPITRE 2 PRÉLIMINAIRES ET REVUE DE LA LITTÉRATURE

Dans ce chapitre, nous donnons les préliminaires et l'état de l'art permettant de comprendre les réseaux programmables et l'état de la recherche dans ce domaine. Tout d'abord, nous présentons les plans des données programmables. Par la suite, nous présentons différents langages réseau pour les plans des données et notamment le langage P4. Cela nous amène à discuter de différentes architectures P4. Ensuite, nous présentons la compilation du langage P4 à l'aide des différents compilateurs existants. Finalement, nous concluons cette section en posant certaines questions concernant l'implémentation, sur FPGA, de processeurs réseau modélisés avec le langage P4.

### 2.1 Le réseau programmable

Dans cette section nous présentons différentes recherches qui ont permis d'arriver au plan des données programmables. Dans un premier temps, nous présentons les évolutions qui ont permis de rendre le plan de contrôle programmable. Puis nous discutons des processeurs réseau. Finalement, nous présentons l'architecture de commutateur indépendante des protocoles — *Protocol Independent Switch Architecture* (PISA).

#### 2.1.1 La programmation du plan de contrôle

La programmation des réseaux est étudiée depuis de nombreuses années par les chercheurs [31]. En effet, l'incapacité à programmer les réseaux a pendant longtemps limité le test et le déploiement de nouveaux algorithmes [6], ce qui a limité l'innovation dans les réseaux.

Un tournant majeur a été atteint pour la programmation des réseaux lors de l'introduction du SDN [32]. Le SDN découle de deux éléments :

- L'introduction de l'abstraction du plan de contrôle et du plan des données

- La création d'une architecture réseau où le plan des données est séparé du plan de contrôle.

Le plan des données effectue le traitement sur les paquets. Le plan de contrôle est une entité logiquement centralisée qui configure le plan des données, à travers des règles, afin de déterminer les opérations à effectuer sur les paquets.

Pour configurer le plan des données depuis le plan de contrôle, McKeown et al. propose une interface standard, OpenFlow [6]. Comme cette interface est standard, il est possible de concevoir des systèmes d'exploitation pour le réseau ainsi que des langages de haut niveau

pour décrire des applications réseau [33–35]. On obtient ainsi une structure, telle que présentée dans la figure 2.1, où des applications réseau utilisent une interface fournie par le plan de contrôle qui configure le plan des données à l'aide d'une autre interface tel qu'OpenFlow.

Bien qu'OpenFlow permette de configurer le plan des données, les commutateurs compatibles avec OpenFlow ne sont pas totalement programmables. En effet, la spécification d'OpenFlow [36] définit un ensemble de protocoles qu'un commutateur doit pouvoir traiter afin d'y être compatible. Il est donc nécessaire de rendre également le plan des données programmable afin d'avoir un réseau totalement programmable.

Figure 2.1 Les différentes abstractions d'un réseau

### 2.1.2 Les processeurs réseau

Les processeurs réseau sont apparus vers la fin des années 1990 [3]. Il s'agit d'équipements spécialisés dans le traitement des paquets réseau, mais pouvant être programmés afin d'exécuter différentes applications. Les processeurs réseau ont des architectures parallèles contenant plusieurs coeurs de calculs avec des coprocesseurs afin d'accélérer le traitement de certaines fonctionnalités telles que les opérations de recherche. Un ordonnanceur assigne à chaque cœur de calcul un paquet à traiter [37].

Les processeurs réseau sont principalement implémentés en utilisant l'architecture de Von Neumann [38]. Cette approche permet aux processeurs réseau d'exécuter une variété importante d'algorithmes allant du routage de paquets jusqu'à l'inspection en profondeur de paquets. En général, les paquets sont assignés à un cœur de calcul qui effectue tous les traitements. De plus, la latence de traitement ne peut être garantie, notamment parce que les différents coeurs de calcul doivent accéder à de la mémoire partagée. Comme la latence de

traitement varie et qu'elle ne peut être garantie, il est courant de devoir réordonner les paquets dans un processeur réseau pour garantir leur ordre de sortie.

Un des éléments limitants des processeurs réseau est la complexité à les programmer. Kulkarni et al. ont identifié trois éléments limitant dans la programmation des processeurs réseau [39]. Le premier élément est la répartition des fonctionnalités à exécuter sur les différents coeurs de calcul. Le second élément est l'organisation et l'assignation des différentes ressources disponibles. Le troisième élément est le transfert de données de la mémoire vers les coeurs de calcul ainsi que la répartition des données dans la mémoire. Firestone et al. ont également montré dans le cas des NIC que, pour supporter des débits de plus de 100 Gb/s, l'utilisation d'architectures multicoeurs n'était pas possible notamment à cause de la synchronisation entre les différents coeurs [14].

### **2.1.3 Une architecture de commutateur indépendante des protocoles**

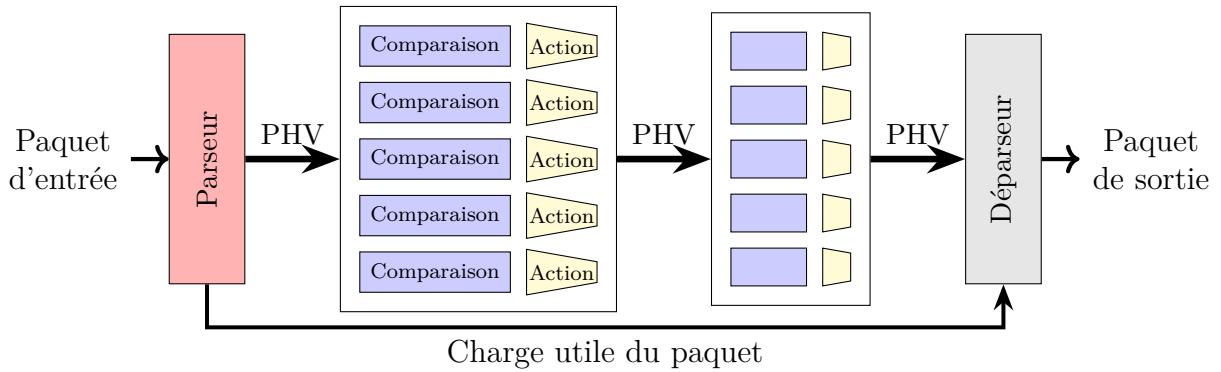

Afin de résoudre les problèmes liés aux architectures des processeurs réseaux, Bosshart et al. ont proposé en 2013 une architecture de commutateur indépendante des protocoles — *Protocol Independent Switch Architecture* (PISA) [7]. PISA est une architecture qui propage les données vers l'avant et elle se structure autour de trois abstractions principales : le parseur de paquets, les tables de comparaison-action et le déparseur de paquets. Tous les modules de PISA sont configurables et dépendent du programme que le plan des données doit exécuter. La figure 2.2 présente une architecture PISA composée d'un parseur de paquets, de deux étages de comparaison-action et d'un déparseur. Le parseur reçoit un paquet et en extrait les en-têtes pour les insérer dans le vecteur d'en-têtes de paquet — *Packet Header Vector* (PHV). Les étages de comparaison-action reçoivent le PHV et le modifient. Finalement, le déparseur reçoit le PHV et génère un nouveau paquet en tenant compte des délais dans le traitement des en-têtes. La charge utile est transmise directement depuis le parseur vers le déparseur. Dans le reste de cette section, les différents modules composant PISA sont présentés.

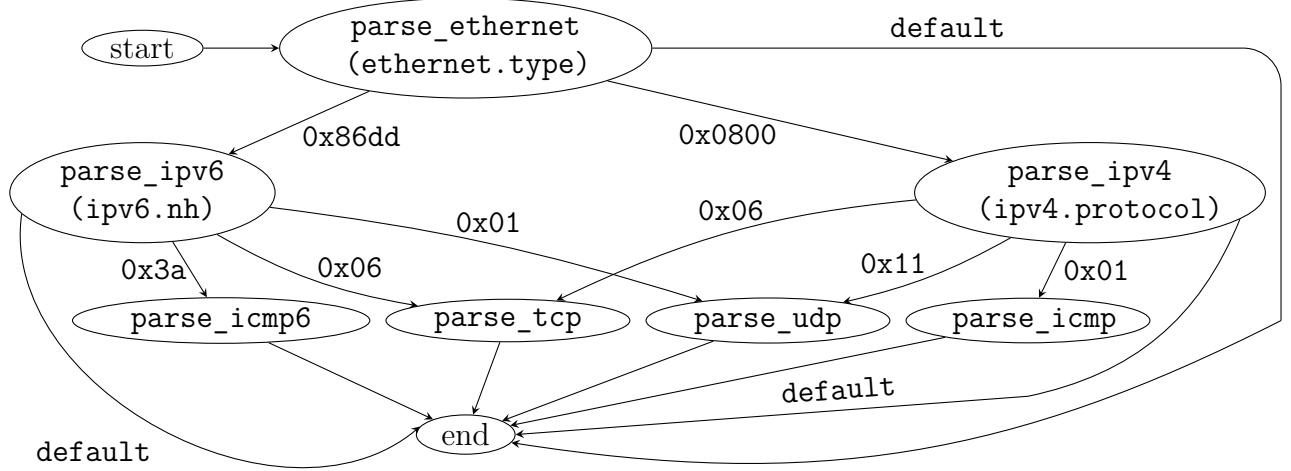

#### **Le parseur de paquets**

Le parseur de paquets a pour rôle d'extraire les en-têtes du paquet et de les insérer dans le PHV. Gibb et al. présentent les principes pour la conception d'un parseur de paquets [40]. On considère trois éléments que tous les parseurs de paquets contiennent : un élément pour identifier un en-tête, un bloc pour extraire les champs de l'en-tête et les insérer dans le PHV et finalement un tampon pour stocker le PHV. L'ordre d'extraction des en-têtes ainsi que les éléments permettant d'identifier l'en-tête sont définis à l'aide du Graphe Dirigé Acyclique

Figure 2.2 Architecture PISA [7] avec deux étages de comparaison-action

(GDA) de parsage. Une fois tous les en-têtes extraits du paquet, le reste du paquet, appelé charge utile, est transmis au déparseur.

### L'étage de comparaison-action

L'étage de comparaison-action se compose de deux éléments : le bloc de comparaison et le bloc d'action. Le principe de la comparaison-action consiste à effectuer une action en fonction du résultat d'une comparaison. La table de comparaison associe ainsi une clé à des valeurs et les valeurs contiennent des actions et des paramètres associés aux actions. Une action consiste en une suite d'opérations qui peuvent entre autres modifier les en-têtes du PHV.

Trois types de comparaisons sont possibles : la comparaison exacte, la comparaison ternaire et la comparaison du plus long préfixe — *Longest Prefix Match* (LPM). La comparaison exacte consiste à regarder si la clé recherchée est présente dans la liste de clés de la table. La comparaison ternaire permet de déterminer pour les clés présentes dans la table quelles parties de la clé sont à comparer. Finalement, la comparaison de type LPM consiste à rechercher une portion contiguë de la clé dans la table.

Dans la figure 2.2, deux étages de comparaison-action sont montrés et chacun contient plusieurs tables de comparaison et plusieurs unités pour mettre en œuvre l'action spécifiée. Dans un étage de comparaison-action, plusieurs comparaisons et plusieurs actions peuvent être effectuées en parallèle. Comme PISA est une architecture avec la propagation de données vers l'avant, si des dépendances de données sont présentes, alors la dépendance est résolue en exécutant l'opération sur un étage subséquent. Ainsi, si une comparaison-action  $B$  requiert le résultat d'une opération  $A$ , alors un étage de comparaison-action va effectuer l'opération  $A$  et l'étage de comparaison-action suivant effectuera l'opération  $B$ .

## Le déparseur

Le déparseur est le dernier module dans le pipeline PISA, il est responsable de la construction du nouveau paquet à émettre. Pour cela, le déparseur reçoit le PHV du dernier étage de comparaison-action ainsi que la charge utile du parseur. La construction du paquet de sortie se fait en combinant les en-têtes modifiés avec la charge utile dans un nouveau paquet. L'ordre d'insertion des en-têtes est défini par le graphe de déparsing.

## 2.2 Les langages pour les plans des données

Dans cette section, nous présentons des langages permettant de programmer les plans des données. Dans un premier temps, nous résumons l'évolution des langages de programmation pour les plans des données. Par la suite, nous introduisons le langage P4 et ses évolutions.

### 2.2.1 L'évolution des langages pour le plan des données

Afin de palier à la complexité de programmation des processeurs réseau (Section 2.1.2), des langages dédiés pour les plans des données ont été proposés. Dans cette section nous présentons les langages dédiés tel que défini par Mernik et al., à savoir un langage propre à un domaine ou bien des bibliothèques augmentant l'expressivité d'un langage existant [41].

Click [42] et sa variante, NP-click [43] ciblant plus spécifiquement les processeurs réseaux, sont des exemples de langages dédiés pour le traitement de paquets pour le plan des données. Le langage Click est une bibliothèque de classes C++ permettant de définir des modules élémentaires pour le traitement de paquets. Les modules sont connectés entre eux par des ports d'entrées sorties. Les opérations effectuées par les modules dérivent d'opérations de haut niveau des réseaux telles que la vérification de la somme de contrôle d'un en-tête. Pour ajouter de nouveaux protocoles, il faut modifier des classes de la bibliothèque de Click.

En 2014, Bonelli et al. ont proposé PFQ-Lang, un langage fonctionnel pour le traitement des paquets [44]. Le langage permet de définir les traitements à effectuer sur les paquets réseau, cependant, il est dépendant des protocoles intégrés. Ainsi, pour pouvoir utiliser un nouveau protocole réseau, il est nécessaire de modifier le langage afin d'y insérer le nouveau protocole.

Les langages Click, NP-click, PFQ-Lang fournissent une abstraction de haut niveau pour programmer des applications réseau. Toutefois, ces langages ne permettent pas de programmer un plan des données personnalisé. En effet, pour intégrer de nouveaux protocoles, il faut modifier ces langages.

En 2009, Duncan et Jungck ont proposé packetC, un langage dérivé de la norme C99 adapté au traitement de paquets [45]. Le langage consiste à définir un programme pour le traitement de paquets, et ce programme est ensuite exécuté sur plusieurs fils d'exécution. Bien que le langage autorise certaines abstractions propres au réseau, telles que les ensembles de recherche, le langage reste de très bas niveau et requiert une bonne connaissance, par le programmeur, du matériel sur lequel le programme est implémenté pour être performant. Le langage requiert également une architecture de processeur réseau massivement multicœur dans lesquel chaque cœur traite un paquet.

En 2013, Song a proposé POF, un langage dérivé de la spécification d'OpenFlow [46]. Le langage peut être considéré comme un jeu d'instructions adapté aux plans des données réseau et indépendant de la plateforme cible du programme. Les instructions disponibles dans POF peuvent être séparées en deux classes : les instructions de recherche et les instructions de calculs. Un élément majeur de POF est d'être indépendant des protocoles, ce qui permet de le distinguer des langages précédents. Le langage contient toutefois des instructions spécialisées comme le calcul de la somme de contrôle IPv4. La présence d'instructions spécialisées implique que lors de la création d'un processeur réseau, ces instructions doivent être insérées.

Brebner et Jiang ont développé le langage PX en 2014. Ce langage cible les FPGA Xilinx et permet de définir un pipeline de traitement pour des paquets. Le langage est indépendant des protocoles et il propose une structure pour exprimer le parseur des en-têtes du paquet et une structure différente pour le traitement à effectuer sur les en-têtes avec notamment des table de comparaison.

Les langages packetC, POF et PX permettent de programmer un plan des données et d'y insérer de nouveaux protocoles. PacketC et POF contraignent la conception des cibles sur lesquelles les programmes sont exécutés. Dans le cas de packetC, il faut que la cible soit massivement multicœur. Pour pouvoir être compatible avec POF, une cible doit pouvoir exécuter certaines opérations spécialisées. Le langage de Xilinx, PX, est propriétaire et n'est donc utilisable qu'avec des FPGA Xilinx.

### **2.2.2 Le langage P4**

La première version du langage P4, P4<sub>14</sub>, a été proposée en 2014 par Bosshart et al., il s'agit d'un langage qui permet d'exprimer le traitement à effectuer sur un paquet dans un plan des données réseau [8]. Le consortium P4 est responsable du maintien de la spécification du langage ainsi que du compilateur de référence.

P4 est un langage impératif basé sur le modèle de comparaison-action. Le modèle d'exécution s'organise autour de l'architecture PISA. On retrouve donc dans le langage P4 cinq composantes principales :

- la définition des en-têtes ;

- le parseur de paquets ;

- la définition des actions ;

- les tables de comparaison ; et

- le bloc de contrôle.

En P4, le vecteur d'en-têtes est une structure composée de champs de type `header`. Le type `header` est lui-même une structure pouvant être définie par le programmeur et contenant toujours un champ booléen dit de validité de l'en-tête. Ce champ de validité est caché, et il existe trois méthodes pour y accéder : `isValid`, `setValid` et `setInvalid`. Le champ de validité est initialisé à faux au démarrage du programme.

Le parseur de paquets est défini comme une machine à états. Le rôle du parseur est d'extraire du paquet les en-têtes qui sont traités dans le programme. Lors de l'extraction d'un en-tête, les données de ce dernier sont insérées dans un des champs du vecteur d'en-tête, et le champ de validité de cet en-tête est mis à vrai. Le parseur permet ainsi de définir les en-têtes qui seront traités par le commutateur.

Les actions sont des éléments qui peuvent être comparés à des procédures. Les actions peuvent avoir des paramètres et contiennent une séquence d'opérations élémentaires à effectuer, ces opérations peuvent notamment modifier le champ d'un en-tête.

Une table est un conteneur défini dans un bloc de contrôle. Le programme P4 permet de définir la structure de la table mais ne peut pas modifier son contenu. La modification du contenu d'une table s'effectue uniquement par le plan de contrôle pendant l'exécution du programme. La définition d'une table se compose de quatre éléments :

- la clé ;

- les actions ;

- le nombre d'entrées ; et

- une action par défaut.

La clé se compose d'un ou plusieurs éléments sur lesquels on doit effectuer la comparaison, pour chacun de ces éléments, un type de comparaison y est associé. Les actions indiquent quelles actions définies dans le code peuvent être exécutées par la table. La taille indique le nombre d'entrées que la table contient. L'action par défaut permet de définir l'action à exécuter si aucune correspondance n'est trouvée lors de la recherche dans la table.

Le bloc de contrôle permet de programmer le flot de traitement dans le programme. Les tables et les actions sont définies dans un bloc de contrôle et sont également appliquées dans ce dernier. Dans le bloc de contrôle, on peut organiser l'ordre dans lequel les comparaisons-actions sont effectuées ainsi que les conditions qu'il faut rencontrer pour effectuer ces opérations. Également, d'autres opérations peuvent être faites comme la modification du champ d'un en-tête, notamment pour le champ de validité des en-têtes permettant ainsi d'insérer ou de retirer un en-tête du paquet.

En 2016, le langage P4 a été révisé en profondeur [48], et la nouvelle version du langage est appelée P4<sub>16</sub>. P4<sub>16</sub> a pour objectif de stabiliser le langage, tout en permettant d'ajouter de nouvelles fonctionnalités aux commutateurs. Pour cela, le langage n'est plus spécifique à une architecture, il est possible d'intégrer des opérations non disponibles dans le langage à l'aide de fonctions dites externes. Également, une modification importante entre P4<sub>14</sub> et P4<sub>16</sub> est le fait que le déparseur de paquet n'est plus dépendant du parseur. En effet, en P4<sub>14</sub>, le déparseur est le symétrique du parseur, alors qu'avec P4<sub>16</sub> le déparseur est défini dans un bloc de contrôle dans lequel on indique l'ordre d'émission des en-têtes. Ceci implique qu'un programme P4<sub>16</sub> peut émettre un paquet que le commutateur ne peut pas parser.

### 2.3 Les architectures P4

Avec P4<sub>16</sub>, il est possible de définir différentes architectures de commutateurs. Dans ce contexte, une «architecture» est un modèle de programmation indiquant au concepteur les capacités ainsi que l'organisation logique du pipeline de traitement de la cible à programmer. Un programme P4 est donc développé pour une architecture spécifique. Toutefois, le programme doit être compilé pour les différentes cibles sur lesquels il est exécuté. Par exemple, si un programme P4 est exécuté sur une cible logiciel et un FPGA, il sera nécessaire de compiler le programme deux fois même s'il utilise la même architecture.

Une architecture peut contenir certaines parties non programmables en P4. Également, la définition d'une architecture peut définir un ensemble de fonctionnalités externes que le programme P4 peut implémenter à l'aide de fonctions externes définies avec le mot-clé `extern`. On dénombre quatre architectures courantes dans le cas de P4 :

- `v1model`;

- architecture portable de commutateurs — *Portable Switch Architecture* (PSA) ;

- architecture native du Tofino — *Tofino Native Architecture* (TNA) ; et

- `SimpleSumeSwitch`.

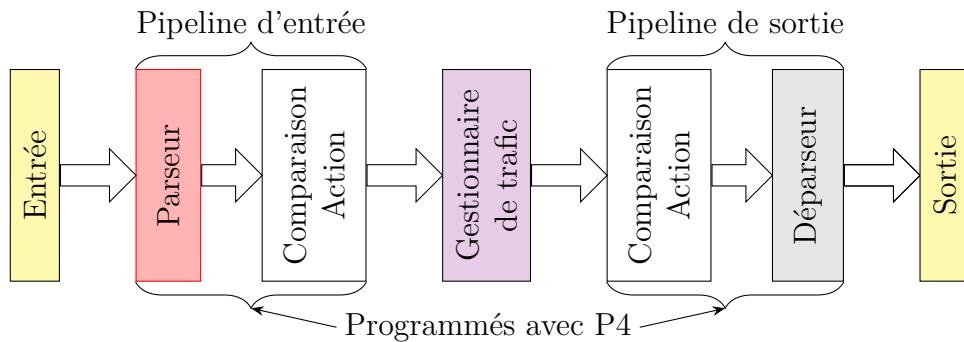

L'architecture `v1model` est l'architecture P4<sub>16</sub> correspondante à l'architecutre utilisée en P4<sub>14</sub>. Tel que montré dans la figure 2.3, elle se compose d'un parseur suivi d'un pipeline

de comparaison-action puis d'un gestionnaire de trafic, d'un pipeline de comparaison action et d'un déparseur. La présence de cette architecture permet au compilateur P4c de convertir des programmes P4<sub>14</sub> vers P4<sub>16</sub>. D'autre part, il s'agit également de la première architecture supportée par le modèle comportemental de référence modèle comportemental version 2 — *Behavioral Model version 2* (BMv2).

Figure 2.3 Vue d'ensemble de l'architecture P4 v1model

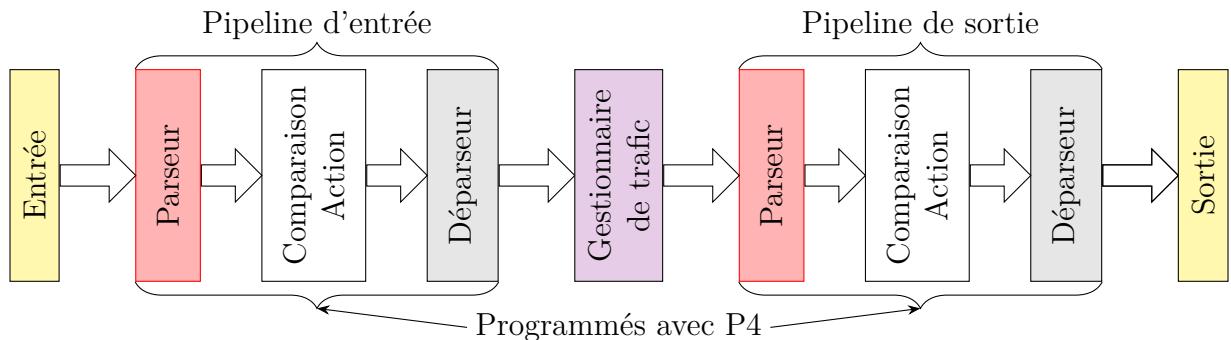

La figure 2.4 montre l'architecture PSA, qui se compose de deux pipelines, un d'entrée et un de sortie, séparés par un gestionnaire de trafic [49]. Les pipelines d'entrée et de sortie sont identiques, ils sont composés d'un parseur, d'un pipeline de comparaison-action et d'un déparseur. Seulement ces pipelines sont pour le moment programmables en P4. Le gestionnaire de trafic n'est actuellement pas programmable en P4, cependant des recherches sont en cours pour essayer d'intégrer au langage P4 la programmation de ce module [50].

L'architecture TNA est l'architecture P4 propriétaire du Tofino™, qui est une version étendue de PSA. Comme les puces Tofino™ peuvent avoir deux ou quatre unités de traitement, l'architecture TNA contient deux à quatre pipelines PSA [51]. Également l'architecture TNA définit certaines fonctions externes qui ne sont pas définies dans l'architecture PSA [52].

Figure 2.4 Vue d'ensemble de l'architecture P4 PSA [49]

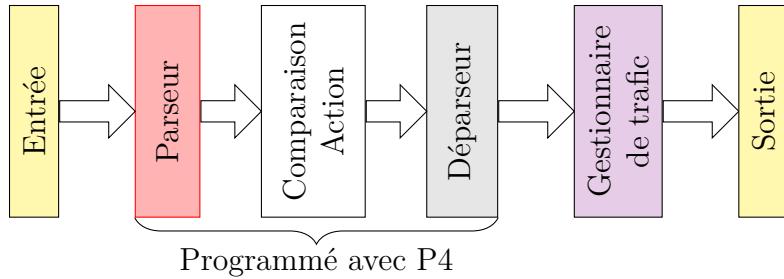

L'architecture **SimpleSumeSwitch**, présentée dans la figure 2.5, contient un pipeline composé d'un parseur, d'un étage de comparaison-action, d'un déparseur et d'un gestionnaire de trafic [50]. Comme pour PSA, le gestionnaire de trafic ne peut pas être programmé en P4. Seul le parseur, l'étage de comparaison-action et le déparseur sont programmés en P4. L'architecture **SimpleSumeSwitch** est généralement l'architecture utilisée pour implémenter des programmes P4 sur FPGA [16, 17, 25, 53].

Figure 2.5 Présentation de l'architecture P4 **SimpleSumeSwitch** [25]

## 2.4 Compilation de P4

Les compilateurs P4 traduisent un programme P4 dans un langage qui pourra être exécuté sur une cible spécifique. Tout d'abord, nous présentons la structure couramment utilisée par les compilateurs P4. Par la suite, nous présentons différentes cibles ayant des compilateurs P4. Ensuite, nous discutons de différents travaux traitant de l'analyse de programmes P4. Finalement, nous explorons des techniques permettant d'améliorer la compilation de langages dédiés.

### 2.4.1 La structure d'un compilateur P4

Les compilateurs P4 se basent généralement sur un modèle à deux couches. La première couche est une partie frontale commune à tous les compilateurs et la partie dorsale est spécifique à une cible [52].

La partie frontale permet de convertir le code P4 dans la représentation intermédiaire et effectue les analyses sémantiques indépendantes des architectures et des cibles. La représentation intermédiaire est par la suite utilisée par la partie dorsale pour effectuer les transformations spécifiques à l'architecture et à la cible. Comme plusieurs cibles peuvent utiliser la même architecture, la partie dorsale est composée de deux parties, une partie pour effectuer des modifications basées sur des politiques propres à l'architecture et une partie qui effectue les

transformations propres à la cible. Afin de pouvoir réutiliser certaines transformations de la représentation intermédiaire, des bibliothèques de passes de transformations sont disponibles [54].

La représentation intermédiaire utilisée est celle fournie par le compilateur de référence P4c [55]. La représentation intermédiaire est basée sur des objets C++ et elle peut être exportée en P4 ou dans un fichier au format JSON [54]. La communauté P4 propose un ensemble de compilateurs P4 de référence pour différentes cibles telles que le modèle comportemental BMv2, eBPF ou bien uBPF.

#### **2.4.2 Les cibles pour la compilation de P4**

On distingue trois catégories de cibles vers lesquelles le code P4 est compilé : les processeurs à usage général, les cibles matérielles et les FPGA. Dans cette section, nous commençons par présenter les différents compilateurs P4 à destination des processeurs à usage général. Par la suite, nous explorons différentes solutions matérielles étant compatibles avec P4. Finalement, nous présentons différents compilateurs P4 pour FPGA.

#### **Compilation et exécution de P4 sur des processeurs à usage général**

Il y a deux approches de compilation pour l'exécution du code P4 sur des processeurs à usage général. Une première méthode est la compilation du code P4 dans un langage qui est interprété. La seconde méthode est la compilation du code P4 vers un code exécuté par un processeur à usage général.

Plusieurs solutions exécutants une représentation intermédiaire d'un code P4 existent. Le BMv2 [56], est le logiciel proposé par la communauté P4 afin de tester des programmes P4. Ce commutateur logiciel charge un fichier JSON qui est compilé avec le compilateur P4c de référence. Trois autres solutions, p4c-ebpf [57], p4c-ubpf [58] et p4c-xdp [59], compilent des programmes P4 vers une représentation eBPF [60] afin de les exécuter directement avec des outils intégrés au noyau Linux.

Il existe également des solutions pour la compilation de programmes P4 vers des fichiers binaires exécutés sur des processeurs à usage général. Shahbaz et al. proposent PISCES, un commutateur logiciel qui est généré à partir d'un code P4 compilé en C [61]. Zanna et al. proposent de compiler des codes P4 pour être exécutés sur la carte d'évaluation et de test ZodiacFX [62, 63]. Finalement, Vörös et al. proposent T<sub>4</sub>P<sub>4</sub>s pour compiler des codes P4 vers du code C indépendant de la cible [64].

## Compilation pour des puces spécialisées programmables

Il existe des compilateurs P4 pour des puces spécialisées programmables. Intel® Tofino™ est la première puce spécialisée pouvant être programmée avec P4 à avoir été proposée. La première version pouvait traiter un débit agrégé de 6,5 Tbit/s [9], la dernière version de la puce, Tofino™ 3 [65], peut traiter jusqu'à 25,6 Tbit/s de trafic réseau agrégé. Intel® fournit un compilateur P4, Intel® P4 Studio. Seibulescu et Baldi proposent un compilateur P4 pour le processeur de Pensando [66, 67]. Les auteurs utilisent des fonctions externes qu'ils ajoutent à l'architecture P4 utilisée afin de pouvoir utiliser les instructions spécialisées disponibles sur le processeur. Finalement, Netronome [68], propose aussi un compilateur P4 pour leur NIC.

## L'implémentation de P4 sur FPGA

Plusieurs solutions ont été proposées pour compiler des programmes P4 afin de les implémenter sur des FPGA. Wang et al. proposent P4FPGA, un compilateur qui traduit un programme P4 en BlueSpec SystemVerilog qui peut ensuite être traduit en Verilog synthétisable par le compilateur propriétaire BlueSpec [16]. Benáček et al. proposent un compilateur qui convertit directement en VHDL le code P4 [17]. Finalement, Xilinx® propose le compilateur Xilinx SDNet [53] qui permet de convertir un code P4 en VHDL pour des FPGA Xilinx. Ibanez et al. présentent P4 → NetFPGA, une méthode permettant de compiler des codes P4 vers la plateforme NetFPGA [25]. Cette méthode utilise le compilateur Xilinx SDNet pour compiler le code P4 vers du VHDL.

D'autres travaux pour la compilation de P4 sur FPGA se sont plus axés sur les aspects de microarchitecture pour l'implémentation de structure PISA. L'implémentation du parseur de paquets sur FPGA a été explorée [27–30]. Les résultats montrent qu'il est possible de faire des parseurs de paquets pouvant soutenir des débits de plus de 100 Gb/s. Kekely et Korenek étudient l'implémentation de tables de comparaison-action définies en P4 sur un FPGA [69]. Stimpfling explore l'implémentation de mémoires associatives de type LPM définies en P4 sur FPGA [70]. Pontarelli et al. proposent une approche semblable aux processeurs RISC pour implémenter des actions définies en P4 sur FPGA [71]. Cabal et al. explorent l'implémentation du déparseur P4 sur FPGA [72], l'architecture est extraite du travail de Benáček et al. [17]. Le travail proposé se base cependant sur P4<sub>14</sub>, une version de P4 dans laquelle le graphe de déparsage est dérivé du graphe de parsage.

### 2.4.3 L'analyse de programmes P4

Dans la section précédente, on présente un ensemble de compilateurs P4 permettant de cibler une variété de plateformes pour l'exécution du code. Dans cette section, nous présentons les travaux orientés sur l'analyse et l'optimisation des applications P4.

Jose et al. s'intéressent à l'allocation des ressources pour PISA dans le cas de commutateurs spécialisés comme le Tofino [73]. Les auteurs introduisent le concept de graphe de dépendance de tables — *Table Dependency Graph* (TDG). Il s'agit d'un Graphe Dirigé Acyclique (GDA) dans lequel les sommets représentent les tables et les arêtes représentent la dépendance entre les tables dans le flot de contrôle du programme. Jose et al. montrent que l'allocation de ressources peut être faite en utilisant un algorithme d'Optimisation Linéaire en Nombres Entiers (OLNE).

Chole et al. proposent une variante au TDG en introduisant le concept de graphe de dépendance des opérations — *Operation Dependency Graph* (ODG) [74]. La différence entre les deux approches est principalement liée à l'architecture cible. En effet, dans [74], l'architecture est orientée autour de processeur qui accèdent à des mémoires de comparaison alors que l'approche de [73] cible des commutateurs avec des mémoires de comparaison organisée dans un pipeline. Les deux solutions peuvent toutefois utiliser des OLNE afin de résoudre le problème d'allocation des ressources.

Vass et al. analysent les aspects algorithmiques de la compilation de programmes P4 [75]. Les auteurs caractérisent les aspects algorithmiques notamment en ce qui concerne la complexité, afin d'évaluer les techniques actuellement utilisées pour la compilation de programme P4. Le résultat de leur analyse est que la compilation d'un programme P4 peut se faire dans un temps presque linéaire avec la taille du programme.

Gibb et al. présentent une solution pour faire des parseurs de paquets configurables, l'extraction des en-têtes se fait par le parcours d'un GDA dans lequel les sommets représentent un en-tête et les arêtes indique l'en-tête suivant à extraire en fonction d'une condition [40]. Santiago da Silva et al. proposent de transformer le graphe de parsage afin de simplifier le pipeline implémenté sur le FPGA [28].

Dangeti et al. utilisent la représentation intermédiaire de LLVM pour compiler un programme P4 [76]. Le compilateur proposé convertit la représentation intermédiaire de p4c vers la représentation intermédiaire de LLVM, puis génère un fichier JSON après les phases d'optimisations propres à LLVM. Avec ce travail, les auteurs montrent que LLVM s'adapte bien à la compilation de code P4 et que les optimisations existantes dans LLVM sont utiles à l'optimisation de code P4.

Ma et al. proposent d'insérer une table de comparaison-action comme cache à l'entrée du traitement à l'aide d'un préprocesseur sur le code P4 [77]. Cette cache permet d'accélérer le traitement de certains flots à l'exécution. Cette approche requiert cependant d'avoir des mécanismes afin de contourner les étages de comparaison-action n'étant plus utile à évaluer. Abhashkumar et al. proposent d'intégrer des contraintes liées aux applications lors de la compilation du code P4 [78]. Les contraintes sont indiquées par le programmeur et permettent notamment d'enlever des dépendances dans le TDG. Wintermeyer et al. proposent comme Abhashkumar et al. une approche pour prendre en compte les contraintes des applications en analysant des traces de trafic réseaux lors de la compilation. Cette approche permet ainsi de ne pas avoir à insérer les contraintes comme Abhashkumar et al., mais requiert d'avoir des traces réseaux valides.

## 2.5 Conclusion