|                         | Studying the Practices and Challenges of Developing Hardware<br>Description Language Programs                                                                                                                                       |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Fatemeh Yousefifeshki                                                                                                                                                                                                               |

| Date:                   | 2022                                                                                                                                                                                                                                |

| Туре:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                           |

| Référence:<br>Citation: | Yousefifeshki, F. (2022). Studying the Practices and Challenges of Developing<br>Hardware Description Language Programs [Mémoire de maîtrise, Polytechnique<br>Montréal]. PolyPublie. <u>https://publications.polymtl.ca/10340/</u> |

# **Document en libre accès dans PolyPublie** Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/10340/ |

|------------------------------------------|----------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Foutse Khomh, & Heng Li                |

| Programme:<br>Program:                   | Génie informatique                     |

## POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

# Studying the Practices and Challenges of Developing Hardware Description Language Programs

## FATEMEH YOUSEFIFESHKI

Département de génie informatique et génie logiciel

Mémoire présenté en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* Génie informatique

Mai2022

© Fatemeh Yousefifeshki, 2022.

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Ce mémoire intitulé :

# Studying the Practices and Challenges of Developing Hardware Description Language Programs

## présenté par Fatemeh YOUSEFIFESHKI

en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* a été dûment accepté par le jury d'examen constitué de :

Jinghui CHENG, président Foutse KHOMH, membre et directeur de recherche Heng LI, membre et codirecteur de recherche Maxime LAMOTHE, membre

## DEDICATION

To my family, specially my parents, who always supported me...

#### ACKNOWLEDGEMENTS

This dissertation is supervised by Dr. Foutse Khomh and co-supervised by Dr. Heng Li. I would like to express my most sincere appreciation to Dr. Khomh and Dr. Li for their patience, wise comments, advice, precious assistance, and valuable support throughout my Master's program. I would like to thank my committee members, Dr. Jinghui Cheng, and Dr. Maxime Lamothe for evaluating my master's thesis. Besides all the support from my advisors, I cannot ignore my family's unconditional love and generous support. I would like to dedicate my dissertation to my amazing father and my mom for her continued love.

### RÉSUMÉ

Avec la fin de la loi de Moore et de la mise à l'échelle de Dennard, les architectures à usage général (par exemple, les CPU RISC) deviennent insuffisantes pour répondre à nos besoins croissants en matière de calcul haute performance. Les architectures spécifiques à un domaine (par exemple, le TPU de Google) sont optimisées pour des applications spécifiques et peuvent donc atteindre de meilleures performances. Le développement de telles architectures spécifiques à un domaine nécessite généralement l'écriture de programmes dans des langages de description du matériel (HDL). Par rapport aux langages de programmation polyvalents (GPPL) traditionnels (par exemple, C++, Java, Python), le développement de programmes en HDL (par exemple, VHDL ou Verilog) a actuellement peu de soutien de la communauté de génie logiciel. Un tel déséquilibre dans le soutien aux GPPL et aux HDL entravera les progrès futurs des systèmes informatiques. L'une des raisons de ce déséquilibre semble être la méconnaissance des défis posés par les langages de description du matériel. Afin d'améliorer cette situation, dans ce mémoire, nous faisons une première tentative d'élucidation de ces défis, en étudiant les pratiques et les défis du développement de programmes en HDL, en examinant deux sources de données liées au développement de programmes HDL : 1) les forums techniques où les développeurs posent des questions relatives aux HDL, et 2) les projets open-source où les développeurs écrivent du code HDL.

Les développeurs posent généralement des questions techniques et y répondent sur des plateformes tels que les forums Stack Exchange. Ces questions peuvent communiquer les défis rencontrés par ces derniers lors du développement de programmes HDL. Par conséquent, notre première étude identifie et analyse plus de 16 000 questions relatives au HDL provenant de deux forums Stack Exchange : Stack Overflow (SO) et Electrical Engineering (EE). Nous analysons ces questions en combinant une analyse qualitative et une modélisation automatique des sujets, afin de comprendre les défis auxquels sont confrontés les développeurs lors du développement de programmes HDL.

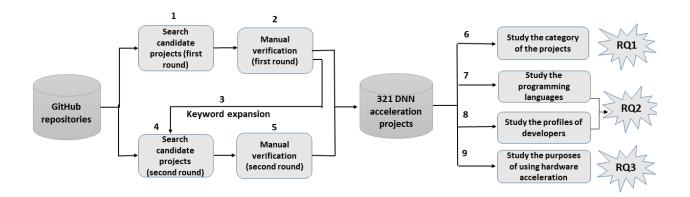

Ces dernières années, l'accélération matérielle des réseaux neuronaux profonds (DNN) est devenue un domaine d'application populaire de la co-conception matériel-logiciel spécifique à un domaine. Par conséquent, dans notre deuxième étude, nous examinons 321 projets opensource liés à l'accélération matérielle pour les réseaux neuronaux profonds, afin de mieux comprendre les pratiques et les défis du développement HDL dans les projets du monde réel. Nous étudions les catégories de projets qui exploitent l'accélération matérielle pour les DNN, la distribution des langages de programmation et les profils des développeurs de ces projets, ainsi que les objectifs de l'utilisation de l'accélération matérielle pour les DNN dans ces projets.

Notre travail a mis en évidence les différences entre le développement de programmes HDL et GPPL, et a permis d'identifier des possibilités d'amélioration pour le développement HDL. Nous espérons que notre travail contribuera à sensibiliser la communauté du génie logiciel sur la nécessité de soutenir le développement HDL, afin d'éviter que les composants HDL ne developpement des goulots d'étranglement dans le développement de futurs systèmes informatiques spécifiques à un domaine.

#### ABSTRACT

Modern computer systems typically consist of two indispensable components: general-purpose hardware (e.g., CPU) and highly-versatile software (e.g., web applications). In this context, Turing award winners John Hennessy and David Patterson, in their recent Turing lecture, declared that computer architectures are at the point of shifting from a general-purpose approach to a domain-specific hardware-software co-design approach. Developing such domain specific architectures typically requires writing programs in Hardware Description Languages (HDLs). This work makes an initial attempt to understand the practices and challenges of developing HDL programs and explore opportunities for the Software Engineering community to support the practices of HDL program development, by examining two sources of data related to HDL program development: 1) technical forums where developers ask HDL-related questions, and 2) open-source projects where developers write HDL code.

Developers usually ask and answer technical questions on technical forums such as Stack Exchange forums. These questions may communicate challenges faced by developers when developing HDL programs. Therefore, our first study identifies and analyzes over 16,000 HDL-related questions from two Stack Exchange forums: Stack Overflow (SO) and Electrical Engineering (EE) Stack Exchange. We analyze these HDL-related questions using a combination of qualitative analysis and automated topic modelling, in order to understand the challenges faced by developers when developing HDL programs.

In recent years, hardware acceleration for Deep Neural Networks (DNNs) have become a popular application area of domain-specific hardware-software co-design. Therefore, in our second study, we examine 321 open-source projects that are related to hardware acceleration for DNNs, to further understand the practices and challenges of HDL development in real-world projects. We study the categories of projects that leverage hardware acceleration for DNN, the distribution of programming languages and developer profiles of these projects, as well as the purposes of using hardware acceleration for DNN in these projects.

Our work highlights the differences between developing HDL programs and general-purpose programming language (GPPL) programs and identified opportunities for improving HDL development. We expect our work to draw the software engineering community's attention to supporting HDL development and prevent HDLs from becoming the bottleneck in developing future domain-specific computer systems.

# TABLE OF CONTENTS

| DEDIC               | ATION i                                                                            | ii     |

|---------------------|------------------------------------------------------------------------------------|--------|

| ACKNO               | DWLEDGEMENTS i                                                                     | v      |

| RÉSUM               | ſÉ                                                                                 | v      |

| ABSTR               | ACT v                                                                              | ii     |

| TABLE               | OF CONTENTS vi                                                                     | ii     |

| LIST O              | F TABLES                                                                           | х      |

| LIST O              | F FIGURES                                                                          | ĸi     |

| LIST O              | F SYMBOLS AND ACRONYMS                                                             | ii     |

| CHAP7<br>1.1<br>1.2 |                                                                                    | 1<br>1 |

|                     | projects that leverage hardware acceleration for DNN $\ . \ . \ . \ . \ . \ . \ .$ | 3      |

| 1.3                 | Contributions of the Thesis                                                        | 4      |

| 1.4                 | Organization of the Thesis                                                         | 5      |

| CHAPT               | TER 2 BACKGROUND AND LITERATURE REVIEW                                             | 6      |

| 2.1                 | Background                                                                         | 6      |

|                     | 2.1.1 Background on Hardware Description Languages (HDL)                           | 6      |

|                     | 2.1.2 Background on Hardware Acceleration for DNN                                  | 7      |

| 2.2                 | Literature Review                                                                  | 7      |

|                     | 2.2.1 Domain-Specific Architectures                                                | 8      |

|                     | 2.2.2 HDL Development                                                              | 8      |

|                     | 2.2.3 Technical Forum Analysis                                                     | 9      |

|                     | 2.2.4 Hardware acceleration for DNN                                                | 0      |

| CHAPT               |                                                                                    |        |

| SCF                 | AIPTION LANGUAGE    1                                                              | 2      |

| 3.1                 | Introduction                                                                       | 3      |

| 3.2   | Experiment Setup                                                                                                     | 15 |

|-------|----------------------------------------------------------------------------------------------------------------------|----|

|       | 3.2.1 Context of the Study $\ldots$ | 15 |

|       | 3.2.2 Data extraction and analysis steps                                                                             | 16 |

| 3.3   | Experiment Results                                                                                                   | 19 |

| 3.4   | Discussions and Implications                                                                                         | 37 |

| 3.5   | Threats to Validity                                                                                                  | 38 |

| 3.6   | Summary                                                                                                              | 39 |

| СНАРТ | TER 4 STUDYING DNN HARDWARE ACCELERATION PRACTICES IN                                                                |    |

| GIT   | HUB PROJECTS                                                                                                         | 40 |

| 4.1   | Introduction                                                                                                         | 40 |

| 4.2   | Experiment Setup                                                                                                     | 42 |

|       | 4.2.1 Overview of the Study                                                                                          | 43 |

|       | 4.2.2 Data extraction and analyses steps                                                                             | 43 |

| 4.3   | Experiment Results                                                                                                   | 45 |

| 4.4   | Discussions and Implications                                                                                         | 54 |

| 4.5   | Threats to Validity                                                                                                  | 55 |

| 4.6   | Summary                                                                                                              | 55 |

| СНАРТ | FER 5 CONCLUSION                                                                                                     | 57 |

| 5.1   | Summary                                                                                                              | 57 |

| 5.2   | Future Work                                                                                                          | 58 |

| REFER | RENCES                                                                                                               | 59 |

## LIST OF TABLES

| Table 3.1  | The distributions of programming languages (tags) involved in the                                                                                     |    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | HDL-related questions                                                                                                                                 | 21 |

| Table 3.2  | A taxonomy of question categories which bases on and extends $[1].$ .                                                                                 | 22 |

| Table 3.3  | Topics extracted from HDL related posts on Stack Overflow                                                                                             | 26 |

| Table 3.4  | Popularity of HDL-related topics on both forums                                                                                                       | 29 |

| Table 3.5  | Topic distribution (%) in questions related to each language $\ldots$ .                                                                               | 30 |

| Table 3.6  | Difficulty level of questions related to each language in both forums $% \mathcal{A}^{(n)}$ .                                                         | 33 |

| Table 3.7  | The percentage of questions without accepted answers in SO forum                                                                                      |    |

|            | $(per topic and language) \dots \dots$                                  | 35 |

| Table 3.8  | The median time (hr:min) to get accepted answers in SO forum (per                                                                                     |    |

|            | topic and language) $\ldots$                                                                                                                          | 35 |

| Table 3.9  | The percentage of questions in EE forum without accepted answers                                                                                      |    |

|            | $(per topic and language) \dots \dots$                                  | 36 |

| Table 3.10 | The median time (hr:min) to get accepted answers in EE forum (per                                                                                     |    |

|            | topic and language) $\ldots$                                         | 36 |

| Table 4.1  | The categories of DNN models that use hardware acceleration in the                                                                                    |    |

|            | studied projects.                                                                                                                                     | 47 |

| Table 4.2  | The categories of high-level tasks that use hardware acceleration in the                                                                              |    |

|            | studied projects.                                                                                                                                     | 48 |

| Table 4.3  | The distributions of programming languages code involved in the FPGA- $$                                                                              |    |

|            | related projects                                                                                                                                      | 50 |

| Table 4.4  | The distributions of developers involved in the DNN acceleration projects $% \left( {{{\left[ {{{\left[ {{\left[ {{\left[ {{\left[ {{\left[ {{\left[$ |    |

|            | according to their involved programming languages                                                                                                     | 52 |

| Table 4.5  | The distributions of developers involved in the FPGA-related projects.                                                                                | 52 |

| Table 4.6  | classification of developers in the FPGA acceleration for DNN projects                                                                                | 52 |

| Table 4.7  | The phase of models leveraging hardware a acceleration for DNN projects.                                                                              | 53 |

|            |                                                                                                                                                       |    |

# LIST OF FIGURES

| Figure 2.1 | Illustration of combinational logic circuits and sequential logic circuits | 6  |

|------------|----------------------------------------------------------------------------|----|

| Figure 3.1 | An overview of our data extraction and analysis process                    | 16 |

| Figure 3.2 | The difficulty aspect of HDL-related topics on SO                          | 34 |

| Figure 3.3 | The difficulty aspect of HDL-related topics on the EE forum                | 37 |

| Figure 4.1 | An overview of our data extraction and analysis process                    | 44 |

# LIST OF SYMBOLS AND ACRONYMS

| HDL                   | Hardware Description Language             |

|-----------------------|-------------------------------------------|

| $\operatorname{GPPL}$ | General-purpose programming language      |

| Q&A                   | Questions and Answers                     |

| SO                    | Stack Overflow                            |

| $\mathbf{EE}$         | Electrical Engineering Stack Exchange     |

| DNN                   | Deep Neural Network                       |

| $\mathbf{ML}$         | Machine Learning                          |

| API                   | Application Programming Interface         |

| CNN                   | Convolution Neural Network                |

| ANN                   | Artificial Neural Network                 |

| BNN                   | Binary Neural Network                     |

| $\mathbf{SNN}$        | Spiking Neural Network                    |

| RNN                   | Recurrent Neural Network                  |

| $\operatorname{GPU}$  | Graphic Processing Unit                   |

| CPU                   | Central Processing Unit                   |

| $\mathbf{TF}$         | TensorFlow                                |

| $\mathbf{UI}$         | User Interface                            |

| RISC                  | Resources Information Standards Committee |

| TPU                   | Cloud Tensor Processing Units             |

#### CHAPTER 1 INTRODUCTION

Modern computer systems typically consist of two indispensable components: general-purpose hardware (e.g., CPU) and highly-versatile software (e.g., web applications). However, with Moore's law and the Dennard scaling ending, it has been increasingly difficult to increase the number of transistors on a chip, which poses critical challenges to enhancing the computing power of general-purpose architectures (e.g., RISC) [2–4]. In this context, Turing award winners John Hennessy and David Patterson, in their recent Turing lecture, declared that computer architectures are at the point of shifting from a general-purpose approach to a domain-specific hardware-software co-design approach [2]. Domain-specific architectures (e.g., Google's TPU, Apple's Neural Engine, or Microsoft's FPGAs for deep neural networks) are more closely tailored to the application domain and can provide new opportunities to improve the performance of computer systems. Developing such domain-specific architectures typically requires writing programs in Hardware Description Languages (HDLs) [3]. However, there exists an imbalance between the support for HDL program development and that for developing programs in traditional general-purpose programming languages (GPPLs) (e.g., C++, Java, Python) [2–4]. We believe that such an imbalance in GPPLs and HDLs will impede future advances in computer systems, particularly in domain-specific applications. This work makes an initial attempt to understand the practices and challenges of developing HDL programs and explore opportunities for the Software Engineering community to support the practices of HDL program development. This work is organized through two perspectives: 1) mining technical forums where developers ask HDL-related questions to understand the challenges of developing HDL programs, and 2) mining open-source projects where developers write HDL code, in particular, projects that leverage hardware acceleration for DNN, to understand the practices of writing HDL in real-world projects.

# 1.1 Studying the challenges of developing HDL programs by mining technical forums

Hardware description languages (HDLs) are programming languages with particular capabilities for describing the concurrent nature of digital logic and electronics. On the time and space dimensions, HDLs represent the structure and behavior of hardware. VHDL [5] and Verilog [6] [7] are the two most widely used HDLs in reality applications. They are now the bridges every design needs to traverse to access synthesis and implementation technologies, independent of whatever HDL was used to generate it. Any HDL-capable programming language may be isolated from lower-level stages and tools by producing Verilog or VHDL code from its synthesizable subset. Hardware designers are always searching for innovative ways to save design time and expenses [3]. The fact that the hardware ecosystem is a monoculture of a few chip designs from a few manufacturers limits design productivity. An ecosystem of readily available intellectual property blocks that may be combined to generate new chip designs is critical for the hardware industry. Improvements in HDLs will help this transition. Modern high-level programming languages include several features that support modularity and abstraction. A type system, for example, may restrict data at an interface [8]. However, most hardware description languages (HDLs) only offer a few of these features. We use the term wires to describe the module's interface, which may be further refined to input or output. Hundreds of designs revealed that these interfaces have complex needs, not only in terms of data use and processing but also in terms of compositions that contribute to well-defined digital designs [8]. These languages lack strong abstraction capabilities seen in contemporary software languages, reducing designer productivity by making component reuse difficult. This new development paradigm raises concerns about how hardware developers should build and treat HDL implementations. This work makes an initial attempt to understand the challenges of developing HDL programs and explore opportunities for the SE community to support the practices of HDL program development. Developers usually ask and answer technical questions on technical forums such as Stack Exchange forums<sup>1</sup>. These questions may communicate challenges faced by developers when developing HDL programs. Therefore, this work identifies and analyzes over 16, 000 HDL-related questions from two Stack Exchange forums: Stack Overflow (SO) and Electrical Engineering (EE) Stack Exchange. We analyze these HDL-related questions using qualitative analysis and automated topic modeling to understand developers' challenges when developing HDL programs. Our study is organized by answering the following three research questions (RQs):

#### RQ 1.1: What types of questions do developers ask about HDL?

We manually examined a statistically significant representative sample of HDL-related questions posted in the SO and EE forums to understand the types of information sought by developers about HDL program development. We discovered ten types of questions by expanding on a prior classification [1]. Our findings indicate the need for more resources and tools to aid developers in understanding, verifying and diagnosing issues in HDL programs.

#### RQ 1.2: What are the topics in the HDL-related questions?

We use topic models to derive the semantic topics included in developers' questions to under-

<sup>&</sup>lt;sup>1</sup>https://stackexchange.com

stand developers' challenges in developing HDL programs. We observe that HDL program development shares most of the challenges (e.g., syntax errors and file I/O) of GPPL program development. However, some challenges (e.g., lower level operations such as bit operations and register operations, or synchronization through clocked processes) are only notable for HDLs.

#### RQ 1.3: What questions are difficult for developers to get answers?

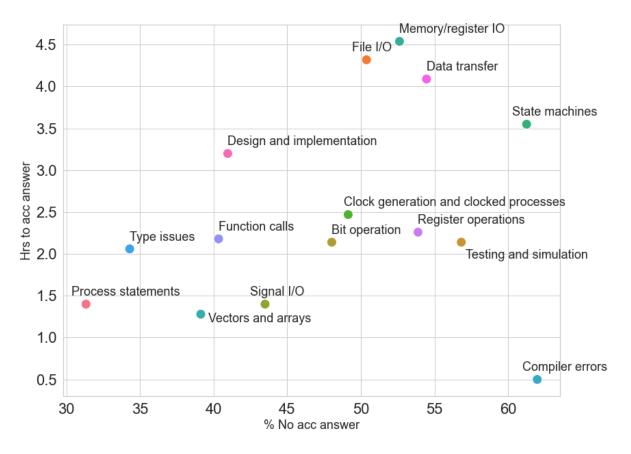

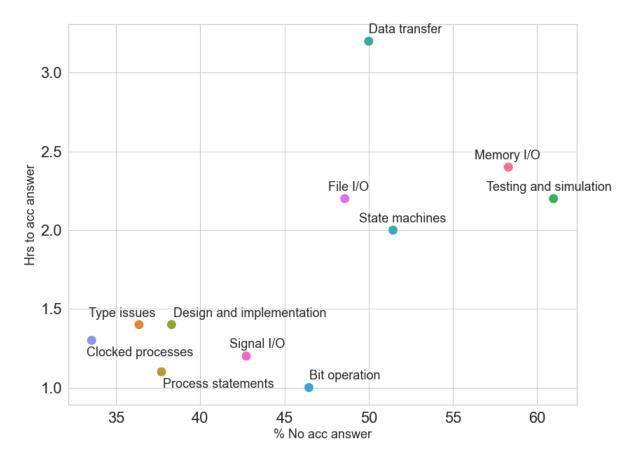

We estimate the difficulty level of HDL-related questions by determining whether and how fast a question receives an accepted answer. We observe that HDL-related questions are less likely and take longer than questions related to GPPLs to get accepted answers. Besides, the most difficult topics (e.g., *file/memory IO*, *data transfer*, *state machines*, *syntax errors*, and *testing and simulation*) are consistent across different languages.

## 1.2 Studying the practices of developing HDL programs by mining open-source projects that leverage hardware acceleration for DNN

Deep Neural Networks (DNNs), also known as Deep Learning, are a subset of AI, which, according to John McCarthy, the computer scientist who invented the phrase in the 1950s, is "the science and engineering of constructing intelligent computers that can achieve goals as people do". DNNs are the cutting-edge solutions for various applications, including computer vision, speech recognition, and natural language processing, among others. Artificial Neural Networks (ANNs) are a mathematical architecture that connects a vast number of essential elements known as neurons, each of which can make simple mathematical decisions [9]. An external neural network has only three layers: the input layer, one hidden layer, and the output layer. As the number of hidden layers in a neural network grows, it becomes a Deep Neural Network (DNN). As a result, Deep Learning can be thought of as a subset of Artificial Neural Networks with many processing layers. They are more precise and continue to improve as more neuron layers are added. Feed-Forward Neural Network, Recurrent Neural Network (RNN), and Convolutional Neural Network (CNN) are three popular Deep Neural Network models [9].

However, DNNs' increased accuracy comes at the cost of significant computational complexity. While general-purpose compute engines, particularly graphics processing units (GPUs), have been the basis for much DNN processing, there is growing interest in more specialized DNN acceleration. Over the last two decades, many DNN models have been built. A DNN model is typically very complex and takes long time and expensive resources to perform training and inferences. Thus, researchers and practitioners have proposed various approaches to make DNN model training and inferences more efficient. These approaches typically fall into two categories: 1) model optimization (the software way) and 2) hardware acceleration (the hardware way). There has been recent evidence from the field of deep learning that FPGAs (Field-Programmable Gate Arrays) are an important factor in the acceleration of DNNs (Deep Neural Networks). An HDL (Hardware Description Language) vendor tool is used to synthesize DNN from a high-level language such as python after manual transformation. HDL expertise is required for this transition, which limits the use of FPGAs [10]. In data centers, FPGAs are now widely used to offload GPU- and CPU-based inference engines. Starting with targeted FPGAs, model development and optimization frameworks, and an ecosystem of supported libraries, we are still in the early stages of defining, expanding, and deploying such capabilities. Over the next five years, FPGA capabilities are expected to rapidly improve, allowing them to tackle a wide range of real-world applications [9]. In this thesis, we investigate hardware acceleration for DNN projects to answering the following research questions (RQs):

## RQ 2.1: What are the categories of the projects that leverage hardware acceleration for DNN?

To determine the type of models used in the projects, we manually examined 321 projects linked to hardware acceleration for DNN on GitHub. We also look at the kind of tasks that may be aided by employing hardware acceleration.

# RQ 2.2: What are the distributions of programming languages and developer profiles in the projects leveraging hardware acceleration for DNN?

We extracted the programming languages used in the DNN hardware acceleration projects and determine the portions of code corresponding to HDL and GPPL languages. In addition, we collected and analyzed information about developers' activities to identify their area of expertise.

# RQ 2.3: What are the purposes of using hardware acceleration in the projects leveraging hardware acceleration for DNN?

The description of 321 DNN hardware acceleration projects were manually inspected in order to identify the purpose of using hardware acceleration in these projects.

## 1.3 Contributions of the Thesis

In summary, this thesis makes the following contributions:

- We observe that developing HDL programs face similar challenges as GPPL and identified challenges specific to HDLs (e.g., lower level operations such as bit and register operations or synchronization through clocked processes).

- We also observe that it is more challenging for developers of HDL programs to receive community support than GPPL (i.e., HDL-related questions are less likely and take longer to get accepted answers), which calls for efforts to enhance developer engagement or platform support in answering questions in technical forums (e.g., SO).

- Our work identified opportunities for the research community to improve the practices of developing HDL programs, such as to improve the language abstraction for handling bit/register operations or file/memory I/Os, provide actionable information to address syntax errors, and-or to develop tools to improve testing and simulation.

- We investigate an application domain of hardware-software co-design: DNN hardware acceleration, and the practices of real-world open source projects in this domain. Our results provide insights for practitioners and researchers to understand the practices of DNN acceleration as well as the practices and challenges of hardware-software co-design in this context.

## 1.4 Organization of the Thesis

The remainder of this thesis is organized as follows: Chapter 2 introduces the concepts and background that help to understand our research work related to hardware description languages and DNN hardware acceleration. Chapter 3 examines the challenges of developing Hardware Description Language Programs. Chapter 4 examines DNN hardware acceleration practices in GitHub projects. Finally, Chapter 5 summarizes and concludes the thesis, and discusses future work.

#### CHAPTER 2 BACKGROUND AND LITERATURE REVIEW

#### 2.1 Background

We first introduce some background related to our work, including the background on hardware description languages and hardware acceleration for DNN.

#### 2.1.1 Background on Hardware Description Languages (HDL)

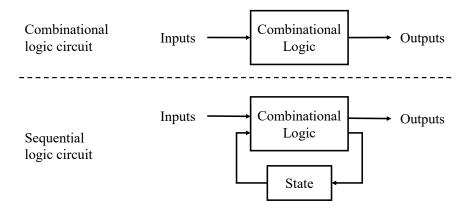

Hardware Description Languages (HDLs) are programming languages used to describe the structures and behaviors of digital logic circuits, which are the essential components of modern computer systems [11]. As illustrated in Figure 2.1, there are two types of digital logic circuits: combinational logic circuits and sequential logic circuits. The inputs fully determine the outputs of a combinational logic circuit. Examples of the combinational logic includes the basic *and*, *or*, and *xor* gates and calculators for which outputs only depends on the inputs. The outputs of a sequential logic circuit are determined by both the inputs and a previous state. Examples of sequential logic include flip-flops and register circuits. A sequential logic circuit needs a mechanism to control the timing of updating the state, either synchronously or asynchronously; thus, sequential logic is further divided into synchronous and asynchronous logic. The synchronous logic synchronizes the state changes by using a clock signal, while the state changes in the asynchronous logic can occur in response to changes in the inputs.

HDLs typically support both combinational logic and sequential logic [3]. Thus, the most significant difference between HDLs and GPPLs is the explicit inclusion of the notion of time in HDLs [11]. The most popular HDLs include Verilog [12], VHDL [13], and SystemVer-

Figure 2.1 Illustration of combinational logic circuits and sequential logic circuits

ilog [14]. Verilog is the dominant HDL adopted by practitioners [3]. Verilog can describe, verify, and simulate digital logic circuits its structure is inspired by C. It possesses most of the same features as C, including a preprocessor, control flow, and operators. SystemVerilog is an enhanced version of Verilog that extends Verilog by adding a rich and robust type system, especially for user-defined systems, while still keeping weak typing for the built-in Verilog types [15]. System-Verilog also extends Verilog by providing capabilities for interface abstraction and packaging [15]. VHDL is another popular HDL, providing similar functionalities as Verilog. However, VHDL is derived from the Ada programming language, and it is firmly and richly typed. VHDL is usually more verbose than Verilog [15].

#### 2.1.2 Background on Hardware Acceleration for DNN

Deep Neural Networks (DNN) have recently proved to be one of the most powerful machine learning methods. DNNs owe their efficacy to their ability to learn complex models. Thus, researchers and practitioners have proposed various approaches to make DNN model training and inferences more efficient. There are two main approaches to improving DNN methods. The model optimization methods are used in the first approach, which focuses on software solutions. The Tensorflow Model Optimization Toolkit [16] is one of the tools in softwarebased approaches with a concentration on aspects like post-training quantization, weight clustering, quantization aware training, etc. [16]. The second approach, which we will focus on in this study, is hardware-based methods concentrating on hardware acceleration. Hardwares (including FPGA) are typically designed/programmed by hardware description languages (HDLs) such as Verilog. A multi-language system that provides a framework for developing solutions to these intellectual problems is presented by the authors of [2,3] in their discussion of the challenges that researchers interested in hardware description language, compilers, and formal methods face. They identify opportunities to apply programming language techniques to address productivity issues in hardware design. One of the best-known solutions in this category is Microsoft Azure FPGAs [17]. With Microsoft Azure FPGAs, developers will be able to deploy machine learning models to field-programmable gate arrays (FPGAs).

#### 2.2 Literature Review

In this section we review the related literature on domain-specific architectures, HDL development, technical forum analysis, and hardware acceleration for DNN.

#### 2.2.1 Domain-Specific Architectures

With Moore's law and the Dennard scaling ending, general-purpose architectures (e.g., RISC CPU) are becoming insufficient to handle our growing needs for high-performance computing [2–4]. According to Turing award winners John Hennessy and David Patterson, computer architectures are at the point of shifting from a general-purpose approach to a domain-specific hardware/software co-design approach [2]. Domain specific architectures (e.g., Google's TPU, Apple's Neural Engine, or Microsoft's FPGAs for deep neural networks), trading off specificity for flexibility, are more closely tailored to the application and thus can achieve (order(s) of magnitude) higher efficiency [18,19]. For example, prior work has proposed domain-specific architectures to accelerate the training and inference of deep neural network models [20–24]. In addition, domain-specific architectures have found applications in a wide range of other emerging domains that require intensive and efficient computations, such as security [25], image processing [26, 27], simulation [28], bioinformatics [29], and big data [30]. Developing such domain specific architectures typically requires writing programs in HDLs which are then compiled into specifications of hardware units (e.g., transistors) and their interconnections [3]. The increasing demand and applications of domain-specific architectures motivate us to study the challenges and opportunities in HDL program development.

#### 2.2.2 HDL Development

Prior work improves the practices of HDL development from two aspects: 1) HDL design and 2) HDL compilers and transpilers. The first line of work aims to improve the design of HDL. In particular, recent studies have explored the opportunities of leveraging the advances in GPPLs (e.g., meta-programming) to improve HDL [7,31–38]. For example, *Chisel* [31] and *Magma* [32] are HDLs based on the GPPLs Scala and Python, respectively, by embedding hardware units in these GPPLs through meta-programming. The HDL *SystemC* [39] is derived from C++ by providing a set of classes and macros for system-level design, modeling, and verification. *ASystemC* [37] extends *SystemC* by adding the features of Aspect Oriented Programming (AOP). Truong and Hanrahan [3] propose a vision for future HDLs that is based on a meta-programming language, an embedded HDL, and a variety of domain-specific languages.

Another line of work targets HDL compilers [40–45] and transpilers [36, 46–48]. To improve the development of compilers, prior studies have developed common infrastructures (e.g., intermediate representations, or IR) for HDL compilers [40, 41, 43–45]. Prior studies have also developed approaches to transform GPPLs to HDLs or vice-versa (i.e., transpilers). For example, Quokka [47] is a transpiler that can transform C# to HDLs. In contrast, Verilator [46] can transforms Verilog and SystemVerilog to C++. Despite these efforts in HDL language development, prior work did not investigate the practical issues faced by HDL developers. Therefore, this work examines the questions and answers in technical forums such as SO to understand developers' challenges when developing HDL programs.

#### 2.2.3 Technical Forum Analysis

Extensive studies have been performed to study posts in technical forums, in particular, the Stack Exchange forums [49]. Here we focus on the studies that are most relevant to our work: 1) studies that analyze the categories of questions and 2) studies that analyze the topics of questions.

#### Categorization of technical forums questions.

Prior studies have investigated the categories of technical forum questions [1, 50-54].

For example, Rosen and Shihab [51] manually studied a random sample of 384 SO questions related to mobile development and derived four categories of questions: *why, how, what,* and *other*. Beyer et al. [1] surveyed these studies [50–54] and summarized a categorization of SO questions, including seven categories of questions: *API usage, discrepancy, errors, review, conceptual,* and *API change.* In this work, we study the categories of HDL-related questions on two Stack Exchange forums, and we base on the categorization of the work of Beyer et al. [1].

#### Topic analysis of technical forum posts.

Topic models are used extensively in prior work to understand the topics of general technical forum posts and the topic trends [55], [56], [50]. Prior work also leverages topic models to understand the topics of technical forum posts related to specific application development domains, such as mobile application development [51,57], client application development [58], concurrent programming [59], security-related development [60], big data development [61], Swift programming [62], IoT development [63], and deep learning development [64]. In addition, prior work leverages topic models to understand non-functional requirements communicated in technical forum posts [65, 66]. Zhang et al. [67] use topic models to detect duplicate questions in technical forums. Finally, Treude et al. [68] proposes an automated approach to suggest configurations of topic models for analyzing technical forum data. Most of these studies use the Latent Dirichlet Allocation (LDA) algorithm or its variants to extract topics from the text of the technical forum posts. In this work, we also leverage the LDA

algorithm to extract topics from technical forum posts related to HDLs. The increasing demand for domain-specific architectures calls for our emphasis on HDL program development. However, no work exists that studies the practical issues faced by HDL developers. Therefore, this work makes an initial effort to study the challenges of HDL program development and identify opportunities to address these challenges.

#### 2.2.4 Hardware acceleration for DNN

Hardware acceleration refers to the technique of moving a complex computing operation from the CPU to specialized hardware in order to achieve greater efficiency than would be possible with a traditional software implementation of the same task. Better models and a larger dataset are needed to get real-time results that are as precise as possible. Taking time to make a decision is also vital. Deep Learning models become increasingly complicated as they evolve. A large number of procedures and parameters, as well as increased computational resources, are required as a result of this expansion. GPUs, ASICs, and FPGAs are examples of hardware accelerators [9]. The Versatile Tensor Accelerator (VTA) is a deep learning accelerator that is open, generic, and adaptable, according to the authors of [69]. Brandon Reagen et al. [70] have introduced Minerva, a highly automated co-design technique to improve DNN hardware accelerators across the algorithm, architecture, and circuit levels. Authors of [71] have provided a comprehensive comparison of model compression methods and hardware acceleration methods. They describe various hardware platforms used for DNNs and explain different optimizations applied to improve throughput.

To speed up the simulation of ResNet networks using approximate multipliers, Filip Vaverka et al. [72] developed a Tensor Flow extension TFApprox. Vojtech et al. [73] demonstrate how a large number of approximate multipliers can be applied to do a resilience study of a ResNet DNN hardware accelerator and to choose the best approximate multiplier for a specific application. According to Charles Mackin and colleagues [74], a methodology for selecting the best hardware circumstances under which to program weights, and its usefulness in the face of substantial NVM variability, is examined via simulations. For wearable devices, Johnson Loh et al. [75] designed a DSP (digital signal processing) accelerator for ECG data categorization. An infrastructure for analyzing and exploring the architectural design space of deep neural network (DNN) accelerators has been developed by Angshuman Parashar et al [76]. A research by Siva Kumar Sastry Hari et al. [77] examines the propagation of soft mistakes in DNN systems and proposes two effective protective measures to reduce their influence and increase dependability. Using a cycle-accurate simulator called SCALE-SIM, Ananda Samajdar et al. [78] provide an analytical methodology for determining the best scale-up vs. scale-out ratio for DNN inference given hardware restrictions. Maria I. Mera Collantes et al. [79] proposed a Safe-TPU implementation with high parallelism and reuse of current resources already deployed in the baseline DNN accelerator, as well as additional protocol innovations that considerably decrease the space and time necessary to construct proofs.

FPGA-based accelerators are more popular than GPU and ASIC-based accelerators due to their high performance, customizable and flexible design, high throughput with large parallelism, faster data transfer, and high speed of a DNN implemented on them [9]. Storage, computational resources, and memory bandwidth are all concerns that must be addressed when DNNs are implemented on FPGAs. The accuracy, latency, throughput, and portability of the implementation are all used to evaluate the mapping of DNNs into FPGAs [10]. Some of the effort in this field is centered on developing automated tools for rapidly deploying DNNs to FPGAs. X. Wei et al. [80] the design of a framework using systolic arrays to accelerate DNN inference. To ensure diverse network setups, the framework adopts a uniform RTL design for CONV layers and runs software in the host CPU [81]. However, the Fully-connected (FC) layers are not implemented on FPGA. Other frameworks for autonomously mapping DNNs onto FPGAs using RTL [82,83] or RTL-HLS [84] templates have been proposed. Zhang et al. [85] have developed DNNBuilder, a tool for automatically developing high-performance DNN hardware accelerators on FPGAs to bridge the gap between quick DNN generation in software (e.g., Caffe, TensorFlow) and sluggish hardware implementation. FPGA-based accelerators are more cost-effective than GPU and ASIC-based accelerators. Noronha et al. provide an open-source tool-flow for transferring DNN numerical computing models developed in Tensorflow to FPGA [86]. V. Sze and A. Shawahna et al. [87, 88] provide tutorials and surveys of hardware acceleration for DNN. There are also many open-source projects on FPGA-based model acceleration [89].

Prior work proposed different approaches that use hardware acceleration to improve DNN model performance. However, no prior work has studied how hardware acceleration is used in real-world DNN projects. Thus, this work studies open-source GitHub projects that uses hardware acceleration for DNN, to understand the practices and challenges of DNN hardware acceleration.

## CHAPTER 3 STUDYING THE CHALLENGES OF DEVELOPING HARDWARE DESCRIPTION LANGUAGE

The content of this chapter is currently under review for publication in the Information and Software Technology Journal<sup>1</sup>.

**Context:** As Moore's law and the Dennard scaling ended, general-purpose architectures (e.g., RISC CPU) are becoming insufficient to handle our growing needs for high-performance computing. Domain specific architectures (e.g., Google's TPU) are more closely tailored for specific applications and thus can achieve better performance. Developing such domain specific architectures typically requires writing programs in Hardware Description Languages (HDLs). Compared to traditional general-purpose programming languages (GPPLs) (e.g., C++, Java, Python), developing programs in HDLs (e.g., VHDL or Verilog) lacks support from our community. Such an imbalance in the support for GPPLs and HDLs will impede future advances in computer systems.

**Objective:** We believe that our software engineering community should pay more attention to supporting HDL development. Thus, we make an initial attempt in this direction to study the challenges of developing programs in HDLs by mining HDL-related questions in technical forums.

**Method:** We identified 16,700 HDL-related questions in two Stack Exchange forums: Stack Overflow (SO) and Electrical Engineering (EE) Stack Exchange. We examined the types of questions, the questions' topics, and identify the most challenging topics for developers.

**Results:** We identified ten types of HDL-related questions, including seven types identified in prior work and three new types more relevant to HDLs (e.g., questions related to code explanation and tool search). We also observed that most of the challenges facing HDL developers are similar to those facing GPPL developers, while some challenges (e.g., lowerlevel operations such as bit and register operations) are more specific to HDLs. Finally, we observed that HDL-related questions are less likely and take a longer time to get accepted answers than GPPL-related questions, and identified the most challenging topics of questions (e.g., file/memory I/O).

**Conclusion:** Our work identified opportunities for the research community to improve the practices of developing HDL programs, such as to improve the language abstraction of handling bit/register operations or file/memory I/Os, to provide actionable information to ad-

<sup>&</sup>lt;sup>1</sup>Fatemeh Yousefifeshki, Heng Li, Foutse Khomh, Studying the Challenges of Developing Hardware Description Language Programs, Information and Software Technology, 2022 (under review).

dress syntax errors, or to develop tools to improve testing and simulation. We hope that our work can draw the software engineering community's attention to HDLs and prevent HDLs from becoming the bottleneck in developing future computer systems.

#### 3.1 Introduction

Modern computer systems typically consist of two indispensable components: general-purpose hardware (e.g., CPU) and highly-versatile software (e.g., web applications). Software talks to hardware through a concise vocabulary called an instruction set architecture (ISA) (e.g., the reduced instruction set computer or RISC) [2]. Compilers (e.g., GCC) convert programs written in high-level programming languages (e.g., C++) into machine-readable programs based on the ISA-defined vocabulary. Advances in ISA and compilers allow modern computer systems to achieve highly-diverse functionalities through general-purpose hardware and highly-customizable software applications.

However, with Moore's law and the Dennard scaling ending, it has been increasingly difficult to increase the number of transistors on a chip, which poses critical challenges to enhancing the computing power of general-purpose architectures (e.g., RISC) [2–4]. In this context, Turing award winners John Hennessy and David Patterson, in their recent Turing lecture, declared that computer architectures are at the point of shifting from a general-purpose approach to a hardware/software co-design approach [2]. Domain specific architectures (e.g., Google's TPU, Apple's Neural Engine, or Microsoft's FPGAs for deep neural networks) are more closely tailored to the application domain and can provide new opportunities to improve the performance of computer systems. Developing such domain specific architectures typically requires writing programs in hardware description languages (HDLs) (e.g., VHDL, Chisel, or Verilog), which are then compiled into specifications of hardware units (e.g., transistors) and their interconnections [3]. For example, Google uses Chisel to develop Edge TPU. However, there exists an imbalance between the support for HDL program development and that for developing programs in traditional GPPLs (e.g., C++, Java, Python) [2–4]. We believe that such an imbalance in GPPLs and HDLs will impede future advances of computer systems, in particular, in domain-specific applications; thus, our SE community should pay more attention to supporting HDL program development.

This work makes an initial attempt to understand the challenges of developing HDL programs and explore opportunities for the SE community to support the practices of HDL program development. Developers usually ask and answer technical questions on technical forums such as Stack Exchange forums<sup>2</sup>. These questions may communicate challenges faced by developers when developing HDL programs. Therefore, this work identifies and analyzes over 16, 000 HDL-related questions from two Stack Exchange forums: Stack Overflow (SO) and Electrical Engineering (EE) Stack Exchange. We analyze these HDL-related questions using qualitative analysis and automated topic modeling to understand the challenges developers face when developing HDL programs. Our study is organized by answering the following three research questions (RQs):

## RQ1: What types of questions do developers ask about HDL?

We manually examined 376 statistically significant representative samples of HDL-related questions posted in the SO and EE forums to understand the types of information sought by developers about HDL program development. Our findings indicate the need for more resources and tools to aid developers in understanding, verifying and diagnosing issues in HDL programs.

## RQ2: What are the topics in the HDL-related questions?

We use topic models to derive the semantic themes included in developers' questions to understand developers' challenges in developing HDL programs. We observe that HDL program development shares most of the challenges (e.g., syntax issues) of GPPL program development. However, some challenges (e.g., lower level operations such as bit and register operations or synchronization through clocked processes) are only notable for HDLs.

## RQ3:What questions are difficult for developers to get answers?

We estimate the difficulty level of HDL-related questions by determining whether and how fast a question receives an accepted answer. We observe that HDL-related questions are less likely and take longer than questions related to GPPLs to get accepted answers. Besides, the most difficult topics (e.g., *file/memory IO*, *data transfer*, *testing and simulation*, and *state machines*) are consistent across different languages.

Our work highlights the challenges of HDL program development (e.g., lower level operations such as bit and register operations or synchronization through clocked processes). It identifies opportunities for the research community to improve the practices of HDL program development, such as to improve the language abstraction of handling file/memory I/Os, provide actionable information to address syntax errors, or develop tools to improve testing and simulation. We hope to draw the SE community's attention to the importance of HDL program development which may become a bottleneck in developing domain-specific systems that are critical in increasing computing power in the future. We encourage researchers and practi-

$<sup>^{2} \</sup>rm https://stackexchange.com$

tioners in the SE community to leverage the advanced methodology, techniques, and tools in traditional software development to improve the practices of HDL program development. To encourage and help future research, we share our replication package<sup>3</sup>

**Chapter organization.** The rest of the chapter is organized as follows. In Section 3.2 we describe the experiment setup of our study. In Section 3.3, we present and discuss our results for answering our research questions. In Section 3.4, we discuss the implications of our findings. Section 3.5 discusses threats to the validity of our findings. Finally, Section 3.6 we have a summary of the study.

#### 3.2 Experiment Setup

This study aims to understand the challenges faced by developers during HDL program development. The perspective is that of researchers and practitioners interested in developing methodologies, techniques, and tools to support the development of HDL programs.

#### 3.2.1 Context of the Study

To understand the challenges of developing HDL programs, we study Stack Exchange forums where developers ask and answer technical questions, including HDL-related questions. We manually examined all the Stack Exchange forums<sup>4</sup> to identify the ones that contain HDLrelated questions. Specifically, we first read the description of each forum to identify the ones that may potentially contain HDL-related questions. Then, we searched HDL-related keywords (e.g., "VHDL", "Verilog") in these forums to confirm whether they indeed contained HDL-related questions. In the end, we found two Stack Exchange forums that contain HDLrelated questions:

- Stack Overflow  $(SO)^5$  is a technical Q&A forum for professional, enthusiast, and student programmers .

- Electrical Engineering (EE) Stack Exchange<sup>6</sup> is a technical Q&A forum for electronics and electrical engineering professionals, students, and enthusiasts.

This work extracts and studies the HDL-related questions in these two Stack Exchange forums to understand the challenges of developing HDL programs.

<sup>&</sup>lt;sup>3</sup>Replication package: https://github.com/mahkamehy/Developing-HDL-program.

<sup>&</sup>lt;sup>4</sup>https://stackexchange.com/sites

<sup>&</sup>lt;sup>5</sup>https://stackoverflow.com

$<sup>^{6} \</sup>rm https://electronics.stackexchange.com$

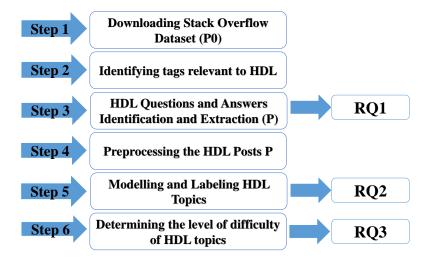

Figure 3.1 shows an overview of our data extraction and analysis process. We first download the datasets of SO questions and answers using SOTorrent [90] and EE questions and answers using Stack Exchange Data Explorer [91] (Step 1).

Then, we identify the tags related to HDL and the related questions and their answers (Steps 2 and 3). A random sample of the questions is used to study the categories of HDL-related questions (RQ1). Then, we preprocess all the HDL-related questions and answers (Step 4) and use topic modeling to extract topics from these questions and answers (Step5). We analyze the topics to answer RQ2. Finally, we analyze the level of difficulty of the HDL questions related to different topics (Step 6) and answer RQ3. Below, we describe each of these steps in detail.

Figure 3.1 An overview of our data extraction and analysis process.

### 3.2.2 Data extraction and analysis steps

The SO and EE forums are selected because they include HDL-related postings and are commonly used for studying different GPPL and HDL topics [92].

### Step 1 - Downloading SO Datasets.

We used SOTorrent [90] to download a dataset of SO  $(P_0)$  containing questions, their associated answers, and the associated metadata. The dataset was downloaded in May 2021.

**Downloading EE datasets.** We used Stack Exchange Data Explorer [91] to collect data  $(P_0)$  containing questions, answers, and metadata from the EE forum. The dataset includes questions and answers that were posted until December 2021. In both forums (SO and EE), for each question in the dataset, we obtain the question id, the title, the tag names, the

question body, the creation time of the question, the view counts, the scores, the accepted answer body (if any), and the creation time of the accepted answer (if any). Each question can have up to five tags. An answer to a question is accepted, provided that the question's creator voted it as accepted.

#### Step 2 - Identifying SO and EE tags relevant to HDLs.

To identify and extract HDL-related questions on both SO and EE, we need to identify a set of SO and EE tags related to HDLs. We follow the process used in prior work [93] to identify the set of HDL-related tags for both SO and EE forums. While we follow the same process to identify the HDL-related tags in the SO and EE forums, the tags of these two forums are identified separately. The initial HDL tag set  $T_i$  was derived from the most popular HDLs described in the background, i.e., tags "vhdl", "verilog", and "system-verilog". Then, the three tags in  $T_i$  were used to extract from each forum's dataset  $P_0$  the set of questions Qassociated with these tags. In the next step, we extract all the tags in the question set Qto form a more extensive set of tags  $T_j$ . It should be noted that not all the tags in  $T_j$  are related to HDLs. Thus, we follow prior work [93] and use some heuristics to filter the tags in  $T_j$  based on their relationships with the initial tag set  $T_i$ . For each tag t in  $T_j$ , we use the significance and relevance scores defined below to determine if it is a HDL-related tag:

(Significance)

$$S(t) = \frac{\# \text{ of questions with tag } t \text{ in } Q}{\# \text{ of questions with tag } t \text{ in } P_0}$$

(3.1)

(Relevance)

$$R(t) = \frac{\# \text{ of questions with tag } t \text{ in } Q}{\# \text{ of questions in } Q}$$

(3.2)

For a tag t to be selected, the value for significance (S(t)) and relevance (R(t)) should be higher than a threshold. Based on prior work [93] and our experiments using different thresholds, we finally set the optimal threshold for S and R as 0.2 and 0.005 respectively. We further performed a manual inspection of the description and the top voted questions of each of the selected tags and identified those that are genuinely associated with HDLs: we only keep a tag in our final set if it is associated with one HDL programming language (e.g., "vhdl").

Finally, our tag set  $T_{final}$  for SO includes the tags: "vhdl," "verilog," "system-Verilog," "systemc," "chisel," "lava," "hdl," "vpi," "system-verilog-dpi," "systemverilog-assertions". Our final tag set  $T_{final}$  for the EE forum includes the tags: "vhdl," "verilog," "system-verilog," and "hdl".

#### Step 3 - HDL Questions and Answers Identification and Extraction.

We used the tag set  $T_{final}$  identified in Step 2 to extract the HDL-related questions from

the SO and EE datasets  $P_0$ . In the end, we extracted 13,300 and 3,400 questions and their corresponding answers from the SO and EE forums, respectively, as our final data set P. A statistically representative 376 sample of these questions is manually examined to identify type of questions to answer our RQ1.

#### Step 4 - Preprocessing the HDL Posts.

In this step, the final post set P was preprocessed for topic modeling (Step 5). The process began by joining the title of each question and the question and answers' body text to generate one coherent final body. An issue with the extracted post texts was that they contained HTML tags (such as tags representing a paragraph, URL, etc.) and code snippets. Therefore, HTML tags like  $\langle p \rangle \langle /p \rangle$  and  $\langle a \rangle \langle /a \rangle$  and code snippets created by  $\langle code \rangle \langle /code \rangle$  were removed from the post text. A further step was taken to remove stop words such as numbers, articles ("a," "an," and "the"), different forms of "be" ("is," "are," "been," etc.), punctuation marks, as well as symbols and non-alphabetical characters, as recognized by the MALLET's stop words list. As the final step of the process, the Porter stemmer [94] was used to clip words to their stemmed representation. We used stemmer insted of lemmatization because it can use on a large scale to improve search results. By searching not only the search phrase alone but also the word stems in the index, different word forms can be overcome and the search can also be greatly accelerated. For instance, a word like "developer" was reduced to "develop," and words like "configuration," "configure," and "configured" were all cut short to "configr."

#### Step 5 – Modelling and Labeling HDL Topics.

In this step, we extracted the HDL topics from the preprocessed questions and answers from the previous step (Step 4). We use the Latent Dirichlet Allocation (LDA) [95] algorithm implemented by the MALLET [96] toolkit<sup>7</sup>. LDA is a probabilistic topic modeling technique that models a topic based on a set of words co-occurring frequently. To enhance the quality of topic modeling results, both uni-grams and bi-grams were considered as *words* in our topic modeling process [97].

Three main hyper-parameters are typically configured to control the topic modeling results, including K,  $\alpha$ , and  $\beta$ , where K controls the number of topics,  $\alpha$  controls the topic distribution in the documents (i.e., SO posts in our context), and  $\beta$  controls the word distribution in the topics. Our used MALLET LDA implementation can automatically search for the optimal  $\alpha$  and  $\beta$  values. We experiment with different K values (from 5 to 40 incremented by one each time) to find the best K according to a coherence score which estimates the quality of a topic by measuring the semantic similarity between the top words in the topic [98]. We

<sup>&</sup>lt;sup>7</sup>Specifically, we used the Gensim wrapper of MALLET: gensim.models.wrappers.LdaMallet

use the resulting topics with the highest average coherence score as our final topics. After the automated topic modeling process generated the topics, we manually examined the resulting topics to derive a meaningful label for each topic. To assign a meaningful label to a topic, one author of this study first derived a label according to (1) the topic's top 20 keywords and (2) the top 10-15 most relevant questions associated with the topic. Then, the three authors of the study reviewed the labels together in a meeting and reassigned the labels when needed. The resulting topics from this step are analyzed to answer our RQ2.

#### Step 6 - Determining the level of difficulty of HDL topics

In this step, to understand how challenging and demanding the topics may be to developers, the difficulty level of each topic was estimated by two widely used heuristics [51, 52, 60, 61]: the percentages of questions of the topic receiving an accepted answer and the time taken for these questions to receive an accepted answer. Intuitively, a more complicated topic is when the related questions receive fewer accepted answers after a long waiting time. The estimated difficulty level of the topics is used to answer our RQ3.

#### 3.3 Experiment Results

In this section, we report and discuss the results of our three research questions. We first present the motivation and approach for each research question, then discuss the results for answering the research question.

#### RQ1: What types of questions do developers ask about HDLs?

#### Motivation

As part of our effort to better understand developers' challenges, we should first discover the types of questions they are asking. This is important because it allows us to identify the types of help HDL developers seek (i.e., the areas where developers need more assistance).

In particular, we focus on the intent behind the questions asked by developers instead of the topics of the questions, similar to prior work [1].

#### Approach

To understand the type of HDL-related questions developers ask in the studied technical forums, we first calculate the distribution of the programming languages involved in the questions, then manually analyze a statistically representative sample of the questions to understand the developers' intent behind these questions. Calculating the distribution of HDL programming languages in the questions. Each of the 16,700 HDL-related questions that we identified (i.e., Step 3 in Section 3.2) is associated with several tags, including at least one HDL programming language tag<sup>8</sup> (e.g., "vhdl"). To understand the distribution of programming languages in the HDL-related questions, we count the number of questions associated with the corresponding tag for each language. Please note that one question may be associated with more than one programming language tag.

Sampling of questions for manual analysis. To further understand the categories of developers' questions, we perform a manual analysis on a statistically representative sample of the HDL-related questions. Specifically, we randomly sample 376 questions from the two forums using a stratified sampling approach. This sample represents a 95.0% level of confidence within a 5.0% confidence interval.

Hybrid card sorting process. We adopted a hybrid card sorting process [99] to derive the categories of HDL-related questions manually. This manual analysis was based on the question categories derived in an earlier study [1]. One label was assigned to each question, and if a question is related to more than one label, which is rarely the case, the most relevant one was selected. In a joint effort, the three authors performed hybrid card sorting. The sample data were randomly divided into three equal groups of questions, and the card sorting process was done in two independent rounds, which was similar to an earlier work [100]. This method of card sorting ensures that at least two authors examine all questions.

In the first round, each author independently examined and assigned labels to one-third of the questions (i.e., one of the random groups). After that, we had discussions to ensure that all authors do a consistent labeling method. We reached a set of agreed-upon labels during these discussions. We then revisited our labels based on our consistent understanding and the agreed-upon labels.

In the second round, each author labeled another one-third of the questions, which were labeled by the other two authors in the first round. To avoid bias, each half of the one-third questions (i.e., one-sixth of the total questions) was randomly drawn from another author's previously labeled questions in the first round. We made sure that each question was labeled by two authors in the two rounds combined. We based our labeling on the results from the first round, but the authors were free to assign new labels in this round. After the individual labeling, the second round of discussions was held to analyze the second-round labeling results and verify the assigned labels' consistency. To finalize the process of labeling the

$<sup>^{8}\</sup>mathrm{As}$  described in Section 3.2, we only kept the tags that are associated with HDL programming languages in our final tag set.

questions, each author revisited its labels according to the second-round discussions. Finally, we arranged another meeting to resolve the disagreement on the labeling results and decided on the final agreed-upon label for each question.

#### Results

Developers' questions are dominantly related to VHDL, Verilog, and System Verilog. Table 4.4 shows the distribution of questions related to each hardware description language. In the two studied forums, VHDL is associated with most of the questions (i.e., 42.2%), followed closely by Verilog, which is associated with 40.5% of questions, and System Verilog, which is associated with 16.7% of questions. Questions associated with at least one of these top three languages account for 93.0% of all the questions; questions associated with at least one of the top five languages account for 98.0% of all the HDL-related questions. There is a minimal number of questions associated with some less-popular languages, such as VPI and Lava, which are associated with only 15 (0.1%) and 11 (0.1%).

Table 3.1 The distributions of programming languages (tags) involved in the HDL-related questions.

| Language        | VHDL                | Verilog             | SystemVerilog    | HDL                                              | Chisel            | SystemC                                           | SystemVerilog<br>Assertions | SystemVerilog<br>DPI | VPI                                           | Lava                                           | Total               |

|-----------------|---------------------|---------------------|------------------|--------------------------------------------------|-------------------|---------------------------------------------------|-----------------------------|----------------------|-----------------------------------------------|------------------------------------------------|---------------------|

| SO Questions    | 5,544<br>(41.6%)    | 5,346<br>(40.1%)    | 2,651<br>(19.9%) | $  \begin{array}{c} 819\\ (6.1\%) \end{array}  $ | $565 \\ (4.2 \%)$ | $ \begin{array}{c c} 265 \\ (1.9\%) \end{array} $ | 158 (1.1%)                  | $49 \\ (0.3\%)$      | $\begin{vmatrix} 15 \\ (0.1\%) \end{vmatrix}$ | $\begin{vmatrix} 11 \\ (0.1\%) \end{vmatrix}$  | 13,300<br>(100%)    |

| EE Questions    | $1,701 \\ (43.9\%)$ | $1,616 \\ (41.7\%)$ | 310<br>(8.0%)    | $\begin{vmatrix} 240\\ (6.2\%) \end{vmatrix}$    | -                 | -                                                 | -                           | -                    | -                                             | -                                              | 3,867<br>(100%)     |

| Total Questions | 7,245<br>(42.2%)    | $6,962 \\ (40.5\%)$ | 2,871<br>(16.7%) | 1,059<br>(6.1%)                                  | $565 \\ (3.2\%)$  | 265 (1.5%)                                        | $158 \\ (0.9\%)$            | 49<br>(0.2%)         | $15 \\ (0.1\%)$                               | $ \begin{array}{c} 11 \\ (0.1\%) \end{array} $ | $17,167 \\ (100\%)$ |

Note: Each question may be associated with more than one programming language tag.

Developers ask similar types of HDL-related questions as the questions related to GPPLs (e.g., Java). Table 3.2 describes the type of questions asked about HDLs on the SO and EE forums and their frequency. All seven types of questions identified in prior work [1] were also identified in HDL-related questions, indicating that developers ask similar types of questions across HDLs and GPPLs.

Compared to questions related to GPPLs, developers of HDLs ask more questions related to *error* and *reviews*, and fewer questions related to *API usage* and *API change*. In the 376 manual examined questions, the *error* category is the most frequently occurring category, accounting for 28.9% of all occurrences. Developers in HDL- related posts have more challenges related to code errors and compiler errors. Generally, questions in this category are associated with "why," e.g.,

| Category                      | Description                                                                                                                                                                                                                  | % in<br>SO | % in<br>EE | % in<br>Both |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------|

| Error                         | When creating or running HLD<br>programs, this category of<br>questions looks for explanations<br>for "why" and answers to<br>errors and exceptions.                                                                         | 30.6       | 22.3       | 28.9         |

| API usage                     | This kind of question is typically<br>characterised by the phrase "how to",<br>such as "how to utilize an API" or<br>"how to implement a function".                                                                          | 19.6       | 13.1       | 18.3         |

| Discrepancy                   | Typically, questions in this category<br>seek explanations or answers for<br>unanticipated outcomes (e.g., "what is<br>the issue", "why does it not work").                                                                  | 17.0       | 17.1       | 17.0         |