**Titre:** Techniques de routage pseudo-aléatoire pour une application micro-électronique

Title: [Techniques de routage pseudo-aléatoire pour une application micro-électronique](#)

**Auteur:** Étienne Lepercq

Author: [Etienne Lepercq](#)

**Date:** 2012

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Lepercq, É. (2012). Techniques de routage pseudo-aléatoire pour une application micro-électronique [Thèse de doctorat, École Polytechnique de Montréal].

Citation: PolyPublie. <https://publications.polymtl.ca/1006/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/1006/>

PolyPublie URL: <https://publications.polymtl.ca/1006/>

**Directeurs de recherche:** Yvon Savaria, & Yves Blaquier

Advisors: [Yvon Savaria](#), [Yves Blaquier](#)

**Programme:** Génie électrique

Program: [Génie électrique](#)

UNIVERSITÉ DE MONTRÉAL

TECHNIQUES DE ROUTAGE PSEUDO-ALÉATOIRE POUR UNE

APPLICATION MICRO-ÉLECTRONIQUE

ÉTIENNE LEPERCQ

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2012

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée :

TECHNIQUES DE ROUTAGE PSEUDO-ALÉATOIRE

POUR UNE APPLICATION MICRO-ÉLECTRONIQUE

présentée par : LEPERCQ Étienne

en vue de l'obtention du diplôme de : Philosophiae Doctor

a été dûment acceptée par le jury d'examen constitué de :

M. DAVID Jean-Pierre, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. BLAQUIÈRE Yves, Ph.D., membre et codirecteur de recherche

M. BOIS Guy, Ph.D., membre

M. HABIB Mehrez, Ph.D., membre

# Remerciements

Je remercie d'abord et avant tout mes professeurs et directeurs de thèse : Yvon Savaria et Yves Blaquièvre. Cette thèse et ces recherches n'étaient pas possible sans vous.

Je remercie l'équipe *DreamWafer*, en particulier Yan B.B, Nicolas L.M., Walder A., Olivier V. : on a énormément travaillé sur ce projet, c'était passionnant et « ça valait la peine ».

Je remercie les partenaires industriels du projet : vos exigences m'ont fait me dépasser plus d'une fois, pour des choses qui bien souvent ne se retrouvent pas dans cette thèse.

J'ai appris, et pas seulement sur le plan technique.

Je remercie les fonds de recherche MITACS ainsi que Gestion TechnoCap Inc., qui m'ont supportés financièrement tout au long de mon doctorat.

Grâce à vous, je n'ai fait aucun compromis sur mes recherches et suis resté pleinement concentré.

Je remercie ma famille : c'est plus que merci, ce chemin je l'ai fait avec vous, avec toutes vos forces, votre amour, vos espoirs aussi.

Je remercie ma femme Emanuelle F., qui m'a tant supporté (surtout sur la fin !).

Je t'aime.

# Résumé

La problématique de routage est très actuelle. On en trouve des applications dans les *GPS*, les prévisions de trafic routier, mais aussi pour le prototypage sur *FPGA*, la fabrication de puces électroniques ou le trafic *TCP/IP* sur Internet. On trouve des publications sur le sujet depuis plusieurs dizaines d'années, mais on observe actuellement une recrudescence confirmant l'actualité, l'importance et la complexité de ce problème.

Cette thèse concerne le routage et ses ressources pour une application dans un nouveau type de système micro-électronique, nommé le *WaferBoard<sup>TM</sup>*. Son noyau consiste en un circuit électronique intégré à l'échelle d'une tranche de silicium (*wafer*). Peu d'applications commerciales de la micro-électronique ont exploité ce niveau d'intégration. Ce système de prototypage rapide vise à réduire d'un ou deux ordres de grandeur le temps de développement de systèmes électroniques. Il nécessite un ensemble d'outils logiciel de support, dont un outil de routage très rapide, capable de produire des solutions valables en des temps de l'ordre de la minute, et de certaines fonctionnalités spécifiques, l'équilibrage de délai ou le reroutage à la volée, au sein d'une netlist déjà routée.

La problématique de routage pour cette application peut être imagée comme suit. Étant donné un réseau routier régulier (les routes d'Amériques du Nord en version cartésienne par exemple) et 100,000 voitures au départ lundi à 8h a.m. dans tout le pays avec des sources et destinations très variées ; calculer les chemins pour toutes les voitures de telle sorte qu'aucune ne prenne la même route dans la journée. Il est 7h59 a.m, vous avez 1 minute, et des ponts sont inaccessibles pour travaux, en voici la liste.

Cet exemple simpliste donne une idée des ordres de grandeurs de la problématique de routage que l'on cherche à résoudre pour cette application. Un algorithme de routage prend en paramètres deux structures de données : un graphe (ou réseau d'interconnexions) constitué de nœuds (sommets) et d'arcs<sup>1</sup>, et une *netlist*<sup>2</sup>, liste de nœuds électriques dont les points de départ et d'arrivée sont positionnés géographiquement. Ainsi, au lieu de voitures, il s'agit de router des signaux électriques dont les points de départ et d'arrivée sont dictés par la position des broches des composants placés sur le système de prototypage. Un réseau régulier maillé multi-dimensionnel (plus généralement appelé « réseau d'interconnexions ») sert de réseau routier dont certaines routes sont défectueuses, des ponts inaccessibles. En effet, le réseau d'interconnexions est un circuit électronique intégré à l'échelle d'une tranche de silicium complète, ce qui

---

1. Un arc relie deux sommets du graphe

2. Dans ce contexte, un *netlist* réfère à une liste d'interconnexions entre composants

implique la présence de défectuosités au sein de chaque circuit fabriqué. Contrairement aux circuits électroniques classiques, où chacun est testé et les défectueux écartés, une intégration à l'échelle de la tranche demande de fortes redondances au sein du circuit pour minimiser le taux de rejets. Pour l'application du *WaferBoard*, un certain nombre d'éléments du réseau d'interconnexions seront fort probablement défectueux sur chaque circuit produit ; l'algorithme de routage se doit de prendre en compte ces éléments très particuliers. Cette contrainte ne se retrouve pas dans les applications plus classiques des routeurs que l'on retrouve dans les *PCB*, circuits *FPGA* ou circuits *VLSI*. D'autres contraintes s'appliquent à ce projet particulier : la latence induite par la technologie est environ un ordre de grandeur plus importante que celle dans les circuits sur *PCB*, ce qui impose un routage orienté vers sa réduction. Cette contrainte explique en partie l'architecture du réseau utilisé. Au sein du *WaferIC*, la distance la plus courte n'est pas forcément celle qui offre la latence la plus petite. Cette propriété du réseau complexifie quelque peu le routage. L'équilibrage des délais au sein d'un groupe de *net* de taille arbitraire est une fonctionnalité nécessaire de l'algorithme de routage, dont la difficulté de l'approche est décuplée par les temps de calcul visés. En effet, l'intérêt du *WaferBoard* est la rapidité pour l'utilisateur de tester un circuit : le temps de mise en œuvre est extrêmement court, et estimé à quelques minutes seulement. Les temps de calculs pour le routage devront donc rester inférieurs à 10 minutes environ, soit l'ordre de grandeur acceptable par l'utilisateur.

Pour situer les travaux de cette thèse, une revue de littérature approfondie du domaine des routeurs pour les outils de conception de systèmes électroniques est réalisée dans cette thèse, pour en tirer une classification des différentes familles d'algorithmes de routage connues. Il apparaît que la majorité des approches aujourd'hui classiques appliquées aux circuits *FPGA* et *VLSI* se focalisent sur la qualité du routage final au détriment des temps de calcul qui sont donc généralement très longs. Un mouvement récent apparaît dans la littérature, qui vise la construction d'algorithmes qui routent plus rapidement sans trop perdre en qualité. Les recherches présentées dans ce document s'associent à ce mouvement.

Parmi mes différentes contributions, une technique de routage proposée est caractérisée par le calcul de permutations des arcs utilisés par chaque route. Ainsi, chaque permutation correspond à une nouvelle solution pour relier deux points du circuit, équivalente en terme de délai, et possiblement non conflictuelle. Cette technique utilisée seule ne suffit pas, mais elle est compatible avec des approches séquentielles utilisées dans la littérature, comme l'algorithme A\*. Il est probable que la littérature soit passée à côté de ces techniques en raison de l'intérêt général pour des techniques de routage permettant de router avec succès des netlist toujours plus denses. Cependant des réductions de temps de calcul intéressantes peuvent être obtenues avec la technique proposée. Une autre contribution concerne un algorithme pour calculer le plus court chemin dans un graphe multi-dimensionnel, avec une complexité de calcul linéaire avec la distance à parcourir, indépendante de la taille du graphe. Cette complexité est donc très largement inférieure aux routeurs de type labyrinthe tel le A\*, qui ont globalement une complexité quadratique en fonction du nombre total de noeuds du graphe. La démonstration mathématique de cette approche est proposée au chapitre 2.2.6 avec les techniques

décrivées dans ce paragraphe.

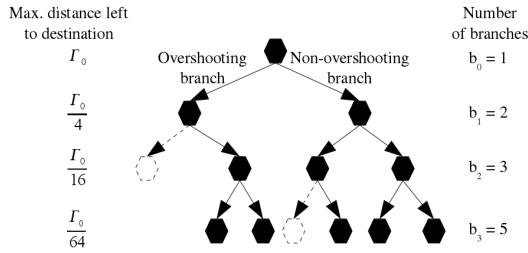

En plus de ces techniques de routage qui considèrent chaque *net* indépendant, une autre contribution ajoute un algorithme d'équilibrage des délais. Fonctionnalité majeure de l'algorithme de routage pour le WaferBoard, il vise à assurer que la différence de temps de propagation au sein d'un groupe de routes soit inférieur à une borne spécifiée par l'utilisateur. Bien sûr, il faut également s'assurer que les routes calculées ne soient pas en conflit avec d'autres. L'équilibrage des délais est donc une contrainte supplémentaire, et même prioritaire, au routage. De plus, l'équilibrage n'est pas forcément possible en une itération, il est nécessaire de construire un algorithme qui relaxe progressivement les délais maximums autorisés, pour assurer le fonctionnement du circuit. La latence augmente, mais l'équilibrage est respecté. L'algorithme proposé est construit selon deux axes : le premier est une extension d'un algorithme publié récemment dans le domaine des *FPGA* appelé *Routing Cost Valley (RCV)*. Celui-ci est robuste, non-aléatoire et fondé sur le A\*. *RCV* tient compte lors du routage de contraintes de délais minimum et maximum pour un *net* (borne), mais ne gère pas les contraintes associées à des groupes. L'extension proposée le permet par l'adjonction de deux routines de gestion des groupes de *net*. Les contraintes associées à l'équilibrage des délais augmentent fortement les temps de calcul, observation que l'on retrouve dans la littérature. Un algorithme d'accélération est ainsi proposé, algorithme qui fusionne avec celui basé sur *RCV*. Cette contribution utilise une propriété des réseaux d'interconnexion *CMOS*, qui sont l'allongement du délai d'une route par l'utilisation de plusieurs segments, au lieu d'un seul. Les propriétés de cette technique sont analysées au chapitre 4.

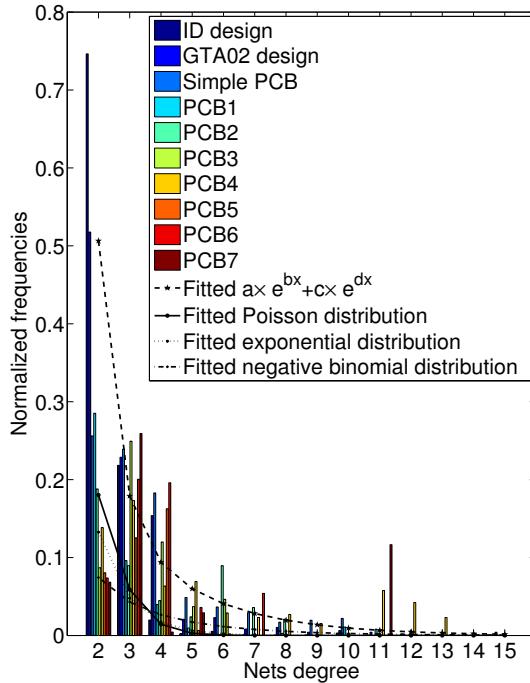

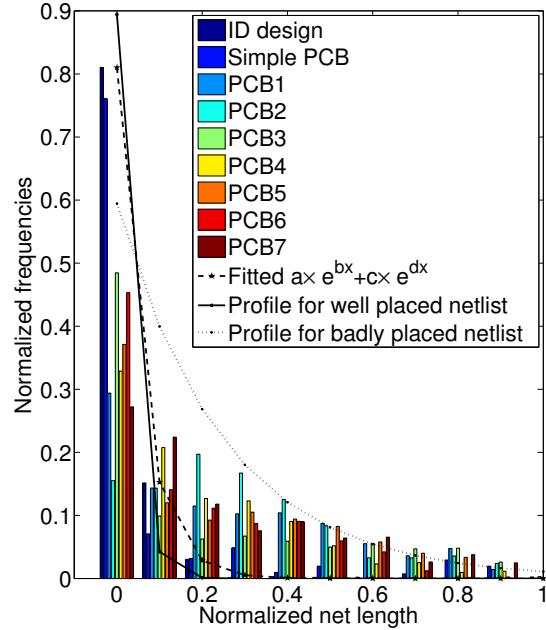

Le routeur pour ce projet traite des *netlist* similaires à celles pour *PCB*, et utilise un réseau d'interconnexions particulier. Or, bien qu'il existe plusieurs *netlist* admises comme bancs d'essais pour comparer les algorithmes sur *FPGA* et *VLSI*, il n'en existe pas pour les *PCB*. Des ensembles de données existent comme celui qui était à la base d'une compétition sur les outils de routage, mais malheureusement, ces données ne sont pas publiques ; la recherche académique sur les routeurs *PCB* n'est donc pratiquement plus active, et ce depuis plus de 10 ans. Les *netlist* placés sont des informations confidentielles pour l'industrie. Plusieurs publications existent sur les générateurs de *netlist* synthétiques au sein des communautés travaillant sur *FPGA* et circuits *VLSI* mais aucune pour les *netlist* de *PCB*. Les *netlist* synthétiques ont pour avantage d'être modulables à souhait selon différentes métriques (densité, complexité d'interconnexions, qualité du placement par exemple). Idéalement, il est possible de moduler ces métriques indépendamment les unes des autres, ce qui facilite la caractérisation des algorithmes, afin de mieux visualiser leurs forces et faiblesses. Comme contribution, j'ai réalisé le premier générateur de *netlist* synthétiques pour *PCB* publié. Dans le cadre de cette thèse, il est démontré qu'une métrique, la loi de Rent, couramment utilisée pour représenter les *netlist* sur *FPGA* et *VLSI*, est inapplicable aux *PCB* modernes. Ainsi, un modèle novateur fondé sur deux métriques importantes, la distribution du degré des *net* et celle de la longueur des *net*, a été développé pour les besoins du projet. Ce modèle a conduit à la construction d'un générateur qui permettra à des chercheurs d'obtenir facilement des *netlist* pour *PCB*, et ainsi établir les bases d'un ensemble de bancs d'essais réalistes pour *PCB*. Ces résultats sont présentés au chapitre 4.4.

Pour terminer, une contribution de mon travail est la réalisation d'un outil fonctionnel pour le WaferBoard : l'algorithme, les structures de données et même l'interface graphique sont intégrés au sein du logiciel. Bien que ne constituant pas une contribution scientifique du même ordre, il s'agit d'une réalisation majeure en terme pratique qui a contribué à l'avancement du projet dans sa globalité.

# Abstract

The routing problem is very actual. Applications are found in *GPS*, road traffic forecast, but also for prototyping on *FPGA*, or *TCP/IP* traffic on the Internet. Publications on the subject have existed for several decades, but new publications keep appearing, confirming the importance and complexity of the problem.

This thesis deals with routing and the resources it requires for a new category of micro-electronic applications, called the *WaferBoard*. It is an electronic circuit integrated at the wafer scale. Few commercial applications of micro-electronics have exploited this level of integration. This rapid prototyping system aims at reducing by one or two orders of magnitude the development time of digital circuits. It requires a very fast routing tool, capable of producing viable solutions in a few minutes, with dedicated functionality such as balancing delays and rerouting on the fly parts of a netlist.

The routing problem for this application can be pictured as follows. Given a regular road network of the size of north america, if 100.000 cars were to start Monday 8 a.m. across the continent with a wide variety of sources and destinations ; the challenge is to compute paths for all cars so none of them take the same route that day. It is 7 :59 am, you have 1 minute, and some bridges are under road work : here is the list.

This simplistic example gives an idea of the orders of magnitude of the problem that need to be solved for this application. A routing algorithm takes as input : a graph (or interconnection network) made of nodes and edges, and a netlist, a list of electrical nodes with starting and ending points physically placed. Therefore, instead of cars, the problem consists of routing electrical signals with points of departure and arrival dictated by the pin position of components placed on the prototyping system. A regular, multi-dimensional mesh (also called "interconnection network") serves as a road network, which contains defective roads and inaccessible bridges. Indeed, the interconnection network is an electronic circuit integrated across a full wafer, implying the presence of defects within each manufactured circuit. Unlike conventional electronic circuits, where each is tested and defective ones are set apart, wafer scale integrated applications require lots of redundancy in the circuit to minimize the rejection rate. In the *WaferBoard*, a number of elements of the interconnection network will be defective in each circuit ; the routing algorithm must take into account these very specific elements. This constraint is not found in the classic applications of routers found in *PCB*, *FPGA* or *VLSI* circuits. Other restrictions apply to this particular project : the latency induced by the technology is about one order of magnitude greater than that in the circuits of *PCBs*, which requires a routing oriented towards computation time

reduction. This constraint partly explains the network architecture used. Within the *WaferIC*, the shortest distance is not necessarily the one that offers the smallest latency. This property of the network complexifies the routing problem. Balancing delays within a group of arbitrary size nets is a necessary feature of the routing algorithm, and the difficulty is amplified by the computation time limit. Indeed, the interest of the application is to reduce the time for a user to test a circuit : the time of setup is extremely short, and estimated at a few minutes only. The computation time for the routing should ideally stay under 10 minutes, which is acceptable to the user.

A complete literature review of routers for the electronic technologies is performed in this thesis. It allows us to classify the different families of known routing algorithms. It appears that the conventional approaches now used for *VLSI* circuits and *FPGA*, which include the vast majority of publications today, focuses on the quality of the final routing at the expense of computation time that are generally very long. A recent trend appears in the literature, which involves algorithms trying to route faster without losing quality. Researches presented in this document are associated with this movement.

Among various contributions, a proposed routing technique is characterized by calculating permutations of edges used by each route. Thus, each permutation correspond to a new solution to connect two points of the circuit, equivalent in terms of delay, and possibly non-conflicting. Alone, this technique is not sufficient for routing, but it is compatible with sequential approaches used in the literature, such as the A \* algorithm. It is likely that these techniques were not developed in the literature, because of general interest for pushing the limits of maximum density. However, interesting reductions of computation time can be obtained with the proposed techniques. Another contribution concerns an algorithm to compute the shortest path in a multi-dimensional graph that has a linear complexity with the distance to travel, independent of the size of the graph. This complexity is far less than that of labyrinth algorithms, such as the A \*, which have an overall complexity that depends on a quadratic function of the total number of nodes in the graph. A mathematical demonstration of this approach is proposed in Chapter 2.2.6, along with the other techniques briefly described in this paragraph.

In addition to simple routing techniques that consider each net independently from others, a delay balancing algorithm is proposed. As a major feature of the routing algorithm for the WaferBoard, it seeks to ensure that the difference in propagation delays in a group of nets is less than some user-specified constraint. Of course, it must also ensure that routed nets are not in conflict with others. Delay-balancing is an additional constraint for routing. Moreover, the balance is not necessarily possible in one iteration, it is required to build an algorithm that gradually relaxes the maximum latency allowed, to ensure the correct operation of the circuit. While latency increases, the balance is respected. The proposed algorithm is built on two foundations : the first one is an extension of an algorithm published recently in the field of *FPGA*, called the *Routing Cost Valley (RCV)*. It is robust and based on the A \*. *RCV* takes into account minimum and maximum delay constraints for a net, but does not handle constraints associated to groups of nets. The proposed extension allows it by the addition of two functions dedicated to group constraints. Constraints associated

with delay balancing greatly increases computation times, an observation found in the literature. An acceleration algorithm is proposed, which merges with *RCV*. It uses a feature of *CMOS* interconnection networks, which is a longer delay with the use of multiple edges, instead of one. The properties of this technique are analyzed in chapter V.

The router for this project deals with netlist similar to those for *PCBs*, and uses a specific interconnection network. However, although there are several netlists generally admitted as benchmarks for comparing algorithms on *FPGAs* and *VLSI*, none exist for *PCBs*. In absence of generally accepted benchmarks, the academic research on *PCB* routers is therefore almost inactive, and this has been so for over 10 years. Placed netlist are confidential information for the industry. However, literature on synthetic netlist generators exists in communities working on *FPGAs* and *VLSI ASICs*, but none are available for *PCBs*. Synthetic netlist have the advantage of being adjustable at will according to different metrics (density, complexity of interconnections, placement quality for example). Ideally, it is possible to modulate these metrics independently of each other, which facilitates the characterization of routing algorithms, in order to better visualize their strengths and weaknesses. This thesis reports the first published synthetic netlist generator for *PCBs*. As part of this thesis, we demonstrate that a well-known metric, the Rent's rule, commonly used to represent *FPGA* and *VLSI* netlists, is inapplicable to modern *PCBs*. Thus, an original model based on two important metrics, the distribution of the net degree and the net length distribution, has been developed for the needs of the project. This model has led to the construction of a generator that will allow researchers to easily obtain netlists for *PCBs*, and establish the basis of a set of realistic benchmarks for *PCBs*. These results are presented in chapter 4.4.

Finally, a practical contribution of this work is the implementation of a functional tool to support that WaferBoard : algorithms, data structures and even a GUI were integrated within a complete software. While this is not a pure scientific contribution, it is a major practical contribution to engineering that supported the demonstration that tools for supporting the WaferBoard technology are feasible.

# Table des matières

|                                                                |      |

|----------------------------------------------------------------|------|

| <b>Remerciements</b>                                           | iii  |

| <b>Résumé</b>                                                  | iv   |

| <b>Abstract</b>                                                | viii |

| <b>Table des matières</b>                                      | xi   |

| <b>Liste des tableaux</b>                                      | xiv  |

| <b>Table des figures</b>                                       | xvi  |

| <b>Liste des symboles</b>                                      | xx   |

| <b>Introduction</b>                                            | 1    |

| <b>Chapitre 1 Problématique et Contributions</b>               | 11   |

| 1.1 Problématique                                              | 11   |

| 1.2 Description des contributions                              | 16   |

| 1.2.1 Modèle et générateur de <i>netlist</i>                   | 16   |

| 1.2.2 Techniques de routage point à point                      | 17   |

| 1.2.3 Équilibrage des délais d'un groupe de <i>net</i>         | 19   |

| 1.3 Discussion                                                 | 20   |

| <b>Chapitre 2 Revue de littérature</b>                         | 23   |

| 2.1 Publications                                               | 23   |

| 2.1.1 Routage : les différentes approches explorées            | 23   |

| 2.1.1.1 Les principaux domaines de recherche                   | 23   |

| 2.1.1.2 Classification des algorithmes de routage              | 24   |

| 2.1.1.3 Approches dites globales                               | 26   |

| 2.1.1.4 Approches dites séquentielles                          | 29   |

| 2.1.2 PathFinder pour FPGA : une formulation identique au DCLC | 31   |

| 2.1.3 Équilibrage des délais                                   | 32   |

| 2.1.4 Modèle de <i>netlist</i>                                 | 35   |

| 2.2 Algorithmes clé de la littérature                          | 37   |

| 2.2.1 Dijkstra                                                 | 37   |

| 2.2.2 A*                                                       | 41   |

| 2.2.3 Rip-up and Reroute : retire et recommence                | 45   |

|                                                                                                                                    |                                                                                  |            |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------|

| 2.2.4                                                                                                                              | PathFinder et VPR . . . . .                                                      | 46         |

| 2.2.5                                                                                                                              | RCV : Routing Cost Valley . . . . .                                              | 48         |

| 2.2.6                                                                                                                              | Graphe de Rent . . . . .                                                         | 49         |

| <b>Chapitre 3 - Article 1 - A Permutation-Based Routing Algorithm for a Novel Electronic System Prototyping Platform . . . . .</b> |                                                                                  | <b>51</b>  |

| 3.1                                                                                                                                | Abstract . . . . .                                                               | 51         |

| 3.2                                                                                                                                | Introduction . . . . .                                                           | 51         |

| 3.3                                                                                                                                | The Wafer-Scale Interconnection Network . . . . .                                | 53         |

| 3.4                                                                                                                                | Proposed PermFinder Routing Algorithm . . . . .                                  | 55         |

| 3.4.1                                                                                                                              | Finding the shortest path in an ideal mesh . . . . .                             | 58         |

| 3.4.2                                                                                                                              | Solving Conflicts With Permutations . . . . .                                    | 65         |

| 3.4.3                                                                                                                              | Solving Remaining Conflicts . . . . .                                            | 66         |

| 3.5                                                                                                                                | Results . . . . .                                                                | 67         |

| 3.5.1                                                                                                                              | Permutations Effort Trade-off . . . . .                                          | 68         |

| 3.5.2                                                                                                                              | Parallelized permutations . . . . .                                              | 71         |

| 3.5.3                                                                                                                              | Edge based versus route based routing . . . . .                                  | 72         |

| 3.5.4                                                                                                                              | Comparisons with PathFinder . . . . .                                            | 74         |

| 3.6                                                                                                                                | Conclusion . . . . .                                                             | 76         |

| <b>Chapitre 4 Équilibrage des délais appliqué au routage de bus . . . . .</b>                                                      |                                                                                  | <b>77</b>  |

| 4.1                                                                                                                                | Introduction . . . . .                                                           | 77         |

| 4.2                                                                                                                                | Description générale de l'algorithme utilisé . . . . .                           | 79         |

| 4.2.1                                                                                                                              | Algorithme d'allocation dynamique des délais . . . . .                           | 80         |

| 4.2.2                                                                                                                              | Algorithme d'équilibrage des délais par table d'équivalences . . . . .           | 85         |

| 4.2.3                                                                                                                              | Version tronquée de la fonction coût de RCV . . . . .                            | 88         |

| 4.3                                                                                                                                | Résultats des approches proposées . . . . .                                      | 89         |

| 4.4                                                                                                                                | Conclusion . . . . .                                                             | 93         |

| <b>Chapitre 5 - Article 2 - A PCB Netlist Model and Generator for a Routing Algorithm . . . . .</b>                                |                                                                                  | <b>94</b>  |

| 5.1                                                                                                                                | Abstract . . . . .                                                               | 94         |

| 5.2                                                                                                                                | Introduction . . . . .                                                           | 95         |

| 5.3                                                                                                                                | PCB Netlist Model . . . . .                                                      | 98         |

| 5.3.1                                                                                                                              | Model Parameters . . . . .                                                       | 99         |

| 5.3.2                                                                                                                              | Rent's Rule Analysis for PCB Netlist Generator . . . . .                         | 100        |

| 5.3.3                                                                                                                              | Analysis and Generation of Netlist Degree and Net Length Distributions . . . . . | 102        |

| 5.4                                                                                                                                | Netlist Generation . . . . .                                                     | 105        |

| 5.4.1                                                                                                                              | Interconnection network description . . . . .                                    | 106        |

| 5.4.2                                                                                                                              | Netlist generation algorithm . . . . .                                           | 106        |

| 5.5                                                                                                                                | Results . . . . .                                                                | 108        |

| 5.6                                                                                                                                | Discussion . . . . .                                                             | 110        |

| 5.7                                                                                                                                | Conclusion . . . . .                                                             | 113        |

| <b>Chapitre 6 Discussion générale . . . . .</b>                                                                                    |                                                                                  | <b>115</b> |

| <b>Conclusion . . . . .</b>                                                                                                        |                                                                                  | <b>118</b> |

|                         |     |

|-------------------------|-----|

| Bibliographie . . . . . | 123 |

|-------------------------|-----|

# Liste des tableaux

|                                                                                                                                                                                                                                                                                                                        |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 0.1: Comparaison des réseaux d’interconnexions de type Routier, <i>PCB</i> , <i>ASIC</i> , <i>FPGA</i> et multi-dimensionnel ( <i>WaferIC</i> ), selon différentes métriques. Les dimensions sont rapportées en prenant la technologie la plus avancée actuellement publiée. . . . .                           | 7   |

| Tableau 2.1: Les principales familles de routeur les plus couramment utilisés par les outils CAD en microélectronique. . . . .                                                                                                                                                                                         | 26  |

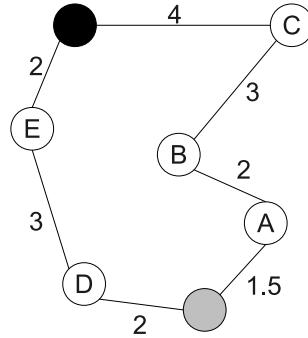

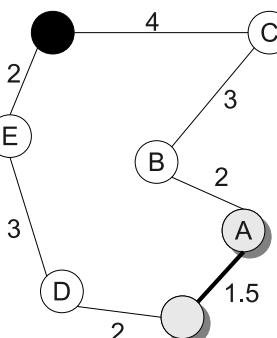

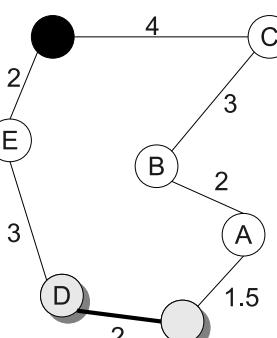

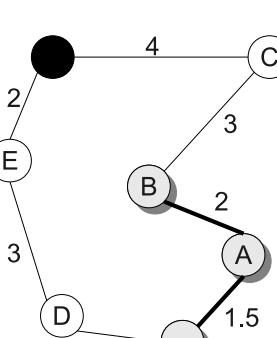

| Tableau 2.3: Étapes de résolution du chemin le plus court sur un graphe simple, du nœud gris (en bas sans identifiant) au nœud noir (haut) par l’algorithme Dijkstra. . . . .                                                                                                                                          | 38  |

| Tableau 2.5: Étapes de résolution du chemin le plus court sur un graphe simple, du nœud gris (bas sans identifiant) au nœud noir (haut) par l’algorithme A*. . . . .                                                                                                                                                   | 42  |

| Tableau 3.7: Examples of paths belonging to $P_{\text{me}}$ and $P_{\text{md}}$ with vertices pair $(v_s, v_d)$ distant of seven vertices. The interconnection network assumes links of length $\lambda = 1, 2, 4, 8$ . . . . .                                                                                        | 61  |

| Tableau 3.8: Maximum number of paths computed for a 1-D interconnection network with edges of power-of-two length, for various maximum edge lengths. . . . .                                                                                                                                                           | 65  |

| Tableau 3.9: Routing time (in seconds) for various netlist densities and permutation efforts. Results are averaged over 5 runs. . . . .                                                                                                                                                                                | 69  |

| Tableau 3.10: Percentage of routed nets after $N$ computed permutations for various netlists (graph size of 82,944 vertices, effort of $10^6$ ). . . . .                                                                                                                                                               | 70  |

| Tableau 3.11: Acceleration factor of the parallel permutations approach (routing time) for several netlist densities and permutation efforts (graph size of 82,944 vertices). The best routing times for each netlist density are shown in italic. . . . .                                                             | 72  |

| Tableau 3.12: Impact on route delays for Route based vs. Edge based routing for a graph size of 82944 vertices (effort $e = 10^6$ ). . . . .                                                                                                                                                                           | 73  |

| Tableau 3.13: Routing results for PathFinder (R) and the proposed approach (P) using an effort of 1,000 (parallel permutations) and the edge-based routing approach, for a graph of 82,944 vertices. . . . .                                                                                                           | 75  |

| Tableau 3.14: Routing results for PathFinder (R) and the proposed approach (P) using an effort of 1,000 and the edge-based routing approach. . . . .                                                                                                                                                                   | 75  |

| Tableau 4.1: Tableau partiel de l’augmentation du délai (normalisé), via le «découpage» d’un segment de longueur $\lambda$ (première colonne) en plusieurs autres (colonnes 2-7). Les valeurs sont normalisées par rapport à l’augmentation minimale du délai $d_c$ accessible à la technologie du WaferBoard. . . . . | 87  |

| Tableau 4.2: Résultats de routage avec équilibrage pour les approches basées sur la table d’équivalences. . . . .                                                                                                                                                                                                      | 92  |

| Tableau 4.3: Influence des différentes approches basées sur la table d’équivalences sur le délai total des routages générés. . . . .                                                                                                                                                                                   | 92  |

| Tableau 5.4: An example of net degree distribution profile that could match the ID design. Similar distributions can match any profile. . . . .                                                                                                                                                                        | 103 |

|                                                                                                                                                                                                                                                                      |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 5.5: Parameters used for netlist generation in this paper. . . . .                                                                                                                                                                                           | 104 |

| Tableau 5.6: An example of a generated net-degree distribution, that complies with profile of table 5.4. . . . .                                                                                                                                                     | 107 |

| Tableau 5.7: Net-degree distribution profile used for generating netlists. This profile can match the various profiles that have been observed on real-world netlists. . . . .                                                                                       | 110 |

| Tableau 5.8: Percentage of routing resources used for real netlist versus generated one (for several wire lengths of the interconnection network). Occupancy percentage are very similar for real and synthetic generated netlists. . . . .                          | 111 |

| Tableau 5.9: Average computation times to route real and synthetic generated netlists for three routing passes. Most synthetic netlists generated with our tool are slightly harder to route than real ones, but the differences are in general within 10 %. . . . . | 112 |

# Table des figures

|                                                                                                                                |    |

|--------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 0.0.1: Modèle tridimensionnel du système physique dans son ensemble : le <i>WaferBoard</i> <sup>TM</sup> . Crédit Tech- |    |

| noCap Inc. <i>DreamWafer</i> Division. Reproduit avec permission. . . . .                                                      | 3  |

| Figure 0.0.2: Architecture du <i>WaferIC</i> , vue schématique peu détaillée. La mer de cellules permet au circuit             |    |

| d'être répété à l'infini. . . . .                                                                                              | 4  |

| Figure 0.0.3: Architecture du réseau d'interconnexions intégré au <i>WaferIC</i> . Chaque cellule (représentée par un          |    |

| carré avec une coordonnée) possède des liens (arcs) vers ses 4 plus proches voisines, 4 voisines à                             |    |

| distance 2, distance 4, ... jusqu'à 32 dans l'implémentation actuelle. Ainsi, ils forment un réseau                            |    |

| multi-dimensionnel. Seuls sont représentés les liens de la cellule 0;0 sur quelques distances, mais                            |    |

| le patron est répété pour chaque cellule. . . . .                                                                              | 5  |

| Figure 0.0.4: Schéma de l'architecture interne du <i>crossbar</i> , implémentation actuelle. Seul un groupe d'entrées          |    |

| vers une sortie sont représentés, les autres sont identiques. Chaque entrée traverse 2 multiplexeurs                           |    |

| 4 vers 1 et 1 multiplexeur 2 vers 1. . . . .                                                                                   | 6  |

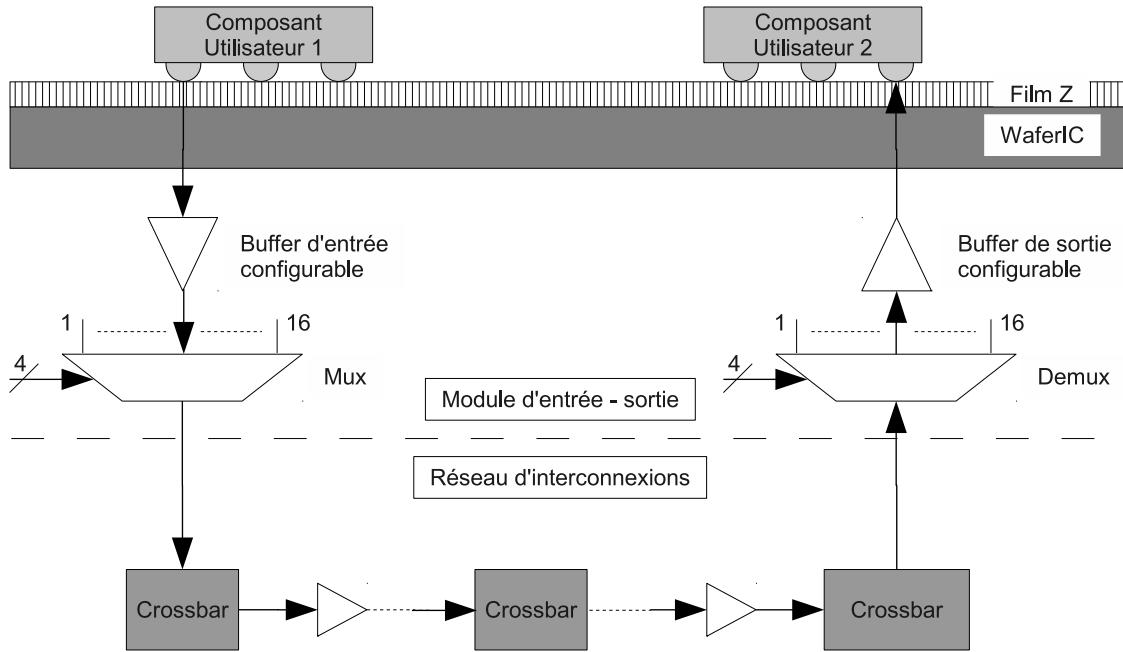

| Figure 0.0.5: Schéma de principe de configuration et de parcourt d'un signal électrique entre deux broches                     |    |

| en contact avec le <i>WaferIC</i> . Le signal électrique d'une bille du composant 1 de l'utilisateur se                        |    |

| propage dans le réseau d'interconnexions, en passant par les étages d'entrées et de sorties jusqu'à                            |    |

| la bille désirée du composant 2. . . . .                                                                                       | 7  |

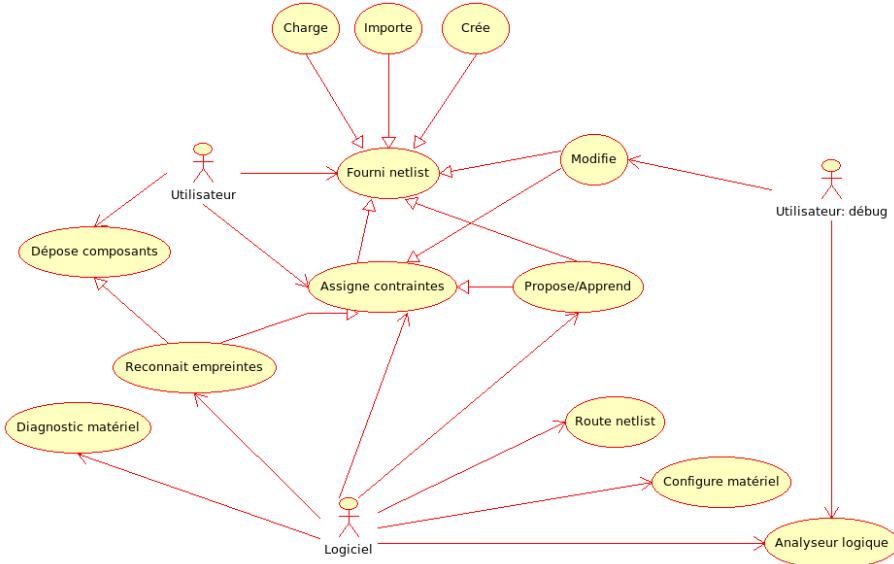

| Figure 1.1.1: Cas d'utilisation à haut niveau du système de prototypage. . . . .                                               | 12 |

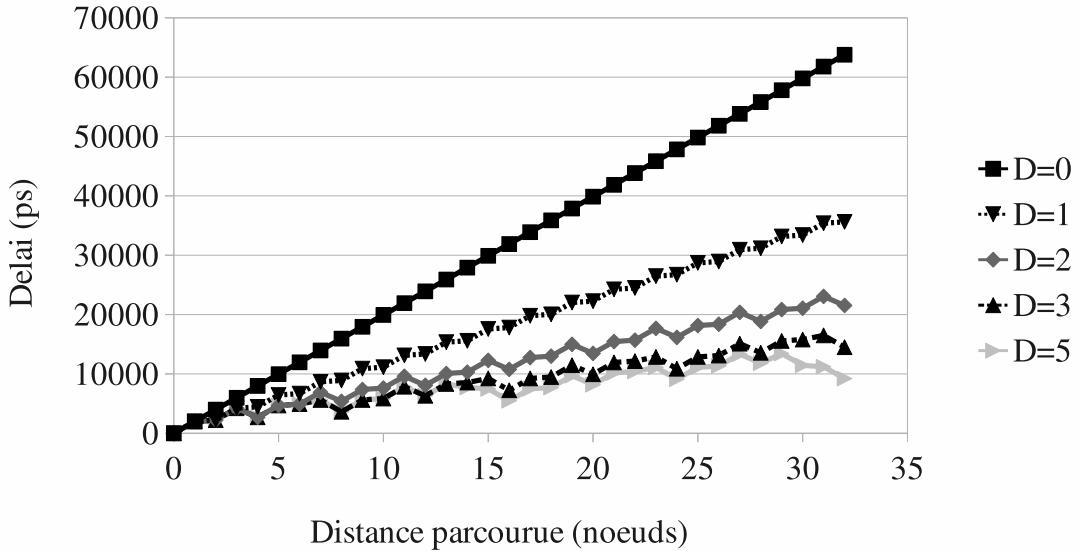

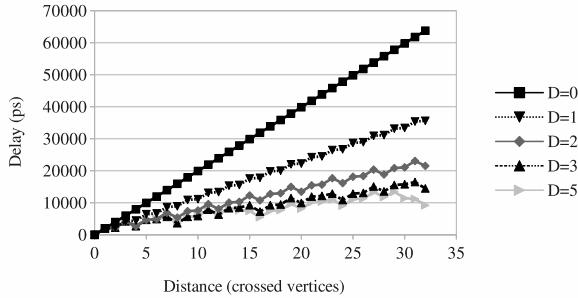

| Figure 1.1.2: Délai en fonction de la distance parcourue, pour différents arcs choisi dans un réseau multi-                    |    |

| dimensionnel régulier. D réfère à la dimension de l'arc. Par exemple $D = 0$ correspond à un                                   |    |

| arc de longueur $2^D = 2^0 = 1$ cellule (plus proche voisin). Dès que des arcs de longueur supérieure                          |    |

| à 2 sont utilisés, la fonction du délai n'est plus monotone avec la distance parcourue. . . . .                                | 15 |

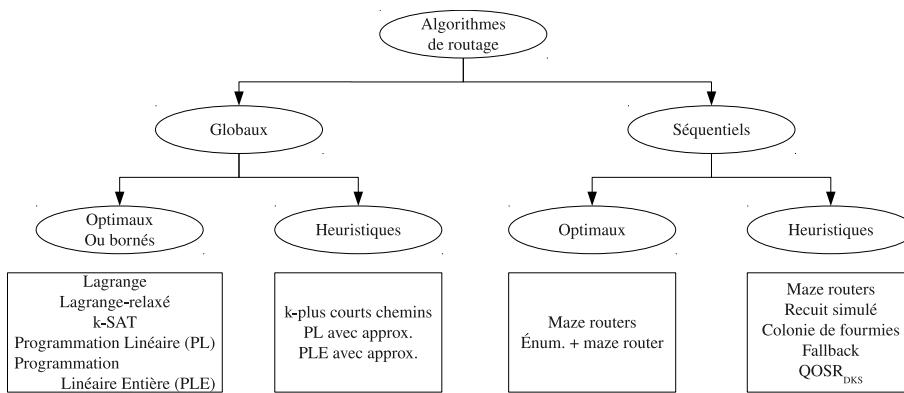

| Figure 2.1.1: Essai de classification des différentes techniques de routage existantes. Quelques exemples d'al-                |    |

| gorithmes pour chaque catégorie sont donnés. Quelques références, qui seront détaillées plus loin :                            |    |

| Lagrange [1], Lagrange relaxé [2, 3], Programmation Linéaire [4] (avec approximations [5]), Pro-                               |    |

| grammation Linéaire Entière [6] (avec approximations [7]), <i>QOSRDKS</i> [8]. . . . .                                         | 26 |

| Figure 2.2.1: Graphe utilisé comme exemple de résolution du chemin le plus court par l'algorithme Dijkstra                     |    |

| et $A^*$ . Le noeud de départ est en gris (bas) et le noeud d'arrivée en noir (haut). . . . .                                  | 38 |

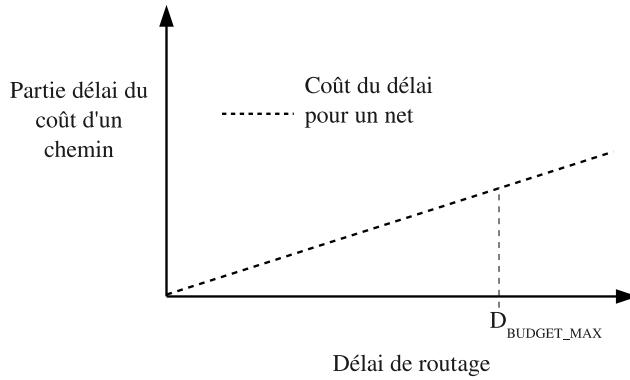

| Figure 2.2.2: Fonction de coût en rapport avec le délai d'un noeud pour l'algorithme <i>PathFinder</i> . La fonction $C_n$     |    |

| tient compte de cette fonction, qui évolue linéairement. . . . .                                                               | 47 |

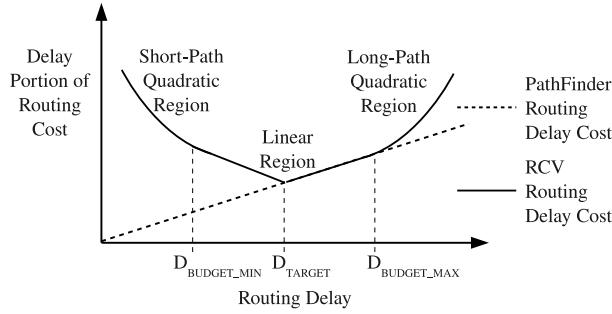

| Figure 2.2.3: Portion du délai dans la fonction coût lors de l'évaluation d'un chemin pour l'algorithme <i>RCV</i> .           |    |

| L'ajout par rapport à la fonction utilisée par <i>PathFinder</i> est mise en évidence : une progression                        |    |

| exponentielle en dehors de la zone d'intérêt, et un miroir côté chemin court centré sur le délai                               |    |

| objectif. . . . .                                                                                                              | 49 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

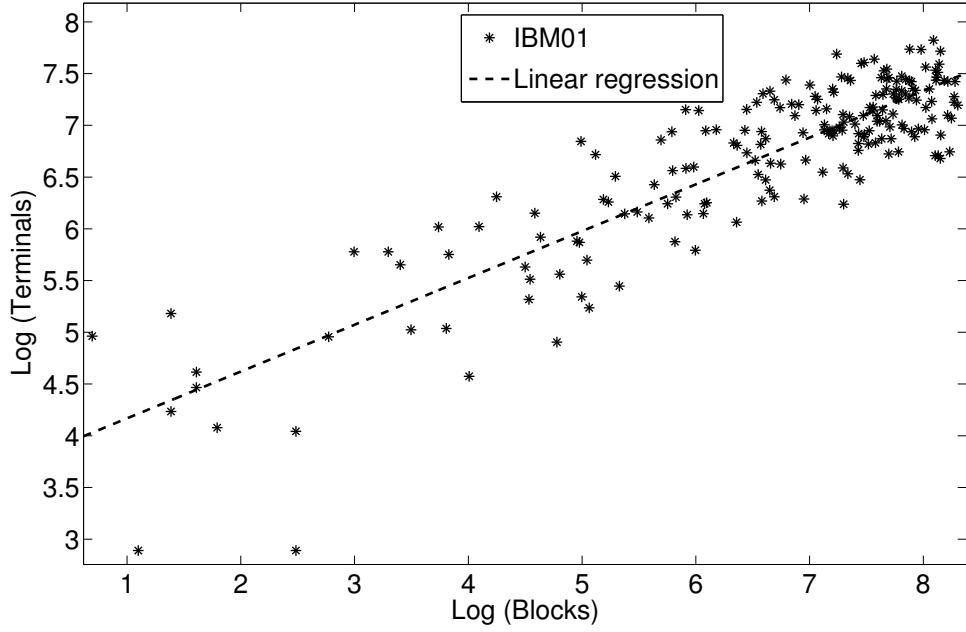

| Figure 2.2.4: Exemple de graphe de Rent pour le banc d'essai IBM Place 01, calculé en utilisant la technique décrite dans [9]. L'exposant de Rent calculé est 0.45 avec un $R^2 = 0.76$ . . . . .                                                                                                                                                                                                                                         | 50 |

| Figure 3.2.1: The DreamWafer board: user's IC are manually deposited on the wafer's surface, external connections are possible as well as probing digital on-wafer interconnection signals – in real time. . . . .                                                                                                                                                                                                                        | 52 |

| Figure 3.3.1: Multi-dimensional mesh network: vertices are represented by squares (physically, crossbars) with their relative coordinates, and edges (wires). Edges for the vertex at coordinates (0;0) are shown for a mesh of dimension 2 ( $2^2 = 4$ ). . . . .                                                                                                                                                                        | 56 |

| Figure 3.3.2: Delay of the shortest path, function of distance in terms of crossed vertices, for several interconnection network dimension. $D=5$ is the network dimension in the WaferIC, with $d_c = 10d_w = 2300$ ps. One important property of the interconnection network is that the delay versus distance is not a monotonic function when $D > 0$ . . . . .                                                                       | 56 |

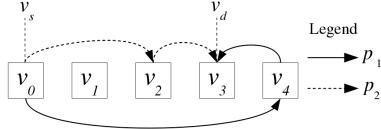

| Figure 3.4.1: Two different solutions (with and without overshoot) of a uni-dimensional path between vertices $(v_s, v_d)$ distant of 4 crossbars (vertices). In these examples, path $p_2$ has the smallest propagation delay (same number of vertices with smaller total distance). . . . .                                                                                                                                             | 61 |

| Figure 3.4.2: An example of the decision tree for a route. Each octagon represents a decision point at vertex $v$ , a left-pointing arrow corresponds to a path overshooting at $v$ and a right-pointing arrow corresponds to a path not overshooting at $v$ . Dotted arrows and octagons represent branches that are not explored, in relation to corollary 3.4.1. The number of branches explored at step $j$ are noted $b_i$ . . . . . | 61 |

| Figure 3.4.3: When destination vertex is in the last quarter of $\lambda$ (between $\frac{3}{4}\lambda$ and $\lambda$ ), the choice for overshooting may build a path with a smaller delay (theorem 3.4.1). . . . .                                                                                                                                                                                                                       | 62 |

| Figure 3.4.4: A path that overshoots its destination twice in a row reaches the edge at $\frac{3}{4}\lambda$ . Therefore, it always builds a path with a delay longer than a path passing through $\frac{1}{2}\lambda$ that does not overshoot (theorem 3.4.1). . . . .                                                                                                                                                                   | 63 |

| Figure 3.4.5: An example of two equivalent paths with minimum number of edges. . . . .                                                                                                                                                                                                                                                                                                                                                    | 66 |

| Figure 3.4.6: A conflicting situation example where the dotted edge is used by another route, for a 1-D mesh with links of length 1 and 2 (a). Conflict is solved by routing only conflicting edges (b) or solved by rerouting from start to end (c). The latter ensures the optimality of the solution in terms of propagation delays but takes more time to compute. . . . .                                                            | 67 |

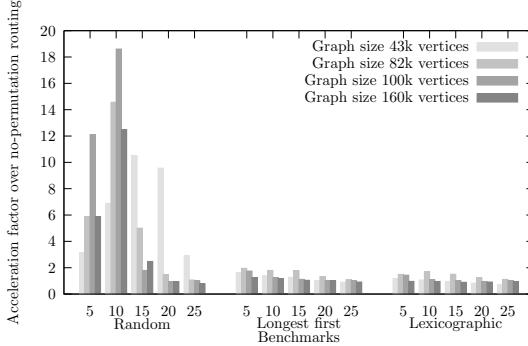

| Figure 3.5.1: Acceleration provided by 3 different strategies for permutations, namely random shuffle, longest edge first and lexicographic order (effort of 10,000). The acceleration is computed against routing without permutations. The fastest technique is the random approach on densities of 5-15 %. . . . .                                                                                                                     | 69 |

| Figure 3.5.2: Acceleration provided by the route based approach versus the edge based approach, for several netlists and graph size and an effort of 10,000. A very important acceleration is seen, especially on large networks with low to medium density netlists. Note that the acceleration factor for graph of 43k vertices on 10 % density netlist is of 1, making it non-visible on the graph. . . . .                            | 74 |

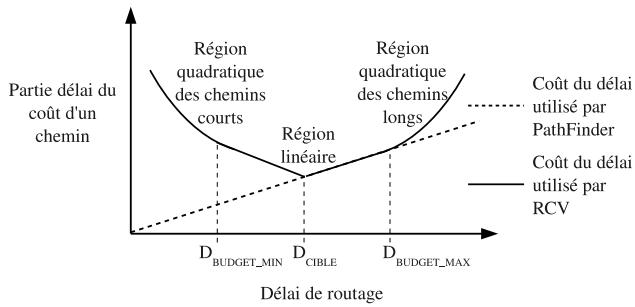

| Figure 4.2.1: La fonction coût lors de l'évaluation d'un chemin pour l'algorithme RCV. L'ajout par rapport à la fonction utilisée par PathFinder est mise en évidence : une progression exponentielle en dehors de la zone d'intérêt, et un miroir côté chemin court centré sur le délai objectif. . . . .                                                                                                                                | 80 |

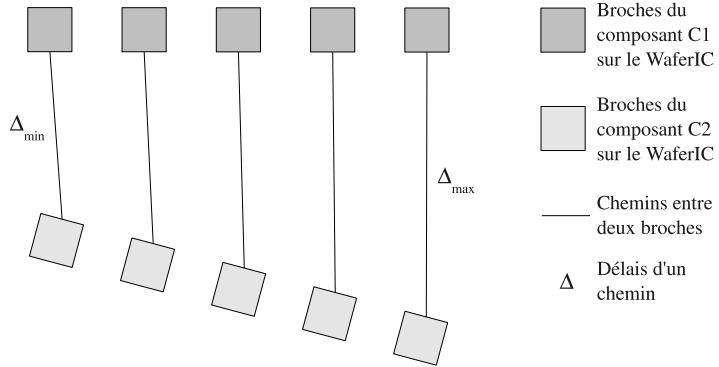

| Figure 4.2.2: Situation générale de l'équilibrage d'un bus : deux composants (C1 et C2) se font face, mais les délais optimaux de chaque net ne sont pas égaux. . . . .                                                                                                                                                                                                                                                                   | 82 |

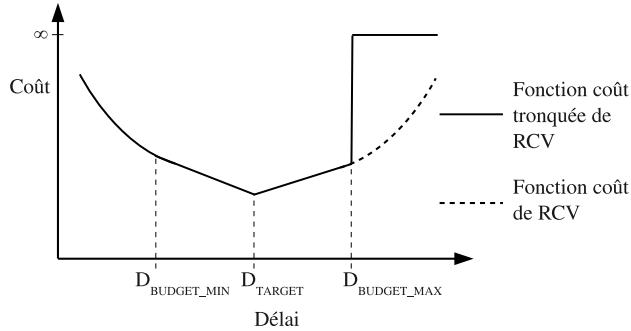

| Figure 4.2.3: La fonction de coût proposée : une troncature de la fonction utilisée par RCV. Ainsi, l'espace de recherche est réduit. La fonction utilisée par RCV est en pointillés, pour faciliter la comparaison.                                                                                                                                                                                                                      | 89 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

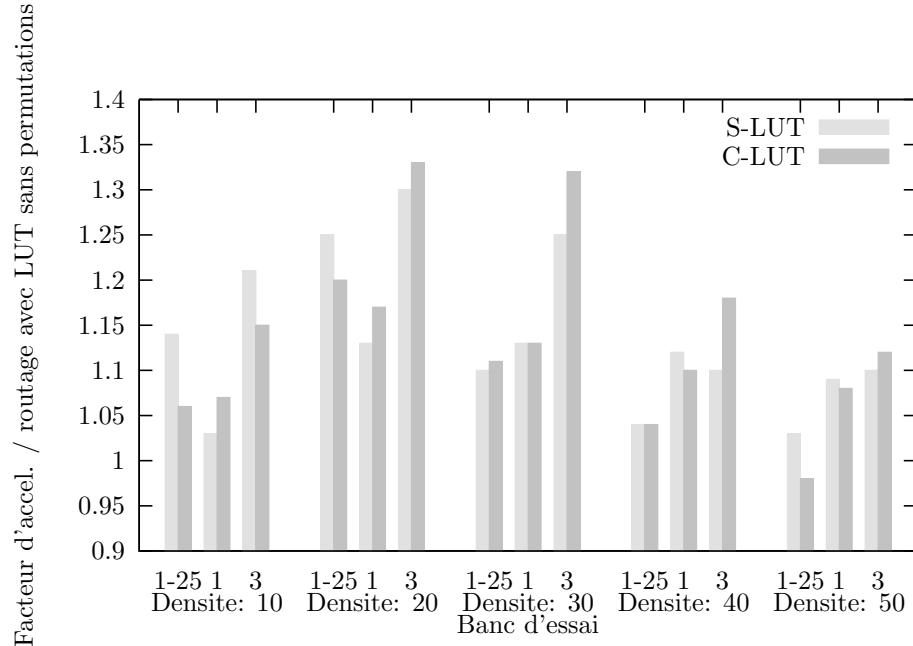

| Figure 4.3.1: Facteur d'accélération sur le temps de calcul apporté par le calcul des permutations, appliqué avec les deux approches de routage par table d'équivalences. Les permutations apportent pratiquement toujours une accélération, parfois jusqu'à un facteur 1.33. . . . .                                                                                                                                                       | 92  |

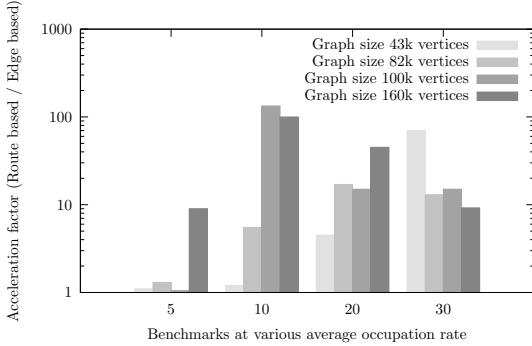

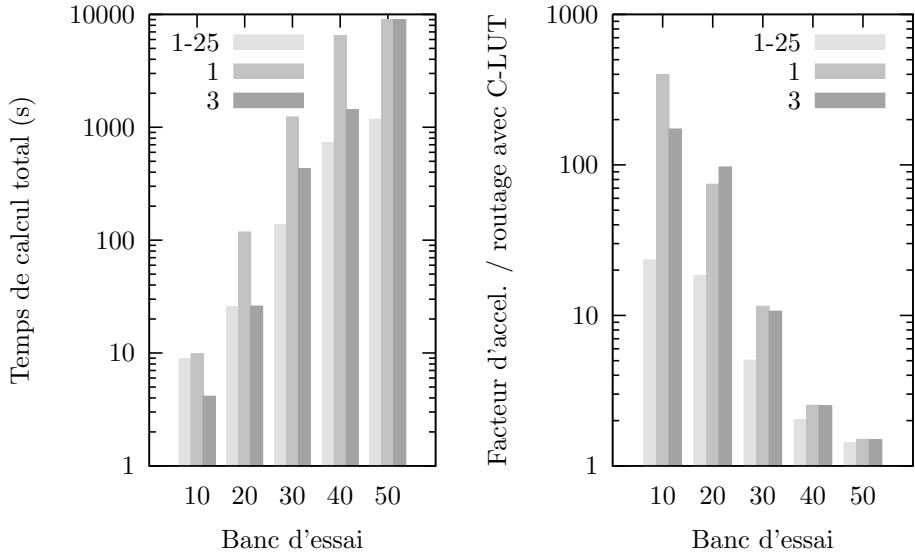

| Figure 4.3.2: Temps de calcul et facteur d'accélération apporté par la nouvelle fonction de coût. L'accélération est normalisée par rapport à la meilleure solution, soit l'utilisation la table complète d'équivalences. Les temps de calcul pour les bancs d'essais attendus (entre 10 et 30 % de densité moyenne avec un équilibrage « normal ») sont routés en moins de 10 minutes, soit l'objectif pour le système WaferBoard. . . . . | 93  |

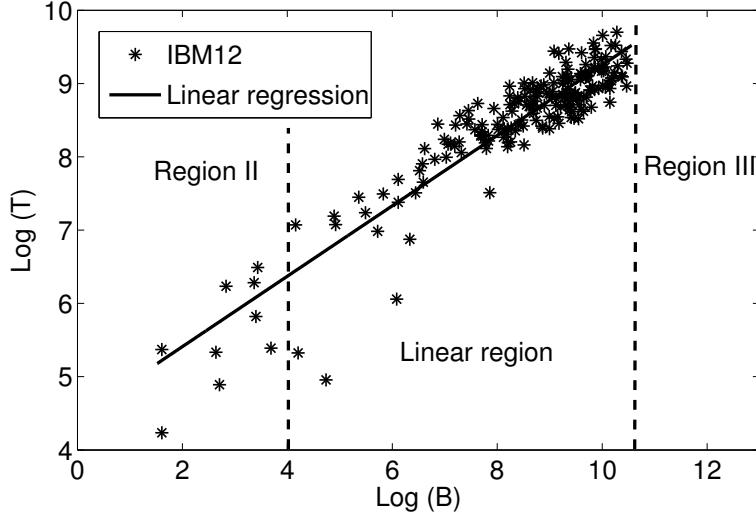

| Figure 5.2.1: Rent characteristic of IBM12 benchmark (IBM-Place V2), a VLSI benchmark used for VLSI placer and global routers, created using the technique described in [9]. This netlist does not have data in Rent region III. The Rent exponent is evaluated to be 0.48 with $R^2 = 0.85$ . . . . .                                                                                                                                      | 96  |

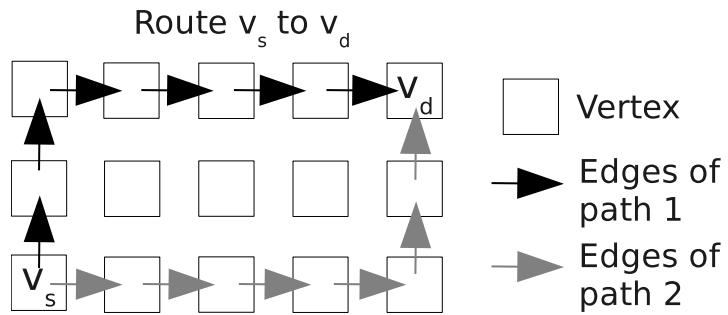

| Figure 5.3.1: Two different paths (black and gray arrows) for one route, from vertices $v_s$ to $v_d$ . This example assumes that edges connect each vertex to its 4 nearest neighbours. Other graph topologies are possible, for example with non-Manhattan edges. . . . .                                                                                                                                                                 | 98  |

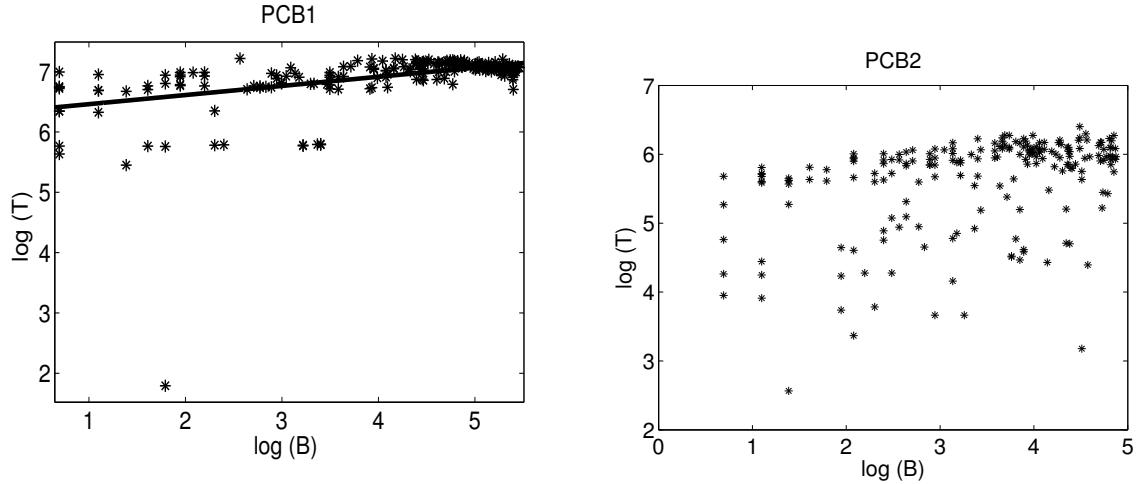

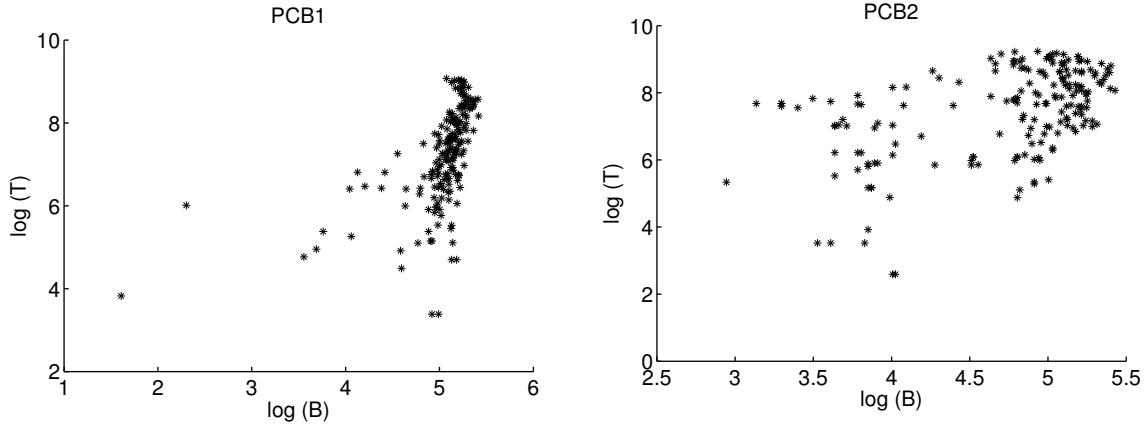

| Figure 5.3.2: Rent's plot for two representative PCB netlists, PCB1 and PCB2. PCB1 above presents a better fit (still not good) when compared to others, while PCB2 below is one that seems incompatible with Rent's power-law (as is 30 % of our data set). . . . .                                                                                                                                                                        | 101 |

| Figure 5.3.3: Rent's plot of PCB1 and PCB2 using random square as partitions, and plotting the total area of chips inside the partitions. These plots are representative of the available netlist set, and they cannot be modeled using the Rent's power-law. . . . .                                                                                                                                                                       | 101 |

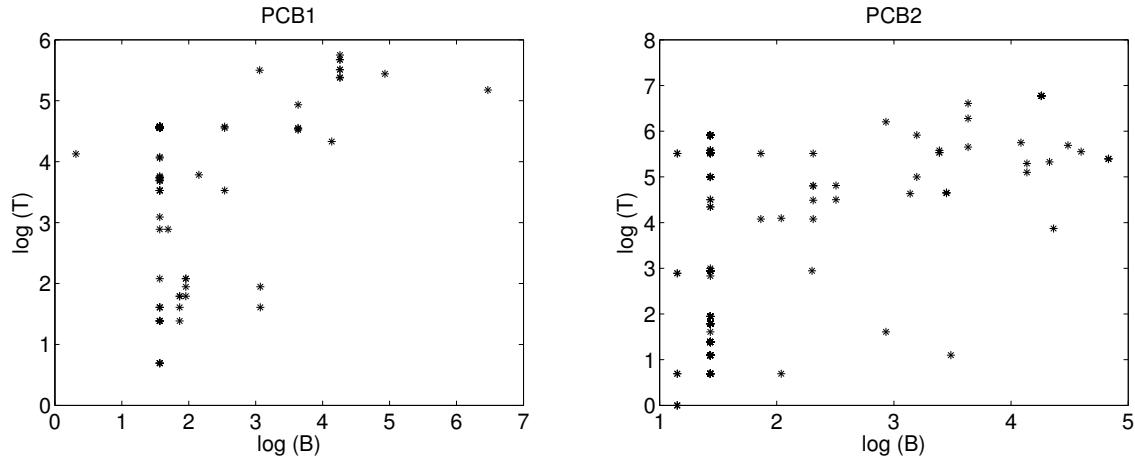

| Figure 5.3.4: Rent's plot of PCB1 and PCB2 using each component area on the board as a partition of the netlist. These plots are representative of the available netlist set, and they cannot be modeled using the Rent's power-law. . . . .                                                                                                                                                                                                | 102 |

| Figure 5.3.5: Histogram of the net degrees for several real netlists, and fitting with some distribution models using nonlinear least squares method and a 95% confidence rate. The exponential relation provides the best fit on all PCB profile (with various values), confirmed by a Chi-2 test with 95% confidence.                                                                                                                     | 104 |

| Figure 5.3.6: Histogram of net length distribution for PCB and VLSI netlists, fitted with an exponential distribution model. The fit is accepted by a Chi-2 test with 95% confidence. The net length distribution is normalized over the size of each netlist routing area. . . . .                                                                                                                                                         | 105 |

| Figure 5.4.1: The prototyping system schematic: user's IC are manually deposited on the wafer's surface, external connections are possible as well as probing digital on-wafer interconnection signals – in real time. . . . .                                                                                                                                                                                                              | 106 |

| Figure 5.4.2: Multi-dimensional mesh network: vertices are represented by squares (physically, crossbars) with their relative coordinates, and edges as wires. Edges for the vertex at coordinates (0;0) are shown for a mesh of dimension 2 ( $2^2 = 4$ ). . . . .                                                                                                                                                                         | 107 |

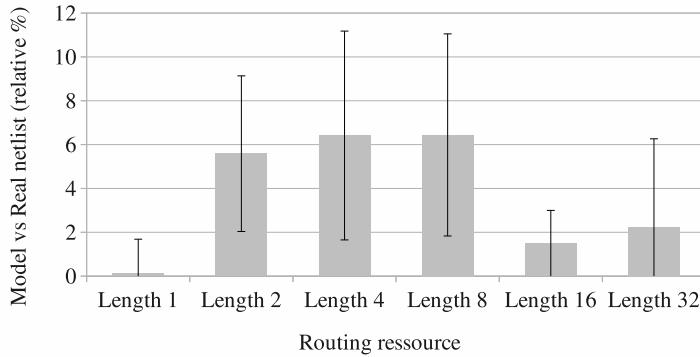

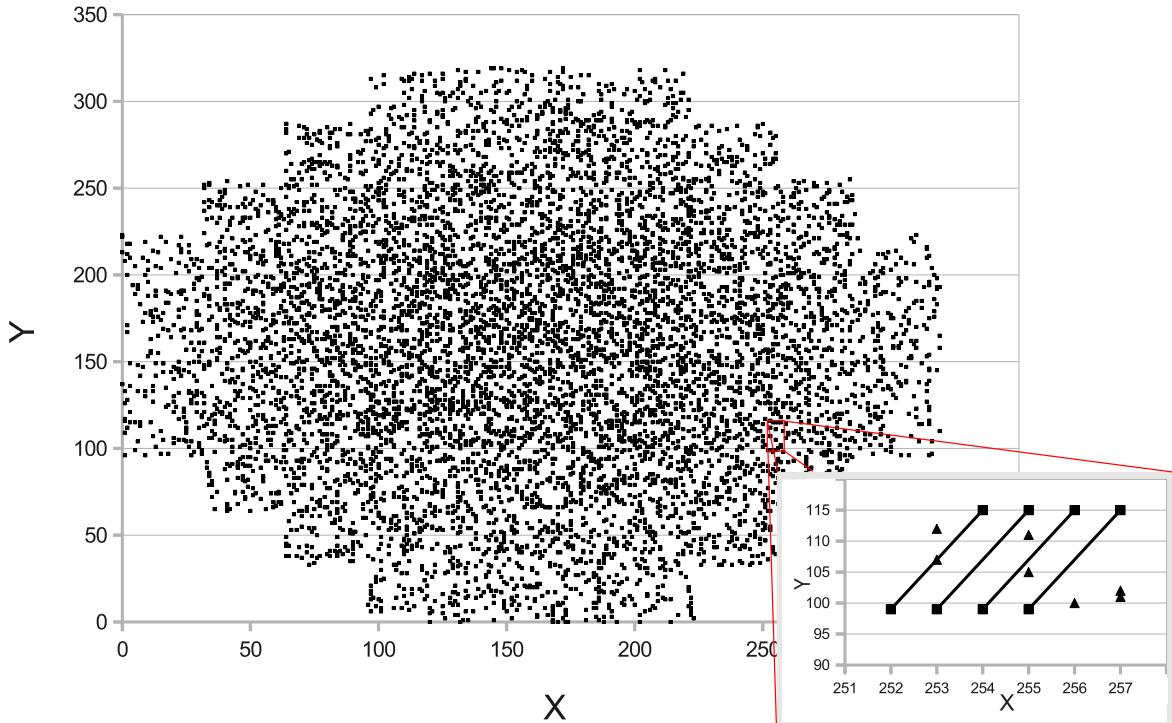

| Figure 5.5.1: Relative differences between synthetic and real netlists (%) for each category of routing resources, averaged over the fourteen netlists. The differences are larger for interconnect lengths 2, 4, 8 but are always below 12 %. . . . .                                                                                                                                                                                      | 110 |

113

# Liste des symboles

- ASIC** En anglais Application Specific Integration Circuit. Un circuit intégré (micro-électronique) dédié à une application particulière, réalisé avec l'aide de portes logiques assemblées, contrairement aux circuits dits full-custom. En général, il regroupe un grand nombre de fonctionnalités uniques et/ou sur mesure.

- BSG** En anglais Bounded Slice-surface Grid. Algorithme capable de réaliser un placement en fonction de contraintes qui caractérisent une fonction coût.

- CAD** En anglais Computed Aided Design (conception assistée par ordinateur). Comprend l'ensemble des logiciels et des techniques de modélisation géométrique permettant de concevoir, de tester virtuellement - à l'aide d'un ordinateur et des techniques de simulation numérique - et de réaliser des produits manufacturés et les outils pour les fabriquer. Source Wikipedia France.

- DCLC** En anglais Delay-constraint least cost problem (Problème du plus petit coût avec contrainte de délai). Problème général théorisé par les chercheurs dans le domaine des télécommunications.

- FLUTE** En anglais Fast Lookup Table Based Rectilinear. Algorithme capable de résoudre le problème d'arbre de Steiner, c'est-à-dire un problème d'optimisation combinatoire proche de l'arbre couvrant minimal.

- FPGA** En anglais Field Programmable Gate Arrays. Un circuit intégré logique qui peut être reprogrammé après sa fabrication. Source Wikipedia France.

- FPIC** En anglais Field Programmable Integrated Circuit. Un circuit reprogrammable, en particulier au niveau de ses entrées/sorties. Ils sont surtout utilisés pour des applications qui nécessitent de la flexibilité dans les interconnections, tout en offrant des vitesses de transfert importantes.

- PCB** En anglais Printed Circuit Board. Support, en général une plaque, permettant de relier électriquement un ensemble de composants électroniques entre eux, dans le but de réaliser un circuit électronique complexe. Source Wikipedia France.

- QoS** En anglais Quality of service. Capacité à véhiculer dans de bonnes conditions un type de trafic donné, en termes de disponibilité, débit, délais de transmission, gigue, taux de perte de paquets... Source Wikipedia France.

- RCV** En anglais Routing Cost Valley. Algorithme de routage capable de prendre en compte une contrainte de délai minimal et maximal pour une route donnée.

- TSV** En anglais Through Silicon Vias. Une technique de fabrication qui permet de percer des trous dans un wafer de silicium. En général, le perçage est réalisé par le dessous du wafer, pour atteindre une couche de métalisation. Un perçage complet est toutefois possible.

- VLSI** En anglais Very-Large-Scale Integration. Technologie de circuit intégré (CI) dont la densité d'intégration permet de supporter plus de 100 000 composants électroniques sur une même puce. Source Wikipedia France.

- VPR En anglais Versatile Place and Route. Outil capable de réaliser le placement et le routage global et détaillé pour FPGA.

- CMOS En anglais Complementary Metal Oxide Semiconductor. Technologie de fabrication de composants électroniques et, par extension, l'ensemble des composants fabriqués selon cette technologie. À l'instar de la famille Transistor-Transistor logic (TTL), ces composants sont en majeure partie des portes logiques (NAND, NOR, etc.) mais peuvent être aussi utilisés comme résistance variable. Source Wikipedia France.

- CPU En anglais Central Processing Unit. Le composant de l'ordinateur qui exécute les programmes informatiques. Avec la mémoire notamment, c'est l'un des composants qui existent depuis les premiers ordinateurs et qui sont présents dans tous les ordinateurs. Un processeur construit en un seul circuit intégré est un microprocesseur. Source Wikipedia France.

- GPS En anglais Global Positionning System. Un système de géolocalisation fonctionnant au niveau mondial. En 2011, il est avec GLONASS, un système de positionnement par satellites entièrement opérationnel et accessible au grand public. Source Wikipedia France.

- ISCAS En anglais International Symposium on Circuits and Systems.

- ISCAS En anglais International Symposium on Circuits and Systems.

- ISPD En anglais International Symposium On Physical Design. Conférence sur le design physique, principalement les outils d'aide à la conception.

- MCNC En anglais Microelectronics Center of North Carolina. Dans cette thèse, réfère aux bancs d'essais de circuits VLSI pour le placement et le routage.

- PL Programmation Linéaire. Un problème d'optimisation linéaire est un problème d'optimisation dans lequel on minimise une fonction linéaire sur un polyèdre convexe. Source Wikipedia France.

- PLE Programmation Linéaire Entière. Problème identique à un problème de Programmation Linéaire, mais dans lequel l'ensemble des variables du problème prennent des valeurs entières.

- R and R En anglais Rip-up and Reroute. Technique de routage utilisée par les algorithmes séquentiels, qui consiste à sélectionner une liste de routes à enlever, puis router à nouveau avec un nouvel ordre de priorité.

- RAM En anglais Random Access Memory. Mémoire dont les informations sont perdues lors de l'extinction du système.

- RSMT En anglais Rectilinear Steiner Minimum Tree. Arbre rectiligne de Steiner minimal.

- TCP/IP En anglais Transmission Control Protocol, Internet Protocol. La suite TCP/IP est l'ensemble des protocoles utilisés pour le transfert des données sur Internet.

Elle est souvent appelée TCP/IP, d'après le nom de deux de ses protocoles : TCP (Transmission Control Protocol) et IP (Internet Protocol), qui ont été les premiers à être définis. Source Wikipedia France.

# Introduction

Les recherches présentées dans cette thèse sont nées des besoins et contraintes particulières d'une nouvelle application micro-électronique : le *WaferBoard*<sup>TM</sup>. Cette application fut développée dans le cadre d'un projet de recherche appelé *DreamWafer*<sup>TM</sup> dans lequel plusieurs partenaires industriels sont également impliqués. Les principales universités participantes sont l'École Polytechnique de Montréal, l'Université du Québec à Montréal, l'Université du Québec en Outaouais. Le principal partenaire industriel est Gestion TechnoCap Inc.

Le marché de l'électronique oblige, pour rester compétitif, à augmenter fortement la complexité et le nombre de composants intégrés dans un même circuit. En conséquence, la complexité de mise au point et le temps de développement des *PCB* (*Printed Circuit Board*) augmentent fortement. L'augmentation de la densité des boîtiers des composants entraîne la mise au point de nouvelles technologies pour les supporter. C'est dans ce contexte que le projet mentionné vise la réalisation d'une nouvelle plateforme de prototypage rapide de systèmes électroniques. Son objectif est de permettre de réduire le cycle de développement de systèmes complexes de plusieurs mois à quelques jours, sinon quelques minutes, tout en réduisant le coût de fabrication du prototype. Une solution existante est l'utilisation des *FPIC* (*Field Programable Integrated Circuit*) [10] permettant de programmer quelques milliers de connexions sur un *PCB* classique. Plusieurs limitations existent avec cette technologie (en dehors de son coût) notamment la nécessité de produire un *PCB* pour chaque prototype avec les empreintes exactes de chaque composant utilisé, ou la nécessité d'étager plusieurs *FPIC* (dans un réseau de type Benes [11]) pour des systèmes complexes. Ces contraintes supplémentaires réduisent fortement le taux d'intégration sur une même carte. Le projet *DreamWafer* enlève ces inconvénients tout en accélérant la mise au point du matériel et du logiciel prototypé. Le cycle de développement est assuré par un logiciel dont les principaux aspects sont décrits plus loin. Pour alléger cette section, une revue de littérature complète des algorithmes de routage est faite au chapitre 2. Les contraintes et spécificités du projet qui touchent l'algorithme de routage sont résumés ci-après :

- Taille importante du réseau, comparée aux autres technologies comme les *VLSI* (*Very Large Scale Integration*) et *FPGA* (*Field Programmable Gate Arrays*). Le tableau 0.1 présente une comparaison des tailles respectives des technologies ;

- Architecture du réseau différente de celles utilisées sur circuits *FPGA*, *VLSI* ou *PCB* ;

- Absence d'algorithme de placement intelligent (le placement est réalisé par l'utilisateur, pour un prototype qui

ne durera pas) tel qu'utilisé pour les *FPGA* et *ASIC* ;

- Ressources de routage amputées par les défectuosités lors de la fabrication ;

- Contraintes fortes de temps de routage, de l'ordre quelques minutes ;

- Délai de propagation non monotone en fonction de la distance ;

- Le routeur prend comme entrée des *netlist* similaires à celles qui décrivent des systèmes réalisés à l'aide de circuits imprimés (*PCB*), difficiles à obtenir de la part d'industriels pour vérifier et étalonner les algorithmes implémentés.

Il est important pour la bonne compréhension de la portée et du contexte des recherches de présenter la plateforme matérielle qui sert de support à ces recherches. Une présentation en est donc faite dans cette introduction. Une analyse des points communs et des différences majeures avec d'autres technologies est proposée. Enfin, un aspect plus logiciel, les interactions de l'algorithme de routage au sein de l'outil complet de développement prévu, *WaferConnect*, est détaillé. Ainsi, cette introduction mettra en lumière le contexte des recherches, les principales contraintes matérielles en contraste avec d'autres domaines tels que les *FPGA*, les *PCB* ou encore les routeurs *VLSI*, ainsi que les contraintes côté logiciel.

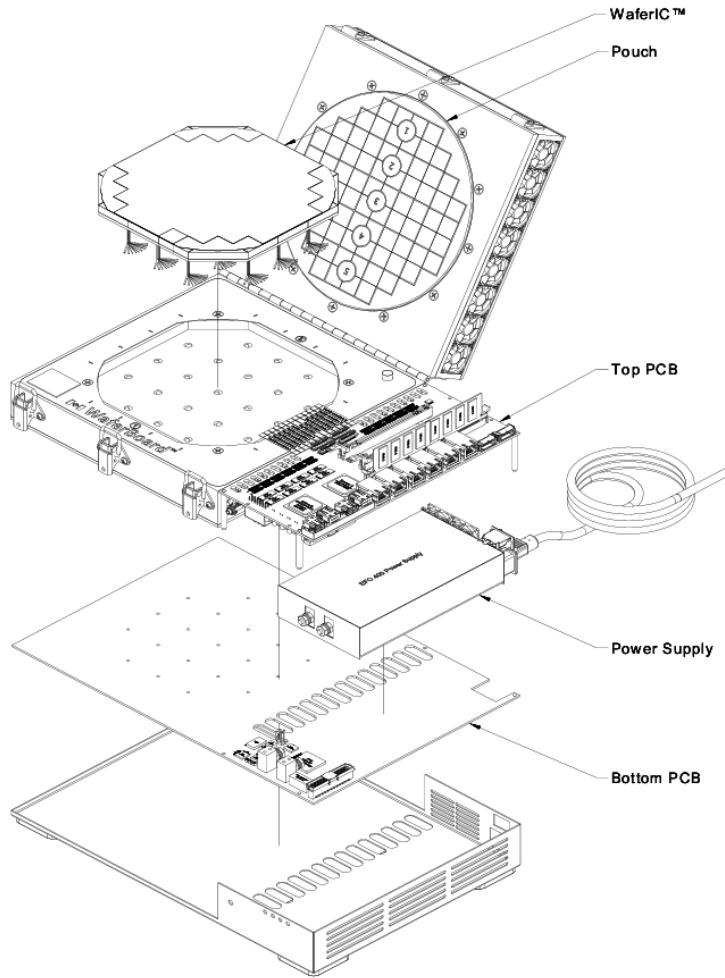

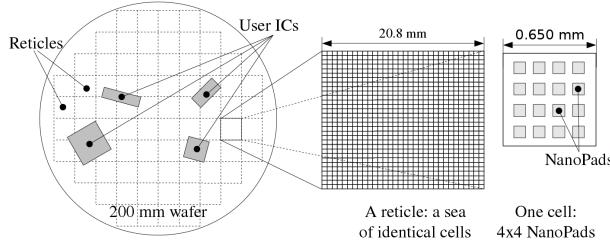

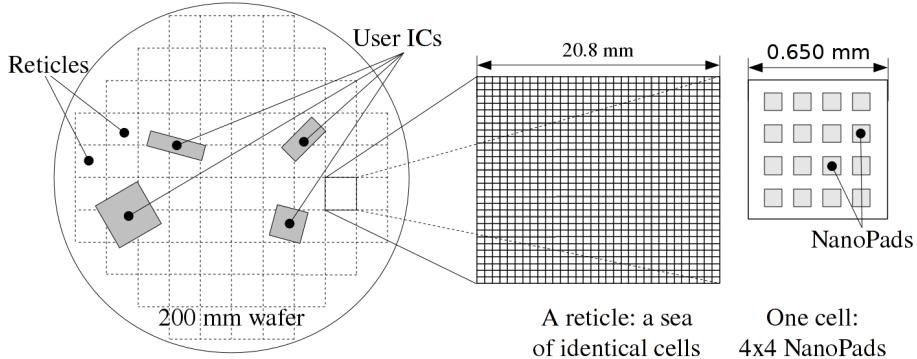

Pour appréhender la complexité du *WaferBoard*, il convient de le décrire sous la forme de subdivisions en modules distincts (figure 0.0.1). Le *WaferBoard* se présente sous la forme d'un ordinateur portable en plus épais (environ 20 cm × 15 cm × 10 cm). Il s'ouvre en deux comme montré sur la figure 0.0.1, avec d'un côté le couvercle et de l'autre une surface active appelée *WaferIC*. Il s'agit d'un circuit de la taille d'une tranche complète de silicium, contrairement aux circuits classiques sur *FPGA* et *VLSI*, qui occupent au plus quelques centimètres carrés. Dans le cadre du projet, le circuit qui sert de support à toute la technologie est une puce intégrée à l'échelle d'une tranche (on parle de *Wafer-Scale*) ce qui impose des contraintes uniques, notamment sur l'algorithme de routage qui nous intéresse ici tout particulièrement. Les composants sont déposés par l'utilisateur (sans soudure) sur le *WaferIC* en fonction de ses besoins, tel que schématisé sur la figure 0.0.2. Les billes ou broches doivent être non-traversantes pour être acceptées par la plateforme. Il est à noter que la très large majorité des systèmes électroniques aujourd'hui utilisent des boîtiers dont les broches ne traversent pas le *PCB*. Un film anisotropique appelé film Z (*Z-axis film*) constitué de centaines de millions de minuscules fils de cuivres verticaux garantis sans court-circuits est placé sur la surface du *wafer*. Ce film sert d'interface entre les broches et le *WaferIC* proprement dit. Ce film est élastique (en particulier sur l'axe vertical), ce qui permet d'avoir un bon retour en position de repos lorsque le couvercle est ouvert - la pression étant alors relâchée.

Sous le *WaferIC*, un ensemble de 21 blocs d'alimentations très particuliers appelés *PowerBlock* sont connectés au *WaferIC* par le dessous. Des « trous » appelés *TSV* (*Through Silicon Vias*) dans le *WaferIC* sont réalisés par un flux ionique qui traverse l'épaisseur du substrat jusqu'à rencontrer le cuivre d'une piste de la première couche de métal. Chaque bloc d'alimentation est connecté au *WaferIC* au travers de billes soudées sous les *TSV*, ce qui fournit les masses, deux rails d'alimentation (1.8 V et 3.3 V) et 5 fils pour la configuration du *WaferIC*. En plus de l'alimentation,

FIGURE 0.0.1: Modèle tridimensionnel du système physique dans son ensemble : le *WaferBoard*<sup>TM</sup>. Crédit TechnoCap Inc. *DreamWafer* Division. Reproduit avec permission.

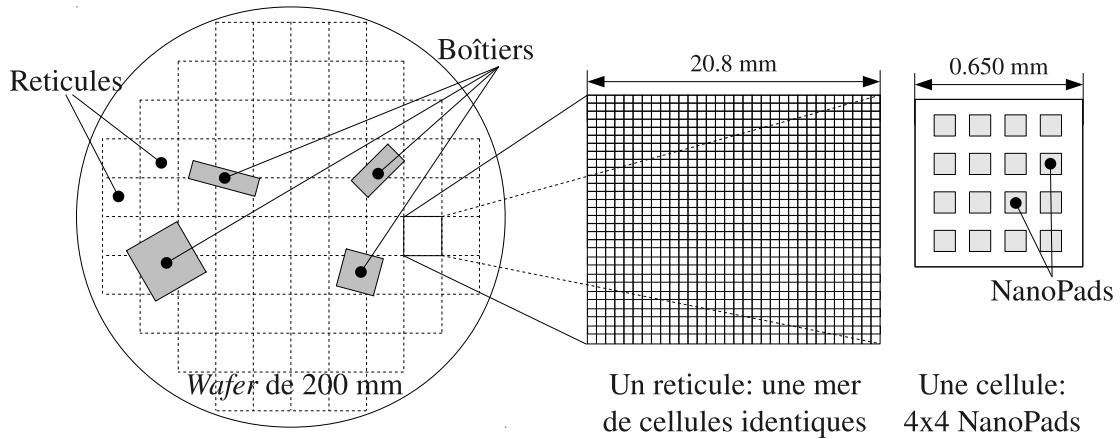

ces modules réalisent le lien de communication nécessaire entre le *Bottom-PCB* décrit plus loin, et les *WaferIC*. Un *PCB* appelé *Top-PCB* intègre des connexions vers un ordinateur, des *FPGA* et connecteurs externes destinés à compléter la connectique du *WaferBoard*. Les *FPGA* sur cette carte réalisent le pont de communication entre l'ordinateur de support et le *WaferIC*, mais ils sont également dimensionnés pour permettre d'injecter et de capturer des signaux directement au sein du réseau du *WaferIC*. Ces *FPGA* autorisent donc une communication directe avec les composants déposés sur le *WaferIC*. Un deuxième *PCB* appelé *Bottom-PCB*, placé sous le *WaferIC*, possède les connexions nécessaires vers ses signaux de configuration au travers des *PowerBlock*. Le flot de configuration part d'un ordinateur (celui de l'utilisateur), passe au travers d'un *FPGA* sur le *Top-PCB*, un autre sur le *Bottom-PCB*, est interprété par les *PowerBlock* pour finalement arriver au *WaferIC*. En réalité, un *PowerBlock* supporte 4 images de réticule (en pointillés sur la figure 0.0.2) qui sont des réminiscences de la méthode de fabrication des puces électroniques. Le circuit généré sur le *WaferIC* correspond à chaque image de réticule, et est accessible indépendamment.

Une question d'importance qui n'a pas encore été abordée suite à cette rapide présentation du *WaferBoard*, est de

FIGURE 0.0.2: Architecture du *WaferIC*, vue schématique peu détaillée. La mer de cellules permet au circuit d'être répété à l'infini.

comprendre comment les composants placés sur le *WaferIC* peuvent être interconnectés de la même façon que sur un *PCB*. Cet aspect est au cœur des contraintes de l'algorithme de routage. Pour le saisir il est nécessaire d'expliquer quelques détails de l'architecture interne du *WaferIC*.

Celui-ci est un substrat configurable fabriqué par juxtaposition d'images d'un réticule. De la même façon que tout circuit électronique sur silicium, chaque image de réticule correspond à un circuit à part entière. Cependant, les circuits classiques (sans redondance) sont testés sur la tranche directement, les fonctionnels sont conservés (et découpés) et les autres jetés, ou reconditionnés. Au contraire, le *WaferIC* est une seule tranche non découpée ; une opération non conventionnelle supplémentaire est réalisée lors de la fabrication pour « imprimer » des pistes de métal qui relient les circuits de chaque réticule entre eux, appelé *reticle stitching*. Ainsi, le *WaferIC* est donc bien un seul et même circuit de silicium.

Chaque image de réticule est constituée d'une mer de cellules identiques (figure 0.0.2), couvertes à leur surface de  $4 \times 4$  NanoPads, qui sont autant de points de contact possibles avec des billes de composants posés sur le wafer. Chaque cellule est un carré dont le côté mesure environ  $650 \mu\text{m}$ . L'espacement des NanoPads est petit devant la taille des billes des boîtiers présentement sur le marché, ce qui assure un contact d'un minimum de 2 NanoPads par bille. La cellule constitue la brique de base du circuit, et elle est répétée sur une image complète de réticule ( $32 \times 32$  cellules). Le nombre de NanoPads total est d'environ 1.8 millions, autant d'entrées et sorties qui peuvent être redirigées vers le réseau d'interconnexions interne au *WaferIC*.

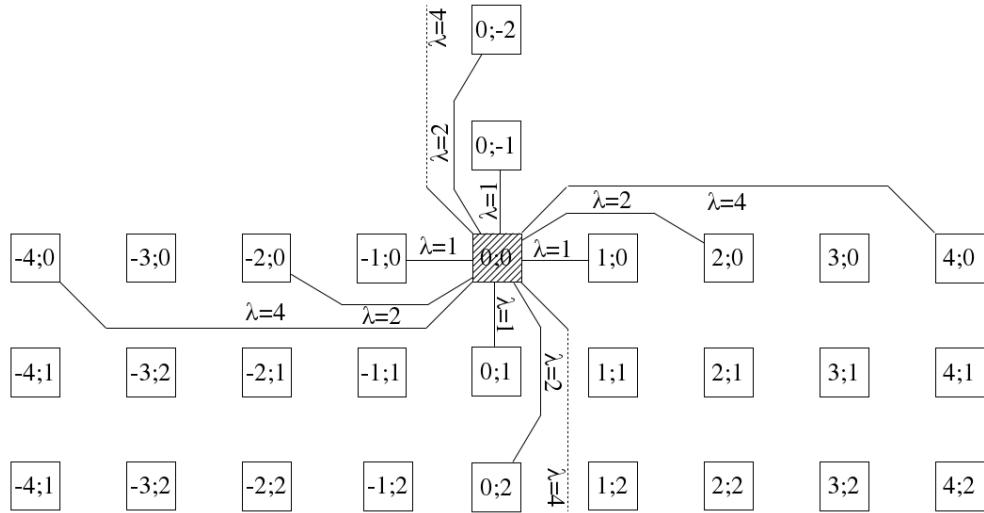

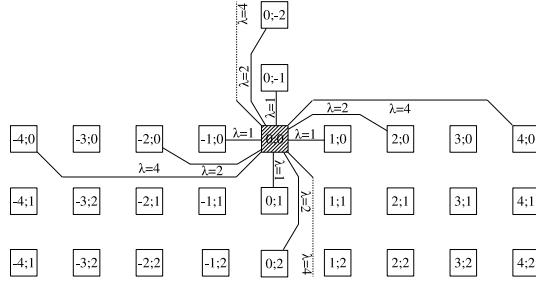

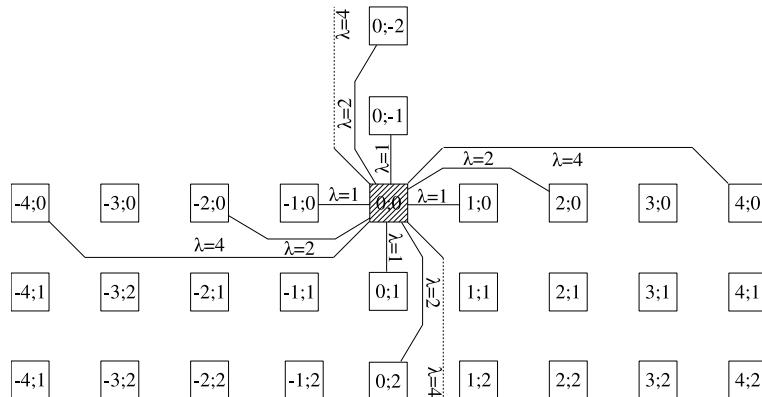

C'est ce réseau d'interconnexions qui sert de support à l'algorithme de routage pour réaliser un circuit fonctionnel. Du point de vue matériel, ce réseau est constitué de nœuds et d'arcs. Chaque nœud représente une cellule physique. Les arcs sont les nombreuses pistes métalliques qui relient les cellules entre elles. La figure 0.0.3 présente un schéma de quelques liens pour une cellule (hachurée). Pour chaque cellule, on retrouve les connexions présentes pour un réseau maillé classique, soit les 4 plus proches voisins selon les 4 points cardinaux. À ces connexions sont ajoutées des arcs

FIGURE 0.0.3: Architecture du réseau d’interconnexions intégré au *WaferIC*. Chaque cellule (représentée par un carré avec une coordonnée) possède des liens (arcs) vers ses 4 plus proches voisines, 4 voisines à distance 2, distance 4, ... jusqu’à 32 dans l’implémentation actuelle. Ainsi, ils forment un réseau multi-dimensionnel. Seuls sont représentés les liens de la cellule 0;0 sur quelques distances, mais le patron est répété pour chaque cellule.

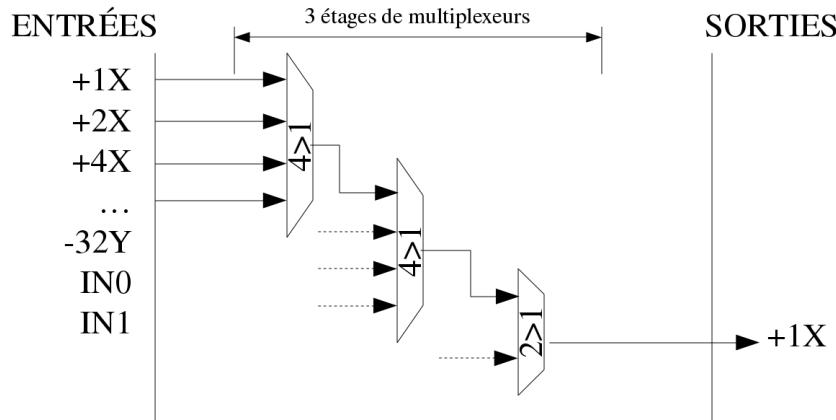

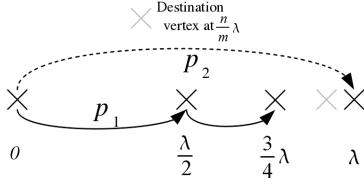

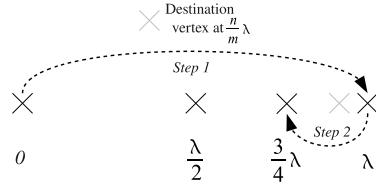

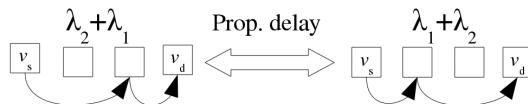

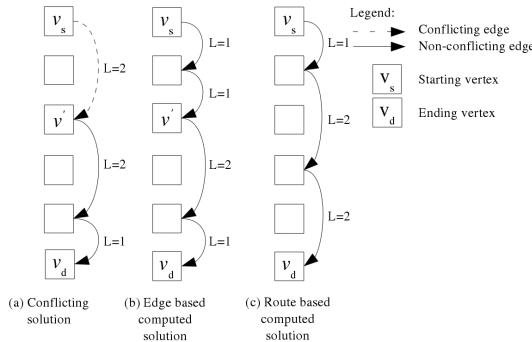

connectés aux cellules de distance 2, 4, 8, 16, 32 selon les 4 points cardinaux, soit 6 longueurs différentes. Enfin, chaque arc est unidirectionnel, il existe donc 2 arcs pour chaque paire de cellule source-destination, un dans chaque direction. Au total, le nombre de connexions d’une cellule vers ses voisines directes est de 2 directions  $\times$  4 points  $\times$  6 longueurs = 48 arcs. Un réseau maillé multi-dimensionnel possède des arcs de longueur  $2^n, n \in [0 : N]$  et  $N \in \mathbb{N}$ . Le degré d’un tel réseau réfère à  $n$ , le degré de l’arc le plus grand. Spécifier  $n$  suffit à caractériser le réseau. Ainsi, le *WaferIC* possède un réseau de degré 5 ( $2^5 = 32$ ). La toute première version, qui a été testée physiquement sur une puce de test fabriquée par TSMC, possédait un réseau de degré 6.