|                         | An Image Processing Approach Toward a Visual Intra-Cortical Stimulator                                                                                                                                                                                           |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Anthony Ghannoum                                                                                                                                                                                                                                                 |

| Date:                   | 2012                                                                                                                                                                                                                                                             |

| Туре:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                        |

| Référence:<br>Citation: | Ghannoum, A. (2012). An Image Processing Approach Toward a Visual Intra-<br>Cortical Stimulator [Mémoire de maîtrise, École Polytechnique de Montréal].<br>PolyPublie. <a href="https://publications.polymtl.ca/1003/">https://publications.polymtl.ca/1003/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/1003/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Mohamad Sawan                         |

| <b>Programme:</b><br>Program:            | Génie Électrique                      |

# UNIVERSITÉ DE MONTRÉAL

# AN IMAGE PROCESSING APPROACH TOWARD A VISUAL INTRA-CORTICAL STIMULATOR

ANTHONY GHANNOUM DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (GÉNIE ÉLECTRIQUE) DÉCEMBRE 2012

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

# AN IMAGE PROCESSING APPROACH TOWARD A VISUAL INTRA-CORTICAL STIMULATOR

présenté par : <u>GHANNOUM Anthony</u> en vue de l'obtention du diplôme de : <u>Maîtrise ès sciences appliquées</u> a été dûment accepté par le jury d'examen constitué de :

M. <u>BRAULT Jean-Jules</u>, Ph.D., président

M. <u>SAWAN Mohamad</u>, Ph.D., membre et directeur de recherche

Mme CHÉRIET Farida, Ph.D., membre

## **ACKNOWLEDGEMENTS**

I would like to start by thanking my Master thesis supervisor professor Mohamad Sawan for his support and patience as well as the Polystim Neurotechnologies Lab members who always provided a lighthearted mood and critical thinking environment.

I would also like to thank my sister Roula Ghannoum for her outstanding help throughout this period.

Moreover, I would like to acknowledge support from NSERC and the Canada Research Chair on Smart Medical Devices.

## RÉSUMÉ

La déficience visuelle n'est actuellement pas médicalement traitable. Par contre, des approches biomédicales modernes, tel que le projet Cortivision, emploient la micro stimulation intra-corticale pour stimuler la vision électriquement. Cela fait apparaître des «phosphènes», des points lumineux, dans le champ visuel du patient. Des constellations de ces phosphènes peuvent être utilisées pour reproduire une certaine vision de base.

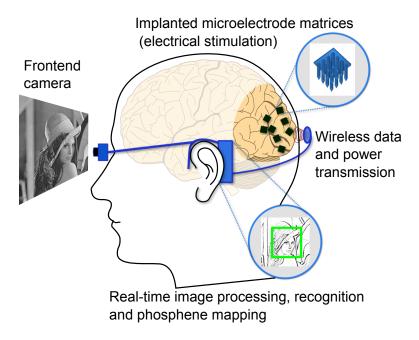

Le système comprend une caméra, un module de traitement d'images, un lien sans fil, et des matrices de micro-électrodes implantées directement dans le cortex visuel du patient.

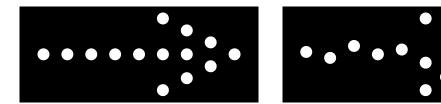

La carte phosphène (l'arrangement de point lumineux dans le champ de vision) est directement liée au placement physique des électrodes; elle est généralement plus dense vers le centre (plutôt que d'être espacée uniformément comme dans une image numérique). Cela veut dire qu'il n'existe pas une fonction simple pour traduire les images acquises par la caméra sur la carte phosphène, d'où la nécessité d'avoir un module de traitement d'image.

L'aide du patient est nécessaire pour déterminer sa carte phosphène particulière et réelle. Une méthode de calibration qui expose le patient à des combinaisons de paires de phosphènes différentes est utilisée avec des algorithmes de triangulation et minimisation d'erreur. Toute erreur dans la phase d'estimation induirait des distorsions dans l'image finale (dans les stimuli envoyés au cortex du patient).

Néanmoins, la plupart des systèmes utilisent une carte phosphène simplifiée uniformément répartie ainsi que des techniques simples de traitement d'image comme un seuillage simple ou la segmentation. Nous proposons d'utiliser un traitement d'image de plus haut niveau, comme la reconnaissance d'objets, afin d'être en mesure d'identifier et de «simplifier» les données avant de les envoyer au patient. Dans ce cas, nous envoyons une représentation du contenu de la scène au cortex du patient, et non pas une version abrégée de la scène — l'algorithme utilise les vraies images pour identifier les objets, tandis que dans le cas des autres systèmes, le patient doit identifier les objets lui-même à partir d'une image très simplifiée; une tâche non-triviale. Une telle approche est coûteuse en terme de calcul, et nécessiteraient également de rouler en temps réel pour notre application. Pour subvenir à ces besoins, nous proposons d'accélérer les goulots d'étranglement de l'algorithme en utilisant une approche matérielle parallélisable (FPGA).

L'objectif est de développer un système temps-réel, paramétrable, et efficace en termes de ressources matérielles FPGA et de bande passante. Ceci nous permettra d'effectuer des tâches de reconnaissance d'objet robustes rapidement qui peuvent ensuite être utilisés pour stimuler la carte phosphène d'une manière plus adéquate, plus utile, et moins exigeante du

patient.

Après avoir examiné les algorithmes possibles et les approches qui peuvent être utilisées, nous avons identifié le Scale Invariant Feature Transform (SIFT) comme un bon candidat pour notre système, principalement en raison du fait qu'il est très robuste aux variations d'images telles que l'éclairage, les transformations affines, et les occlusions partielles d'un objet.

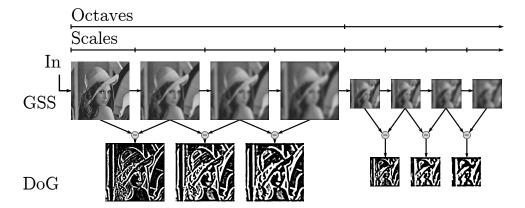

Le SIFT peut être divisé en deux grandes parties : l'extraction et la description de caractéristiques. L'étape d'extraction est basée sur le calcul de la différence de gaussiennes (DoG) et peut être considéré comme un détecteur de blob invariant à l'échelle qui permet de détecter les points «intéressants» dans une image. La deuxième partie considère la région qui entoure le point d'intérêt et constitue un vecteur de description (ou une signature), qui est essentiellement une collection d'histogrammes de gradients normalisés à la rotation.

Après avoir mis en place un prototype logiciel de reconnaissance d'objet spécifique, nous avons remarqué que le goulot d'étranglement qui empêche l'algorithme SIFT de fonctionner en temps réel se trouve dans la partie DoG. Nous avons alors recueilli nos efforts pour migrer cette partie de l'architecture vers du matériel parallélisable d'un FPGA.

La partie DoG nécessite le calcul d'une pyramide d'images, qui est essentiellement une répétition de filtres Gaussien 2D (pour former des échelles), suivi d'un sous-échantillonnage (pour former des octaves). Les résultats des différentes échelles doivent par la suite être synchronisés et soustraits, et les points d'extrêmes locaux à travers les échelles sont considérés comme des points d'intérêt.

Après avoir examiné les implémentations existantes du DoG, nous proposons une nouvelle architecture efficace capable de partager les ressources FPGA bloc RAM pour le filtrage et aussi de réduire la taille des FIFOs de synchronisation. Nous avons également exploité des concepts tels que l'entrelacement d'octaves, la séparabilité des filtres 2D, et la symétrie des filtres. Notre architecture utilise moins de ressources que d'autres implémentations dans la littérature, tout en étant comparable en terme de précision à une implémentation logicielle à virgule flottante. L'implémentation FPGA est capable de rouler à deux ordres de grandeur plus vite qu'une implémentation logicielle équivalente.

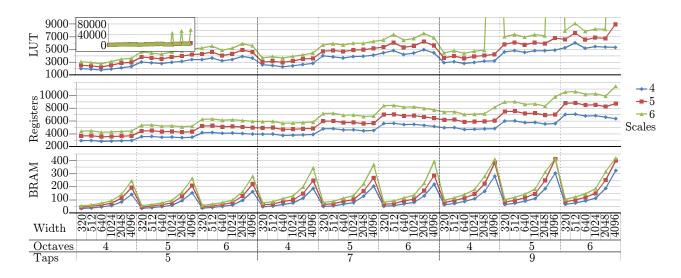

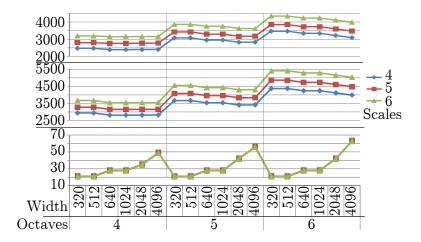

De plus, notre architecture est paramétrable en utilisant les génériques VHDL, et nous démontrons comment notre consommation de ressources est affectée en effectuant des balayages de paramètres pour : le nombre d'échelles, le nombre d'octaves, la largeur des filtres, et la largeur maximale de l'image.

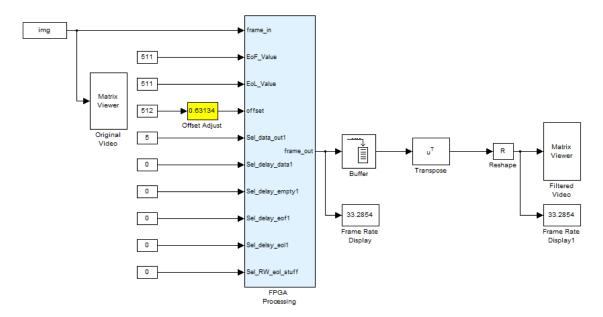

Le système a été validé sur une carte de prototypage Xilinx ML605 en utilisant MATLAB et Xilinx System Generator afin de fonctionner en mode co-simulation avec le matériel dans la boucle. L'interface Ethernet est utilisée pour le transfert d'images.

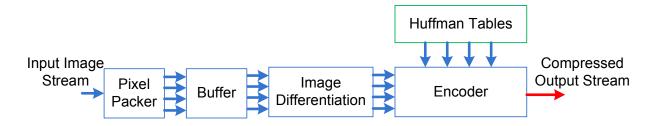

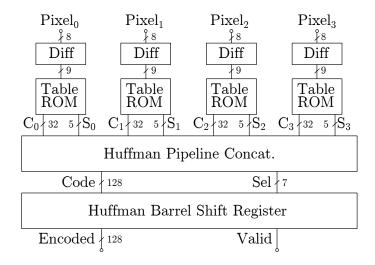

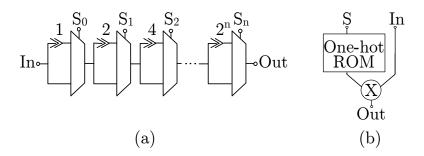

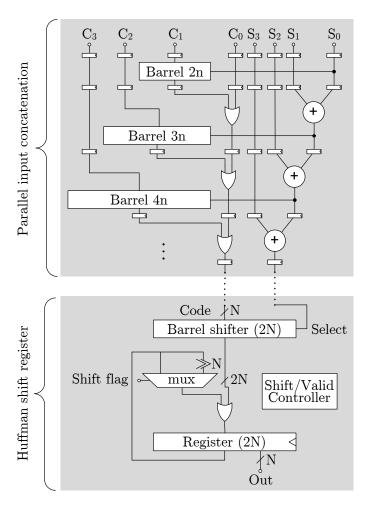

Afin de calculer les descripteurs de caractéristique (deuxième partie du SIFT), nous avons parfois besoin d'envoyer la pyramide d'images à l'hôte, ou de la sauvegarder dans la mémoire externe pour un traitement ultérieur. Après avoir remarqué la similitude des données (dans les sens x et y) et aussi à travers les échelles adjacentes à cause du filtrage, nous sommes arrivés avec une architecture pour un encodeur de Huffman parallèle qui est capable de traiter plusieurs pixels à la fois. Cet encodeur peut être utilisé pour la compression sans perte des images ou des pyramides d'images. Pour les pyramides d'images, nous avons utilisé une version modifiée du prédicteur Paeth qui tient compte de l'échelle adjacente pour l'étape de différenciation et nous avons réussi à atteindre des taux de compression de 27, 3% sur la base d'images Caltech-256.

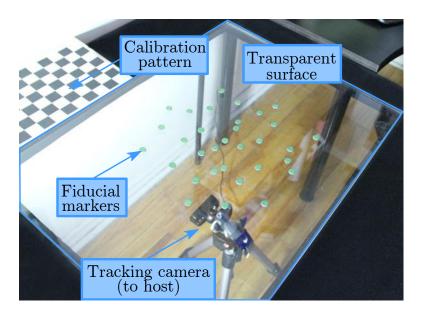

Une autre voie qui a été explorée concerne l'estimation de la carte phosphène. Dans la littérature, certains avaient suggérer une installation de calibration qui consiste à utiliser un écran tactile et des lunettes de réalité virtuelle pour simuler le champ de vue du patient. Le patient est ensuite présenté avec des paires de phosphènes et devra fournir de la rétroaction en utilisant deux doigts pour toucher l'écran tactile et essayer d'évoquer aussi précisément que possible ce qu'il perçoit (distance et angle).

Nous proposons une configuration alternative qui n'utilise pas un écran tactile, mais plutôt une installation d'une caméra qui localise et suit plusieurs marqueurs fiduciaires qui peuvent être manipulés simultanément par le patient pour fournir une rétroaction pour la calibration de la carte phosphène. La caméra sera placée sous une table de surface transparente et les marqueurs fiduciaires seront donc toujours visibles par la caméra. L'image est rectifiée pour enlever les distorsions et les marqueurs sont suivis simultanément. Ceci nous donne l'avantage d'avoir une résolution plus élevé qu'un écran tactile, la possibilité d'utiliser des constellations de phosphènes (au lieu de seulement deux paires à la fois) et la possibilité de modifier l'estimation de la carte calibrée en temps réel en utilisant la rétroaction du patient. Si le nombre de marqueurs est le même que le nombre de phosphènes, l'emplacement physique final des marqueurs sur la table représente directement la carte phosphène qui est effectivement perçue par le patient.

Pour résumer, nous avons identifié l'algorithme SIFT comme un bon candidat pour la reconnaissance d'objets et nous l'avons accéléré en utilisant une nouvelle architecture pour calculer l'extraction de caractéristiques (partie DoG) dans le matériel qui est paramétrable et efficace en termes de consommation de ressources, tout en conservant une précision comparable à une implémentation logicielle. En outre, nous avons identifié la redondance des données dans les images et les résultats intermédiaires pyramidales et nous avons proposé une architecture pour un encodeur de Huffman parallèle qui peut être utilisée pour soulager les goulots d'étranglement. Aussi, nous avons proposé une installation alternative à explorer

pour la calibration et l'estimation de la carte phosphène.

Notre système permet un traitement d'information haut niveau pour l'implant intracortical. La compréhension de l'entourage par des méthodes telles que la reconnaissance d'objets nous permettra de simplifier les données avant de les envoyer vers la stimulation sur un nombre limité de phosphènes.

#### **ABSTRACT**

Visual impairment may be caused by various factors varying from trauma, birth-defects, and diseases. Until today there are no viable medical treatments for this condition; hence bio-medical approaches are being employed to overcome that. The Cortivision team has been working on an intra-cortical implant that can bypass the retina and optic nerve and directly stimulate the visual cortex. In this work we aimed to implement a modular, reusable, and parameterizable object recognition system that tends to "simplify" video data prior to stimulation; hence opening new horizons for partial vision restoration, navigational and even recognition abilities.

We identified the Scale Invariant Feature Transform (SIFT) algorithm as being a robust candidate for our application's needs. A multithreaded software prototype of the SIFT and Lucas-Kanade tracker was implemented to ensure proper overall operation. The feature extractor, difference of Gaussians (DoG) part of the SIFT, being the most computationally expensive, was migrated to an FPGA implementation due to the real-time restrictions that is not achievable on a host machine. The VHDL implementation is highly parameterizable for different application needs and tradeoffs. We introduced a novel architecture employing the sub-kernel trick to reduce resource usage compared to preexisting architectures while still being comparably accurate to a software floating point implementation. In order to alleviate transmission bottlenecks, the system also includes a new parallel Huffman encoder design that is capable of performing lossless compression of both images and scale space image pyramids taking into account spatial and scale data correlations during the predictor phase. The encoder was able to achieve compression ratios of 27.3% on the Caltech-256 data-set. Furthermore, a new camera and fiducial markers setup based on image processing was proposed in order to target the phosphene map estimation problem which affects the quality of the final stimulation that is perceived by the patient.

# CONDENSÉ EN FRANÇAIS

## Introduction et objectifs

La déficience visuelle, qui est définie par la perte totale ou partielle de la vision, n'est actuellement pas médicalement traitable. Des approches biomédicales modernes sont utilisées pour stimuler électriquement la vision; ces approches peuvent être divisées en trois groupes principaux : le premier ciblant les implants rétiniens Humayun et al. (2003), Kim et al. (2004), Chow et al. (2004); Palanker et al. (2005), Toledo et al. (2005); Yanai et al. (2007), Winter et al. (2007); Zrenner et al. (2011), le deuxième ciblant les implants du nerf optique Veraart et al. (2003), Sakaguchi et al. (2009), et le troisième ciblant les implants intra-corticaux Doljanu et Sawan (2007); Coulombe et al. (2007); Srivastava et al. (2007). L'inconvénient principal des deux premiers groupes, c'est qu'ils ne sont pas suffisamment génériques pour surmonter la majorité des maladies de déficience visuelle, car ils dépendent du fait que le patient doit avoir un nerf optique intact et/ou une rétine partiellement opérationnelle; ce qui n'est pas le cas pour le troisième groupe.

L'équipe du Laboratoire Polystim Neurotechnologies travaille actuellement sur un implant intra-cortical qui stimule directement le cortex visuel primaire (région V1); le nom du projet global est Cortivision. Le système utilise une caméra, un module de traitement d'image, un transmetteur RF (radiofréquence) et un stimulateur implantable. Cette méthode est robuste et générique car elle contourne l'oeil et le nerf optique. Un des défis majeurs est le traitement d'image nécessaire pour «simplifier» les données antérieures à la stimulation, l'extraction de l'information utile en écartant les données superflues. Les pixels qui sont capturés par la caméra n'ont pas de correspondance un-à-un sur le cortex visuel comme dans une image rectangulaire, ils sont plutôt mis en correspondance avec une carte complexe de «phosphènes» Coulombe et al. (2007); Srivastava et al. (2007). Les phosphènes sont des points lumineux qui apparaissent dans le champ de vision du patient quand le cerveau est stimulé électriquement. Ces points changent en terme de taille, de luminosité et d'emplacement en fonction de la façon dont la stimulation électrique est effectuée (c'est à dire un changement dans la fréquence, la tension, la durée, etc. ...) et même par le placement physique des électrodes dans le cortex visuel.

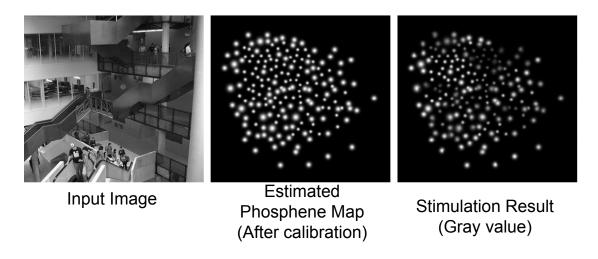

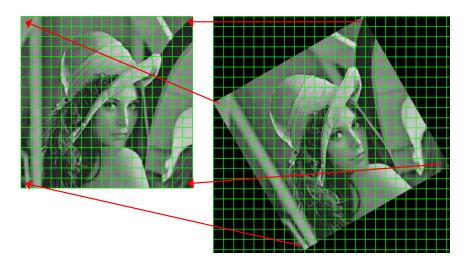

Les approches actuelles visent à stimuler des images de phosphènes monochromes à basse résolution. Sachant cela, nous nous attendons plutôt à une vision de faible qualité qui rend des activités comme naviguer, interpréter des objets, ou encore lire, difficile pour le patient. Ceci est principalement dû à la complexité de l'étalonnage de la carte phosphène et sa correspondance, et aussi à la non-trivialité de savoir comment simplifier les données à partir des images qui viennent de la camera de façon qu'on conserve seulement les données pertinentes. La Figure 1.1 est un exemple qui démontre la non-trivialité de transformer une image grise en stimulation phosphène.

Des techniques de traitement d'images comme la détection de bords, la segmentation et des approches de vision stéréo ont été proposées dans la littérature comme un moyen de réduire l'information avant la stimulation.

Le concept de réalité augmentée a récemment été introduit. Il s'agit d'un domaine de recherche en informatique qui traite le mélange des données réelles avec des données générées par ordinateur en temps réel.

Un problème principal qui est souvent ignoré, c'est que la carte phosphène n'est pas assez précise; d'où l'utilisation d'un système en temps réel de reconnaissance d'objets peut amplement contribuer à la simplification de l'environnement pour que les patients non-voyants puissent mieux naviguer dans leur environnement et se doter de capacités de reconnaissance. Les systèmes de déficience visuelle précédents utilisent des techniques de traitement d'images simples qui n'incorporent pas la reconnaissance.

L'objectif serait d'améliorer la qualité ou la méthodologie utilisée pour la perception en temps réel en utilisant des techniques de traitement d'images accélérées sur le matériel parallélisable (FPGA), offrant ainsi une réalité augmentée dans lequel des objets spécifiques peuvent être localisés et/ou reconnus, puis transmis au patient.

Le système doit aussi être paramétrable et indépendant de la plateforme, pour être efficace et réutilisable pour des taches différentes. En outre, la mise en œuvre d'un prototype se servant des ressources FPGA doit être économe en ressources au cas où elle doit être mappée sur des circuits intégrés dédiés.

Les objectifs peuvent être résumés de la façon suivante : 1) Identifier et développer un algorithme logiciel robuste et parallélisable qui peut effectuer la localisation et la reconnaissance d'un nombre limité d'objets sur lesquels il a été formé; ceux-ci devraient varier dans la pose et l'éclairage. 2) Accélérer les goulots d'étranglement de l'algorithme en utilisant des modules sur matériel (FPGA) qui sont en mesure d'atteindre des performances temps réel. Ces modules doivent être suffisamment génériques pour être réutilisables (peuvent être facilement transférées à une autre plate-forme) et paramétrable, tout en étant aussi efficaces que possible à la fois en termes de ressources et d'utilisation de bande passante. 3) Valider la précision des modules matériels en les comparants à une mise en œuvre équivalente en logiciel.

4) Enquêter sur les méthodes possibles d'estimation et d'étalonnage de la carte phosphène.

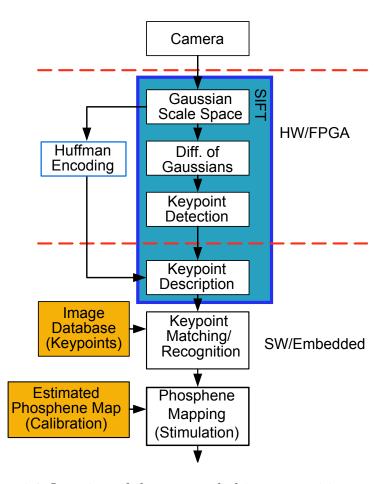

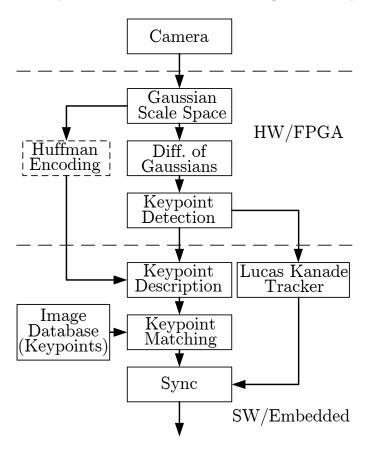

Figure 1.2 montre une vue d'ensemble du système qu'on propose. Les détails des différentes parties seront expliqués dans les chapitres à venir. Nous allons utiliser le Scale Invariant

Feature Transform (SIFT) pour extraire et décrire des points clés. La première partie du SIFT sera accélérée dans un FPGA en utilisant une nouvelle architecture pour économiser les ressources. Une base de données d'objet en forme de points-clés est utilisé pour les comparer avec ceux des images qui viennent de la camera. La reconnaissance d'objets est faite quand assez de point-clés sont assortis et après, une stimulation appropriée peut être envoyée aux matrices d'électrodes. Un codeur de Huffman est utilisé pour réduire les goulots d'étranglement HW/SW, et on propose aussi une nouvelle configuration pour la calibration de la carte phosphène.

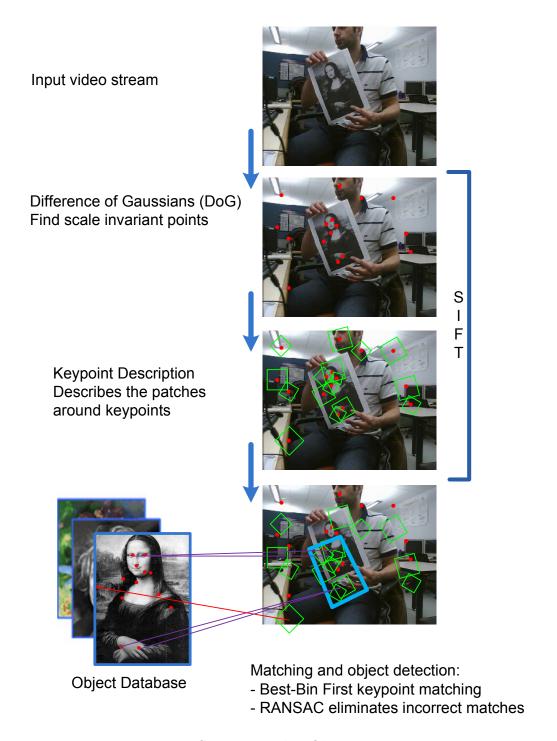

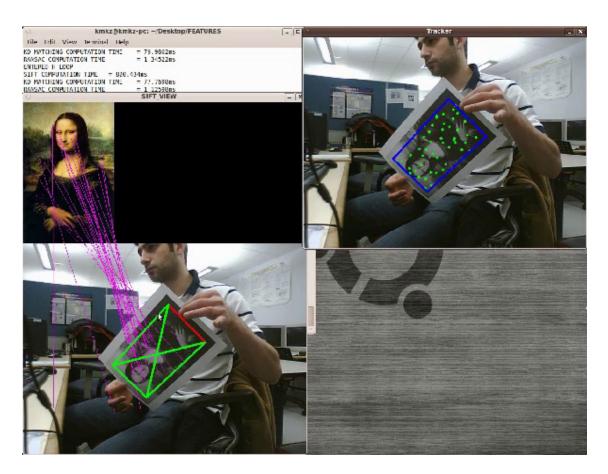

Un exemple visuel qui décrit l'utilisation du SIFT pour la reconnaissance d'objets est montré dans la Figure 2.8

## Étapes de recherche

Nous avons commencé par examiner les différentes approches de traitement d'image et des algorithmes qui peuvent être utilisés à des fins de reconnaissance d'objets. Après cela, nous avons étudié comment les FPGA peuvent être utilisés efficacement pour nos tâches spécifiques d'une manière optimisée.

L'une des méthodes de base de traitement d'image utilisées pour déterminer si un objet (ou plutôt un modèle spécifique) se trouve dans une image d'entrée est la mise en correspondance de modèle. Le modèle est généralement plus petit que l'image cible, et le but serait de déterminer la boîte qui englobe l'objet en question. En termes d'entrainement, cette méthode nécessite un modèle exact de l'image ou de l'objet cible. Le score de correspondance peut être calculée en utilisant de différentes méthodes d'où on peut avoir un compromis entre la complexité de calcul et la robustesse, tels que : la différence des carrés, la corrélation et la corrélation normalisée.

L'avantage principal d'une telle approche réside dans la simplicité algorithmique de la méthode, mais dans des situations réelles il existe plusieurs désavantages, comme ceux qui sont indiquées ci-dessous : 1) La dépendance d'illumination : Si la luminosité du modèle est différente de celle de l'objet dans l'image de recherche, il serait difficile de trouver une bonne correspondance. 2) Gradients d'éclairage : Bien que le processus de normalisation puisse être utilisé pour cibler le problème précédent, un éclairage gradient va probablement échouer même avec la normalisation. 3) La complexité de calcul : Comme il est clair d'après les équations de correspondance, le temps de calcul dépend directement de la taille du modèle. 4) Les transformations affines et d'échelles, la rotation et/ou l'inclinaison de l'objet cible dans l'image de recherche causerait cette méthode d'échouer, car elle ne tient pas en compte les transformations affines ou les distorsions. 5) Occlusion/correspondances partielles : Le

modèle ne doit pas être obstrué et doit avoir plus ou moins une correspondance parfaite sur toute la surface du modèle pour une bonne détection. 6) Choix du Seuil : Choisir le seuil approprié pourrait s'avérer un peu difficile quand on essaie d'adapter le système pour des environnements différents.

Les méthodes basées sur les caractéristiques des images pour la détection d'objets ont culminé dans la littérature, telles que celles qu'on trouve dans Lowe (2004), Bay et al. (2008), Mikolajczyk et Schmid (2005), Bosch et al. (2007), Dalal et Triggs (2005). Ces méthodes ont plusieurs applications tel que la détection d'objets Lowe (2004), Lowe (2001), Lowe (1999), Bay et al. (2008), Bay et al. (2006), le mosaïquage d'images Brown et Lowe (2003), la cartographie et localisation simultanée (SLAM) Montemerlo et al. (2002) Castle et al. (2010) et même la classification de scènes et de contexte Lazebnik et al. (2006).

Les méthodes basées sur les caractéristiques utilisent des patchs (ou caractéristiques) prises autour de points «intéressants» (ou points-clés) dans l'image qui seront utilisées pour déterminer des correspondances.

Au lieu d'utiliser une image de référence comme modèle, nous extrayons les caractéristiques intéressantes à partir de l'image modèle d'un objet et nous essayons ensuite de trouver des correspondances de caractéristiques dans une image différente. Une telle approche va supprimer la plupart des limitations qu'on avait mentionnées précédemment.

Ces algorithmes peuvent être divisés en deux grandes étapes : la localisation (ou l'extraction) de point-clés et la description des caractéristiques. À l'étape de localisation des point-clés, nous essayons d'extraire des points saillants et «intéressants» de l'image (pour qu'on puisse plus tard décrire les caractéristiques ou patchs qui entourent ces points). Les points-clés peuvent être considérés comme des arêtes, des coins, ou même des points invariants à l'échelle.

Les coins d'une image sont généralement considérés comme des bonnes caractéristiques car, ceux-ci ont des variations dans toutes les directions et donc sont relativement stables et peuvent être extraits d'une manière robuste.

En termes de définitions mathématiques, un coin peut avoir de différentes caractéristiques et certaines définitions peuvent être plus robustes en termes de rotation, mise à l'échelle, transformations affines et/ou même pour extraire des blobs. Quelques détecteurs de coins que nous avons étudiés sont : Le détecteur de coins Harris, Shi-Tomasi, détecteur de coins morphologique et les détecteurs de coins multi-échelles.

Les détecteurs de coins multi-échelles ont l'avantage d'être en mesure de relocaliser le même point-clé à une échelle différente; ce qui est pas mal fréquent dans des situations réelles.

Le résultat des détecteurs de coins, utilisés indépendamment comme coordonnées, peut

être assez bon pour correspondre des caractéristiques ou des points-clés à travers des images avec des mouvements mineurs, par exemple pour des fins de suivre un objet. Mais pour l'exigence d'apparier les caractéristiques ou même des objets entiers à travers des images avec des différences en illumination, échelle et/ou rotation, un détecteur de coin tout seul ne fonctionnera pas. Par conséquence on se fie plutôt à des approches basées sur les caractéristiques tel le «Scale Invariant Feature Transform (SIFT)» Lowe (2004); Ces approches rajoutent une description ou une signature aux coins (ou point-clés) afin d'obtenir des caractéristiques distinctives et discriminantes.

Nous ferons appel à l'algorithme SIFT à cause de sa robustesse et sa capacité de faire correspondre des caractéristiques avec des variations d'échelle, des changements de point de vue, des rotations, des différences d'éclairage et même des occlusions partielles. De plus, les caractéristiques sont assez distinctives pour les comparer à une grande base de données, ce qui rend le SIFT idéal pour des applications telles que la détection d'objets, la classification de scènes et la mise en correspondance d'images.

La méthode peut être divisée en deux parties majeures :

- L'extraction de point-clés : Cette partie est comparable à une extraction coin multiéchelle (ou l'extraction blob) et est basé sur la pyramide d'images et plus spécifiquement la différence de Gaussiennes (Difference of Gaussians DoG).

- Description de points-clés : Les patches autour d'un point clé sont choisies et caractérisées pour être utilisées comme un vecteur de signature en utilisant des histogrammes de gradients qui sont normalisés en angle de rotation.

Après avoir identifié un algorithme approprié pour notre application nous avons étudié les différentes techniques de traitement d'images à utiliser sur FPGA. Nous avons défini des interfaces qui peuvent être montées en cascade et qui respectent le contrôle de flux simple. En raison que les données sont en forme de flux de pixels et le fait que les FPGA sont généralement limités en termes de mémoire interne, nous pouvons diviser les opérateurs de traitement d'images en matériel en trois grandes catégories : 1) Traitement par pixel (aucune mémoire tampon nécessaire) 2) Traitement par voisinage (des blocs RAM internes peuvent être utilisés) 3) Traitement par trame d'image (une RAM externe sera nécessaire)

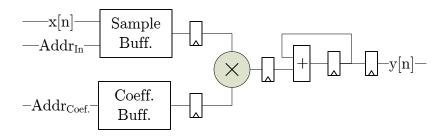

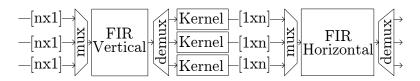

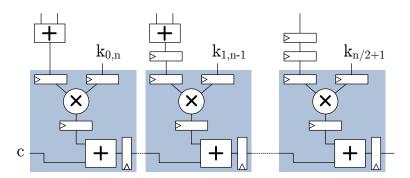

Nous avons également étudié les différentes architectures pour les filtres à réponse impulsionnelle finie qui optimisent les ressources et l'efficacité en terme de fréquence et latence.

Nous avons commencé par faire un prototype logiciel du système en question afin d'évaluer la faisabilité et la robustesse. Nous avons utilisé la librairie OpenCV de traitement d'images à cet effet. L'algorithme SIFT était lent pour des performances temps réel et donc nous l'avons combiné avec l'algorithme Lucas-Kanade de flux optique pour suivre un objet qui a été reconnu. Le principal goulot d'étranglement de l'algorithme SIFT est la partie de différence

de Gaussiennes (DoG) dont nous avions l'intention d'accélérer sur le FPGA.

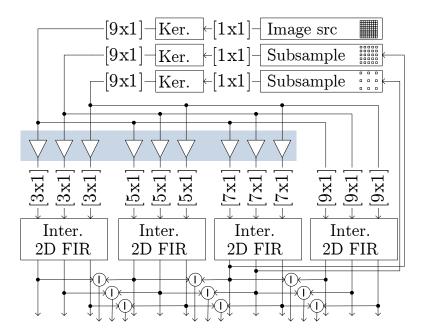

En ce qui concerne la mise en œuvre du matériel, nous avons évalué de différentes méthodes de mise en œuvre de la différence de gaussiennes et nous avons réussi à implémenter une nouvelle architecture qui utilise une technique de partage de bloc de mémoire RAM pour les opérations de voisinage ainsi que l'entrelacement des données, la séparation des filtres 2D, et l'exploitation de la symétrie du filtre afin de réduire l'utilisation des ressources par rapport à d'autres architectures dans la littérature tout en maintenant la précision.

Notre architecture est paramétrable en utilisant des génériques VHDL en termes d'échelles, des octaves, de nombres de coefficients de filtres et de largeur maximale des images.

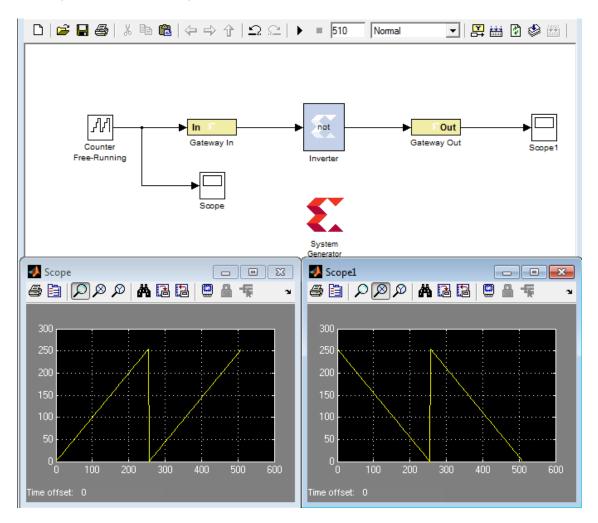

La plateforme de prototypage Xilinx ML605 a été utilisée en conjonction avec MATLAB et Xilinx System Generator. Nous avons testé notre implémentation en utilisant de la cosimulation matérielle, c'est à dire en utilisant le réseau Ethernet pour effectuer les I/O et en testant avec le matériel en boucle.

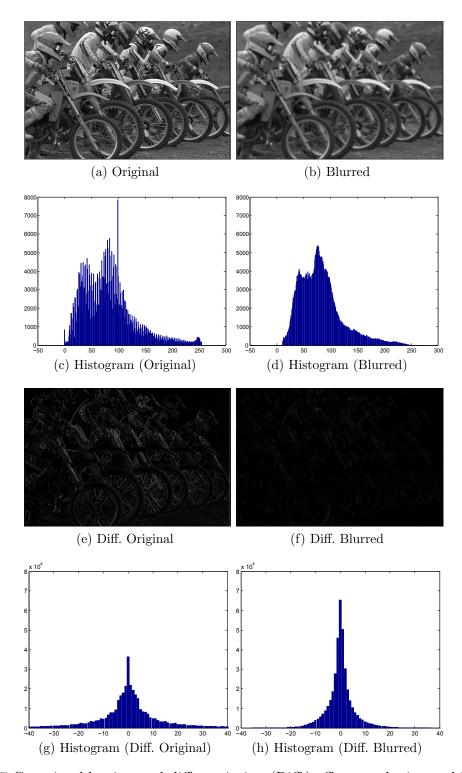

Dans de nombreux cas, la pyramide d'image ou les images doivent être transférées à l'hôte (ou mémoire externe) pour le traitement de niveau supérieur. Nous avons remarqué deux choses, tout d'abord toutes les images floues (après le filtrage Gaussien) ont tendance à avoir très peu de composantes haute fréquence dans les directions x et y. Donc l'histogramme d'une image de différence spatiale et causale aurait tendance à avoir un pic très raide autour de zéro. Ces images sont bien compressibles à l'aide d'un encodeur de Huffman.

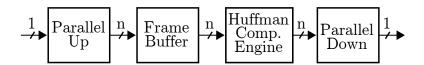

Nous avons donc proposé une architecture parallèle pour un encodeur de Huffman qui est capable de traiter plusieurs pixels en parallèle et de manière adéquate peut être utilisée pour compresser des images individuelles ainsi que des pyramides d'image complètes. Pour la compression de pyramides d'images, un prédicteur de Paeth modifié a été utilisé. Une telle méthode de compression permettrait d'atténuer les goulots d'étranglement de bande passante sans taxer l'exactitude en raison de sa nature de compression sans perte.

Une autre voie qui a été explorée concerne l'estimation de la carte phosphène. En générale, après avoir effectué la reconnaissance des objets, une représentation de cette information devra être transmise au patient. La représentation peut être évoquée par des signaux audibles, ou même comme des stimulations intra-corticales pour le cas du projet Cortivision.

Pour qu'un tel système fonctionne, on dépend sur une supposition majeure que la carte phosphène est déjà connue. Une carte approximative du cerveau où le placement physique des électrodes se traduirait par un phosphène étant éclairé spécifiquement dans le champ de vision a été présenté dans Dobelle et Mladejovsky (1974). Une telle carte est généralement plus dense vers le centre du champ de vision et il ne faut pas s'attendre à obtenir une grille parfaitement uniforme (comme une image de pixels).

Typiquement la carte phosphène peut être calculée avec l'aide du patient et ses réactions

afin de minimiser l'erreur en estimant la position des phosphènes. Notez que si la carte est déformée, la stimulation sera également déformée ce qui compliquera la reconnaissance.

## RÉSULTATS

Une implémentation paramétrable en VHDL de la différence de gaussiennes et encodeur de Huffman a été mise en œuvre sur un FPGA Xilinx Virtex-6 ML605 et testée en co-simulation de matériel dans «System Generator». L'architecture peut fonctionner à 100 MHz, émet un résultat à tous les deux cycles d'horloge (en raison de l'architecture entrelacée) et est à deux ordres de grandeur plus rapide qu'une mise en œuvre en logiciel Vedaldi et Fulkerson (2010) pour des images de  $640 \times 480$  testées sur une machine hôte (Intel Core i5@2.27 GHz, 6 Go de RAM).

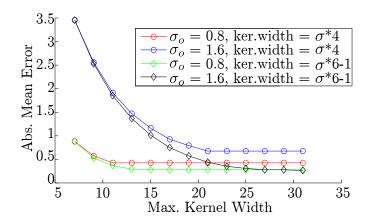

En termes de précision numérique, nous avons montré que l'architecture utilisée est comparable à un modèle de logiciel en double précision utilisant des filtres de 31-coefficients. Notez que nous pouvons réduire davantage la consommation de ressources en réduisant la précision.

L'ensemble de données d'images Caltech-256 a été utilisé pour tester les taux de compression de l'encodeur Huffman. Une table fixe Huffman a été construise en prenant 10 images d'entrainement de chaque catégorie d'objets. La même table a été utilisée pour encoder toutes les images et leurs pyramides qui sont constitués de combinaisons octaves/échelles. Les résultats de compression sans perte de 27, 3% ont été réalisés sur l'ensemble de données d'images Caltech-256.

#### Conclusion

Notre objectif principal était de traiter les images afin de «comprendre» le contenu des images et être capable de simplifier les données par le biais d'un système temps réel embarqué de reconnaissance d'objets.

Nous avons principalement contribué en introduisant une nouvelle architecture pour la différence de gaussiennes (DoG) qui partage les blocs RAM pour les opérations de voisinage afin d'utiliser les ressources FPGA efficacement tout en conservant la précision et en augmentant la vitesse de traitement de deux ordres de grandeur par rapport à une implémentation logicielle. Nous avons également fourni une méthodologie d'utiliser un prédicteur Paeth modifié combiné avec une architecture Huffman du codeur parallèle pour compresser les pyramides d'images ainsi que des images courantes permettant d'économiser de la bande passante de transmission. Par ailleurs, nous avons proposé une alternative qui peut en outre être explorée pour l'estimation carte phosphène basée sur le suivi des marqueurs repères en

utilisant des outils de traitement d'image.

Nous avons adopté l'algorithme SIFT pour la reconnaissance d'objets. L'algorithme s'est avéré être assez robuste pour gérer les variations d'image différents tels que la luminosité, le contraste, redimensionnement, de rotation et de transformations affines.

Un prototype logiciel a été implémenté comme une application multithread qui fusionne les algorithmes SIFT et Lucas-Kanade pour la reconnaissance et la poursuite d'objets. Le SIFT n'est pas capable de fonctionner en temps réel pour le traitement vidéo sur un ordinateur hôte, car il nécessite environ une seconde pour le traitement d'une seule image et à détecter un objet. Le suiveur a été utilisé pour surmonter cette limitation de suivi de l'objet reconnu en temps réel.

Après avoir identifié la différence de gaussiennes comme étant le goulot d'étranglement de l'algorithme SIFT, nous sommes passés à la migration de cette partie de la mise en œuvre d'un FPGA.

Nous nous sommes concentrés sur le codage d'une architecture hautement paramétrable qui sera en mesure de cibler les besoins des différentes applications, soit la précision par rapport aux arbitrages d'utilisation de ressources et le codage fixe de l'un des paramètres. En outre, le VHDL a été codé pour être réutilisable et portable.

En reconnaissant un traitement de flux de données, nous avons examiné les différentes techniques de traitement d'images pour les implémentations FPGA.

Afin de parvenir à une conception efficace des ressources, la mise en œuvre de notre DoG utilise des concepts tels que : pipeline, les données d'octave entrelacement, la séparabilité du filtre, la symétrie du filtre et le partage de blocs RAM pour les opérations de voisinage que nous avons introduit.

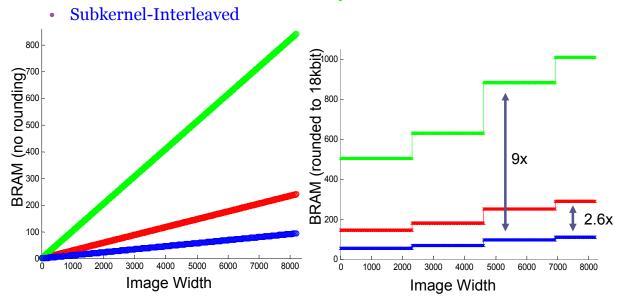

Des balayages de paramètres (largeur, nombres de coefficients de filtres, octaves, échelles) de l'architecture ont été réalisés et tracées et aussi comparés par rapport à d'autres architectures en termes d'estimation des ressources FPGA.

La mise en œuvre DoG matériel a également été démontrée d'être comparable en terme de précision à une mise en œuvre logiciel en virgule flottante.

Par ailleurs, nous avons introduit une nouvelle architecture pour un encodeur Huffman parallèle qui peut être utilisée à la fois pour pyramide d'images ainsi que la compression d'image simple. Nous avons obtenu des taux de compression sans perte de 27,3% sur l'ensemble de données d'images Caltech-256.

Nous avons également proposé une nouvelle méthodologie d'effectuer la calibration de carte de phosphènes en utilisant une installation simple qui emploie une caméra filmant une table avec des marqueurs de repère qui peuvent être manipulés par le patient qui fournira une sorte de rétroaction directe.

#### Recommandations

En raison de l'entrelacement d'octaves de données, le module de DoG est capable de traiter 1 pixel à chaque 2 cycles d'horloge. Cette limitation peut être surmontée par le traitement de plusieurs pixels à la fois, quelques-uns des modules qui sont mis en œuvre supportent déjà cette fonctionnalité.

Une autre limitation réside dans les tables de Huffman. Idéalement, le codeur de Huffman devrait être en mesure d'utiliser des tables adaptatives.

Une autre amélioration sera la possibilité de calculer la deuxième partie de l'algorithme SIFT (les vecteurs de description) sur un processeur embarqué comme ARM qui est présent dans la nouvelle famille Xilinx Zynq.

Les caractéristiques SIFT peuvent également être utilisées pour la reconnaissance de scène comme indiqué dans Lazebnik et al. (2006). Cette information peut être intégrée dans le système pour modifier la base de données qui est utilisée pour la recherche d'objet en fonction du contexte, par exemple si le patient est dans une cuisine, le système interrogera une base de données d'articles de ménage, alors que s'il est à l'extérieur, une base de données de voitures, motos et de panneaux d'arrêts pourrait être utilisée. Cela permettra de réduire le nombre de faux positifs et de comparaisons inutiles.

Enfin, la technique de cartographie phosphène peut être testée avec la rétroaction de patients pour intégrer un ensemble de modèles par exemple en utilisant des formes géométriques de base et des objets mouvants. Un émulateur peut être configuré avec des lunettes de réalité virtuelle pour modéliser le champ de vision du patient et le patient pourra manipuler les marqueurs de repères pour calibrer la carte phosphène perçue en temps réel.

# TABLE OF CONTENTS

|        | 2.3.3  | Finite Impulse Response                          | 30         |

|--------|--------|--------------------------------------------------|------------|

| СНАРТ  | TER 3  | APPROACH AND ORGANIZATION                        | 34         |

| 3.1    | Softwa | are Prototype                                    | 34         |

|        | 3.1.1  | Image Processing Libraries                       | 34         |

|        | 3.1.2  | SIFT                                             | 34         |

|        | 3.1.3  | Keypoint Matching                                | 34         |

|        | 3.1.4  | Object Localization                              | 35         |

|        | 3.1.5  | Lucas-Kanade                                     | 36         |

| 3.2    | Hardw  | rare Implementation                              | 37         |

|        | 3.2.1  | Xilinx System Generator                          | 37         |

|        | 3.2.2  | VHDL Coding                                      | 40         |

|        | 3.2.3  | Architecture Optimization                        | 41         |

|        | 3.2.4  | Huffman Encoding                                 | 44         |

| 3.3    | Phospl | hene Map Estimation                              | 46         |

| СНАРТ  | TED 1  | AN IMAGE PROCESSING SYSTEM DEDICATED TO A VISUAL |            |

| ·      |        | RTICAL STIMULATOR                                |            |

| 4.1    |        | uction                                           |            |

| 4.2    |        | ence of Gaussians                                |            |

| 4.3    |        | el Huffman Encoder                               |            |

| 1.0    | 4.3.1  | Image Differentiation                            |            |

|        | 4.3.2  | Architecture of the Proposed Encoder             |            |

| 4.4    |        | hene Map Calibration                             |            |

| 4.5    |        | ation and Experimental Results                   |            |

|        | 4.5.1  |                                                  |            |

|        | 4.5.2  | VHDL Synthesis                                   |            |

|        | 4.5.3  | Huffman Encoding                                 |            |

| 4.6    | Conclu | sion                                             |            |

| CILADO |        | CENEDAL DISCUSSION                               | <i>c</i> = |

| CHAPT  |        | GENERAL DISCUSSION                               |            |

| 5.1    |        | thm Robustness                                   |            |

| 5.2    | Hardw  | rare Implementation                              | 67         |

| СНАРТ  | TER 6  | CONCLUSION AND RECOMMENDATIONS                   | 70         |

| 6.1    | Resear | ch Synthesis                                     | 70         |

| 6.2    | Future | Recommendations                                  | 72         |

| 6.3   | Concluding Remarks |  |  |  |  | • | • | • |  |  | • |  |  |  |  |  | 72 |

|-------|--------------------|--|--|--|--|---|---|---|--|--|---|--|--|--|--|--|----|

| REFER | ENCES              |  |  |  |  |   |   |   |  |  |   |  |  |  |  |  | 74 |

# LIST OF TABLES

| Tableau 4.1 | Precision of cascaded DoG and sub-kernel DoG | 63 |

|-------------|----------------------------------------------|----|

| Tableau 4.2 | DoG Resource Usage                           | 63 |

| Tableau 4.3 | Parallel Huffman encoder resource usage      | 64 |

| Tableau 4.4 | Huffman Encoder Compression Ratio            | 66 |

# LIST OF FIGURES

| Figure 1.1  | Example of mapping a gray image onto the phosphene map                          | 2  |

|-------------|---------------------------------------------------------------------------------|----|

| Figure 1.2  | Overview of the proposed object recognition approach                            | 4  |

| Figure 2.1  | Template matching: Template (a) is swept over the search image (b)              |    |

|             | until a match is found                                                          | 6  |

| Figure 2.2  | Distortions that will cause template matching to fail                           | 9  |

| Figure 2.3  | Feature-based object recognition                                                | 10 |

| Figure 2.4  | Feature matching - Good features (green) have stable locations and are          |    |

|             | distinctive. Bad features (red) can be easily mistaken for one another          | 11 |

| Figure 2.5  | Edge features are bad since they tend to slide along the edge and are           |    |

|             | similar in nature                                                               | 12 |

| Figure 2.6  | Morphological operators applied to a binarized image. $5 \times 5$ square       |    |

|             | structuring element were used in this case                                      | 14 |

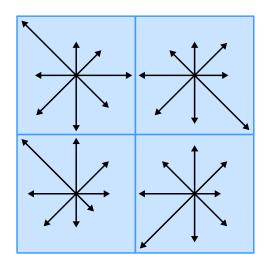

| Figure 2.7  | Morphological kernels used for corner detection : Cross; Diamond; $X$ ;         |    |

|             | Box                                                                             | 15 |

| Figure 2.8  | SIFT example : Object recognition                                               | 17 |

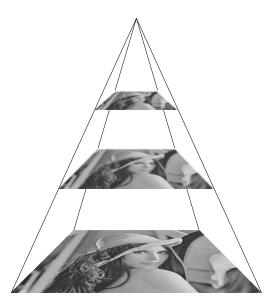

| Figure 2.9  | Image pyramid                                                                   | 18 |

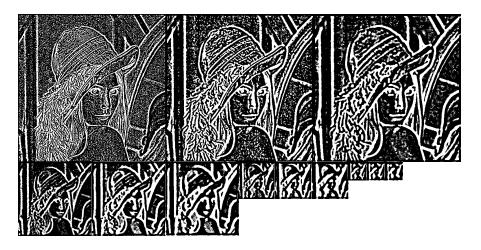

| Figure 2.10 | Gaussian Scale Space (GSS)                                                      | 18 |

| Figure 2.11 | Difference of Gaussians (DoG)                                                   | 19 |

| Figure 2.12 | SIFT descriptor. Note : The figure shows a sample $2\times 2$ grid of 8 bin     |    |

|             | histograms, whereas the actual algorithm uses a $4 \times 4$ grid               | 21 |

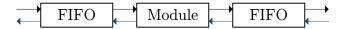

| Figure 2.13 | Module with a generic FIFO interface                                            | 23 |

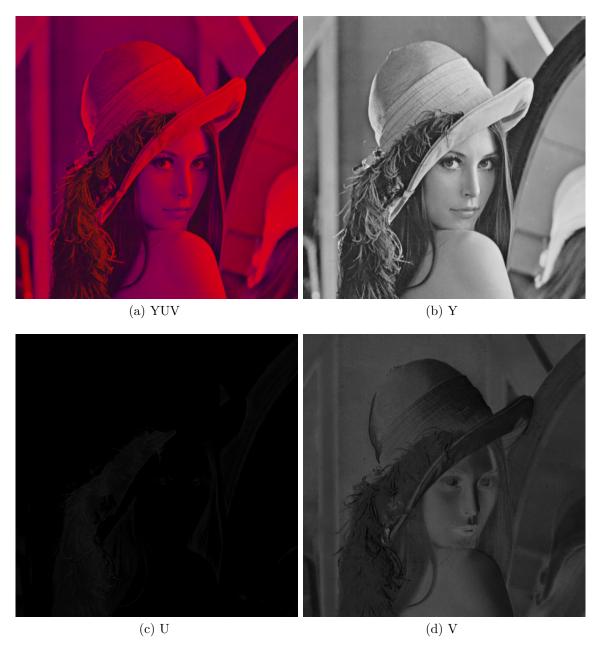

| Figure 2.14 | RGB to YUV output                                                               | 25 |

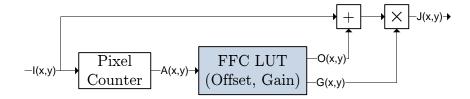

| Figure 2.15 | Flat Field Correction - Pixel-based                                             | 26 |

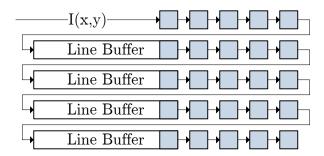

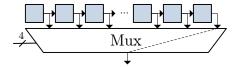

| Figure 2.16 | $[5{\times}5]$ Kernelizer. Line buffers are used to form a moving window around |    |

|             | the required pixel                                                              | 27 |

| Figure 2.17 | $\rm SRL16E$ - LUT can be configured as a shift register (maximum 16            |    |

|             | latency)                                                                        | 27 |

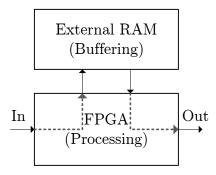

| Figure 2.18 | FPGA external RAM buffering                                                     | 28 |

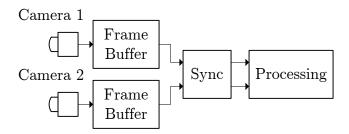

| Figure 2.19 | Multi-camera synchronization                                                    | 28 |

| Figure 2.20 | Image rotation - Backward mapping                                               | 29 |

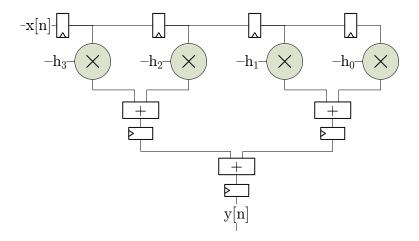

| Figure 2.21 | FIR - Direct form using an adder tree                                           | 31 |

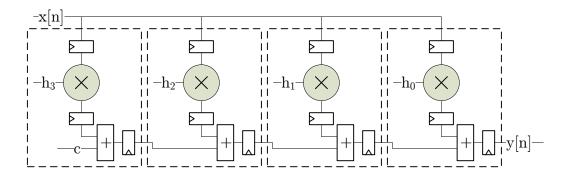

| Figure 2.22 | FIR - Transpose form                                                            | 31 |

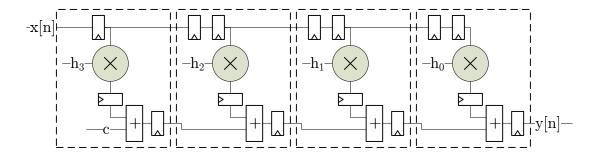

| Figure 2.23 | FIR - Systolic form                                                             | 32 |

| Figure 2.24 | FIR - Multiply Accumulate (MACC)                                            |

|-------------|-----------------------------------------------------------------------------|

| Figure 3.1  | Snapshot of the multithreaded SIFT and Lucas-Kanade tracker 37              |

| Figure 3.2  | Xilinx System Generator - Basic inverter                                    |

| Figure 3.3  | Hardware co-simulation test bench                                           |

| Figure 3.4  | $[7 \times 7]$ Kernel. $[5 \times 5]$ and $[3 \times 3]$ Sub-kernels        |

| Figure 3.5  | Cascaded approach for 2 scales                                              |

| Figure 3.6  | Sub-kernel approach for 2 scales                                            |

| Figure 3.7  | Gaussian blurring and differentiation (Diff.) effect on the image histo-    |

|             | gram                                                                        |

| Figure 3.8  | Example usage of Huffman encoder                                            |

| Figure 3.9  | Original arrow symbol (left), distorted symbol (right) due to errors in     |

|             | phosphene map estimation                                                    |

| Figure 4.1  | Overview of the Cortivision system                                          |

| Figure 4.2  | SIFT : Image Pyramid. 2 Octaves 4 Scales. Blurring at every scale and       |

|             | subsampling $(2 \times 2)$ at every octave. Notation : Gaussian Scale Space |

|             | (GSS) and Difference of Gaussians (DoG)                                     |

| Figure 4.3  | Image processing system used for object recognition and tracking 51         |

| Figure 4.4  | Interleaved DoG. (3 Octaves, 4 Scales) Notation : Kernelizer (Ker.) and     |

|             | Interleaved (Inter.)                                                        |

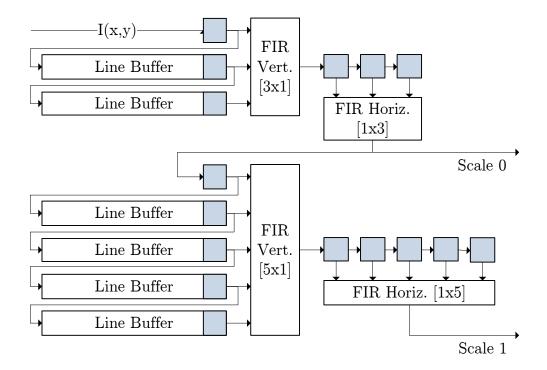

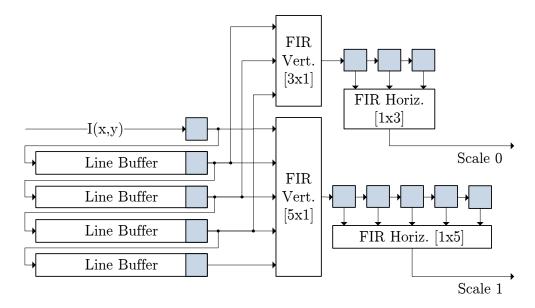

| Figure 4.5  | 2D Interleaved FIR filter. Taking advantage of the of 2D Gaussian           |

|             | separability, we save resources by performing a 1D vertical filtering       |

|             | followed by a 1D horizontal one                                             |

| Figure 4.6  | Symmetric FIR with pre-adder. Notation : Registers are indicated with       |

|             | a triangular notch                                                          |

| Figure 4.7  | Simplified Block Diagram of Parallel Huffman Encoder 57                     |

| Figure 4.8  | Barrel Shifter (a) Basic Architecture (b) Multiplier-based (Notation :      |

|             | $\gg logical \ bit \ shift)  \ldots \qquad 58$                              |

| Figure 4.9  | Parallel Huffman Barrel Shift Register                                      |

| Figure 4.10 | Set-up of the phosphene map calibration                                     |

| Figure 4.11 | DoG absolute mean error, compared to a double precision 31-tap kernel       |

|             | (for all octave/scale combinations)                                         |

| Figure 4.12 | Cascaded DoG Resource Usage – Parametric Sweep 62                           |

| Figure 4.13 | Sub-Kernel DoG Resource Usage – Parametric Sweep 64                         |

| Figure 4.14 | Compression Buffering Scheme                                                |

| Figure 4.15 | Caltech-256 samples: mars, galaxy, mussels & trilobite 65                   |

| Figure 5.1  | BRAM utilization estimate                                                   |

#### LIST OF ACRONYMS AND ABBREVIATIONS

BBF Best-Bin-First

BPP Bits per Pixel

BRAM Block Random Access Memory

BW Bandwidth

CORDIC Coordinate Rotation Digital Computer

DDR SDRAM Double Data Rate Synchronous Dynamic Random Access Memory

DEMUX Demultiplexer

DoG Difference of Gaussians

DSP Digital Signal Processing

FFC Flat Field Correction

FFT Fast Fourier Transform

FIFO First In First Out

FIR Finite Impulse Response

FOV Field of View

FPGA Field Programmable Gate Array

FPS Frames per Second

GSS Gaussian Scale Space

HSV Hue Saturation Value

HW Hardware

LK Lucas-Kanade

LoG Laplacian of Gaussians

LUT Look-Up Table

MACC Multiply Accumulate

MUX Multiplexer

PCA Principal Component Analysis

RAM Random Access Memory RANSAC Random Sample Consensus

RGB Red Green Blue

RLDRAM Reduced Latency Dynamic Random Access Memory

RLE Run Length Encoding

ROI Region of Interest

ROM Read Only Memory

SAD Sum of Absolute Differences

SIFT Scale Invariant Feature Transform

SLAM Simultaneous Localization and Mapping

SRAM Static Random Access Memory

SURF Speeded Up Robust Features

SW Software

VHDL VHSIC hardware description language

VHSIC Very-High-Speed Integrated Circuits

#### CHAPTER 1

#### INTRODUCTION

Visual impairment, defined by the full or partial loss of vision, as of today is not medically treatable. The causes of such a handicap vary widely and can range anywhere between trauma and congenital issues.

Modern bio-medical approaches are being employed to recover or stimulate vision electrically; these may be divided into three main groups: the first one targeting retinal implants Humayun et al. (2003); Kim et al. (2004); Chow et al. (2004); Palanker et al. (2005); Toledo et al. (2005); Yanai et al. (2007); Winter et al. (2007); Zrenner et al. (2011), the second optic nerve implants Veraart et al. (2003); Sakaguchi et al. (2009), and the third ones involving cortical implants Doljanu and Sawan (2007); Coulombe et al. (2007); Srivastava et al. (2007). The main drawback of the former two is that they are not generic enough to cope with most of the visual impairment diseases, since they rely on the patient having an intact optic nerve and/or a partially operational retina. This is not the case for the third. Other non-invasive methods that may involve stimulation by sound are also being used, but these are not well agreed upon to fit in the same scope.

#### 1.1 Theoretical Framework

The *Polystim Neurotechnologies* team is currently working on an intra-cortical implant that directly stimulates the primary visual cortex (V1 region); the global project name is *Cortivision*. The process uses a front-end camera, an image processing module, an RF (Radio Frequency) link, and an implantable stimulator for the purpose; this method is robust and generic since it bypasses the eye and optic nerve. One of the major challenges is the image processing required to "simplify" the data prior to stimulation, extracting all of the useful information and discarding the superfluous data. The pixels that are being captured by the camera do not have a one-to-one mapping on to the visual cortex as in a rectangular image; they are rather mapped into a complicated map of "phosphenes" Coulombe *et al.* (2007); Srivastava *et al.* (2007) which are bright dots that are perceived by the patients when the brain is electrically stimulated. These dots change in size, illumination, and location depending on how the electrical stimulation is performed (i.e. a change in frequency, voltage, duration, etc...) and even by the electrode placement in the cortex.

Current approaches aim at stimulating low-resolution grayscale phosphene images. Knowing

that, we would expect a rather low-quality vision making it hard for the patient to navigate, interpret objects, or even read. This is mainly due to the complexity of the phosphene mapping and also to the non-triviality of knowing how to simplify the data in the captured images in such a way that only relevant data is kept.

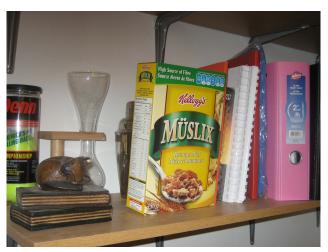

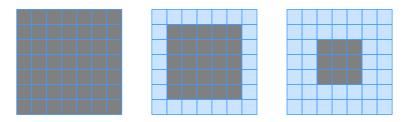

Figure 1.1 is an example that shows the complexity of illustrating a captured input video stream onto a pre-calibrated phosphine map. The input image is shown on the left, the middle image shows the available phosphene map (this is what the subject would be "seeing" in case we showing a stimulating a white image or a white wall), and the leftmost image shows the mapping of the gray image onto the available phosphenes using the local gray value.

Figure 1.1 Example of mapping a gray image onto the phosphene map

Edge detectors, segmentation, and stereo vision approaches have been proposed in the literature as a way of reducing information prior to stimulation. A stereo vision module has been implemented in Cortivision; the output of such a module is a disparity map in which close surfaces are indicated by a brighter intensity (or gray value) than ones that are further away (black). The main drawbacks of this module is that it uses an infrared-light pattern projector and a camera to achieve its purpose, which may be cumbersome, and the actual output may not be meaningful enough by itself for the patient to interpret, which is why we plan to add a degree of processing upon that.

The concept of augmented reality has recently been introduced and is proving to be quite appealing. It is a field of computer research which deals with blending real-world data with computer-generated data in real-time; a common example is using special projective eyeglasses to overlay text on the real-world (this could indicate shopping malls, object dimensions, etc...). Some medical applications intended for visual impairment Toledo *et al.* (2005) have relied on that concept being implemented on Field Programmable Gate Arrays

(FPGAs); such approaches are used in retinal implants where the patient still has some partial vision.

We would be investigating the use of such a system in terms of high-speed image processing modules and techniques that can be hardware implementable on FPGAs and or a mix of hardware/software processing to attain real-time performance. Such techniques would be targeted to provide a simplified and interactive environment for the patient.

### 1.2 Research Question

How to come up with a parameterizable and reusable system that can process, simplify, and present the captured image stream in real-time in order to provide a more useful mapping prior to stimulation?

## 1.3 Hypothesis

- Hypothesis: The phosphene map is not accurate enough, hence the use of a real-time object recognition system is required to simplify the environment for visually impaired patients and lead to better navigation and recognition abilities.

- Justification of originality: Augmented reality systems are quite recent in the literature, and are usually overlaid over a person's natural vision system (being handicapped or not), but in this case it overrides the actual vision and is interacting directly with the visual cortex to provide better context awareness. Moreover, previous visual impairment systems rely on simple image processing tasks rather than recognition to convey information to the patient.

- Refutability: The hypothesis would be refuted if the system cannot operate in real-time or is not robust enough to varying conditions.

#### 1.4 Research Goals

The research goals would be to improve the quality or methodology used for perception by means of real-time image processing techniques accelerated on parallelizable hardware (FPGA), hence providing an augmented reality in which specific objects can be localized and/or recognized and then passed on to the patient.

The system should be parameterizable and possibly platform-independent in order to be efficiently reusable. Moreover, the FPGA implementation should be resource-efficient in case it needs to be mapped on to smaller devices.

### 1.5 Objectives

- Identify and develop a robust and parallelizable software algorithm that can perform localization and recognition on a limited number of objects on which it was trained; these are expected to vary in pose and illumination.

- Accelerate the algorithm's bottlenecks using hardware (FPGA) modules to be able to achieve real-time performance. These modules should be generic enough to be reusable (can be easily transferred to a different platform) and parameterizable while being as efficient as possible on both resource and bandwidth utilization.

- Validate the hardware modules' accuracy as compared to a software equivalent implementation.

- Investigate possible methods for estimating the phosphene map.

Figure 1.2 Overview of the proposed object recognition approach

Figure 1.2 shows an overview and the intended roadmap that we will be following throughout the text. The details of the different parts will explained in the chapters to come.

Basically we would be using the Scale Invariant Feature Transform (SIFT) to extract and describe keypoints. The first part of SIFT (being computationally expensive) will be accelerated in an FPGA using a novel architecture to save resources. An object database of keypoints is kept and compared to the incoming frames, and whenever enough keypoints are matched, an object is recognized and afterwards an appropriate stimulation image can be sent to the electrode matrices. A Huffman encoder is to be used to reduce HW/SW transmission bottlenecks and also a new setup for calibrating the phosphene map is proposed.

In what follows we will be investigating different image processing techniques that can be used for the purpose of our application. After having identifying a suitable algorithm and validating it in software, we will accelerate the computationally intensive parts using reconfigurable hardware in order to be able to support real-time operation. While doing so, we propose a novel architecture for sharing and saving hardware resources. Moreover, the architecture, as will be seen in throughout the document, will be coded in a highly parameterizable fashion in order to be reusable and portable. An architecture for a hardware Huffman encoder is also proposed that can treat pixels in parallel and can be used for data reduction. Finally, we suggest a viable setup for phosphene map estimation that makes use of fiducial markers and image processing techniques as an alternative to the current tactile screen approaches.

A literature review is covered in Chapter 2, followed by the overall approach that was used in Chapter 3, the journal article entitled "An Image Processing System Dedicated to a Visual Intra-Cortical Stimulator" in Chapter 4, a general discussion in Chapter 5, and we will then conclude and discuss future improvements in Chapter 6.

#### CHAPTER 2

#### LITERATURE REVIEW

This chapter provides an overview of image processing approaches and algorithms that can be used for the purpose of object recognition; Moreover we will also review how FPGAs are used in an image processing context by applying certain design rules and differentiating between the various processing functions.

## 2.1 Template Matching

Template matching is one of the basic image processing methods used to determine if an object (or rather a specific template) is found in an input image. The template is typically smaller than the target image, and the purpose would be to determine the bounding box of the object in question. In terms of training, this method requires an exact template of the image to be pre-collected such as the one shown in Figure 2.1a and to be matched in a larger image as indicated with the green rectangle in Figure 2.1b.

Figure 2.1 Template matching: Template (a) is swept over the search image (b) until a match is found.

In essence, template matching works by sliding a template T in a raster scan order (top-left to bottom-right) over the input image I and calculating a correlation factor or matching

score to determine whether we have a positive match.

NOTE: in terms of image processing terminology, correlation and convolution are typically used interchangeably.

In what follows, we will go over the border handling techniques, the various scores of template matching and the advantages and disadvantages of this method.

#### 2.1.1 Border Handling

Assuming that the template and target images have the respective dimensions (Width\*Height) of M\*N and W\*H. Obviously, we will encounter the issue of border errors where the template would actually surpass the image boundary. For that, either the template will only be scanned *inside* the input image and the resulting "match image" would have smaller dimensions than the original, or the input image would have to be border padded, resulting in an input image of dimensions (W+M-1)\*(H+N-1). Border handling would be performed in one of the following fashions:

- Zero padding: the border would simply be padded with zeros.

- Constant padding: a constant value (e.g. 128) would be used for the borders.

- Border replication : The edge pixel is replicated for the whole border.

- Mirroring: The image borders would be a mirrored version of the input image. This

technique tends to minimize the artifacts in convolution operators and will work well

for symmetric templates.

NOTE: These border handling techniques are also used in any image processing convolution operations (e.g. Gaussian blurring) as will be seen later on in Section 2.2.2.

## 2.1.2 Matching Scores

In order to determine a positive match, a certain match score or result image R has to be calculated; afterwards a threshold is chosen to detect a match. Various ways of calculating a matching score have been proposed in the literature Brunelli (2009), Bradski and Kaehler (2008); these can be summarized as follows.

#### Squared Difference

Assuming that T is the template and I is the search image; the simplest of the methods would be to calculate the sum of squared differences

$$R(x,y) = \sum_{x'} \sum_{y'} \left[ T(x',y') - I(x+x',y+y') \right]^2$$

(2.1)

or the sum of absolute differences (SAD)

$$R(x,y) = \sum_{x'} \sum_{y'} |T(x',y') - I(x+x',y+y')|$$

(2.2)

a lower match score (closer to zero) would actually indicate a better match.

#### Correlation

Alternatively, correlation can be used as the match measure

$$R(x,y) = \sum_{x'} \sum_{y'} T(x',y') * I(x+x',y+y')$$

(2.3)

A higher score in this case would indicate a better match. It should be noted that this method would prove to be sensitive to white areas in the image which would result in false positives.

#### Normalized Correlation

By normalizing the previous method, we end up with what is known as the normalized correlation

$$R_n(x,y) = \frac{\sum_{x'} \sum_{y'} T(x',y') * I(x+x',y+y')}{\sqrt{\sum_{x'} \sum_{y'} T(x',y')^2 * \sum_{x'} \sum_{y'} I(x+x',y+y')^2}}$$

(2.4)

The normalization step alleviates the issues where there is a mismatch in illumination between the template and the input search image and even the false matches that could result from white patches. This improvement definitely comes at the high computational cost.

#### 2.1.3 Advantages/Disadvantages

Template matching is one of the straight forward methods used for object detection. Its main advantage would lie in the algorithmic simplicity of the method, which works a bit as a brute force approach. But, while it might prove to be useful for applications in controlled environments (e.g. machine vision and inspection Crispin and Rankov (2007)), it has many draw backs in real life situations, mainly the ones cited below:

- Illumination dependency: If the template brightness is different from the search image's one, a good match might not be trivial to attain.

- Illumination gradients: While the normalization process can be used to target the previously mentioned problem, a gradient illumination (see Figure 2.2a) would probably fail.

- Calculation complexity: As would be clear from the matching equations, the calculation time is directly dependent on the template's size.

- Affine transformations: Scaling, rotating, and/or skewing the target object in the search image would cause this method to fail, since it does not account in any way for any affine transforms or distortions (see Figure 2.2b).

- Occlusions/partial matches: The template is expected not be occluded and to have more or less a perfect match over the whole area of the template for proper matching.

- Threshold choice: Choosing the appropriate threshold might prove to be a bit tricky when one is trying to accommodate the system for different operating environments.

(a) Artificial Lighting Gradient

(b) Distorted Template

Figure 2.2 Distortions that will cause template matching to fail.

#### 2.2 Feature-Based Methods

Feature-based methods for object detection have peaked in the literature such as the ones found in Lowe (2004), Bay et al. (2008), Mikolajczyk and Schmid (2005), Bosch et al. (2007), Dalal and Triggs (2005). Applications for such methods include object detection Lowe (2004), Lowe (2001), Lowe (1999), Bay et al. (2008), Bay et al. (2006), image mosaicing Brown and Lowe (2003), Simultaneous Mapping and Localization (SLAM) Montemerlo et al. (2002) Castle et al. (2010) and even scene classification Lazebnik et al. (2006). Note that we will be using the terms feature and keypoint interchangeably to describe an interesting point in the image.

Feature-based methods differ from basic template matching ones in that a subset of patches (or features) taken around "interesting" points (or keypoints) in the image would be used to determine matches. A caricaturized description of these approaches is shown in Figure 2.3.

Figure 2.3 Feature-based object recognition.

Instead of using a reference image as a template, we extract *interesting* patches from a training image of an object for example and find matches of that same object in a different image (or video stream). As will be seen later on, such an approach will remove many of the previously mentioned limitations found in template matching.

These algorithms can be divided into two main stages: keypoint localization (or extraction) and feature description. At the keypoint localization stage, we mainly try to extract

salient and "interesting" points in the image (in order to later on describe the patches surrounding these points). Keypoints can be thought of as edges, corners, or even scale invariant points.

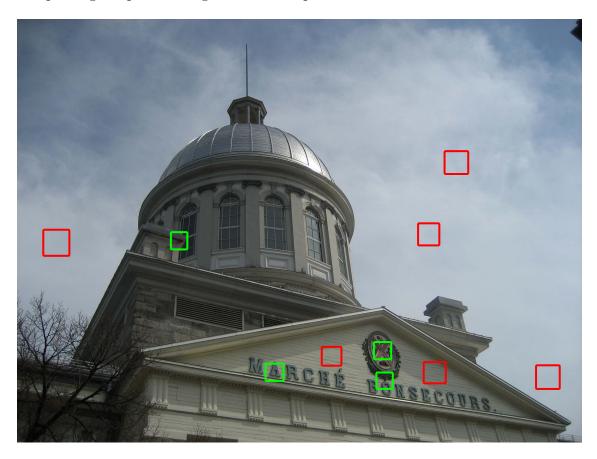

As previously discussed in template matching, one could choose patches to be matched from one image to another; a training image or set of images can be used for that purpose. The problem with that approach is that some patches are more salient, or contain more distinctive information, and thus can be matched more easily than others. Figure 2.4 shows an example of good patches in green and bad patches in red.

Figure 2.4 Feature matching - Good features (green) have stable locations and are distinctive. Bad features (red) can be easily mistaken for one another.

The red patches are not stable and are very similar in nature hence causing them to be very easily mistaken for one another.

The matching procedure naturally assume a certain amount of resemblance in between the images to be compared. From a first observation one could notice that if we sample patches around corner points, these would tend to be more distinctive or uniquely identifiable.

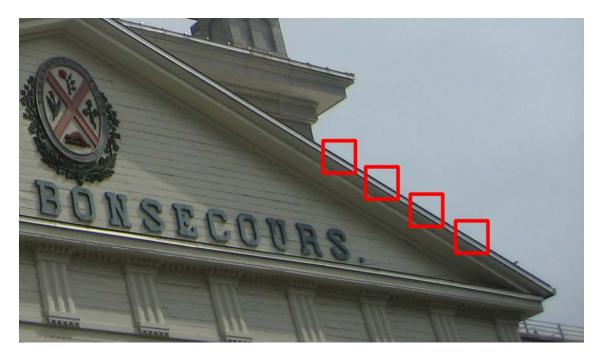

In terms of a mathematical definition, weak features, that cannot be easily matched, have

a low variance like a plain wall for example. One may then argue that edges may form good candidates. Looking at Figure 2.5, we can see, that even though edges do have significant variance, they tend to have it in a single direction (e.g. in the x-direction). This causes what is known as the aperture problem Todorovic (1996). The net result is that the motion vector of the feature would be ambiguous, and if we slide along the edge we may find many similar patches.

Figure 2.5 Edge features are bad since they tend to slide along the edge and are similar in nature.

Corners, on the other hand, would make for good features since, these have variations in all directions and hence will be relatively stable and can be extracted robustly.

### 2.2.1 Corner Detectors

Feature based methods depend on corner or interest point extraction. Corners may have different mathematical definitions and some may be more robust in terms of rotation, scaling, affine transformations, and even determining textured or blob regions.

#### Harris Corner Detector

The Harris corner detector Harris and Stephens (1988) is one the most commonly noted methods for extracting corners in literature. In a nutshell it attempts to find windows around a point in the image that when translated slightly produces a large difference. The window has to be moved in both the x, and y directions. From a mathematical perspective, the boils down to calculating the autocorrelation matrix of the second derivatives of the image as shown in the equation below:

$$M(x,y) = \begin{bmatrix} \sum_{-K \le i,j \le K} w_{i,j} I_x^2(u,v) & \sum_{-K \le i,j \le K} w_{i,j} I_x(u,v) I_y(u,v) \\ \sum_{-K \le i,j \le K} w_{i,j} I_x(u,v) I_y(u,v) & \sum_{-K \le i,j \le K} w_{i,j} I_y^2(u,v) \end{bmatrix}$$

(2.5)

Note that u = x + i and v = y + j. The window size is defined using the K parameter.  $I_x$  and  $I_y$  respectively indicate the image derivatives in the x and y directions. A weighting window, typically a Gaussian one or a uniform one, can be applied to the equation using the  $w_{i,j}$  term. The second derivative terms do not respond to uniform gradient changes and hence when the eigenvalues of the above matrix are considered, we end up with a quantitative signature value that is invariant to rotations Bradski and Kaehler (2008).

A cornerness score R can be calculated using the determinant and trace value of the M matrix, to determine whether a certain point qualifies as corner point.

$$R = det(M) - \alpha * trace(M)^2$$

(2.6)

$\alpha$  in this case is a weighting factor and the score can then be compared to a fixed threshold value.

### Shi-Tomasi

Shi and Tomasi presented a slight variation to the Harris corner detector which improved the performance and robustness of the method. Their method involved comparing the smaller eigenvalue to a fixed threshold, and it was proven to be enough to determine corners Shi and Tomasi (1994).

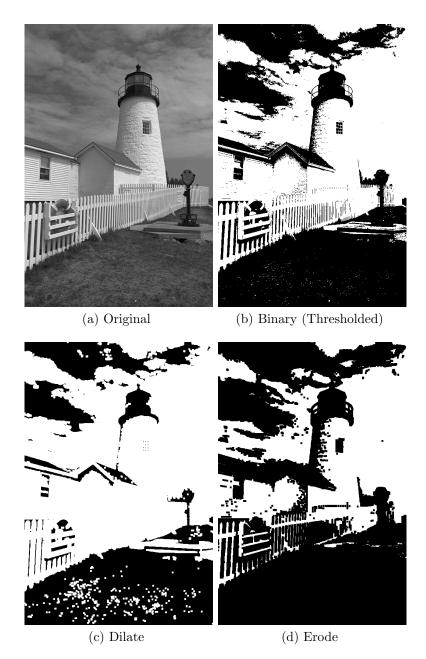

# Morphological Corner Detection

Image morphology, whether in a grayscale or binarized context, can also provide an appealing approach to corner detection. These operators depend on the brightness level and are typically computationally simpler in nature as compared to the other methods while still being robust to noise Laganière (2011). Image morphology is typically formed of combinations of dilate (or maximum) and erode (or minimum) operations operating with pre-define mask structure or structuring element. Figure 2.6 shows erode and dilate operations being performed on binarized image.

Sequential combinations of these operators can be used to perform morphological close

Figure 2.6 Morphological operators applied to a binarized image.  $5 \times 5$  square structuring element were used in this case.

(dilate followed by erode) and open (erode followed by dilate). For the purpose of corner detection asymmetrical closing morphological elements Laganière (1998) are used like the ones shown in Figure 2.7.

The cornerness measure in this case would be calculated as such:

$$R = |I_{\text{cross,diamond}}^c - I_{\times,\text{box}}^c| \tag{2.7}$$

Figure 2.7 Morphological kernels used for corner detection: Cross; Diamond; X; Box.

where  $I^c$  denotes a morphological close operation. Afterwards, the cornerness can be simply compared to a fixed threshold Laganière (2011). Note that sometimes this may lead to multiple pixel responses, not just a single corner location, hence non maxima suppression can be applied to avoid such conditions.

### **Multi-Scale Detectors**

It is to be noted that the Harris detector is not scale invariant; for that a multi-scale Harris detector is also found in the literature Lindeberg (1998). Instead of operating on a single image scale, the image is repetitively blurred to form a scale-space and the cornerness score is now compared with the finer and coarser scales. A corner would thus be an extremum.

Similar approaches, such as the Difference of Gaussians (DoG) that was used in the Scale Invariant Feature Transform (SIFT), are scale invariant and will be discussed in Section 4.2. In depth reviews and comparisons of such interest point detectors were performed in Mikolajczyk and Schmid (2005) Mikolajczyk and Schmid (2004).

### 2.2.2 Scale Invariant Feature Transform

Corner detectors, on their own, may be good enough to match features or keypoints across images with minor movements, for example for tracking purposes. But for the requirement of matching features or even whole objects in images with varying illumination, scale, and rotation, corner detectors alone fall short and hence feature-based method such as the Scale Invariant Feature Transform (SIFT) Lowe (2004) come into play; These add a feature description or signature than enhances the matching and distinctiveness of features.

The SIFT algorithm is appealing to us since is it quite robust and able to match features with variations in scale, rotation, illumination, and even partial viewpoint changes that can be characterized as affine transformations. Moreover the features are distinctive enough that any given one can be matched against a large database, making it ideal for applications such as object detection, scene classification, and image registration.

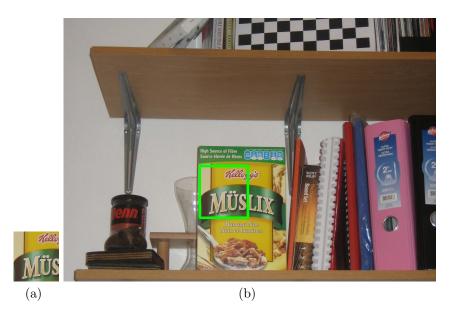

An example of SIFT being used for an object recognition application is shown in Figure 2.8. The incoming video stream SIFT features are calculated by extracting "interesting"

keypoints and then describing the "patches" around these keypoints. Afterwards we try to match know objects from our database with the incoming keypoints. For the matching stage, a best-bin first (which is similar to a nearest neighbor search) is performed. The actual recognition stage is done by the use of RANSAC which would eliminate false matches which are considered as noise. In Figure 2.8 the purple lines and indicate correct matches whereas the red line shows an incorrect match. The final output would be able to estimate the pose of the object in the incoming video stream (shown as the blue rectangle).

The method can be divided into two major parts:

- Keypoint extraction: This part is comparable to a multi-scale corner extraction (or blob extraction).

- Keypoint description: Patches around a keypoint are chosen and characterized to be used as the patch signature.

Note that such algorithms tend to be computationally complex in nature due to the shear amount of data required to be processed. On the other hand, some parts of the algorithm are parallelizable and we will taking advantage of that as will be seen later on.

### Keypoint Extraction

The keypoint extraction part can further be divided into smaller stages:

- Gaussian scale space (GSS)

- Difference of Gaussians (DoG)

- Keypoint localization

- Keypoint refinement

### Gaussian Scale Space

Image pyramids as shown in Figure 2.9 are a common practice in the image processing world Adelson *et al.* (1984) (image pyramid some history) and are typically used to model scale variations. The image is progressively blurred to generate *scales* and then subsampled to form a new *octave*.

The 2D Gaussian filter has the following form:

$$G(x,y) = \frac{1}{\sqrt{2\pi\sigma^2}} e^{-\left[\frac{x^2 + y^2}{2\sigma^2}\right]}$$

(2.8)