| <b>Titre:</b><br>Title: | Low-Impact Operating System Tracing                                                                                                                                        |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Mathieu Desnoyers                                                                                                                                                          |

| Date:                   | 2009                                                                                                                                                                       |

| Туре:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                  |

| Référence:<br>Citation: | Desnoyers, M. (2009). Low-Impact Operating System Tracing [Thèse de doctorat,<br>École Polytechnique de Montréal]. PolyPublie. <u>https://publications.polymtl.ca/206/</u> |

# **Document en libre accès dans PolyPublie** Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/206/ |

|------------------------------------------|--------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Michel Dagenais                      |

| Programme:<br>Program:                   | Génie informatique                   |

UNIVERSITÉ DE MONTRÉAL

### LOW-IMPACT OPERATING SYSTEM TRACING

### MATHIEU DESNOYERS DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

### THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE PHILOSOPHIÆ DOCTOR (Ph.D.) (GÉNIE INFORMATIQUE) DÉCEMBRE 2009

© Mathieu Desnoyers, 2009.

### UNIVERSITÉ DE MONTRÉAL

### ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée :

#### LOW-IMPACT OPERATING SYSTEM TRACING

présentée par : <u>DESNOYERS Mathieu</u> en vue de l'obtention du diplôme de : <u>Philosophiæ Doctor</u> a été dûment acceptée par le jury constitué de :

Mme. BOUCHENEB Hanifa, Doctorat, présidente

M. DAGENAIS Michel, Ph.D., membre et directeur de recherche

- M. BOYER François-Raymond, Ph.D., membre

- M. STUMM Michael, Ph.D., membre

I dedicate this thesis to my family, to my friends, who help me keeping balance between the joy of sharing my work, my quest for knowledge and life.

Je dédie cette thèse à ma famille, à mes amis, qui m'aident à conserver l'équilibre entre la joie de partager mon travail, ma quête de connaissance et la vie.

### Acknowledgements

I would like to thank Michel Dagenais, my advisor, for believing in my potential and letting me explore the field of operating systems since the beginning of my undergraduate studies.

I would also like to thank my mentors, Robert Wisniewski from IBM Research and Martin Bligh, from Google, who have been guiding me through the internships I have done in the industry. I keep a good memory of these experiences and am honored to have worked with them.

A special thanks to Paul E. McKenney, who I found has an insatiable curiosity and never-ending will to teach, discuss and learn. I really enjoyed working with him on the user-space RCU implementations.

Thanks to my family, Normand, Hélène and Alexandre for their support through the duration of this research. A special thanks to my friend Etienne Bergeron, who helped me making this thesis better with his thorough reviews and relevant criticism. Thanks to everyone who reviewed this thesis: Nicolas Gorse and Matthew Khouzam. Thanks to the students with whom I shared the laboratory for the discussions, always useful to explore the many faces of a problem. Thanks to the Montréal Art Café staff for feeding the writing of this thesis with their joviality and excellent Café Moka.

Thanks to Google, IBM Research, Ericsson, Autodesk, Natural Sciences and Engineering Research Council of Canada and Defence Research and Development Canada for funding this research.

Thanks to the countless industry collaborators at Fujitsu, Wind River, Nokia, Siemens, Novell and Monta Vista. Thanks to the SystemTAP team for their collaboration, especially to Frank Ch. Eigler.

Finally, I would like to thank the Linux kernel developers community for their constructive criticism and their input. Special thanks to Ingo Molnar, Steven Rostedt, Andrew Morton, Linus Torvalds, Christoph Hellwig, Christoph Lameter, H. Peter Anvin, Rusty Russell, Andi Kleen, Tim Bird, Kosaki Motohiro, Lai Jiangshan, Peter Zijlstra and James Bottomley. I would not have developed such a thorough knowledge of operating systems without all these heated discussions on the Linux Kernel Mailing list.

## Abstract

Computer systems, both at the hardware and software-levels, are becoming increasingly complex. In the case of Linux, used in a large range of applications, from small embedded devices to high-end servers, the size of the operating system kernels increases, libraries are added, and major software redesign is required to benefit from multi-core architectures, which are found everywhere. As a result, the software development industry and individual developers are facing problems which resolution requires to understand the interaction between applications and all components of an operating system.

In this thesis, we propose the LTTng (*Linux Trace Toolkit next generation*) tracer as an answer to the industry and open source community tracing needs. The lowintrusiveness of the tracer is a key aspect to its usefulness, because we need to be able to reproduce, under tracing, problems occurring in normal conditions. In some cases, users leave tracers active at all times in production, which makes the tracer overhead definitely critical. Our approach involves the design of synchronization primitives that meet the low-impact requirements. The linearly scalable and wait-free RCU (*Read-Copy Update*) synchronization mechanism used by the LTTng tracer fulfills these requirements with respect to data read. A custom-made buffer synchronization scheme is proposed to extract tracing data while preserving linear scalability and wait-free characteristics.

By measuring the LTTng impact, we demonstrate that it is possible to create a tracer that satisfy all the following characteristics: low latency, deterministic realtime impact (wait-free), small impact on operating system throughput and linear scalability with the number of cores. Experiments on various architectures show that this tracer is portable.

We propose a general model for superscalar multi-core systems with weaklyordered memory accesses to perform formal verification of the RCU correctness and wait-free guarantees by model-checking. The LTTng buffering scheme is also formally verified for safety and progress. Formal verification demonstrates that these algorithms allow reentrancy from multiple execution contexts, ranging from standard thread to non-maskable interrupts handlers, allowing a wide instrumentation coverage of the operating system.

## Résumé

Les systèmes informatiques, tant au niveau matériel que logiciel, deviennent de plus en plus complexes. En ce qui concerne Linux, système d'exploitation utilisé dans une vaste catégorie d'applications, des petits systèmes embarqués aux serveurs de haut-niveau, la taille des noyaux de systèmes d'exploitations augmente, des librairies sont ajoutées et une réingénierie logicielle est requise pour bénéficier des architectures multi-cœurs, lesquelles sont omniprésentes. Par conséquent, l'industrie du développement logiciel et les développeurs individuels font face à des problèmes dont la résolution nécessite de comprendre l'interaction entre les applications et tous les composants d'un système d'exploitation.

Dans cette thèse, nous proposons le traceur LTTng (*Linux Trace Toolkit next generation*) comme réponse aux besoins de traçage de l'industrie et de la communauté du logiciel libre. La faible intrusivité du traceur est un aspect clé menant à son utilisabilité, puisqu'il est nécessaire de reproduire, sous traçage, des problèmes observés sous des conditions d'exécution normales. Dans certains cas, les usagers souhaitent laisser des traceurs actifs en tout temps sur des systèmes en production, ce qui rend l'impact en performance définitivement critique. Notre approche implique l'élaboration de primitives de synchronisation qui rencontrent les requis de faible impact. Le mécanisme de synchronisation permettant la mise à l'échelle et sans attente RCU (*Read-Copy Update*) utilisé par le traceur LTTng remplit ces requis en ce qui concerne la lecture de données. Nous proposons un mécanisme de synchronisation pour extraire les données de traçage en préservant les caractéristiques de mise à l'échelle linéaire et de non-attente.

En mesurant l'impact du traceur LTTng, nous démontrons qu'il est possible de créer un traceur qui satisfait toutes les caractéristiques suivantes : faible latence, comportement temps-réel déterministe (sans attente), faible impact sur le débit du système d'exploitation et une mise à l'échelle linéaire par rapport au nombre de processeurs. Une expérimentation sur plusieurs architectures permet d'observer la portabilité du traceur.

Nous proposons un modèle général pour les systèmes superscalaires multi-cœurs avec accès mémoire faiblement ordonnés pour permettre la vérification formelle des garanties quant à l'exactitude de l'exécution et l'exécution sans attente à l'aide de la vérification de modèle. Le mécanisme de tampon de LTTng est également vérifié formellement quant à son exactitude et son exécution sans attente. La vérification formelle permet également de démontrer que ces algorithmes permettent la réentrance de plusieurs contextes d'exécution, du fil d'exécution standard aux gestionnaires d'interruptions non-masquables, permettant une large couverture d'instrumentation du système d'exploitation.

### Condensé en français

La croissance en complexité des systèmes informatiques actuels rend les tâches de déverminage et l'analyse de performance de plus en plus difficiles. Le besoin en outils d'analyse qui tiennent compte de l'ensemble du système se fait sentir, mais leur impact en performance est généralement un obstacle à leur adoption.

Le traçage est une technique éprouvée pour permettre l'étude des interactions entre composants d'un système informatique, mais son impact en performance le rend inutilisable sous plusieurs charges de calcul. Cette recherche tente de rendre le traçage largement utilisable par une vaste catégorie d'applications.

Il importe également pour un traceur de modifier le comportement du système observé de façon minimale afin de permettre la reproductibilité des problèmes observés sans traçage. Il est également important que le traceur n'utilise qu'une fraction des ressources du système et ne modifie son comportement que de façon déterministe afin de permettre une activation du traçage sur des systèmes en production.

Le problème étudié dans ce travail est l'extraction d'information de traçage d'un système d'exploitation, ce qui implique la collecte d'information à partir de l'exécution de ce système d'exploitation et le transfert de cette information hors du noyau. Les aspects de ce problème qui rendent cette étude intéressante sont l'impact du traceur sur le fonctionnement du système et la couverture d'instrumentation : quelles parties du système peuvent êtres instrumentées.

L'hypothèse servant de point de départ à cette étude est qu'il est possible de tracer un système d'exploitation qui exécute une charge de travail élevée sur des ordinateurs multiprocesseurs, en n'utilisant qu'une petite fraction des ressources systèmes, tout en permettant l'instrumentation de n'importe quel site noyau ou usager, rendant ainsi possible la modélisation du comportement original du système. Ceci implique l'utilisation d'une fraction du débit du système ainsi qu'un ajout d'une faible quantité à sa latence moyenne. La conservation des propriétés suivantes du système d'exploitation est recherchée : mise à l'échelle, réponse temps-réel, portabilité et réentrance.

Le but de cette étude est la création d'un traceur à faible impact, hautement réentrant et permettant la mise à l'échelle, pour le noyau d'un système d'exploitation largement utilisé : Linux. Cette infrastructure doit être capable de gérer un débit de traçage généré par des charges de travail élevées sur des systèmes multiprocesseurs. Celui-ci doit préserver, ou modifier dans une faible proportion, les caractéristiques du noyau Linux.

Les objectifs de recherche sont les suivants :

- rencontrer les requis de traçage de l'industrie et de la communauté du logiciel libre,

- mettre au point de nouveaux algorithmes pour solutionner les problèmes de l'industrie identifiés,

- implanter un traceur pour Linux, un système d'exploitation largement utilisé,

- développer chaque composant du traceur afin que leur combinaison conserve les propriétés de mise à l'échelle et ait un faible impact sur le débit et la latence moyenne du système d'exploitation,

- garantir un impact temp-réel déterministe du traçage,

- obtenir des mécanismes de traçage ayant une portabilité et réentrance accrues.

La contribution scientifique principale de cette recherche est la création de mécanismes de synchronisation adaptés au traçage, incluant : un algorithme de synchronisation de tampons sans attente, pouvant être mis à l'échelle de manière linéaire et supportant les NMIs (*interruptions non-masquables*), l'application de techniques d'auto-modification de code pour gérer l'activation d'instrumentation statique de manière efficace, l'amélioration des mécanismes de synchronisation RCU en espace usager et la création d'un modèle d'architecture générique pour la vérification formelle d'algorithmes parallèles, modélisant les accès mémoire et l'ordonnancement d'instructions faiblement ordonnés. Ces contributions permettent l'atteinte des objectifs de recherche identifiés.

La méthodologie utilisée pour répondre à ces objectifs se détaille comme suit. Une interaction avec l'industrie et la communauté du logiciel libre permet initialement d'obtenir plus d'information sur le contexte d'utilisation typique et les besoins perçus en entreprise. Des stages chez IBM Research, Google, ainsi qu'une collaboration avec Autodesk et Ericsson, ont permis de mieux comprendre ces besoins. En parallèle avec cette étude de terrain, des prototypes du traceur sont réalisés et proposés aux communautés LTT et du noyau Linux afin de bénéficier de leurs commentaires. À travers les phases de son développement, LTTng est testé avec des charges de travail extrêmes, et l'utilisation de bancs d'essais en performance permettent de s'assurer que l'impact du traceur se situe dans des limites acceptables. La vérification de modèle est utilisée afin de vérifier formellement les algorithmes de synchronisation de tampons quant à leur exactitude ainsi que d'assurer l'absence de famine.

Tôt dans le développement, j'ai identifié le besoin de découpler l'instrumentation du traceur, dans le but de permettre à des contributeurs externes et experts de procéder à l'instrumentation de chaque sous-système du noyau. C'est pourquoi j'ai créé les Kernel Markers et Tracepoints afin de permettre de gérer cette instrumentation et aider à l'ajout d'instrumentation dans le noyau Linux. Ces infrastructures sont maintenant intégrées dans le noyau Linux et utilisées largement par la communauté de développeurs Linux.

Plusieurs prototypes de traceur pour l'espace usager ont également été réalisés au cours de ce projet. Le projet UST (*User-Space Tracer*) présentement en cours bénéficie de l'expérience acquise via l'implantation de ces prototypes, réutilisant l'algorithme de synchronisation de tampons de LTTng ainsi que les mécanismes de *Kernel Markers* et *Tracepoints*. Un aspect clé de la conception du traceur LTTng pour permettre la mise à l'échelle et un faible impact sur les performances est l'utilisation de RCU (Read-Copy Update) pour la synchronisation de l'accès en lecture aux données de contrôle du traçage. Cependant, puisque ce mécanisme était inexistant en espace usager, nous avons conçu de nouveaux algorithmes permettant à RCU d'être utilisé dans ce contexte plus contraint. Ce travail a été effectué en collaboration avec Paul E. McKenney, Alan Stern et Jonathan Walpole. J'ai procédé à la mise en application de ces algorithmes en les implantant dans une librairie de synchronisation RCU offrant des services similaires à ceux de l'implantation du noyau Linux.

Vu la complexité des algorithmes de RCU et de synchronisation de tampon de LTTng, procéder à leur vérification formelle est souhaitable afin d'augmenter le niveau de confiance dans leur implantation. J'ai donc entrepris la tâche de créer un modèle de processeurs avec accès mémoire et exécution faiblement ordonnés, afin d'assurer l'exactitude et le progrès au plus bas niveau, tout en restant assez général pour assurer la portabilité de l'implantation des algorithmes.

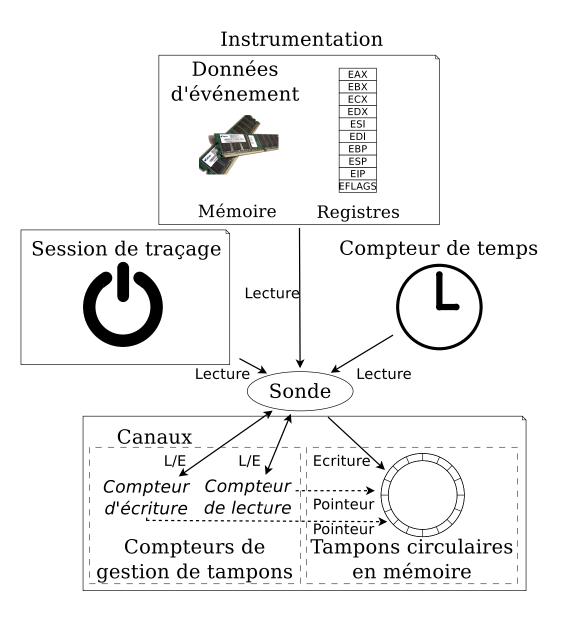

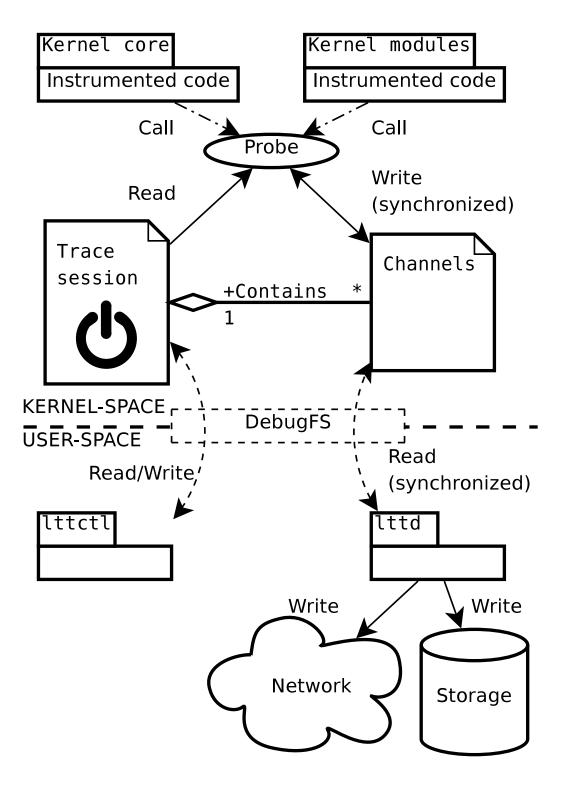

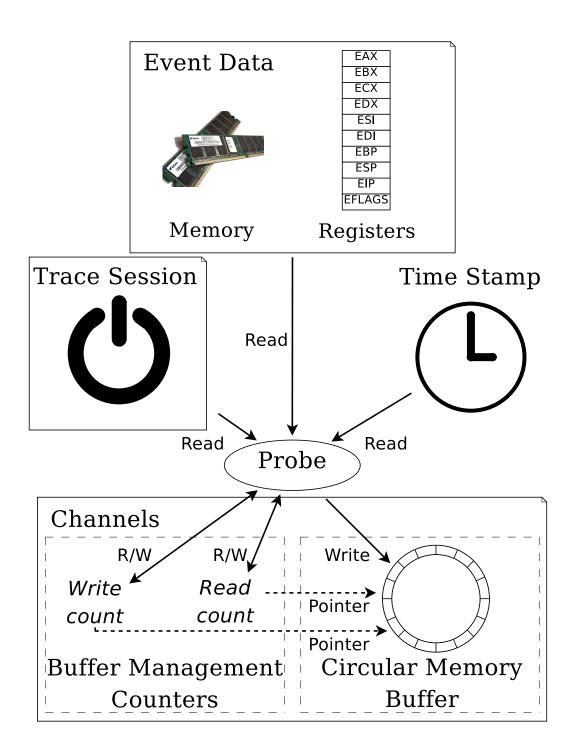

Afin de s'assurer que le traceur respecte l'ensemble de ces propriétés, il faut s'attarder à chaque mécanisme qui le composent, tant au niveau du support à l'instrumentation, de la lecture de temps, du contrôle du traçage que de la synchronisation des tampons. Ces mécanismes sont coordonnés par l'exécution de la *sonde (probe)*. Le schéma fonctionnel de celle-ci se retrouve à la Figure 0.1.

Au niveau de l'instrumentation, j'ai créé les mécanismes de Tracepoints et Linux

Figure 0.1 Schéma fonctionnel de la sonde LTTng

Kernel Markers. Ceux-ci dépendent du mécanisme de synchronisation RCU de manière extensive pour assurer la cohérence des données pointant vers les fonctions de rappels. L'exécution de ces primitives implique donc l'utilisation d'un verrou en lecture RCU, lequel est sans attente et pouvant être mis à l'échelle linéairement.

Afin de minimiser l'impact sur l'exécution du noyau Linux lorsque l'instrumentation est désactivée, j'ai créé le mécanisme *Immediate Values*, lequel permet l'activation de branchements en procédant à la modification dynamique d'instructions à l'exécution. Celui-ci se base sur une technique de détournement de l'exécution par *breakpoint* combiné avec une synchronisation des processeurs par interruption interprocesseurs, ce qui permet de conserver la caractéristique de réentrance.

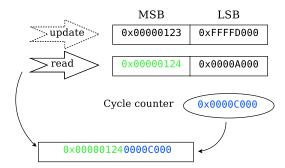

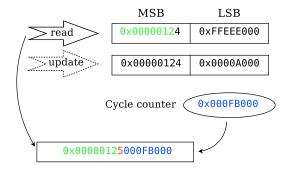

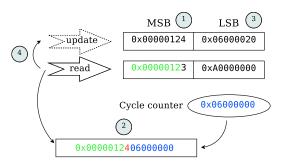

La source de temps utilisée est une lecture directe du compteur de cycles lorsque celui-ci est disponible. Cependant, lorsqu'il est nécessaire de compléter l'information de temps lue du matériel par de l'information complémentaire dans une structure de données en mémoire, il faut également procéder à une synchronisation des accès à cette structure. J'ai donc créé un mécanisme de gestion d'horloge de traçage permettant l' extension d'un compteur de cycles limité à 32 bits vers un compteur 64-bit complet en utilisant une technique basée sur les RCU. Ceci permet donc d'accéder à une base de temps sans toutefois perdre les propriétés recherchées, puisqu'un simple verrou en lecture RCU est requis.

Les accès aux structures de données de contrôle du traçage sont également synchronisés par le mécanisme de RCU, ce qui permet d'altérer le comportement du traçage alors que celui-ci est en cours d'exécution tout en conservant l'ensemble des propriétés recherchées.

Finalement, un composant d'importance majeure, duquel LTTng est formé, est le mécanisme de synchronisation de tampons. Celui-ci gère l'écriture de données dans un tampon partagé entre contextes d'exécution. Il est donc impossible d'utiliser un verrou en lecture RCU pour cette synchronisation, puisqu'il s'agit ici de synchroniser des écritures.

En s'assurant que chaque composant du traceur respecte les propriétés recherchées, on démontre, par construction, que le traceur dans son ensemble les respecte également.

L'expérimentation réalisée afin de s'assurer du respect des propriétés d'impact sur la mise à l'échelle, le débit, la latence moyenne, la réentrance et le comportement temps-réel est appliquées au mécanisme RCU ainsi qu'à la synchronisation de tampons. Ceci permet de s'assurer du respect des propriétés pour chaque composant. Cette expérimentation utilise deux approches : les bancs d'essai, pour les mesures de performances, et la vérification formelle par model-checking, pour procéder à la vérification des propriétés de réentrance et de comportement temps-réel.

Les bancs d'essais réalisés visent à mesurer l'impact sur la mise à l'échelle, le débit et la latence moyenne du système d'exploitation.

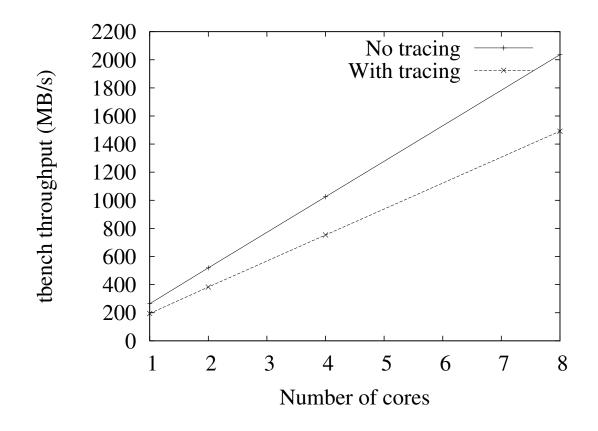

Un premier banc d'essai mesure la différence de débit d'une charge de travail offrant initialement de bonnes caractéristiques de mise à l'échelle avec et sans traçage. Les résultats obtenus sont que le débit augmente de manière linéaire avec et sans traçage de 1 à 8 nœuds, ce qui démontre la préservation de la caractéristique de mise à l'échelle de l'ensemble des mécanismes utilisés par le traceur. Des bancs d'essais spécialisés ont également permis de vérifier la mise à l'échelle linéaire des primitives de synchronisation en lecture RCU sur des configurations variant de 1 à 64 nœuds.

Un deuxième ensemble de bancs d'essais vise à déterminer l'impact sur le débit pouvant être soutenu par le système d'exploitation. L'exécution de charges de travail réseau, disque et de calcul mesurant le débit du système d'exploitation ou le temps requis pour effectuer une même tâche permet de caractériser ce débit. La comparaison des mesures avec et sans traçage permet de connaître l'impact du traceur sur ce débit. Dans des conditions d'exécution typique à haute fréquence d'événements, le ralentissement du débit système est, au plus, de 6%. Dans des cas extrêmes, le ralentissement peut atteindre 35%.

Une troisième série de bancs d'essais a pour but de mesurer l'impact du traçage d'un événement sur la latence moyenne du système d'exploitation. Cette série de bancs d'essais se subdivise en deux sous-parties : l'étude de la latence liée au traceur lorsque celui-ci est présent en antémémoire, ainsi que l'étude comparative de latence en fonctionnement normal avec une charge de travail en bruit de fond. Ceci a pour objectif de tenir compte des effets de cache dans l'analyse de l'impact en latence. Sur une architecture Intel Xeon doté d'une fréquence d'horloge de 2.0 GHz, on obtient comme résultats que le traceur a un impact sur la latence de 119 ns par événement lorsque le traceur est présent en antémémoire et de 333 ns par événement pour tracer une charge de travail standard.

Le second plan d'expérimentation est la vérification formelle d'une modélisation des algorithmes RCU et de synchronisation des tampons LTTng. Ce volet a pour objectif la vérification du bon fonctionnement de ces algorithmes (absence de corruption) ainsi que la vérification du progrès (absence de famine). L'impact d'algorithmes sur le comportement temp-réel peut se classer selon qu'ils soient bloquants ou non-bloquants. Dans la classe des algorithmes non-bloquants, on retrouve, en ordre croissant de garanties temps-réel, les algorithmes sans obstruction, sans verrou et sans attente. Les catégories d'intérêt dans notre cas sont les algorithmes sans verrou et sans attente. Un algorithme sans verrou assure un progrès global du système, alors qu'un algorithme sans attente assure le progrès de chaque processus considéré dans le système.

La vérification de modèles de synchronisation de tampons LTTng impliquant plusieurs écrivains, ainsi que la présence d'écrivains et de lecteurs, permet de confirmer que l'algorithme de synchronisation de LTTng est sans attente pour les écrivains. C'est-à-dire que ni un lecteur, ni un autre écrivain concurrent ne peut causer la famine d'un écrivain. Cette propriété s'applique aux implantations noyau, puisqu'il est possible de désactiver l'ordonnanceur. Il est également démontré que l'impossibilité de désactiver l'ordonnanceur en espace usager élimine la garantie de type "sans attente", rendant une telle implantation seulement "sans verrou", puisqu'il devient possible pour un écrivain concurrent de causer la famine d'un autre écrivain.

La vérification d'un modèle adapté aux primitives de synchronisation RCU permet de s'assurer qu'un lecteur RCU est également sans attente.

L'impact sur la réentrance du traceur est vérifié à l'aide des modèles d'exécution de processus concurrents utilisés pour vérifier le comportement correct et l'absence d'interblocage lors de l'exécution de paires de processus. Ceux-ci couvrent les cas d'exécution de multiples interruptions entre deux étapes atomiques, ce qui permet d'assurer l'absence d'interblocage dans tous les cas. Ces mêmes modèles sont utilisés pour vérifier l'absence de corruption causée par des accès concurrents des tampons en écriture et lecture.

Des modèles similaires sont utilisés pour vérifier les propriétés des mécanismes de synchronisation RCU. Les résultats démontrent que tant RCU que le mécanisme de synchronisation d'accès aux tampons de LTTng supportent la réentrance de gestionnaires d'interruptions NMI.

Afin d'augmenter la précision du modèle RCU quant à la représentation des effets d'accès mémoire et d'exécution faiblement ordonnés des architectures modernes, nous avons créé deux modèles d'architectures : *OoOmem* et *OoOisched*. Ceci permet de vérifier que les barrières mémoires ainsi que les barrières restreignant les optimisations du compilateur sont adéquates en vérifiant toutes les traces possibles d'exécution respectant les contraintes exprimées dans le modèle.

Le déploiement et l'expérimentation sur les architectures Intel 32/64-bit, PowerPC 32/64-bit, ARM, MIPS, Sparc64 ainsi que les contributions externes pour SH, S/390 ainsi que S/390x permettent de confirmer la portabilité de LTTng. Les prototypes de traçage rapide en espace usager et pour l'hyperviseur Xen que j'ai réalisés démontrent également la portabilité et la réutilisabilité des algorithmes créés dans des environnements d'exécution variés.

Puisque chacune des composantes satisfait les propriétés recherchées, que ce soit en utilisant RCU pour la synchronisation ou bien le mécanisme de synchronisation de tampons pour l'écriture, nous pouvons affirmer, par construction, que le traceur respecte toutes les propriétés recherchées.

La satisfaction de ces propriétés ouvre des champs d'utilisations diversifiés. La discussion qui suit fait le lien entre chacune des propriétés et les champs d'applications ciblés. Les propriétés de faible impact sur les performances (latence, débit et mise à l'échelle linéaire) ciblent les serveurs commerciaux qui nécessitent une surveillance constante du bon fonctionnement des systèmes en production utilisant Linux. Ceci permet à des compagnies comme Google d'identifier plus aisément la cause de problèmes de fonctionnement et de performance. Cependant, pour laisser un traceur actif en tout temps sur ces serveurs opérationnels en production, il faut avoir un impact minimal sur leurs performances. Des besoins similaires sont évoqués dans les applications à contraintes de temps douces chez Autodesk, lequels utilisent actuellement LTTng. Ericsson collaborent pour rendre LTTng utilisable dans leurs systèmes de télécommunication. Les développeurs de Siemens dépendent également, de leur côté, de LTTng pour certains de leurs produits sous Linux.

Les garanties temps-réel permettent également au domaine des systèmes tempsréel d'utiliser le traceur LTTng pour des fins de déverminage et d'analyse des systèmes comportant des contraintes de temps. C'est ce que font actuellement les distributions Linux de Wind River, Monta Vista et STLinux en intégrant LTTng comme outil de traçage à leur distribution visant le marché temps-réel. Ils permettent ainsi à leurs utilisateurs d'obtenir une information sur le comportement du système d'exploitation similaire à ceux retrouvés dans les autres systèmes d'exploitation temps-réels usuels. La portabilité du traceur LTTng permet son intégration dans la plate-forme de développement Maemo pour les téléphones cellulaires et tablettes Internet de Nokia.

La réentrance accrue du traceur bénéficie à la communauté de développeurs Linux,

leur permettant d'ajouter des points d'instrumentation sans se soucier de l'interaction du traceur avec le site instrumenté. Ceci bénéficie également aux utilisateurs Linux, les assurant que leur noyau ne cessera pas de fonctionner lors qu'ils activent le traceur. Ceci leur permet d'avoir une infrastructure de traçage en laquelle ils peuvent avoir confiance.

Toutes ces applications de LTTng démontrent qu'il remplit un besoin de traçage noyau à faible impact dans plusieurs champs d'application de l'industrie. Une conséquence de cette recherche est donc d'améliorer les infrastructures de déverminage pour les systèmes multi-cœurs, rendant disponible un outil qui permet de trouver les goulots d'étranglement de performance. Ceci permet une accélération des applications en trouvant toutes sortes d'utilisations inefficaces des ressources, ce qui aide à améliorer le temps de réponse, la réponse temps-réel, le débit système ainsi que l'efficacité énergétique des systèmes.

Cette recherche a eu des impacts autres que ceux directement reliés au traceur LTTng. Les Local Atomic Operations, Kernel Markers et Tracepoints ont chacun contribué à d'autres champs d'application et d'autres projets. Le traçage de l'espace usager, bien que périphérique à la cible principale de cette recherche, a été un champs dans lequel nous avons également innové. Au niveau de la contribution scientifique, 5 articles provenant d'auteurs externes ayant utilisé LTTng dans leur expérimentation ont été répertoriés à ce jour. Dans ces articles, LTTng a été utilisé à des fins variées, en permettant l'analyse de la consommation de puissance de pilotes, l'analyse des habitudes des utilisateurs et l'analyse de la précision des sources de temps.

La principale réalisation de cette recherche est la création d'algorithmes de synchronization novateurs rendant possible l'implantation du traceur LTTng pour le système d'exploitation Linux. Ce traceur satisfait les propriétés de faible impact sur la mise à l'échelle, le débit et la latence moyenne du système d'exploitation, d'impact déterministe sur la réponse temps-réel, de portabilité vers des architectures variées et un haut niveau de réentrance. Des bancs d'essais en performance et la vérification formelle ont démontré que chaque composant du traceur satisfait ces propriétés. Ainsi, le traceur LTTng répond à des requis auxquels ses prédécesseurs ne répondaient que partiellement, ce qui rend possible le traçage du système d'exploitation Linux, dont la flexibilité permet son utilisation dans un large spectre de champs d'application.

Il a été possible d'atteindre ces objectifs en procédant à un choix parcimonieux, à l'élaboration et à l'implantation de mécanismes de synchronisation : RCU pour la syn-

chronisation en lecture et le mécanisme de synchronisation de tampons de LTTng pour l'écriture. Les algorithmes utilisés dans ces deux mécanismes garantissent une mise à l'échelle linéaire et la non-attente, caractéristiques utiles pour le traçage de systèmes multi-cœurs ainsi que pour assurer un comportement temps-réel déterministe et une réentrance complète.

La réponse appropriée aux requis de traçage de l'industrie et de la communauté du logiciel libre est démontrée par le fait que divers composants de traçages que nous avons créé, les *Tracepoints* et *Linux Kernel Markers*, sont intégrés au noyau Linux et que le traceur LTTng bénéficie d'une large communauté d'utilisateurs et contributeurs, en particulier Google, IBM, Ericsson, Autodesk, Wind River, Fujitsu, Monta Vista, STMicroelectronics, C2 Microsystems, Sony, Siemens, Nokia et Recherche et développement pour la défense Canada.

En conclusion de cette recherche, nous pouvons affirmer que le traçage de charges de travail importantes sur un système d'exploitation à usage général s'exécutant sur des architectures multi-cœurs peut être accompli en n'utilisant qu'une fraction du débit et en n'augmentant la latence du système que faiblement, tout en conservant complètement la mise à l'échelle, la réponse temps-réel, la portabilité et la réentrance du système d'exploitation. L'implantation réalisée permet une couverture d'instrumentation du noyau dans son ensemble, incluant les gestionnaires d'interruptions non-masquables (NMIs).

L'analyse de traces du système dans son ensemble implique la collecte de traces à partir tant du noyau que de l'espace usager. Suite aux résultats prometteurs des prototypes de traçage usager réalisés, il est maintenant temps de stabiliser une telle infrastructure afin de permettre un traçage usager d'un niveau utilisable en production sous Linux.

Les charges de travail qui peuvent maintenant êtres tracées sur des systèmes en production permet la collecte d'information menant à l'analyse et la résolution de problèmes en comportement et en performance dans les systèmes complexes actuels. It sera intéressant d'explorer les analyses rendues possibles par une modélisation du système d'exploitation orientée par les données extraites par LTTng.

Vu son utilité dans le cadre de l'observation de systèmes, de l'identification de goulots d'étranglement en performance et en déverminage, la décision d'activer un traceur en tout temps sur des systèmes en production devient naturelle pour les développeurs système si la pénalité en performance est assez faible. Cette recherche

démontre clairement que l'impact du traceur LTTng, lorsqu'activé, est assez faible pour permettre son utilisation sur des systèmes en production faisant face à des charges de travail élevées, sans pour autant diminuer les performances de manière prohibitive.

## Contents

| Dedicati  | on                                               |

|-----------|--------------------------------------------------|

| Acknowl   | edgements                                        |

| Abstract  | v                                                |

| Résumé    | vii                                              |

| Condens   | é en français                                    |

| Contents  | 5xx                                              |

| List of 7 | Tables   xxv                                     |

| List of F | ligures                                          |

| List of A | lgorithms                                        |

| List of S | igns and Abbreviations                           |

| Chapter   | 1 Introduction                                   |

| 1.1       | Theoretical Framework                            |

| 1.2       | Problem                                          |

| 1.3       | Hypothesis                                       |

| 1.4       | Objectives                                       |

| 1.5       | Claim for Originality                            |

| 1.6       | Outline                                          |

| Chapter   | 2 State of the Art                               |

| 2.1       | Computer Architecture                            |

|           | 2.1.1 Parallelism                                |

|           | 2.1.2 Memory Access                              |

|           | 2.1.3 Software-Level Support for Multiprocessing |

| 2.2       | Real-time                                        |

| 2.3     | Distributed Systems                                                  | 11 |

|---------|----------------------------------------------------------------------|----|

| 2.4     | Commercial Servers                                                   | 12 |

| Chapter | r 3 Methodology                                                      | 13 |

| 3.1     | Interaction with the community                                       | 14 |

|         | 3.1.1 Tracing in the Industry                                        | 15 |

|         | 3.1.2 Tracing in the Open-Source Community                           | 16 |

|         | 3.1.3 Authored publications                                          | 16 |

|         | 3.1.4 Co-authored publications                                       | 17 |

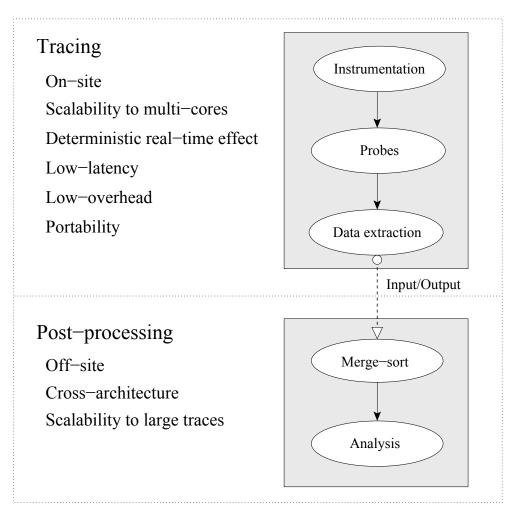

| 3.2     | Tracer Architecture                                                  | 17 |

|         | 3.2.1 Overview                                                       | 17 |

|         | 3.2.2 Instrumentation                                                | 19 |

|         | 3.2.3 Synchronization Primitives                                     | 21 |

|         | 3.2.4 Buffering                                                      | 21 |

|         | 3.2.5 Read-Copy Update                                               | 22 |

| 3.3     | Experimentation                                                      | 23 |

|         | 3.3.1 Benchmarks                                                     | 23 |

|         | 3.3.2 Formal Verification                                            | 24 |

| Chapter | r 4 Paper 1: Synchronization for Fast and Reentrant Operating System |    |

| Chapter | Kernel Tracing                                                       | 25 |

| 4.1     | Abstract                                                             | 25 |

| 4.2     | Introduction                                                         | 25 |

| 4.3     | Introduction to Tracing                                              | 27 |

| 4.4     | State of the Art                                                     | 28 |

| 4.5     | Linux Trace Toolkit Next Generation                                  | 34 |

| 4.6     | Tracing Synchronization                                              | 35 |

|         | 4.6.1 Atomic Primitives                                              | 35 |

|         | 4.6.2 Recursion with the Operating System Kernel                     | 38 |

|         | 4.6.3 Timekeeping                                                    | 39 |

| 4.7     | Benchmarks                                                           | 46 |

| 4.8     | Least Priviledged Execution Contexts                                 | 50 |

| 4.9     | Conclusion                                                           | 50 |

| Chapter | 5 Pap   | per 2: Lockless Multi-Core High-Throughput Buffering Scheme for                                                                                  |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Ke      | rnel Tracing                                                                                                                                     |

| 5.1     | Introdu | $1 ction \dots \dots$                      |

| 5.2     | State o | f the art $\ldots \ldots 59$                          |

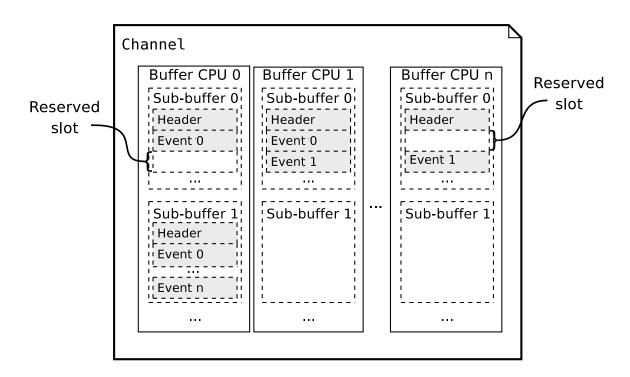

| 5.3     | Design  | of LTTng 62                                                                                                                                      |

|         | 5.3.1   | Components overview                                                                                                                              |

|         | 5.3.2   | Channels                                                                                                                                         |

|         | 5.3.3   | Control                                                                                                                                          |

|         | 5.3.4   | Probe Data Flow                                                                                                                                  |

| 5.4     | Atomic  | Buffering Scheme                                                                                                                                 |

|         | 5.4.1   | Atomic data structures                                                                                                                           |

|         | 5.4.2   | Equations $\ldots \ldots \ldots$ |

|         | 5.4.3   | Algorithms                                                                                                                                       |

|         | 5.4.4   | Memory Barriers                                                                                                                                  |

|         | 5.4.5   | Buffer allocation                                                                                                                                |

| 5.5     | Experi  | mental results                                                                                                                                   |

|         | 5.5.1   | Methodology                                                                                                                                      |

|         | 5.5.2   | Probe CPU-cycles overhead                                                                                                                        |

|         | 5.5.3   | tbench                                                                                                                                           |

|         | 5.5.4   | Scalability                                                                                                                                      |

|         | 5.5.5   | dbench                                                                                                                                           |

|         | 5.5.6   | lmbench                                                                                                                                          |

|         | 5.5.7   | gcc                                                                                                                                              |

|         | 5.5.8   | Comparison                                                                                                                                       |

| 5.6     | Conclu  | sion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$                                                      |

| Chapter | 6 Pap   | per 3: User-Level Implementations of Read-Copy Update 97                                                                                         |

| 6.1     | Introdu | $action \dots \dots$                       |

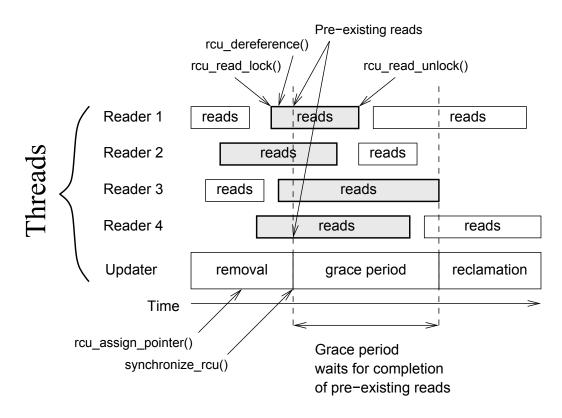

| 6.2     | Brief C | Overview of RCU                                                                                                                                  |

|         | 6.2.1   | Conceptual View of RCU Algorithms                                                                                                                |

|         | 6.2.2   | User-Space RCU Desiderata                                                                                                                        |

|         | 6.2.3   | RCU Deletion From a Linked List                                                                                                                  |

|         | 6.2.4   | Overview of RCU Semantics                                                                                                                        |

| 6.3     | User-S  | pace RCU Usage Scenarios                                                                                                                         |

### xxiii

| 6.4        | Classe  | s of RCU Implementations                                      | 107 |

|------------|---------|---------------------------------------------------------------|-----|

|            | 6.4.1   | Notation                                                      | 107 |

|            | 6.4.2   | Quiescent-State-Based Reclamation RCU                         | 109 |

|            | 6.4.3   | General-Purpose RCU                                           | 112 |

|            | 6.4.4   | Low-Overhead RCU Via Signal Handling                          | 117 |

|            | 6.4.5   | Wait-Free RCU Updates                                         | 123 |

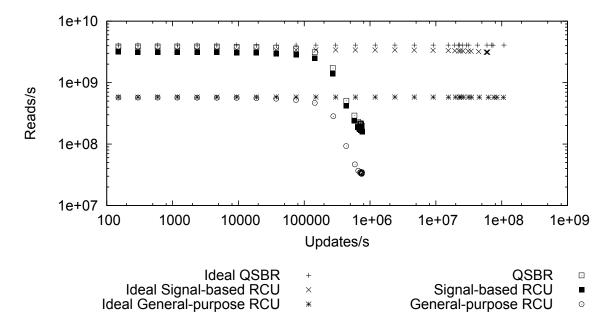

| 6.5        | Experi  | imental Results                                               | 124 |

|            | 6.5.1   | Scalability                                                   | 125 |

|            | 6.5.2   | Read-Side Critical Section Length                             | 126 |

|            | 6.5.3   | RCU Grace-Period Batch Calibration                            | 128 |

|            | 6.5.4   | Update Overhead                                               | 129 |

| 6.6        | Conclu  | usions                                                        | 132 |

| Ackr       | nowledg | gement                                                        | 134 |

| Lega       | l State | ment                                                          | 134 |

| Classic    | 7 D.    |                                                               | ſ   |

| Chapter    |         | aper 4: Multi-Core Systems Modeling for Formal Verification o |     |

| <b>P</b> 1 |         | rallel Algorithms                                             | 135 |

| 7.1        |         | uction                                                        | 135 |

| 7.2        |         | ing Challenges                                                | 136 |

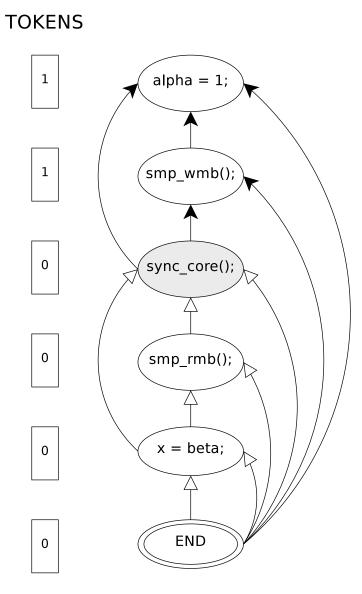

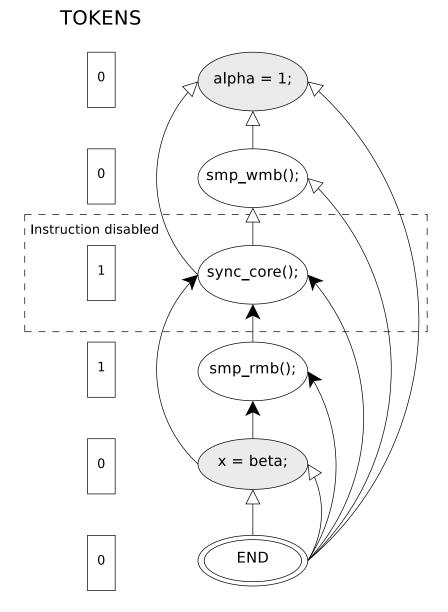

| 7.3        |         | ing and Model-Checking                                        | 137 |

|            | 7.3.1   | LTL Model-Checking                                            | 137 |

| - 4        | 7.3.2   | Introduction to Parallel Algorithm Modeling                   | 139 |

| 7.4        |         | y-Ordered Memory Framework                                    | 142 |

|            | 7.4.1   | Architecture                                                  | 142 |

|            | 7.4.2   | Testing                                                       | 145 |

| 7.5        |         | f-Order Instruction Scheduling Framework                      | 146 |

|            | 7.5.1   | Architecture                                                  | 146 |

|            | 7.5.2   | Testing                                                       | 149 |

| 7.6        |         | Copy Update Algorithm Modeling                                | 155 |

|            | 7.6.1   | State-Space Compression                                       | 160 |

|            | 7.6.2   | RCU Model-Checking Results                                    | 161 |

|            | 7.6.3   | RCU Verification Discussion                                   | 166 |

| 7.7        | Frame   | work Discussion                                               | 167 |

| 7.8        | Conclu  | usion                                                         | 168 |

#### xxiv

| Ackr    | nowledgement                       | 169   |

|---------|------------------------------------|-------|

| Lega    | l Statement                        | 169   |

|         |                                    | . – . |

| Chapter | 1 0                                | 170   |

| 8.1     | Kernel Markers                     | 170   |

| 8.2     | Tracepoints                        | 171   |

| 8.3     | Immediate Values                   | 172   |

| 8.4     | Analysis of LTTng Latency Impact   | 173   |

| 8.5     | Analysis of LTTng Real-Time Impact | 175   |

| 8.6     | Formal verification of LTTng       | 177   |

|         | 8.6.1 Modeling                     | 178   |

|         | 8.6.2 Correctness                  | 179   |

|         | 8.6.3 Real-Time Impact             | 180   |

| 8.7     | Reentrancy                         | 182   |

|         |                                    |       |

| Chapter | 9 General Discussion               | 184   |

| 9.1     | Tracer Properties                  | 184   |

| 9.2     | Tracer Application Domains         | 185   |

| 9.3     | Contributions                      | 187   |

|         | 9.3.1 Local Atomic Operations      | 187   |

|         | 9.3.2 Kernel Markers               | 188   |

|         | 9.3.3 Tracepoints                  | 188   |

|         | 9.3.4 Fast User-space Tracing      | 189   |

| 9.4     | Scientific Studies Using LTTng     | 190   |

| Chapter | 10 Conclusion and Recommendations  | 191   |

| -       | References                         | 193   |

## List of Tables

| Table 4.1 | Benchmark comparison between locking primitives and added                           |     |

|-----------|-------------------------------------------------------------------------------------|-----|

|           | inner operations, on Intel Xeon E5405                                               | 52  |

| Table 4.2 | Cycles taken to execute ${\tt CAS}$ compared to interrupt disabling $% {\tt CAS}$ . | 53  |

| Table 4.3 | Breakdown of cycles taken for spin lock disabling interrupts .                      | 54  |

| Table 4.4 | Breakdown of cycles taken for using a read $seqlock$ and using a                    |     |

|           | synchronized CAS                                                                    | 55  |

| Table 4.5 | Breakdown of cycles taken for disabling preemption and using                        |     |

|           | a local CAS                                                                         | 56  |

| Table 4.6 | Speedup of tracing synchronization primitives compared to dis-                      |     |

|           | abling interrupts and spin lock                                                     | 56  |

| Table 5.1 | Cycles taken to execute a LTTng 0.140 probe, Linux 2.6.30 $$                        | 87  |

| Table 5.2 | $tbench$ client network throughput tracing overhead $\ldots$ .                      | 88  |

| Table 5.3 | ${\tt tbench}$ local<br>host client/server throughput tracing overhead              | 89  |

| Table 5.4 | dbench disk write throughput tracing overhead $\ldots$                              | 90  |

| Table 5.5 | Linux kernel compilation tracing overhead $\ldots \ldots \ldots \ldots$             | 93  |

| Table 5.6 | Comparison of lockless and interrupt disabling LTTng probe ex-                      |     |

|           | ecution time overhead, Linux $2.6.30 \ldots \ldots \ldots \ldots \ldots \ldots$     | 94  |

| Table 7.1 | General-purpose ${\tt RCU}$ verification results for the Alpha architec-            |     |

|           | ture                                                                                | 162 |

| Table 7.2 | General-purpose ${\tt RCU}$ verification results for the Intel/PowerPC              |     |

|           | architectures                                                                       | 163 |

| Table 7.3 | Signal-based $\mathtt{RCU}$ verification results for the Alpha architecture         | 163 |

| Table 7.4 | Signal-based $\mathtt{RCU}$ verification results for the Intel/PowerPC ar-          |     |

|           | chitectures                                                                         | 164 |

| Table 7.5 | General-purpose ${\tt RCU}$ signal-handler reader nested over reader                |     |

|           | verification (no instruction scheduling) $\ldots \ldots \ldots \ldots \ldots$       | 165 |

| Table 7.6 | General-purpose ${\tt RCU}$ signal-handler reader nested over updater               |     |

|           | verification (no instruction scheduling) $\ldots \ldots \ldots \ldots \ldots$       | 165 |

| Table 8.1 | Tracer latency overhead for a ping round-trip. Local host,                          |     |

|           | Linux 2.6.30.9, 100,000 requests sample, at 2 ms interval $\ .$ .                   | 174 |

| Table 8.2 | Tracer latency overhead for a ping round-trip. 100 Mb/s net-  |     |

|-----------|---------------------------------------------------------------|-----|

|           | work, tracing receiver host only, Linux 2.6.30.9, 100,000 re- |     |

|           | quests sample, at 2 ms interval                               | 175 |

# List of Figures

| Figure 0.1 | Schéma fonctionnel de la sonde LTTng                                              | xii |

|------------|-----------------------------------------------------------------------------------|-----|

| Figure 3.1 | Tracer architecture diagram                                                       | 18  |

| Figure 4.1 | Trace clock read (no $32^{nd}$ bit overflow)                                      | 42  |

| Figure 4.2 | Trace clock read ( $32^{nd}$ bit overflow)                                        | 42  |

| Figure 4.3 | Trace clock update $(1, 3, 4)$ interrupted by a read $(2)$                        | 42  |

| Figure 4.4 | Synthetic clock read-side                                                         | 43  |

| Figure 4.5 | Synthetic clock periodic update                                                   | 45  |

| Figure 4.6 | Assembly listings for Intel Xeon benchmarks (CAS loop content)                    | 52  |

| Figure 4.7 | Assembly listings for Intel Xeon benchmarks (interrupt save/res-                  |     |

|            | tore loop content) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 53  |

| Figure 4.8 | Assembly listings for Intel Xeon benchmarks (spin lock loop                       |     |

|            | $\operatorname{content}$ )                                                        | 54  |

| Figure 4.9 | Assembly listings for Intel Xeon benchmarks (sequence lock and                    |     |

|            | preemption disabling loop content) $\ldots \ldots \ldots \ldots \ldots \ldots$    | 55  |

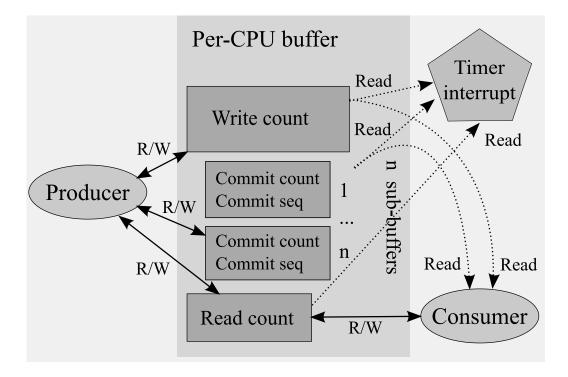

| Figure 5.1 | Tracer components overview                                                        | 64  |

| Figure 5.2 | Channel components                                                                | 66  |

| Figure 5.3 | Probe data flow                                                                   | 68  |

| Figure 5.4 | Producer-consumer synchronization                                                 | 71  |

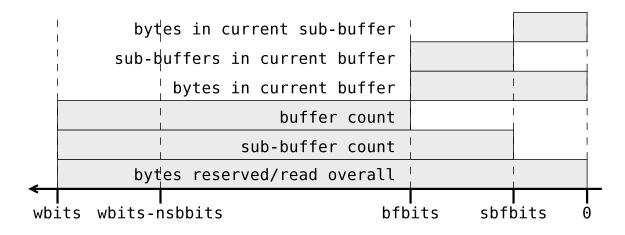

| Figure 5.5 | Write and read counter masks                                                      | 74  |

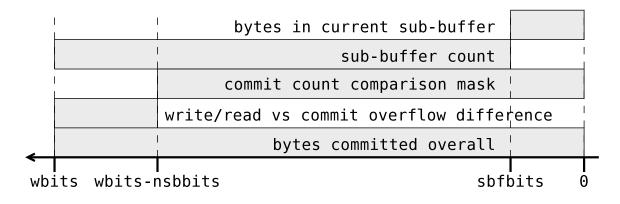

| Figure 5.6 | Commit counter masks                                                              | 75  |

| Figure 5.7 | Impact of tracing overhead on localhost tbench workload scal-                     |     |

|            | ability                                                                           | 90  |

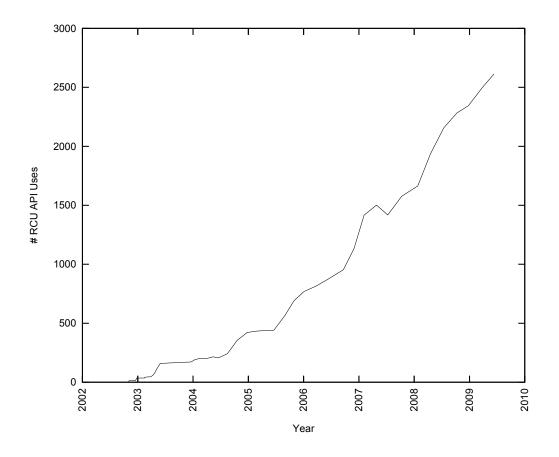

| Figure 6.1 | Linux-kernel usage of RCU                                                         | 99  |

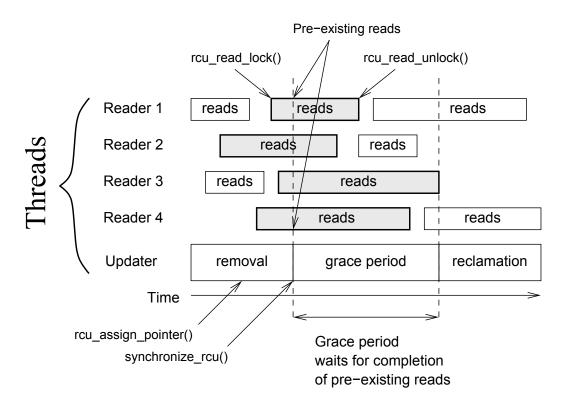

| Figure 6.2 | Schematic of RCU grace period and read-side critical sections                     | 100 |

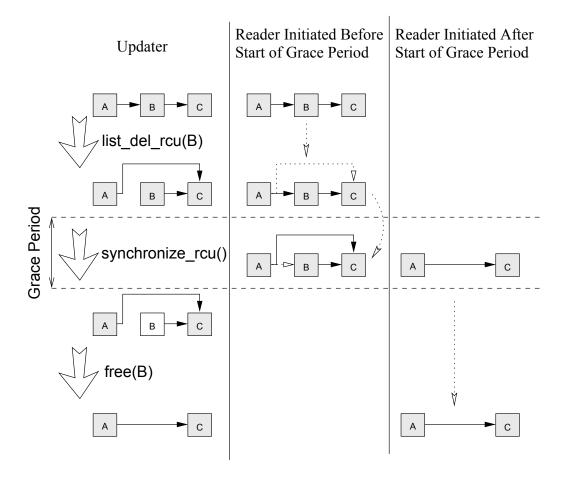

| Figure 6.3 | RCU linked-list deletion                                                          | 103 |

| Figure 6.4 | RCU read side using quiescent states                                              | 108 |

| Figure 6.5 | RCU update side using quiescent states                                            | 110 |

| Figure 6.6 | RCU read side using memory barriers                                               | 113 |

| Figure 6.7 | RCU update side using memory barriers                                             | 114 |

| Figure 6.8 | RCU read side using signals                                                       | 118 |

### xxviii

| Figure 6.9  | RCU signal handling                                                                                                        | 119 |

|-------------|----------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.10 | RCU update side using signals                                                                                              | 121 |

| Figure 6.11 | Avoiding update-side blocking by RCU                                                                                       | 123 |

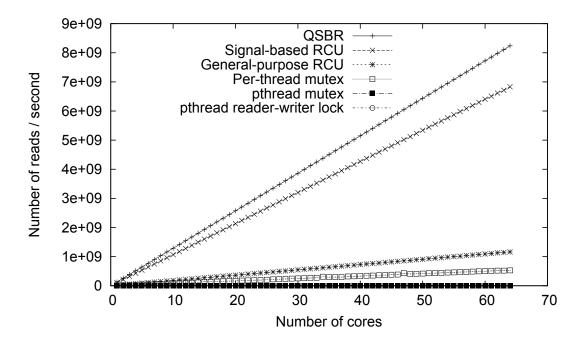

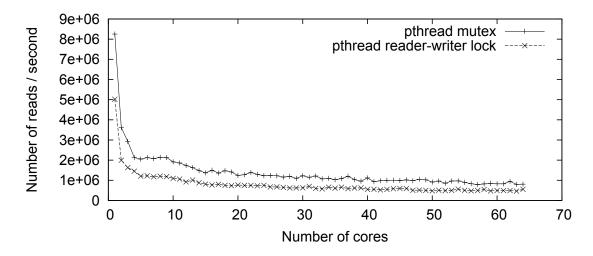

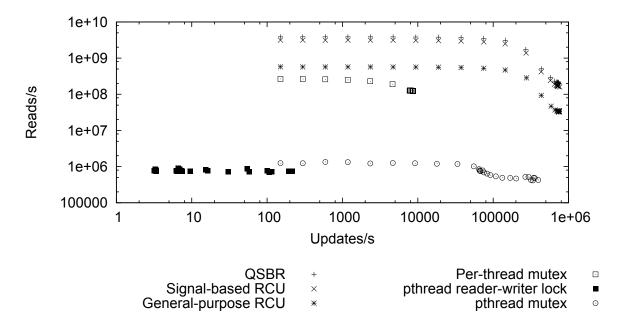

| Figure 6.12 | Read-side scalability of various synchronization primitives, 64-                                                           |     |

|             | core POWER5+                                                                                                               | 125 |

| Figure 6.13 | Read-side scalability of mutex and reader-writer lock, 64-core                                                             |     |

|             | POWER5+                                                                                                                    | 126 |

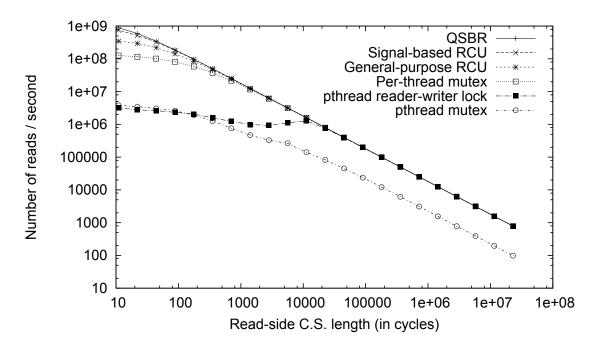

| Figure 6.14 | Impact of read-side critical section length, 8-core Intel Xeon,                                                            |     |

|             | logarithmic scale                                                                                                          | 127 |

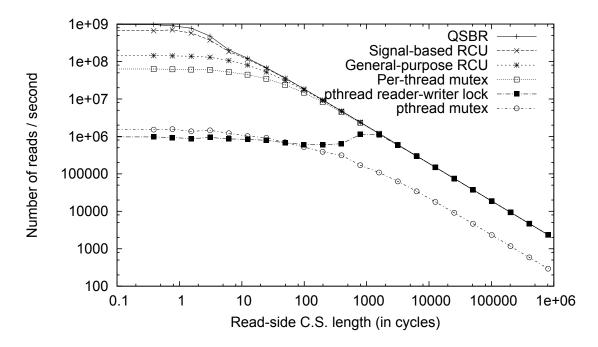

| Figure 6.15 | Impact of read-side critical section length, 8 reader threads on                                                           |     |

|             | POWER5+, logarithmic scale                                                                                                 | 128 |

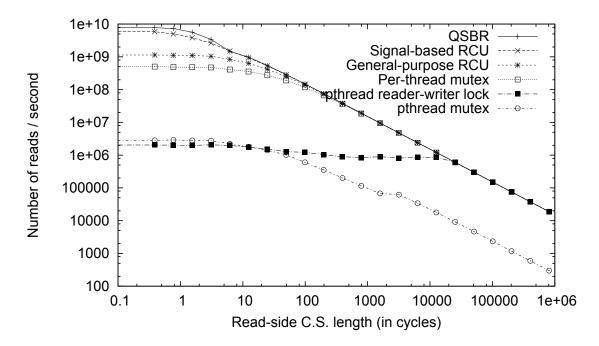

| Figure 6.16 | Impact of read-side critical section length, 64 reader threads on                                                          |     |

|             | POWER5+, logarithmic scale                                                                                                 | 129 |

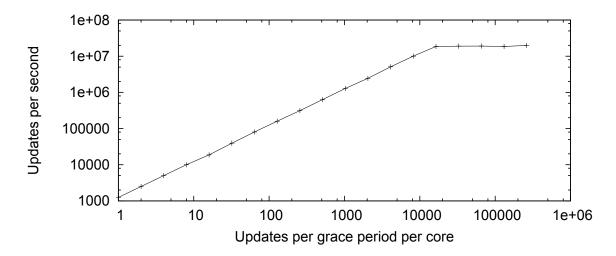

| Figure 6.17 | Impact of grace-period batch-size on number of update opera-                                                               |     |

|             | tions, 8-core Intel Xeon, logarithmic scale                                                                                | 130 |

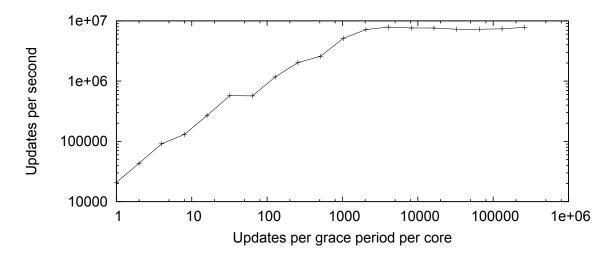

| Figure 6.18 | Impact of grace-period batch-size on number of update opera-                                                               |     |

|             | tions, 64-core POWER5+, logarithmic scale $\ldots$ $\ldots$ $\ldots$                                                       | 130 |

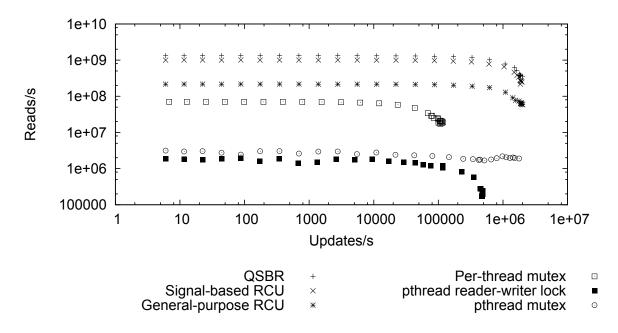

| Figure 6.19 | Update overhead, 8-core Intel Xeon, logarithmic scale                                                                      | 131 |

| Figure 6.20 | Impact of pointer exchange on update overhead, 8-core Intel                                                                |     |

|             | Xeon, logarithmic scale                                                                                                    | 132 |

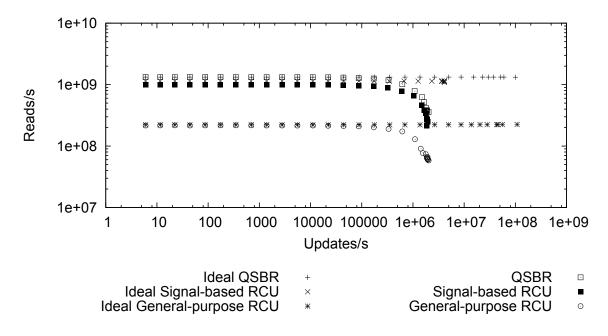

| Figure 6.21 | Update overhead, 64-core POWER5+, logarithmic scale $\ .$ .                                                                | 133 |

| Figure 6.22 | Impact of pointer exchange on update overhead, 64-core POW-                                                                |     |

|             | ER5+, logarithmic scale $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                              | 134 |

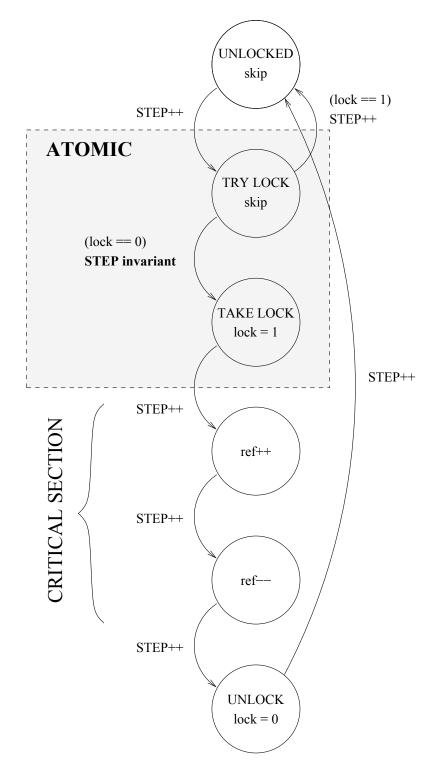

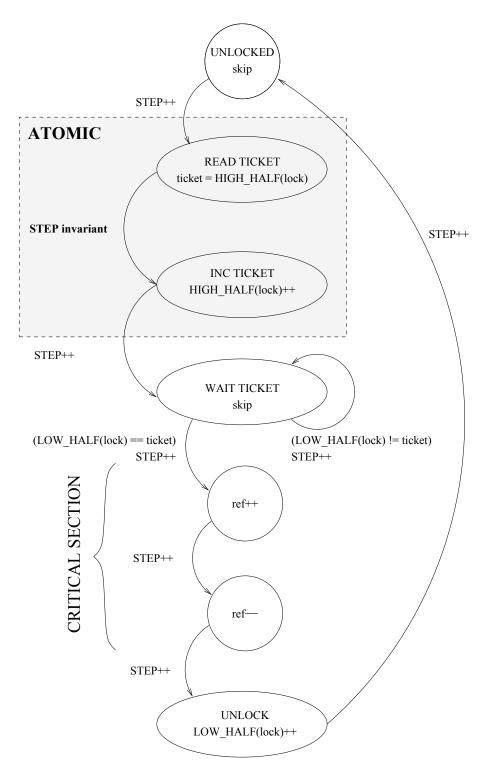

| Figure 7.1  | Promela model for PowerPC spinlock                                                                                         | 140 |

| Figure 7.2  | Diagram representation of PowerPC spinlock model                                                                           | 141 |

| Figure 7.3  | Diagram representation of Intel ticket spinlock model $\ . \ . \ .$                                                        | 143 |

| Figure 7.4  | Out-of-order instruction scheduling and memory frameworks                                                                  |     |

|             | promela test code, Processor A $\ \ldots \ \ldots$ | 151 |

| Figure 7.5  | Instruction dependencies of out-of-order instruction scheduling                                                            |     |

|             | and memory framework test $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                            | 152 |

| Figure 7.6  | Instruction dependencies of out-of-order instruction scheduling                                                            |     |

|             | and memory framework test (error injection)                                                                                | 153 |

| Figure 7.7  | Schematic of RCU grace period and read side critical sections                                                              | 157 |

# List of Algorithms

| Algorithm 5.1 | $\operatorname{TryReserveSlot}(payload\_size)$ | 77 |

|---------------|------------------------------------------------|----|

| Algorithm 5.2 | $ReserveSlot(payload_size)$                    | 78 |

| Algorithm 5.3 | COMMITSLOT(slot_size, slot_offset)             | 78 |

| Algorithm 5.4 | ForceSwitch()                                  | 80 |

| Algorithm 5.5 | ReadPoll()                                     | 81 |

| Algorithm 5.6 | ReadGetSubbuf()                                | 82 |

| Algorithm 5.7 | $ReadPutSubbuf(arg\_read\_count)$              | 82 |

| Algorithm 5.8 | AsyncWakeupReadersTimer()                      | 84 |

# List of Signs and Abbreviations

| API                  | Application Programming Interface            |

|----------------------|----------------------------------------------|

| BIOS                 | Basic Input/Output System                    |

| BDD                  | Binary Decision Diagram                      |

| CAS                  | Compare-And-Swap                             |

| CISC                 | Complex Instruction Set Computer             |

| CPU                  | Central Processing Unit                      |

| DFA                  | Deterministic Finite Automaton               |

| GNU                  | GNU's Not Unix                               |

| $\operatorname{GPL}$ | GNU General Public License                   |

| GPS                  | Global Positioning System                    |

| HTM                  | Hardware Transactional Memory                |

| IBM                  | International Business Machines              |

| IRQ                  | Interrupt Request                            |

| IPI                  | Interprocessor Interrupt                     |

| I/O                  | Input/Output                                 |

| KVM                  | Kernel-based Virtual Machine                 |

| LGPL                 | GNU Lesser General Public License            |

| LTL                  | Linear Temporal Logic                        |

| LTTng                | Linux Trace Toolkit Next Generation          |

| LTTV                 | Linux Trace Toolkit Viewer                   |

| Mutex                | Mutual exclusion                             |

| MPI                  | Message Passing Interface                    |

| NAND                 | Not AND                                      |

| NMI                  | Non-Maskable Interrupt                       |

| NOR                  | Not OR                                       |

| NUMA                 | Non-Uniform Memory Access                    |

| OS                   | Operating System                             |

| POSIX                | Portable Operating System Interface for Unix |

| QSBR                 | Quiescent-State Based Reclamation            |

| RAM                  | Random Access Memory                         |

|                      |                                              |

| RCU  | Read-Copy Update                 |

|------|----------------------------------|

| RT   | Real-Time                        |

| RTAI | Real-Time Application Interface  |

| RISC | Reduced Instruction Set Computer |

| RP   | Relativistic Programming         |

| RPC  | Remote Procedure Call            |

| SMP  | Symmetric Multiprocessing        |

| SPE  | Synergistic Processing Element   |

| STM  | Software Transactional Memory    |

| TLS  | Thread-Local Storage             |

| UST  | User-Space Tracer                |

## Chapter 1

## Introduction

Growth in hardware and software complexity that industry of software development must cope with now turns debugging and performance monitoring into increasingly challenging tasks. The need for global system-wide problem diagnosis facilities emerges, but their associated high performance impact is usually frowned upon. This compromises their deployment on production systems, where processor time and input/output bandwidth must be fully utilized by the workload.

This increase in complexity and size has been a steady trend in computers since their appearance. At the hardware-level, multiprocessor systems become increasingly large and interconnection buses become more complex. At the software-level, operating system (OS), library, virtual machine and application layers contribute to this complexity. As a result, the effective complexity that software developers have to deal with, represented by the number of interactions between components, grows even faster.

### **1.1** Theoretical Framework

Debugging and performance monitoring tools are needed to provide insight into component interactions, to help diagnosing issues in those large complex systems. Tracing provides insight into interactions within system components. This technique can diagnose the most difficult performance problems and bugs in software development. It can provide both high-level and detailed views of the operating system (**OS**) as a whole and of each of its individual subsystems. It consists in collecting event records associated with time stamps, allowing to reconstruct the trace (a sequence of events) in the order events occurred. The major drawback of this technique is its heavy use of computer resources. It provides detailed system activity information, at the expense of system resources required to extract large amounts of data. As an observer, the challenge for a tracer is to minimally alter the original system behavior, hence permitting its reproducibility when the observer is active. This technique is therefore inherently limited by the portion of system resources required to perform tracing. Using faster computers does not solve the problem: newer architectures will be expected to execute workloads faster and will create new timing conditions by allowing execution of larger workloads. As a result, faster hardware does not improve tracer's ability to trace workloads, because the workload grows to fully use the available resources, mostly due to the evolution of application complexity. When supplementary computational resources are available, they will be allocated to the system's primary purpose rather than tracing.

This research is conducted within the GNU/Linux open-source operating system, which becomes increasingly popular in the industry. It is used on a wide variety of computer systems, from small embedded devices to large multiprocessor servers. Supporting a broad hardware diversity makes it subject to subtle compatibility breakages with specific hardware combinations. In order to deal with the complexity of software development, the operating system is the fruit of interaction of many individuals and companies part of an active developer community. Due to the increasing complexity of the operating system, the people who understand it globally are very rare. Even kernel developers specialize in areas (e.g. memory management, thread scheduling, block device layer, ...). Solving complex subsystem interaction problems therefore becomes a hard problem not only for the Linux users, but also for its own developer community.

This research addresses the need for system-wide problem diagnosis tools, grown from the increased hardware and software complexity. It focuses on the Linux operating system, a candidate already heavily used by the industry and presenting the complexity characteristics requiring such tools. The software development industry currently lacks the appropriate tools to diagnose problems requiring system-wide observability of the system. Tracing fills this need due to some of its unique features. It permits diagnosing performance problems and bugs introduced by the interactions between execution layers and different subsystems. Furthermore, a post-processing analysis approach, where all collected information is made available for a posteriori analysis, is elected to permit diagnosing bugs occurring rarely, which are amongst the hardest to identify.

### 1.2 Problem

Tracing the Linux operating system brings many challenges, which define the major problems inherent to tracing. These challenges are caused by the need for a system observer that minimally impact the system behavior.

As an initial point, tracer CPU usage must be kept low, so the majority of the CPU time can still be available for the traced workload. Also, exporting data outside of its producing execution context involves consuming bandwidth at many levels: various levels of caches, memory, and optionally disk and network input/output. This bandwidth consumption must also be kept within fractions of the amount of bandwidth used by the operating system traced.

Characteristics met by the operating system, such as support for real-time (increasingly supported by Linux Preempt-RT tree) and scalability to large number of processors (4096) must also be supported by a tracer aiming to meet the requirements faced by this operating system.

At the processor level, reentrancy of tracer operations with respect with concurrent execution contexts is required to ensure coherent data is collected. Moreover, data gathered from multiple processors must be synchronized to keep event ordering information for a posteriori analysis.

Instrumented parts of the operating system are used as calling sites to execute tracer code. This means that instrumentation coverage is directly limited by reentrancy of the tracer code. For example, instrumentation of kernel code executed from non-maskable interrupt (NMI) context require the tracer to be reentrant with respect to these interrupts.

Given that the kernel code executed, and thus the tracer usage, directly depends on the type of workload, it makes sense to principally consider the tracer impact on workloads representing various typical heavy system usage.

The problem studied in this work is the extraction of tracing data from an operating system, which involves collecting data from the operating system execution and streaming this information outside of the kernel. The aspects of the problem making its study worthwhile are the impacts of tracing (workload disruption) and the instrumentation coverage: which parts of the system can be instrumented.

### 1.3 Hypothesis

The hypothesis serving as starting point for this research is that it is possible to trace an operating system, which runs intensive workloads on large multiprocessor machines, using a small fraction of the resources, allowing to instrument any kernel and user-space code location and permitting to model the original workload behavior. This involves using a fraction of the operating system throughput and adding a constant small amount to its average latency, as well as preserving the following properties: scalability, real-time response, portability and reentrancy.

### 1.4 Objectives

The purpose of this study is to create a low-overhead, highly-reentrant and scalable tracer for Linux, a widely used operating system. It must be able to handle trace throughput generated by heavy workloads on multiprocessor systems. It must preserve, or modify within a small proportion, the Linux kernel characteristics.

The research objectives are detailed as follow:

- meet the industry and open source community tracing requirements,

- create new algorithms to solve the problems identified in industry,

- implement a tracer for Linux, an existent mainstream operating system,

- develop each tracer component so the tracer meets properties of preserving scalability and having a low-impact on the operating system throughput and average latency,

- guarantee a deterministic impact of tracing on real-time response,

- provide high portability and reentrancy of tracer mechanisms.

### 1.5 Claim for Originality

The main scientific contribution of this research is the creation of original synchronization algorithms suitable for tracing. The new algorithms created and the application of these algorithms to tracing is detailed as follows:

- creation of a wait-free, linearly scalable, and NMI-safe kernel buffering scheme,

- creation of an RCU-based trace clock permitting to atomically update current time information, which is larger than a word, atomically with respect to the

reader execution contexts, thus offering a wait-free, linearly scalable and NMI-safe time-source,

- design of a complete kernel tracer based on wait-free, linearly scalable and NMIsafe algorithms,

- application of self-modifying code techniques to dynamically enable and disable static instrumentation, with non-measurable overhead when disabled and low overhead when enabled, allowing NMI context instrumentation (presented in Section 8.3),

- improvements to the RCU (*Read-Copy Update*) synchronization mechanisms for efficient execution in user-space context, specifically proposing:

- 1. using signal-handlers to execute memory barriers only when waiting for a grace period, allowing fast read-side,

- 2. using TLS (*Thread-Local Storage*) to perform local RCU state access efficiently for reader threads.

- 3. chaining TLS data within a doubly linked-list to create a reader thread registry, allowing to detect quiescent state with O(1) thread registration and unregistration,

- creation of a generic architecture model for formal verification of parallel algorithms, modeling weakly-ordered memory accesses and instruction scheduling,

The careful design of synchronization primitives enables the creation of the LTTng tracer and of its components.

# 1.6 Outline

The state of the art is presented in Chapter 2, which focuses on the high-level aspects of tracing. The state of the art refers to each article's state-of-the-art section for in-depth per-subject literature review. Each contains a detailed review for its specific topic.

The methodology organizing this research is presented in Chapter 3. It explains how the tracing requirements were first identified by collaborating with the industry. It presents the tracer architecture developed to fulfill these requirements. The instrumentation requirements are then detailed, referring to Chapter 8 for the detailed presentation of this work not part of the four main articles. It then depicts an overview of the four articles.

The core of this thesis consists in four articles. Synchronization primitive choices for the kernel tracer are presented in the article "Synchronization for Fast and Reentrant Operating System Kernel Tracing" [1], in Chapters 4. This article is currently re-submitted after revision to Software – Practice and Experience. The reviewers recommended its publication, although acceptation depends on approval of modifications performed in the re-submitted version. The presentation of a lock-less buffering scheme using the results of the first article follows in the article "Lockless Multi-Core High-Throughput Buffering Scheme for Kernel Tracing" [2] in Chapter 5. It is currently submitted to ACM Transactions on Computer Systems (TOCS). Then, our implementations of the RCU (Read-Copy Update) synchronization mechanism for user-space are presented in the article "User-Level Implementations of Read-Copy Update" [3], in Chapter 6. This article is currently submitted to IEEE Transactions on Parallel and Distributed Systems (TPDS). An architecture-level model for formal parallel algorithm verification is presented in "Multi-Core Systems Modeling for Formal Verification of Parallel Algorithms" [4], in Chapter 7. This last article is also currently submitted to IEEE TPDS.

Chapter 8 presents additional results and discusses impacts of this research which are not presented in the four main articles. This includes conference publications, contributions to open source projects and external work based on the research results.

Chapter 9 discusses the results obtained from a high-level perspective. It shows links between the main results obtained in the individual articles.

Finally, the conclusion recall the progress realized, the principal research contributions and ends by proposing future work leveraging this research.

# Chapter 2

# State of the Art

This chapter first presents the major computer architecture aspects which impact the current research. Aiming at portability to different architectures implies taking into account multiprocessor system effects. Then, the main tracing systems available today will be classified in categories related to their target systems: parallel, distributed or real-time systems.